判定帰還型自動等化器評価装置および判定帰還型自動等化器評価方法

【課題】従来の判定帰還型自動等化器(DFE)の評価装置では、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することはできなかった。

【解決手段】

既知のデジタル入力信号を受けてDFEから出力されるデジタル信号をDFEの各タップに対応する信号タイミングにおいてサンプリングする信号サンプリング部と、

サンプリングされた前記デジタル信号から各タップ毎にデジタル信号のビット誤り率を測定するビット誤り率測定部とを備える。

【解決手段】

既知のデジタル入力信号を受けてDFEから出力されるデジタル信号をDFEの各タップに対応する信号タイミングにおいてサンプリングする信号サンプリング部と、

サンプリングされた前記デジタル信号から各タップ毎にデジタル信号のビット誤り率を測定するビット誤り率測定部とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、判定帰還型自動等化器を評価する装置及び判定帰還型児童等化器を評価する方法に関する。

【背景技術】

【0002】

デジタル信号は伝送路による様々な影響を受けて歪んでしまう。このようなデジタル信号の歪みに対処するための技術としてよく知られているものに、プリエンファシスや判定帰還型自動等化がある。プリエンファシスは、伝送路の影響による信号の歪みを見越して、信号が受信側に届いたときに最適な信号波形となるようにあらかじめ送信側で伝送路による信号の歪とは逆方向に積極的に信号を歪ませておく技術である。プリエンファシスは伝送路による信号への影響が既知であるときには有効な技術であるが、伝送路の影響が未知の場合や時間的に変動する場合には適用が困難である。

【0003】

一方、判定帰還型自動等化は、信号の受信側における技術であって、受信した信号をフィードバックして重み付け合成することにより伝送路による信号の歪みを除去しようとするものである。このような判定帰還型自動等化に特化した、判定帰還型自動等化器(Decision Feedback Equalizer、以下DFE)と呼ばれる専用回路がデジタル信号の受信側に組み込まれていることが多い。

【0004】

DFEの典型的な回路構成を図4に示す。図4のDFE回路は3個の遅延器と4個のタップによる4段のフィードバック回路によって構成されている。なお、遅延器やタップの個数は図4のものに限られず、様々な個数が利用可能である。各タップには可変増幅器が設けられ、これによって各タップを経由する信号が重み付け合成される。このとき各タップの重み付け係数をタップ係数と呼ぶ。このタップ係数を最適な値に調節することにより、DFEに入力される信号の歪みを除去して元の信号波形を復元する、すなわち等化することができる。

【0005】

DFEは例えば、コンピュータのインタフェース用のシリアル/パラレル変換回路(Serializer/Deserializer、以下SerDes)に組み込まれている。近年、インタフェースの伝送速度がますます高速化するにつれ、SerDesの高速動作性能に対する要求も厳しくなってきたが、その中でもDFEの等化性能がボトルネックとなることがある。そのため、インタフェースの開発者等は、SerDesに組み込まれたDFEが実装状態で適切に動作しているのかを検証することや、DFEがどれくらいの信号歪みまで等化できるのかの余裕度を評価する必要があった。

【0006】

DFEの等化性能を評価するための装置として、例えば、特許文献1に記載されているような装置が知られている。特許文献1に記載されている装置では、DFEの等化誤差を時間平均することによりDFEの等化性能の余裕度を算出している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2004−146975号公報(0033〜0041、図1)

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来のDFEの評価装置では、DFEの回路全体としての等化性能は評価可能であるものの、各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することはできなかった。

【0009】

本発明はこのような状況に鑑みて成されたものであり、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することを目的としている。

【課題を解決するための手段】

【0010】

上記の目的のため、本発明に係る判定帰還型自動等化器評価装置は、既知のデジタル入力信号を受けてDFEから出力されるデジタル信号を各タップにおける遅延時間に対応する信号タイミングにおいてサンプリングする信号サンプリング部と、信号サンプリング部によってサンプリングされたデジタル信号から、各タップ毎にデジタル信号のビット誤り率を測定するビット誤り率測定部とを備えている。

【0011】

また、上記の目的のため、本発明に係る判定帰還型自動等化器評価方法は、既知のデジタル入力信号を受けてDFEから出力されるデジタル信号を各タップにおける遅延時間に対応する信号タイミングにおいてサンプリングする段階と、サンプリングされた前記デジタル信号から、各タップ毎にデジタル信号のビット誤り率を測定する段階とを含んでいる。

【発明の効果】

【0012】

本発明の判定帰還型自動等化器評価装置または判定帰還型自動等化器評価方法によれば、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することができる。

【図面の簡単な説明】

【0013】

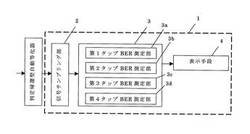

【図1】本発明の実施形態を示す判定帰還型自動等化器評価装置の構成図

【図2】本発明のサンプリング方法を示す説明図

【図3】本発明によるビット誤り率とビット誤りの個数の画面表示例

【図4】典型的なDFEの回路図

【発明を実施するための形態】

【0014】

以下、本発明の実施の形態を図1から図3に基いて説明する。

【0015】

図1は本発明の一実施形態である判定帰還型自動等化器評価装置の構成図である。

本発明の一実施形態である判定帰還型自動等化器評価装置(1)は、信号サンプリング部(2)、ビット誤り率測定部(3)および表示手段(4)から構成されている。

【0016】

信号サンプリング部(2)には、既知のデジタル入力信号を入力されたDFEからの出力信号が入力される。既知のデジタル入力信号は、例えば、信号発生器によって発生されたデジタル信号を用いることができる。

【0017】

DFEが例えばSerDesに実装された状態では、DFEの出力信号を直接に信号サンプリング部(2)に導くことは困難である場合が多い。この場合には例えば、SerDesが受信した信号をSerDes内部でループバックさせて出力した信号を信号サンプリング部(2)に導けばよい。又は、SerDesが受信した信号をSerDesの外部でループバックさせてもよい。

【0018】

信号サンプリング部(2)は、上記のようにして入力されたDFEの出力信号を、DFEの各タップの遅延時間に対応する信号タイミングでサンプリングする。この各タップの遅延時間に対応する信号タイミングでサンプリングするとは、本実施形態では以下のとおりである。既知のデジタル入力信号において、第(n−m+1)ビットから第nビットまで同じ値が連続しており、かつ、その第(n−m+1)ビットから第nビットまでの値は第(n−m)ビットの値から反転していれば、信号サンプリング部(2)はこの第nビットに対応するDFEの出力信号をサンプリングして第mタップビット誤り率測定部に送る。

【0019】

ここでm=1の場合とは、既知のデジタル入力信号の第nビットの値が第(n−1)ビットの値から反転している場合であり、このような場合には信号サンプリング部(2)はこの第nビットに対応するDFEの出力信号をサンプリングして第1タップビット誤り率測定部(3a)に送る。

【0020】

m=2の場合、すなわち既知のデジタル入力信号の第(n−1)ビットと第nビットの値が同じであり、かつ、第(n−2)ビットの値から反転している場合は、信号サンプリング部(2)はこの第nビットに対応するDFEの出力信号をサンプリングして第2タップビット誤り率測定部(3b)に送る。

【0021】

m=3の場合、すなわち既知のデジタル入力信号の第(n−2)ビットから第nビットまでの連続3ビットの値が同じであり、かつ、第(n−3)ビットの値から反転している場合は、信号サンプリング部(2)はこの第nビットに対応するDFEの出力信号をサンプリングして第3タップビット誤り率測定部(3c)に送る。

既知のデジタル入力信号の第(n−3)ビットから第nビットまでの連続4ビットの値が同じである場合は、信号サンプリング部(2)はこのnビット目のDFEの出力信号D(n)をサンプリングして第4タップビット誤り率測定部(3d)に送る。

【0022】

ここで、本来ならば連続4ビットが同じ値であっても連続5ビット以上同じ値である場合には第4タップビット誤り率測定部(3d)でなく第5やそれ以上のビット誤り率測定部にサンプリング結果が送られるべきであるが、本実施形態ではビット誤り率測定部(3)には第1ビット誤り率測定部(3a)から第4ビット誤り率測定部(3d)までの4個しか設けられていないので、既知のデジタル入力信号の連続する5ビット以上が同じ値手ある場合にもサンプリング結果は第4タップビット誤り率測定部(3d)に送られている。実運用状態の一般的なDFEにおいて5ビット以上前の信号状態が現在の信号に及ぼす影響は非常に小さいと考えられるので、このような処理方法で十分である。もちろん、第5ビット誤り率測定部やそれ以上のビット誤り率測定部を持つように判定帰還型自動等化器評価装置を構成しても良い。

【0023】

以上のようなサンプリング方法の具体例を図2に示す。図2には例として、既知のデジタル入力信号が1ビット目から順に0、1、1、1、1、0、0、0、1、1である場合が示されている。

【0024】

DFEの出力信号の第1ビットは直前のビット値が不明であるため、サンプリングされない。あるいは、信号サンプリング部(2)はこのようなビットの出力信号をサンプリングするが、そのサンプリング結果をどのビット誤り率測定部にも送らずに廃棄するようにしてもよい。

【0025】

第2ビットの出力信号は、既知のデジタル入力信号の第2ビットの値1が第1ビットの値0に対して反転しているため、サンプリングされて第1タップビット誤り率測定部(3a)に送られる。

【0026】

第3ビットの出力信号は、既知のデジタル入力信号の第3ビットの値1が第2ビットの値1と同じであり、かつ、第1ビットの値0からは反転しているため、サンプリングされて第2タップビット誤り率測定部(3b)に送られる。

【0027】

第4ビットの出力信号は、既知のデジタル入力信号の第4ビットの値1が第2ビット及び第3ビットの値1と同じであるが、第1ビットの値0からは反転しているため、サンプリングされて第3タップビット誤り率測定部(3c)に送られる。

【0028】

第5ビットの出力信号は、既知のデジタル入力信号の第5ビットの値1が第2〜4第ビットの値1と同じであるため、サンプリングされて第4タップビット誤り率測定部(3d)に送られる。

【0029】

第6ビットの出力信号は、第5ビットの値から反転しているため、サンプリングされて第1タップビット誤り率(3a)測定部に送られる。以下同様にして、第7ビットの出力信号は第2タップビット誤り率測定部(3b)に、第8ビットの出力信号は第3タップビット誤り率測定部(3c)に、第9ビットの出力信号は第1タップビット誤り率測定部(3a)に、第10ビットの出力信号は第2タップビット誤り率測定部(3b)に、それぞれ送られる。

【0030】

なお、信号サンプリング部(2)がサンプリングした結果をどのビット誤り率測定部に送るかを決定するためには、以上の説明のように既知のデジタル入力信号に基いて判断すべきである。DFEの出力信号のサンプリング結果に基いてサンプリング結果の送り先を判断すると、DFEの等化機能が適切に発揮されている限りはDFEの出力信号のサンプリング結果は既知のデジタル入力信号に一致するから問題ないが、DFEの入力信号がDFEの等化性能を上回る程の強い歪みを受けている場合等では誤ったビット誤り率測定部にサンプリング結果を送ってしまうことがあるからである。

【0031】

以上のようにサンプリングされたサンプリング信号(13)はビット誤り率測定部(3)に入力される。図1に示されているように、本発明の一実施形態である判定帰還型自動等化器評価装置(1)のビット誤り測定部(3)は、第1タップビット誤り率測定部(3a)、第2タップビット誤り率測定部(3b)、第3タップビット誤り率測定部(3c)、第4タップビット誤り率測定部(3d)から構成されている。なお、本発明における各タップのビット誤り率測定部の総数は4に限定されるものではなく、評価対象となるDFEのタップ数にあわせて適切に構成すれば良い。

【0032】

各ビット誤り率測定部(3a〜3d)では、信号サンプリング部(2)から送られたサンプリング値を判定し、その判定結果が既知の入力信号の該当ビット値と一致するか否かを更に判定し、これを所定の時間繰り返してその第1タップのビット誤り率を測定する。このように本発明の一実施形態では複数のビット誤り率測定部が並列的に使用されているが、一つのビット誤り率測定部のみを用いてソフト的にそれぞれのタップ毎のサンプリング値を分離して判定し、各タップ毎のビット誤り率を測定しても良い。

【0033】

このようにして測定された各タップ毎のビット誤り率は表示手段(4)に渡され、例えばCRTなどの表示装置に表示される。ビット誤り率測定部(3)によるビット誤り率の測定を所定時間毎に繰り返し、その測定結果を表示手段(4)が随時更新しながら表示するようにしても良い。また、ビット誤り率でなく、ビット誤りの個数を表示するようにしても良いし、ビット誤り率とビット誤りの個数の両方を表示するようにしても良い。

【0034】

図3は本発明の一実施形態である判定帰還型自動等化器評価装置の画面表示の例である。図3の例では、タップ数を10として、第1タップから第10タップそれぞれに対応するビット誤り率(ER)とビット誤りの個数(EC)を表示している。なお、第10タップに対応するビット誤りは検出されなかったため、ERとECはそれぞれ0となっている。

【0035】

このようにして測定された各タップ毎のビット誤り率は、それ自体でDFEの等化性能を定量的に示す指標となるが、更に様々な目的に利用可能である。例えば、DFEの各タップ係数が外部から制御可能であれば、各タップ係数を適当に変更しつつそれぞれのビット誤り率を測定することにより、DFEの各タップ係数が本当に最適値に決定されているのかを検証することが可能である。また、DFEに入力させる既知の入力信号の信号レベル、雑音レベル等を変更しつつ各タップ毎のビット誤り率を測定することにより、DFEの各タップの余裕度を測定することができる。

【符号の説明】

【0036】

1…判定帰還型自動等化器評価装置

2…信号サンプリング部

3…ビット誤り率測定部

3a…第1タップビット誤り率測定部

3b…第2タップビット誤り率測定部

3c…第3タップビット誤り率測定部

3d…第4タップビット誤り率測定部

4…表示手段

【技術分野】

【0001】

本発明は、判定帰還型自動等化器を評価する装置及び判定帰還型児童等化器を評価する方法に関する。

【背景技術】

【0002】

デジタル信号は伝送路による様々な影響を受けて歪んでしまう。このようなデジタル信号の歪みに対処するための技術としてよく知られているものに、プリエンファシスや判定帰還型自動等化がある。プリエンファシスは、伝送路の影響による信号の歪みを見越して、信号が受信側に届いたときに最適な信号波形となるようにあらかじめ送信側で伝送路による信号の歪とは逆方向に積極的に信号を歪ませておく技術である。プリエンファシスは伝送路による信号への影響が既知であるときには有効な技術であるが、伝送路の影響が未知の場合や時間的に変動する場合には適用が困難である。

【0003】

一方、判定帰還型自動等化は、信号の受信側における技術であって、受信した信号をフィードバックして重み付け合成することにより伝送路による信号の歪みを除去しようとするものである。このような判定帰還型自動等化に特化した、判定帰還型自動等化器(Decision Feedback Equalizer、以下DFE)と呼ばれる専用回路がデジタル信号の受信側に組み込まれていることが多い。

【0004】

DFEの典型的な回路構成を図4に示す。図4のDFE回路は3個の遅延器と4個のタップによる4段のフィードバック回路によって構成されている。なお、遅延器やタップの個数は図4のものに限られず、様々な個数が利用可能である。各タップには可変増幅器が設けられ、これによって各タップを経由する信号が重み付け合成される。このとき各タップの重み付け係数をタップ係数と呼ぶ。このタップ係数を最適な値に調節することにより、DFEに入力される信号の歪みを除去して元の信号波形を復元する、すなわち等化することができる。

【0005】

DFEは例えば、コンピュータのインタフェース用のシリアル/パラレル変換回路(Serializer/Deserializer、以下SerDes)に組み込まれている。近年、インタフェースの伝送速度がますます高速化するにつれ、SerDesの高速動作性能に対する要求も厳しくなってきたが、その中でもDFEの等化性能がボトルネックとなることがある。そのため、インタフェースの開発者等は、SerDesに組み込まれたDFEが実装状態で適切に動作しているのかを検証することや、DFEがどれくらいの信号歪みまで等化できるのかの余裕度を評価する必要があった。

【0006】

DFEの等化性能を評価するための装置として、例えば、特許文献1に記載されているような装置が知られている。特許文献1に記載されている装置では、DFEの等化誤差を時間平均することによりDFEの等化性能の余裕度を算出している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2004−146975号公報(0033〜0041、図1)

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来のDFEの評価装置では、DFEの回路全体としての等化性能は評価可能であるものの、各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することはできなかった。

【0009】

本発明はこのような状況に鑑みて成されたものであり、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することを目的としている。

【課題を解決するための手段】

【0010】

上記の目的のため、本発明に係る判定帰還型自動等化器評価装置は、既知のデジタル入力信号を受けてDFEから出力されるデジタル信号を各タップにおける遅延時間に対応する信号タイミングにおいてサンプリングする信号サンプリング部と、信号サンプリング部によってサンプリングされたデジタル信号から、各タップ毎にデジタル信号のビット誤り率を測定するビット誤り率測定部とを備えている。

【0011】

また、上記の目的のため、本発明に係る判定帰還型自動等化器評価方法は、既知のデジタル入力信号を受けてDFEから出力されるデジタル信号を各タップにおける遅延時間に対応する信号タイミングにおいてサンプリングする段階と、サンプリングされた前記デジタル信号から、各タップ毎にデジタル信号のビット誤り率を測定する段階とを含んでいる。

【発明の効果】

【0012】

本発明の判定帰還型自動等化器評価装置または判定帰還型自動等化器評価方法によれば、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施形態を示す判定帰還型自動等化器評価装置の構成図

【図2】本発明のサンプリング方法を示す説明図

【図3】本発明によるビット誤り率とビット誤りの個数の画面表示例

【図4】典型的なDFEの回路図

【発明を実施するための形態】

【0014】

以下、本発明の実施の形態を図1から図3に基いて説明する。

【0015】

図1は本発明の一実施形態である判定帰還型自動等化器評価装置の構成図である。

本発明の一実施形態である判定帰還型自動等化器評価装置(1)は、信号サンプリング部(2)、ビット誤り率測定部(3)および表示手段(4)から構成されている。

【0016】

信号サンプリング部(2)には、既知のデジタル入力信号を入力されたDFEからの出力信号が入力される。既知のデジタル入力信号は、例えば、信号発生器によって発生されたデジタル信号を用いることができる。

【0017】

DFEが例えばSerDesに実装された状態では、DFEの出力信号を直接に信号サンプリング部(2)に導くことは困難である場合が多い。この場合には例えば、SerDesが受信した信号をSerDes内部でループバックさせて出力した信号を信号サンプリング部(2)に導けばよい。又は、SerDesが受信した信号をSerDesの外部でループバックさせてもよい。

【0018】

信号サンプリング部(2)は、上記のようにして入力されたDFEの出力信号を、DFEの各タップの遅延時間に対応する信号タイミングでサンプリングする。この各タップの遅延時間に対応する信号タイミングでサンプリングするとは、本実施形態では以下のとおりである。既知のデジタル入力信号において、第(n−m+1)ビットから第nビットまで同じ値が連続しており、かつ、その第(n−m+1)ビットから第nビットまでの値は第(n−m)ビットの値から反転していれば、信号サンプリング部(2)はこの第nビットに対応するDFEの出力信号をサンプリングして第mタップビット誤り率測定部に送る。

【0019】

ここでm=1の場合とは、既知のデジタル入力信号の第nビットの値が第(n−1)ビットの値から反転している場合であり、このような場合には信号サンプリング部(2)はこの第nビットに対応するDFEの出力信号をサンプリングして第1タップビット誤り率測定部(3a)に送る。

【0020】

m=2の場合、すなわち既知のデジタル入力信号の第(n−1)ビットと第nビットの値が同じであり、かつ、第(n−2)ビットの値から反転している場合は、信号サンプリング部(2)はこの第nビットに対応するDFEの出力信号をサンプリングして第2タップビット誤り率測定部(3b)に送る。

【0021】

m=3の場合、すなわち既知のデジタル入力信号の第(n−2)ビットから第nビットまでの連続3ビットの値が同じであり、かつ、第(n−3)ビットの値から反転している場合は、信号サンプリング部(2)はこの第nビットに対応するDFEの出力信号をサンプリングして第3タップビット誤り率測定部(3c)に送る。

既知のデジタル入力信号の第(n−3)ビットから第nビットまでの連続4ビットの値が同じである場合は、信号サンプリング部(2)はこのnビット目のDFEの出力信号D(n)をサンプリングして第4タップビット誤り率測定部(3d)に送る。

【0022】

ここで、本来ならば連続4ビットが同じ値であっても連続5ビット以上同じ値である場合には第4タップビット誤り率測定部(3d)でなく第5やそれ以上のビット誤り率測定部にサンプリング結果が送られるべきであるが、本実施形態ではビット誤り率測定部(3)には第1ビット誤り率測定部(3a)から第4ビット誤り率測定部(3d)までの4個しか設けられていないので、既知のデジタル入力信号の連続する5ビット以上が同じ値手ある場合にもサンプリング結果は第4タップビット誤り率測定部(3d)に送られている。実運用状態の一般的なDFEにおいて5ビット以上前の信号状態が現在の信号に及ぼす影響は非常に小さいと考えられるので、このような処理方法で十分である。もちろん、第5ビット誤り率測定部やそれ以上のビット誤り率測定部を持つように判定帰還型自動等化器評価装置を構成しても良い。

【0023】

以上のようなサンプリング方法の具体例を図2に示す。図2には例として、既知のデジタル入力信号が1ビット目から順に0、1、1、1、1、0、0、0、1、1である場合が示されている。

【0024】

DFEの出力信号の第1ビットは直前のビット値が不明であるため、サンプリングされない。あるいは、信号サンプリング部(2)はこのようなビットの出力信号をサンプリングするが、そのサンプリング結果をどのビット誤り率測定部にも送らずに廃棄するようにしてもよい。

【0025】

第2ビットの出力信号は、既知のデジタル入力信号の第2ビットの値1が第1ビットの値0に対して反転しているため、サンプリングされて第1タップビット誤り率測定部(3a)に送られる。

【0026】

第3ビットの出力信号は、既知のデジタル入力信号の第3ビットの値1が第2ビットの値1と同じであり、かつ、第1ビットの値0からは反転しているため、サンプリングされて第2タップビット誤り率測定部(3b)に送られる。

【0027】

第4ビットの出力信号は、既知のデジタル入力信号の第4ビットの値1が第2ビット及び第3ビットの値1と同じであるが、第1ビットの値0からは反転しているため、サンプリングされて第3タップビット誤り率測定部(3c)に送られる。

【0028】

第5ビットの出力信号は、既知のデジタル入力信号の第5ビットの値1が第2〜4第ビットの値1と同じであるため、サンプリングされて第4タップビット誤り率測定部(3d)に送られる。

【0029】

第6ビットの出力信号は、第5ビットの値から反転しているため、サンプリングされて第1タップビット誤り率(3a)測定部に送られる。以下同様にして、第7ビットの出力信号は第2タップビット誤り率測定部(3b)に、第8ビットの出力信号は第3タップビット誤り率測定部(3c)に、第9ビットの出力信号は第1タップビット誤り率測定部(3a)に、第10ビットの出力信号は第2タップビット誤り率測定部(3b)に、それぞれ送られる。

【0030】

なお、信号サンプリング部(2)がサンプリングした結果をどのビット誤り率測定部に送るかを決定するためには、以上の説明のように既知のデジタル入力信号に基いて判断すべきである。DFEの出力信号のサンプリング結果に基いてサンプリング結果の送り先を判断すると、DFEの等化機能が適切に発揮されている限りはDFEの出力信号のサンプリング結果は既知のデジタル入力信号に一致するから問題ないが、DFEの入力信号がDFEの等化性能を上回る程の強い歪みを受けている場合等では誤ったビット誤り率測定部にサンプリング結果を送ってしまうことがあるからである。

【0031】

以上のようにサンプリングされたサンプリング信号(13)はビット誤り率測定部(3)に入力される。図1に示されているように、本発明の一実施形態である判定帰還型自動等化器評価装置(1)のビット誤り測定部(3)は、第1タップビット誤り率測定部(3a)、第2タップビット誤り率測定部(3b)、第3タップビット誤り率測定部(3c)、第4タップビット誤り率測定部(3d)から構成されている。なお、本発明における各タップのビット誤り率測定部の総数は4に限定されるものではなく、評価対象となるDFEのタップ数にあわせて適切に構成すれば良い。

【0032】

各ビット誤り率測定部(3a〜3d)では、信号サンプリング部(2)から送られたサンプリング値を判定し、その判定結果が既知の入力信号の該当ビット値と一致するか否かを更に判定し、これを所定の時間繰り返してその第1タップのビット誤り率を測定する。このように本発明の一実施形態では複数のビット誤り率測定部が並列的に使用されているが、一つのビット誤り率測定部のみを用いてソフト的にそれぞれのタップ毎のサンプリング値を分離して判定し、各タップ毎のビット誤り率を測定しても良い。

【0033】

このようにして測定された各タップ毎のビット誤り率は表示手段(4)に渡され、例えばCRTなどの表示装置に表示される。ビット誤り率測定部(3)によるビット誤り率の測定を所定時間毎に繰り返し、その測定結果を表示手段(4)が随時更新しながら表示するようにしても良い。また、ビット誤り率でなく、ビット誤りの個数を表示するようにしても良いし、ビット誤り率とビット誤りの個数の両方を表示するようにしても良い。

【0034】

図3は本発明の一実施形態である判定帰還型自動等化器評価装置の画面表示の例である。図3の例では、タップ数を10として、第1タップから第10タップそれぞれに対応するビット誤り率(ER)とビット誤りの個数(EC)を表示している。なお、第10タップに対応するビット誤りは検出されなかったため、ERとECはそれぞれ0となっている。

【0035】

このようにして測定された各タップ毎のビット誤り率は、それ自体でDFEの等化性能を定量的に示す指標となるが、更に様々な目的に利用可能である。例えば、DFEの各タップ係数が外部から制御可能であれば、各タップ係数を適当に変更しつつそれぞれのビット誤り率を測定することにより、DFEの各タップ係数が本当に最適値に決定されているのかを検証することが可能である。また、DFEに入力させる既知の入力信号の信号レベル、雑音レベル等を変更しつつ各タップ毎のビット誤り率を測定することにより、DFEの各タップの余裕度を測定することができる。

【符号の説明】

【0036】

1…判定帰還型自動等化器評価装置

2…信号サンプリング部

3…ビット誤り率測定部

3a…第1タップビット誤り率測定部

3b…第2タップビット誤り率測定部

3c…第3タップビット誤り率測定部

3d…第4タップビット誤り率測定部

4…表示手段

【特許請求の範囲】

【請求項1】

複数の遅延器とそれらに各々対応するタップから構成された判定帰還型自動等化器の等化性能を評価するために、既知のデジタル入力信号を受けて前記判定帰還型自動等化器から出力されるデジタル信号のビット誤り率を測定することにより前記評価を行う判定帰還型自動等化器評価装置であって、

前記デジタル信号を、前記各タップにおける遅延時間に対応する信号タイミングにおいてサンプリングする信号サンプリング部と、

前記信号サンプリング部によってサンプリングされた前記デジタル信号から、前記各タップ毎に前記デジタル信号のビット誤り率を測定するビット誤り率測定部と

を備えたことを特徴とする判定帰還型自動等化器評価装置。

【請求項2】

複数の遅延器とそれらに各々対応するタップから構成された判定帰還型自動等化器の等化性能を評価するために、既知のデジタル入力信号を受けて前記判定帰還型自動等化器から出力されるデジタル信号のビット誤り率を測定することにより前記評価を行う判定帰還型自動等化器評価方法であって、

前記デジタル信号を、前記各タップにおける遅延時間に対応する信号タイミングにおいてサンプリングする段階と、

前記段階によってサンプリングされた前記デジタル信号から、前記各タップ毎に前記デジタル信号のビット誤り率を測定する段階と

を含むことを特徴とする判定帰還型自動等化器評価方法。

【請求項1】

複数の遅延器とそれらに各々対応するタップから構成された判定帰還型自動等化器の等化性能を評価するために、既知のデジタル入力信号を受けて前記判定帰還型自動等化器から出力されるデジタル信号のビット誤り率を測定することにより前記評価を行う判定帰還型自動等化器評価装置であって、

前記デジタル信号を、前記各タップにおける遅延時間に対応する信号タイミングにおいてサンプリングする信号サンプリング部と、

前記信号サンプリング部によってサンプリングされた前記デジタル信号から、前記各タップ毎に前記デジタル信号のビット誤り率を測定するビット誤り率測定部と

を備えたことを特徴とする判定帰還型自動等化器評価装置。

【請求項2】

複数の遅延器とそれらに各々対応するタップから構成された判定帰還型自動等化器の等化性能を評価するために、既知のデジタル入力信号を受けて前記判定帰還型自動等化器から出力されるデジタル信号のビット誤り率を測定することにより前記評価を行う判定帰還型自動等化器評価方法であって、

前記デジタル信号を、前記各タップにおける遅延時間に対応する信号タイミングにおいてサンプリングする段階と、

前記段階によってサンプリングされた前記デジタル信号から、前記各タップ毎に前記デジタル信号のビット誤り率を測定する段階と

を含むことを特徴とする判定帰還型自動等化器評価方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−151808(P2012−151808A)

【公開日】平成24年8月9日(2012.8.9)

【国際特許分類】

【出願番号】特願2011−10933(P2011−10933)

【出願日】平成23年1月21日(2011.1.21)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

【公開日】平成24年8月9日(2012.8.9)

【国際特許分類】

【出願日】平成23年1月21日(2011.1.21)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

[ Back to top ]