制御・監視信号伝送システムにおける信号伝送方式

【課題】単一の制御部と複数の被制御装置を備えた制御・監視信号伝送システムにおいて、親局と子局との伝送信号にノイズがのった場合であっても、データ値を正確に伝送できる信号伝送方式を提供する。

【解決手段】制御部からの制御データとセンサ部からの監視データの伝送において、伝送クロックに同期した所定のタイミング信号の制御下で制御データの値に応じて制御データ信号として出力される一連のパルス状信号に、第1および第2信号受信有効時間幅を設ける。第1信号受信有効時間幅は、制御データを判断すべき所定の時点に設定される。第2信号受信有効時間幅は、伝送クロック信号の1周期の開始時点に設定される。そして、パルス信号の第1信号受信有効時間幅および第2信号受信有効時間幅以外の時間帯では、パルス信号の変化信号として受け付けない。

【解決手段】制御部からの制御データとセンサ部からの監視データの伝送において、伝送クロックに同期した所定のタイミング信号の制御下で制御データの値に応じて制御データ信号として出力される一連のパルス状信号に、第1および第2信号受信有効時間幅を設ける。第1信号受信有効時間幅は、制御データを判断すべき所定の時点に設定される。第2信号受信有効時間幅は、伝送クロック信号の1周期の開始時点に設定される。そして、パルス信号の第1信号受信有効時間幅および第2信号受信有効時間幅以外の時間帯では、パルス信号の変化信号として受け付けない。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、単一の制御部と複数の被制御装置を備え、制御部及びデータ信号線に親局が接続され、複数の被制御装置に対応する複数の子局が、共通のデータ信号線及び対応する被制御装置に接続される構成の制御・監視信号伝送システムに好適な、信号伝送方式に関する。

【背景技術】

【0002】

単一の制御部と複数の被制御装置(制御部の指示に応じて動作する被制御部と制御部に情報を送信するセンサ部とで構成されるもの)を備える制御システムにおいて、配線の数を減らすことは、配線スペースの低減、配線工数の低減、装置製作工期の低減、或いは設備の小型化に繋がり、これによって、設備の信頼性向上、コスト低減などを図ることができる。

【0003】

そこで、上記のような制御システムにおいて配線の数を減らす試みがなされている。具体的には、電源を含むクロック信号の線路に、各クロックに対応する1つ(1ビット)の制御信号やセンサ信号(被制御装置からの入力信号)を重畳する信号伝送方式を採用することで、制御部と被制御装置の間の省配線が実現されている。

【0004】

また、この信号伝送方式において、制御部と被制御装置との間における信号伝送速度を高めるための手法が特開2002−152864号公報に開示されている。ここで開示されている制御・監視信号伝送システムは、制御部及び共通のデータ信号線に親局が接続され、複数の被制御装置に対応する複数の子局が、共通のデータ信号線及び対応する被制御装置に接続される構成となる。そして、クロックの1周期毎の後半又は前半を更に制御信号エリア及び監視信号エリアとに時分割し、各々に制御信号及び監視信号を重畳し検出する。これにより、電源を含むクロック信号に、制御部から被制御部への制御信号に加えて、センサ部から制御部への監視信号をも重畳することができる。従って、制御部と被制御部およびセンサ部間の双方向の高速な信号伝送を実現することができると共に、制御信号と監視信号とを共通のデータ信号線に出力し、かつ、これらを同時に双方向に伝送することができる。この結果、共通のデータ信号線において制御信号又は監視信号を伝送する期間を別々に設ける必要をなくすことができ、信号伝送の速度(レート)を従来の2倍に高速化することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−152864号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記の制御・監視信号伝送システムで採用されている伝送方式においては、伝送クロックの1周期毎に、電圧レベルの変化、すなわちパルス信号の変化を各子局が認識することで、実質的に双方向の信号伝送(全二重)が可能となっている。ところが、パルス信号が変化する時間、すなわち立ち上がり点、または立ち下り点以外の時間に、ノイズなどによる電圧変化が生じると、その変化が極めて短い時間のものであったとしてもパルス信号の変化とみなされ、パルス信号が本来意図するデータ値とは異なる値として認識されるという問題があった。

【0007】

そこで本発明は、単一の制御部と複数の被制御装置を備えた制御・監視信号伝送システムにおいて、親局と子局との伝送信号にノイズがのった場合であっても、データ値を正確に伝送できる信号伝送方式を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る信号伝送方式は、制御部および共通のデータ信号線に接続された親局と、前記共通のデータ信号線および対応する被制御装置に接続された複数の子局を備えた制御・監視信号伝送システムにおいて使用されるものである。前記被制御装置は、前記制御部の出力指示に応じて動作する被制御部および/または前記制御部へ入力情報を伝えるセンサ部を有する。前記親局は、所定の周期の伝送クロックに同期した所定のタイミング信号を発生するためのタイミング発生手段を有する。また、前記親局は、前記タイミング信号の制御下で、前記制御部からの制御データの値に応じて、制御データ信号として一連のパルス状信号を、前記データ信号線に出力すると共に、前記タイミング信号の制御下で、前記伝送クロックの1周期毎に、前記一連のパルス状信号に重畳された監視データ信号のデータ値を抽出し、これを前記制御部に引き渡す。前記複数の子局の各々は、前記タイミング信号の制御下で、前記伝送クロックの1周期毎に、前記制御データ信号の各データの値を抽出して、前記各データの値の中の自局に対応するデータを対応する前記被制御部に引き渡し、および/または、前記タイミング信号の制御下で、前記伝送クロック信号の1周期毎に、対応する前記センサ部の監視データの値に応じて、前記監視データ信号を前記一連のパルス状信号に重畳する。そして、所定のパルス幅を有するスタート信号の終了を基点とし、前記伝送クロック信号の1周期において、前記制御データを判断すべき所定の時点に所定の時間幅を有する第1信号受信有効時間幅を設け、前記伝送クロック信号の1周期の開始時点に第2信号受信有効時間幅を設け、前記パルス信号の前記第1信号受信有効時間幅および第2信号受信有効時間幅以外では、前記パルス信号の変化信号として受け付けない。

【0009】

前記制御データの値は、前記伝送クロック信号の1周期における複数種類のパルス幅であってもよく、前記伝送クロック信号の1周期における複数種類のパルスレベルであってもよい。

【0010】

本発明において、制御データを判断すべき所定の時点とは、例えば、制御データの値が伝送クロック信号の1周期における複数種類のパルス幅である場合は、パルスの立上る可能性のある全ての時点となる。より具体的には、パルス幅を2種類とした場合、幅が長い場合にパルスが立上る時点と、前記幅が短い場合に前記パルスが立上る時点の双方が、制御データを判断すべき時点となる。

【0011】

なお、信号受信有効時間幅の設定手法に制限はないが、制御データの値が2種類のパルス幅である場合は、4個のタイマーを使用して設定することができる。すなわち、前記パルス幅が第一の状態と第二の状態をとり、前記第一の状態におけるパルスの変位点を含む前記第1信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第1のタイマーで設定する。また、前記第二の状態におけるパルスの変位点を含む前記第1信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第2のタイマーで設定する。更に、前記第2信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第3のタイマーで設定する。そして、前記第1信号受信有効時間幅および前記第2信号受信有効時間幅の時間幅を第4のタイマーで設定する。

【発明の効果】

【0012】

本発明に係る信号伝送方式では、親局と子局との間で伝送される、一連のパルス状信号の1周期おいて、子局に、伝送クロック信号の1周期の開始時点、および、制御データを判断すべき所定の時点に所定の時間幅を有する信号受信有効時間幅を設けさせ、この信号受信有効時間幅以外では、子局はパルス信号の変化信号として受け付けない。そのため、伝送信号にノイズがのった場合であっても、そのノイズがパルス信号の変化として誤認されることはなく、従って、データ値を正確に伝送できる。なお、信号受信有効時間幅の時間幅を、子局がパルス信号の変化を検知できる範囲で極めて短いものとすれば、信号受信有効時間幅にノイズがのる可能性は極めて低いものとなるため、実用は可能である。

【図面の簡単な説明】

【0013】

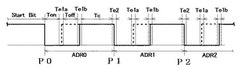

【図1】本発明に係る信号伝送方式の実施例において設定される信号受信有効時間幅を示す、伝送信号のタイムチャート図である。

【図2】同信号伝送方式が採用された制御・監視信号伝送システムの概略構成を示すシステム構成図である。

【図3】親局のシステム構成図である。

【図4】子局出力部のブロック図である。

【図5】子局入力部のブロック図である。

【図6】親局と子局との間で授受される信号のタイムチャート図である。

【図7】従来の信号伝送方式による、子局において伝送信号から抽出される信号を示し、(a)は伝送信号にノイズがのっていない場合に抽出される信号のタイムチャート図、(b)は伝送信号にノイズがのっている場合に抽出される信号のタイムチャート図である。

【図8】監視データの表現形式として電圧レベルの高低を採用した更に他の実施例において親局と子局との間で授受される信号のタイムチャート図である。

【発明を実施するための形態】

【0014】

図1〜6を参照しながら、本発明に係る信号伝送方式の実施例を説明する。

まず、この信号伝送方式が採用されている制御・監視信号伝送システムの構成について説明する。この制御・監視信号伝送システムは、図2に示すように、制御部1および共通のデータ信号線DP、DN(以下、データ信号線DP、DNとする)に接続された親局6と、前記データ信号線DP、DNおよび対応する被制御装置5に接続された複数の子局2を備える。被制御装置5は、制御部1の出力指示に応じて動作する被制御部51と、制御部1へ入力情報を伝えるセンサ部52を有している。被制御部51は、被制御装置5を構成する種々の部品、例えば、アクチュエータ、(ステッピング)モータ、ソレノイド、電磁弁、リレー、サイリスタ、ランプ等からなる。一方、センサ部52は、対応する被制御部51に応じて選択され、例えば、リードスイッチ、マイクロスイッチ、押釦スイッチ、光センサ等からなり、オン、オフの状態(2値信号)を出力する。

【0015】

制御部1は、例えばプログラマブルコントローラ、コンピュータ等であり、制御データ13を送出する出力ユニット11と、被制御装置5側からのセンサデータ(監視データ信号のデータ)15を受け取る入力ユニット12を有する。そして、これら出力ユニット11と入力ユニット12が親局6に接続されている。

【0016】

親局6は、図3に示すように、出力データ部61、タイミング発生部63、親局出力部64、親局入力部65、入力データ部66を備える。

【0017】

出力データ部61は、制御部1の出力ユニット11から制御データ13として受けた並列データを親局出力部64へ引き渡す。この制御データ13は、被制御部51の動作指示を行うものである。

【0018】

タイミング発生部63は、発振回路(OSC)71とタイミング発生手段72からなり、OSC71を基にタイミング発生手段72が、この伝送システムのタイミングクロックを生成し親局出力部64に引き渡す。親局出力部64は、制御データ発生手段73とラインドライバ74からなり、制御データ発生手段73が、出力データ部61から受けたデータと、タイミング発生部63から受けたタイミングクロックに基づき一連のパルス状信号である制御データ信号を生成し、ラインドライバ74を介してデータ信号線DP、DNに送出する。ここで、データ信号線DP、DNに送出される制御データ信号は、本発明における、一連のパルス状信号に相当するものであるが、以下、データ信号線DP、DNを流れる制御データ信号を伝送クロック信号というものとする。ラインドライバ74は、また、DC電源75から電源供給を受け、伝送クロック信号とともに、共通データ信号線DP、DNを経由し、子局2の回路電源を供給する。

【0019】

親局入力部65は監視信号検出手段76と監視データ抽出手段77で構成され、入力データ部66へ入力データを送出する。監視信号検出手段76は、共通データ信号線DP、DNを経由して子局2から送出された監視データ信号を検出する。子局2から送出される監視データ信号は、センサ部52における検知対象の検知の有無が電流レベルとして表わされたもので、スタート信号が送信された後、各子局2から順次受け取るものとなっている。そして、監視データ信号の監視データは、タイミング発生手段72の信号に同期して監視データ抽出手段77で抽出され、直列の入力データとして入力データ部66に送出される。

【0020】

親局入力部65から直列の入力データを受け取った入力データ部66は、その直列の入力データを並列(パラレル)データに変換し、センサデータ15として制御部1の入力ユニット12へ引き渡す。

【0021】

親局6は、また、伝送インターフェイス回路として、伝送ブリーダ電流回路67を有している。伝送ブリーダ電流回路67は、親局出力部64内のラインドライバ74に接続されており、データ信号線DPとDN間の伝送路を安定化させる。

【0022】

子局2は、子局出力部30と子局入力部40を備え、その各々がデータ信号線DP、DNに接続され、センサ部52から受けた信号を監視データ信号としてデータ信号線DP、DNに送出するとともに、データ信号線DP、DN上を伝送される伝送クロック信号から必要な情報を抽出し、被制御部51を動作させる。

【0023】

子局出力部30は、図4に示すように、アドレス設定手段31、アドレス抽出手段32、子局データ出力手段33、出力データ部34、および制御データ信号抽出手段36を備えている。また、接続端子outNを備え、そこに被制御部51が接続されている。

【0024】

なお、この子局出力部30には、マイクロコンピュータ・コントロール・ユニット(MCU)39が搭載されており、アドレス設定手段31、アドレス抽出手段32、子局データ出力手段33、および出力データ部34のそれぞれにおける処理は、MCU39により行われるものとなっている。そして、それぞれの処理において必要となる演算や記憶は、MCU39の備えるCPU、RAMおよびROMを使用して実行されるものとなっている。ただし、図4においては、それぞれの処理におけるCPU、RAMおよびROMとの関係は、説明の便宜上、その図示を省略するものとする。

【0025】

アドレス設定手段31は、図示しないアドレス設定スイッチで設定されたアドレス値を認識し、アドレス抽出手段32に引き渡す。なお、アドレスの設定は、スイッチ等による機械的方法に限定されず、例えば、予め設定された値を親局6から送信し、それを記憶させる方法で行ってもよい。

【0026】

アドレス抽出手段32には、アドレス設定手段31で認識された自局アドレスが引き渡されるとともに、データ信号線DP、DNから制御データ信号抽出手段36を経て、伝送クロック信号が伝えられる。アドレス抽出手段32は、これらの情報を基に、自局アドレスのデータを得て、そのデータを子局データ出力手段33に引き渡す。子局データ出力手段33に引き渡されたデータは、更に出力データ部34に引き渡され、それらデータに基づき被制御部51が動作する。なお、これら一連の処理は、データ信号線DP、DNに伝送される伝送クロック信号のクロックに同期して、すなわち、タイミング信号の制御下で行われることになる。

【0027】

この子局出力部30は、特に専用の電源を保有していないが、共通データ信号線DP、DNから供給される、電源が重畳された伝送クロック信号から、子局出力部30内部で使用する電源電圧を、ダイオードとコンデンサと三端子電源素子によって作り出している。

【0028】

子局入力部40は、図5に示すように、アドレス設定手段41、アドレス抽出手段42、子局データ入力手段43、入力データ部44、および制御データ信号抽出手段46を備えている。また、接続端子inNを備え、そこにセンサ52が接続されている。更に、この子局入力部40にも、子局出力部30と同様にマイクロコンピュータ・コントロール・ユニット(MCU)49が搭載されており、アドレス設定手段41、アドレス抽出手段42、子局データ入力手段43、および入力データ部44のそれぞれにおける処理は、MCU49により行われるものとなっている。なお、アドレス設定手段41、アドレス抽出手段42、および制御データ信号抽出46は、子局出力部30のアドレス設定手段31、アドレス抽出手段32、および制御データ信号抽出手段36とほぼ同一の構成であり、ほぼ同一の動作をするため、その説明は省略する。また、図6においては、図5と同様、それぞれの処理におけるCPU、RAMおよびROMとの関係は、説明の便宜上、その図示を省略するものとする。

【0029】

入力データ部44は、センサ部52から入力された1又は複数の(ビットの)データ信号を子局データ入力手段43に引き渡す。ここで引き渡されたデータは、子局データ入力手段43において保持される。子局データ入力手段43では、アドレス抽出手段42からアドレスが入力されると、保持している1又は複数のデータに応じて、Iout0信号の出力を“on”または“off”とする。Iout0信号が“on”の場合、トランジスタ47は”on”となり、データ信号線DP、DNに監視データ信号が出力される。ここで子局データ入力手段43は、監視データ信号についての並列/直列変換を行、出力される監視データ信号は直列の信号となる。このとき監視データ信号のデータ値は、伝送クロック信号の1周期の前半(低電位レベルの期間)における電流レベルとして表現される。

【0030】

なお、子局入力部40も、子局出力部30と同様に、電源を重畳された伝送クロック信号から、子局入力部40内部で使用する電源電圧を、ダイオードとコンデンサと三端子電源素子によって作り出している。

【0031】

次に、この制御・監視信号伝送システムの信号伝送方式について説明する。

親局出力部64からデータ信号線DP、DNに送出される伝送クロック信号のデータ値は、伝送クロックの1周期における電圧レベルの高い期間の幅(電圧パルスの幅)により表現される。この実施例では、図1に示すように、1周期の後半が高電位レベル(この実施例では+24V)と、前半が低電位レベル(この実施例では+19V)とされている。そして、電圧パルスの幅は、制御部1から入力される制御データ13の各データの値に応じて、図1の破線で示すように拡張される。また、この伝送クロック信号の1周期毎にはアドレス(図1ではADR0、ADR1、ADR2と表示する)が割り当てられ、子局2は、このアドレスをカウントする方式により、自局が受信すべき制御信号を取り込むものとなっている。

【0032】

図6に、伝送クロック信号の一例を示す。この実施例においては、各アドレス番号0、1、2、3における制御データの値(出力データ)はそれぞれ“0”、“0”、“1”、“0”を表わすものとなっている。一方、監視データの値(入力データ)は、伝送クロック信号の1周期の前半(低電位レベルの期間)における電流レベルとして表現される。この実施例では、監視データ信号のデータ値が「1」の場合には所定値Ith以上の電流(例えば、30mA)を流し、「0」の場合にはブリーダ電流(例えば、10mA)のみとして表現されている。従って、各アドレス番号0、1、2、3における監視データはそれぞれ“0”、“0”、“1”、“0”を表わすことになる。

【0033】

なお、図6において図示は省略されているが、図1に示すように、伝送クロック信号には、アドレスのカウントを行うための最初を決定するために、スタート信号(StartBit)が形成される。スタート信号は、伝送クロック信号の高電位レベルと同じ電位レベルであって、伝送クロック信号の1周期より長い信号とされる。

【0034】

図6に示す伝送クロック信号は、従来の伝送方式にも用いられているもので、この形式のままでは、伝送クロック信号にのったノイズをパルス信号の変化として誤認することになる。例えば、ノイズがのっていない状態であれば、図7(a)に示すような抽出信号となる場合であっても、検知の閾値電圧Vthを超える電圧変化がノイズによって生じ、それがパルス信号の変化信号と判断されると、図7(b)に示すように、伝送信号が意図するものと全く異なる信号が抽出され、アドレス番号が誤認されることになる。そこで、この実施例では、図1に示すように、信号受信有効時間幅を設定することで、伝送クロック信号にのったノイズをパルス信号の変化として誤認することを防止している。

【0035】

図1に示すように、信号受信有効時間幅としては、高電位レベルの電圧パルス幅が長い場合にその電圧パルスが立上る時点に第1信号受信有効時間幅Te1aが、高電位レベルの電圧パルス幅が短い場合にその電圧パルスが立上る時点に第1信号受信有効時間幅Te1bが、そして、伝送クロック信号の1周期の開始時点に第2信号受信有効時間幅Te2が設定される。子局6は、第1、第2、第3および第4のタイマーを備えており、第1信号受信有効時間幅Te1a、Te1bおよび第2信号受信有効時間幅Te2の始まり時点が、伝送クロック信号の1周期の始まりP0、P1またはP2を基点として、第1、第2および第3のタイマーでそれぞれ設定される。そして、第1信号受信有効時間幅Te1a、Te1bおよび第2信号受信有効時間幅Te2の時間幅が第4のタイマーで設定される。

【0036】

第2信号受信有効時間幅Te2には、伝送クロック信号の1周期の開始時点であるパルスの立下りが含まれる。そこで、この第2信号受信有効時間幅Te2にパルスの立下りを検出した場合にのみ、子局6のアドレスのカウントを進めることとすれば、第2信号受信有効帯域Te2以外で伝送クロック信号にのったノイズにより発生した電位変化をカウントすることがなく、アドレスのカウントを正確に行うことができる。

【0037】

前記カウントの数が自局に対応するもの、すなわち、自局に対応するアドレスになったと判断した子局6は、監視データ信号を伝送クロックの1周期の前半である低電位レベルに重畳するとともに、第1信号受信有効時間幅Te1a、Te1bにおけるパルスの立上りを検知することでパルス幅を判断し、そのパルス幅により示される値を制御データとして抽出する。ここで、第1信号受信有効時間幅Te1a、Te1b以外での電位変化は、検出されない。従って、伝送クロック信号にのったノイズにより発生した電位変化を電圧パルスの立上りと誤認することはない。

【0038】

図1に示す伝送クロック信号において、伝送クロック信号の最初の1周期の開始時点P0に信号受信有効時間幅は設定されていないが、この時点に第2信号受信有効時間幅を設定してもよい。この時点P0を含む第2信号受信有効時間幅は、スタート信号の始まりを基点として設定することができ、この場合、伝送クロック信号の始まりをより正確に検出できるという利点がある。

【0039】

なお、この実施例では、制御データの表現形式として電圧パルスの幅を、監視データの表現形式として電流の有無を採用しているが、その表現形式に制限はなく、電圧パルスレベルや、電流パルスの幅或いはレベルなど、その他の表現形式を適宜採用してもよい。図9に、監視データの表現形式として電圧パルスレベルを採用した場合の実施例を示す。

【符号の説明】

【0040】

1 制御部

2 子局

5 被制御装置

6 親局

11 出力ユニット

12 入力ユニット

13 制御データ

15 センサデータ

30 子局出力部

31 アドレス設定手段

32 アドレス抽出手段

33 子局データ出力手段

34 出力データ部

36 制御データ信号抽出手段

39、49 MCU

40 子局入力部

41 アドレス設定手段

42 アドレス抽出手段

43 子局データ入力手段

44 入力データ部

46 制御データ信号抽出手段

47 トランジスタ

51 被制御部

52 センサ部

61 出力データ部

63 タイミング発生部

64 親局出力部

65 親局入力部

66 入力データ部

67 伝送ブリーダ電流回路

71 発信器

72 タイミング発生手段

73 制御データ発生手段

74 ラインドライバ

75 DC電源

76 監視信号検出手段

77 監視データ抽出手段

Te1a、Te1b 第1信号受信有効時間幅

Te2 第2信号受信有効時間幅

【技術分野】

【0001】

本発明は、単一の制御部と複数の被制御装置を備え、制御部及びデータ信号線に親局が接続され、複数の被制御装置に対応する複数の子局が、共通のデータ信号線及び対応する被制御装置に接続される構成の制御・監視信号伝送システムに好適な、信号伝送方式に関する。

【背景技術】

【0002】

単一の制御部と複数の被制御装置(制御部の指示に応じて動作する被制御部と制御部に情報を送信するセンサ部とで構成されるもの)を備える制御システムにおいて、配線の数を減らすことは、配線スペースの低減、配線工数の低減、装置製作工期の低減、或いは設備の小型化に繋がり、これによって、設備の信頼性向上、コスト低減などを図ることができる。

【0003】

そこで、上記のような制御システムにおいて配線の数を減らす試みがなされている。具体的には、電源を含むクロック信号の線路に、各クロックに対応する1つ(1ビット)の制御信号やセンサ信号(被制御装置からの入力信号)を重畳する信号伝送方式を採用することで、制御部と被制御装置の間の省配線が実現されている。

【0004】

また、この信号伝送方式において、制御部と被制御装置との間における信号伝送速度を高めるための手法が特開2002−152864号公報に開示されている。ここで開示されている制御・監視信号伝送システムは、制御部及び共通のデータ信号線に親局が接続され、複数の被制御装置に対応する複数の子局が、共通のデータ信号線及び対応する被制御装置に接続される構成となる。そして、クロックの1周期毎の後半又は前半を更に制御信号エリア及び監視信号エリアとに時分割し、各々に制御信号及び監視信号を重畳し検出する。これにより、電源を含むクロック信号に、制御部から被制御部への制御信号に加えて、センサ部から制御部への監視信号をも重畳することができる。従って、制御部と被制御部およびセンサ部間の双方向の高速な信号伝送を実現することができると共に、制御信号と監視信号とを共通のデータ信号線に出力し、かつ、これらを同時に双方向に伝送することができる。この結果、共通のデータ信号線において制御信号又は監視信号を伝送する期間を別々に設ける必要をなくすことができ、信号伝送の速度(レート)を従来の2倍に高速化することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2002−152864号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上記の制御・監視信号伝送システムで採用されている伝送方式においては、伝送クロックの1周期毎に、電圧レベルの変化、すなわちパルス信号の変化を各子局が認識することで、実質的に双方向の信号伝送(全二重)が可能となっている。ところが、パルス信号が変化する時間、すなわち立ち上がり点、または立ち下り点以外の時間に、ノイズなどによる電圧変化が生じると、その変化が極めて短い時間のものであったとしてもパルス信号の変化とみなされ、パルス信号が本来意図するデータ値とは異なる値として認識されるという問題があった。

【0007】

そこで本発明は、単一の制御部と複数の被制御装置を備えた制御・監視信号伝送システムにおいて、親局と子局との伝送信号にノイズがのった場合であっても、データ値を正確に伝送できる信号伝送方式を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る信号伝送方式は、制御部および共通のデータ信号線に接続された親局と、前記共通のデータ信号線および対応する被制御装置に接続された複数の子局を備えた制御・監視信号伝送システムにおいて使用されるものである。前記被制御装置は、前記制御部の出力指示に応じて動作する被制御部および/または前記制御部へ入力情報を伝えるセンサ部を有する。前記親局は、所定の周期の伝送クロックに同期した所定のタイミング信号を発生するためのタイミング発生手段を有する。また、前記親局は、前記タイミング信号の制御下で、前記制御部からの制御データの値に応じて、制御データ信号として一連のパルス状信号を、前記データ信号線に出力すると共に、前記タイミング信号の制御下で、前記伝送クロックの1周期毎に、前記一連のパルス状信号に重畳された監視データ信号のデータ値を抽出し、これを前記制御部に引き渡す。前記複数の子局の各々は、前記タイミング信号の制御下で、前記伝送クロックの1周期毎に、前記制御データ信号の各データの値を抽出して、前記各データの値の中の自局に対応するデータを対応する前記被制御部に引き渡し、および/または、前記タイミング信号の制御下で、前記伝送クロック信号の1周期毎に、対応する前記センサ部の監視データの値に応じて、前記監視データ信号を前記一連のパルス状信号に重畳する。そして、所定のパルス幅を有するスタート信号の終了を基点とし、前記伝送クロック信号の1周期において、前記制御データを判断すべき所定の時点に所定の時間幅を有する第1信号受信有効時間幅を設け、前記伝送クロック信号の1周期の開始時点に第2信号受信有効時間幅を設け、前記パルス信号の前記第1信号受信有効時間幅および第2信号受信有効時間幅以外では、前記パルス信号の変化信号として受け付けない。

【0009】

前記制御データの値は、前記伝送クロック信号の1周期における複数種類のパルス幅であってもよく、前記伝送クロック信号の1周期における複数種類のパルスレベルであってもよい。

【0010】

本発明において、制御データを判断すべき所定の時点とは、例えば、制御データの値が伝送クロック信号の1周期における複数種類のパルス幅である場合は、パルスの立上る可能性のある全ての時点となる。より具体的には、パルス幅を2種類とした場合、幅が長い場合にパルスが立上る時点と、前記幅が短い場合に前記パルスが立上る時点の双方が、制御データを判断すべき時点となる。

【0011】

なお、信号受信有効時間幅の設定手法に制限はないが、制御データの値が2種類のパルス幅である場合は、4個のタイマーを使用して設定することができる。すなわち、前記パルス幅が第一の状態と第二の状態をとり、前記第一の状態におけるパルスの変位点を含む前記第1信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第1のタイマーで設定する。また、前記第二の状態におけるパルスの変位点を含む前記第1信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第2のタイマーで設定する。更に、前記第2信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第3のタイマーで設定する。そして、前記第1信号受信有効時間幅および前記第2信号受信有効時間幅の時間幅を第4のタイマーで設定する。

【発明の効果】

【0012】

本発明に係る信号伝送方式では、親局と子局との間で伝送される、一連のパルス状信号の1周期おいて、子局に、伝送クロック信号の1周期の開始時点、および、制御データを判断すべき所定の時点に所定の時間幅を有する信号受信有効時間幅を設けさせ、この信号受信有効時間幅以外では、子局はパルス信号の変化信号として受け付けない。そのため、伝送信号にノイズがのった場合であっても、そのノイズがパルス信号の変化として誤認されることはなく、従って、データ値を正確に伝送できる。なお、信号受信有効時間幅の時間幅を、子局がパルス信号の変化を検知できる範囲で極めて短いものとすれば、信号受信有効時間幅にノイズがのる可能性は極めて低いものとなるため、実用は可能である。

【図面の簡単な説明】

【0013】

【図1】本発明に係る信号伝送方式の実施例において設定される信号受信有効時間幅を示す、伝送信号のタイムチャート図である。

【図2】同信号伝送方式が採用された制御・監視信号伝送システムの概略構成を示すシステム構成図である。

【図3】親局のシステム構成図である。

【図4】子局出力部のブロック図である。

【図5】子局入力部のブロック図である。

【図6】親局と子局との間で授受される信号のタイムチャート図である。

【図7】従来の信号伝送方式による、子局において伝送信号から抽出される信号を示し、(a)は伝送信号にノイズがのっていない場合に抽出される信号のタイムチャート図、(b)は伝送信号にノイズがのっている場合に抽出される信号のタイムチャート図である。

【図8】監視データの表現形式として電圧レベルの高低を採用した更に他の実施例において親局と子局との間で授受される信号のタイムチャート図である。

【発明を実施するための形態】

【0014】

図1〜6を参照しながら、本発明に係る信号伝送方式の実施例を説明する。

まず、この信号伝送方式が採用されている制御・監視信号伝送システムの構成について説明する。この制御・監視信号伝送システムは、図2に示すように、制御部1および共通のデータ信号線DP、DN(以下、データ信号線DP、DNとする)に接続された親局6と、前記データ信号線DP、DNおよび対応する被制御装置5に接続された複数の子局2を備える。被制御装置5は、制御部1の出力指示に応じて動作する被制御部51と、制御部1へ入力情報を伝えるセンサ部52を有している。被制御部51は、被制御装置5を構成する種々の部品、例えば、アクチュエータ、(ステッピング)モータ、ソレノイド、電磁弁、リレー、サイリスタ、ランプ等からなる。一方、センサ部52は、対応する被制御部51に応じて選択され、例えば、リードスイッチ、マイクロスイッチ、押釦スイッチ、光センサ等からなり、オン、オフの状態(2値信号)を出力する。

【0015】

制御部1は、例えばプログラマブルコントローラ、コンピュータ等であり、制御データ13を送出する出力ユニット11と、被制御装置5側からのセンサデータ(監視データ信号のデータ)15を受け取る入力ユニット12を有する。そして、これら出力ユニット11と入力ユニット12が親局6に接続されている。

【0016】

親局6は、図3に示すように、出力データ部61、タイミング発生部63、親局出力部64、親局入力部65、入力データ部66を備える。

【0017】

出力データ部61は、制御部1の出力ユニット11から制御データ13として受けた並列データを親局出力部64へ引き渡す。この制御データ13は、被制御部51の動作指示を行うものである。

【0018】

タイミング発生部63は、発振回路(OSC)71とタイミング発生手段72からなり、OSC71を基にタイミング発生手段72が、この伝送システムのタイミングクロックを生成し親局出力部64に引き渡す。親局出力部64は、制御データ発生手段73とラインドライバ74からなり、制御データ発生手段73が、出力データ部61から受けたデータと、タイミング発生部63から受けたタイミングクロックに基づき一連のパルス状信号である制御データ信号を生成し、ラインドライバ74を介してデータ信号線DP、DNに送出する。ここで、データ信号線DP、DNに送出される制御データ信号は、本発明における、一連のパルス状信号に相当するものであるが、以下、データ信号線DP、DNを流れる制御データ信号を伝送クロック信号というものとする。ラインドライバ74は、また、DC電源75から電源供給を受け、伝送クロック信号とともに、共通データ信号線DP、DNを経由し、子局2の回路電源を供給する。

【0019】

親局入力部65は監視信号検出手段76と監視データ抽出手段77で構成され、入力データ部66へ入力データを送出する。監視信号検出手段76は、共通データ信号線DP、DNを経由して子局2から送出された監視データ信号を検出する。子局2から送出される監視データ信号は、センサ部52における検知対象の検知の有無が電流レベルとして表わされたもので、スタート信号が送信された後、各子局2から順次受け取るものとなっている。そして、監視データ信号の監視データは、タイミング発生手段72の信号に同期して監視データ抽出手段77で抽出され、直列の入力データとして入力データ部66に送出される。

【0020】

親局入力部65から直列の入力データを受け取った入力データ部66は、その直列の入力データを並列(パラレル)データに変換し、センサデータ15として制御部1の入力ユニット12へ引き渡す。

【0021】

親局6は、また、伝送インターフェイス回路として、伝送ブリーダ電流回路67を有している。伝送ブリーダ電流回路67は、親局出力部64内のラインドライバ74に接続されており、データ信号線DPとDN間の伝送路を安定化させる。

【0022】

子局2は、子局出力部30と子局入力部40を備え、その各々がデータ信号線DP、DNに接続され、センサ部52から受けた信号を監視データ信号としてデータ信号線DP、DNに送出するとともに、データ信号線DP、DN上を伝送される伝送クロック信号から必要な情報を抽出し、被制御部51を動作させる。

【0023】

子局出力部30は、図4に示すように、アドレス設定手段31、アドレス抽出手段32、子局データ出力手段33、出力データ部34、および制御データ信号抽出手段36を備えている。また、接続端子outNを備え、そこに被制御部51が接続されている。

【0024】

なお、この子局出力部30には、マイクロコンピュータ・コントロール・ユニット(MCU)39が搭載されており、アドレス設定手段31、アドレス抽出手段32、子局データ出力手段33、および出力データ部34のそれぞれにおける処理は、MCU39により行われるものとなっている。そして、それぞれの処理において必要となる演算や記憶は、MCU39の備えるCPU、RAMおよびROMを使用して実行されるものとなっている。ただし、図4においては、それぞれの処理におけるCPU、RAMおよびROMとの関係は、説明の便宜上、その図示を省略するものとする。

【0025】

アドレス設定手段31は、図示しないアドレス設定スイッチで設定されたアドレス値を認識し、アドレス抽出手段32に引き渡す。なお、アドレスの設定は、スイッチ等による機械的方法に限定されず、例えば、予め設定された値を親局6から送信し、それを記憶させる方法で行ってもよい。

【0026】

アドレス抽出手段32には、アドレス設定手段31で認識された自局アドレスが引き渡されるとともに、データ信号線DP、DNから制御データ信号抽出手段36を経て、伝送クロック信号が伝えられる。アドレス抽出手段32は、これらの情報を基に、自局アドレスのデータを得て、そのデータを子局データ出力手段33に引き渡す。子局データ出力手段33に引き渡されたデータは、更に出力データ部34に引き渡され、それらデータに基づき被制御部51が動作する。なお、これら一連の処理は、データ信号線DP、DNに伝送される伝送クロック信号のクロックに同期して、すなわち、タイミング信号の制御下で行われることになる。

【0027】

この子局出力部30は、特に専用の電源を保有していないが、共通データ信号線DP、DNから供給される、電源が重畳された伝送クロック信号から、子局出力部30内部で使用する電源電圧を、ダイオードとコンデンサと三端子電源素子によって作り出している。

【0028】

子局入力部40は、図5に示すように、アドレス設定手段41、アドレス抽出手段42、子局データ入力手段43、入力データ部44、および制御データ信号抽出手段46を備えている。また、接続端子inNを備え、そこにセンサ52が接続されている。更に、この子局入力部40にも、子局出力部30と同様にマイクロコンピュータ・コントロール・ユニット(MCU)49が搭載されており、アドレス設定手段41、アドレス抽出手段42、子局データ入力手段43、および入力データ部44のそれぞれにおける処理は、MCU49により行われるものとなっている。なお、アドレス設定手段41、アドレス抽出手段42、および制御データ信号抽出46は、子局出力部30のアドレス設定手段31、アドレス抽出手段32、および制御データ信号抽出手段36とほぼ同一の構成であり、ほぼ同一の動作をするため、その説明は省略する。また、図6においては、図5と同様、それぞれの処理におけるCPU、RAMおよびROMとの関係は、説明の便宜上、その図示を省略するものとする。

【0029】

入力データ部44は、センサ部52から入力された1又は複数の(ビットの)データ信号を子局データ入力手段43に引き渡す。ここで引き渡されたデータは、子局データ入力手段43において保持される。子局データ入力手段43では、アドレス抽出手段42からアドレスが入力されると、保持している1又は複数のデータに応じて、Iout0信号の出力を“on”または“off”とする。Iout0信号が“on”の場合、トランジスタ47は”on”となり、データ信号線DP、DNに監視データ信号が出力される。ここで子局データ入力手段43は、監視データ信号についての並列/直列変換を行、出力される監視データ信号は直列の信号となる。このとき監視データ信号のデータ値は、伝送クロック信号の1周期の前半(低電位レベルの期間)における電流レベルとして表現される。

【0030】

なお、子局入力部40も、子局出力部30と同様に、電源を重畳された伝送クロック信号から、子局入力部40内部で使用する電源電圧を、ダイオードとコンデンサと三端子電源素子によって作り出している。

【0031】

次に、この制御・監視信号伝送システムの信号伝送方式について説明する。

親局出力部64からデータ信号線DP、DNに送出される伝送クロック信号のデータ値は、伝送クロックの1周期における電圧レベルの高い期間の幅(電圧パルスの幅)により表現される。この実施例では、図1に示すように、1周期の後半が高電位レベル(この実施例では+24V)と、前半が低電位レベル(この実施例では+19V)とされている。そして、電圧パルスの幅は、制御部1から入力される制御データ13の各データの値に応じて、図1の破線で示すように拡張される。また、この伝送クロック信号の1周期毎にはアドレス(図1ではADR0、ADR1、ADR2と表示する)が割り当てられ、子局2は、このアドレスをカウントする方式により、自局が受信すべき制御信号を取り込むものとなっている。

【0032】

図6に、伝送クロック信号の一例を示す。この実施例においては、各アドレス番号0、1、2、3における制御データの値(出力データ)はそれぞれ“0”、“0”、“1”、“0”を表わすものとなっている。一方、監視データの値(入力データ)は、伝送クロック信号の1周期の前半(低電位レベルの期間)における電流レベルとして表現される。この実施例では、監視データ信号のデータ値が「1」の場合には所定値Ith以上の電流(例えば、30mA)を流し、「0」の場合にはブリーダ電流(例えば、10mA)のみとして表現されている。従って、各アドレス番号0、1、2、3における監視データはそれぞれ“0”、“0”、“1”、“0”を表わすことになる。

【0033】

なお、図6において図示は省略されているが、図1に示すように、伝送クロック信号には、アドレスのカウントを行うための最初を決定するために、スタート信号(StartBit)が形成される。スタート信号は、伝送クロック信号の高電位レベルと同じ電位レベルであって、伝送クロック信号の1周期より長い信号とされる。

【0034】

図6に示す伝送クロック信号は、従来の伝送方式にも用いられているもので、この形式のままでは、伝送クロック信号にのったノイズをパルス信号の変化として誤認することになる。例えば、ノイズがのっていない状態であれば、図7(a)に示すような抽出信号となる場合であっても、検知の閾値電圧Vthを超える電圧変化がノイズによって生じ、それがパルス信号の変化信号と判断されると、図7(b)に示すように、伝送信号が意図するものと全く異なる信号が抽出され、アドレス番号が誤認されることになる。そこで、この実施例では、図1に示すように、信号受信有効時間幅を設定することで、伝送クロック信号にのったノイズをパルス信号の変化として誤認することを防止している。

【0035】

図1に示すように、信号受信有効時間幅としては、高電位レベルの電圧パルス幅が長い場合にその電圧パルスが立上る時点に第1信号受信有効時間幅Te1aが、高電位レベルの電圧パルス幅が短い場合にその電圧パルスが立上る時点に第1信号受信有効時間幅Te1bが、そして、伝送クロック信号の1周期の開始時点に第2信号受信有効時間幅Te2が設定される。子局6は、第1、第2、第3および第4のタイマーを備えており、第1信号受信有効時間幅Te1a、Te1bおよび第2信号受信有効時間幅Te2の始まり時点が、伝送クロック信号の1周期の始まりP0、P1またはP2を基点として、第1、第2および第3のタイマーでそれぞれ設定される。そして、第1信号受信有効時間幅Te1a、Te1bおよび第2信号受信有効時間幅Te2の時間幅が第4のタイマーで設定される。

【0036】

第2信号受信有効時間幅Te2には、伝送クロック信号の1周期の開始時点であるパルスの立下りが含まれる。そこで、この第2信号受信有効時間幅Te2にパルスの立下りを検出した場合にのみ、子局6のアドレスのカウントを進めることとすれば、第2信号受信有効帯域Te2以外で伝送クロック信号にのったノイズにより発生した電位変化をカウントすることがなく、アドレスのカウントを正確に行うことができる。

【0037】

前記カウントの数が自局に対応するもの、すなわち、自局に対応するアドレスになったと判断した子局6は、監視データ信号を伝送クロックの1周期の前半である低電位レベルに重畳するとともに、第1信号受信有効時間幅Te1a、Te1bにおけるパルスの立上りを検知することでパルス幅を判断し、そのパルス幅により示される値を制御データとして抽出する。ここで、第1信号受信有効時間幅Te1a、Te1b以外での電位変化は、検出されない。従って、伝送クロック信号にのったノイズにより発生した電位変化を電圧パルスの立上りと誤認することはない。

【0038】

図1に示す伝送クロック信号において、伝送クロック信号の最初の1周期の開始時点P0に信号受信有効時間幅は設定されていないが、この時点に第2信号受信有効時間幅を設定してもよい。この時点P0を含む第2信号受信有効時間幅は、スタート信号の始まりを基点として設定することができ、この場合、伝送クロック信号の始まりをより正確に検出できるという利点がある。

【0039】

なお、この実施例では、制御データの表現形式として電圧パルスの幅を、監視データの表現形式として電流の有無を採用しているが、その表現形式に制限はなく、電圧パルスレベルや、電流パルスの幅或いはレベルなど、その他の表現形式を適宜採用してもよい。図9に、監視データの表現形式として電圧パルスレベルを採用した場合の実施例を示す。

【符号の説明】

【0040】

1 制御部

2 子局

5 被制御装置

6 親局

11 出力ユニット

12 入力ユニット

13 制御データ

15 センサデータ

30 子局出力部

31 アドレス設定手段

32 アドレス抽出手段

33 子局データ出力手段

34 出力データ部

36 制御データ信号抽出手段

39、49 MCU

40 子局入力部

41 アドレス設定手段

42 アドレス抽出手段

43 子局データ入力手段

44 入力データ部

46 制御データ信号抽出手段

47 トランジスタ

51 被制御部

52 センサ部

61 出力データ部

63 タイミング発生部

64 親局出力部

65 親局入力部

66 入力データ部

67 伝送ブリーダ電流回路

71 発信器

72 タイミング発生手段

73 制御データ発生手段

74 ラインドライバ

75 DC電源

76 監視信号検出手段

77 監視データ抽出手段

Te1a、Te1b 第1信号受信有効時間幅

Te2 第2信号受信有効時間幅

【特許請求の範囲】

【請求項1】

制御部および共通のデータ信号線に接続された親局と、前記共通のデータ信号線および対応する被制御装置に接続された複数の子局を備え、

前記被制御装置は、前記制御部の出力指示に応じて動作する被制御部および/または前記制御部へ入力情報を伝えるセンサ部を有し、

前記親局は、所定の周期の伝送クロックに同期した所定のタイミング信号を発生するためのタイミング発生手段を有し、前記タイミング信号の制御下で、前記制御部からの制御データの値に応じて、制御データ信号として一連のパルス状信号を前記データ信号線に出力すると共に、前記タイミング信号の制御下で、前記伝送クロックの1周期毎に、前記一連のパルス状信号に重畳された監視データ信号のデータ値を抽出し、これを前記制御部に引き渡し、

前記複数の子局の各々は、前記タイミング信号の制御下で、前記伝送クロックの1周期毎に、前記制御データ信号の各データの値を抽出して、前記各データの値の中の自局に対応するデータを対応する前記被制御部に引き渡し、および/または、前記タイミング信号の制御下で、前記伝送クロック信号の1周期毎に、対応する前記センサ部の監視データの値に応じて、前記監視データ信号を前記一連のパルス状信号に重畳する制御・監視信号伝送システムにおいて、

所定のパルス幅を有するスタート信号の終了を基点とし、前記伝送クロック信号の1周期において、前記制御データを判断すべき所定の時点に所定の時間幅を有する第1信号受信有効時間幅を設け、前記伝送クロック信号の1周期の開始時点に第2信号受信有効時間幅を設け、前記第1信号受信有効時間幅および第2信号受信有効時間幅以外では、パルス信号の変化信号として受け付けないことを特徴とする信号伝送方式。

【請求項2】

前記制御データの値は、前記伝送クロック信号の1周期における複数種類のパルス幅である請求項1に記載の信号伝送方式。

【請求項3】

前記制御データの値は、前記伝送クロック信号の1周期における複数種類のパルスレベルである請求項1に記載の信号伝送方式。

【請求項4】

前記パルス幅が第一の状態と第二の状態をとり、前記第一の状態におけるパルスの変位点を含む前記第1信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第1のタイマーで設定し、前記第二の状態におけるパルスの変位点を含む前記第1信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第2のタイマーで設定し、前記第2信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第3のタイマーで設定し、前記第1信号受信有効時間幅および前記第2信号受信有効時間幅の時間幅を第4のタイマーで設定する請求項2に記載の信号伝送方式。

【請求項1】

制御部および共通のデータ信号線に接続された親局と、前記共通のデータ信号線および対応する被制御装置に接続された複数の子局を備え、

前記被制御装置は、前記制御部の出力指示に応じて動作する被制御部および/または前記制御部へ入力情報を伝えるセンサ部を有し、

前記親局は、所定の周期の伝送クロックに同期した所定のタイミング信号を発生するためのタイミング発生手段を有し、前記タイミング信号の制御下で、前記制御部からの制御データの値に応じて、制御データ信号として一連のパルス状信号を前記データ信号線に出力すると共に、前記タイミング信号の制御下で、前記伝送クロックの1周期毎に、前記一連のパルス状信号に重畳された監視データ信号のデータ値を抽出し、これを前記制御部に引き渡し、

前記複数の子局の各々は、前記タイミング信号の制御下で、前記伝送クロックの1周期毎に、前記制御データ信号の各データの値を抽出して、前記各データの値の中の自局に対応するデータを対応する前記被制御部に引き渡し、および/または、前記タイミング信号の制御下で、前記伝送クロック信号の1周期毎に、対応する前記センサ部の監視データの値に応じて、前記監視データ信号を前記一連のパルス状信号に重畳する制御・監視信号伝送システムにおいて、

所定のパルス幅を有するスタート信号の終了を基点とし、前記伝送クロック信号の1周期において、前記制御データを判断すべき所定の時点に所定の時間幅を有する第1信号受信有効時間幅を設け、前記伝送クロック信号の1周期の開始時点に第2信号受信有効時間幅を設け、前記第1信号受信有効時間幅および第2信号受信有効時間幅以外では、パルス信号の変化信号として受け付けないことを特徴とする信号伝送方式。

【請求項2】

前記制御データの値は、前記伝送クロック信号の1周期における複数種類のパルス幅である請求項1に記載の信号伝送方式。

【請求項3】

前記制御データの値は、前記伝送クロック信号の1周期における複数種類のパルスレベルである請求項1に記載の信号伝送方式。

【請求項4】

前記パルス幅が第一の状態と第二の状態をとり、前記第一の状態におけるパルスの変位点を含む前記第1信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第1のタイマーで設定し、前記第二の状態におけるパルスの変位点を含む前記第1信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第2のタイマーで設定し、前記第2信号受信有効時間幅の始まり時点を、前記パルスが含まれる周期の始まりを基点として第3のタイマーで設定し、前記第1信号受信有効時間幅および前記第2信号受信有効時間幅の時間幅を第4のタイマーで設定する請求項2に記載の信号伝送方式。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−130305(P2011−130305A)

【公開日】平成23年6月30日(2011.6.30)

【国際特許分類】

【出願番号】特願2009−288522(P2009−288522)

【出願日】平成21年12月18日(2009.12.18)

【出願人】(501194514)株式会社 エニイワイヤ (37)

【Fターム(参考)】

【公開日】平成23年6月30日(2011.6.30)

【国際特許分類】

【出願日】平成21年12月18日(2009.12.18)

【出願人】(501194514)株式会社 エニイワイヤ (37)

【Fターム(参考)】

[ Back to top ]