制御回路を有するLEDディスプレイ

【課題】本発明は改良された性能を提供しつつ簡単な制御構造を有するOLED制御装置を提供することを目的とする。

【解決手段】制御信号に応答してフレーム期間内で蓄積回路に輝度値を蓄積する制御回路を含む、LED表示画素を制御するためのアクティブマトリクス回路。駆動回路が蓄積回路に応答してLEDの電流を制御して輝度値により決定される輝度レベルで発光させる。蓄積回路に接続された輝度値減少回路がフレーム期間における蓄積回路に蓄積された輝度値の制御された減少をもたらす。

【解決手段】制御信号に応答してフレーム期間内で蓄積回路に輝度値を蓄積する制御回路を含む、LED表示画素を制御するためのアクティブマトリクス回路。駆動回路が蓄積回路に応答してLEDの電流を制御して輝度値により決定される輝度レベルで発光させる。蓄積回路に接続された輝度値減少回路がフレーム期間における蓄積回路に蓄積された輝度値の制御された減少をもたらす。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ソリッドステート表示デバイスおよび画素値と画像を記憶し表示する手段に関する。

【背景技術】

【0002】

発光画素を利用するソリッドステート画像表示デバイスは周知であり広く用いられている。例えば、OLEDデバイスがパッシブおよびアクティブマトリクスの双方の形で、およびトップエミッタおよびボトムエミッタの双方の方式でフラットパネルディスプレイにおいて用いられている。OLEDディスプレイの制御回路もまた周知の技術であり、電圧制御および電流制御の双方の機構を含んでいる。

【0003】

従来のパッシブマトリクスOLEDディスプレイは、OLED発光素子が特定の輝度で発光する(フレームまたはフレーム期間としても知られている)固定的な期間においてOLED素子に電流を流すドライバを採用している。OLED素子の行または列に順次エネルギが与えられ、フリッカの発現を回避するに充分な速度でOLEDディスプレイ全体がリフレッシュされる。例えば2003年8月24日に公開された名称「OLED素子ドライバにパルス振幅変調を与えるシステムと方法」のWO2003/034389には、有機発光ダイオードディスプレイのためのパルス幅変調ドライバが記載されている。ビデオディスプレイの一実施形態は、ビデオディスプレイの有機発光ダイオードを駆動する選択された電圧を提供するための電圧ドライバを備えている。電圧ドライバは、経年変化、行抵抗、列抵抗、および他のダイオード特性を考慮した補正テーブルから電圧情報を受け取る。

【0004】

これに対して、アクティブマトリクス回路は、ディスプレイの各発光素子に対して設けられた回路の2次元アレイを採用する。アクティブマトリクス回路は、(代表的にはコンデンサへの電荷としての)値を記憶させる制御機構を提供し、この値は駆動回路を制御して(画素またはサブ画素としても知られる)発光素子に流れる電流をもたらすために使用される。ここで使われているように、各発光素子は色によらず、または他の発光素子とのグループ化にかかわらず画素であると考えられる。例えば、図12を参照すると、LED10を駆動するためのアクティブマトリクス画素回路は選択信号14およびデータ信号16のような制御信号に応答する制御トランジスタ12を含んでいる。選択信号14がアクティブになると、制御トランジスタ12がターンオンし、データ信号がコンデンサ20への電荷をもたらす。制御トランジスタ12はその後選択信号14がアクティブでなくなることでターンオフする。コンデンサ20に蓄えられた電荷は駆動トランジスタ22をターンオンしてコンデンサ20に蓄えられた電荷に比例した電流をLED10にもたらす。図13Aを参照すると、画素は第1のフレーム期間T1において輝度レベルL1で発光し、第2のフレーム期間T2において第2の輝度L2で発光する。輝度の変化は、観察者により、画像の変化、例えば或る場面における動きとして知覚される。

【0005】

従来のフラットパネルディスプレイにおいて、表示信号は、代表的には、映像ストリームの連続するフレームにおいて滑らかな動きの発現をもたらすに充分な速度で周期的にリフレッシュされる。リフレッシュ速度は代表的にはモニタで1秒あたり30,60,70,75,80,90または100フレームであり、テレビで1秒あたり50または60フレームである。そのため、従来のフラットパネルディスプレイにおいては、コンデンサ20の電荷は用途に応じて選択されたリフレッシュ速度で更新される。

【0006】

各画素の輝度値は代表的にはフレーム期間を定める(例えば30Hzまたは60Hzの)リフレッシュ速度でリフレッシュされる。フレーム期間は、画素の輝度値が変化するときに動性錯覚をもたらすように充分に短く選ばれる。知られているように、このようなアクティブマトリクス回路は、観察者の目がディスプレイを横切って画像が網膜の異なる部分に映されると、画像がフレーム期間中静止しているため、観察者に残像(モーションブラー)を引き起こす。この残像はリフレッシュ期間を短くする、すなわち高い周波数でリフレッシュすることで減らすことができる。しかしながら、そのような解決策は、高い周波数が採用されるとドライバのコストが上昇し各画素位置に電荷を蓄積するために用いられる制御線における伝送線の影響を悪化させるという点で問題がある。或いはまた、例えばフレーム期間の一部だけより明るく発光させて、各フレームで画素が発光する時間を短くすることもできる。フレーム期間が充分に短いとフリッカは感じられなくなる。図13Bを参照すると、第1のフレーム期間T1では期間T1の半分の期間で2倍の光2L1を発し、同様に、期間T2の半分の期間で2倍の輝度レベル2L2で発光するよう画素が制御される。関連する解決策において、ディスプレイの複数の部分がディスプレイを横切ってスクロールする黒いバーを表示する。しかしながら、これらの解決策はコストを上昇させる高周波制御を必要とし、より長い制御線を有する大規模なディスプレイに対しては問題がある。

【0007】

図13Bに示されたような表示画素を制御するためには公知のパルス幅変調技術を採用することができる。さらに、アクティブマトリクスにおいて採用される薄膜駆動トランジスタの閾値スイッチング特性のバラツキがOLEDディスプレイの不均一性の1つの原因であるから、アクティブマトリクスOLEDディスプレイの不均一性を改善する1つのアプローチは電荷蓄積制御技術とは対照的なパルス幅変調技術を採用することである。これらパルス幅変調技術は、1つのフレーム期間内で、特定の第1の時間において最大電流および輝度でOLEDを駆動し、次に第2の時間においてOLEDをターンオフすることで機能する。第1および第2の時間の合計が充分に小さければOLEDを周期的にオンオフすることによるフリッカは観察者に感じられない。OLED素子の輝度は、OLEDがオフになっている時間に対するOLEDがオンになっている時間の比を変えることで制御される。

【0008】

パルス幅変調を使ってOLEDディスプレイを制御する様々な方法が知られている。例えば2004年10月26日に付与された「電子ディスプレイのグレースケール画素ドライバおよびそのための動作方法」という名称の米国特許第6,809,710号はグラフィックディスプレイにおいてOLEDを駆動する回路を開示している。その回路はスイッチングモードで動作するOLEDの端子に接続された電流源を採用している。電流源は選択的に設定された周期的な電圧信号と周期的な可変振幅電圧信号の組み合わせに応答する。電流源はオンであるときLEDが最大輝度を達成するのに必要な電流をOLEDに供給するよう設計され最適化されている。オフになると、電流源はOLEDへの電流の供給を阻止してOLEDディスプレイに均一な黒レベルをもたらす。OLEDのみかけ上の輝度はOLEDに供給される電流のパルス幅を変調して電流がOLEDに供給される時間を変えることにより制御される。

【0009】

電流源のスイッチングの動作モードを使用することで回路は電流駆動OLEDディスプレイの輝度値を制御するための広い範囲の電圧を採用することが可能になる。しかしながら、電流駆動回路は複雑であり表示装置の各画素に対して広いスペースを必要とする。

【0010】

単一の回路でパルス幅制御と可変電荷蓄積制御の双方を提供する方法もまた知られている。「アクティブマトリクス発光装置の駆動回路」という名称の米国特許6,670,773がOLED素子と並列なトランジスタを示唆している。しかしながら、記述された技術はOLEDからの駆動電流を分岐して回路の動作効率を低下させるものである。その他の設計では、OLED素子の性能を制御または測定する、OLED素子に直列な回路素子が採用される。例えば、2004年4月29日に公開された「アクティブマトリクス有機EL表示装置」という名称のWO2004/036536はOLED素子に直列に付加された素子を有する回路を開示する。しかしながら、OLED素子に直列に置かれると、トランジスタはOLED素子を駆動するのに必要な全電圧を増大させるか、OLED素子が使用する全電力を増加させるか、或いは、OLED素子に利用可能な電流の範囲を減少させる。

【0011】

2006年8月8日に発行されたCokによる米国特許7,088,051号においては、可変制御を伴うパルス幅変調機構が開示され、これを参照することによりその全体がここに組み入れられる。この開示はフレーム期間の画素の輝度を制御する手段を記述するが、外部的な制御が必要であり、そのためコストを増大させ装置の開口率を減少させる。

【発明の概要】

【発明が解決しようとする課題】

【0012】

したがって、簡潔で柔軟な設計のアクティブマトリクスOLED装置の改善された制御回路に対するニーズが存在する。本発明は改良された性能を提供しつつ簡単な制御構造を有するOLED制御装置を提供する。

【課題を解決するための手段】

【0013】

一実施形態において、本発明は、a)制御信号に応答してフレーム期間において蓄積回路に輝度値を蓄積する制御回路と、b)蓄積回路に応答してLEDの電流を制御して輝度値により決定される輝度レベルで発光させる駆動回路と、c)蓄積回路に接続されフレーム期間において蓄積回路に蓄積される輝度値の減少を制御する輝度値減少回路とを具備する、LED表示画素を制御するためのアクティブマトリクス回路を提供することを特徴とする。

【図面の簡単な説明】

【0014】

【図1】本発明の構成要素を示すブロック図である。

【図2】本発明の一実施形態を示す回路図である。

【図3】本発明の他の実施形態を示す回路図である。

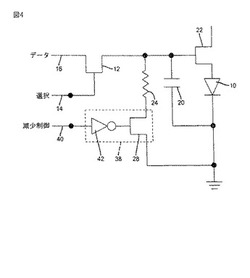

【図4】本発明のさらに他の実施形態を示す回路図である。

【図5】本発明の代替的な実施形態を示す回路図である。

【図6】本発明の一実施形態に係る画素の輝度を示すタイミング図である。

【図7】本発明の他の実施形態に係る画素の輝度を示すタイミング図である。

【図8】本発明の一実施形態に係る画素の輝度を図示しディジタル制御信号を含むより詳細なタイミング図である。

【図9】本発明の一実施形態に係る画素の輝度を図示しディジタル制御信号を含むより詳細なタイミング図である。

【図10】本発明の一実施形態に係る画素の輝度を図示しアナログ制御信号を含むより詳細なタイミング図である。

【図11】本発明の一実施形態に係る回路素子を図示する回路図とブロック図である。

【図12】先行技術のアクティブマトリクス画素の回路図である。

【図13A】先行技術において知られている制御方法に従う画素輝度を示すタイミング図である。

【図13B】先行技術において知られている制御方法に従う画素輝度を示すタイミング図である。

【図14】本発明の一実施形態に係る表示システムを示すブロック図である。

【図15】本発明の一実施形態に係る方法を示すフロー図である。

【発明を実施するための形態】

【0015】

図1を参照すると、本発明の一実施形態によれば、LED表示画素を制御するためのアクティブマトリクス回路8は、制御信号15に応答してフレームの期間において蓄積回路32に輝度値を蓄積する制御回路30と、蓄積回路32に応答してLED10の電流を制御して輝度値により決定される輝度レベルで発光させる駆動回路34と、蓄積回路32に接続されフレーム期間において蓄積回路32に蓄積される輝度値の減少を制御する輝度値減少回路36とを具備する。輝度値の制御された減少はアナログ的またはディジタル的であり連続的または不連続である。しかしながら、ここで採用されるように、制御された減少は好ましくはオンとオフのような少なくとも2つの状態を有している。そのような2状態制御は本発明において包含されないパルス幅変調機構において採用されている。ここで採用されるように、蓄積回路における輝度値の制御された減少は、輝度値を第1の非ゼロ値から第2のより小さい値へ、そして第2の値より小さい第3の値へ変える。第3の値はゼロでも良いがそれは必須ではない。

【0016】

図2を参照すると、本発明の1つの例示的な実施形態において、(図1の)制御回路30または駆動回路34は、例えば低温ポリシリコン、結晶シリコンまたはアモルファスシリコンにより基板上に形成された、それぞれトランジスタ12または22として図示されている。蓄積回路32は輝度値を表わす電荷を蓄積するコンデンサ20であってもよい。この場合に、輝度値減少回路36はコンデンサ20に蓄積された電荷を時間とともに減少させてもよい。さらなる具体例において、図2に示すように、輝度値減少回路36はコンデンサ20に並列に接続された抵抗24である。図1のVddは電圧供給源であり回路は接地電圧を基準として描かれているが、様々な回路要素に対して他の基準電圧を採用し得る。図11を参照すると、(破線で描かれた)図示の要素が図2の要素との関係において示されている。

【0017】

図3に示される代替的で例示的な実施形態において、輝度値減少回路36は、コンデンサ20に並列に接続され減少制御信号40に応答してコンデンサ20の電荷が時間とともに減少する速度を制御するトランジスタ26である。

【0018】

図4に示された本発明のさらなる例示的な実施形態において、減少制御信号40に応答する減少制御回路38が輝度値減少回路36に接続されて輝度値減少回路36が輝度値を減少させる速度を制御する。図4に示されるように、減少制御回路38は、(輝度値減少回路36を具備する)抵抗24と直列の減少制御トランジスタ28を具備して減少制御信号40に応答して抵抗24に流れる電流を制御する。(図示されないが)減少制御信号40は、減少制御トランジスタ28を直接制御するか、または(破線で示すように)減少制御信号40がインバータ42を介して選択信号14から導出されて選択信号14がアクティブでないときのみ輝度値が減少される。図5を参照すると、そのようなインバータ42は反転トランジスタ44を具備しても良い。したがって、図2または図5に示すように、制御された輝度値の減少を引き起こすためには外部からの制御は必須ではない。

【0019】

動作において、図12を参照して上記に記述したように、画素回路は蓄積回路に電荷を蓄積する。コンデンサ20が充電されると、駆動トランジスタ22は比例的にターンオンされて電力信号Vddから駆動トランジスタ22およびLED10を経て陰極接地電圧への電流を提供し、それによってコンデンサ16の電荷に相当する量の光をLEDに発光させる。しかしながら本発明によれば、輝度値が蓄積回路に蓄積され駆動回路がLEDを発光させると、輝度値は例えば(図2に示すような)抵抗を経て、または(図3に示すような)トランジスタを経て減少する。減少が起こる速度は(図2に示すように)抵抗と容量の値の選択、または(図3に示すように)採用される制御機構に依存する。放電は連続的かつ指数関数的または何らかの他の減少曲線を持ち得る。図6を参照すると、その結果は、LEDの輝度がリフレッシュ期間T1内で輝度レベルL3からゼロへ時間とともに減少し、第2のリフレッシュ期間T2において輝度レベルL4からゼロへ減少するものであり得る。(図13Aに示すような)従来技術のアクティブマトリクス回路と同様に見える明るさを維持するためには、輝度曲線の下側の面積が好ましくは同じでなければならないことに留意すべきである。LEDデバイスの平均的な明るさはリフレッシュ期間における全発光量であると知覚される。そのため、T3は図13BにおけるT2と同様にT1よりも大きい。図6に示されるように、輝度値の制御された減少は、実質的な遅延なく蓄積サイクルが完了すると同時に、すなわち選択信号がアクティブでなくなった時に始まる。実質的な遅延がないということは、選択信号がアクティブでなくなるとき、そして何らかの制御信号40があるとすればそれがアクティブになったときに制御された減少が始まることを意味する。

【0020】

図7に示されるように、蓄積回路に電荷を蓄積する画素回路の選択に対して輝度減少のタイミングを制御する外部的な減少制御信号40を採用することにより、発光のプロファイルが、例えばリフレッシュ期間の一部Tsにおいて輝度減少を妨げることで制御される。前述したように、一定の輝度の知覚を維持するためには、曲線の下側の全面積が好ましくは一定であるべきである。そのため、(第1のリフレッシュ期間T1については)初期輝度レベルL5はL3よりも小さく、(第2のリフレッシュ期間T2については)初期輝度レベルL6はL4よりも小さい。この場合において、輝度値の制御された減少は選択信号がアクティブでなくなった後の或る時まで遅延される。

【0021】

図6および図7には蓄積回路に輝度値を蓄積するのに必要なリフレッシュ期間が含まれていない。蓄積回路は、(それが代表的であるが必ずしもそれが必須なことではないが)電荷を蓄積するコンデンサであるため、いずれかの放電機構(例えば抵抗)は抵抗によるインピーダンスの増加およびその結果としての伝送線ロスのために電荷が蓄積される速度を低下させる。そのため、リフレッシュ期間の電荷蓄積部分においてアクティブにならないトランジスタを採用することで、そのような伝送線ロスが減少するか回避され、各画素回路に輝度値が蓄積される速度を改善する。

【0022】

図8を参照すると、リフレッシュ期間T1またはT2の一部Tcにおいて蓄積回路に電荷が蓄積される。部分Tcは、図示されているような選択信号が有効の状態に相当する。減少制御信号Aは選択信号の反転したタイミングを示す。より複雑な制御が必要であれば、例えば輝度減少を遅延させることにより図9の減少制御タイミングBを採用し得る。図8も図9もディジタルの減少制御信号を採用する。しかしながら、本発明は図10に示すようなアナログ制御も採用し得る。輝度値減少過程を制御することにより、広く多様な輝度減少プロファイルが達成される。

【0023】

本発明の様々な実施形態によれば、(LEDを駆動するのに必要な電圧(Vdd)を増加させてシステムの効率を低下させることになる)LED素子に直列な制御トランジスタまたは(電流を分岐させてシステムの効率を低下させる)LEDに並列の分流トランジスタは必須ではなく、それでもなお、単一の期間内で輝度レベルを低下させてアクティブマトリクスLED素子を駆動する手段を提供する。

【0024】

知られているように、従来のアクティブマトリクスOLEDディスプレイ装置にみられるような蓄積および保持回路は、観察者の目がディスプレイ装置のスクリーンを横切って動く対象物を追おうとすると残像の知覚を引き起こす。蓄積回路内の輝度値を変調してOLEDが発光する時間を短くすることでこの残像効果を減らすことができる。本発明に係る画素が出力する輝度は従来のアクティブマトリクス制御機構におけるよりも早く減衰するので観察者の目が視野を横切って動く間一定の輝度に保つことの残像効果は減少する。本発明はそのようなディスプレイ装置における動きアーチファクトをより簡単に減らすべく採用され得る。

【0025】

フラットパネルディスプレイにおいて基板上に形成されるトランジスタは多様な性能、特に多様な閾値電圧を持ち得る。本発明は(例えばTsという)リフレッシュ期間の一部において駆動トランジスタは飽和駆動状態にある、という付加的な利点を有する。(トランジスタが動作し得る最大値である)そのような飽和状態は装置のバラツキにさらされることが少なく、ディスプレイはリフレッシュサイクルのこの部分においてより均一な外観を提供し得る。そのため、本発明の付加的な実施形態において、駆動トランジスタは蓄積回路の輝度値に応答してリフレッシュサイクルの一部であるがすべてではない期間、飽和状態にある。

【0026】

従来技術の代表的なパルス幅変調機構においては、LEDは、一周期の、データに依存する可変の部分において一定の高い輝度で駆動される。この機構においては、LEDをオンにし再度オフするために各周期においてデータが2回書き込まれる。この機構は大きいLED駆動電流をも必要として材料の寿命を縮め、可変パルス幅を制御するために複雑で非常に高速の制御信号を採用する必要がある。可変パルス幅は8ビットのグレースケール表示をサポートするためには一周期の少なくとも256分の1内で制御される。これは達成することが困難である。したがって、本発明の他の利点は制御が簡単化されていることである。例えば、データは1回だけ書き込まれる。

【0027】

本発明はOLED素子の動作特性の変化を補償するためにも採用され得る。OLEDが使用されるにつれ、効率が低下し抵抗が増加する。リフレッシュ期間の第2の部分に関してリフレッシュ期間の第1の部分内での輝度減少を制御することにより多くの光がデバイスから放射され、それによってOLED素子の光出力効率の低下を補償する。したがって、本発明のさらに他の例示的な実施形態において、減少制御信号はOLED材料の経年変化を補償するために採用される。

【0028】

減少制御信号を個々に調節してリフレッシュ期間の画素からの全発光量を変えることにより不均一な変化を補償するためにも採用することができる。

【0029】

図14を参照すると、本発明は、多数の発光画素108を有し、各画素が発光する目的で電流に応答する発光素子を含むディスプレイ100と、(例えば図1に相当する)相当の発光素子を制御するためのアクティブマトリクス画素駆動回路において採用され得る。これら発光素子108は行と列に組織化されそれらに供給される制御信号が多数の行および列を一度に駆動する。各画素駆動回路は輝度値を蓄積回路に蓄積するための制御信号に応答する制御回路を具備している。蓄積回路に応答してLEDに流れる電流を制御して輝度値によって決定される輝度レベルで発光させるための駆動回路もまた含まれている。さらに、輝度値減少回路が蓄積回路に接続され蓄積回路に蓄積される輝度値を時間とともに減少させる。ディスプレイ100は、入力信号104に応答してコントローラ102によって供給される(電源および制御信号を含む)信号106で駆動され得る。

【0030】

減少制御信号は単一の制御構造がすべての変調回路を動作させるようにLED素子のすべてに共通に接続されても良い。或いはまた、OLEDのグループに対して別々の減少制御信号が採用される。これらのグループは例えば、カラーディスプレイにおける特定の量の光を発するすべてのLED素子を具備している。カラーディスプレイにおいて異なるLED材料が異なる色を発光するために採用され経年変化も異なるのでLED素子の各グループを別々に制御することは有利である。代表的には、データおよび選択制御信号はディスプレイのラインまたは列を一度にリフレッシュする。行または列を循環する同じ手法が変調信号を制御するためにも採用され、変調信号に共通に接続された各LEDが一行または一列について一度に更新され同じ時間だけLEDを発光させる。

【0031】

本発明とともに使用されるのに適したLEDコントローラは通常のディジタル論理制御の手法を用いて構成され得る。通常の設計を用いて回路制御信号が適用される。図15を参照すると、そのようなコントローラは、ステップ200において、輝度値を蓄積回路に蓄積して輝度値により決定される輝度レベルで発光すべくLEDに流れる電流を制御し、ステップ202において、蓄積回路に接続された輝度値減少回路を採用することでフレーム期間内での輝度値の減少を制御して蓄積回路に蓄積される輝度値を減少させるべく、LED画素制御信号を採用することでフレーム期間内の表示装置の輝度を減少する方法を実現する。

【0032】

好ましい実施形態において、Tang et al.に対して1988年9月6日に発行された「修正された薄膜発光ゾーンを有するデバイス」という名称の米国特許第4,769,292号、およびVanSlyke et al.に対して1991年10月29日に発行された「有機電子発光媒体を有するエレクトロルミネッセンスデバイス」という名称の米国特許第5,061,569号において開示されるような、しかしそれに限定されない低分子または高分子OLEDからなる有機発光ダイオード(OLED)を含む発光ディスプレイにおいて本発明は採用される。OLED材料および技術の多くの組み合わせおよび変形が当業者に利用可能であり、本発明に係るOLED表示装置の製造に使用され得る。代替的な実施形態において、本発明は、例えば多結晶半導体マトリクス内の燐光結晶または量子ドットのような無機発光材料と共に採用される。

【符号の説明】

【0033】

8 アクティブマトリクス制御回路

10 発光ダイオード

12 制御トランジスタ

14 選択信号

15 制御信号

16 データ信号

20 コンデンサ

22 駆動トランジスタ

24 抵抗

26 輝度値減少トランジスタ

28 減少制御トランジスタ

30 制御回路

32 蓄積回路

34 駆動回路

36 輝度値減少回路

38 減少制御回路

40 減少制御信号

42 インバータ

44 インバータトランジスタ

100 ディスプレイ

102 コントローラ

104 信号

106 信号

108 発光素子

200 輝度値蓄積ステップ

202 輝度値減少ステップ

【技術分野】

【0001】

本発明は、ソリッドステート表示デバイスおよび画素値と画像を記憶し表示する手段に関する。

【背景技術】

【0002】

発光画素を利用するソリッドステート画像表示デバイスは周知であり広く用いられている。例えば、OLEDデバイスがパッシブおよびアクティブマトリクスの双方の形で、およびトップエミッタおよびボトムエミッタの双方の方式でフラットパネルディスプレイにおいて用いられている。OLEDディスプレイの制御回路もまた周知の技術であり、電圧制御および電流制御の双方の機構を含んでいる。

【0003】

従来のパッシブマトリクスOLEDディスプレイは、OLED発光素子が特定の輝度で発光する(フレームまたはフレーム期間としても知られている)固定的な期間においてOLED素子に電流を流すドライバを採用している。OLED素子の行または列に順次エネルギが与えられ、フリッカの発現を回避するに充分な速度でOLEDディスプレイ全体がリフレッシュされる。例えば2003年8月24日に公開された名称「OLED素子ドライバにパルス振幅変調を与えるシステムと方法」のWO2003/034389には、有機発光ダイオードディスプレイのためのパルス幅変調ドライバが記載されている。ビデオディスプレイの一実施形態は、ビデオディスプレイの有機発光ダイオードを駆動する選択された電圧を提供するための電圧ドライバを備えている。電圧ドライバは、経年変化、行抵抗、列抵抗、および他のダイオード特性を考慮した補正テーブルから電圧情報を受け取る。

【0004】

これに対して、アクティブマトリクス回路は、ディスプレイの各発光素子に対して設けられた回路の2次元アレイを採用する。アクティブマトリクス回路は、(代表的にはコンデンサへの電荷としての)値を記憶させる制御機構を提供し、この値は駆動回路を制御して(画素またはサブ画素としても知られる)発光素子に流れる電流をもたらすために使用される。ここで使われているように、各発光素子は色によらず、または他の発光素子とのグループ化にかかわらず画素であると考えられる。例えば、図12を参照すると、LED10を駆動するためのアクティブマトリクス画素回路は選択信号14およびデータ信号16のような制御信号に応答する制御トランジスタ12を含んでいる。選択信号14がアクティブになると、制御トランジスタ12がターンオンし、データ信号がコンデンサ20への電荷をもたらす。制御トランジスタ12はその後選択信号14がアクティブでなくなることでターンオフする。コンデンサ20に蓄えられた電荷は駆動トランジスタ22をターンオンしてコンデンサ20に蓄えられた電荷に比例した電流をLED10にもたらす。図13Aを参照すると、画素は第1のフレーム期間T1において輝度レベルL1で発光し、第2のフレーム期間T2において第2の輝度L2で発光する。輝度の変化は、観察者により、画像の変化、例えば或る場面における動きとして知覚される。

【0005】

従来のフラットパネルディスプレイにおいて、表示信号は、代表的には、映像ストリームの連続するフレームにおいて滑らかな動きの発現をもたらすに充分な速度で周期的にリフレッシュされる。リフレッシュ速度は代表的にはモニタで1秒あたり30,60,70,75,80,90または100フレームであり、テレビで1秒あたり50または60フレームである。そのため、従来のフラットパネルディスプレイにおいては、コンデンサ20の電荷は用途に応じて選択されたリフレッシュ速度で更新される。

【0006】

各画素の輝度値は代表的にはフレーム期間を定める(例えば30Hzまたは60Hzの)リフレッシュ速度でリフレッシュされる。フレーム期間は、画素の輝度値が変化するときに動性錯覚をもたらすように充分に短く選ばれる。知られているように、このようなアクティブマトリクス回路は、観察者の目がディスプレイを横切って画像が網膜の異なる部分に映されると、画像がフレーム期間中静止しているため、観察者に残像(モーションブラー)を引き起こす。この残像はリフレッシュ期間を短くする、すなわち高い周波数でリフレッシュすることで減らすことができる。しかしながら、そのような解決策は、高い周波数が採用されるとドライバのコストが上昇し各画素位置に電荷を蓄積するために用いられる制御線における伝送線の影響を悪化させるという点で問題がある。或いはまた、例えばフレーム期間の一部だけより明るく発光させて、各フレームで画素が発光する時間を短くすることもできる。フレーム期間が充分に短いとフリッカは感じられなくなる。図13Bを参照すると、第1のフレーム期間T1では期間T1の半分の期間で2倍の光2L1を発し、同様に、期間T2の半分の期間で2倍の輝度レベル2L2で発光するよう画素が制御される。関連する解決策において、ディスプレイの複数の部分がディスプレイを横切ってスクロールする黒いバーを表示する。しかしながら、これらの解決策はコストを上昇させる高周波制御を必要とし、より長い制御線を有する大規模なディスプレイに対しては問題がある。

【0007】

図13Bに示されたような表示画素を制御するためには公知のパルス幅変調技術を採用することができる。さらに、アクティブマトリクスにおいて採用される薄膜駆動トランジスタの閾値スイッチング特性のバラツキがOLEDディスプレイの不均一性の1つの原因であるから、アクティブマトリクスOLEDディスプレイの不均一性を改善する1つのアプローチは電荷蓄積制御技術とは対照的なパルス幅変調技術を採用することである。これらパルス幅変調技術は、1つのフレーム期間内で、特定の第1の時間において最大電流および輝度でOLEDを駆動し、次に第2の時間においてOLEDをターンオフすることで機能する。第1および第2の時間の合計が充分に小さければOLEDを周期的にオンオフすることによるフリッカは観察者に感じられない。OLED素子の輝度は、OLEDがオフになっている時間に対するOLEDがオンになっている時間の比を変えることで制御される。

【0008】

パルス幅変調を使ってOLEDディスプレイを制御する様々な方法が知られている。例えば2004年10月26日に付与された「電子ディスプレイのグレースケール画素ドライバおよびそのための動作方法」という名称の米国特許第6,809,710号はグラフィックディスプレイにおいてOLEDを駆動する回路を開示している。その回路はスイッチングモードで動作するOLEDの端子に接続された電流源を採用している。電流源は選択的に設定された周期的な電圧信号と周期的な可変振幅電圧信号の組み合わせに応答する。電流源はオンであるときLEDが最大輝度を達成するのに必要な電流をOLEDに供給するよう設計され最適化されている。オフになると、電流源はOLEDへの電流の供給を阻止してOLEDディスプレイに均一な黒レベルをもたらす。OLEDのみかけ上の輝度はOLEDに供給される電流のパルス幅を変調して電流がOLEDに供給される時間を変えることにより制御される。

【0009】

電流源のスイッチングの動作モードを使用することで回路は電流駆動OLEDディスプレイの輝度値を制御するための広い範囲の電圧を採用することが可能になる。しかしながら、電流駆動回路は複雑であり表示装置の各画素に対して広いスペースを必要とする。

【0010】

単一の回路でパルス幅制御と可変電荷蓄積制御の双方を提供する方法もまた知られている。「アクティブマトリクス発光装置の駆動回路」という名称の米国特許6,670,773がOLED素子と並列なトランジスタを示唆している。しかしながら、記述された技術はOLEDからの駆動電流を分岐して回路の動作効率を低下させるものである。その他の設計では、OLED素子の性能を制御または測定する、OLED素子に直列な回路素子が採用される。例えば、2004年4月29日に公開された「アクティブマトリクス有機EL表示装置」という名称のWO2004/036536はOLED素子に直列に付加された素子を有する回路を開示する。しかしながら、OLED素子に直列に置かれると、トランジスタはOLED素子を駆動するのに必要な全電圧を増大させるか、OLED素子が使用する全電力を増加させるか、或いは、OLED素子に利用可能な電流の範囲を減少させる。

【0011】

2006年8月8日に発行されたCokによる米国特許7,088,051号においては、可変制御を伴うパルス幅変調機構が開示され、これを参照することによりその全体がここに組み入れられる。この開示はフレーム期間の画素の輝度を制御する手段を記述するが、外部的な制御が必要であり、そのためコストを増大させ装置の開口率を減少させる。

【発明の概要】

【発明が解決しようとする課題】

【0012】

したがって、簡潔で柔軟な設計のアクティブマトリクスOLED装置の改善された制御回路に対するニーズが存在する。本発明は改良された性能を提供しつつ簡単な制御構造を有するOLED制御装置を提供する。

【課題を解決するための手段】

【0013】

一実施形態において、本発明は、a)制御信号に応答してフレーム期間において蓄積回路に輝度値を蓄積する制御回路と、b)蓄積回路に応答してLEDの電流を制御して輝度値により決定される輝度レベルで発光させる駆動回路と、c)蓄積回路に接続されフレーム期間において蓄積回路に蓄積される輝度値の減少を制御する輝度値減少回路とを具備する、LED表示画素を制御するためのアクティブマトリクス回路を提供することを特徴とする。

【図面の簡単な説明】

【0014】

【図1】本発明の構成要素を示すブロック図である。

【図2】本発明の一実施形態を示す回路図である。

【図3】本発明の他の実施形態を示す回路図である。

【図4】本発明のさらに他の実施形態を示す回路図である。

【図5】本発明の代替的な実施形態を示す回路図である。

【図6】本発明の一実施形態に係る画素の輝度を示すタイミング図である。

【図7】本発明の他の実施形態に係る画素の輝度を示すタイミング図である。

【図8】本発明の一実施形態に係る画素の輝度を図示しディジタル制御信号を含むより詳細なタイミング図である。

【図9】本発明の一実施形態に係る画素の輝度を図示しディジタル制御信号を含むより詳細なタイミング図である。

【図10】本発明の一実施形態に係る画素の輝度を図示しアナログ制御信号を含むより詳細なタイミング図である。

【図11】本発明の一実施形態に係る回路素子を図示する回路図とブロック図である。

【図12】先行技術のアクティブマトリクス画素の回路図である。

【図13A】先行技術において知られている制御方法に従う画素輝度を示すタイミング図である。

【図13B】先行技術において知られている制御方法に従う画素輝度を示すタイミング図である。

【図14】本発明の一実施形態に係る表示システムを示すブロック図である。

【図15】本発明の一実施形態に係る方法を示すフロー図である。

【発明を実施するための形態】

【0015】

図1を参照すると、本発明の一実施形態によれば、LED表示画素を制御するためのアクティブマトリクス回路8は、制御信号15に応答してフレームの期間において蓄積回路32に輝度値を蓄積する制御回路30と、蓄積回路32に応答してLED10の電流を制御して輝度値により決定される輝度レベルで発光させる駆動回路34と、蓄積回路32に接続されフレーム期間において蓄積回路32に蓄積される輝度値の減少を制御する輝度値減少回路36とを具備する。輝度値の制御された減少はアナログ的またはディジタル的であり連続的または不連続である。しかしながら、ここで採用されるように、制御された減少は好ましくはオンとオフのような少なくとも2つの状態を有している。そのような2状態制御は本発明において包含されないパルス幅変調機構において採用されている。ここで採用されるように、蓄積回路における輝度値の制御された減少は、輝度値を第1の非ゼロ値から第2のより小さい値へ、そして第2の値より小さい第3の値へ変える。第3の値はゼロでも良いがそれは必須ではない。

【0016】

図2を参照すると、本発明の1つの例示的な実施形態において、(図1の)制御回路30または駆動回路34は、例えば低温ポリシリコン、結晶シリコンまたはアモルファスシリコンにより基板上に形成された、それぞれトランジスタ12または22として図示されている。蓄積回路32は輝度値を表わす電荷を蓄積するコンデンサ20であってもよい。この場合に、輝度値減少回路36はコンデンサ20に蓄積された電荷を時間とともに減少させてもよい。さらなる具体例において、図2に示すように、輝度値減少回路36はコンデンサ20に並列に接続された抵抗24である。図1のVddは電圧供給源であり回路は接地電圧を基準として描かれているが、様々な回路要素に対して他の基準電圧を採用し得る。図11を参照すると、(破線で描かれた)図示の要素が図2の要素との関係において示されている。

【0017】

図3に示される代替的で例示的な実施形態において、輝度値減少回路36は、コンデンサ20に並列に接続され減少制御信号40に応答してコンデンサ20の電荷が時間とともに減少する速度を制御するトランジスタ26である。

【0018】

図4に示された本発明のさらなる例示的な実施形態において、減少制御信号40に応答する減少制御回路38が輝度値減少回路36に接続されて輝度値減少回路36が輝度値を減少させる速度を制御する。図4に示されるように、減少制御回路38は、(輝度値減少回路36を具備する)抵抗24と直列の減少制御トランジスタ28を具備して減少制御信号40に応答して抵抗24に流れる電流を制御する。(図示されないが)減少制御信号40は、減少制御トランジスタ28を直接制御するか、または(破線で示すように)減少制御信号40がインバータ42を介して選択信号14から導出されて選択信号14がアクティブでないときのみ輝度値が減少される。図5を参照すると、そのようなインバータ42は反転トランジスタ44を具備しても良い。したがって、図2または図5に示すように、制御された輝度値の減少を引き起こすためには外部からの制御は必須ではない。

【0019】

動作において、図12を参照して上記に記述したように、画素回路は蓄積回路に電荷を蓄積する。コンデンサ20が充電されると、駆動トランジスタ22は比例的にターンオンされて電力信号Vddから駆動トランジスタ22およびLED10を経て陰極接地電圧への電流を提供し、それによってコンデンサ16の電荷に相当する量の光をLEDに発光させる。しかしながら本発明によれば、輝度値が蓄積回路に蓄積され駆動回路がLEDを発光させると、輝度値は例えば(図2に示すような)抵抗を経て、または(図3に示すような)トランジスタを経て減少する。減少が起こる速度は(図2に示すように)抵抗と容量の値の選択、または(図3に示すように)採用される制御機構に依存する。放電は連続的かつ指数関数的または何らかの他の減少曲線を持ち得る。図6を参照すると、その結果は、LEDの輝度がリフレッシュ期間T1内で輝度レベルL3からゼロへ時間とともに減少し、第2のリフレッシュ期間T2において輝度レベルL4からゼロへ減少するものであり得る。(図13Aに示すような)従来技術のアクティブマトリクス回路と同様に見える明るさを維持するためには、輝度曲線の下側の面積が好ましくは同じでなければならないことに留意すべきである。LEDデバイスの平均的な明るさはリフレッシュ期間における全発光量であると知覚される。そのため、T3は図13BにおけるT2と同様にT1よりも大きい。図6に示されるように、輝度値の制御された減少は、実質的な遅延なく蓄積サイクルが完了すると同時に、すなわち選択信号がアクティブでなくなった時に始まる。実質的な遅延がないということは、選択信号がアクティブでなくなるとき、そして何らかの制御信号40があるとすればそれがアクティブになったときに制御された減少が始まることを意味する。

【0020】

図7に示されるように、蓄積回路に電荷を蓄積する画素回路の選択に対して輝度減少のタイミングを制御する外部的な減少制御信号40を採用することにより、発光のプロファイルが、例えばリフレッシュ期間の一部Tsにおいて輝度減少を妨げることで制御される。前述したように、一定の輝度の知覚を維持するためには、曲線の下側の全面積が好ましくは一定であるべきである。そのため、(第1のリフレッシュ期間T1については)初期輝度レベルL5はL3よりも小さく、(第2のリフレッシュ期間T2については)初期輝度レベルL6はL4よりも小さい。この場合において、輝度値の制御された減少は選択信号がアクティブでなくなった後の或る時まで遅延される。

【0021】

図6および図7には蓄積回路に輝度値を蓄積するのに必要なリフレッシュ期間が含まれていない。蓄積回路は、(それが代表的であるが必ずしもそれが必須なことではないが)電荷を蓄積するコンデンサであるため、いずれかの放電機構(例えば抵抗)は抵抗によるインピーダンスの増加およびその結果としての伝送線ロスのために電荷が蓄積される速度を低下させる。そのため、リフレッシュ期間の電荷蓄積部分においてアクティブにならないトランジスタを採用することで、そのような伝送線ロスが減少するか回避され、各画素回路に輝度値が蓄積される速度を改善する。

【0022】

図8を参照すると、リフレッシュ期間T1またはT2の一部Tcにおいて蓄積回路に電荷が蓄積される。部分Tcは、図示されているような選択信号が有効の状態に相当する。減少制御信号Aは選択信号の反転したタイミングを示す。より複雑な制御が必要であれば、例えば輝度減少を遅延させることにより図9の減少制御タイミングBを採用し得る。図8も図9もディジタルの減少制御信号を採用する。しかしながら、本発明は図10に示すようなアナログ制御も採用し得る。輝度値減少過程を制御することにより、広く多様な輝度減少プロファイルが達成される。

【0023】

本発明の様々な実施形態によれば、(LEDを駆動するのに必要な電圧(Vdd)を増加させてシステムの効率を低下させることになる)LED素子に直列な制御トランジスタまたは(電流を分岐させてシステムの効率を低下させる)LEDに並列の分流トランジスタは必須ではなく、それでもなお、単一の期間内で輝度レベルを低下させてアクティブマトリクスLED素子を駆動する手段を提供する。

【0024】

知られているように、従来のアクティブマトリクスOLEDディスプレイ装置にみられるような蓄積および保持回路は、観察者の目がディスプレイ装置のスクリーンを横切って動く対象物を追おうとすると残像の知覚を引き起こす。蓄積回路内の輝度値を変調してOLEDが発光する時間を短くすることでこの残像効果を減らすことができる。本発明に係る画素が出力する輝度は従来のアクティブマトリクス制御機構におけるよりも早く減衰するので観察者の目が視野を横切って動く間一定の輝度に保つことの残像効果は減少する。本発明はそのようなディスプレイ装置における動きアーチファクトをより簡単に減らすべく採用され得る。

【0025】

フラットパネルディスプレイにおいて基板上に形成されるトランジスタは多様な性能、特に多様な閾値電圧を持ち得る。本発明は(例えばTsという)リフレッシュ期間の一部において駆動トランジスタは飽和駆動状態にある、という付加的な利点を有する。(トランジスタが動作し得る最大値である)そのような飽和状態は装置のバラツキにさらされることが少なく、ディスプレイはリフレッシュサイクルのこの部分においてより均一な外観を提供し得る。そのため、本発明の付加的な実施形態において、駆動トランジスタは蓄積回路の輝度値に応答してリフレッシュサイクルの一部であるがすべてではない期間、飽和状態にある。

【0026】

従来技術の代表的なパルス幅変調機構においては、LEDは、一周期の、データに依存する可変の部分において一定の高い輝度で駆動される。この機構においては、LEDをオンにし再度オフするために各周期においてデータが2回書き込まれる。この機構は大きいLED駆動電流をも必要として材料の寿命を縮め、可変パルス幅を制御するために複雑で非常に高速の制御信号を採用する必要がある。可変パルス幅は8ビットのグレースケール表示をサポートするためには一周期の少なくとも256分の1内で制御される。これは達成することが困難である。したがって、本発明の他の利点は制御が簡単化されていることである。例えば、データは1回だけ書き込まれる。

【0027】

本発明はOLED素子の動作特性の変化を補償するためにも採用され得る。OLEDが使用されるにつれ、効率が低下し抵抗が増加する。リフレッシュ期間の第2の部分に関してリフレッシュ期間の第1の部分内での輝度減少を制御することにより多くの光がデバイスから放射され、それによってOLED素子の光出力効率の低下を補償する。したがって、本発明のさらに他の例示的な実施形態において、減少制御信号はOLED材料の経年変化を補償するために採用される。

【0028】

減少制御信号を個々に調節してリフレッシュ期間の画素からの全発光量を変えることにより不均一な変化を補償するためにも採用することができる。

【0029】

図14を参照すると、本発明は、多数の発光画素108を有し、各画素が発光する目的で電流に応答する発光素子を含むディスプレイ100と、(例えば図1に相当する)相当の発光素子を制御するためのアクティブマトリクス画素駆動回路において採用され得る。これら発光素子108は行と列に組織化されそれらに供給される制御信号が多数の行および列を一度に駆動する。各画素駆動回路は輝度値を蓄積回路に蓄積するための制御信号に応答する制御回路を具備している。蓄積回路に応答してLEDに流れる電流を制御して輝度値によって決定される輝度レベルで発光させるための駆動回路もまた含まれている。さらに、輝度値減少回路が蓄積回路に接続され蓄積回路に蓄積される輝度値を時間とともに減少させる。ディスプレイ100は、入力信号104に応答してコントローラ102によって供給される(電源および制御信号を含む)信号106で駆動され得る。

【0030】

減少制御信号は単一の制御構造がすべての変調回路を動作させるようにLED素子のすべてに共通に接続されても良い。或いはまた、OLEDのグループに対して別々の減少制御信号が採用される。これらのグループは例えば、カラーディスプレイにおける特定の量の光を発するすべてのLED素子を具備している。カラーディスプレイにおいて異なるLED材料が異なる色を発光するために採用され経年変化も異なるのでLED素子の各グループを別々に制御することは有利である。代表的には、データおよび選択制御信号はディスプレイのラインまたは列を一度にリフレッシュする。行または列を循環する同じ手法が変調信号を制御するためにも採用され、変調信号に共通に接続された各LEDが一行または一列について一度に更新され同じ時間だけLEDを発光させる。

【0031】

本発明とともに使用されるのに適したLEDコントローラは通常のディジタル論理制御の手法を用いて構成され得る。通常の設計を用いて回路制御信号が適用される。図15を参照すると、そのようなコントローラは、ステップ200において、輝度値を蓄積回路に蓄積して輝度値により決定される輝度レベルで発光すべくLEDに流れる電流を制御し、ステップ202において、蓄積回路に接続された輝度値減少回路を採用することでフレーム期間内での輝度値の減少を制御して蓄積回路に蓄積される輝度値を減少させるべく、LED画素制御信号を採用することでフレーム期間内の表示装置の輝度を減少する方法を実現する。

【0032】

好ましい実施形態において、Tang et al.に対して1988年9月6日に発行された「修正された薄膜発光ゾーンを有するデバイス」という名称の米国特許第4,769,292号、およびVanSlyke et al.に対して1991年10月29日に発行された「有機電子発光媒体を有するエレクトロルミネッセンスデバイス」という名称の米国特許第5,061,569号において開示されるような、しかしそれに限定されない低分子または高分子OLEDからなる有機発光ダイオード(OLED)を含む発光ディスプレイにおいて本発明は採用される。OLED材料および技術の多くの組み合わせおよび変形が当業者に利用可能であり、本発明に係るOLED表示装置の製造に使用され得る。代替的な実施形態において、本発明は、例えば多結晶半導体マトリクス内の燐光結晶または量子ドットのような無機発光材料と共に採用される。

【符号の説明】

【0033】

8 アクティブマトリクス制御回路

10 発光ダイオード

12 制御トランジスタ

14 選択信号

15 制御信号

16 データ信号

20 コンデンサ

22 駆動トランジスタ

24 抵抗

26 輝度値減少トランジスタ

28 減少制御トランジスタ

30 制御回路

32 蓄積回路

34 駆動回路

36 輝度値減少回路

38 減少制御回路

40 減少制御信号

42 インバータ

44 インバータトランジスタ

100 ディスプレイ

102 コントローラ

104 信号

106 信号

108 発光素子

200 輝度値蓄積ステップ

202 輝度値減少ステップ

【特許請求の範囲】

【請求項1】

a)制御信号に応答してフレーム期間において蓄積回路に輝度値を蓄積する制御回路と;

b)前記蓄積回路に応答してLEDの電流を制御して前記輝度値により決定される輝度レベルで発光させる駆動回路と;

c)前記蓄積回路に接続され前記フレーム期間において前記蓄積回路に蓄積される前記輝度値の減少を制御する輝度値減少回路とを具備する、LED表示画素を制御するためのアクティブマトリクス回路。

【請求項2】

前記制御回路または駆動回路は基板上に形成されたトランジスタである請求項1記載のアクティブマトリクス回路。

【請求項3】

前記蓄積回路は前記輝度値を表現する電荷を蓄積するコンデンサである請求項1記載のアクティブマトリクス回路。

【請求項4】

前記輝度値減少回路は前記コンデンサに蓄積される前記電荷を時間とともに減少させる請求項3記載のアクティブマトリクス回路。

【請求項5】

前記輝度値減少回路は前記コンデンサに並列に接続された抵抗である請求項4記載のアクティブマトリクス回路。

【請求項6】

前記輝度値減少回路は前記コンデンサに並列に接続されたトランジスタであり制御信号に応答して前記コンデンサの前記電荷が時間とともに減少する速度を制御する請求項4記載のアクティブマトリクス回路。

【請求項7】

前記輝度値減少回路に接続され減少制御信号に応答して輝度値減少回路が輝度値を減少させる速度を制御する減少制御回路をさらに具備する請求項1記載のアクティブマトリクス回路。

【請求項8】

前記減少制御回路はトランジスタである請求項7記載のアクティブマトリクス回路。

【請求項9】

前記蓄積回路は前記輝度値を表現する電荷を蓄積するコンデンサであり、前記輝度値減少回路は前記コンデンサに並列に接続された抵抗であり、前記減少制御トランジスタは前記抵抗に直列に接続されて前記減少制御信号に応答して前記抵抗に流れる電流を制御する請求項8記載のアクティブマトリクス回路。

【請求項10】

前記制御信号は前記制御回路を制御する選択信号を含み、前記減少制御信号は前記選択信号の反転信号である請求項7記載のアクティブマトリクス回路。

【請求項11】

前記減少制御回路はインバータである請求項10記載のアクティブマトリクス回路。

【請求項12】

前記インバータはトランジスタである請求項11記載のアクティブマトリクス回路。

【請求項13】

前記制御された減少は前記輝度値が前記蓄積回路に蓄積された後、実質的な遅延なく始まる請求項1記載のアクティブマトリクス回路。

【請求項14】

前記輝度値は、前記輝度値が前記蓄積回路に蓄積された後前記フレーム期間よりも短い第1の期間において一定値に保たれ前記第1の期間の終わりに減少される請求項1記載のアクティブマトリクス回路。

【請求項15】

前記輝度値は前記輝度値が前記蓄積回路に蓄積された後連続的に減少する請求項1記載のアクティブマトリクス回路。

【請求項16】

a)基板上に形成された複数の発光画素であって、各画素は電流に応答して発光する発光ダイオード(LED)と該LEDに電流を提供する画素駆動回路とを含む複数の発光画素を具備し、各画素駆動回路はさらに、

i)制御信号に応答して蓄積回路に輝度値を蓄積する制御回路と;

ii)前記蓄積回路に応答してLEDの電流を制御して前記輝度値により決定される輝度レベルで発光させる駆動回路と;

iii)前記蓄積回路に接続され前記蓄積回路に蓄積される前記輝度値を時間とともに減少させる輝度値減少回路とを具備する、表示装置。

【請求項17】

前記LEDは有機発光ダイオードである請求項16記載の表示装置。

【請求項18】

前記LEDは無機発光ダイオードである請求項16記載の表示装置。

【請求項19】

前記無機LEDは多結晶半導体マトリクスにおける量子ドットである請求項16記載の表示装置。

【請求項20】

フレーム期間内で表示装置の輝度を減少させる方法であって、

a)LED画素制御信号を使用して輝度値を蓄積回路に蓄積してLEDの電流を制御して前記輝度値により決定される輝度レベルで発光させ;

b)前記蓄積回路に接続された輝度値減少回路を使用することによってフレーム期間内で前記輝度値の減少を制御して前記蓄積回路に蓄積される前記輝度値を減少させるステップを具備する方法。

【請求項1】

a)制御信号に応答してフレーム期間において蓄積回路に輝度値を蓄積する制御回路と;

b)前記蓄積回路に応答してLEDの電流を制御して前記輝度値により決定される輝度レベルで発光させる駆動回路と;

c)前記蓄積回路に接続され前記フレーム期間において前記蓄積回路に蓄積される前記輝度値の減少を制御する輝度値減少回路とを具備する、LED表示画素を制御するためのアクティブマトリクス回路。

【請求項2】

前記制御回路または駆動回路は基板上に形成されたトランジスタである請求項1記載のアクティブマトリクス回路。

【請求項3】

前記蓄積回路は前記輝度値を表現する電荷を蓄積するコンデンサである請求項1記載のアクティブマトリクス回路。

【請求項4】

前記輝度値減少回路は前記コンデンサに蓄積される前記電荷を時間とともに減少させる請求項3記載のアクティブマトリクス回路。

【請求項5】

前記輝度値減少回路は前記コンデンサに並列に接続された抵抗である請求項4記載のアクティブマトリクス回路。

【請求項6】

前記輝度値減少回路は前記コンデンサに並列に接続されたトランジスタであり制御信号に応答して前記コンデンサの前記電荷が時間とともに減少する速度を制御する請求項4記載のアクティブマトリクス回路。

【請求項7】

前記輝度値減少回路に接続され減少制御信号に応答して輝度値減少回路が輝度値を減少させる速度を制御する減少制御回路をさらに具備する請求項1記載のアクティブマトリクス回路。

【請求項8】

前記減少制御回路はトランジスタである請求項7記載のアクティブマトリクス回路。

【請求項9】

前記蓄積回路は前記輝度値を表現する電荷を蓄積するコンデンサであり、前記輝度値減少回路は前記コンデンサに並列に接続された抵抗であり、前記減少制御トランジスタは前記抵抗に直列に接続されて前記減少制御信号に応答して前記抵抗に流れる電流を制御する請求項8記載のアクティブマトリクス回路。

【請求項10】

前記制御信号は前記制御回路を制御する選択信号を含み、前記減少制御信号は前記選択信号の反転信号である請求項7記載のアクティブマトリクス回路。

【請求項11】

前記減少制御回路はインバータである請求項10記載のアクティブマトリクス回路。

【請求項12】

前記インバータはトランジスタである請求項11記載のアクティブマトリクス回路。

【請求項13】

前記制御された減少は前記輝度値が前記蓄積回路に蓄積された後、実質的な遅延なく始まる請求項1記載のアクティブマトリクス回路。

【請求項14】

前記輝度値は、前記輝度値が前記蓄積回路に蓄積された後前記フレーム期間よりも短い第1の期間において一定値に保たれ前記第1の期間の終わりに減少される請求項1記載のアクティブマトリクス回路。

【請求項15】

前記輝度値は前記輝度値が前記蓄積回路に蓄積された後連続的に減少する請求項1記載のアクティブマトリクス回路。

【請求項16】

a)基板上に形成された複数の発光画素であって、各画素は電流に応答して発光する発光ダイオード(LED)と該LEDに電流を提供する画素駆動回路とを含む複数の発光画素を具備し、各画素駆動回路はさらに、

i)制御信号に応答して蓄積回路に輝度値を蓄積する制御回路と;

ii)前記蓄積回路に応答してLEDの電流を制御して前記輝度値により決定される輝度レベルで発光させる駆動回路と;

iii)前記蓄積回路に接続され前記蓄積回路に蓄積される前記輝度値を時間とともに減少させる輝度値減少回路とを具備する、表示装置。

【請求項17】

前記LEDは有機発光ダイオードである請求項16記載の表示装置。

【請求項18】

前記LEDは無機発光ダイオードである請求項16記載の表示装置。

【請求項19】

前記無機LEDは多結晶半導体マトリクスにおける量子ドットである請求項16記載の表示装置。

【請求項20】

フレーム期間内で表示装置の輝度を減少させる方法であって、

a)LED画素制御信号を使用して輝度値を蓄積回路に蓄積してLEDの電流を制御して前記輝度値により決定される輝度レベルで発光させ;

b)前記蓄積回路に接続された輝度値減少回路を使用することによってフレーム期間内で前記輝度値の減少を制御して前記蓄積回路に蓄積される前記輝度値を減少させるステップを具備する方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13A】

【図13B】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13A】

【図13B】

【図14】

【図15】

【公開番号】特開2013−101351(P2013−101351A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2012−265463(P2012−265463)

【出願日】平成24年12月4日(2012.12.4)

【分割の表示】特願2010−532070(P2010−532070)の分割

【原出願日】平成20年11月3日(2008.11.3)

【出願人】(510059907)グローバル オーエルイーディー テクノロジー リミティド ライアビリティ カンパニー (45)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成24年12月4日(2012.12.4)

【分割の表示】特願2010−532070(P2010−532070)の分割

【原出願日】平成20年11月3日(2008.11.3)

【出願人】(510059907)グローバル オーエルイーディー テクノロジー リミティド ライアビリティ カンパニー (45)

【Fターム(参考)】

[ Back to top ]