制御回路及びそれを用いた電子機器

【課題】電源回路が故障し、負電圧を印加できなくなると、GaN−HEMTは、ON状態となってしまい、意図しない電力が出力されてしまうことがあることを防止する。

【解決手段】制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、前記ゲートを制御するPWM信号から前記第1のスイッチング素子の閾値以下の負電位の電圧を生成する負電圧発生回路と、前記PWM信号のレベルを前記負電位の電圧分シフトした信号を前記ゲートに出力するゲート制御回路と、前記第1のスイッチング素子のドレイン側に設けられた第2のスイッチング素子と、前記負電圧発生回路が生成する負電位の電圧が所定の負電位に達したことを検出して前記第2のスイッチング素子をオンする信号を出力する負電圧検出回路とを有する。

【解決手段】制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、前記ゲートを制御するPWM信号から前記第1のスイッチング素子の閾値以下の負電位の電圧を生成する負電圧発生回路と、前記PWM信号のレベルを前記負電位の電圧分シフトした信号を前記ゲートに出力するゲート制御回路と、前記第1のスイッチング素子のドレイン側に設けられた第2のスイッチング素子と、前記負電圧発生回路が生成する負電位の電圧が所定の負電位に達したことを検出して前記第2のスイッチング素子をオンする信号を出力する負電圧検出回路とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ノーマリーオンのスイッチング素子を含む制御回路及びそれを用いた電子機器に関する。

【背景技術】

【0002】

近年、様々な分野におけるエネルギー資源の節約が注目され、例えば、電源の分野においてもその影響が波及している。具体的には、例えば、スイッチング電源のさらなる高効率化が求められるようになってきている。

【0003】

スイッチング電源は、入力された直流電圧をDC(Direct Current)−DCコンバータを用いて所望の直流電圧に変換し、安定化電源電圧として出力するようにしてある。コンピュータに用いられるCPU( Central Processing Unit )等の半導体素子は、電源の低電圧化及び消費電力の増大に伴って、低電圧かつ大電流を出力可能なスイッチング電源が使用されてきている。

【0004】

図1は、DC−DCコンバータの一種の一般的な降圧型コンバータの回路図を示す。

【0005】

図1に示す降圧型コンバータ10は、入力電圧V1を降圧して所望の電位の出力電圧を生成し、負荷回路RL0に供給する。降圧型コンバータ10は、入力電圧V1をオンオフする主スイッチとなるスイッチング素子SW10と、整流用ダイオードD10と、インダクタL10と、平滑コンデンサC10とを備えている。

【0006】

スイッチング素子SW10には、例えば、MOSFET(Metal Oxide Semiconductor Field-Effect Transistor)が用いられる。スイッチング素子SW10は、PWM信号発生回路20からゲートにパルス状のゲート電圧が印加されることによってオン/オフ動作が行われ、PWM(Pulse Width Modulation:パルス幅変調)駆動される。

【0007】

ダイオードD10は、直流電源V1の負極からインダクタL10の方向の整流方向を有していればよく、例えば、ファーストリカバリーダイオード、SiCショットキーダイオードが用いられる。

【0008】

図2を用いて、前記降圧型コンバータ10の動作について説明する。図2は前記降圧型コンバータ10のタイミングチャートである。各グラフの横軸及び縦軸夫々は、時間、並びに電圧値又は電流値を示す。

【0009】

PWM信号発生回路20より、スイッチング素子SW10のゲートにオンオフを制御するPWM信号が印加される。PWM信号がオンとなると、電源からスイッチング素子SW10を通ってインダクタL10に電流I10が流れると共に、インダクタL10にエネルギーが蓄積され、電流I10は、時間に対して徐々に増加する。

【0010】

次いで、PWM信号をオフにすると、スイッチング素子SW10がオフされ、電流I10は直ちにゼロになる。インダクタL10に流れる電流I30は慣性力を持ち流れ続けようとするため、ダイオードD10を通して電流I20が流れ、徐々に減衰していく。このように、スイッチング素子SW10のオン、オフを繰り返すことにより、インダクタL1Oに流れる電流I30は、電流I10及び電流I20の和となり、直流成分と、単調増加及び単調減少を繰り返すリップル成分とを含んだ直流電流となる。

【0011】

電流I30は、コンデンサC10により、リップル成分が除去されて平滑化され、所定の直流電圧に降圧された直流電流として負荷回路RL0に出力される。負荷回路RL0に出力される直流電圧は、スイッチング素子SW10のゲートのオンオフを制御するPWM信号のデューティ比を変更することにより調整される。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開平11−220874号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

降圧型コンバータの出力効率をさらに向上させるためには、例えば、使用するスイッチング素子(スイッチング用トランジスタ)で消費される電力を減らす必要がある。このスイッチング用トランジスタで電力が消費される原因は、トランジスタのオン抵抗と呼ばれるトランジスタがオンした状態でのソース・ドレイン間の抵抗成分によるもの、並びに、いわゆるスイッチングロスといわれるトランジスタのオンオフの切り替え時の過渡状態で生じるものにあると考えられている。

【0014】

図3は、スイッチング用トランジスタのスイッチングロスについて、説明する図である。スイッチング用トランジスタは、ゲート−ソース間に加える電圧によって、ドレイン−ソース間の抵抗が変化する性質を利用して、オン/オフして用いられている。

【0015】

まず、トランジスタのオン抵抗に起因した問題は、トランジスタがオン状態の時に生じる。すなわち、トランジスタのオン抵抗は、トランジスタをオン状態にして、トランジスタに電流を流したとき、オームの法則によって、そのオン抵抗および電流によりトランジスタの電流の流れる端子間に電圧を発生させる。

【0016】

ここで、トランジスタで消費される電力は、トランジスタに流れる電流と、トランジスタに電流が流れる両端子間に生じる電圧の積となるため、この電力は、スイッチング電源の出力として取り出せるものでは無く、トランジスタで熱に変換されて電力損失となる。

【0017】

次に、スイッチングロスといわれるオン/オフの過渡状態で発生する損失は、オンオフの切り替え時に、スイッチング時間と呼ばれる電流・電圧ともにゼロでない時間が存在するために発生する。過渡状態での電流・電圧の変化を近似的に時間の一関数であるとすると、スイッチングロスは、電流×電圧×スイッチング時間/2であらわすことができるため、スイッチング損失を減らすためには、トランジスタのドライブ能力を高く、つまりスイッチング速度を速くする必要がある。

【0018】

そこで、上述したスイッチング素子での電力損失を低減するためには、オン抵抗が小さく、スイッチング速度が速いスイッチング素子を用いるのが望ましい。その両方の特性を満足する、シリコンではない化合物半導体材料である窒素ガリウム(GaN)を用いた高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)が開発されている。以下、このスイッチング用トランジスタをGaN−HEMTと称する。

【0019】

すなわち、化合物半導体の多くはシリコンに比べて電子の移動度が大きく相互コンダクタンスが大きいため、オン抵抗を小さくすることができ、また、トランジスタの各端子間に見える容量も小さいという特徴がある。

【0020】

しかしながら、従来のシリコンのMOSFETが、ゲートに電圧を印加しない状態でオフになるノーマリーオフ型(エンハンスメント型)であるのに対して、GaN−HEMTは、通常、ゲートに電圧を印加しない状態でオンになるノーマリーオン型(デプレッション型)である。そのためGaN−HEMTをスイッチングするためには、負電源回路による印加を行う。

【0021】

しかしながら、この負電源回路が故障し、負電圧を印加できなくなると、GaN−HEMTは、ON状態となってしまい、意図しない電力が出力されてしまうことがある。

【課題を解決するための手段】

【0022】

1つの案では、制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、前記ゲートを制御するPWM信号から前記第1のスイッチング素子の閾値以下の負電位の電圧を生成する負電圧発生回路と、前記PWM信号のレベルを前記負電位の電圧分シフトした信号を前記ゲートに出力するゲート制御回路と、前記第1のスイッチング素子のドレイン側に設けられた第2のスイッチング素子と、前記負電圧発生回路が生成する負電位の電圧が所定の負電位に達したことを検出して前記第2のスイッチング素子をオンする信号を出力する負電圧検出回路とを有する。

【発明の効果】

【0023】

一実施態様の制御回路によれば、ノーマリーオンのGaN−HEMTのゲート信号の負電位を発生する負電圧発生回路のレベルが一定に達しないと、GaN−HEMTのドレイン側に電力が供給されないので、負電源回路の故障が生じた場合に、意図しない電力が出力されてしまうことを抑制することができる。

【図面の簡単な説明】

【0024】

【図1】一般的な降圧型コンバータの回路図である。

【図2】降圧型コンバータの動作について説明する図である。

【図3】スイッチング素子の損失について説明する図である。

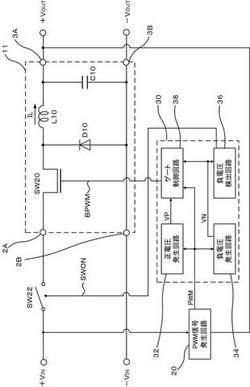

【図4】第1の実施形態のバイアスシフト回路を適用した降圧型コンバータの回路図である。

【図5】第1の実施形態の降圧型コンバータの動作について説明する図である。

【図6】第1の実施形態の降圧型コンバータのバイアスシフト回路の回路図である。

【図7】第2の実施形態のバイアスシフト回路を適用したPFC回路を有する電源装置の回路図である。

【発明を実施するための形態】

【0025】

以下に図面を参照して、本開示の技術にかかる好適な実施の形態を詳細に説明する。

【0026】

図4は、開示のバイアスシフト回路を電源回路の降圧型コンバータに適用した実施形態を示す回路図である。図4において、図1に示す降圧型コンバータと同一又は同等の構成要素には同一符号を付し、その説明を省略する。

【0027】

降圧型コンバータ11は、入力端子2A、2B、前記入力端子2A−2B間に与えられる電圧をオンオフする主スイッチとなるスイッチング素子SW20、整流用ダイオードD10、インダクタL10と平滑コンデンサC10とを含む。

【0028】

電源端子+VIN、−VINから入力端子2A、2Bに、直流電圧が入力される。出力端子3Aは、降圧型コンバータ11が降圧した直流電圧を出力する正極端子であり、出力端子3Bは、負極端子である。出力端子3A、3Bは、負荷回路に与える電圧を出力する+VOUT、−VOUTに接続される。降圧型コンバータ11は、例えば、電圧が385(V)の直流電圧を電圧が12(V)の直流電圧に変換して負荷回路に出力する。

【0029】

PWM信号発生回路20は、一般的な降圧型コンバータ10でも用いられるものと同等のもので、発生するPWM信号のデューティ比によって降圧型コンバータ11の出力電圧レベルを調整する。PWM信号発生回路20は、降圧される前の直流電圧で動作し、出力電圧をモニターして、PWM信号のデューティ比を調整する。

【0030】

スイッチング素子SW20には、GaN−HEMTを用いる。GaN(窒化ガリウム)で作成したHEMTは、シリコン製のMOSFETよりも高速動作が可能で、オン抵抗も小さいという特性を有する。しかしながら、GaN−HEMTは、通常、ゲートに電圧を印加しない状態でオンになるノーマリーオン型のため、スイッチングするためには、ソース−ゲート間に閾値以下の負電位を与えなければならない。この負電位を与える回路が、バイアスシフト回路30である。

【0031】

バイアスシフト回路30は、スイッチング素子のゲート信号をバイアスして負側にシフトすることで、ノーマリーオンのスイッチング素子SW20をオンオフ制御する。また、バイアスシフト回路30は、PWM信号をスイッチング素子SW20に出力するタイミングを調整する。また、バイアスシフト回路30は、スイッチング素子SW20のドレイン側に設けられたスイッチSW22のオンオフを制御する。

【0032】

スイッチング素子SW20のドレイン側に設けられたスイッチSW22は、バイアスシフト回路30に何らかの異常が発生し、スイッチング素子SW20がオンのままになってしまったとしても、降圧型コンバータ11に入力される電流をオフすることによって、降圧型コンバータ11を保護する働きを有する。

【0033】

スイッチSW22は、リレーなどのメカスイッチでも良いし、MOSFETなどの半導体スイッチでもよい。メカスイッチの動作速度は早くとも数ミリ秒で、電流を遮断するのに時間がかかるが、メカスイッチは、低抵抗で、コストも安く、数千ボルトの入力サージ電圧に耐えられるという利点がある。それに対して、半導体スイッチの動作速度は数マイクロ秒と、電流を即時に遮断することができるが、半導体スイッチは、サージ耐圧が低く、メカスイッチよりも高価である。メカスイッチ、半導体スイッチのどちらを用いるかは、一長一短がある。

【0034】

バイアスシフト回路30は、正電圧発生回路32、負電圧発生回路34、負電圧検出回路36、ゲート制御回路38を含む。

【0035】

次に、図5を用いて、バイアスシフト回路30の動作について説明する。図5は前記バイアスシフト回路30のタイミングチャートである。各グラフの横軸及び縦軸夫々は、時間、並びに電圧値又は電流値を示す。

【0036】

正電圧発生回路32は、PWM信号発生回路20が出力するPWM信号から正電圧VPを生成する。正電圧VPは、ノーマリーオンのスイッチング素子SW20のオンする閾値よりも高い電圧である必要がある。

【0037】

負電圧発生回路34は、PWM信号発生回路20が出力するPWM信号から負電圧VNを生成する。負電圧VNは、ノーマリーオンのスイッチング素子SW20のオフする閾値よりも低い電圧である必要がある。

【0038】

負電圧検出回路36は、負電圧発生回路34が生成する負電圧VNがt1の時点で一定のレベルに達したことを検知すると、スイッチSW22のオンオフを制御するSWON信号をオンする。スイッチング素子SW20のドレイン側は、電源端子+VINと接続状態になる。

【0039】

同時に、ゲート制御回路38は、スイッチング素子SW20をオンオフ制御するBPWM信号を出力する。このBPWM信号は、PWM信号のゼロレベルを負電圧発生回路34が生成する負電圧VNにシフトした信号となる。このBPWM信号によって、ノーマリーオンのスイッチング素子SW20のオンオフ制御が可能となり、降圧型コンバータ11は動作する。

【0040】

次に、スイッチング素子20のドレイン側に設けられたスイッチSW22の働きについて、説明する。図5において、例えば、t2の時点で、何らかの理由でバイアスシフト回路30にPWM信号が入力されなくなったとする。正電圧発生回路32は、PWM信号から正電圧VPを生成しているので、正電圧VPを生成できなくなる。同様に、負電圧発生回路34もPWM信号から負電圧VNを生成しているので、負電圧VNを生成できなくなる。ゲート制御回路38が生成するBPWM信号のマイナス側のレベルは、負電圧VNが上昇するため、スイッチング素子SW20の閾値以下まで下がりきらないので、スイッチング素子SW20がオンの状態のままとなってしまう。しかし、その後t3の時点で、負電圧検出回路36が負電圧VNの上昇を検知すると、スイッチSW22のオンオフを制御するSWON信号をオフとする。SWON信号がオフとなるので、スイッチング素子SW20には、電流が流れなくなり、降圧コンバータ11の動作は停止する。

【0041】

図6は、バイアスシフト回路30内の正電圧発生回路32、負電圧発生回路34、負電圧検出回路36、ゲート制御回路38の具体的な回路構成図である。図から解る様に

これらの回路は、電源を必要としない。PWM信号が発生するエレルギーから必要な電源を生成し、スイッチング素子SW20及びスイッチSW22の制御信号を生成している。一般的な負電圧を発生する回路は、正電圧の電源に専用のスイッチング電源回路を設け負電圧を生成しているため、かなり規模の大きい回路になってしまう。図6に示す負電圧発生回路34は、電源ラインの配線も不要で、小規模の回路で負電圧を生成することが可能である。

【0042】

本実施形態によれば、降圧型コンバータ11において、スイッチング素子SW20をMOSFETからGaN−HEMTに置き換えることにより、スイッチングロスを減らすことが可能となる。また、ノーマリーオンのGaN−HEMTのゲート電圧をシフトするバイアスシフト回路30も、大規模な負電源発生回路を必要としないため、簡単で、小規模の回路で構成できる。

【0043】

また、GaN−HEMTは、スイッチング速度が速いという特徴を有している。このため、PWM信号の周期を早くして、スイッチング素子SW20のスイッチング周波数fを速くして、降圧型コンバータ11の負荷電流が急激に変動しても出力電圧の変動を小さくすることができる。

【0044】

これは、図4に示すゲート制御回路38からスイッチング素子SW20のゲートに接続されるBPWM信号の配線インダクタLpを

Lp≦1/(4×π2×f2×C)・・・(1)

とすることで、寄生インダクタンスLpとGaN−HEMT素子のゲート寄生容量Cで決まる共振周波数をスイッチング周波数fより高くし、スイッチング波形を安定してGaN−HEMTに供給し、出力電圧を安定化することが可能となる。

【0045】

次に、図7を用いて、開示の制御回路を電源装置のPFC(Power Factor Correction:力率改善)回路に適用した実施形態について説明する。

【0046】

図7は、PFC回路を有する電源装置の回路図である。

【0047】

図7に示す電源装置は、整流回路40、PFC回路50、DC−DCコンバータ60を含む。

【0048】

整流回路40は、4つのダイオードがブリッジ状に接続されたダイオードブリッジである。整流回路40は、交流電源100に接続されており、交流電力を全波整流して出力する。整流回路40には、例えば、電圧が80(V)〜265(V)の交流電圧が入力される。

【0049】

PFC回路50は、T字型に接続された、インダクタL51、スイッチング素子Q52、ダイオードD53、及び平滑用キャパシタC54を含み、整流回路40で整流された電流に含まれる高調波等の歪みを低減し、電力の力率を改善するアクティブフィルタ回路である。

【0050】

インダクタL51は、例えば、昇圧用のインダクタが用いられる。

【0051】

ダイオードD53は、インダクタL51から平滑用キャパシタC54の方向の整流方向を有していればよく、例えば、ファーストリカバリーダイオード、SiCショットキーダイオードが用いられる。

【0052】

平滑用キャパシタC54は、PFC回路50が出力する電圧を平滑化してDC−DCコンバータ60に出力する。

【0053】

DC−DCコンバータ60は、例えば、フォワード型又はフルブリッジ型のDC−DCコンバータを用いればよい。DC−DCコンバータ60には、例えば、電圧が385(V)の直流電圧が入力される。DC−DCコンバータ60は、直流電力の電圧値を変換して出力する変換回路であり、出力側には負荷回路70が接続される。ここでは、DC−DCコンバータ60は、例えば、電圧が385(V)の直流電圧を電圧が12(V)の直流電圧に変換して負荷回路70に出力する。

【0054】

電源装置の整流回路40には、正弦波状の交流電圧が入力電圧Vinとして入力される。一般に電源装置の負荷回路は、単純な抵抗ではなく、さまざまな回路が含まれるため、入力電圧Vinが平滑用キャパシタC54の両端間電圧を上回ったときだけ入力電流Iinが流れるので、入力電流Iinが流れている時間が短くピークの値が高い高調波電流となる。

【0055】

PFC回路50は、PFC回路50内のスイッチング素子Q52を負荷回路70の入力端子間の電圧値に応じてオン/オフすることにより、正弦波状の交流電流として、力率を改善する働きを有する。

【0056】

このPFC回路50においても、スイッチング素子Q52にMOSFETを用いるとオン抵抗が高いため電力損失が発生してしまう。そこで、上述したスイッチング素子Q52にオン抵抗が小さく、スイッチング速度が速いGaN−HEMTを用いるのが望ましい。

【0057】

本実施形態においても、スイッチング素子Q52をGaN−HEMTに置き換えることにより、スイッチングロスを減らすことが可能となる。

【0058】

また、本発明はモータ制御回路のインバータなどのスイッチングにより電力を制御する装置に適用可能である。

【0059】

以上本発明の好ましい実施形態について詳述したが、本発明は係る特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【符号の説明】

【0060】

2A、2B 入力端子

3A、3B 出力端子

10、11 降圧型コンバータ

20 PWM信号発生回路

30 バイアスシフト回路

32 正電圧発生回路

34 負電圧発生回路

36 負電圧検出回路

38 ゲート制御回路

40 整流回路

50 PFC回路

60 DC−DCコンバータ

70 負荷回路

100 交流電源

【技術分野】

【0001】

本発明は、ノーマリーオンのスイッチング素子を含む制御回路及びそれを用いた電子機器に関する。

【背景技術】

【0002】

近年、様々な分野におけるエネルギー資源の節約が注目され、例えば、電源の分野においてもその影響が波及している。具体的には、例えば、スイッチング電源のさらなる高効率化が求められるようになってきている。

【0003】

スイッチング電源は、入力された直流電圧をDC(Direct Current)−DCコンバータを用いて所望の直流電圧に変換し、安定化電源電圧として出力するようにしてある。コンピュータに用いられるCPU( Central Processing Unit )等の半導体素子は、電源の低電圧化及び消費電力の増大に伴って、低電圧かつ大電流を出力可能なスイッチング電源が使用されてきている。

【0004】

図1は、DC−DCコンバータの一種の一般的な降圧型コンバータの回路図を示す。

【0005】

図1に示す降圧型コンバータ10は、入力電圧V1を降圧して所望の電位の出力電圧を生成し、負荷回路RL0に供給する。降圧型コンバータ10は、入力電圧V1をオンオフする主スイッチとなるスイッチング素子SW10と、整流用ダイオードD10と、インダクタL10と、平滑コンデンサC10とを備えている。

【0006】

スイッチング素子SW10には、例えば、MOSFET(Metal Oxide Semiconductor Field-Effect Transistor)が用いられる。スイッチング素子SW10は、PWM信号発生回路20からゲートにパルス状のゲート電圧が印加されることによってオン/オフ動作が行われ、PWM(Pulse Width Modulation:パルス幅変調)駆動される。

【0007】

ダイオードD10は、直流電源V1の負極からインダクタL10の方向の整流方向を有していればよく、例えば、ファーストリカバリーダイオード、SiCショットキーダイオードが用いられる。

【0008】

図2を用いて、前記降圧型コンバータ10の動作について説明する。図2は前記降圧型コンバータ10のタイミングチャートである。各グラフの横軸及び縦軸夫々は、時間、並びに電圧値又は電流値を示す。

【0009】

PWM信号発生回路20より、スイッチング素子SW10のゲートにオンオフを制御するPWM信号が印加される。PWM信号がオンとなると、電源からスイッチング素子SW10を通ってインダクタL10に電流I10が流れると共に、インダクタL10にエネルギーが蓄積され、電流I10は、時間に対して徐々に増加する。

【0010】

次いで、PWM信号をオフにすると、スイッチング素子SW10がオフされ、電流I10は直ちにゼロになる。インダクタL10に流れる電流I30は慣性力を持ち流れ続けようとするため、ダイオードD10を通して電流I20が流れ、徐々に減衰していく。このように、スイッチング素子SW10のオン、オフを繰り返すことにより、インダクタL1Oに流れる電流I30は、電流I10及び電流I20の和となり、直流成分と、単調増加及び単調減少を繰り返すリップル成分とを含んだ直流電流となる。

【0011】

電流I30は、コンデンサC10により、リップル成分が除去されて平滑化され、所定の直流電圧に降圧された直流電流として負荷回路RL0に出力される。負荷回路RL0に出力される直流電圧は、スイッチング素子SW10のゲートのオンオフを制御するPWM信号のデューティ比を変更することにより調整される。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開平11−220874号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

降圧型コンバータの出力効率をさらに向上させるためには、例えば、使用するスイッチング素子(スイッチング用トランジスタ)で消費される電力を減らす必要がある。このスイッチング用トランジスタで電力が消費される原因は、トランジスタのオン抵抗と呼ばれるトランジスタがオンした状態でのソース・ドレイン間の抵抗成分によるもの、並びに、いわゆるスイッチングロスといわれるトランジスタのオンオフの切り替え時の過渡状態で生じるものにあると考えられている。

【0014】

図3は、スイッチング用トランジスタのスイッチングロスについて、説明する図である。スイッチング用トランジスタは、ゲート−ソース間に加える電圧によって、ドレイン−ソース間の抵抗が変化する性質を利用して、オン/オフして用いられている。

【0015】

まず、トランジスタのオン抵抗に起因した問題は、トランジスタがオン状態の時に生じる。すなわち、トランジスタのオン抵抗は、トランジスタをオン状態にして、トランジスタに電流を流したとき、オームの法則によって、そのオン抵抗および電流によりトランジスタの電流の流れる端子間に電圧を発生させる。

【0016】

ここで、トランジスタで消費される電力は、トランジスタに流れる電流と、トランジスタに電流が流れる両端子間に生じる電圧の積となるため、この電力は、スイッチング電源の出力として取り出せるものでは無く、トランジスタで熱に変換されて電力損失となる。

【0017】

次に、スイッチングロスといわれるオン/オフの過渡状態で発生する損失は、オンオフの切り替え時に、スイッチング時間と呼ばれる電流・電圧ともにゼロでない時間が存在するために発生する。過渡状態での電流・電圧の変化を近似的に時間の一関数であるとすると、スイッチングロスは、電流×電圧×スイッチング時間/2であらわすことができるため、スイッチング損失を減らすためには、トランジスタのドライブ能力を高く、つまりスイッチング速度を速くする必要がある。

【0018】

そこで、上述したスイッチング素子での電力損失を低減するためには、オン抵抗が小さく、スイッチング速度が速いスイッチング素子を用いるのが望ましい。その両方の特性を満足する、シリコンではない化合物半導体材料である窒素ガリウム(GaN)を用いた高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)が開発されている。以下、このスイッチング用トランジスタをGaN−HEMTと称する。

【0019】

すなわち、化合物半導体の多くはシリコンに比べて電子の移動度が大きく相互コンダクタンスが大きいため、オン抵抗を小さくすることができ、また、トランジスタの各端子間に見える容量も小さいという特徴がある。

【0020】

しかしながら、従来のシリコンのMOSFETが、ゲートに電圧を印加しない状態でオフになるノーマリーオフ型(エンハンスメント型)であるのに対して、GaN−HEMTは、通常、ゲートに電圧を印加しない状態でオンになるノーマリーオン型(デプレッション型)である。そのためGaN−HEMTをスイッチングするためには、負電源回路による印加を行う。

【0021】

しかしながら、この負電源回路が故障し、負電圧を印加できなくなると、GaN−HEMTは、ON状態となってしまい、意図しない電力が出力されてしまうことがある。

【課題を解決するための手段】

【0022】

1つの案では、制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、前記ゲートを制御するPWM信号から前記第1のスイッチング素子の閾値以下の負電位の電圧を生成する負電圧発生回路と、前記PWM信号のレベルを前記負電位の電圧分シフトした信号を前記ゲートに出力するゲート制御回路と、前記第1のスイッチング素子のドレイン側に設けられた第2のスイッチング素子と、前記負電圧発生回路が生成する負電位の電圧が所定の負電位に達したことを検出して前記第2のスイッチング素子をオンする信号を出力する負電圧検出回路とを有する。

【発明の効果】

【0023】

一実施態様の制御回路によれば、ノーマリーオンのGaN−HEMTのゲート信号の負電位を発生する負電圧発生回路のレベルが一定に達しないと、GaN−HEMTのドレイン側に電力が供給されないので、負電源回路の故障が生じた場合に、意図しない電力が出力されてしまうことを抑制することができる。

【図面の簡単な説明】

【0024】

【図1】一般的な降圧型コンバータの回路図である。

【図2】降圧型コンバータの動作について説明する図である。

【図3】スイッチング素子の損失について説明する図である。

【図4】第1の実施形態のバイアスシフト回路を適用した降圧型コンバータの回路図である。

【図5】第1の実施形態の降圧型コンバータの動作について説明する図である。

【図6】第1の実施形態の降圧型コンバータのバイアスシフト回路の回路図である。

【図7】第2の実施形態のバイアスシフト回路を適用したPFC回路を有する電源装置の回路図である。

【発明を実施するための形態】

【0025】

以下に図面を参照して、本開示の技術にかかる好適な実施の形態を詳細に説明する。

【0026】

図4は、開示のバイアスシフト回路を電源回路の降圧型コンバータに適用した実施形態を示す回路図である。図4において、図1に示す降圧型コンバータと同一又は同等の構成要素には同一符号を付し、その説明を省略する。

【0027】

降圧型コンバータ11は、入力端子2A、2B、前記入力端子2A−2B間に与えられる電圧をオンオフする主スイッチとなるスイッチング素子SW20、整流用ダイオードD10、インダクタL10と平滑コンデンサC10とを含む。

【0028】

電源端子+VIN、−VINから入力端子2A、2Bに、直流電圧が入力される。出力端子3Aは、降圧型コンバータ11が降圧した直流電圧を出力する正極端子であり、出力端子3Bは、負極端子である。出力端子3A、3Bは、負荷回路に与える電圧を出力する+VOUT、−VOUTに接続される。降圧型コンバータ11は、例えば、電圧が385(V)の直流電圧を電圧が12(V)の直流電圧に変換して負荷回路に出力する。

【0029】

PWM信号発生回路20は、一般的な降圧型コンバータ10でも用いられるものと同等のもので、発生するPWM信号のデューティ比によって降圧型コンバータ11の出力電圧レベルを調整する。PWM信号発生回路20は、降圧される前の直流電圧で動作し、出力電圧をモニターして、PWM信号のデューティ比を調整する。

【0030】

スイッチング素子SW20には、GaN−HEMTを用いる。GaN(窒化ガリウム)で作成したHEMTは、シリコン製のMOSFETよりも高速動作が可能で、オン抵抗も小さいという特性を有する。しかしながら、GaN−HEMTは、通常、ゲートに電圧を印加しない状態でオンになるノーマリーオン型のため、スイッチングするためには、ソース−ゲート間に閾値以下の負電位を与えなければならない。この負電位を与える回路が、バイアスシフト回路30である。

【0031】

バイアスシフト回路30は、スイッチング素子のゲート信号をバイアスして負側にシフトすることで、ノーマリーオンのスイッチング素子SW20をオンオフ制御する。また、バイアスシフト回路30は、PWM信号をスイッチング素子SW20に出力するタイミングを調整する。また、バイアスシフト回路30は、スイッチング素子SW20のドレイン側に設けられたスイッチSW22のオンオフを制御する。

【0032】

スイッチング素子SW20のドレイン側に設けられたスイッチSW22は、バイアスシフト回路30に何らかの異常が発生し、スイッチング素子SW20がオンのままになってしまったとしても、降圧型コンバータ11に入力される電流をオフすることによって、降圧型コンバータ11を保護する働きを有する。

【0033】

スイッチSW22は、リレーなどのメカスイッチでも良いし、MOSFETなどの半導体スイッチでもよい。メカスイッチの動作速度は早くとも数ミリ秒で、電流を遮断するのに時間がかかるが、メカスイッチは、低抵抗で、コストも安く、数千ボルトの入力サージ電圧に耐えられるという利点がある。それに対して、半導体スイッチの動作速度は数マイクロ秒と、電流を即時に遮断することができるが、半導体スイッチは、サージ耐圧が低く、メカスイッチよりも高価である。メカスイッチ、半導体スイッチのどちらを用いるかは、一長一短がある。

【0034】

バイアスシフト回路30は、正電圧発生回路32、負電圧発生回路34、負電圧検出回路36、ゲート制御回路38を含む。

【0035】

次に、図5を用いて、バイアスシフト回路30の動作について説明する。図5は前記バイアスシフト回路30のタイミングチャートである。各グラフの横軸及び縦軸夫々は、時間、並びに電圧値又は電流値を示す。

【0036】

正電圧発生回路32は、PWM信号発生回路20が出力するPWM信号から正電圧VPを生成する。正電圧VPは、ノーマリーオンのスイッチング素子SW20のオンする閾値よりも高い電圧である必要がある。

【0037】

負電圧発生回路34は、PWM信号発生回路20が出力するPWM信号から負電圧VNを生成する。負電圧VNは、ノーマリーオンのスイッチング素子SW20のオフする閾値よりも低い電圧である必要がある。

【0038】

負電圧検出回路36は、負電圧発生回路34が生成する負電圧VNがt1の時点で一定のレベルに達したことを検知すると、スイッチSW22のオンオフを制御するSWON信号をオンする。スイッチング素子SW20のドレイン側は、電源端子+VINと接続状態になる。

【0039】

同時に、ゲート制御回路38は、スイッチング素子SW20をオンオフ制御するBPWM信号を出力する。このBPWM信号は、PWM信号のゼロレベルを負電圧発生回路34が生成する負電圧VNにシフトした信号となる。このBPWM信号によって、ノーマリーオンのスイッチング素子SW20のオンオフ制御が可能となり、降圧型コンバータ11は動作する。

【0040】

次に、スイッチング素子20のドレイン側に設けられたスイッチSW22の働きについて、説明する。図5において、例えば、t2の時点で、何らかの理由でバイアスシフト回路30にPWM信号が入力されなくなったとする。正電圧発生回路32は、PWM信号から正電圧VPを生成しているので、正電圧VPを生成できなくなる。同様に、負電圧発生回路34もPWM信号から負電圧VNを生成しているので、負電圧VNを生成できなくなる。ゲート制御回路38が生成するBPWM信号のマイナス側のレベルは、負電圧VNが上昇するため、スイッチング素子SW20の閾値以下まで下がりきらないので、スイッチング素子SW20がオンの状態のままとなってしまう。しかし、その後t3の時点で、負電圧検出回路36が負電圧VNの上昇を検知すると、スイッチSW22のオンオフを制御するSWON信号をオフとする。SWON信号がオフとなるので、スイッチング素子SW20には、電流が流れなくなり、降圧コンバータ11の動作は停止する。

【0041】

図6は、バイアスシフト回路30内の正電圧発生回路32、負電圧発生回路34、負電圧検出回路36、ゲート制御回路38の具体的な回路構成図である。図から解る様に

これらの回路は、電源を必要としない。PWM信号が発生するエレルギーから必要な電源を生成し、スイッチング素子SW20及びスイッチSW22の制御信号を生成している。一般的な負電圧を発生する回路は、正電圧の電源に専用のスイッチング電源回路を設け負電圧を生成しているため、かなり規模の大きい回路になってしまう。図6に示す負電圧発生回路34は、電源ラインの配線も不要で、小規模の回路で負電圧を生成することが可能である。

【0042】

本実施形態によれば、降圧型コンバータ11において、スイッチング素子SW20をMOSFETからGaN−HEMTに置き換えることにより、スイッチングロスを減らすことが可能となる。また、ノーマリーオンのGaN−HEMTのゲート電圧をシフトするバイアスシフト回路30も、大規模な負電源発生回路を必要としないため、簡単で、小規模の回路で構成できる。

【0043】

また、GaN−HEMTは、スイッチング速度が速いという特徴を有している。このため、PWM信号の周期を早くして、スイッチング素子SW20のスイッチング周波数fを速くして、降圧型コンバータ11の負荷電流が急激に変動しても出力電圧の変動を小さくすることができる。

【0044】

これは、図4に示すゲート制御回路38からスイッチング素子SW20のゲートに接続されるBPWM信号の配線インダクタLpを

Lp≦1/(4×π2×f2×C)・・・(1)

とすることで、寄生インダクタンスLpとGaN−HEMT素子のゲート寄生容量Cで決まる共振周波数をスイッチング周波数fより高くし、スイッチング波形を安定してGaN−HEMTに供給し、出力電圧を安定化することが可能となる。

【0045】

次に、図7を用いて、開示の制御回路を電源装置のPFC(Power Factor Correction:力率改善)回路に適用した実施形態について説明する。

【0046】

図7は、PFC回路を有する電源装置の回路図である。

【0047】

図7に示す電源装置は、整流回路40、PFC回路50、DC−DCコンバータ60を含む。

【0048】

整流回路40は、4つのダイオードがブリッジ状に接続されたダイオードブリッジである。整流回路40は、交流電源100に接続されており、交流電力を全波整流して出力する。整流回路40には、例えば、電圧が80(V)〜265(V)の交流電圧が入力される。

【0049】

PFC回路50は、T字型に接続された、インダクタL51、スイッチング素子Q52、ダイオードD53、及び平滑用キャパシタC54を含み、整流回路40で整流された電流に含まれる高調波等の歪みを低減し、電力の力率を改善するアクティブフィルタ回路である。

【0050】

インダクタL51は、例えば、昇圧用のインダクタが用いられる。

【0051】

ダイオードD53は、インダクタL51から平滑用キャパシタC54の方向の整流方向を有していればよく、例えば、ファーストリカバリーダイオード、SiCショットキーダイオードが用いられる。

【0052】

平滑用キャパシタC54は、PFC回路50が出力する電圧を平滑化してDC−DCコンバータ60に出力する。

【0053】

DC−DCコンバータ60は、例えば、フォワード型又はフルブリッジ型のDC−DCコンバータを用いればよい。DC−DCコンバータ60には、例えば、電圧が385(V)の直流電圧が入力される。DC−DCコンバータ60は、直流電力の電圧値を変換して出力する変換回路であり、出力側には負荷回路70が接続される。ここでは、DC−DCコンバータ60は、例えば、電圧が385(V)の直流電圧を電圧が12(V)の直流電圧に変換して負荷回路70に出力する。

【0054】

電源装置の整流回路40には、正弦波状の交流電圧が入力電圧Vinとして入力される。一般に電源装置の負荷回路は、単純な抵抗ではなく、さまざまな回路が含まれるため、入力電圧Vinが平滑用キャパシタC54の両端間電圧を上回ったときだけ入力電流Iinが流れるので、入力電流Iinが流れている時間が短くピークの値が高い高調波電流となる。

【0055】

PFC回路50は、PFC回路50内のスイッチング素子Q52を負荷回路70の入力端子間の電圧値に応じてオン/オフすることにより、正弦波状の交流電流として、力率を改善する働きを有する。

【0056】

このPFC回路50においても、スイッチング素子Q52にMOSFETを用いるとオン抵抗が高いため電力損失が発生してしまう。そこで、上述したスイッチング素子Q52にオン抵抗が小さく、スイッチング速度が速いGaN−HEMTを用いるのが望ましい。

【0057】

本実施形態においても、スイッチング素子Q52をGaN−HEMTに置き換えることにより、スイッチングロスを減らすことが可能となる。

【0058】

また、本発明はモータ制御回路のインバータなどのスイッチングにより電力を制御する装置に適用可能である。

【0059】

以上本発明の好ましい実施形態について詳述したが、本発明は係る特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【符号の説明】

【0060】

2A、2B 入力端子

3A、3B 出力端子

10、11 降圧型コンバータ

20 PWM信号発生回路

30 バイアスシフト回路

32 正電圧発生回路

34 負電圧発生回路

36 負電圧検出回路

38 ゲート制御回路

40 整流回路

50 PFC回路

60 DC−DCコンバータ

70 負荷回路

100 交流電源

【特許請求の範囲】

【請求項1】

ソース、ゲート及びドレインを有する第1のスイッチング素子と、

前記ゲートを制御するPWM信号から前記第1のスイッチング素子の閾値以下の負電位の電圧を生成する負電圧発生回路と、

前記PWM信号のレベルを前記負電位の電圧分シフトした信号を前記ゲートに出力するゲート制御回路と、

前記第1のスイッチング素子のドレイン側に設けられた第2のスイッチング素子と、

前記負電圧発生回路が生成する負電位の電圧が所定の負電位に達したことを検出して前記第2のスイッチング素子をオンする信号を出力する負電圧検出回路と

を有する制御回路。

【請求項2】

前記第2のスイッチング素子は、メカスイッチである

ことを特徴とする請求項1に記載の制御回路。

【請求項3】

前記第2のスイッチング素子は、半導体スイッチである

ことを特徴とする請求項1に記載の制御回路。

【請求項4】

前記負電圧検出回路は、前記負電圧発生回路が生成する負電位の電圧が所定の負電位以上になったことを検出し、前記第2のスイッチング素子をオフする信号を出力する

ことを特徴とする請求項1に記載の制御回路。

【請求項5】

ソース、ゲート及びドレインを有する第1のスイッチング素子を含むコンバータ回路と、

前記ゲートを制御するPWM信号から前記第1のスイッチング素子の閾値以下の負電位の電圧を生成する負電圧発生回路と、

前記PWM信号のレベルを前記負電位の電圧分シフトした信号を前記ゲートに出力するゲート制御回路と

前記第1のスイッチング素子のドレイン側に設けられた第2のスイッチング素子と、

前記負電圧発生回路が生成する負電位の電圧が所定の負電位に達したことを検出して、前記第2のスイッチング素子をオンする信号を出力する負電圧検出回路と

を有する電子機器。

【請求項1】

ソース、ゲート及びドレインを有する第1のスイッチング素子と、

前記ゲートを制御するPWM信号から前記第1のスイッチング素子の閾値以下の負電位の電圧を生成する負電圧発生回路と、

前記PWM信号のレベルを前記負電位の電圧分シフトした信号を前記ゲートに出力するゲート制御回路と、

前記第1のスイッチング素子のドレイン側に設けられた第2のスイッチング素子と、

前記負電圧発生回路が生成する負電位の電圧が所定の負電位に達したことを検出して前記第2のスイッチング素子をオンする信号を出力する負電圧検出回路と

を有する制御回路。

【請求項2】

前記第2のスイッチング素子は、メカスイッチである

ことを特徴とする請求項1に記載の制御回路。

【請求項3】

前記第2のスイッチング素子は、半導体スイッチである

ことを特徴とする請求項1に記載の制御回路。

【請求項4】

前記負電圧検出回路は、前記負電圧発生回路が生成する負電位の電圧が所定の負電位以上になったことを検出し、前記第2のスイッチング素子をオフする信号を出力する

ことを特徴とする請求項1に記載の制御回路。

【請求項5】

ソース、ゲート及びドレインを有する第1のスイッチング素子を含むコンバータ回路と、

前記ゲートを制御するPWM信号から前記第1のスイッチング素子の閾値以下の負電位の電圧を生成する負電圧発生回路と、

前記PWM信号のレベルを前記負電位の電圧分シフトした信号を前記ゲートに出力するゲート制御回路と

前記第1のスイッチング素子のドレイン側に設けられた第2のスイッチング素子と、

前記負電圧発生回路が生成する負電位の電圧が所定の負電位に達したことを検出して、前記第2のスイッチング素子をオンする信号を出力する負電圧検出回路と

を有する電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−93970(P2013−93970A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−234422(P2011−234422)

【出願日】平成23年10月25日(2011.10.25)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月25日(2011.10.25)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]