制御回路及び電子機器

【課題】ノーマリーオフ化したGaN−HEMTを電源回路に用いた場合、長期間電源をオフしている間にノーマリーオンに戻るのを防止する制御回路を提供する。

【解決手段】制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路とを有する。

【解決手段】制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ノーマリーオンのスイッチング素子を含む制御回路及びその制御回路を用いた電子機器に関する。

【背景技術】

【0002】

近年、様々な分野におけるエネルギー資源の節約が注目され、例えば、電源の分野においてもその影響が波及している。具体的には、例えば、スイッチング電源のさらなる高効率化が求められるようになってきている。

【0003】

スイッチング電源は、入力された直流電圧をDC(Direct Current)−DCコンバータを用いて所望の直流電圧に変換し、安定化電源電圧として出力する。コンピュータに用いられるCPU( Central Processing Unit )等の半導体素子の低電圧化及び消費電力の増大に伴って、電源装置も低電圧かつ大電流を出力可能なスイッチング電源が使用されてきている。

【0004】

電源装置の出力効率をさらに向上させるためには、例えば、使用するスイッチング素子(スイッチング用トランジスタ)で消費される電力を減らす必要がある。そこで、電力損失を低減するためには、オン抵抗が小さく、スイッチング速度が速いスイッチング素子を用いるのが望ましい。その両方の特性を満足する、シリコンではない化合物半導体材料を用いたスイッチング電源用トランジスタが開発されている。

【0005】

化合物半導体の一例として、窒素ガリウム(GaN)を用いた高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)について説明する。以下、このトランジスタをGaN−HEMTと称する。

【0006】

GaN−HEMTは、ドレイン、ソース、ゲートを有する三端子トランジスタである。例えば、ソースを接地し、ソース−ドレイン間に所定の正電圧を印加し、ソース−ゲート間に印加する電圧を閾値以上にすると、ソース−ドレイン間が導通する(オンになる)。ソース−ゲート間に印加する電圧の閾値は、例えば、−10(V)〜+10(V)である。GaN−HEMTは、動作を含めてMOSFETと同様に取り扱うことができる。

【0007】

従来のシリコンのMOSFETが、ゲートに電圧を印加しない状態でオフになるノーマリーオフ型(エンハンスメント型)であるのに対して、GaN−HEMTは、通常、ゲートに電圧を印加しない状態でオンになるノーマリーオン型(デプレッション型)である。そのためGaN−HEMTをスイッチングするためには、負電位の閾値以下にゲート電圧を下げるための負電源が必要になる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭53−048426号公報

【特許文献2】特開2007−159364号公報

【特許文献3】特開2008−182884号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

ノーマリーオン型のGaN−HEMTを高電圧でスイッチング動作させると、ゲート直下のゲート絶縁膜の界面に電荷がチャージされて、閾値が上がり、疑似的にノーマリーオフになることが判っている。

【0010】

図1(A)は、GaN−HEMTの断面を示す。GaN−HEMTは、サファイア、SiC、GaN、Si等の基板90上に、GaN層91、AlGaN層92を結晶成長し、その上にn−GaN層94を挟んで、ソース81、ドレイン82が形成されている。ゲート80は、ゲート絶縁膜95を挟んでn−GaN層94上に形成されている。GaN−HEMTにおいては、GaN層91とAlGaN層92間の二次元電子ガス層93を電子走行層としている。GaN−HEMTを高電圧でスイッチング動作させると、図に示す様に、ゲート80直下のゲート絶縁膜95の界面に電荷が溜まることによって、閾値が正電圧に上昇する。

【0011】

図1(B)は、ゲート直下に電荷がチャージされたGaN−HEMTの閾値の変化を表わす。GaN−HEMTをスイッチング動作させて、ゲート80直下のゲート絶縁膜95の界面にある程度の電荷がチャージされた状態では、ゲート電圧を零電位にしても、閾値は正電圧レベルのままとなる。ゲートを零電圧にして長時間(数ケ月〜年)放置しておくと、ゲート下の電荷が徐々に放電されてしまうため、ノーマリーオンに戻る。

【0012】

ノーマリーオフ化したGaN−HEMTを装置の電源のスイッチング素子に用いた場合、長期間装置を電源オフの状態にしておくと、ノーマリーオンに戻ってしまう。この状態では、GaN−HEMTのゲートに、負電位を加えないとスイッチングができなくなってしまう。また、電源を立ち上げた時に、GaN−HEMTに高電圧が急に加わって、リーク電流で破壊する恐れがある。

【課題を解決するための手段】

【0013】

1つの案では、制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路とを有する。

【発明の効果】

【0014】

一実施態様の制御回路によれば、電源をオフしている間もノーマリーオフ化したGaN−HEMTのゲートはバッテリーで閾値以上に保持されているため、ノーマリーオンに戻るのを防止することができる。

【図面の簡単な説明】

【0015】

【図1】GaN−HEMTについて説明する図である。

【図2】GaN−HEMTをノーマリーオフ化する手法について説明する図である。

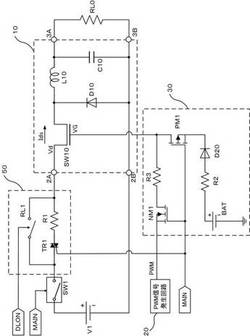

【図3】第1の実施形態の降圧型コンバータの回路図である。

【図4】第1の実施形態のゲート制御回路30の動作について説明する図である。

【図5】電源を立ち上げる制御方法について説明する図である。

【図6】リカバリー処理を含んだ電源を立ち上げる制御方法について説明する図である。

【発明を実施するための形態】

【0016】

まず、初めにノーマリーオン型のGaN−HEMTをノーマリーオフ化する手法について説明する。

【0017】

図2(A)は、ノーマリーオン型のGaN−HEMTをノーマリーオフ化する回路兼閾値測定回路を示す。GaN−HEMTに負荷電源4V、負荷抵抗20Ωを接続し、GaN−HEMTのゲートに、−5〜+10V、1KHzのデューティ比50%の三角波を加えて、GaN−HEMTをノーマリーオフ化する。

【0018】

図2(B)は、GaN−HEMTの閾値の変化を示す。図2(B)のA線は、電荷がチャージされる前、つまり初期状態のGaN−HEMTの閾値を示している。閾値は−1V程度でノーマリーオンの特性を示している。

【0019】

図2(B)のB線は、GaN−HEMTのゲートに、−5〜+10V、1KHzのデューティ比50%の三角波を加え続けた1時間後のGaN−HEMTの閾値を示している。閾値が正電位側にシフトしており、ノーマリーオフ化されている。

【0020】

ノーマリーオフ化したGaN−HEMT素子を、サーバー用の電源回路のPFC回路部に接続し、スイッチング素子として動作させる。周波数100kHz、ゲート電圧0〜10V、デューティ比0〜100%まで変動させて、ソース・ドレイン間電圧400Vの条件で連続スイッチングを行ない、1時間サーバー用の電源回路内で動作させた後の閾値特性は、ほぼB線と等しくなる。高電圧の電源負荷をかけても閾値は変動していない。これはノーマリーオフ化した時点で電荷のチャージが十分に飽和しており、より大きな負荷をかけても閾値が変化しないことがわかる。

【0021】

次いで、ノーマリーオフ化したGaN−HEMTのゲートソース間に+3Vを印加した状態で1ヶ月放置した後の閾値特性をC線に示す。C線もほぼB線と等しくなる。ゲート電圧を閾値以上に保っておけば閾値の低下は起きない。

【0022】

以下に図面を参照して、本開示の技術にかかる好適な実施の形態を詳細に説明する。

【0023】

図3は、ノーマリーオフ化したGaN−HEMTを電源回路の降圧型コンバータに適用した実施形態を示す回路図である。

【0024】

図3に示す降圧型コンバータ10は、例えば、電圧が385(V)の直流電圧V1を電圧が12(V)の直流電圧に変換して負荷回路RL0に出力する。

【0025】

降圧型コンバータ10は、入力電圧V1をオンオフする主スイッチとなるスイッチング素子SW10と、整流用ダイオードD10と、インダクタL10と、平滑コンデンサC10とを備えている。

【0026】

PWM信号発生回路20は、発生するPWM信号のデューティ比によって降圧型コンバータ10の出力電圧レベルを調整する。PWM信号発生回路20は、降圧される前の直流電圧で動作し、出力電圧をモニターして、PWM信号のデューティ比を調整する。

【0027】

スイッチング素子SW10は、PWM信号発生回路20からゲートにパルス状のゲート電圧が印加されることによってオン/オフ動作が行われ、PWM(Pulse Width Modulation:パルス幅変調)駆動される。スイッチング素子SW10には、前記の手法にてノーマリーオフ化したGaN−HEMTを用いる。

【0028】

ダイオードD10は、直流電源V1の負極からインダクタL10の方向の整流方向を有していればよく、例えば、ファーストリカバリーダイオード、SiCショットキーダイオードが用いられる。

【0029】

ゲート制御回路30は、電源のオンオフを制御する電源制御信号MAINがオフの時に、スイッチング素子SW10のゲートにバッテリーBATの電圧を供給し、電源制御信号MAINがオンの時に、スイッチング素子SW10のゲートにPWM信号を供給する働きを有する。

【0030】

降圧型コンバータ10と直流電圧V1との間には、突入電流防止回路50が設けられている。突入電流防止回路50は、トライアックTR1と制限抵抗R1を直列にした経路と、リレーRL1の経路を有する。トライアックTR1は、双方向サイリスタであって、ゲートからカソードにゲート電流を流すことにより、アノードとカソード間を導通させることができ、アノードとカソードの間の電流が一定値以下に下がると導通状態は停止する(セルフターンオフ)という特性を有する3端子の半導体整流素子である。電源制御信号MAINがオンとなった時点では、トライアックTR1が導通し、スイッチング素子SW10のドレインには、制限抵抗R1を介して直流電圧V1からの電流が流れる。この電流は、制限抵抗R1で制限されているので、スイッチング素子SW10のドレイン及び平滑コンデンサC10に大電流が急に流れこむのを防いでいる。次に電源制御信号MAINより遅延した遅延信号DLONによって、トライアックTR1と制限抵抗R1と並列に設けられたリレーRL1をオンすると、スイッチング素子SW10のドレインには、リレーRL1の経路で電流が流れる。トライアックTR1と制限抵抗R1を直列にした経路に流れる電流は少なくなるので、トライアックTR1はセルフターンオフとなり、トライアックTR1と制限抵抗R1での電力損失は無くなる。

【0031】

次に、図4を参照して、ゲート制御回路30の動作について説明する。図4は、スイッチング素子SW10の動作を表わすタイムチャートである。

【0032】

図4において、0.0msからT1時間までの間は、電源がオフの状態を示していて、電源制御信号MAINはオフとなっている。

【0033】

図3を参照して、この間は、PWM信号発生回路20にドレイン側が接続されたスイッチング素子NM1はオフとなり、バッテリーBATの電圧がPWM信号発生回路20側に逆流して回路破壊や誤動作を起こすのを防いでいる。スイッチング素子NM1は、例えばNMOS−FETとする。

【0034】

同時に、スイッチング素子SW10のゲートにドレイン側が接続されたスイッチング素子PM1がオンとなり、ダイオードD20、抵抗R2を介してバッテリーBATの電圧が、スイッチング素子SW10のゲートに供給される。スイッチング素子PM1は、例えばPMOS−FETとし、バッテリーBATは、ノーマリーオフ化してあるスイッチング素子SW10の閾値電圧より高い、例えば3Vのバッテリーとする必要がある。この時、バッテリーBATから流れる電流はスイッチング素子SW10のゲートリーク電流程度であり、長時間放置してもバッテリーの消耗は最低限に抑えられている。

【0035】

図4を参照して、スイッチング素子SW10のゲート電圧VGは、約3Vに保持されていることを示している。この様に電源がオフの間は、ノーマリーオフ化されたスイッチング素子SW10のゲートに、閾値以上の電圧が供給されるので、ノーマリーオフ化は維持される。

【0036】

次に、T1の時点で、電源がオンとなり電源制御信号MAINがオンになると、スイッチング素子PM1がオフとなり、スイッチング素子SW10のゲートには、バッテリーBATの電圧が供給されなくなり、スイッチング素子SW10のゲート電圧VGは一旦ゼロとなる。スイッチング素子SW10は、ノーマリーオフ化してあるので、スイッチング素子SW10はオフのままで、ドレイン−ソース間電流Idsは流れない。同時にスイッチング素子NM1はオンとなり、PWM信号発生回路20とスイッチング素子SW10のゲートが電気的に接続され、スイッチング素子SW10のスイッチングが可能な状態になる。

【0037】

次に、T2の時点で、PWM信号発生回路20からPWM信号が出力され始め、スイッチング素子SW10のスイッチングが行なわれる。負荷回路RL0に出力される直流電圧は、スイッチング素子SW10のゲートのオンオフを制御するPWM信号のデューティ比を変更することにより調整される。

【0038】

以降、スイッチング動作が継続すれば、スイッチング素子SW10のノーマリーオフの特性は維持され続ける。サーバー等常に電源がオンの状態で使用される装置の電源においては、半永久的にノーマリーオフのままGaN−HEMTを使用することが可能となる。

【0039】

また、装置を工場から顧客へ搬送するまでの期間、装置を保守する期間など、装置の電源をオフする期間があったとしても、バッテリーBATによって、スイッチング素子SW10のゲートは閾値以上に保たれているので、GaN−HEMTのノーマリーオフの特性は維持される。

【0040】

本実施形態によれば、ノーマリーオフ化したGaN−HEMTを、ノーマリーオフの状態で使い続けることが可能となるので、ノーマリーオンのGaN−HEMTを制御するための負電源発生回路が不要となる。

【0041】

次に、図5を用いて電源を立ち上げる制御方法について説明する。

【0042】

装置の電源がオフされていた期間が例えば数ヶ月以上と長いと、バッテリーが消耗して、ノーマリーオフ化したGaN−HEMTがノーマリーオンに戻ってしまう恐れがある。前にも述べたが、ノーマリーオン状態のGaN−HEMTに高電圧を加えるとリーク電流で破壊する恐れがある。これを防ぐために、装置の電源を立ち上げる前に、コンパレータ等でバッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値より高いことを確認してから通常の動作を始める方法がある。この方法では、図3に示す降圧型コンバータ10の周辺に、バッテリー電圧検出回路を設ける必要がある。

【0043】

まず、降圧型コンバータ10の電源をオンする前に、バッテリー電圧検出回路に電源を供給するためのサブ電源をオンする。

【0044】

次いで、バッテリー電圧検出回路によって、バッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値電圧以上であるかを比較する。

【0045】

その際に、バッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値電圧より低かった場合は、GaN−HEMTがノーマリーオンに戻っていると判断して、何らかの表示装置にエラー表示をして、処理を終了する。

【0046】

バッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値電圧より高い場合は、GaN−HEMTがノーマリーオフの状態を維持していると判断して、通常の電源オンの処理を始める。この処理では、バッテリーの電圧がノーマリーオフ化を維持できる電圧より低かった場合は、GaN−HEMTがノーマリーオンに戻っていると判断して、処理を終了させているが、バッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値電圧より低くなっていたとしても、必ずしも、GaN−HEMTがノーマリーオンに戻っているとは限らない。その場合は、閾値を上げるためのリカバリー処理を行なうことによって、GaN−HEMTを通常の動作させることができる場合がある。

【0047】

次に、図6を用いて、リカバリー処理を含んだ電源を立ち上げる制御方法について説明する。

【0048】

この制御方式では、図2(A)に示す閾値測定回路に相当する閾値測定回路を必要とする。

【0049】

まず、降圧型コンバータ10の電源をオンする前に、閾値測定回路に電源を供給するためのサブ電源をオンしてから、主電源をオンする。スイッチング素子SW10のゲートにバッテリーBATの電圧が供給されるのを遮断したあと、PWM発生回路にて、スイッチング素子SW10のゲートに、通常動作時のPWM信号とはかなり低い周波数のPWM信号を供給する。スイッチング素子SW10のドレインにも通常動作時の電圧とはかなり低い電圧を供給し、スイッチングを行なう。この時、GaN−HEMTがノーマリーオンになっていたとしても、ドレインに加えられる電圧は低いので、GaN−HEMTがリーク電流で破壊されることはない。

【0050】

次いで、閾値測定回路を用いてGaN−HEMTの閾値を測定する。閾値がある程度、例えば1.2Vくらいあれば、通常の動作ができると判断して、閾値の測定を終了するため、閾値測定回路を切り離す。そして、通常動作を行なうため、PWM発生回路にて、スイッチング素子SW10のゲートに通常動作時の周波数のPWM信号を供給する。スイッチング素子SW10のドレインにも通常動作時の電圧を供給し、スイッチングを行なう。

【0051】

閾値が1.2V以下だった場合は、スイッチング素子SW10のゲートに通常動作時のPWM信号とはかなり低い周波数でPWM信号を供給し続ける。場合によっては、徐々に閾値が上昇することがある。タイマー監視を行ない、閾値が1.2Vまで上昇するかどうかを閾値測定回路で測定し、閾値が1.2Vになったら、通常動作に移行する。

【0052】

低い周波数でPWM信号を供給し続けても閾値が1.2Vに達しない場合は、リカバリーできないと判断し、何らかの表示装置にエラー表示をして、処理を終了する。

【0053】

以上本発明の好ましい実施形態について詳述したが、本発明は係る特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【符号の説明】

【0054】

2A、2B 入力端子

3A、3B 出力端子

10 降圧型コンバータ

20 PWM信号発生回路

30 ゲート制御回路

50 突入電流防止回路

80 ゲート

81 ソース

82 ドレイン

90 基板

91 GaN層

92 AlGaN層

93 二次元電子ガス層

94 n−GaN層

95 ゲート絶縁膜

【技術分野】

【0001】

本発明は、ノーマリーオンのスイッチング素子を含む制御回路及びその制御回路を用いた電子機器に関する。

【背景技術】

【0002】

近年、様々な分野におけるエネルギー資源の節約が注目され、例えば、電源の分野においてもその影響が波及している。具体的には、例えば、スイッチング電源のさらなる高効率化が求められるようになってきている。

【0003】

スイッチング電源は、入力された直流電圧をDC(Direct Current)−DCコンバータを用いて所望の直流電圧に変換し、安定化電源電圧として出力する。コンピュータに用いられるCPU( Central Processing Unit )等の半導体素子の低電圧化及び消費電力の増大に伴って、電源装置も低電圧かつ大電流を出力可能なスイッチング電源が使用されてきている。

【0004】

電源装置の出力効率をさらに向上させるためには、例えば、使用するスイッチング素子(スイッチング用トランジスタ)で消費される電力を減らす必要がある。そこで、電力損失を低減するためには、オン抵抗が小さく、スイッチング速度が速いスイッチング素子を用いるのが望ましい。その両方の特性を満足する、シリコンではない化合物半導体材料を用いたスイッチング電源用トランジスタが開発されている。

【0005】

化合物半導体の一例として、窒素ガリウム(GaN)を用いた高電子移動度トランジスタ(HEMT:High Electron Mobility Transistor)について説明する。以下、このトランジスタをGaN−HEMTと称する。

【0006】

GaN−HEMTは、ドレイン、ソース、ゲートを有する三端子トランジスタである。例えば、ソースを接地し、ソース−ドレイン間に所定の正電圧を印加し、ソース−ゲート間に印加する電圧を閾値以上にすると、ソース−ドレイン間が導通する(オンになる)。ソース−ゲート間に印加する電圧の閾値は、例えば、−10(V)〜+10(V)である。GaN−HEMTは、動作を含めてMOSFETと同様に取り扱うことができる。

【0007】

従来のシリコンのMOSFETが、ゲートに電圧を印加しない状態でオフになるノーマリーオフ型(エンハンスメント型)であるのに対して、GaN−HEMTは、通常、ゲートに電圧を印加しない状態でオンになるノーマリーオン型(デプレッション型)である。そのためGaN−HEMTをスイッチングするためには、負電位の閾値以下にゲート電圧を下げるための負電源が必要になる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭53−048426号公報

【特許文献2】特開2007−159364号公報

【特許文献3】特開2008−182884号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

ノーマリーオン型のGaN−HEMTを高電圧でスイッチング動作させると、ゲート直下のゲート絶縁膜の界面に電荷がチャージされて、閾値が上がり、疑似的にノーマリーオフになることが判っている。

【0010】

図1(A)は、GaN−HEMTの断面を示す。GaN−HEMTは、サファイア、SiC、GaN、Si等の基板90上に、GaN層91、AlGaN層92を結晶成長し、その上にn−GaN層94を挟んで、ソース81、ドレイン82が形成されている。ゲート80は、ゲート絶縁膜95を挟んでn−GaN層94上に形成されている。GaN−HEMTにおいては、GaN層91とAlGaN層92間の二次元電子ガス層93を電子走行層としている。GaN−HEMTを高電圧でスイッチング動作させると、図に示す様に、ゲート80直下のゲート絶縁膜95の界面に電荷が溜まることによって、閾値が正電圧に上昇する。

【0011】

図1(B)は、ゲート直下に電荷がチャージされたGaN−HEMTの閾値の変化を表わす。GaN−HEMTをスイッチング動作させて、ゲート80直下のゲート絶縁膜95の界面にある程度の電荷がチャージされた状態では、ゲート電圧を零電位にしても、閾値は正電圧レベルのままとなる。ゲートを零電圧にして長時間(数ケ月〜年)放置しておくと、ゲート下の電荷が徐々に放電されてしまうため、ノーマリーオンに戻る。

【0012】

ノーマリーオフ化したGaN−HEMTを装置の電源のスイッチング素子に用いた場合、長期間装置を電源オフの状態にしておくと、ノーマリーオンに戻ってしまう。この状態では、GaN−HEMTのゲートに、負電位を加えないとスイッチングができなくなってしまう。また、電源を立ち上げた時に、GaN−HEMTに高電圧が急に加わって、リーク電流で破壊する恐れがある。

【課題を解決するための手段】

【0013】

1つの案では、制御回路は、ソース、ゲート及びドレインを有する第1のスイッチング素子と、第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路とを有する。

【発明の効果】

【0014】

一実施態様の制御回路によれば、電源をオフしている間もノーマリーオフ化したGaN−HEMTのゲートはバッテリーで閾値以上に保持されているため、ノーマリーオンに戻るのを防止することができる。

【図面の簡単な説明】

【0015】

【図1】GaN−HEMTについて説明する図である。

【図2】GaN−HEMTをノーマリーオフ化する手法について説明する図である。

【図3】第1の実施形態の降圧型コンバータの回路図である。

【図4】第1の実施形態のゲート制御回路30の動作について説明する図である。

【図5】電源を立ち上げる制御方法について説明する図である。

【図6】リカバリー処理を含んだ電源を立ち上げる制御方法について説明する図である。

【発明を実施するための形態】

【0016】

まず、初めにノーマリーオン型のGaN−HEMTをノーマリーオフ化する手法について説明する。

【0017】

図2(A)は、ノーマリーオン型のGaN−HEMTをノーマリーオフ化する回路兼閾値測定回路を示す。GaN−HEMTに負荷電源4V、負荷抵抗20Ωを接続し、GaN−HEMTのゲートに、−5〜+10V、1KHzのデューティ比50%の三角波を加えて、GaN−HEMTをノーマリーオフ化する。

【0018】

図2(B)は、GaN−HEMTの閾値の変化を示す。図2(B)のA線は、電荷がチャージされる前、つまり初期状態のGaN−HEMTの閾値を示している。閾値は−1V程度でノーマリーオンの特性を示している。

【0019】

図2(B)のB線は、GaN−HEMTのゲートに、−5〜+10V、1KHzのデューティ比50%の三角波を加え続けた1時間後のGaN−HEMTの閾値を示している。閾値が正電位側にシフトしており、ノーマリーオフ化されている。

【0020】

ノーマリーオフ化したGaN−HEMT素子を、サーバー用の電源回路のPFC回路部に接続し、スイッチング素子として動作させる。周波数100kHz、ゲート電圧0〜10V、デューティ比0〜100%まで変動させて、ソース・ドレイン間電圧400Vの条件で連続スイッチングを行ない、1時間サーバー用の電源回路内で動作させた後の閾値特性は、ほぼB線と等しくなる。高電圧の電源負荷をかけても閾値は変動していない。これはノーマリーオフ化した時点で電荷のチャージが十分に飽和しており、より大きな負荷をかけても閾値が変化しないことがわかる。

【0021】

次いで、ノーマリーオフ化したGaN−HEMTのゲートソース間に+3Vを印加した状態で1ヶ月放置した後の閾値特性をC線に示す。C線もほぼB線と等しくなる。ゲート電圧を閾値以上に保っておけば閾値の低下は起きない。

【0022】

以下に図面を参照して、本開示の技術にかかる好適な実施の形態を詳細に説明する。

【0023】

図3は、ノーマリーオフ化したGaN−HEMTを電源回路の降圧型コンバータに適用した実施形態を示す回路図である。

【0024】

図3に示す降圧型コンバータ10は、例えば、電圧が385(V)の直流電圧V1を電圧が12(V)の直流電圧に変換して負荷回路RL0に出力する。

【0025】

降圧型コンバータ10は、入力電圧V1をオンオフする主スイッチとなるスイッチング素子SW10と、整流用ダイオードD10と、インダクタL10と、平滑コンデンサC10とを備えている。

【0026】

PWM信号発生回路20は、発生するPWM信号のデューティ比によって降圧型コンバータ10の出力電圧レベルを調整する。PWM信号発生回路20は、降圧される前の直流電圧で動作し、出力電圧をモニターして、PWM信号のデューティ比を調整する。

【0027】

スイッチング素子SW10は、PWM信号発生回路20からゲートにパルス状のゲート電圧が印加されることによってオン/オフ動作が行われ、PWM(Pulse Width Modulation:パルス幅変調)駆動される。スイッチング素子SW10には、前記の手法にてノーマリーオフ化したGaN−HEMTを用いる。

【0028】

ダイオードD10は、直流電源V1の負極からインダクタL10の方向の整流方向を有していればよく、例えば、ファーストリカバリーダイオード、SiCショットキーダイオードが用いられる。

【0029】

ゲート制御回路30は、電源のオンオフを制御する電源制御信号MAINがオフの時に、スイッチング素子SW10のゲートにバッテリーBATの電圧を供給し、電源制御信号MAINがオンの時に、スイッチング素子SW10のゲートにPWM信号を供給する働きを有する。

【0030】

降圧型コンバータ10と直流電圧V1との間には、突入電流防止回路50が設けられている。突入電流防止回路50は、トライアックTR1と制限抵抗R1を直列にした経路と、リレーRL1の経路を有する。トライアックTR1は、双方向サイリスタであって、ゲートからカソードにゲート電流を流すことにより、アノードとカソード間を導通させることができ、アノードとカソードの間の電流が一定値以下に下がると導通状態は停止する(セルフターンオフ)という特性を有する3端子の半導体整流素子である。電源制御信号MAINがオンとなった時点では、トライアックTR1が導通し、スイッチング素子SW10のドレインには、制限抵抗R1を介して直流電圧V1からの電流が流れる。この電流は、制限抵抗R1で制限されているので、スイッチング素子SW10のドレイン及び平滑コンデンサC10に大電流が急に流れこむのを防いでいる。次に電源制御信号MAINより遅延した遅延信号DLONによって、トライアックTR1と制限抵抗R1と並列に設けられたリレーRL1をオンすると、スイッチング素子SW10のドレインには、リレーRL1の経路で電流が流れる。トライアックTR1と制限抵抗R1を直列にした経路に流れる電流は少なくなるので、トライアックTR1はセルフターンオフとなり、トライアックTR1と制限抵抗R1での電力損失は無くなる。

【0031】

次に、図4を参照して、ゲート制御回路30の動作について説明する。図4は、スイッチング素子SW10の動作を表わすタイムチャートである。

【0032】

図4において、0.0msからT1時間までの間は、電源がオフの状態を示していて、電源制御信号MAINはオフとなっている。

【0033】

図3を参照して、この間は、PWM信号発生回路20にドレイン側が接続されたスイッチング素子NM1はオフとなり、バッテリーBATの電圧がPWM信号発生回路20側に逆流して回路破壊や誤動作を起こすのを防いでいる。スイッチング素子NM1は、例えばNMOS−FETとする。

【0034】

同時に、スイッチング素子SW10のゲートにドレイン側が接続されたスイッチング素子PM1がオンとなり、ダイオードD20、抵抗R2を介してバッテリーBATの電圧が、スイッチング素子SW10のゲートに供給される。スイッチング素子PM1は、例えばPMOS−FETとし、バッテリーBATは、ノーマリーオフ化してあるスイッチング素子SW10の閾値電圧より高い、例えば3Vのバッテリーとする必要がある。この時、バッテリーBATから流れる電流はスイッチング素子SW10のゲートリーク電流程度であり、長時間放置してもバッテリーの消耗は最低限に抑えられている。

【0035】

図4を参照して、スイッチング素子SW10のゲート電圧VGは、約3Vに保持されていることを示している。この様に電源がオフの間は、ノーマリーオフ化されたスイッチング素子SW10のゲートに、閾値以上の電圧が供給されるので、ノーマリーオフ化は維持される。

【0036】

次に、T1の時点で、電源がオンとなり電源制御信号MAINがオンになると、スイッチング素子PM1がオフとなり、スイッチング素子SW10のゲートには、バッテリーBATの電圧が供給されなくなり、スイッチング素子SW10のゲート電圧VGは一旦ゼロとなる。スイッチング素子SW10は、ノーマリーオフ化してあるので、スイッチング素子SW10はオフのままで、ドレイン−ソース間電流Idsは流れない。同時にスイッチング素子NM1はオンとなり、PWM信号発生回路20とスイッチング素子SW10のゲートが電気的に接続され、スイッチング素子SW10のスイッチングが可能な状態になる。

【0037】

次に、T2の時点で、PWM信号発生回路20からPWM信号が出力され始め、スイッチング素子SW10のスイッチングが行なわれる。負荷回路RL0に出力される直流電圧は、スイッチング素子SW10のゲートのオンオフを制御するPWM信号のデューティ比を変更することにより調整される。

【0038】

以降、スイッチング動作が継続すれば、スイッチング素子SW10のノーマリーオフの特性は維持され続ける。サーバー等常に電源がオンの状態で使用される装置の電源においては、半永久的にノーマリーオフのままGaN−HEMTを使用することが可能となる。

【0039】

また、装置を工場から顧客へ搬送するまでの期間、装置を保守する期間など、装置の電源をオフする期間があったとしても、バッテリーBATによって、スイッチング素子SW10のゲートは閾値以上に保たれているので、GaN−HEMTのノーマリーオフの特性は維持される。

【0040】

本実施形態によれば、ノーマリーオフ化したGaN−HEMTを、ノーマリーオフの状態で使い続けることが可能となるので、ノーマリーオンのGaN−HEMTを制御するための負電源発生回路が不要となる。

【0041】

次に、図5を用いて電源を立ち上げる制御方法について説明する。

【0042】

装置の電源がオフされていた期間が例えば数ヶ月以上と長いと、バッテリーが消耗して、ノーマリーオフ化したGaN−HEMTがノーマリーオンに戻ってしまう恐れがある。前にも述べたが、ノーマリーオン状態のGaN−HEMTに高電圧を加えるとリーク電流で破壊する恐れがある。これを防ぐために、装置の電源を立ち上げる前に、コンパレータ等でバッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値より高いことを確認してから通常の動作を始める方法がある。この方法では、図3に示す降圧型コンバータ10の周辺に、バッテリー電圧検出回路を設ける必要がある。

【0043】

まず、降圧型コンバータ10の電源をオンする前に、バッテリー電圧検出回路に電源を供給するためのサブ電源をオンする。

【0044】

次いで、バッテリー電圧検出回路によって、バッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値電圧以上であるかを比較する。

【0045】

その際に、バッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値電圧より低かった場合は、GaN−HEMTがノーマリーオンに戻っていると判断して、何らかの表示装置にエラー表示をして、処理を終了する。

【0046】

バッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値電圧より高い場合は、GaN−HEMTがノーマリーオフの状態を維持していると判断して、通常の電源オンの処理を始める。この処理では、バッテリーの電圧がノーマリーオフ化を維持できる電圧より低かった場合は、GaN−HEMTがノーマリーオンに戻っていると判断して、処理を終了させているが、バッテリーの電圧がノーマリーオフ化したGaN−HEMTの閾値電圧より低くなっていたとしても、必ずしも、GaN−HEMTがノーマリーオンに戻っているとは限らない。その場合は、閾値を上げるためのリカバリー処理を行なうことによって、GaN−HEMTを通常の動作させることができる場合がある。

【0047】

次に、図6を用いて、リカバリー処理を含んだ電源を立ち上げる制御方法について説明する。

【0048】

この制御方式では、図2(A)に示す閾値測定回路に相当する閾値測定回路を必要とする。

【0049】

まず、降圧型コンバータ10の電源をオンする前に、閾値測定回路に電源を供給するためのサブ電源をオンしてから、主電源をオンする。スイッチング素子SW10のゲートにバッテリーBATの電圧が供給されるのを遮断したあと、PWM発生回路にて、スイッチング素子SW10のゲートに、通常動作時のPWM信号とはかなり低い周波数のPWM信号を供給する。スイッチング素子SW10のドレインにも通常動作時の電圧とはかなり低い電圧を供給し、スイッチングを行なう。この時、GaN−HEMTがノーマリーオンになっていたとしても、ドレインに加えられる電圧は低いので、GaN−HEMTがリーク電流で破壊されることはない。

【0050】

次いで、閾値測定回路を用いてGaN−HEMTの閾値を測定する。閾値がある程度、例えば1.2Vくらいあれば、通常の動作ができると判断して、閾値の測定を終了するため、閾値測定回路を切り離す。そして、通常動作を行なうため、PWM発生回路にて、スイッチング素子SW10のゲートに通常動作時の周波数のPWM信号を供給する。スイッチング素子SW10のドレインにも通常動作時の電圧を供給し、スイッチングを行なう。

【0051】

閾値が1.2V以下だった場合は、スイッチング素子SW10のゲートに通常動作時のPWM信号とはかなり低い周波数でPWM信号を供給し続ける。場合によっては、徐々に閾値が上昇することがある。タイマー監視を行ない、閾値が1.2Vまで上昇するかどうかを閾値測定回路で測定し、閾値が1.2Vになったら、通常動作に移行する。

【0052】

低い周波数でPWM信号を供給し続けても閾値が1.2Vに達しない場合は、リカバリーできないと判断し、何らかの表示装置にエラー表示をして、処理を終了する。

【0053】

以上本発明の好ましい実施形態について詳述したが、本発明は係る特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【符号の説明】

【0054】

2A、2B 入力端子

3A、3B 出力端子

10 降圧型コンバータ

20 PWM信号発生回路

30 ゲート制御回路

50 突入電流防止回路

80 ゲート

81 ソース

82 ドレイン

90 基板

91 GaN層

92 AlGaN層

93 二次元電子ガス層

94 n−GaN層

95 ゲート絶縁膜

【特許請求の範囲】

【請求項1】

ソース、ゲート及びドレインを有する第1のスイッチング素子と、

第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、

第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、

電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路と

を有することを特徴とする制御回路。

【請求項2】

前記第1のスイッチング素子は、ノーマリーオンからノーマリーオフ化されたGaN−HEMTである

ことを特徴とする請求項1に記載の制御回路。

【請求項3】

前記バッテリーの電圧は、前記ノーマリーオフ化されたGaN−HEMTの閾値よりも大きい電圧である

ことを特徴とする請求項2に記載の制御回路。

【請求項4】

さらに、前記バッテリーの電圧を比較する検出回路を有し、

該検出回路は、前記バッテリーの電圧が前記ノーマリーオフ化されたGaN−HEMTの閾値より低い場合は、電源をオフする

ことを特徴とする請求項3に記載の制御回路。

【請求項5】

さらに、前記第1のスイッチング素子の閾値を測定する閾値測定回路を有し、

該閾値測定回路は、前記第1のスイッチング素子の閾値が所定の電圧より低い場合は、電源をオフする

ことを特徴とする請求項1に記載の制御回路。

【請求項6】

前記PWM信号発生回路は、第1の周波数の第1のPWM信号と、前記第1の周波数よりも遅い第2の周波数の第2のPWM信号を出力する

ことを特徴とする請求項1に記載の制御回路。

【請求項7】

さらに、前記第1のスイッチング素子の閾値を測定する閾値測定回路を有し、

該閾値測定回路は、前記第1のスイッチング素子の閾値が所定の電圧より低い場合は、前記ゲートに前記第2のPWM信号を供給し、前記第1のスイッチング素子の閾値が所定の電圧より高くなった場合は、前記ゲートに前記第1のPWM信号を供給する

ことを特徴とする請求項6に記載の制御回路。

【請求項8】

前記第2のスイッチング素子は、PMOS−FETであり、

前記第3のスイッチング素子は、NMOS−FETである

ことを特徴とする請求項1に記載の制御回路。

【請求項9】

さらに、前記第1のスイッチング素子のドレイン側に突入電流防止回路を有し、

該突入電流防止回路は、直列に接続されたトライアックと抵抗、及び前記トライアックと前記抵抗に並列に接続されたリレーを有する

ことを特徴とする請求項1に記載の制御回路。

【請求項10】

ソース、ゲート及びドレインを有する第1のスイッチング素子を含むコンバータ回路と、

第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、

第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、

電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路と

を有することを特徴とする電子機器。

【請求項1】

ソース、ゲート及びドレインを有する第1のスイッチング素子と、

第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、

第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、

電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路と

を有することを特徴とする制御回路。

【請求項2】

前記第1のスイッチング素子は、ノーマリーオンからノーマリーオフ化されたGaN−HEMTである

ことを特徴とする請求項1に記載の制御回路。

【請求項3】

前記バッテリーの電圧は、前記ノーマリーオフ化されたGaN−HEMTの閾値よりも大きい電圧である

ことを特徴とする請求項2に記載の制御回路。

【請求項4】

さらに、前記バッテリーの電圧を比較する検出回路を有し、

該検出回路は、前記バッテリーの電圧が前記ノーマリーオフ化されたGaN−HEMTの閾値より低い場合は、電源をオフする

ことを特徴とする請求項3に記載の制御回路。

【請求項5】

さらに、前記第1のスイッチング素子の閾値を測定する閾値測定回路を有し、

該閾値測定回路は、前記第1のスイッチング素子の閾値が所定の電圧より低い場合は、電源をオフする

ことを特徴とする請求項1に記載の制御回路。

【請求項6】

前記PWM信号発生回路は、第1の周波数の第1のPWM信号と、前記第1の周波数よりも遅い第2の周波数の第2のPWM信号を出力する

ことを特徴とする請求項1に記載の制御回路。

【請求項7】

さらに、前記第1のスイッチング素子の閾値を測定する閾値測定回路を有し、

該閾値測定回路は、前記第1のスイッチング素子の閾値が所定の電圧より低い場合は、前記ゲートに前記第2のPWM信号を供給し、前記第1のスイッチング素子の閾値が所定の電圧より高くなった場合は、前記ゲートに前記第1のPWM信号を供給する

ことを特徴とする請求項6に記載の制御回路。

【請求項8】

前記第2のスイッチング素子は、PMOS−FETであり、

前記第3のスイッチング素子は、NMOS−FETである

ことを特徴とする請求項1に記載の制御回路。

【請求項9】

さらに、前記第1のスイッチング素子のドレイン側に突入電流防止回路を有し、

該突入電流防止回路は、直列に接続されたトライアックと抵抗、及び前記トライアックと前記抵抗に並列に接続されたリレーを有する

ことを特徴とする請求項1に記載の制御回路。

【請求項10】

ソース、ゲート及びドレインを有する第1のスイッチング素子を含むコンバータ回路と、

第2のスイッチング素子を介して前記ゲートに電圧を供給するバッテリーと、

第3のスイッチング素子を介して前記ゲートにPWM信号を供給するPWM信号発生回路と、

電源がオフの状態で、前記第2のスイッチング素子をオンして前記ゲートに前記バッテリーの電圧を供給すると共に、前記第3のスイッチング素子をオフし、電源がオンの状態で、前記第3のスイッチング素子をオンして前記ゲートに前記PWM信号電圧を供給すると共に、前記第2のスイッチング素子をオフするゲート制御回路と

を有することを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−110831(P2013−110831A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253321(P2011−253321)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]