加速度センサ回路

【課題】安価で高性能な加速度センサ回路を提供することを目的とする。

【解決手段】加速度に応じて容量が変化する第1のキャパシタC1と、加速度に応じて第1のキャパシタと相反するように容量が変化する第2のキャパシタC2とを有する加速度センサ11と、第1のキャパシタC1と第2のキャパシタC2に互いに逆位相で印加する所定周波数の正弦波交流信号を生成する第1の回路15Aと、加速度に応じた信号を、第1のキャパシタC1の容量と第2のキャパシタC2の容量との比、及び第1のキャパシタC1と第2のキャパシタC2に印加した正弦波交流信号とに基づいて生成する第2の回路12と、第2の回路12が生成した信号を符号化したデータを解析して、所定周波数と略同一の周波数成分の信号をデータから抽出し、抽出した信号に基づいて加速度のデータを出力する演算回路14と、を備える加速度センサ回路1。

【解決手段】加速度に応じて容量が変化する第1のキャパシタC1と、加速度に応じて第1のキャパシタと相反するように容量が変化する第2のキャパシタC2とを有する加速度センサ11と、第1のキャパシタC1と第2のキャパシタC2に互いに逆位相で印加する所定周波数の正弦波交流信号を生成する第1の回路15Aと、加速度に応じた信号を、第1のキャパシタC1の容量と第2のキャパシタC2の容量との比、及び第1のキャパシタC1と第2のキャパシタC2に印加した正弦波交流信号とに基づいて生成する第2の回路12と、第2の回路12が生成した信号を符号化したデータを解析して、所定周波数と略同一の周波数成分の信号をデータから抽出し、抽出した信号に基づいて加速度のデータを出力する演算回路14と、を備える加速度センサ回路1。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、静電容量の変化により加速度を検知する加速度センサ回路に関する。

【背景技術】

【0002】

加速度センサは、自動車のエアバッグ、及びゲーム機等の幅広い分野で利用される。これらの加速度センサは、小型で周波数特性が0近傍から数千Hzという低周波数帯域まで感度が伸びている。

【0003】

物理探査の一種である反射法地震探査法は、人工的に地震波を発生させ、地表に設置した受振器により地下から跳ね返ってくる反射波を捉え、その結果を解析して地下構造を解明する方法である。この受振器には加速度センサが備えられ、反射波による振動を加速度として検知する。反射法地震探査法では、1000個程度の受振器を設置して地下構造を検出する。将来的には、受振器を10m程の格子間隔で100万個ほど設置することも想定される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平11−258265号公報

【特許文献2】特開2010−169534号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

反射法地震探査法などの分野では、加速度センサは、ダイナミックレンジとして120dB程度の加速度検出が必要となる。しかしながら、例えば、車両制御用の加速度センサでは、ダイナミックレンジとして60〜80dB程度の加速度検知しかしておらず、更なる性能の向上が求められている。ここで、高性能な増幅回路やフィルタ回路を駆使することも考えられるが、例えば、反射法地震探査法などの分野では多数のセンサを設置する必要があるため、より安価で高性能な加速度センサが求められる。

【0006】

本発明は、上記の点に鑑みてなされたものであり、安価で高性能な加速度センサ回路を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明は、上記課題を解決するため、加速度センサのキャパシタに所定周波数の正弦波交流信号を印加し、加速度センサの信号から、前記所定周波数と同じ周波数成分の信号を演算回路で抽出することにした。

【0008】

詳細には、本発明に係る加速度センサ回路は、加速度に応じて容量が変化する第1のキャパシタと、前記加速度に応じて前記第1のキャパシタと相反するように容量が変化する第2のキャパシタとを有する加速度センサと、前記第1のキャパシタと前記第2のキャパシタに互いに逆位相で印加する所定周波数の正弦波交流信号を生成する第1の回路と、前記加速度に応じた信号を、前記第1のキャパシタの容量と前記第2のキャパシタの容量との比、及び前記第1のキャパシタと前記第2のキャパシタに印加した前記正弦波交流信号とに基づいて生成する第2の回路と、前記第2の回路が生成した信号を符号化したデータを解析して、前記所定周波数と略同一の周波数成分の信号を前記データから抽出し、抽出した信号に基づいて前記加速度のデータを出力する演算回路と、を備える。

【0009】

上記加速度センサ回路であれば、加速度センサの各キャパシタに所定周波数の正弦波交流信号を印加し、これを用いて加速度に応じた信号を生成している。よって、生成した加速度信号に含まれる、前記所定周波数以外の不要な周波数の信号を演算回路で除去し、所望の信号のみを容易に抽出できる。

【0010】

この結果、高性能な増幅回路やアナログフィルタ回路を用いることなく、高性能な加速度センサ回路を安価に実現することができる。

【0011】

なお、前記第1の回路は、前記演算回路が生成した前記所定周波数の正弦波を変換したデジタル信号に基づいてアナログの前記正弦波交流信号を生成するDAコンバータを有するものであってもよい。前記所定周波数の正弦波の信号が、前記演算回路から派生して生成されたものであれば、前記第2の回路が生成した信号を解析して所望波を抽出する際、演算回路の演算処理のタイミングとDAコンバータが出力する交流信号のタイミングとが一致し、適正に信号を処理することができる。

【0012】

また、前記第1の回路は、前記DAコンバータが生成した信号と同位相の正弦波交流信号を前記第1のキャパシタへ印加する非反転アンプと、前記DAコンバータが生成した信号と位相が反転する正弦波交流信号を前記第2のキャパシタへ印加する反転アンプと、を有するものであってもよい。第1の回路をこのように構成すれば、加速度センサの第1のキャパシタへ印加する信号のタイミングと第2のキャパシタへ印加する信号のタイミングとが一致し、加速度を適正に検知することができる。

【0013】

また、前記演算回路は、前記非反転アンプから出力された前記第1のキャパシタへ印加される正弦波交流信号と、前記反転アンプから出力された前記第2のキャパシタへ印加される正弦波交流信号とに、所定の電圧を加算してオフセット調整を行なうものであってもよい。演算回路は、第2の回路が生成した信号を解析して各種の処理を行うことを前提としているため、加速度センサの各キャパシタに印加する正弦波交流信号のオフセットを演算回路に実行させることにすれば、第2の回路が生成した信号を解析して容易にオフセット量を決定し、調整することができる。

【発明の効果】

【0014】

本発明であれば、高性能な加速度センサ回路を安価に実現することができる。

【図面の簡単な説明】

【0015】

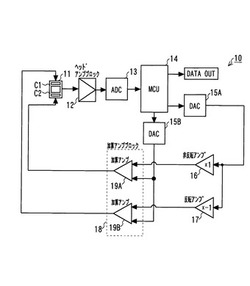

【図1】実施形態に係る加速度センサ回路を示す図である。

【図2】加速度センサの動作説明図である。

【図3】実施例に係る加速度センサ回路を示す図である。

【図4】加速度センサ回路において実行される処理のフロー図である。

【図5】DAコンバータが生成する正弦波の波形の一例を示す図である。

【図6】加速度センサのコンデンサC1側に印加される信号の一例を示す図である。

【図7】加速度センサのコンデンサC2側に印加される信号の一例を示す図である。

【図8】ヘッドアンプブロックが出力する信号の一例を示す図である。

【図9】アナログ信号の波形のサンプリング処理の一例を示す図である。

【図10】BPFが処理する信号のスペクトラムの一例を示す図である。

【図11】頂点検出処理の一例を示す図である。

【発明を実施するための形態】

【0016】

以下、本願発明の実施形態について説明する。以下に示す実施形態は、本願発明の一態様を例示的に示すものであり、本願発明の技術的範囲を以下の実施形態に限定するものではない。

【0017】

<実施形態>

実施形態に係る加速度センサ回路を図1に示す。加速度センサ回路10は、加速度を検知する加速度センサ11、ヘッドアンプブロック12、AD(Analog to Digital)コン

バータ13、MCU(Micro-controller unit)14、DA(Digital to Analog)コンバータ15A,15B、非反転アンプ16、反転アンプ17、加算アンプブロック18を備える。

【0018】

MCU14は、演算素子やメモリ、入出力インターフェース等のコンピュータシステムを一つの集積回路に組み込んだ電子部品であり、不揮発性メモリに格納されたコンピュータプログラムを実行して各種の演算処理を実行する。MCU14は、ADコンバータ13から入力されるデジタル信号を、フーリエ変換を用いたBPF(Band-pass filter)によってフィルタリングしたり、DAコンバータ15A,15Bへデジタルデータを出力したりする。

【0019】

加速度センサの動作を図2に示す。加速度センサ11は、MEMS(Micro Electro Mechanical System)のセンサであり、コンデンサ(キャパシタ)C1,C2を備える静電

容量方式の加速度センサである。この加速度センサ11は、微小な2つの固定電極と2つの可動電極との組み合わせからなっており、加速度が加わるとカンチレバーが曲がって可動電極が移動し、可動電極と各固定電極との間の静電容量が変化する。すなわち、この加速度センサ11は、対峙する2つの固定電極の間に可動電極が挿置されていることにより、加速度センサ11に加速度が加わって可動電極が移動し、例えば、図2(B)に示すように可動電極がコンデンサC1側の固定電極へ近づくとコンデンサC1の静電容量が増加してコンデンサC2の静電容量が減少し、図2(C)に示すように可動電極がコンデンサC2側の固定電極へ近づくとコンデンサC1の静電容量が減少してコンデンサC2の静電容量が増加するようになっている。また、加速度がかかっていない状態では、図2(A)に示すようにコンデンサC1とコンデンサC2の容量は共に均等な状態となる。

【0020】

ヘッドアンプブロック12は、加速度センサ11のコンデンサC1,C2の静電容量の変化を電気信号として取り出し、加速度に比例した電圧として出力するCV(Capacitance Voltage)変換回路である。

【0021】

ADコンバータ13は、アナログ信号をデジタル信号へ変換する変換回路である。AD変換の方式としては、フラッシュ型やパイプライン型、逐次比較型、デルタシグマ型、二十積分型などが存在するが、各種の加速度の計測に用いる本実施形態においては、例えば、音声処理や各種計測に好適なデルタシグマ型が好適である。ADコンバータ13のサンプリング周波数は、目的のサンプリング周波数よりも充分に高い周波数に設定されており、アナログ信号を適正に標本化可能である。

【0022】

DAコンバータ15A,15Bは、デジタル信号をアナログ信号へ変換する変換回路である。DA変換の方式としては、抵抗ラダー型や抵抗ストリング型、電流出力型、デルタシグマ型などが存在するが、各種の加速度の計測に用いる本実施形態においては、例えば、音声処理や各種計測に好適なデルタシグマ型が好適である。DAコンバータ15A,15Bのサンプリング周波数は、充分に高い周波数に設定されており、高精度なアナログ信号を適正に生成可能である。

【0023】

加算アンプブロック18は、加算アンプ19A,19Bを備える回路である。加算アンプブロック18は、DAコンバータ15Aから非反転アンプ16および反転アンプ17を介して入力される正弦波のアナログ信号に、DAコンバータ15Bから出力されるオフセット電圧を加算し、オフセット電圧を加算した正弦波のアナログ信号を加速度センサ11

のコンデンサC1,C2へ印加する。

【0024】

上記加速度センサ回路10は、次のように動作する。まず、加速度センサ回路10の電源がオンになると、MCU14が起動して所定のコンピュータプログラムの実行を開始すると共に、ADコンバータ13やDAコンバータ15A,15Bが起動して信号の変換処理を開始する。

【0025】

ここで、MCU14は、DAコンバータ15Aのアナログ出力から所定のバイアス周波数の正弦波(Sin波)が出力されるように、正弦波のデジタルデータを生成し、生成したデジタルの波形データをDAコンバータ15Aへ送る。このバイアス周波数は、加速度センサ11が検出する振動(検出波)の周波数よりも遥かに高い値に設定される。DAコンバータ15Aから出力された正弦波のアナログ信号は途中で分岐し、何れか一方は非反転アンプ16を経由して加算アンプブロック18の加算アンプ19Aへ入力され、何れか他方は反転アンプ17を経由して加算アンプブロック18の加算アンプ19Bへ入力される。

【0026】

加算アンプブロック18では、非反転アンプ16および反転アンプ17から出力された正弦波のアナログ信号に、DAコンバータ15Bからのオフセット電圧が加えられる。これにより、加算アンプ19Aからは、DAコンバータ15Aが出力するアナログ信号と位相が同じで振幅がオフセット電圧の分だけシフトした正弦波が出力され、また、加算アンプ19Bからは、DAコンバータ15Aが出力するアナログ信号と位相が反転し更に振幅がオフセット電圧の分だけシフトした正弦波が出力される。加算アンプ19Aから出力された正弦波のアナログ信号は、加速度センサ11にある2つの固定電極のうちコンデンサC1側の固定電極に印加される。また、加算アンプ19Bから出力された正弦波のアナログ信号は、加速度センサ11にある2つの固定電極のうちコンデンサC2側の固定電極に印加される。

【0027】

ここで、加算アンプ19Aと加算アンプ19Bから出力される正弦波は、180°の位相差を持つため、加速度センサ11の可動電極には、静電容量の差(C1−C2)に比例し、正弦波の振幅に比例した電荷量が蓄積される。静電容量の差(C1−C2)は、加速度センサ11の加速度に比例するため、静電容量の差(C1−C2)の変化を測定すれば、加速度センサ11に加わっている加速度を検出できる。

【0028】

ヘッドアンプブロック12では、加速度センサ11のコンデンサC1,C2の静電容量の差(C1−C2)が電気信号として取り出され、電圧が加速度に比例したアナログ信号が出力される。ヘッドアンプブロック12から出力されたアナログ信号は、ADコンバータ13で符号化された後、MCU14に入力される。MCU14では、デジタル信号に変換されたヘッドアンプブロック12からの信号を、ソフトウェアによって実現するバンドパスフィルタによってフィルタリングし、DAコンバータ15Aが出力する正弦波の所定のバイアス周波数以外の周波数成分を除去する。そして、MCU14によってフィルタリングされたデジタル信号は、加速度信号として外部へ出力される。なお、加速度信号は、デジタル信号のまま外部へ出力してもよいし、DAコンバータでアナログ信号へ変換してから外部へ出力してもよい。

【0029】

以上に示したように、加速度センサの信号を取り扱う回路を、上記実施形態に係る加速度センサ回路10のように構成すれば、非常に安価な回路構成とすることができる。

【0030】

例えば、加速度センサに印加する信号の波形を矩形波とした場合、矩形波には、基本周波数の他に奇数次の高調波成分(基本波の奇数倍の成分)を含んでいる。よって、アナログ回路においては、高調波が回路の非線形性に伴う波形の歪みの結果として生じることが

多いため、このような高調波成分を十分に減衰させることができるフィルタ回路を設ける必要があり、回路構成が複雑になる。しかし、上記実施形態に係る加速度センサ回路10であれば、加速度センサに印加する信号の波形を正弦波にしているため、歪のない正弦波を使うと、そのスペクトラムは基本周波数だけとなるので回路構成を簡単にすることができる。

【0031】

また、上記実施形態に係る加速度センサ回路10であれば、基本周波数の成分のみを取り扱えばよいので、オペアンプ等に市販のデジタルオーディオ用のIC(Integrated Circuit)を用いることができ、加速度センサ回路を汎用的に構成することができる。更に、加速度センサの信号を全てアナログで処理するのではなく、一時的にデジタルへ置き換えて、バイアス周波数以外の成分を急峻なデジタルのバンドパスフィルタによってフィルタリング除去することにより、オペアンプを用いた場合に特有の1/fノイズ等も容易に排除できる。

【0032】

<実施例>

以下、市販のデジタルオーディオ用IC等を用いて、上記実施形態に係る加速度センサ回路10を実現する場合の一例を示す。本実施例に係る加速度センサ回路を図3に示す。なお、以下において、上記実施形態に係る構成と同様のものには同一の名称を付し、その詳細な説明を省略する。また、本実施例では、3つの加速度センサで3軸の加速度を検知する場合を例にしている。しかし、本実施例は、1軸あるいは2軸の加速度を検知するようにしてもよい。

【0033】

本実施例に係る加速度センサ回路50は、X軸方向の加速度を検知する加速度センサ51X、Y軸方向の加速度を検知する加速度センサ51Y、Z軸方向の加速度を検知する加速度センサ51Z、ヘッドアンプブロック52A,52B,52C、ADコンバータ53A,53B、MCU54、DAコンバータ55A,55B,55C、LPF(Low-pass filter)60A,60B,60C,60D、非反転アンプ56、反転アンプ57、加算ア

ンプブロック58A,58B,58C、アッテネータ61、電源回路ブロック62を備える。

【0034】

ADコンバータ53A,53B及びDAコンバータ55A,55B,55Cは、市販のデジタルオーディオ機器用のADコンバータやDAコンバータを流用したものであり、コストパフォーマンスに優れ、また、左右独立の音声信号を生成するための2つのチャンネル(LchとRch)をそれぞれ有している。ADコンバータ53A,53B及びDAコンバータ55A,55Bのサンプリング周波数は、本実施例で用いるバイアス周波数(9.6kHz)の正弦波の信号を適正に処理可能な周波数(例えば、96kHz)に設定されている。

【0035】

LPF60A,60B,60C,60Dは、オペアンプや抵抗、コンデンサからなる積分回路によって構成したローパスフィルタであり、低周波の信号を通し、所定の周波数よりも高い周波数の信号を遮断する(減衰させる)フィルタである。LPF60A,60B,60C,60Dは、DAコンバータ55A,55Bの出力信号に特有の高調波成分を取り除く。

【0036】

CAN(Controller Area Network)トランシーバ63は、車内通信等に用いられてい

る通信規格CANの通信線を介して周辺機器と通信するための入出力インターフェースである。CANは、一本の信号線で複数のセンサ回路を直列に繋ぐことができるため、各種の計測を行う際のデータ収集に便利である。

【0037】

非反転アンプ56および反転アンプ57の機能は、基本的に上記実施形態に係る非反転

アンプ16および反転アンプ17と同様であるが、オペアンプや抵抗、コンデンサからなる微分回路によって構成したハイパスフィルタとしての機能も兼ね備えている。

【0038】

次に、上記加速度センサ回路50の動作について説明する。加速度センサ回路50の電源がオンになると、加速度センサ回路50は、以下のように動作する。加速度センサ回路50において実行される処理のフローを図4に示す。

【0039】

(ステップS101)加速度センサ回路50の電源がオンになると、MCU54は、イニシャライズを行なう。すなわち、MCU54は、内部のメモリをクリアしたり、所定のコンピュータプログラムを実行してデジタルバンドパスフィルタ等を内部に実現する。

【0040】

(ステップS102)次に、MCU54は、ADコンバータ53A,53BおよびDAコンバータ55A,55B,55Cを作動させて、AD変換およびDA変換処理を開始させる。ここで、MCU54は、DAコンバータ55Aのアナログ出力(Rch)から9.6kHzの正弦波が出力されるように、正弦波のデジタルデータを生成し、DAコンバータ55AへRch用のデジタルデータとして送る。これにより、DAコンバータ55Aでは図5に示すような正弦波のアナログ信号が生成されてRchから出力され、正弦波のアナログ信号が非反転アンプ56および反転アンプ57へ入力される。これにより、非反転アンプ56からは9.6kHzの正弦波(Vp-p5V)が出力されると共に、反転アンプ

57からは非反転アンプ56が出力する正弦波と周波数が同じで位相が逆の正弦波(Vp-p5V)が出力される。これにより、加算アンプブロック58A,58B,58Cから、

9.6kHzの正弦波(Vp-p10V)が出力される。

【0041】

(ステップS103)次に、MCU54は、加速度センサ51X,51Y,51Zのオフセット調整を行なう。例えば、加算アンプブロック58Aに2.5Vのオフセット電圧を加えた場合を考える。

【0042】

加算アンプブロック58A,58B,58Cでは、非反転アンプ56および反転アンプ57から出力された正弦波のアナログ信号に、MCU54やDAコンバータ55Cからのオフセット電圧が加わるように回路構成されている。よって、例えば、加算アンプブロック58Aに+2.5Vのオフセット電圧を加えた場合、加速度センサ51XのコンデンサC1側へは、例えば、図6に示すような、DAコンバータ55Bが出力するアナログ信号と位相が同じで振幅がオフセット電圧の分だけシフトした正弦波が送られる。また、加速度センサ51XのコンデンサC2側へは、例えば、図7に示すような、DAコンバータ55Bが出力するアナログ信号と位相が反転し更に振幅がオフセット電圧の分だけシフトした正弦波が送られる。

【0043】

ここで、加速度センサ51XのコンデンサC1側に入力される正弦波とコンデンサC2側に入力される正弦波される正弦波は、180°の位相差を持つため、例えば、ヘッドアンプブロック52Aの帰還容量をCR、基準電位をVinとすると、ヘッドアンプブロック52Aの出力電圧V3は、下記の式で表される。

【数1】

【0044】

上記式(数1)より、ヘッドアンプブロック52Aの出力電圧V3は、例えば、図8の

グラフのような波形を描く。すなわち、例えば、コンデンサC1の静電容量の方がコンデンサC2の静電容量より大きい場合(C1>C2)、ヘッドアンプブロック52Aの出力

電圧V3は、DAコンバータ55Bの出力電圧と同位相になる。また、コンデンサC1の

静電容量C1とコンデンサC2の静電容量C2とが等しい場合(C1=C2)、ヘッドアンプブロック52Aの出力電圧V3は、一定になる。また、コンデンサC1の静電容量C

1の方がコンデンサC2の静電容量より小さい場合(C1<C2)、ヘッドアンプブロック52Aの出力電圧V3は、DAコンバータ55Bの出力電圧と逆位相になる。なお、図

8のグラフでは、位相の確認のため、DAコンバータ55Bから非反転アンプ56および反転アンプ57へ送られる信号の波形を併記している。このような位相の確認は、例えば、アッテネータ61からADコンバータ53Bを介してMCU54へ送られる信号を用いて行なうことができる。

【0045】

そこで、MCU54は、加速度センサ51X,51Y,51Zに加速度が加わっていない状態ではヘッドアンプブロック52A,52B,52Cの出力電圧が一定になるように、加算アンプブロック58A,58B,58Cに加えるオフセット電圧を調整する。

【0046】

(ステップS104)一連の処理(S101〜S103)を終えて、加速度センサ回路50を起動する際の処理が完了した後、加速度センサ回路50では、以下のような処理が実行されて、加速度のデータの計測が行なわれる。すなわち、ヘッドアンプブロック52A,52B,52Cから出力されたアナログ信号が、ADコンバータ53A,53Bに入力される。そして、ADコンバータ53A,53Bでは、例えば、図9に示すように、アナログ信号の波形のサンプリングが行なわれ、アナログ信号がデジタル信号に変換される。

【0047】

(ステップS105)MCU54では、デジタル信号に変換されたヘッドアンプブロック52Aからの信号が、フーリエ変換に基づく急峻なデジタルのバンドパスフィルタにより、図10に示すようにフィルタリングされ、バイアス周波数(9.6kHz±250Hz)以外の周波数成分の信号が除去される。

【0048】

(ステップS106)MCU54では、バンドパスフィルタによってフィルタリングした信号の波形を解析し、図11に示すような波形の頂点(VH,VL)の値を検出する。この波形は、バイアス周波数と同じ周波数の正弦波であるため、頂点(VH,VL)の値の検出処理は0.1042ミリ秒毎に行われることになる。

【0049】

(ステップS107)MCU54は、頂点(VH,VL)の値を検出すると、検出した値をMCU54内のメモリに逐次格納する。

【0050】

(ステップS108)また、MCU54は、検出した頂点(VH,VL)の値を以下の数式(数2)に代入し、加速度に比例した電圧のデジタル値を算出する。そして、算出したデジタル値に、DAコンバータ55A,55Bの特性に応じた所定の係数を乗算したデジタル値DOUTのデータをDAコンバータ55A,55Bへ送る。これによりDAコンバ

ータ55A,55Bから、加速度のアナログ信号が出力される。なお、加速度のアナログ信号は、図3に示すように、X軸のシングルエンド信号がLPF60Aから出力され、Y軸のシングルエンド信号がLPF60Bから出力され、Z軸のシングルエンド信号がLPF60Cから出力されるようにしてもよいが、例えば、何れかの軸に関するシングルエンド信号のみを出力するようにしてもよいし、或いは、何れかの軸に関する差動信号を2つのLPFを使って出力するようにしてもよい。出力する信号の具体的な態様については、MCU54が実行するプログラムによって適宜変更可能である。

【数2】

【0051】

(ステップS109)MCU54は、上記一連のステップ(S104〜S108)を0.1042ミリ秒毎に実行する。また、MCU54は、CANの更新レートに合わせて、1ミリ秒が経過する毎に下記の処理を実行し、CANトランシーバ63を介してCANの通信線に加速度のデジタルデータを送出する。

【0052】

(ステップS110)すなわち、MCU54は、メモリに格納されている直近の過去4つ分の頂点(VH,VL)の値のデータを下記の数式(数3)に代入して平均処理を行い、CAN用の加速度データを生成する。

【数3】

【0053】

(ステップS111)そして、MCU54は、算出したCAN用の加速度データを、CANトランシーバ63を介してCANの通信線に加速度のデジタルデータを送出する。

【0054】

以上、一連の処理(S101〜S111)が加速度センサ回路50で繰り返し実行されることにより、感度の良い良好な加速度データを、安価な回路構成で得ることができる。すなわち、上記加速度センサ回路50であれば、市販のオーディオ用IC等の利用を可能にして安価な回路構成を実現しつつ、加速度センサに入力する電圧に対して広い範囲の出力電圧を得て高感度な信号処理を実現することができる。よって、非常に効率の良い回路構成である。

【0055】

なお、上記実施例で示した周波数や電圧値等は単なる例示であり、本発明は、上記の態様に限定されるものではない。すなわち、本発明に係る加速度センサ回路は、所望の振動等を捉えることが可能な範囲で、周波数や電圧等を適宜変更してもよい。

【符号の説明】

【0056】

10,50・・加速度センサ回路

11,51X,51Y,51Z・・加速度センサ

12,52A,52B,52C・・ヘッドアンプブロック

13,53A,53B・・ADコンバータ

14,54・・MCU

15A,15B,55A,55B,55C・・DAコンバータ

16,56・・非反転アンプ

17,57・・反転アンプ

18,58A,58B,58C・・加算アンプブロック

19A,19B・・加算アンプ

60A,60B,60C,60D・・LPF

61・・アッテネータ

62・・電源回路ブロック

63・・CANトランシーバ

【技術分野】

【0001】

本発明は、静電容量の変化により加速度を検知する加速度センサ回路に関する。

【背景技術】

【0002】

加速度センサは、自動車のエアバッグ、及びゲーム機等の幅広い分野で利用される。これらの加速度センサは、小型で周波数特性が0近傍から数千Hzという低周波数帯域まで感度が伸びている。

【0003】

物理探査の一種である反射法地震探査法は、人工的に地震波を発生させ、地表に設置した受振器により地下から跳ね返ってくる反射波を捉え、その結果を解析して地下構造を解明する方法である。この受振器には加速度センサが備えられ、反射波による振動を加速度として検知する。反射法地震探査法では、1000個程度の受振器を設置して地下構造を検出する。将来的には、受振器を10m程の格子間隔で100万個ほど設置することも想定される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平11−258265号公報

【特許文献2】特開2010−169534号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

反射法地震探査法などの分野では、加速度センサは、ダイナミックレンジとして120dB程度の加速度検出が必要となる。しかしながら、例えば、車両制御用の加速度センサでは、ダイナミックレンジとして60〜80dB程度の加速度検知しかしておらず、更なる性能の向上が求められている。ここで、高性能な増幅回路やフィルタ回路を駆使することも考えられるが、例えば、反射法地震探査法などの分野では多数のセンサを設置する必要があるため、より安価で高性能な加速度センサが求められる。

【0006】

本発明は、上記の点に鑑みてなされたものであり、安価で高性能な加速度センサ回路を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明は、上記課題を解決するため、加速度センサのキャパシタに所定周波数の正弦波交流信号を印加し、加速度センサの信号から、前記所定周波数と同じ周波数成分の信号を演算回路で抽出することにした。

【0008】

詳細には、本発明に係る加速度センサ回路は、加速度に応じて容量が変化する第1のキャパシタと、前記加速度に応じて前記第1のキャパシタと相反するように容量が変化する第2のキャパシタとを有する加速度センサと、前記第1のキャパシタと前記第2のキャパシタに互いに逆位相で印加する所定周波数の正弦波交流信号を生成する第1の回路と、前記加速度に応じた信号を、前記第1のキャパシタの容量と前記第2のキャパシタの容量との比、及び前記第1のキャパシタと前記第2のキャパシタに印加した前記正弦波交流信号とに基づいて生成する第2の回路と、前記第2の回路が生成した信号を符号化したデータを解析して、前記所定周波数と略同一の周波数成分の信号を前記データから抽出し、抽出した信号に基づいて前記加速度のデータを出力する演算回路と、を備える。

【0009】

上記加速度センサ回路であれば、加速度センサの各キャパシタに所定周波数の正弦波交流信号を印加し、これを用いて加速度に応じた信号を生成している。よって、生成した加速度信号に含まれる、前記所定周波数以外の不要な周波数の信号を演算回路で除去し、所望の信号のみを容易に抽出できる。

【0010】

この結果、高性能な増幅回路やアナログフィルタ回路を用いることなく、高性能な加速度センサ回路を安価に実現することができる。

【0011】

なお、前記第1の回路は、前記演算回路が生成した前記所定周波数の正弦波を変換したデジタル信号に基づいてアナログの前記正弦波交流信号を生成するDAコンバータを有するものであってもよい。前記所定周波数の正弦波の信号が、前記演算回路から派生して生成されたものであれば、前記第2の回路が生成した信号を解析して所望波を抽出する際、演算回路の演算処理のタイミングとDAコンバータが出力する交流信号のタイミングとが一致し、適正に信号を処理することができる。

【0012】

また、前記第1の回路は、前記DAコンバータが生成した信号と同位相の正弦波交流信号を前記第1のキャパシタへ印加する非反転アンプと、前記DAコンバータが生成した信号と位相が反転する正弦波交流信号を前記第2のキャパシタへ印加する反転アンプと、を有するものであってもよい。第1の回路をこのように構成すれば、加速度センサの第1のキャパシタへ印加する信号のタイミングと第2のキャパシタへ印加する信号のタイミングとが一致し、加速度を適正に検知することができる。

【0013】

また、前記演算回路は、前記非反転アンプから出力された前記第1のキャパシタへ印加される正弦波交流信号と、前記反転アンプから出力された前記第2のキャパシタへ印加される正弦波交流信号とに、所定の電圧を加算してオフセット調整を行なうものであってもよい。演算回路は、第2の回路が生成した信号を解析して各種の処理を行うことを前提としているため、加速度センサの各キャパシタに印加する正弦波交流信号のオフセットを演算回路に実行させることにすれば、第2の回路が生成した信号を解析して容易にオフセット量を決定し、調整することができる。

【発明の効果】

【0014】

本発明であれば、高性能な加速度センサ回路を安価に実現することができる。

【図面の簡単な説明】

【0015】

【図1】実施形態に係る加速度センサ回路を示す図である。

【図2】加速度センサの動作説明図である。

【図3】実施例に係る加速度センサ回路を示す図である。

【図4】加速度センサ回路において実行される処理のフロー図である。

【図5】DAコンバータが生成する正弦波の波形の一例を示す図である。

【図6】加速度センサのコンデンサC1側に印加される信号の一例を示す図である。

【図7】加速度センサのコンデンサC2側に印加される信号の一例を示す図である。

【図8】ヘッドアンプブロックが出力する信号の一例を示す図である。

【図9】アナログ信号の波形のサンプリング処理の一例を示す図である。

【図10】BPFが処理する信号のスペクトラムの一例を示す図である。

【図11】頂点検出処理の一例を示す図である。

【発明を実施するための形態】

【0016】

以下、本願発明の実施形態について説明する。以下に示す実施形態は、本願発明の一態様を例示的に示すものであり、本願発明の技術的範囲を以下の実施形態に限定するものではない。

【0017】

<実施形態>

実施形態に係る加速度センサ回路を図1に示す。加速度センサ回路10は、加速度を検知する加速度センサ11、ヘッドアンプブロック12、AD(Analog to Digital)コン

バータ13、MCU(Micro-controller unit)14、DA(Digital to Analog)コンバータ15A,15B、非反転アンプ16、反転アンプ17、加算アンプブロック18を備える。

【0018】

MCU14は、演算素子やメモリ、入出力インターフェース等のコンピュータシステムを一つの集積回路に組み込んだ電子部品であり、不揮発性メモリに格納されたコンピュータプログラムを実行して各種の演算処理を実行する。MCU14は、ADコンバータ13から入力されるデジタル信号を、フーリエ変換を用いたBPF(Band-pass filter)によってフィルタリングしたり、DAコンバータ15A,15Bへデジタルデータを出力したりする。

【0019】

加速度センサの動作を図2に示す。加速度センサ11は、MEMS(Micro Electro Mechanical System)のセンサであり、コンデンサ(キャパシタ)C1,C2を備える静電

容量方式の加速度センサである。この加速度センサ11は、微小な2つの固定電極と2つの可動電極との組み合わせからなっており、加速度が加わるとカンチレバーが曲がって可動電極が移動し、可動電極と各固定電極との間の静電容量が変化する。すなわち、この加速度センサ11は、対峙する2つの固定電極の間に可動電極が挿置されていることにより、加速度センサ11に加速度が加わって可動電極が移動し、例えば、図2(B)に示すように可動電極がコンデンサC1側の固定電極へ近づくとコンデンサC1の静電容量が増加してコンデンサC2の静電容量が減少し、図2(C)に示すように可動電極がコンデンサC2側の固定電極へ近づくとコンデンサC1の静電容量が減少してコンデンサC2の静電容量が増加するようになっている。また、加速度がかかっていない状態では、図2(A)に示すようにコンデンサC1とコンデンサC2の容量は共に均等な状態となる。

【0020】

ヘッドアンプブロック12は、加速度センサ11のコンデンサC1,C2の静電容量の変化を電気信号として取り出し、加速度に比例した電圧として出力するCV(Capacitance Voltage)変換回路である。

【0021】

ADコンバータ13は、アナログ信号をデジタル信号へ変換する変換回路である。AD変換の方式としては、フラッシュ型やパイプライン型、逐次比較型、デルタシグマ型、二十積分型などが存在するが、各種の加速度の計測に用いる本実施形態においては、例えば、音声処理や各種計測に好適なデルタシグマ型が好適である。ADコンバータ13のサンプリング周波数は、目的のサンプリング周波数よりも充分に高い周波数に設定されており、アナログ信号を適正に標本化可能である。

【0022】

DAコンバータ15A,15Bは、デジタル信号をアナログ信号へ変換する変換回路である。DA変換の方式としては、抵抗ラダー型や抵抗ストリング型、電流出力型、デルタシグマ型などが存在するが、各種の加速度の計測に用いる本実施形態においては、例えば、音声処理や各種計測に好適なデルタシグマ型が好適である。DAコンバータ15A,15Bのサンプリング周波数は、充分に高い周波数に設定されており、高精度なアナログ信号を適正に生成可能である。

【0023】

加算アンプブロック18は、加算アンプ19A,19Bを備える回路である。加算アンプブロック18は、DAコンバータ15Aから非反転アンプ16および反転アンプ17を介して入力される正弦波のアナログ信号に、DAコンバータ15Bから出力されるオフセット電圧を加算し、オフセット電圧を加算した正弦波のアナログ信号を加速度センサ11

のコンデンサC1,C2へ印加する。

【0024】

上記加速度センサ回路10は、次のように動作する。まず、加速度センサ回路10の電源がオンになると、MCU14が起動して所定のコンピュータプログラムの実行を開始すると共に、ADコンバータ13やDAコンバータ15A,15Bが起動して信号の変換処理を開始する。

【0025】

ここで、MCU14は、DAコンバータ15Aのアナログ出力から所定のバイアス周波数の正弦波(Sin波)が出力されるように、正弦波のデジタルデータを生成し、生成したデジタルの波形データをDAコンバータ15Aへ送る。このバイアス周波数は、加速度センサ11が検出する振動(検出波)の周波数よりも遥かに高い値に設定される。DAコンバータ15Aから出力された正弦波のアナログ信号は途中で分岐し、何れか一方は非反転アンプ16を経由して加算アンプブロック18の加算アンプ19Aへ入力され、何れか他方は反転アンプ17を経由して加算アンプブロック18の加算アンプ19Bへ入力される。

【0026】

加算アンプブロック18では、非反転アンプ16および反転アンプ17から出力された正弦波のアナログ信号に、DAコンバータ15Bからのオフセット電圧が加えられる。これにより、加算アンプ19Aからは、DAコンバータ15Aが出力するアナログ信号と位相が同じで振幅がオフセット電圧の分だけシフトした正弦波が出力され、また、加算アンプ19Bからは、DAコンバータ15Aが出力するアナログ信号と位相が反転し更に振幅がオフセット電圧の分だけシフトした正弦波が出力される。加算アンプ19Aから出力された正弦波のアナログ信号は、加速度センサ11にある2つの固定電極のうちコンデンサC1側の固定電極に印加される。また、加算アンプ19Bから出力された正弦波のアナログ信号は、加速度センサ11にある2つの固定電極のうちコンデンサC2側の固定電極に印加される。

【0027】

ここで、加算アンプ19Aと加算アンプ19Bから出力される正弦波は、180°の位相差を持つため、加速度センサ11の可動電極には、静電容量の差(C1−C2)に比例し、正弦波の振幅に比例した電荷量が蓄積される。静電容量の差(C1−C2)は、加速度センサ11の加速度に比例するため、静電容量の差(C1−C2)の変化を測定すれば、加速度センサ11に加わっている加速度を検出できる。

【0028】

ヘッドアンプブロック12では、加速度センサ11のコンデンサC1,C2の静電容量の差(C1−C2)が電気信号として取り出され、電圧が加速度に比例したアナログ信号が出力される。ヘッドアンプブロック12から出力されたアナログ信号は、ADコンバータ13で符号化された後、MCU14に入力される。MCU14では、デジタル信号に変換されたヘッドアンプブロック12からの信号を、ソフトウェアによって実現するバンドパスフィルタによってフィルタリングし、DAコンバータ15Aが出力する正弦波の所定のバイアス周波数以外の周波数成分を除去する。そして、MCU14によってフィルタリングされたデジタル信号は、加速度信号として外部へ出力される。なお、加速度信号は、デジタル信号のまま外部へ出力してもよいし、DAコンバータでアナログ信号へ変換してから外部へ出力してもよい。

【0029】

以上に示したように、加速度センサの信号を取り扱う回路を、上記実施形態に係る加速度センサ回路10のように構成すれば、非常に安価な回路構成とすることができる。

【0030】

例えば、加速度センサに印加する信号の波形を矩形波とした場合、矩形波には、基本周波数の他に奇数次の高調波成分(基本波の奇数倍の成分)を含んでいる。よって、アナログ回路においては、高調波が回路の非線形性に伴う波形の歪みの結果として生じることが

多いため、このような高調波成分を十分に減衰させることができるフィルタ回路を設ける必要があり、回路構成が複雑になる。しかし、上記実施形態に係る加速度センサ回路10であれば、加速度センサに印加する信号の波形を正弦波にしているため、歪のない正弦波を使うと、そのスペクトラムは基本周波数だけとなるので回路構成を簡単にすることができる。

【0031】

また、上記実施形態に係る加速度センサ回路10であれば、基本周波数の成分のみを取り扱えばよいので、オペアンプ等に市販のデジタルオーディオ用のIC(Integrated Circuit)を用いることができ、加速度センサ回路を汎用的に構成することができる。更に、加速度センサの信号を全てアナログで処理するのではなく、一時的にデジタルへ置き換えて、バイアス周波数以外の成分を急峻なデジタルのバンドパスフィルタによってフィルタリング除去することにより、オペアンプを用いた場合に特有の1/fノイズ等も容易に排除できる。

【0032】

<実施例>

以下、市販のデジタルオーディオ用IC等を用いて、上記実施形態に係る加速度センサ回路10を実現する場合の一例を示す。本実施例に係る加速度センサ回路を図3に示す。なお、以下において、上記実施形態に係る構成と同様のものには同一の名称を付し、その詳細な説明を省略する。また、本実施例では、3つの加速度センサで3軸の加速度を検知する場合を例にしている。しかし、本実施例は、1軸あるいは2軸の加速度を検知するようにしてもよい。

【0033】

本実施例に係る加速度センサ回路50は、X軸方向の加速度を検知する加速度センサ51X、Y軸方向の加速度を検知する加速度センサ51Y、Z軸方向の加速度を検知する加速度センサ51Z、ヘッドアンプブロック52A,52B,52C、ADコンバータ53A,53B、MCU54、DAコンバータ55A,55B,55C、LPF(Low-pass filter)60A,60B,60C,60D、非反転アンプ56、反転アンプ57、加算ア

ンプブロック58A,58B,58C、アッテネータ61、電源回路ブロック62を備える。

【0034】

ADコンバータ53A,53B及びDAコンバータ55A,55B,55Cは、市販のデジタルオーディオ機器用のADコンバータやDAコンバータを流用したものであり、コストパフォーマンスに優れ、また、左右独立の音声信号を生成するための2つのチャンネル(LchとRch)をそれぞれ有している。ADコンバータ53A,53B及びDAコンバータ55A,55Bのサンプリング周波数は、本実施例で用いるバイアス周波数(9.6kHz)の正弦波の信号を適正に処理可能な周波数(例えば、96kHz)に設定されている。

【0035】

LPF60A,60B,60C,60Dは、オペアンプや抵抗、コンデンサからなる積分回路によって構成したローパスフィルタであり、低周波の信号を通し、所定の周波数よりも高い周波数の信号を遮断する(減衰させる)フィルタである。LPF60A,60B,60C,60Dは、DAコンバータ55A,55Bの出力信号に特有の高調波成分を取り除く。

【0036】

CAN(Controller Area Network)トランシーバ63は、車内通信等に用いられてい

る通信規格CANの通信線を介して周辺機器と通信するための入出力インターフェースである。CANは、一本の信号線で複数のセンサ回路を直列に繋ぐことができるため、各種の計測を行う際のデータ収集に便利である。

【0037】

非反転アンプ56および反転アンプ57の機能は、基本的に上記実施形態に係る非反転

アンプ16および反転アンプ17と同様であるが、オペアンプや抵抗、コンデンサからなる微分回路によって構成したハイパスフィルタとしての機能も兼ね備えている。

【0038】

次に、上記加速度センサ回路50の動作について説明する。加速度センサ回路50の電源がオンになると、加速度センサ回路50は、以下のように動作する。加速度センサ回路50において実行される処理のフローを図4に示す。

【0039】

(ステップS101)加速度センサ回路50の電源がオンになると、MCU54は、イニシャライズを行なう。すなわち、MCU54は、内部のメモリをクリアしたり、所定のコンピュータプログラムを実行してデジタルバンドパスフィルタ等を内部に実現する。

【0040】

(ステップS102)次に、MCU54は、ADコンバータ53A,53BおよびDAコンバータ55A,55B,55Cを作動させて、AD変換およびDA変換処理を開始させる。ここで、MCU54は、DAコンバータ55Aのアナログ出力(Rch)から9.6kHzの正弦波が出力されるように、正弦波のデジタルデータを生成し、DAコンバータ55AへRch用のデジタルデータとして送る。これにより、DAコンバータ55Aでは図5に示すような正弦波のアナログ信号が生成されてRchから出力され、正弦波のアナログ信号が非反転アンプ56および反転アンプ57へ入力される。これにより、非反転アンプ56からは9.6kHzの正弦波(Vp-p5V)が出力されると共に、反転アンプ

57からは非反転アンプ56が出力する正弦波と周波数が同じで位相が逆の正弦波(Vp-p5V)が出力される。これにより、加算アンプブロック58A,58B,58Cから、

9.6kHzの正弦波(Vp-p10V)が出力される。

【0041】

(ステップS103)次に、MCU54は、加速度センサ51X,51Y,51Zのオフセット調整を行なう。例えば、加算アンプブロック58Aに2.5Vのオフセット電圧を加えた場合を考える。

【0042】

加算アンプブロック58A,58B,58Cでは、非反転アンプ56および反転アンプ57から出力された正弦波のアナログ信号に、MCU54やDAコンバータ55Cからのオフセット電圧が加わるように回路構成されている。よって、例えば、加算アンプブロック58Aに+2.5Vのオフセット電圧を加えた場合、加速度センサ51XのコンデンサC1側へは、例えば、図6に示すような、DAコンバータ55Bが出力するアナログ信号と位相が同じで振幅がオフセット電圧の分だけシフトした正弦波が送られる。また、加速度センサ51XのコンデンサC2側へは、例えば、図7に示すような、DAコンバータ55Bが出力するアナログ信号と位相が反転し更に振幅がオフセット電圧の分だけシフトした正弦波が送られる。

【0043】

ここで、加速度センサ51XのコンデンサC1側に入力される正弦波とコンデンサC2側に入力される正弦波される正弦波は、180°の位相差を持つため、例えば、ヘッドアンプブロック52Aの帰還容量をCR、基準電位をVinとすると、ヘッドアンプブロック52Aの出力電圧V3は、下記の式で表される。

【数1】

【0044】

上記式(数1)より、ヘッドアンプブロック52Aの出力電圧V3は、例えば、図8の

グラフのような波形を描く。すなわち、例えば、コンデンサC1の静電容量の方がコンデンサC2の静電容量より大きい場合(C1>C2)、ヘッドアンプブロック52Aの出力

電圧V3は、DAコンバータ55Bの出力電圧と同位相になる。また、コンデンサC1の

静電容量C1とコンデンサC2の静電容量C2とが等しい場合(C1=C2)、ヘッドアンプブロック52Aの出力電圧V3は、一定になる。また、コンデンサC1の静電容量C

1の方がコンデンサC2の静電容量より小さい場合(C1<C2)、ヘッドアンプブロック52Aの出力電圧V3は、DAコンバータ55Bの出力電圧と逆位相になる。なお、図

8のグラフでは、位相の確認のため、DAコンバータ55Bから非反転アンプ56および反転アンプ57へ送られる信号の波形を併記している。このような位相の確認は、例えば、アッテネータ61からADコンバータ53Bを介してMCU54へ送られる信号を用いて行なうことができる。

【0045】

そこで、MCU54は、加速度センサ51X,51Y,51Zに加速度が加わっていない状態ではヘッドアンプブロック52A,52B,52Cの出力電圧が一定になるように、加算アンプブロック58A,58B,58Cに加えるオフセット電圧を調整する。

【0046】

(ステップS104)一連の処理(S101〜S103)を終えて、加速度センサ回路50を起動する際の処理が完了した後、加速度センサ回路50では、以下のような処理が実行されて、加速度のデータの計測が行なわれる。すなわち、ヘッドアンプブロック52A,52B,52Cから出力されたアナログ信号が、ADコンバータ53A,53Bに入力される。そして、ADコンバータ53A,53Bでは、例えば、図9に示すように、アナログ信号の波形のサンプリングが行なわれ、アナログ信号がデジタル信号に変換される。

【0047】

(ステップS105)MCU54では、デジタル信号に変換されたヘッドアンプブロック52Aからの信号が、フーリエ変換に基づく急峻なデジタルのバンドパスフィルタにより、図10に示すようにフィルタリングされ、バイアス周波数(9.6kHz±250Hz)以外の周波数成分の信号が除去される。

【0048】

(ステップS106)MCU54では、バンドパスフィルタによってフィルタリングした信号の波形を解析し、図11に示すような波形の頂点(VH,VL)の値を検出する。この波形は、バイアス周波数と同じ周波数の正弦波であるため、頂点(VH,VL)の値の検出処理は0.1042ミリ秒毎に行われることになる。

【0049】

(ステップS107)MCU54は、頂点(VH,VL)の値を検出すると、検出した値をMCU54内のメモリに逐次格納する。

【0050】

(ステップS108)また、MCU54は、検出した頂点(VH,VL)の値を以下の数式(数2)に代入し、加速度に比例した電圧のデジタル値を算出する。そして、算出したデジタル値に、DAコンバータ55A,55Bの特性に応じた所定の係数を乗算したデジタル値DOUTのデータをDAコンバータ55A,55Bへ送る。これによりDAコンバ

ータ55A,55Bから、加速度のアナログ信号が出力される。なお、加速度のアナログ信号は、図3に示すように、X軸のシングルエンド信号がLPF60Aから出力され、Y軸のシングルエンド信号がLPF60Bから出力され、Z軸のシングルエンド信号がLPF60Cから出力されるようにしてもよいが、例えば、何れかの軸に関するシングルエンド信号のみを出力するようにしてもよいし、或いは、何れかの軸に関する差動信号を2つのLPFを使って出力するようにしてもよい。出力する信号の具体的な態様については、MCU54が実行するプログラムによって適宜変更可能である。

【数2】

【0051】

(ステップS109)MCU54は、上記一連のステップ(S104〜S108)を0.1042ミリ秒毎に実行する。また、MCU54は、CANの更新レートに合わせて、1ミリ秒が経過する毎に下記の処理を実行し、CANトランシーバ63を介してCANの通信線に加速度のデジタルデータを送出する。

【0052】

(ステップS110)すなわち、MCU54は、メモリに格納されている直近の過去4つ分の頂点(VH,VL)の値のデータを下記の数式(数3)に代入して平均処理を行い、CAN用の加速度データを生成する。

【数3】

【0053】

(ステップS111)そして、MCU54は、算出したCAN用の加速度データを、CANトランシーバ63を介してCANの通信線に加速度のデジタルデータを送出する。

【0054】

以上、一連の処理(S101〜S111)が加速度センサ回路50で繰り返し実行されることにより、感度の良い良好な加速度データを、安価な回路構成で得ることができる。すなわち、上記加速度センサ回路50であれば、市販のオーディオ用IC等の利用を可能にして安価な回路構成を実現しつつ、加速度センサに入力する電圧に対して広い範囲の出力電圧を得て高感度な信号処理を実現することができる。よって、非常に効率の良い回路構成である。

【0055】

なお、上記実施例で示した周波数や電圧値等は単なる例示であり、本発明は、上記の態様に限定されるものではない。すなわち、本発明に係る加速度センサ回路は、所望の振動等を捉えることが可能な範囲で、周波数や電圧等を適宜変更してもよい。

【符号の説明】

【0056】

10,50・・加速度センサ回路

11,51X,51Y,51Z・・加速度センサ

12,52A,52B,52C・・ヘッドアンプブロック

13,53A,53B・・ADコンバータ

14,54・・MCU

15A,15B,55A,55B,55C・・DAコンバータ

16,56・・非反転アンプ

17,57・・反転アンプ

18,58A,58B,58C・・加算アンプブロック

19A,19B・・加算アンプ

60A,60B,60C,60D・・LPF

61・・アッテネータ

62・・電源回路ブロック

63・・CANトランシーバ

【特許請求の範囲】

【請求項1】

加速度に応じて容量が変化する第1のキャパシタと、前記加速度に応じて前記第1のキャパシタと相反するように容量が変化する第2のキャパシタとを有する加速度センサと、

前記第1のキャパシタと前記第2のキャパシタに互いに逆位相で印加する所定周波数の正弦波交流信号を生成する第1の回路と、

前記加速度に応じた信号を、前記第1のキャパシタの容量と前記第2のキャパシタの容量との比、及び前記第1のキャパシタと前記第2のキャパシタに印加した前記正弦波交流信号とに基づいて生成する第2の回路と、

前記第2の回路が生成した信号を符号化したデータを解析して、前記所定周波数と略同一の周波数成分の信号を前記データから抽出し、抽出した信号に基づいて前記加速度のデータを出力する演算回路と、を備える、

加速度センサ回路。

【請求項2】

前記第1の回路は、前記演算回路が生成した前記所定周波数の正弦波を変換したデジタル信号に基づいてアナログの前記正弦波交流信号を生成するDAコンバータを有する、

請求項1に記載の加速度センサ回路。

【請求項3】

前記第1の回路は、前記DAコンバータが生成した信号と同位相の正弦波交流信号を前記第1のキャパシタへ印加する非反転アンプと、前記DAコンバータが生成した信号と位相が反転する正弦波交流信号を前記第2のキャパシタへ印加する反転アンプと、を有する、

請求項2に記載の加速度センサ回路。

【請求項4】

前記演算回路は、前記非反転アンプから出力された前記第1のキャパシタへ印加される正弦波交流信号と、前記反転アンプから出力された前記第2のキャパシタへ印加される正弦波交流信号とに、所定の電圧を加算してオフセット調整を行なう、

請求項3に記載の加速度センサ回路。

【請求項1】

加速度に応じて容量が変化する第1のキャパシタと、前記加速度に応じて前記第1のキャパシタと相反するように容量が変化する第2のキャパシタとを有する加速度センサと、

前記第1のキャパシタと前記第2のキャパシタに互いに逆位相で印加する所定周波数の正弦波交流信号を生成する第1の回路と、

前記加速度に応じた信号を、前記第1のキャパシタの容量と前記第2のキャパシタの容量との比、及び前記第1のキャパシタと前記第2のキャパシタに印加した前記正弦波交流信号とに基づいて生成する第2の回路と、

前記第2の回路が生成した信号を符号化したデータを解析して、前記所定周波数と略同一の周波数成分の信号を前記データから抽出し、抽出した信号に基づいて前記加速度のデータを出力する演算回路と、を備える、

加速度センサ回路。

【請求項2】

前記第1の回路は、前記演算回路が生成した前記所定周波数の正弦波を変換したデジタル信号に基づいてアナログの前記正弦波交流信号を生成するDAコンバータを有する、

請求項1に記載の加速度センサ回路。

【請求項3】

前記第1の回路は、前記DAコンバータが生成した信号と同位相の正弦波交流信号を前記第1のキャパシタへ印加する非反転アンプと、前記DAコンバータが生成した信号と位相が反転する正弦波交流信号を前記第2のキャパシタへ印加する反転アンプと、を有する、

請求項2に記載の加速度センサ回路。

【請求項4】

前記演算回路は、前記非反転アンプから出力された前記第1のキャパシタへ印加される正弦波交流信号と、前記反転アンプから出力された前記第2のキャパシタへ印加される正弦波交流信号とに、所定の電圧を加算してオフセット調整を行なう、

請求項3に記載の加速度センサ回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−76610(P2013−76610A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−216051(P2011−216051)

【出願日】平成23年9月30日(2011.9.30)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成21年度 独立行政法人石油天然ガス・金属鉱物資源機構 油ガス層把握技術に関する共同研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000000516)曙ブレーキ工業株式会社 (621)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月30日(2011.9.30)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成21年度 独立行政法人石油天然ガス・金属鉱物資源機構 油ガス層把握技術に関する共同研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000000516)曙ブレーキ工業株式会社 (621)

[ Back to top ]