化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、化合物半導体装置及びその製造方法に関し、特に、移動体通信の基地局用高出力デバイスヘの利用が期待されているGaAs系MESFETを対象とする。

【0002】

【従来の技術】移動体通信の基地局用デバイスには高出力が要求され、これに見合う半導体デバイスとして、GaAs系MESFETが注目されている。このGaAs系MESFETを実用に供するには、パワー特性を向上させる必要があり、高耐圧化を図る様々な工夫がなされおり、その具体例としては、以下に示すような2種のものが案出されている。

【0003】(従来例1)図5は、従来例1のGaAs系MESFETの概略構成を示す断面図である。このMESFETは、いわゆるGaAs LD−MESFET(Lateral-Diffused Semiconductor Field-Effect Transistors)であって、Si LD−MOSFETの如き構造を採用しており、衝突イオン化によって生成される正孔をソース101側から引き抜く構成とされている。これにより、ドレイン102側におけるゲート103端での電界集中を抑制することが図られる(特開昭61−267369号公報参照)。

【0004】(従来例2)図6は、従来例2のGaAs系MESFETの概略構成を示す断面図である。このMESFETは、ゲート103とドレイン102との間に形成されたSiN等の絶縁膜104上に、Pt,Auを順次積層してなるフィールドプレート電極105を設け、このフィールドプレート電極105に負の電圧を印加し、空乏層を広げる構成とされている。これにより、ドレイン102側におけるゲート103端での電界集中を抑制し、衝突イオン化を抑えて高耐圧化を図る(Asano etal. Extended Abstracts of Solid State Device and Materials, Hiroshima,Japan, 1998, p.392参照)。

【0005】

【発明が解決しようとする課題】しかしながら、従来のGaAs系MESFETには以下に示すような問題がある。

【0006】従来例1の場合では、GaAs表面に高密度な表面準位が存在するため、アロイオーミックコンタクトを採用せざるを得ず、金属の拡散や異なるドーパント源(例えば、n−GaAsへはAuGe,p−GaAsへはAuZn)を用いる必要から、図7に示すように、p+層106とn+層107とを離間させて形成することを要する。このため、従来例1の場合、トランジスタサイズが大きくなり、高集積化という面で欠点があった。

【0007】また、特開昭61−267369号公報によれば、p+層106へはAuGeでもコンタクト可能であるとしているが、これはGeがドープされたn+層107とp+層106とのpn接合界面のトンネリングを利用しているため、コンタクト抵抗率が高くなり易く、問題である。

【0008】従来例2の場合では、SiN/GaAsの界面準位密度が高いため、空乏層を広げるために負の高電圧を印加しなければならない。このため、消費電力が高くなり、また、ドレイン電流やトランスコンダクタンスが減少するという問題がある。

【0009】ここで、界面準位密度を低減できる絶縁膜上にフィールドプレート電極を設置すれば、当該電極下でのチャネル層の変調を低電圧で行うことができ、消費電力を低減することができる。また、フィールドプレート電極から衝突イオン化により生成する正孔を引き抜くことができれば、これにより電界集中を抑制できることから従来ほど空乏層を広げる必要が無く、従って必要な電力を低減し、ドレイン電流、トランスコンダクタンスの低下を抑制することが可能となる。ところが、図8に示すように、SiN/GaAsに設けられる従来のフィールドプレート電極の構造は、いわゆるタイプI構造であるため、正孔の引き抜きを行うことができないという問題がある。

【0010】このように、従来のGaAs系MESFETでは、様々な工夫により電界緩和を図り高耐圧化を実現しようとしているものの、デバイスサイズの増加や正孔の引き抜きの困難性等の深刻な問題を招来している。

【0011】そこで本発明は、上記した課題を解決すべくなされたものであり、電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置及びその製造方法を提供することを目的とする。

【0012】

【課題を解決するための手段】本発明者は、鋭意検討の結果、以下に示す発明の諸態様に想到した。

【0013】本発明は、第1の化合物半導体層上に第2の化合物半導体層が形成されてなる化合物半導体装置を対象とする。ここで、前記第2の化合物半導体層は、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層である。

【0014】この場合、具体的には、前記3属元素をGa,In,Alから選ばれた1種とすることが好適である。

【0015】更に、前記6属元素をS,Te,Seから選ばれた1種とすることが好ましい。

【0016】また、一具体例として、前記第1の化合物半導体層は、p型領域とn型領域とが隣接する構造を有しており、前記第2の化合物半導体層の前記p型領域上に相当する部位に形成された仕事関数の大きい第1の金属層と、前記第2の化合物半導体層の前記n型領域上に相当する部位に形成された仕事関数の小さい第2の金属層とを有してなる電極を備えるものであり、主に前記電極をソース電極として形成する。

【0017】また、他の具体例として、ゲート電極とドレイン電極との間における前記第2の化合物半導体層上に、フィールドプレート電極を備える。

【0018】更に本発明は、前記各構成の化合物半導体装置を製造する方法も対象とする。

【0019】

【発明の実施の形態】以下、本発明を適用した好適な諸実施形態について、図面を参照しながら詳細に説明する。

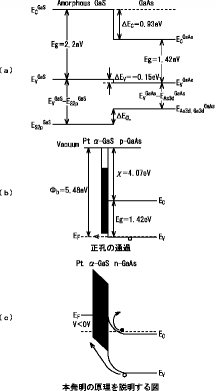

【0020】(本発明の主要原理)初めに、本発明の主要原理について説明する。本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層を有するものである。ここでは便宜上、前記アモルファス層としてアモルファスGaS層(a−GaS層)を例に採る。

【0021】例えば、ターシャリ・ブチル・ガリウム・サルファキュベン[(t−Bu)GaS]4を用いて、GaAs層上にa−GaS層を形成した場合、このGaS/GaAs構造は、図1(a)に示すようにタイプII構造となり、正孔に対する障壁がない。このため、図1R>1(b)に示すように、仕事関数の大きいPt等からなる電極を用いることでノンアロイでもGaAs層のp−GaAs領域とコンタクトを確保することが可能となる。従ってこの場合、GaAs層のp−GaAs領域とn−GaAs領域へ同時に(両者を離間させることなく)ノンアロイオーミックコンタクトが形成でき、トランジスタサイズ大幅な低減が可能となる。

【0022】一方、a−GaS層は、膜厚が20nm以上となると絶縁膜として機能する。図1(a)に示すように、伝導帯不連続△Ecは約1eVと高いので、電子に対してa−GaS層は障壁として機能するが、上述の如くタイプII構造が形成されているため、正孔に対しては障壁とならない。従ってこの場合、a−GaS層上にフィールドプレート電極を設け、当該電極に負の電圧に印加すれば、図1(c)のように空乏層を広げつつ、正孔を容易に引き抜くことが可能となる。

【0023】以下、上述した本発明の主要原理を踏まえ、各実施形態について具体的に詳述する。

【0024】(第1の実施形態)本実施形態では、化合物半導体装置としてノン・アロイ・オーミック型GaAs系LD−MESFETを例示する。ここでは便宜上、当該LD−MESFETの製造方法と共にその構成について開示する。

【0025】図2は、第1の実施形態によるノン・アロイ・オーミック型GaAs系LD−MESFETの製造方法を工程順に示す断面図である。このLD−MESFETを製造するには、先ず図2(a)に示すように、ノン・ドープのGaAs基板1を用意し、このGaAs基板1の表層に加速エネルギーを120keV、ドーズ量を5×1011/cm2の条件でMgをイオン注入した後、このイオン注入部位内の表層に加速エネルギーを40keV、ドーズ量を5×1012/cm2の条件でSiをイオン注入する。これにより、p−GaAs領域2及びn−GaAs領域3が順次形成される。

【0026】続いて、ゲート電極4を形成する。具体的には、スパッタ法によりタングステン・シリサイド(WSi)層(不図示)を堆積形成し、フォトリソグラフィー及びそれに続くドライエッチングによりWSi層を加工して、図2(b)に示すように、n−GaAs領域3上にゲート電極4をパターン形成する。

【0027】続いて、フォトレジストを塗布し、フォトリソグラフィーによりゲート電極4上を含むn−GaAs領域3上の所定領域を覆うレジストマスク(不図示)を形成する。そして、このレジストマスクを用い、図2(c)に示すように、露出したp−GaAs領域2及びn−GaAs領域3の表層(ここではオーミック領域となる部位)に、加速エネルギーを90keV、ドーズ量を2×1013/cm2の条件でSiをイオン注入した後、800℃の条件で10秒間のラピッド・サーマル・アニール(RTA)処理を施して活性化し、一対のn+−GaAs領域5を形成する。

【0028】このとき、所定のレジストマスクを形成し、ソース領域となる部位のみに、加速エネルギーを90keV、ドーズ量を2×1013/cm2の条件でMgをイオン注入するようにしても好適である。

【0029】その後、MBE(分子線エピタキシャル成長)チャンバー内でGaAs基板1の表面にトリスジメチルアミノ砒素を照射し、基板温度を500℃で表面の事前酸化膜を除去する。

【0030】続いて、図2(d)に示すように、MBEチャンバー内で基板温度を350℃として、GaAs基板1の表面に[(t−Bu)GaS]4を照射し、当該表面を覆うように膜厚15nm程度のa−GaS層6を形成する。このとき、図示の如くゲート電極4の表面を露出させておく。

【0031】続いて、ソース電極7及びドレイン電極8を形成する。具体的には、図2(e)に示すように、フォトリソグラフィーによりパターニングした後、Ti膜11,Pt膜12,Au膜13を蒸着リフトオフして、ソース領域及びドレイン領域となる部位、即ちa−GaS層6上の各n+−GaAs領域5上に相当する部位にTi膜11,Pt膜12,Au膜13を残す。

【0032】その後、300℃でGaAs基板1に10分間のアニール処理を施す。これにより、10-6Ω/cm2程度のコンタクト抵抗が得られ、ソース/ドレイン領域におけるn+−GaAs領域5とのオーミック・コンタクトがそれぞれ確保される。

【0033】続いて、図2(f)に示すように、フォトリソグラフィーによりパターニングした後、Pt膜14,Au膜15を蒸着リフトオフして、ソース領域側のみのTi膜11,Pt膜12,Au膜13からなる積層体上及び一方の側面を覆う形状となるようにPt膜14,Au膜15を残す。このとき、Pt膜14,Au膜15はa−GaS層6上ではp−GaAs領域2上に相当する部位のみに積層されており、これによりソース領域におけるp−GaAs領域2とのオーミック・コンタクトが確保される。

【0034】以上の工程により、ソース領域にはTi膜11,Pt膜12,Au膜13の積層体とPt膜14,Au膜15の積層体とが一体に接続されてなるソース電極7が、ドレイン領域にはTi膜11,Pt膜12,Au膜13の積層体からなるドレイン電極8がそれぞれ形成される。

【0035】しかる後、所定の層間絶縁膜やコンタクト孔の形成等の諸工程を経て、ノン・アロイ・オーミック型GaAs系LD−MESFETを完成させる。

【0036】上述のように、本実施形態のLD−MESFETにおいては、GaS/GaAs構造がタイプII構造となり、正孔に対する障壁がないため、p−GaAs領域2とのオーミック・コンタクトには仕事関数の大きいPt膜14を、n−GaAs領域(n+−GaAs領域5)とのオーミック・コンタクトには仕事関数の小さいTi膜11を用いて、Pt膜14とTi膜11を離間させることなく接触させてソース電極7を形成することができる。即ち、ソース領域におけるp−GaAs領域及びn−GaAs領域へのオーミック・コンタクトを安定に確保しつつも、トランジスタサイズの縮小化を実現して更なる高集積化の要請に十分応えることが可能となる。

【0037】(第2の実施形態)本実施形態では、化合物半導体装置として絶縁フィールドプレート型GaAs系MESFETを例示する。ここでは便宜上、当該MESFETの製造方法と共にその構成について開示する。

【0038】図3は、第2の実施形態による絶縁フィールドプレート型GaAs系MESFETの製造方法を工程順に示す断面図である。なお便宜上、図2と同様の構成部材等については同符号を記す。このLD−MESFETを製造するには、先ず図3(a)に示すように、ノン・ドープのGaAs基板1を用意し、このGaAs基板1の表層に加速エネルギーを40keV、ドーズ量を4×1012/cm2の条件でSiをイオン注入する。これにより、n−GaAs領域3が順次形成される。

【0039】続いて、ゲート電極4を形成する。具体的には、スパッタ法によりタングステン・シリサイド(WSi)層(不図示)を堆積形成し、フォトリソグラフィー及びそれに続くドライエッチングによりWSi層を加工して、図3(b)に示すように、n−GaAs領域3上にゲート電極4をパターン形成する。

【0040】続いて、フォトレジストを塗布し、フォトリソグラフィーによりゲート電極4上を含むn−GaAs領域3上の所定領域を覆うレジストマスク(不図示)を形成する。そして、このレジストマスクを用い、図2(c)に示すように、露出したn−GaAs領域3の表層(ここではオーミック領域となる部位)に、加速エネルギーを90keV、ドーズ量を2×1013/cm2の条件でSiをイオン注入した後、800℃の条件で10秒間のラピッド・サーマル・アニール(RTA)処理を施して活性化し、一対のn+−GaAs領域5を形成する。

【0041】その後、MBE(分子線エピタキシャル成長)チャンバー内でGaAs基板1の表面にトリスジメチルアミノ砒素を照射し、基板温度を500℃で表面の事前酸化膜を除去する。

【0042】続いて、図3(d)に示すように、MBEチャンバー内で基板温度を350℃として、GaAs基板1の表面に[(t−Bu)GaS]4を照射し、当該表面を覆うように、絶縁性を確保するために比較的厚く、ここでは膜厚30nm程度にa−GaS層21を形成する。このとき、図示の如くゲート電極4の表面を露出させておく。

【0043】続いて、ソース電極22及びドレイン電極23を形成する。具体的には、先ず図3(e)に示すように、a−GaS層21のソース領域及びドレイン領域に相当する部位に酸を用いてウェットエッチングを施し、当該部位におけるn+−GaAs領域5の表面を露出させる。

【0044】次に、各n+−GaAs領域5の前記露出部位に、AuGeNiを材料として蒸着し、当該AuGeNiを450℃でアロイ処理する。このとき、ソース領域及びドレイン領域における各n+−GaAs領域5とオーミック・コンタクトが確保されてなるソース電極22及びドレイン電極23が形成される。

【0045】続いて、ゲート電極4とドレイン電極23との間におけるa−GaS層21上に、フィールドプレート電極24を形成する。具体的には、Pt膜25,Au膜26を順次積層形成し、これらにフォトリソグラフィー及びそれに続くドライエッチングを施して、ゲート電極4とドレイン電極23との間のみにPt膜25,Au膜26を残し、フィールドプレート電極24を形成する。

【0046】しかる後、所定の層間絶縁膜やコンタクト孔の形成等の諸工程を経て、絶縁フィールドプレート型GaAs系MESFETを完成させる。

【0047】フィールドプレート電極24に負電圧Vを印加すると、空乏層を広げつつ、タイプII構造のために正孔のみを引き抜くことができる。また、正孔を引き抜けることから、従来と同じ耐圧で良ければ、従来ほど空乏層を広げる必要が無いため低電圧でコントロールでき、低消費電力化を実現できる。また、空乏層の広がりが少なければ、ドレイン電流やトランス・コンダクタンスを増加させることができる。

【0048】以上、本発明の各実施形態について説明したが、本発明はこれらの態様に限定されることなく、例えば、第1の実施形態のMESFETの構造と第2の実施形態のMESFETの構造とを組み合わせることも可能である。

【0049】この一例を図4に示す。ここでは、30nm程度の膜厚のa−GaS層21を形成し、ソース領域にはTi膜11,Pt膜12,Au膜13の積層体とPt膜14,Au膜15の積層体とを一体に接続されてなるソース電極7を、ドレイン領域にはTi膜11,Pt膜12,Au膜13の積層体からなるドレイン電極8をそれぞれ形成する。

【0050】この場合、p−GaAs領域2とのオーミック・コンタクトには仕事関数の大きいPt膜14を、n−GaAs領域(n+−GaAs領域5)とのオーミック・コンタクトには仕事関数の小さいTi膜11を用いて、Pt膜14とTi膜11を離間させることなく接触させてソース電極7が形成される。

【0051】更には、ゲート電極4とドレイン電極23との間におけるa−GaS層21上に、Pt膜25,Au膜26の積層体からなるフィールドプレート電極24を形成する。

【0052】本例によれば、第1及び第2の実施形態によるMESFETの奏する諸効果に加え、更なる高耐圧化を図ることができる。

【0053】以下、本発明の諸態様を付記としてまとめて記載する。

【0054】(付記1) 第1の化合物半導体層上に第2の化合物半導体層が形成されてなる化合物半導体装置であって、前記第2の化合物半導体層は、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層であることを特徴とする化合物半導体装置。

【0055】(付記2) 前記3属元素がGa,In,Alから選ばれた1種であることを特徴とする付記1に記載の化合物半導体装置。

【0056】(付記3) 前記6属元素がS,Te,Seから選ばれた1種であることを特徴とする付記1又は2に記載の化合物半導体装置。

【0057】(付記4) 前記第1の化合物半導体層は、p型領域とn型領域とが隣接する構造を有しており、前記第2の化合物半導体層の前記p型領域上に相当する部位に形成された仕事関数の大きい第1の金属層と、前記第2の化合物半導体層の前記n型領域上に相当する部位に形成された仕事関数の小さい第2の金属層とを有してなる電極を備えることを特徴とする付記1〜3のいずれか1項に記載の化合物半導体装置。

【0058】(付記5) 前記電極がソース電極であることを特徴とする付記4に記載の化合物半導体装置。

【0059】(付記6) ゲート電極とドレイン電極との間における前記第2の化合物半導体層上に、フィールドプレート電極を備えることを特徴とする付記1,2,3,5のいずれか1項に記載の化合物半導体装置。

【0060】(付記7) 第1の化合物半導体層上に第2の化合物半導体層を形成する化合物半導体装置の製造方法であって、前記第2の化合物半導体層を、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層とすることを特徴とする化合物半導体装置の製造方法。

【0061】(付記8) 前記3属元素をGa,In,Alから選ばれた1種とすることを特徴とする付記7に記載の化合物半導体装置の製造方法。

【0062】(付記9) 前記6属元素をS,Te,Seから選ばれた1種とすることを特徴とする付記7又は8に記載の化合物半導体装置の製造方法。

【0063】(付記10) 前記第1の化合物半導体層を、p型領域とn型領域とが隣接する構造を有するように形成するに際して、前記第2の化合物半導体層の前記p型領域上に相当する部位に仕事関数の大きい第1の金属層を、前記第2の化合物半導体層の前記n型領域上に相当する部位に仕事関数の小さい第2の金属層とを形成し、前記第1及び第2の金属層を有してなる電極を構成することを特徴とする付記7〜9のいずれか1項に記載の化合物半導体装置の製造方法。

【0064】(付記11) 前記電極をソース電極とすることを特徴とする付記10に記載の化合物半導体装置の製造方法。

【0065】(付記12) ゲート電極とドレイン電極との間における前記第2の化合物半導体層上に、フィールドプレート電極を形成することを特徴とする付記7,8,9,11のいずれか1項に記載の化合物半導体装置の製造方法。

【0066】

【発明の効果】本発明によれば、電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置が実現する。

【図面の簡単な説明】

【図1】本発明の主要原理を説明するためのバンド図である。

【図2】第1の実施形態によるノン・アロイ・オーミック型GaAs系LD−MESFETの製造方法を工程順に示す断面図である。

【図3】第2の実施形態による絶縁フィールドプレート型GaAs系MESFETの製造方法を工程順に示す断面図である。

【図4】第1の実施形態のMESFETの構造と第2の実施形態のMESFETの構造とを組み合わせた一例を示す断面図である。

【図5】従来例1のGaAs系MESFETの概略構成を示す断面図である。

【図6】従来例2のGaAs系MESFETの概略構成を示す断面図である。

【図7】従来例1のGaAs系MESFETにおいて、p+層とn+層とを離間させて形成した様子を示す断面図である。

【図8】従来例2のGaAs系MESFETの問題点を説明するためのバンド図である。

【符号の説明】

1 GaAs基板

2 p−GaAs領域

3 n−GaAs領域

4 ゲート電極

5 n+−GaAs領域

6,21 a−GaS層

7,22 ソース電極

8,23 ドレイン電極

11 Ti膜

12,14,25 Pt膜

13,15,26 Au膜

24 フィールドプレート電極

【0001】

【発明の属する技術分野】本発明は、化合物半導体装置及びその製造方法に関し、特に、移動体通信の基地局用高出力デバイスヘの利用が期待されているGaAs系MESFETを対象とする。

【0002】

【従来の技術】移動体通信の基地局用デバイスには高出力が要求され、これに見合う半導体デバイスとして、GaAs系MESFETが注目されている。このGaAs系MESFETを実用に供するには、パワー特性を向上させる必要があり、高耐圧化を図る様々な工夫がなされおり、その具体例としては、以下に示すような2種のものが案出されている。

【0003】(従来例1)図5は、従来例1のGaAs系MESFETの概略構成を示す断面図である。このMESFETは、いわゆるGaAs LD−MESFET(Lateral-Diffused Semiconductor Field-Effect Transistors)であって、Si LD−MOSFETの如き構造を採用しており、衝突イオン化によって生成される正孔をソース101側から引き抜く構成とされている。これにより、ドレイン102側におけるゲート103端での電界集中を抑制することが図られる(特開昭61−267369号公報参照)。

【0004】(従来例2)図6は、従来例2のGaAs系MESFETの概略構成を示す断面図である。このMESFETは、ゲート103とドレイン102との間に形成されたSiN等の絶縁膜104上に、Pt,Auを順次積層してなるフィールドプレート電極105を設け、このフィールドプレート電極105に負の電圧を印加し、空乏層を広げる構成とされている。これにより、ドレイン102側におけるゲート103端での電界集中を抑制し、衝突イオン化を抑えて高耐圧化を図る(Asano etal. Extended Abstracts of Solid State Device and Materials, Hiroshima,Japan, 1998, p.392参照)。

【0005】

【発明が解決しようとする課題】しかしながら、従来のGaAs系MESFETには以下に示すような問題がある。

【0006】従来例1の場合では、GaAs表面に高密度な表面準位が存在するため、アロイオーミックコンタクトを採用せざるを得ず、金属の拡散や異なるドーパント源(例えば、n−GaAsへはAuGe,p−GaAsへはAuZn)を用いる必要から、図7に示すように、p+層106とn+層107とを離間させて形成することを要する。このため、従来例1の場合、トランジスタサイズが大きくなり、高集積化という面で欠点があった。

【0007】また、特開昭61−267369号公報によれば、p+層106へはAuGeでもコンタクト可能であるとしているが、これはGeがドープされたn+層107とp+層106とのpn接合界面のトンネリングを利用しているため、コンタクト抵抗率が高くなり易く、問題である。

【0008】従来例2の場合では、SiN/GaAsの界面準位密度が高いため、空乏層を広げるために負の高電圧を印加しなければならない。このため、消費電力が高くなり、また、ドレイン電流やトランスコンダクタンスが減少するという問題がある。

【0009】ここで、界面準位密度を低減できる絶縁膜上にフィールドプレート電極を設置すれば、当該電極下でのチャネル層の変調を低電圧で行うことができ、消費電力を低減することができる。また、フィールドプレート電極から衝突イオン化により生成する正孔を引き抜くことができれば、これにより電界集中を抑制できることから従来ほど空乏層を広げる必要が無く、従って必要な電力を低減し、ドレイン電流、トランスコンダクタンスの低下を抑制することが可能となる。ところが、図8に示すように、SiN/GaAsに設けられる従来のフィールドプレート電極の構造は、いわゆるタイプI構造であるため、正孔の引き抜きを行うことができないという問題がある。

【0010】このように、従来のGaAs系MESFETでは、様々な工夫により電界緩和を図り高耐圧化を実現しようとしているものの、デバイスサイズの増加や正孔の引き抜きの困難性等の深刻な問題を招来している。

【0011】そこで本発明は、上記した課題を解決すべくなされたものであり、電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置及びその製造方法を提供することを目的とする。

【0012】

【課題を解決するための手段】本発明者は、鋭意検討の結果、以下に示す発明の諸態様に想到した。

【0013】本発明は、第1の化合物半導体層上に第2の化合物半導体層が形成されてなる化合物半導体装置を対象とする。ここで、前記第2の化合物半導体層は、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層である。

【0014】この場合、具体的には、前記3属元素をGa,In,Alから選ばれた1種とすることが好適である。

【0015】更に、前記6属元素をS,Te,Seから選ばれた1種とすることが好ましい。

【0016】また、一具体例として、前記第1の化合物半導体層は、p型領域とn型領域とが隣接する構造を有しており、前記第2の化合物半導体層の前記p型領域上に相当する部位に形成された仕事関数の大きい第1の金属層と、前記第2の化合物半導体層の前記n型領域上に相当する部位に形成された仕事関数の小さい第2の金属層とを有してなる電極を備えるものであり、主に前記電極をソース電極として形成する。

【0017】また、他の具体例として、ゲート電極とドレイン電極との間における前記第2の化合物半導体層上に、フィールドプレート電極を備える。

【0018】更に本発明は、前記各構成の化合物半導体装置を製造する方法も対象とする。

【0019】

【発明の実施の形態】以下、本発明を適用した好適な諸実施形態について、図面を参照しながら詳細に説明する。

【0020】(本発明の主要原理)初めに、本発明の主要原理について説明する。本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層を有するものである。ここでは便宜上、前記アモルファス層としてアモルファスGaS層(a−GaS層)を例に採る。

【0021】例えば、ターシャリ・ブチル・ガリウム・サルファキュベン[(t−Bu)GaS]4を用いて、GaAs層上にa−GaS層を形成した場合、このGaS/GaAs構造は、図1(a)に示すようにタイプII構造となり、正孔に対する障壁がない。このため、図1R>1(b)に示すように、仕事関数の大きいPt等からなる電極を用いることでノンアロイでもGaAs層のp−GaAs領域とコンタクトを確保することが可能となる。従ってこの場合、GaAs層のp−GaAs領域とn−GaAs領域へ同時に(両者を離間させることなく)ノンアロイオーミックコンタクトが形成でき、トランジスタサイズ大幅な低減が可能となる。

【0022】一方、a−GaS層は、膜厚が20nm以上となると絶縁膜として機能する。図1(a)に示すように、伝導帯不連続△Ecは約1eVと高いので、電子に対してa−GaS層は障壁として機能するが、上述の如くタイプII構造が形成されているため、正孔に対しては障壁とならない。従ってこの場合、a−GaS層上にフィールドプレート電極を設け、当該電極に負の電圧に印加すれば、図1(c)のように空乏層を広げつつ、正孔を容易に引き抜くことが可能となる。

【0023】以下、上述した本発明の主要原理を踏まえ、各実施形態について具体的に詳述する。

【0024】(第1の実施形態)本実施形態では、化合物半導体装置としてノン・アロイ・オーミック型GaAs系LD−MESFETを例示する。ここでは便宜上、当該LD−MESFETの製造方法と共にその構成について開示する。

【0025】図2は、第1の実施形態によるノン・アロイ・オーミック型GaAs系LD−MESFETの製造方法を工程順に示す断面図である。このLD−MESFETを製造するには、先ず図2(a)に示すように、ノン・ドープのGaAs基板1を用意し、このGaAs基板1の表層に加速エネルギーを120keV、ドーズ量を5×1011/cm2の条件でMgをイオン注入した後、このイオン注入部位内の表層に加速エネルギーを40keV、ドーズ量を5×1012/cm2の条件でSiをイオン注入する。これにより、p−GaAs領域2及びn−GaAs領域3が順次形成される。

【0026】続いて、ゲート電極4を形成する。具体的には、スパッタ法によりタングステン・シリサイド(WSi)層(不図示)を堆積形成し、フォトリソグラフィー及びそれに続くドライエッチングによりWSi層を加工して、図2(b)に示すように、n−GaAs領域3上にゲート電極4をパターン形成する。

【0027】続いて、フォトレジストを塗布し、フォトリソグラフィーによりゲート電極4上を含むn−GaAs領域3上の所定領域を覆うレジストマスク(不図示)を形成する。そして、このレジストマスクを用い、図2(c)に示すように、露出したp−GaAs領域2及びn−GaAs領域3の表層(ここではオーミック領域となる部位)に、加速エネルギーを90keV、ドーズ量を2×1013/cm2の条件でSiをイオン注入した後、800℃の条件で10秒間のラピッド・サーマル・アニール(RTA)処理を施して活性化し、一対のn+−GaAs領域5を形成する。

【0028】このとき、所定のレジストマスクを形成し、ソース領域となる部位のみに、加速エネルギーを90keV、ドーズ量を2×1013/cm2の条件でMgをイオン注入するようにしても好適である。

【0029】その後、MBE(分子線エピタキシャル成長)チャンバー内でGaAs基板1の表面にトリスジメチルアミノ砒素を照射し、基板温度を500℃で表面の事前酸化膜を除去する。

【0030】続いて、図2(d)に示すように、MBEチャンバー内で基板温度を350℃として、GaAs基板1の表面に[(t−Bu)GaS]4を照射し、当該表面を覆うように膜厚15nm程度のa−GaS層6を形成する。このとき、図示の如くゲート電極4の表面を露出させておく。

【0031】続いて、ソース電極7及びドレイン電極8を形成する。具体的には、図2(e)に示すように、フォトリソグラフィーによりパターニングした後、Ti膜11,Pt膜12,Au膜13を蒸着リフトオフして、ソース領域及びドレイン領域となる部位、即ちa−GaS層6上の各n+−GaAs領域5上に相当する部位にTi膜11,Pt膜12,Au膜13を残す。

【0032】その後、300℃でGaAs基板1に10分間のアニール処理を施す。これにより、10-6Ω/cm2程度のコンタクト抵抗が得られ、ソース/ドレイン領域におけるn+−GaAs領域5とのオーミック・コンタクトがそれぞれ確保される。

【0033】続いて、図2(f)に示すように、フォトリソグラフィーによりパターニングした後、Pt膜14,Au膜15を蒸着リフトオフして、ソース領域側のみのTi膜11,Pt膜12,Au膜13からなる積層体上及び一方の側面を覆う形状となるようにPt膜14,Au膜15を残す。このとき、Pt膜14,Au膜15はa−GaS層6上ではp−GaAs領域2上に相当する部位のみに積層されており、これによりソース領域におけるp−GaAs領域2とのオーミック・コンタクトが確保される。

【0034】以上の工程により、ソース領域にはTi膜11,Pt膜12,Au膜13の積層体とPt膜14,Au膜15の積層体とが一体に接続されてなるソース電極7が、ドレイン領域にはTi膜11,Pt膜12,Au膜13の積層体からなるドレイン電極8がそれぞれ形成される。

【0035】しかる後、所定の層間絶縁膜やコンタクト孔の形成等の諸工程を経て、ノン・アロイ・オーミック型GaAs系LD−MESFETを完成させる。

【0036】上述のように、本実施形態のLD−MESFETにおいては、GaS/GaAs構造がタイプII構造となり、正孔に対する障壁がないため、p−GaAs領域2とのオーミック・コンタクトには仕事関数の大きいPt膜14を、n−GaAs領域(n+−GaAs領域5)とのオーミック・コンタクトには仕事関数の小さいTi膜11を用いて、Pt膜14とTi膜11を離間させることなく接触させてソース電極7を形成することができる。即ち、ソース領域におけるp−GaAs領域及びn−GaAs領域へのオーミック・コンタクトを安定に確保しつつも、トランジスタサイズの縮小化を実現して更なる高集積化の要請に十分応えることが可能となる。

【0037】(第2の実施形態)本実施形態では、化合物半導体装置として絶縁フィールドプレート型GaAs系MESFETを例示する。ここでは便宜上、当該MESFETの製造方法と共にその構成について開示する。

【0038】図3は、第2の実施形態による絶縁フィールドプレート型GaAs系MESFETの製造方法を工程順に示す断面図である。なお便宜上、図2と同様の構成部材等については同符号を記す。このLD−MESFETを製造するには、先ず図3(a)に示すように、ノン・ドープのGaAs基板1を用意し、このGaAs基板1の表層に加速エネルギーを40keV、ドーズ量を4×1012/cm2の条件でSiをイオン注入する。これにより、n−GaAs領域3が順次形成される。

【0039】続いて、ゲート電極4を形成する。具体的には、スパッタ法によりタングステン・シリサイド(WSi)層(不図示)を堆積形成し、フォトリソグラフィー及びそれに続くドライエッチングによりWSi層を加工して、図3(b)に示すように、n−GaAs領域3上にゲート電極4をパターン形成する。

【0040】続いて、フォトレジストを塗布し、フォトリソグラフィーによりゲート電極4上を含むn−GaAs領域3上の所定領域を覆うレジストマスク(不図示)を形成する。そして、このレジストマスクを用い、図2(c)に示すように、露出したn−GaAs領域3の表層(ここではオーミック領域となる部位)に、加速エネルギーを90keV、ドーズ量を2×1013/cm2の条件でSiをイオン注入した後、800℃の条件で10秒間のラピッド・サーマル・アニール(RTA)処理を施して活性化し、一対のn+−GaAs領域5を形成する。

【0041】その後、MBE(分子線エピタキシャル成長)チャンバー内でGaAs基板1の表面にトリスジメチルアミノ砒素を照射し、基板温度を500℃で表面の事前酸化膜を除去する。

【0042】続いて、図3(d)に示すように、MBEチャンバー内で基板温度を350℃として、GaAs基板1の表面に[(t−Bu)GaS]4を照射し、当該表面を覆うように、絶縁性を確保するために比較的厚く、ここでは膜厚30nm程度にa−GaS層21を形成する。このとき、図示の如くゲート電極4の表面を露出させておく。

【0043】続いて、ソース電極22及びドレイン電極23を形成する。具体的には、先ず図3(e)に示すように、a−GaS層21のソース領域及びドレイン領域に相当する部位に酸を用いてウェットエッチングを施し、当該部位におけるn+−GaAs領域5の表面を露出させる。

【0044】次に、各n+−GaAs領域5の前記露出部位に、AuGeNiを材料として蒸着し、当該AuGeNiを450℃でアロイ処理する。このとき、ソース領域及びドレイン領域における各n+−GaAs領域5とオーミック・コンタクトが確保されてなるソース電極22及びドレイン電極23が形成される。

【0045】続いて、ゲート電極4とドレイン電極23との間におけるa−GaS層21上に、フィールドプレート電極24を形成する。具体的には、Pt膜25,Au膜26を順次積層形成し、これらにフォトリソグラフィー及びそれに続くドライエッチングを施して、ゲート電極4とドレイン電極23との間のみにPt膜25,Au膜26を残し、フィールドプレート電極24を形成する。

【0046】しかる後、所定の層間絶縁膜やコンタクト孔の形成等の諸工程を経て、絶縁フィールドプレート型GaAs系MESFETを完成させる。

【0047】フィールドプレート電極24に負電圧Vを印加すると、空乏層を広げつつ、タイプII構造のために正孔のみを引き抜くことができる。また、正孔を引き抜けることから、従来と同じ耐圧で良ければ、従来ほど空乏層を広げる必要が無いため低電圧でコントロールでき、低消費電力化を実現できる。また、空乏層の広がりが少なければ、ドレイン電流やトランス・コンダクタンスを増加させることができる。

【0048】以上、本発明の各実施形態について説明したが、本発明はこれらの態様に限定されることなく、例えば、第1の実施形態のMESFETの構造と第2の実施形態のMESFETの構造とを組み合わせることも可能である。

【0049】この一例を図4に示す。ここでは、30nm程度の膜厚のa−GaS層21を形成し、ソース領域にはTi膜11,Pt膜12,Au膜13の積層体とPt膜14,Au膜15の積層体とを一体に接続されてなるソース電極7を、ドレイン領域にはTi膜11,Pt膜12,Au膜13の積層体からなるドレイン電極8をそれぞれ形成する。

【0050】この場合、p−GaAs領域2とのオーミック・コンタクトには仕事関数の大きいPt膜14を、n−GaAs領域(n+−GaAs領域5)とのオーミック・コンタクトには仕事関数の小さいTi膜11を用いて、Pt膜14とTi膜11を離間させることなく接触させてソース電極7が形成される。

【0051】更には、ゲート電極4とドレイン電極23との間におけるa−GaS層21上に、Pt膜25,Au膜26の積層体からなるフィールドプレート電極24を形成する。

【0052】本例によれば、第1及び第2の実施形態によるMESFETの奏する諸効果に加え、更なる高耐圧化を図ることができる。

【0053】以下、本発明の諸態様を付記としてまとめて記載する。

【0054】(付記1) 第1の化合物半導体層上に第2の化合物半導体層が形成されてなる化合物半導体装置であって、前記第2の化合物半導体層は、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層であることを特徴とする化合物半導体装置。

【0055】(付記2) 前記3属元素がGa,In,Alから選ばれた1種であることを特徴とする付記1に記載の化合物半導体装置。

【0056】(付記3) 前記6属元素がS,Te,Seから選ばれた1種であることを特徴とする付記1又は2に記載の化合物半導体装置。

【0057】(付記4) 前記第1の化合物半導体層は、p型領域とn型領域とが隣接する構造を有しており、前記第2の化合物半導体層の前記p型領域上に相当する部位に形成された仕事関数の大きい第1の金属層と、前記第2の化合物半導体層の前記n型領域上に相当する部位に形成された仕事関数の小さい第2の金属層とを有してなる電極を備えることを特徴とする付記1〜3のいずれか1項に記載の化合物半導体装置。

【0058】(付記5) 前記電極がソース電極であることを特徴とする付記4に記載の化合物半導体装置。

【0059】(付記6) ゲート電極とドレイン電極との間における前記第2の化合物半導体層上に、フィールドプレート電極を備えることを特徴とする付記1,2,3,5のいずれか1項に記載の化合物半導体装置。

【0060】(付記7) 第1の化合物半導体層上に第2の化合物半導体層を形成する化合物半導体装置の製造方法であって、前記第2の化合物半導体層を、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層とすることを特徴とする化合物半導体装置の製造方法。

【0061】(付記8) 前記3属元素をGa,In,Alから選ばれた1種とすることを特徴とする付記7に記載の化合物半導体装置の製造方法。

【0062】(付記9) 前記6属元素をS,Te,Seから選ばれた1種とすることを特徴とする付記7又は8に記載の化合物半導体装置の製造方法。

【0063】(付記10) 前記第1の化合物半導体層を、p型領域とn型領域とが隣接する構造を有するように形成するに際して、前記第2の化合物半導体層の前記p型領域上に相当する部位に仕事関数の大きい第1の金属層を、前記第2の化合物半導体層の前記n型領域上に相当する部位に仕事関数の小さい第2の金属層とを形成し、前記第1及び第2の金属層を有してなる電極を構成することを特徴とする付記7〜9のいずれか1項に記載の化合物半導体装置の製造方法。

【0064】(付記11) 前記電極をソース電極とすることを特徴とする付記10に記載の化合物半導体装置の製造方法。

【0065】(付記12) ゲート電極とドレイン電極との間における前記第2の化合物半導体層上に、フィールドプレート電極を形成することを特徴とする付記7,8,9,11のいずれか1項に記載の化合物半導体装置の製造方法。

【0066】

【発明の効果】本発明によれば、電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置が実現する。

【図面の簡単な説明】

【図1】本発明の主要原理を説明するためのバンド図である。

【図2】第1の実施形態によるノン・アロイ・オーミック型GaAs系LD−MESFETの製造方法を工程順に示す断面図である。

【図3】第2の実施形態による絶縁フィールドプレート型GaAs系MESFETの製造方法を工程順に示す断面図である。

【図4】第1の実施形態のMESFETの構造と第2の実施形態のMESFETの構造とを組み合わせた一例を示す断面図である。

【図5】従来例1のGaAs系MESFETの概略構成を示す断面図である。

【図6】従来例2のGaAs系MESFETの概略構成を示す断面図である。

【図7】従来例1のGaAs系MESFETにおいて、p+層とn+層とを離間させて形成した様子を示す断面図である。

【図8】従来例2のGaAs系MESFETの問題点を説明するためのバンド図である。

【符号の説明】

1 GaAs基板

2 p−GaAs領域

3 n−GaAs領域

4 ゲート電極

5 n+−GaAs領域

6,21 a−GaS層

7,22 ソース電極

8,23 ドレイン電極

11 Ti膜

12,14,25 Pt膜

13,15,26 Au膜

24 フィールドプレート電極

【特許請求の範囲】

【請求項1】 第1の化合物半導体層上に第2の化合物半導体層が形成されてなる化合物半導体装置であって、前記第2の化合物半導体層は、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層であることを特徴とする化合物半導体装置。

【請求項2】 前記3属元素がGa,In,Alから選ばれた1種であることを特徴とする請求項1に記載の化合物半導体装置。

【請求項3】 前記6属元素がS,Te,Seから選ばれた1種であることを特徴とする請求項1又は2に記載の化合物半導体装置。

【請求項4】 前記第1の化合物半導体層は、p型領域とn型領域とが隣接する構造を有しており、前記第2の化合物半導体層の前記p型領域上に相当する部位に形成された仕事関数の大きい第1の金属層と、前記第2の化合物半導体層の前記n型領域上に相当する部位に形成された仕事関数の小さい第2の金属層とを有してなる電極を備えることを特徴とする請求項1〜3のいずれか1項に記載の化合物半導体装置。

【請求項5】 前記電極がソース電極であることを特徴とする請求項4に記載の化合物半導体装置。

【請求項6】 ゲート電極とドレイン電極との間における前記第2の化合物半導体層上に、フィールドプレート電極を備えることを特徴とする請求項1,2,3,5のいずれか1項に記載の化合物半導体装置。

【請求項7】 第1の化合物半導体層上に第2の化合物半導体層を形成する化合物半導体装置の製造方法であって、前記第2の化合物半導体層を、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層とすることを特徴とする化合物半導体装置の製造方法。

【請求項8】 前記3属元素をGa,In,Alから選ばれた1種とすることを特徴とする請求項7に記載の化合物半導体装置の製造方法。

【請求項9】 前記6属元素をS,Te,Seから選ばれた1種とすることを特徴とする請求項7又は8に記載の化合物半導体装置の製造方法。

【請求項10】 前記第1の化合物半導体層を、p型領域とn型領域とが隣接する構造を有するように形成するに際して、前記第2の化合物半導体層の前記p型領域上に相当する部位に仕事関数の大きい第1の金属層を、前記第2の化合物半導体層の前記n型領域上に相当する部位に仕事関数の小さい第2の金属層とを形成し、前記第1及び第2の金属層を有してなる電極を構成することを特徴とする請求項7〜9のいずれか1項に記載の化合物半導体装置の製造方法。

【請求項1】 第1の化合物半導体層上に第2の化合物半導体層が形成されてなる化合物半導体装置であって、前記第2の化合物半導体層は、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層であることを特徴とする化合物半導体装置。

【請求項2】 前記3属元素がGa,In,Alから選ばれた1種であることを特徴とする請求項1に記載の化合物半導体装置。

【請求項3】 前記6属元素がS,Te,Seから選ばれた1種であることを特徴とする請求項1又は2に記載の化合物半導体装置。

【請求項4】 前記第1の化合物半導体層は、p型領域とn型領域とが隣接する構造を有しており、前記第2の化合物半導体層の前記p型領域上に相当する部位に形成された仕事関数の大きい第1の金属層と、前記第2の化合物半導体層の前記n型領域上に相当する部位に形成された仕事関数の小さい第2の金属層とを有してなる電極を備えることを特徴とする請求項1〜3のいずれか1項に記載の化合物半導体装置。

【請求項5】 前記電極がソース電極であることを特徴とする請求項4に記載の化合物半導体装置。

【請求項6】 ゲート電極とドレイン電極との間における前記第2の化合物半導体層上に、フィールドプレート電極を備えることを特徴とする請求項1,2,3,5のいずれか1項に記載の化合物半導体装置。

【請求項7】 第1の化合物半導体層上に第2の化合物半導体層を形成する化合物半導体装置の製造方法であって、前記第2の化合物半導体層を、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にないバンド構造を有する、3属元素と6属元素の化合物からなるアモルファス層とすることを特徴とする化合物半導体装置の製造方法。

【請求項8】 前記3属元素をGa,In,Alから選ばれた1種とすることを特徴とする請求項7に記載の化合物半導体装置の製造方法。

【請求項9】 前記6属元素をS,Te,Seから選ばれた1種とすることを特徴とする請求項7又は8に記載の化合物半導体装置の製造方法。

【請求項10】 前記第1の化合物半導体層を、p型領域とn型領域とが隣接する構造を有するように形成するに際して、前記第2の化合物半導体層の前記p型領域上に相当する部位に仕事関数の大きい第1の金属層を、前記第2の化合物半導体層の前記n型領域上に相当する部位に仕事関数の小さい第2の金属層とを形成し、前記第1及び第2の金属層を有してなる電極を構成することを特徴とする請求項7〜9のいずれか1項に記載の化合物半導体装置の製造方法。

【図1】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2002−231733(P2002−231733A)

【公開日】平成14年8月16日(2002.8.16)

【国際特許分類】

【出願番号】特願2001−27251(P2001−27251)

【出願日】平成13年2月2日(2001.2.2)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成14年8月16日(2002.8.16)

【国際特許分類】

【出願日】平成13年2月2日(2001.2.2)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]