化合物半導体装置及びその製造方法

【課題】第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置を得る。

【解決手段】第1の極性を有する電子走行層2bと、電子走行層2bの上方に形成された第2の極性を有するp型キャップ層2eと、p型キャップ層2e上に形成された第1の極性を有するn型キャップ層2fとを有しており、n型キャップ層2fは、厚みの異なる部位2fa,2fbを有する。

【解決手段】第1の極性を有する電子走行層2bと、電子走行層2bの上方に形成された第2の極性を有するp型キャップ層2eと、p型キャップ層2e上に形成された第1の極性を有するn型キャップ層2fとを有しており、n型キャップ層2fは、厚みの異なる部位2fa,2fbを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、化合物半導体装置及びその製造方法に関する。

【背景技術】

【0002】

窒化物半導体は、高い飽和電子速度及びワイドバンドギャップ等の特徴を利用し、高耐圧及び高出力の半導体デバイスへの適用が検討されている。例えば、窒化物半導体であるGaNのバンドギャップは3.4eVであり、Siのバンドギャップ(1.1eV)及びGaAsのバンドギャップ(1.4eV)よりも大きく、高い破壊電界強度を有する。そのためGaNは、高電圧動作且つ高出力を得る電源用の半導体デバイスの材料として極めて有望である。

【0003】

窒化物半導体を用いたデバイスとしては、電界効果トランジスタ、特に高電子移動度トランジスタ(High Electron Mobility Transistor:HEMT)についての報告が数多くなされている。例えばGaN系のHEMT(GaN−HEMT)では、GaNを電子走行層として、AlGaNを電子供給層として用いたAlGaN/GaN・HEMTが注目されている。AlGaN/GaN・HEMTでは、GaNとAlGaNとの格子定数差に起因した歪みがAlGaNに生じる。これにより発生したピエゾ分極及びAlGaNの自発分極により、高濃度の2次元電子ガス(2DEG)が得られる。そのため、高効率のスイッチ素子、電気自動車用等の高耐圧電力デバイスとして期待されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−220895号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

窒化物半導体デバイスでは、2DEGの発生量を局所的に制御する技術が要求されている。例えばHEMTの場合には、いわゆるフェイルセーフの観点から、電圧のオフ時には電流が流れない、所謂ノーマリオフ動作が望まれる。そのためには、電圧のオフ時においてゲート電極の下方における2DEGの発生量を抑える工夫が必要である。

ノーマリオフ動作のGaN・HEMTを実現するための手法の一つとして、p型GaN層を電子供給層上に形成し、バンド変調効果により2DEGの濃度を制御する手法が提案されている。

【0006】

しかしながら、GaNは、技術的な歴史の長いSiと比較して製造技術が未熟な材料であるため、p型GaNの構造を最適化することが困難である。例えば、Siでは高度なイオン打ち込み技術を用いて、縦方向に長くp型イオン打ち込み層があるスーパージャンクション構造を作製することが可能であるが、GaNではイオン打ち込み技術自体が未完成である。

その一方で、RF分野ではGaN−HEMTは既に実用化されており、イオン打ち込み技術等の製造技術が成熟し、Siのデバイス構造を使用できるのを待つことなく、上記の問題を解決する半導体市場からの強い要請がある。

【0007】

本発明は、上記の課題に鑑みてなされたものであり、第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

化合物半導体装置の一態様は、第1の極性を有する第1の化合物半導体層と、前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層とを含み、前記第3の化合物半導体層は、厚みの異なる部位を有する。

【0009】

化合物半導体装置の製造方法の一態様は、第1の極性を有する第1の化合物半導体層を形成する工程と、前記第1の半導体層の上方に、第2の極性を有する第2の化合物半導体層を形成する工程と、前記第2の半導体層の上方に、第2の極性を有する第3の化合物半導体層を形成する工程と、前記第3の化合物半導体層に、厚みの異なる部位を形成する工程とを含む。

【発明の効果】

【0010】

上記の各態様によれば、第1の極性を有する第1の化合物半導体層と共にこれと逆導電型(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置が実現する。

【図面の簡単な説明】

【0011】

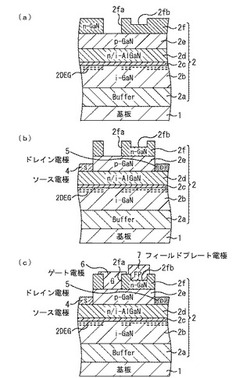

【図1】第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図2】図1に引き続き、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図3】図2に引き続き、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図4】第1の実施形態によるAlGaN/GaN・HEMTの構成を示す概略平面図である。

【図5】第1の実施形態において、ドレイン−ソース間電圧Vdsとドレイン電流Idとの関係について調べた結果を示す特性図である。

【図6】第1の実施形態において、ドレイン−ソース間電圧Vdsを印加し続け、破壊が起こるまでの時間について調べた結果を示す特性図である。

【図7】第1の実施形態において、非動作時における2DEGの濃度について調べた結果を示す特性図である。

【図8】第1の実施形態によるAlGaN/GaN・HEMTを用いたHEMTチップを示す概略平面図である。

【図9】第1の実施形態によるAlGaN/GaN・HEMTを用いたディスクリートパッケージを示す概略平面図である。

【図10】第2の実施形態によるAlGaN/GaN・ダイオードの製造方法の主要工程を示す概略断面図である。

【図11】図10に引き続き、第2の実施形態によるAlGaN/GaN・ダイオードの製造方法の主要工程を示す概略断面図である。

【図12】図11に引き続き、第2の実施形態によるAlGaN/GaN・ダイオードの製造方法の主要工程を示す概略断面図である。

【図13】第2の実施形態において、アノード−カソード間順電圧Vacとアノード電流Iaとの関係について調べた結果を示す特性図である。

【図14】アノード−カソード間に逆電圧を印加し続け、破壊が起こるまでの時間について調べた結果を示す特性図である。

【図15】第2の実施形態によるAlGaN/GaN・ダイオードを用いたダイオードチップを示す概略平面図である。

【図16】第2の実施形態によるAlGaN/GaN・ダイオードを用いたディスクリートパッケージを示す概略平面図である。

【図17】第3の実施形態によるPFC回路を示す結線図である。

【図18】第4の実施形態による電源装置の概略構成を示す結線図である。

【図19】第5の実施形態による高周波増幅器の概略構成を示す結線図である。

【発明を実施するための形態】

【0012】

以下、諸実施形態について図面を参照して詳細に説明する。以下の諸実施形態では、化合物半導体装置の構成について、その製造方法と共に説明する。

なお、以下の図面において、図示の便宜上、相対的に正確な大きさ及び厚みに示していない構成部材がある。

【0013】

(第1の実施形態)

本実施形態では、化合物半導体装置としてAlGaN/GaN・HEMTを開示する。

図1〜図3は、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【0014】

先ず、図1(a)に示すように、成長用基板として例えばSi基板1上に、化合物半導体積層構造2を形成する。成長用基板としては、Si基板の代わりに、サファイア基板、GaAs基板、SiC基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

【0015】

化合物半導体積層構造2は、バッファ層2a、電子走行層2b、中間層(スペーサ層)2c、電子供給層2d、p型キャップ層2e、及びn型キャップ層2fを有して構成される。ここで、電子走行層2bは、後述するように中間層2cとの界面に2次元電子ガスが発生する負の極性を有しており、同様にn型キャップ層2fも導電型がn型であるため負の極性を有する。これに対して、p型キャップ層2eは、導電型がn型と逆のp型であるため、正の極性を有する。

【0016】

詳細には、Si基板1上に、例えば有機金属気相成長(MOVPE:Metal Organic Vapor Phase Epitaxy)法により、以下の各化合物半導体を成長する。MOVPE法の代わりに、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法等を用いても良い。

Si基板1上に、バッファ層2a、電子走行層2b、中間層2c、電子供給層2d、p型キャップ層2e、及びn型キャップ層2fとなる各化合物半導体を順次成長する。バッファ層2aは、Si基板1上に、AlNを0.1μm程度の厚みに成長することで形成される。電子走行層2bは、i(インテンショナリ・アンドープ)−GaNを1μm程度〜3μm程度の厚みに成長することで形成される。中間層2cは、i−AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2dは、n−AlGaNを30nm程度の厚みに成長することで形成される。中間層2cは形成しない場合もある。電子供給層は、i−AlGaNを形成するようにしても良い。

【0017】

p型キャップ層2eは、p−GaNを、例えば10nm程度〜1000nm程度に成長することで形成される。10nmよりも薄いと、所期のノーマリオフ動作が得られなくなる。1000nmよりも厚いと、ゲート電極からチャネルであるAlGaN/GaNへテロ界面までの距離が長くなって応答速度が低下し、チャネルにおけるゲート電極からの電界が不十分になり、ピンチオフ不良等の劣化が惹起される。従って、p型キャップ層2eを10nm程度〜1000nm程度に形成することにより、十分なノーマリオフ動作を得るも、高速の応答速度を確保し、ピンチオフ不良等のデバイス特性の劣化を抑止することができる。本実施形態では、p型キャップ層2eのp−GaNは200nm程度の厚みに形成される。

n型キャップ層2fは、p型キャップ層2eとの関係で、n−GaNを例えば5nm程度〜500nm程度、ここでは100nm程度の厚みに成長することで形成される。

【0018】

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH3)ガスの混合ガスを用いる。AlGaNの成長には、原料ガスとしてTMAlガス、TMGaガス及びNH3ガスの混合ガスを用いる。成長する化合物半導体層に応じて、TMAlガス、TMGaガスの供給の有無及び流量を適宜設定する。共通原料であるNH3ガスの流量は、100sccm〜10slm程度とする。また、成長圧力は50Torr〜300Torr程度、成長温度は1000℃〜1200℃程度とする。

【0019】

AlGaN、GaNをn型として成長する際、即ち電子供給層2d(n−AlGaN)、n型キャップ層2f(n−GaN)の形成には、n型不純物をAlGaN、GaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン(SiH4)ガスを所定の流量で原料ガスに添加し、AlGaN、GaNにSiをドーピングする。Siのドーピング濃度は、1×1018/cm3程度〜1×1020/cm3程度、例えば2×1018/cm3程度とする。

【0020】

GaNをp型として成長する際、即ちp型キャップ層2e(p−GaN)の形成には、p型不純物、例えばMg,Cから選ばれたものをGaNの原料ガスに添加する。本実施形態では、p型不純物としてMgを用いる。Mgを所定の流量で原料ガスに添加し、GaNにMgをドーピングする。Mgのドーピング濃度は、例えば1×1016/cm3程度〜1×1021/cm3程度とする。ドーピング濃度が1×1016/cm3程度よりも低いと、十分なp型とならず、ノーマリオンとなる。1×1021/cm3程度よりも高いと、結晶性が崩れ、十分な特性が得られなくなる。従って、Mgのドーピング濃度を1×1016/cm3程度〜1×1021/cm3程度とすることにより、十分にノーマリオフ特性の得られるp型半導体となる。本実施形態では、p型キャップ層2eのMgのドーピング濃度を1×1019/cm3程度とする。

【0021】

形成された化合物半導体積層構造2では、負の極性を有する電子走行層2bの電子供給層2dとの界面(正確には、中間層2cとの界面。以下、GaN/AlGaN界面と記す。)には、GaNの格子定数とAlGaNの格子定数との差に起因した歪みによるピエゾ分極が生じる。このピエゾ分極の効果と、電子走行層2b及び電子供給層2dの自発分極の効果とが相俟って、GaN/AlGaN界面に高い電子濃度の2次元電子ガス(2DEG)が発生する。

【0022】

化合物半導体積層構造2を形成した後に、p型キャップ層2eを、700℃程度で30分間程度、アニール処理する。

【0023】

図1(b)に示すように、素子分離構造3を形成する。図1(c)以降では、素子分離構造3の図示を省略する。

詳細には、化合物半導体積層構造2の素子分離領域に、例えばアルゴン(Ar)を注入する。これにより、化合物半導体積層構造2及びSi基板1の表層部分に素子分離構造3が形成される。素子分離構造3により、化合物半導体積層構造2上で活性領域が画定される。

なお、素子分離は、上記の注入法の代わりに、例えばSTI(Shallow Trench Isolation)法等既知の他の方法を用いて行っても良い。このとき、化合物半導体積層構造2のドライエッチングには、例えば塩素系のエッチングガスを用いる。

【0024】

続いて、図1(c)〜図3(a)に示すように、n型キャップ層2fを所期形状にエッチング加工する。

詳細には、先ず、図1(c)に示すように、n型キャップ層2f上にレジストを塗布し、リソグラフィーにより加工する。これにより、n型キャップ層2fの表面のゲート電極の形成予定位置を露出させる開口10Aaを有するレジストマスク10Aが形成される。

【0025】

次に、図2(a)に示すように、レジストマスク10Aを用い、Cl2ガスをエッチングガスとして用いて、反応性イオンエッチング(RIE)によりn型キャップ層2fをエッチング加工する。これにより、n型キャップ層2fに、p型キャップ層2eの表面のゲート電極の形成予定位置を露出させる開口2faが形成される。開口2faは、ドレイン電極の形成予定位置よりも、ソース電極の形成予定位置に偏倚した所定部位に形成される。

レジストマスク10Aは、アッシング処理又は所定の薬液を用いたウェット処理により、除去される。

【0026】

n型キャップ層2fに開口2faが形成された化合物半導体積層構造2においては、開口2faではn型キャップ層2fのn−GaNが存在しない。そのため、p型キャップ層2eのp−GaNにより、GaN/AlGaN界面の開口2faの下方に相当する部位では、2DEGが殆ど消失する。図示の例では、2DEGが消失した場合を示す。

【0027】

次に、図2(b)に示すように、開口2faを埋め込むようにn型キャップ層2f上にレジストを塗布し、リソグラフィーにより加工する。これにより、n型キャップ層2fの表面のフィールドプレート電極の形成予定位置を露出させる開口10Baを有するレジストマスク10Bが形成される。

【0028】

次に、図2(c)に示すように、レジストマスク10Bを用い、Cl2ガスをエッチングガスとして用いて、RIEによりn型キャップ層2fをエッチング加工する。これにより、n型キャップ層2fのフィールドプレート電極の形成予定位置が、所期の厚みに薄化される。薄化部分2fbは、開口2faとドレイン電極の形成予定位置との間で、ソース電極の形成予定位置よりもドレイン電極の形成予定位置に偏倚した所定部位に形成される。この薄化部分2fbは、フィールドプレート電極による2DEG量の所期の制御を考慮して、n型キャップ層2fの厚みの半分程度、例えば50nm程度の厚みとされる。なお、例えばダイオードとしてのみ用いる場合には、このn型キャップ層2fの薄化工程は不要であることがある。

【0029】

n型キャップ層2fに薄化部分2fbが形成された化合物半導体積層構造2において、薄化部分2fbではn型キャップ層2fのその他の部分(開口2faは除く)よりもn−GaNが薄い。そのため、p型キャップ層2eのp−GaNにより、GaN/AlGaN界面の薄化部分2fbの下方に相当する部位では、図示のように、薄化部分2fbの薄化に相当する分だけ2DEGが減少する。

【0030】

そして、図3(a)に示すように、レジストマスク10Bを、アッシング処理又は所定の薬液を用いたウェット処理により除去する。以上により、n型キャップ層2fは、開口2fa及び薄化部分2fbが形成された状態で露出する。

【0031】

続いて、図3(b)に示すように、ソース電極4及びドレイン電極5を形成する。

詳細には、先ず、化合物半導体積層構造2の表面におけるソース電極及びドレイン電極の形成予定位置(電極形成予定位置)に電極用リセス2A,2Bを形成する。

化合物半導体積層構造2の表面にレジストを塗布する。レジストをリソグラフィーにより加工し、レジストに、電極形成予定位置に相当する化合物半導体積層構造2の表面を露出する開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

【0032】

このレジストマスクを用いて、電子供給層2dの表面が露出するまで、n型キャップ層2f及びp型キャップ層2eの電極形成予定位置をドライエッチングして除去する。これにより、電子供給層2dの表面の電極形成予定位置を露出する電極用リセス2A,2Bが形成される。エッチング条件としては、Ar等の不活性ガス及びCl2等の塩素系ガスをエッチングガスとして用い、例えばCl2を流量30sccm、圧力を2Pa、RF投入電力を20Wとする。なお、電極用リセス2A,2Bは、例えば電子供給層2d以降までエッチングして形成しても良い。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0033】

ソース電極及びドレイン電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、電極用リセス2A,2Bを露出させる開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電極材料として、例えばTa/Alを、例えば蒸着法により、電極用リセス2A,2Bを露出させる開口内を含むレジストマスク上に堆積する。Taの厚みは20nm程度、Alの厚みは200nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したTa/Alを除去する。その後、Si基板1を、例えば窒素雰囲気中において400℃〜1000℃の温度、例えば600℃程度で熱処理し、残存したTa/Alを電子供給層2dとオーミックコンタクトさせる。Ta/Alの電子供給層2dとのオーミックコンタクトが得られるのであれば、熱処理が不要な場合もある。以上により、電極用リセス2A,2Bを電極材料の一部で埋め込むソース電極4及びドレイン電極5が形成される。

【0034】

続いて、図3(c)に示すように、ゲート電極6及びフィールドプレート電極7を形成する。

詳細には、先ず、ゲート電極及びフィールドプレート電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、開口2fa及び薄化部分2fbを露出させる各開口を形成する。以上により、当該各開口を有するレジストマスクが形成される。

【0035】

このレジストマスクを用いて、電極材料として、例えばNi/Auを、例えば蒸着法により、n型キャップ層2fの開口2fa及び薄化部分2fbを露出させる各開口内を含むレジストマスク上に堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したNi/Auを除去する。以上により、n型キャップ層2fの開口2fa内を電極材料の一部で埋め込むゲート電極6と、n型キャップ層2fの薄化部分2fb上の窪みを電極材料の一部で埋め込むフィールドプレート電極7がそれぞれ形成される。

【0036】

フィールドプレート電極7は、ゲート電極6とドレイン電極5との間に、ソース電極4よりもドレイン電極5に向かって偏倚した位置に形成される。AlGaN/GaN・HEMTでは、ソース電極及びゲート電極に比してドレイン電極に大きな電圧が印加される場合があるが、この構成を採ることにより、大きな電圧印加で発生する電界をフィールドプレート電極7で緩和することができる。

【0037】

しかる後、ソース電極4、ドレイン電極5、ゲート電極6の電気的接続、ソース電極4、ドレイン電極5、ゲート電極6の各パッドの形成等の諸工程を経て、本実施形態によるAlGaN/GaN・HEMTが形成される。

【0038】

本実施形態によるAlGaN/GaN・HEMTを平面視した様子を図4に示す。

図4の破線I−I'に沿った断面が図3(c)に相当する。このように、ソース電極4とドレイン電極5とが櫛歯状に互いに平行に形成されており、ソース電極4とドレイン電極5との間に櫛歯状のゲート電極6がこれらと平行に配されている。

【0039】

なお本実施形態では、ゲート電極が化合物半導体と直接的に接触するショットキー型のAlGaN/GaN・HEMTに例示したが、ゲート電極が化合物半導体との間でゲート絶縁膜を介するMIS型のAlGaN/GaN・HEMTにも適用できる。MIS型のAlGaN/GaN・HEMTを作製する場合には、図2(a)の工程の後に開口2faの側壁面を覆うようにn型キャップ層2f上にゲート絶縁膜を形成し、図2(c)の工程でゲート絶縁膜を貫通すると共に薄化部分2fbを形成する。そして、図3(c)の工程でゲート電極及びフィールドプレート電極を形成すれば良い。

【0040】

本実施形態によるAlGaN/GaN・HEMTでは、2DEGの濃度を制御するために、p−GaNのキャップ層をエッチングしたり、p−GaNを再成長することなく、p型キャップ層2eはそのままでその上のn型キャップ層2fを適宜エッチング加工する。これにより、n型キャップ層2fの厚みでp型キャップ層2eのp型不純物(ここではMg)の量を実効的にコントロールし、容易且つ確実に、フィールドプレート電極7で2DEGの濃度を制御しつつ、所期のノーマリオフ動作が実現する。即ち、ゲート電圧のオフ時にはチャネルには2DEGがなくノーマリオフとなり、ゲート電圧のオン時にはチャネルに所期の2DEGが生成されて駆動する。

【0041】

フィールドプレート電極7の下方では、p型キャップ層2eのp−GaNと電子供給層2dのn−AlGaNとがpn接合している。p型キャップ層2eがn型キャップ層2fとの関係で空乏化し、空乏層が伸びて拡大する。これにより、耐圧が大幅に向上すると共に、寄生容量Cds,Cgdが大幅に低減し、デバイス動作の高速化が実現する。

【0042】

更に本実施形態では、フィールドプレート電極7の下方におけるp型キャップ層2eと電子供給層2dとのpn接合により、フィールドプレート電極7がアノード、ドレイン電極5がカソードとなる保護ダイオードの機能が付与される。この保護ダイオードの整流作用により、AlGaN/GaN・HEMTにサージ電圧が生じても、AlGaN/GaN・HEMTの破壊が抑止される。このように、アバランシェ耐量が十分に確保され、デバイス動作の安定化に寄与する。

【0043】

ここで、本実施形態によるAlGaN/GaN・HEMTの諸特性について調べた諸実験について説明する。本実施形態の比較例として、n−GaNのn型キャップ層上にp−GaNを成長し、p−GaNの不要部分をエッチング除去した後、Mg濃度の異なるp−GaNを再成長し、一括熱アニール処理を行なって作製したAlGaN/GaN・HEMTを例示する。

【0044】

実験1では、ドレイン−ソース間電圧Vdsとドレイン電流Idとの関係について調べた。実験結果を図5に示す。本実施形態では、比較例とは異なり、動作時において非動作時と殆ど変わらない波形を示している。この結果から、本実施形態では、比較例に比して動作時の電流低減を抑止する大幅な改善が確認された。

【0045】

実験2では、ドレイン−ソース間電圧Vdsを印加し続け、破壊が起こるまでの時間(オフストレス試験)について調べた。ここでは、温度200℃でVdsを600V、ゲート−ソース間電圧Vgsを0Vとした。実験結果を図6に示す。この結果から、本実施形態では、比較例に比して破壊までの時間が増加し、デバイスの信頼性が向上することが確認された。

【0046】

実験3では、本実施形態によるAlGaN/GaN・HEMTについて、非動作時における2DEGの濃度について調べた。実験結果を図7に示す。本実施形態において、ゲート電極の下方に相当する部位では、2DEGの濃度が十分小さい値となっており、ノーマリオフが実現している。フィールドプレート電極の下方に相当する部位では、2DEGの濃度が所期の値に変調されていることが判る。

【0047】

以上説明したように、本実施形態によれば、n型キャップ層2fと共にp型キャップ層2eを用い、動作時におけるオン抵抗の増加を抑え、また作製時にp−GaNの再成長をすることなく、実効的にp型不純物のドーピング量が容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧のAlGaN/GaN・HEMTが実現する。

【0048】

本実施形態によるAlGaN/GaN・HEMTは、いわゆるディスクリートパッケージに適用される。

このディスクリートパッケージでは、本実施形態によるAlGaN/GaN・HEMTのチップが搭載される。以下、本実施形態によるAlGaN/GaN・HEMTのチップ(以下、HEMTチップと言う)のディスクリートパッケージについて例示する。

【0049】

HEMTチップの概略構成(図4に対応する)を図8に示す。

HEMTチップ100では、その表面に、上述したAlGaN/GaN・HEMTのトランジスタ領域101と、ドレイン電極が接続されたドレインパッド102と、ゲート電極が接続されたゲートパッド103と、ソース電極が接続されたソースパッド104とが設けられている。

【0050】

図9は、ディスクリートパッケージを示す概略平面図である。

ディスクリートパッケージを作製するには、先ず、HEMTチップ100を、ハンダ等のダイアタッチ剤111を用いてリードフレーム112に固定する。リードフレーム112にはドレインリード112aが一体形成されており、ゲートリード112b及びソースリード112cがリードフレーム112と別体として離間して配置される。

【0051】

続いて、Alワイヤ113を用いたボンディングにより、ドレインパッド102とドレインリード112a、ゲートパッド103とゲートリード112b、ソースパッド104とソースリード112cをそれぞれ電気的に接続する。

その後、モールド樹脂114を用いて、トランスファーモールド法によりHEMTチップ100を樹脂封止し、リードフレーム112を切り離す。以上により、ディスクリートパッケージが形成される。

【0052】

(第2の実施形態)

本実施形態では、化合物半導体装置として、AlGaN/GaNの高電子移動度ダイオード(以下、単にAlGaN/GaN・ダイオードと記す。)を開示する。

図10〜図12は、第2の実施形態によるAlGaN/GaN・ダイオードの製造方法を工程順に示す概略断面図である。

【0053】

先ず、図10(a)に示すように、成長用基板として例えばSi基板1上に、化合物半導体積層構造21を形成する。成長用基板としては、Si基板の代わりに、サファイア基板、GaAs基板、SiC基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

化合物半導体積層構造21は、バッファ層21a、電子走行層21b、中間層(スペーサ層)21c、電子供給層21d、p型キャップ層21e、及びn型キャップ層21fを有して構成される。

【0054】

詳細には、Si基板1上に、例えばMOVPE法により、以下の各化合物半導体を成長する。MOVPE法の代わりに、MBE法等を用いても良い。

SiC基板21上に、バッファ層21a、電子走行層21b、中間層21c、電子供給層21d、p型キャップ層21e、及びn型キャップ層21fとなる各化合物半導体を順次成長する。バッファ層21aは、Si基板1上に、AlNを0.1μm程度の厚みに成長することで形成される。電子走行層21bは、i−GaNを1μm程度〜3μm程度の厚みに成長することで形成される。中間層21cは、i−AlGaNを5nm程度の厚みに成長することで形成される。電子供給層21dは、n−AlGaNを30nm程度の厚みに成長することで形成される。中間層21cは形成しない場合もある。電子供給層は、i−AlGaNを形成するようにしても良い。

【0055】

p型キャップ層21eは、p−GaNを、例えば10nm程度〜1000nm程度に成長することで形成される。10nmよりも薄いと、所期の2DEGの減少効果が得られなくなる。1000nmよりも厚いと、2DEGが減少しすぎて、オン抵抗が上昇してしまう。従って、p型キャップ層21eを10nm程度〜1000nm程度に形成することにより、十分な2DEGの減少効果を得るも、オン抵抗の減少を抑制することができる。本実施形態では、p型キャップ層21eのp−GaNは200nm程度の厚みに形成される。

n型キャップ層21fは、p型キャップ層21eとの関係で、n−GaNを例えば5nm程度〜500nm程度、ここでは100nm程度の厚みに成長することで形成される。

【0056】

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH3)ガスの混合ガスを用いる。AlGaNの成長には、原料ガスとしてTMAlガス、TMGaガス及びNH3ガスの混合ガスを用いる。成長する化合物半導体層に応じて、TMAlガス、TMGaガスの供給の有無及び流量を適宜設定する。共通原料であるNH3ガスの流量は、100sccm〜10slm程度とする。また、成長圧力は50Torr〜300Torr程度、成長温度は1000℃〜1200℃程度とする。

【0057】

AlGaN、GaNをn型として成長する際、即ち電子供給層21d(n−AlGaN)、n型キャップ層21f(n−GaN)の形成には、n型不純物をAlGaN、GaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン(SiH4)ガスを所定の流量で原料ガスに添加し、AlGaN、GaNにSiをドーピングする。Siのドーピング濃度は、1×1018/cm3程度〜1×1020/cm3程度、例えば2×1018/cm3程度とする。

【0058】

GaNをp型として成長する際、即ちp型キャップ層21e(p−GaN)の形成には、p型不純物、例えばMg,Cから選ばれたものをGaNの原料ガスに添加する。本実施形態では、p型不純物としてMgを用いる。Mgを所定の流量で原料ガスに添加し、GaNにMgをドーピングする。Mgのドーピング濃度は、例えば1×1016/cm3程度〜1×1021/cm3程度とする。ドーピング濃度が1×1016/cm3程度よりも低いと、十分なp型とならない。1×1021/cm3程度よりも高いと、結晶性が崩れ、十分な特性が得られなくなる。従って、Mgのドーピング濃度を1×1016/cm3程度〜1×1021/cm3程度とすることにより、十分な特性の得られるp型半導体となる。

【0059】

形成された化合物半導体積層構造21では、電子走行層21bの電子供給層21dとの界面(正確には、中間層21cとの界面。以下、GaN/AlGaN界面と記す。)には、GaNの格子定数とAlGaNの格子定数との差に起因した歪みによるピエゾ分極が生じる。このピエゾ分極の効果と、電子走行層21b及び電子供給層21dの自発分極の効果とが相俟って、GaN/AlGaN界面に高い電子濃度の2次元電子ガス(2DEG)が発生する。

【0060】

化合物半導体積層構造21を形成した後に、p型キャップ層21eを、700℃程度で30分間程度、アニール処理する。

【0061】

続いて、図10(b)〜図11(c)に示すように、n型キャップ層2fを所期形状にエッチング加工する。

詳細には、先ず、図10(b)に示すように、n型キャップ層2f上にレジストを塗布し、リソグラフィーにより加工する。これにより、n型キャップ層2fの表面のアノード電極の形成予定位置よりもカソード電極の形成予定位置に偏倚した所定部位を露出させる開口20Aaを有するレジストマスク20Aが形成される。

【0062】

次に、図10(c)に示すように、レジストマスク20Aを用い、Cl2ガスをエッチングガスとして用いて、RIEによりn型キャップ層21fをエッチング加工する。これにより、n型キャップ層21fに、p型キャップ層21eの表面の所定部位を露出させる開口21faが形成される。

レジストマスク20Aは、アッシング処理又は所定の薬液を用いたウェット処理により、除去される。

【0063】

n型キャップ層21fに開口21faが形成された化合物半導体積層構造21において、開口21faではn型キャップ層21fのn−GaNが存在しない。そのため、p型キャップ層2eのp−GaNにより、GaN/AlGaN界面の開口2faの下方に相当する部位では、図示のように2DEGが殆ど消失し、例えば所定の少量だけ存在する。

【0064】

次に、図11(a)に示すように、開口21faを埋め込むようにn型キャップ層21f上にレジストを塗布し、リソグラフィーにより加工する。これにより、n型キャップ層21fの表面の開口21faに隣接するアノード電極の形成予定位置側の所定部位を露出させる開口20Baを有するレジストマスク20Bが形成される。

【0065】

次に、図11(b)に示すように、レジストマスク20Bを用い、Cl2ガスをエッチングガスとして用いて、RIEによりn型キャップ層21fをエッチング加工する。これにより、n型キャップ層21fの所定部位が、所期の厚みに薄化される。この薄化部分21fbは、AlGaN/GaN・ダイオードにおける2DEG量の所期の制御を考慮して、n型キャップ層21fの厚みの半分程度、例えば50nm程度の厚みとされる。

【0066】

n型キャップ層21fに薄化部分21fbが形成された化合物半導体積層構造21において、薄化部分21fbではn型キャップ層21fのその他の部分(開口21faは除く)よりもn−GaNが薄い。そのため、p型キャップ層21eのp−GaNにより、GaN/AlGaN界面の薄化部分21fbの下方に相当する部位では、図示のように、薄化部分21fbの薄化に相当する分だけ2DEGが減少する。

レジストマスク20Bは、アッシング処理又は所定の薬液を用いたウェット処理により、除去される。

【0067】

次に、図11(c)に示すように、化合物半導体積層構造21の表面におけるカソード電極及びアノード電極の形成予定位置に電極用リセス21A,21Bを形成する。

このレジストマスクを用いて、電子供給層21dの表面が露出するまで、n型キャップ層21f及びp型キャップ層21eの各電極形成予定位置をドライエッチングして除去する。これにより、電子供給層21dの表面の各電極形成予定位置を露出する電極用リセス21A,21Bが形成される。このとき、n型キャップ層21fは、n型キャップ層21f上に階段形状に残存する。エッチング条件としては、Ar等の不活性ガス及びCl2等の塩素系ガスをエッチングガスとして用い、例えばCl2を流量30sccm、圧力を2Pa、RF投入電力を20Wとする。なお、電極用リセス2A,2Bは、例えば電子供給層2d以降までエッチングして形成しても良い。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0068】

以上により、n型キャップ層21fは、p型キャップ層21e上で階段形状に残存する。p型キャップ層21eにおいて、2DEGは、n型キャップ層21fの厚みに対応して変調されている。即ち、p型キャップ層21eの電極用リセス2A側の端部から電極用リセス2B側の端部へ向かうについて、2DEGの濃度が段階的に増加している。このように、カソード電極側では2DEGの濃度を低く、アノード電極側では2DEGの濃度を高く分布させる(カソード電極側からアノード電極側へ2DEGの濃度を徐々に高く分布させる)ことにより、所期の高耐圧のAlGaN/GaN・ダイオードが実現する。

【0069】

続いて、図12(a)に示すように、カソード電極23を形成する。

詳細には、先ず、カソード電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、電極用リセス21Aを露出させる開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電極材料として、例えばTa/Alを、例えば蒸着法により、電極用リセス2Aを露出させる開口内を含むレジストマスク上に堆積する。Taの厚みは20nm程度、Alの厚みは200nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したTa/Alを除去する。以上により、電極用リセス21Aを電極材料の一部で埋め込むカソード電極23が形成される。

【0070】

続いて、図12(b)に示すように、アノード電極24を形成する。

詳細には、先ず、アノード電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、電極用リセス21Bを露出させる開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電極材料として、例えばNiを、例えば蒸着法により、電極用リセス2Bを露出させる開口内を含むレジストマスク上に堆積する。Niの厚みは30nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したNiを除去する。以上により、電極用リセス21Bを電極材料の一部で埋め込むアノード電極24が形成される。

【0071】

しかる後、カソード電極23、アノード電極24の電気的接続、カソード電極23、アノード電極24の各パッドの形成等の諸工程を経て、本実施形態によるAlGaN/GaN・ダイオードが形成される。

【0072】

本実施形態によるAlGaN/GaN・ダイオードでは、2DEGの濃度を制御するために、p−GaNのキャップ層をエッチングしたり、p−GaNを再成長することなく、p型キャップ層21eはそのままでその上のn型キャップ層21fを適宜エッチング加工する。これにより、n型キャップ層21fの厚みでp型キャップ層21eのp型不純物(ここではMg)の量を実効的にコントロールし、容易且つ確実に、2DEGの濃度を制御しつつ、所期の高耐圧が実現する。

【0073】

ここで、本実施形態によるAlGaN/GaN・ダイオードの諸特性について調べた諸実験について説明する。本実施形態の比較例として、n−GaNのn型キャップ層上にp−GaNを成長し、p−GaNの不要部分をエッチング除去した後、Mg濃度の異なるp−GaNを再成長し、一括熱アニール処理を行なって作製したAlGaN/GaN・ダイオードを例示する。

【0074】

実験1では、アノード−カソード間順電圧Vacとアノード電流Iaとの関係について調べた。実験結果を図13に示す。本実施形態では、比較例とは異なり、動作時において非動作時と殆ど変わらない波形を示している。この結果から、本実施形態では、比較例に比して動作時の電流低減を抑止する大幅な改善が確認された。

【0075】

実験2では、アノード−カソード間に逆電圧を印加し続け、破壊が起こるまでの時間について調べた。ここでは、温度200℃でVacを600Vとした。実験結果を図14に示す。この結果から、本実施形態では、比較例に比して破壊までの時間が増加し、デバイスの信頼性が向上することが確認された。

【0076】

以上説明したように、本実施形態によれば、n型キャップ層2fと共にp型キャップ層2eを用い、動作時におけるオン抵抗の増加を抑え、また作製時にp−GaNの再成長をすることなく、実効的にp型不純物のドーピング量が容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧のAlGaN/GaN・ダイオードが実現する。

【0077】

本実施形態によるAlGaN/GaN・ダイオードは、いわゆるディスクリートパッケージに適用される。

このディスクリートパッケージでは、本実施形態によるAlGaN/GaN・ダイオードのチップが搭載される。以下、本実施形態によるAlGaN/GaN・のダイオードチップ(以下、ダイオードチップと言う)のディスクリートパッケージについて例示する。

【0078】

ダイオードチップの概略構成を図15に示す。

ダイオードチップ200では、その表面に、上述したAlGaN/GaN・ダイオードのダイオード領域201と、カソード電極が接続されたカソードパッド202と、アノード電極が接続されたアノードパッド203とが設けられている。

【0079】

図16は、ディスクリートパッケージを示す概略平面図である。

ディスクリートパッケージを作製するには、先ず、ダイオードチップ200を、ハンダ等のダイアタッチ剤211を用いてリードフレーム212に固定する。リードフレーム212と別体として、カソードリード212a及びアノードリード212bがリードフレーム212から離間して配置される。

【0080】

続いて、Alワイヤ213を用いたボンディングにより、カソードパッド202とカソードリード212a、アノードパッド203とアノードリード212bをそれぞれ電気的に接続する。

その後、モールド樹脂214を用いて、トランスファーモールド法によりダイオードチップ200を樹脂封止し、リードフレーム212を切り離す。以上により、ディスクリートパッケージが形成される。

【0081】

(第3の実施形態)

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMT又は第2の実施形態によるAlGaN/GaN・ダイオード、或いは双方を備えたPFC(Power Factor Correction)回路を開示する。

図17は、PFC回路を示す結線図である。

【0082】

PFC回路30は、スイッチ素子(トランジスタ)31と、ダイオード32と、チョークコイル33と、コンデンサ34,35と、ダイオードブリッジ36と、交流電源(AC)37とを備えて構成される。スイッチ素子31に、第1の実施形態によるAlGaN/GaN・HEMTが適用される。又は、ダイオード32に、第2の実施形態によるAlGaN/GaN・ダイオードが適用される。或いは、スイッチ素子31に第1の実施形態によるAlGaN/GaN・HEMTが、ダイオード32に第2の実施形態によるAlGaN/GaN・ダイオードがそれぞれ適用される。また、ダイオードブリッジ36にも第2の実施形態によるAlGaN/GaN・ダイオードを適用しても良い。

【0083】

PFC回路30では、スイッチ素子31のドレイン電極と、ダイオード32のアノード端子及びチョークコイル33の一端子とが接続される。スイッチ素子31のソース電極と、コンデンサ34の一端子及びコンデンサ35の一端子とが接続される。コンデンサ34の他端子とチョークコイル33の他端子とが接続される。コンデンサ35の他端子とダイオード32のカソード端子とが接続される。コンデンサ34の両端子間には、ダイオードブリッジ36を介してAC37が接続される。コンデンサ35の両端子間には、直流電源(DC)が接続される。なお、スイッチ素子31には不図示のPFCコントローラが接続される。

【0084】

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMT及び第2の実施形態によるAlGaN/GaN・ダイオードの一方又は双方をPFC回路30に適用する。これにより、信頼性の高いPFC回路30が実現する。

【0085】

(第4の実施形態)

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMT、更には第2の実施形態によるAlGaN/GaN・ダイオードを備えた電源装置を開示する。

図18は、第4の実施形態による電源装置の概略構成を示す結線図である。

【0086】

本実施形態による電源装置は、高圧の一次側回路41及び低圧の二次側回路42と、一次側回路41と二次側回路42との間に配設されるトランス43とを備えて構成される。

一次側回路41は、第3の実施形態によるPFC回路30と、PFC回路30のコンデンサ35の両端子間に接続されたインバータ回路、例えばフルブリッジインバータ回路40とを有している。フルブリッジインバータ回路40は、複数(ここでは4つ)のスイッチ素子44a,44b,44c,44dを備えて構成される。

二次側回路42は、複数(ここでは3つ)のスイッチ素子45a,45b,45cを備えて構成される。

【0087】

本実施形態では、一次側回路41を構成するPFC回路が第3の実施形態によるPFC回路30であると共に、フルブリッジインバータ回路40のスイッチ素子44a,44b,44c,44dが、第1の実施形態によるAlGaN/GaN・HEMTとされている。一方、二次側回路42のスイッチ素子45a,45b,45cは、シリコンを用いた通常のMIS・FETとされている。

【0088】

第1の実施形態及びその諸変形例から選ばれたAlGaN/GaN・HEMTでは、第1の実施形態で説明したように、フィールドプレート電極の下方でpn接合が形成される。これにより、フィールドプレート電極がアノード、ドレイン電極がカソードとなる保護ダイオードの機能が付与される。本実施形態では、このAlGaN/GaN・HEMTをPFC回路30のスイッチ素子31及びフルブリッジインバータ回路40のスイッチ素子44a,44b,44c,44dに適用している。そのため、一次側回路41において、スイッチ素子31,44a,44b,44c,44dにサージ電圧が生じても、保護ダイオードの整流作用により、スイッチ素子31,44a,44b,44c,44dの破壊が抑止される。このように、大きなアバランシェ耐量が確保され、デバイス動作の安定化に寄与する。

【0089】

本実施形態では、第3の実施形態によるPFC回路30と、第1の実施形態によるAlGaN/GaN・HEMT、更には第2の実施形態によるAlGaN/GaN・ダイオードとを、高圧回路である一次側回路41に適用する。これにより、信頼性の高い大電力の電源装置が実現する。

【0090】

(第5の実施形態)

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMTを備えた高周波増幅器を開示する。

図19は、第5の実施形態による高周波増幅器の概略構成を示す結線図である。

【0091】

本実施形態による高周波増幅器は、ディジタル・プレディストーション回路51と、ミキサー52a,52bと、パワーアンプ53とを備えて構成される。

ディジタル・プレディストーション回路51は、入力信号の非線形歪みを補償するものである。ミキサー52aは、非線形歪みが補償された入力信号と交流信号をミキシングするものである。パワーアンプ53は、交流信号とミキシングされた入力信号を増幅するものであり、第1の実施形態によるAlGaN/GaN・HEMTを有している。なお図19では、例えばスイッチの切り替えにより、出力側の信号をミキサー52bで交流信号とミキシングしてディジタル・プレディストーション回路51に送出できる構成とされている。

【0092】

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMTを高周波増幅器に適用する。これにより、信頼性の高い高耐圧の高周波増幅器が実現する。

【0093】

(他の実施形態)

第1の実施形態では、化合物半導体装置としてAlGaN/GaN・HEMTを例示した。化合物半導体装置としては、AlGaN/GaN・HEMT以外にも、以下のようなHEMTに適用できる。

また、第2の実施形態では、化合物半導体装置としてAlGaN/GaN・ダイオードを例示した。化合物半導体装置としては、AlGaN/GaN・ダイオード以外にも、以下のような高電子移動度ダイオードに適用できる。

【0094】

・その他の装置例1

本例では、化合物半導体装置として、InAlN/GaN・HEMT、InAlN/GaN・ダイオードを開示する。

InAlNとGaNは、組成によって格子定数を近くすることが可能な化合物半導体である。この場合、上記した第1及び第2の実施形態では、電子走行層がi−GaN、中間層がAlN、電子供給層がn−InAlN、p型キャップ層がp−GaN、n型キャップ層がn−GaNで形成される。また、この場合のピエゾ分極がほとんど発生しないため、2次元電子ガスは主にInAlNの自発分極により発生する。

【0095】

本例によれば、上述したAlGaN/GaN・HEMT、AlGaN/GaN・ダイオードと同様に、n型化合物半導体層と共にp型化合物半導体層を用い、化合物半導体層の再成長をすることなく、実効的に第2導電型のドーピング量が容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧のInAlN/GaN・HEMT、InAlN/GaN・ダイオードが実現する。

【0096】

・その他の装置例2

本例では、化合物半導体装置として、InAlGaN/GaN・HEMT、InAlGaN/GaN・ダイオードを開示する。

GaNとInAlGaNは、後者の方が前者よりも組成によって格子定数を小さくすることができる化合物半導体である。この場合、上記した第1及び第2の実施形態では、電子走行層がi−GaN、中間層がi−InAlGaN、電子供給層がn−InAlGaN、p型キャップ層がp−GaN、n型キャップ層がn−GaNで形成される。

【0097】

本例によれば、上述したAlGaN/GaN・HEMT、AlGaN/GaN・ダイオードと同様に、n型化合物半導体層と共にp型化合物半導体層を用い、化合物半導体層の再成長をすることなく、実効的に第2導電型のドーピング量が容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧のInAlGaN/GaN・HEMT、InAlGaN/GaN・ダイオードが実現する。

【0098】

以下、化合物半導体装置及びその製造方法、並びに電源装置及び高周波増幅器の諸態様を付記としてまとめて記載する。

【0099】

(付記1)第1の極性を有する第1の化合物半導体層と、

前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、

前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層と

を含み、

前記第3の化合物半導体層は、厚みの異なる部位を有することを特徴とする化合物半導体装置。

【0100】

(付記2)前記第1の極性は、負の極性であることを特徴とする付記1に記載の化合物半導体装置。

【0101】

(付記3)前記第3の化合物半導体層は、貫通口が形成されており、

前記貫通口を埋め込むゲート電極を更に含むことを特徴とする付記1又は2に記載の化合物半導体装置。

【0102】

(付記4)前記第3の化合物半導体層上に形成されたフィールドプレート電極を更に含むことを特徴とする付記1〜3のいずれか1項に記載の化合物半導体装置。

【0103】

(付記5)前記フィールドプレート電極は、前記第3の化合物半導体層の薄い部位に形成されていることを特徴とする付記4に記載の化合物半導体装置。

【0104】

(付記6)前記第1の化合物半導体層の上方で前記第3の化合物半導体層の両側に形成された一対の電極を更に含み、

前記第3の化合物半導体層は、一方の前記電極側が薄く、他方の前記電極側が一方の前記電極側よりも厚く形成されていることを特徴とする付記1又は2に記載の化合物半導体装置。

【0105】

(付記7)第1の極性を有する第1の化合物半導体層を形成する工程と、

前記第1の半導体層の上方に、第2の極性を有する第2の化合物半導体層を形成する工程と、

前記第2の半導体層の上方に、第2の極性を有する第3の化合物半導体層を形成する工程と、

前記第3の化合物半導体層に、厚みの異なる部位を形成する工程と

を含むことを特徴とする化合物半導体装置の製造方法。

【0106】

(付記8)前記第1の極性は、負の極性であることを特徴とする付記7に記載の化合物半導体装置の製造方法。

【0107】

(付記9)前記第3の化合物半導体層に貫通口を形成し、

前記貫通口を埋め込むゲート電極を形成する工程を更に含むことを特徴とする付記7又は8に記載の化合物半導体装置の製造方法。

【0108】

(付記10)前記第3の化合物半導体層上にフィールドプレート電極を形成する工程を更に含むことを特徴とする付記7〜9のいずれか1項に記載の化合物半導体装置の製造方法。

【0109】

(付記11)前記フィールドプレート電極を、前記第3の化合物半導体層の薄い部位に形成することを特徴とする付記10に記載の化合物半導体装置の製造方法。

【0110】

(付記12)前記第1の化合物半導体層の上方で前記第3の化合物半導体層の両側に一対の電極を形成する工程を更に含み、

前記第3の化合物半導体層を、一方の前記電極側が薄く、他方の前記電極側が一方の前記電極側よりも厚く形成することを特徴とする付記7又は8に記載の化合物半導体装置の製造方法。

【0111】

(付記13)変圧器と、前記変圧器を挟んで高圧回路及び低圧回路とを備えた電源装置であって、

前記高圧回路はトランジスタ及びダイオードを有しており、

前記トランジスタ及び前記ダイオードの少なくも一方は、

第1の極性を有する第1の化合物半導体層と、

前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、

前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層と

を含み、

前記第3の化合物半導体層は、厚みの異なる部位を有することを特徴とする電源装置。

【0112】

(付記14)入力した高周波電圧を増幅して出力する高周波増幅器であって、

トランジスタを有しており、

前記トランジスタは、

第1の極性を有する第1の化合物半導体層と、

前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、

前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層と

を含み、

前記第3の化合物半導体層は、厚みの異なる部位を有することを特徴とする高周波増幅器。

【符号の説明】

【0113】

1 Si基板

2,21 化合物半導体積層構造

2a,21a バッファ層

2b,21b 電子走行層

2c,21c 中間層

2d,21d 電子供給層

2e,21e p型キャップ層

2f,21f n型キャップ層

2fa,21fa 開口

2fb,21fb 薄化部分

2A,2B,21A,21B 電極用リセス

3 素子分離構造

4 ソース電極

5 ドレイン電極

6 ゲート電極

7 フィールドプレート電極

10A,10B,20A,20B レジストマスク

10Aa,10Ba,20Aa,20Ba 開口

23 カソード電極

24 アノード電極

30 PFC回路

31,44a,44b,44c,44d,45a,45b,45c スイッチ素子

32 ダイオード

33 チョークコイル

34,35 コンデンサ

36 ダイオードブリッジ

40 フルブリッジインバータ回路

41 一次側回路

42 二次側回路

43 トランス

51 ディジタル・プレディストーション回路

52a,52b ミキサー

53 パワーアンプ

100 HEMTチップ

101 トランジスタ領域

102 ドレインパッド

103 ゲートパッド

104 ソースパッド

111,211 ダイアタッチ剤

112,212 リードフレーム

112a ドレインリード

112b ゲートリード

112c ソースリード

113,213 Alワイヤ

114,214 モールド樹脂

200 ダイオードチップ

201 ダイオード領域

202 カソードパッド

203 アノードパッド

212a カソードリード

212b アノードリード

【技術分野】

【0001】

本発明は、化合物半導体装置及びその製造方法に関する。

【背景技術】

【0002】

窒化物半導体は、高い飽和電子速度及びワイドバンドギャップ等の特徴を利用し、高耐圧及び高出力の半導体デバイスへの適用が検討されている。例えば、窒化物半導体であるGaNのバンドギャップは3.4eVであり、Siのバンドギャップ(1.1eV)及びGaAsのバンドギャップ(1.4eV)よりも大きく、高い破壊電界強度を有する。そのためGaNは、高電圧動作且つ高出力を得る電源用の半導体デバイスの材料として極めて有望である。

【0003】

窒化物半導体を用いたデバイスとしては、電界効果トランジスタ、特に高電子移動度トランジスタ(High Electron Mobility Transistor:HEMT)についての報告が数多くなされている。例えばGaN系のHEMT(GaN−HEMT)では、GaNを電子走行層として、AlGaNを電子供給層として用いたAlGaN/GaN・HEMTが注目されている。AlGaN/GaN・HEMTでは、GaNとAlGaNとの格子定数差に起因した歪みがAlGaNに生じる。これにより発生したピエゾ分極及びAlGaNの自発分極により、高濃度の2次元電子ガス(2DEG)が得られる。そのため、高効率のスイッチ素子、電気自動車用等の高耐圧電力デバイスとして期待されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2007−220895号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

窒化物半導体デバイスでは、2DEGの発生量を局所的に制御する技術が要求されている。例えばHEMTの場合には、いわゆるフェイルセーフの観点から、電圧のオフ時には電流が流れない、所謂ノーマリオフ動作が望まれる。そのためには、電圧のオフ時においてゲート電極の下方における2DEGの発生量を抑える工夫が必要である。

ノーマリオフ動作のGaN・HEMTを実現するための手法の一つとして、p型GaN層を電子供給層上に形成し、バンド変調効果により2DEGの濃度を制御する手法が提案されている。

【0006】

しかしながら、GaNは、技術的な歴史の長いSiと比較して製造技術が未熟な材料であるため、p型GaNの構造を最適化することが困難である。例えば、Siでは高度なイオン打ち込み技術を用いて、縦方向に長くp型イオン打ち込み層があるスーパージャンクション構造を作製することが可能であるが、GaNではイオン打ち込み技術自体が未完成である。

その一方で、RF分野ではGaN−HEMTは既に実用化されており、イオン打ち込み技術等の製造技術が成熟し、Siのデバイス構造を使用できるのを待つことなく、上記の問題を解決する半導体市場からの強い要請がある。

【0007】

本発明は、上記の課題に鑑みてなされたものであり、第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

化合物半導体装置の一態様は、第1の極性を有する第1の化合物半導体層と、前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層とを含み、前記第3の化合物半導体層は、厚みの異なる部位を有する。

【0009】

化合物半導体装置の製造方法の一態様は、第1の極性を有する第1の化合物半導体層を形成する工程と、前記第1の半導体層の上方に、第2の極性を有する第2の化合物半導体層を形成する工程と、前記第2の半導体層の上方に、第2の極性を有する第3の化合物半導体層を形成する工程と、前記第3の化合物半導体層に、厚みの異なる部位を形成する工程とを含む。

【発明の効果】

【0010】

上記の各態様によれば、第1の極性を有する第1の化合物半導体層と共にこれと逆導電型(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置が実現する。

【図面の簡単な説明】

【0011】

【図1】第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図2】図1に引き続き、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図3】図2に引き続き、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図4】第1の実施形態によるAlGaN/GaN・HEMTの構成を示す概略平面図である。

【図5】第1の実施形態において、ドレイン−ソース間電圧Vdsとドレイン電流Idとの関係について調べた結果を示す特性図である。

【図6】第1の実施形態において、ドレイン−ソース間電圧Vdsを印加し続け、破壊が起こるまでの時間について調べた結果を示す特性図である。

【図7】第1の実施形態において、非動作時における2DEGの濃度について調べた結果を示す特性図である。

【図8】第1の実施形態によるAlGaN/GaN・HEMTを用いたHEMTチップを示す概略平面図である。

【図9】第1の実施形態によるAlGaN/GaN・HEMTを用いたディスクリートパッケージを示す概略平面図である。

【図10】第2の実施形態によるAlGaN/GaN・ダイオードの製造方法の主要工程を示す概略断面図である。

【図11】図10に引き続き、第2の実施形態によるAlGaN/GaN・ダイオードの製造方法の主要工程を示す概略断面図である。

【図12】図11に引き続き、第2の実施形態によるAlGaN/GaN・ダイオードの製造方法の主要工程を示す概略断面図である。

【図13】第2の実施形態において、アノード−カソード間順電圧Vacとアノード電流Iaとの関係について調べた結果を示す特性図である。

【図14】アノード−カソード間に逆電圧を印加し続け、破壊が起こるまでの時間について調べた結果を示す特性図である。

【図15】第2の実施形態によるAlGaN/GaN・ダイオードを用いたダイオードチップを示す概略平面図である。

【図16】第2の実施形態によるAlGaN/GaN・ダイオードを用いたディスクリートパッケージを示す概略平面図である。

【図17】第3の実施形態によるPFC回路を示す結線図である。

【図18】第4の実施形態による電源装置の概略構成を示す結線図である。

【図19】第5の実施形態による高周波増幅器の概略構成を示す結線図である。

【発明を実施するための形態】

【0012】

以下、諸実施形態について図面を参照して詳細に説明する。以下の諸実施形態では、化合物半導体装置の構成について、その製造方法と共に説明する。

なお、以下の図面において、図示の便宜上、相対的に正確な大きさ及び厚みに示していない構成部材がある。

【0013】

(第1の実施形態)

本実施形態では、化合物半導体装置としてAlGaN/GaN・HEMTを開示する。

図1〜図3は、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【0014】

先ず、図1(a)に示すように、成長用基板として例えばSi基板1上に、化合物半導体積層構造2を形成する。成長用基板としては、Si基板の代わりに、サファイア基板、GaAs基板、SiC基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

【0015】

化合物半導体積層構造2は、バッファ層2a、電子走行層2b、中間層(スペーサ層)2c、電子供給層2d、p型キャップ層2e、及びn型キャップ層2fを有して構成される。ここで、電子走行層2bは、後述するように中間層2cとの界面に2次元電子ガスが発生する負の極性を有しており、同様にn型キャップ層2fも導電型がn型であるため負の極性を有する。これに対して、p型キャップ層2eは、導電型がn型と逆のp型であるため、正の極性を有する。

【0016】

詳細には、Si基板1上に、例えば有機金属気相成長(MOVPE:Metal Organic Vapor Phase Epitaxy)法により、以下の各化合物半導体を成長する。MOVPE法の代わりに、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法等を用いても良い。

Si基板1上に、バッファ層2a、電子走行層2b、中間層2c、電子供給層2d、p型キャップ層2e、及びn型キャップ層2fとなる各化合物半導体を順次成長する。バッファ層2aは、Si基板1上に、AlNを0.1μm程度の厚みに成長することで形成される。電子走行層2bは、i(インテンショナリ・アンドープ)−GaNを1μm程度〜3μm程度の厚みに成長することで形成される。中間層2cは、i−AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2dは、n−AlGaNを30nm程度の厚みに成長することで形成される。中間層2cは形成しない場合もある。電子供給層は、i−AlGaNを形成するようにしても良い。

【0017】

p型キャップ層2eは、p−GaNを、例えば10nm程度〜1000nm程度に成長することで形成される。10nmよりも薄いと、所期のノーマリオフ動作が得られなくなる。1000nmよりも厚いと、ゲート電極からチャネルであるAlGaN/GaNへテロ界面までの距離が長くなって応答速度が低下し、チャネルにおけるゲート電極からの電界が不十分になり、ピンチオフ不良等の劣化が惹起される。従って、p型キャップ層2eを10nm程度〜1000nm程度に形成することにより、十分なノーマリオフ動作を得るも、高速の応答速度を確保し、ピンチオフ不良等のデバイス特性の劣化を抑止することができる。本実施形態では、p型キャップ層2eのp−GaNは200nm程度の厚みに形成される。

n型キャップ層2fは、p型キャップ層2eとの関係で、n−GaNを例えば5nm程度〜500nm程度、ここでは100nm程度の厚みに成長することで形成される。

【0018】

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH3)ガスの混合ガスを用いる。AlGaNの成長には、原料ガスとしてTMAlガス、TMGaガス及びNH3ガスの混合ガスを用いる。成長する化合物半導体層に応じて、TMAlガス、TMGaガスの供給の有無及び流量を適宜設定する。共通原料であるNH3ガスの流量は、100sccm〜10slm程度とする。また、成長圧力は50Torr〜300Torr程度、成長温度は1000℃〜1200℃程度とする。

【0019】

AlGaN、GaNをn型として成長する際、即ち電子供給層2d(n−AlGaN)、n型キャップ層2f(n−GaN)の形成には、n型不純物をAlGaN、GaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン(SiH4)ガスを所定の流量で原料ガスに添加し、AlGaN、GaNにSiをドーピングする。Siのドーピング濃度は、1×1018/cm3程度〜1×1020/cm3程度、例えば2×1018/cm3程度とする。

【0020】

GaNをp型として成長する際、即ちp型キャップ層2e(p−GaN)の形成には、p型不純物、例えばMg,Cから選ばれたものをGaNの原料ガスに添加する。本実施形態では、p型不純物としてMgを用いる。Mgを所定の流量で原料ガスに添加し、GaNにMgをドーピングする。Mgのドーピング濃度は、例えば1×1016/cm3程度〜1×1021/cm3程度とする。ドーピング濃度が1×1016/cm3程度よりも低いと、十分なp型とならず、ノーマリオンとなる。1×1021/cm3程度よりも高いと、結晶性が崩れ、十分な特性が得られなくなる。従って、Mgのドーピング濃度を1×1016/cm3程度〜1×1021/cm3程度とすることにより、十分にノーマリオフ特性の得られるp型半導体となる。本実施形態では、p型キャップ層2eのMgのドーピング濃度を1×1019/cm3程度とする。

【0021】

形成された化合物半導体積層構造2では、負の極性を有する電子走行層2bの電子供給層2dとの界面(正確には、中間層2cとの界面。以下、GaN/AlGaN界面と記す。)には、GaNの格子定数とAlGaNの格子定数との差に起因した歪みによるピエゾ分極が生じる。このピエゾ分極の効果と、電子走行層2b及び電子供給層2dの自発分極の効果とが相俟って、GaN/AlGaN界面に高い電子濃度の2次元電子ガス(2DEG)が発生する。

【0022】

化合物半導体積層構造2を形成した後に、p型キャップ層2eを、700℃程度で30分間程度、アニール処理する。

【0023】

図1(b)に示すように、素子分離構造3を形成する。図1(c)以降では、素子分離構造3の図示を省略する。

詳細には、化合物半導体積層構造2の素子分離領域に、例えばアルゴン(Ar)を注入する。これにより、化合物半導体積層構造2及びSi基板1の表層部分に素子分離構造3が形成される。素子分離構造3により、化合物半導体積層構造2上で活性領域が画定される。

なお、素子分離は、上記の注入法の代わりに、例えばSTI(Shallow Trench Isolation)法等既知の他の方法を用いて行っても良い。このとき、化合物半導体積層構造2のドライエッチングには、例えば塩素系のエッチングガスを用いる。

【0024】

続いて、図1(c)〜図3(a)に示すように、n型キャップ層2fを所期形状にエッチング加工する。

詳細には、先ず、図1(c)に示すように、n型キャップ層2f上にレジストを塗布し、リソグラフィーにより加工する。これにより、n型キャップ層2fの表面のゲート電極の形成予定位置を露出させる開口10Aaを有するレジストマスク10Aが形成される。

【0025】

次に、図2(a)に示すように、レジストマスク10Aを用い、Cl2ガスをエッチングガスとして用いて、反応性イオンエッチング(RIE)によりn型キャップ層2fをエッチング加工する。これにより、n型キャップ層2fに、p型キャップ層2eの表面のゲート電極の形成予定位置を露出させる開口2faが形成される。開口2faは、ドレイン電極の形成予定位置よりも、ソース電極の形成予定位置に偏倚した所定部位に形成される。

レジストマスク10Aは、アッシング処理又は所定の薬液を用いたウェット処理により、除去される。

【0026】

n型キャップ層2fに開口2faが形成された化合物半導体積層構造2においては、開口2faではn型キャップ層2fのn−GaNが存在しない。そのため、p型キャップ層2eのp−GaNにより、GaN/AlGaN界面の開口2faの下方に相当する部位では、2DEGが殆ど消失する。図示の例では、2DEGが消失した場合を示す。

【0027】

次に、図2(b)に示すように、開口2faを埋め込むようにn型キャップ層2f上にレジストを塗布し、リソグラフィーにより加工する。これにより、n型キャップ層2fの表面のフィールドプレート電極の形成予定位置を露出させる開口10Baを有するレジストマスク10Bが形成される。

【0028】

次に、図2(c)に示すように、レジストマスク10Bを用い、Cl2ガスをエッチングガスとして用いて、RIEによりn型キャップ層2fをエッチング加工する。これにより、n型キャップ層2fのフィールドプレート電極の形成予定位置が、所期の厚みに薄化される。薄化部分2fbは、開口2faとドレイン電極の形成予定位置との間で、ソース電極の形成予定位置よりもドレイン電極の形成予定位置に偏倚した所定部位に形成される。この薄化部分2fbは、フィールドプレート電極による2DEG量の所期の制御を考慮して、n型キャップ層2fの厚みの半分程度、例えば50nm程度の厚みとされる。なお、例えばダイオードとしてのみ用いる場合には、このn型キャップ層2fの薄化工程は不要であることがある。

【0029】

n型キャップ層2fに薄化部分2fbが形成された化合物半導体積層構造2において、薄化部分2fbではn型キャップ層2fのその他の部分(開口2faは除く)よりもn−GaNが薄い。そのため、p型キャップ層2eのp−GaNにより、GaN/AlGaN界面の薄化部分2fbの下方に相当する部位では、図示のように、薄化部分2fbの薄化に相当する分だけ2DEGが減少する。

【0030】

そして、図3(a)に示すように、レジストマスク10Bを、アッシング処理又は所定の薬液を用いたウェット処理により除去する。以上により、n型キャップ層2fは、開口2fa及び薄化部分2fbが形成された状態で露出する。

【0031】

続いて、図3(b)に示すように、ソース電極4及びドレイン電極5を形成する。

詳細には、先ず、化合物半導体積層構造2の表面におけるソース電極及びドレイン電極の形成予定位置(電極形成予定位置)に電極用リセス2A,2Bを形成する。

化合物半導体積層構造2の表面にレジストを塗布する。レジストをリソグラフィーにより加工し、レジストに、電極形成予定位置に相当する化合物半導体積層構造2の表面を露出する開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

【0032】

このレジストマスクを用いて、電子供給層2dの表面が露出するまで、n型キャップ層2f及びp型キャップ層2eの電極形成予定位置をドライエッチングして除去する。これにより、電子供給層2dの表面の電極形成予定位置を露出する電極用リセス2A,2Bが形成される。エッチング条件としては、Ar等の不活性ガス及びCl2等の塩素系ガスをエッチングガスとして用い、例えばCl2を流量30sccm、圧力を2Pa、RF投入電力を20Wとする。なお、電極用リセス2A,2Bは、例えば電子供給層2d以降までエッチングして形成しても良い。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0033】

ソース電極及びドレイン電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、電極用リセス2A,2Bを露出させる開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電極材料として、例えばTa/Alを、例えば蒸着法により、電極用リセス2A,2Bを露出させる開口内を含むレジストマスク上に堆積する。Taの厚みは20nm程度、Alの厚みは200nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したTa/Alを除去する。その後、Si基板1を、例えば窒素雰囲気中において400℃〜1000℃の温度、例えば600℃程度で熱処理し、残存したTa/Alを電子供給層2dとオーミックコンタクトさせる。Ta/Alの電子供給層2dとのオーミックコンタクトが得られるのであれば、熱処理が不要な場合もある。以上により、電極用リセス2A,2Bを電極材料の一部で埋め込むソース電極4及びドレイン電極5が形成される。

【0034】

続いて、図3(c)に示すように、ゲート電極6及びフィールドプレート電極7を形成する。

詳細には、先ず、ゲート電極及びフィールドプレート電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、開口2fa及び薄化部分2fbを露出させる各開口を形成する。以上により、当該各開口を有するレジストマスクが形成される。

【0035】

このレジストマスクを用いて、電極材料として、例えばNi/Auを、例えば蒸着法により、n型キャップ層2fの開口2fa及び薄化部分2fbを露出させる各開口内を含むレジストマスク上に堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したNi/Auを除去する。以上により、n型キャップ層2fの開口2fa内を電極材料の一部で埋め込むゲート電極6と、n型キャップ層2fの薄化部分2fb上の窪みを電極材料の一部で埋め込むフィールドプレート電極7がそれぞれ形成される。

【0036】

フィールドプレート電極7は、ゲート電極6とドレイン電極5との間に、ソース電極4よりもドレイン電極5に向かって偏倚した位置に形成される。AlGaN/GaN・HEMTでは、ソース電極及びゲート電極に比してドレイン電極に大きな電圧が印加される場合があるが、この構成を採ることにより、大きな電圧印加で発生する電界をフィールドプレート電極7で緩和することができる。

【0037】

しかる後、ソース電極4、ドレイン電極5、ゲート電極6の電気的接続、ソース電極4、ドレイン電極5、ゲート電極6の各パッドの形成等の諸工程を経て、本実施形態によるAlGaN/GaN・HEMTが形成される。

【0038】

本実施形態によるAlGaN/GaN・HEMTを平面視した様子を図4に示す。

図4の破線I−I'に沿った断面が図3(c)に相当する。このように、ソース電極4とドレイン電極5とが櫛歯状に互いに平行に形成されており、ソース電極4とドレイン電極5との間に櫛歯状のゲート電極6がこれらと平行に配されている。

【0039】

なお本実施形態では、ゲート電極が化合物半導体と直接的に接触するショットキー型のAlGaN/GaN・HEMTに例示したが、ゲート電極が化合物半導体との間でゲート絶縁膜を介するMIS型のAlGaN/GaN・HEMTにも適用できる。MIS型のAlGaN/GaN・HEMTを作製する場合には、図2(a)の工程の後に開口2faの側壁面を覆うようにn型キャップ層2f上にゲート絶縁膜を形成し、図2(c)の工程でゲート絶縁膜を貫通すると共に薄化部分2fbを形成する。そして、図3(c)の工程でゲート電極及びフィールドプレート電極を形成すれば良い。

【0040】

本実施形態によるAlGaN/GaN・HEMTでは、2DEGの濃度を制御するために、p−GaNのキャップ層をエッチングしたり、p−GaNを再成長することなく、p型キャップ層2eはそのままでその上のn型キャップ層2fを適宜エッチング加工する。これにより、n型キャップ層2fの厚みでp型キャップ層2eのp型不純物(ここではMg)の量を実効的にコントロールし、容易且つ確実に、フィールドプレート電極7で2DEGの濃度を制御しつつ、所期のノーマリオフ動作が実現する。即ち、ゲート電圧のオフ時にはチャネルには2DEGがなくノーマリオフとなり、ゲート電圧のオン時にはチャネルに所期の2DEGが生成されて駆動する。

【0041】

フィールドプレート電極7の下方では、p型キャップ層2eのp−GaNと電子供給層2dのn−AlGaNとがpn接合している。p型キャップ層2eがn型キャップ層2fとの関係で空乏化し、空乏層が伸びて拡大する。これにより、耐圧が大幅に向上すると共に、寄生容量Cds,Cgdが大幅に低減し、デバイス動作の高速化が実現する。

【0042】

更に本実施形態では、フィールドプレート電極7の下方におけるp型キャップ層2eと電子供給層2dとのpn接合により、フィールドプレート電極7がアノード、ドレイン電極5がカソードとなる保護ダイオードの機能が付与される。この保護ダイオードの整流作用により、AlGaN/GaN・HEMTにサージ電圧が生じても、AlGaN/GaN・HEMTの破壊が抑止される。このように、アバランシェ耐量が十分に確保され、デバイス動作の安定化に寄与する。

【0043】

ここで、本実施形態によるAlGaN/GaN・HEMTの諸特性について調べた諸実験について説明する。本実施形態の比較例として、n−GaNのn型キャップ層上にp−GaNを成長し、p−GaNの不要部分をエッチング除去した後、Mg濃度の異なるp−GaNを再成長し、一括熱アニール処理を行なって作製したAlGaN/GaN・HEMTを例示する。

【0044】

実験1では、ドレイン−ソース間電圧Vdsとドレイン電流Idとの関係について調べた。実験結果を図5に示す。本実施形態では、比較例とは異なり、動作時において非動作時と殆ど変わらない波形を示している。この結果から、本実施形態では、比較例に比して動作時の電流低減を抑止する大幅な改善が確認された。

【0045】

実験2では、ドレイン−ソース間電圧Vdsを印加し続け、破壊が起こるまでの時間(オフストレス試験)について調べた。ここでは、温度200℃でVdsを600V、ゲート−ソース間電圧Vgsを0Vとした。実験結果を図6に示す。この結果から、本実施形態では、比較例に比して破壊までの時間が増加し、デバイスの信頼性が向上することが確認された。

【0046】

実験3では、本実施形態によるAlGaN/GaN・HEMTについて、非動作時における2DEGの濃度について調べた。実験結果を図7に示す。本実施形態において、ゲート電極の下方に相当する部位では、2DEGの濃度が十分小さい値となっており、ノーマリオフが実現している。フィールドプレート電極の下方に相当する部位では、2DEGの濃度が所期の値に変調されていることが判る。

【0047】

以上説明したように、本実施形態によれば、n型キャップ層2fと共にp型キャップ層2eを用い、動作時におけるオン抵抗の増加を抑え、また作製時にp−GaNの再成長をすることなく、実効的にp型不純物のドーピング量が容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧のAlGaN/GaN・HEMTが実現する。

【0048】

本実施形態によるAlGaN/GaN・HEMTは、いわゆるディスクリートパッケージに適用される。

このディスクリートパッケージでは、本実施形態によるAlGaN/GaN・HEMTのチップが搭載される。以下、本実施形態によるAlGaN/GaN・HEMTのチップ(以下、HEMTチップと言う)のディスクリートパッケージについて例示する。

【0049】

HEMTチップの概略構成(図4に対応する)を図8に示す。

HEMTチップ100では、その表面に、上述したAlGaN/GaN・HEMTのトランジスタ領域101と、ドレイン電極が接続されたドレインパッド102と、ゲート電極が接続されたゲートパッド103と、ソース電極が接続されたソースパッド104とが設けられている。

【0050】

図9は、ディスクリートパッケージを示す概略平面図である。

ディスクリートパッケージを作製するには、先ず、HEMTチップ100を、ハンダ等のダイアタッチ剤111を用いてリードフレーム112に固定する。リードフレーム112にはドレインリード112aが一体形成されており、ゲートリード112b及びソースリード112cがリードフレーム112と別体として離間して配置される。

【0051】

続いて、Alワイヤ113を用いたボンディングにより、ドレインパッド102とドレインリード112a、ゲートパッド103とゲートリード112b、ソースパッド104とソースリード112cをそれぞれ電気的に接続する。

その後、モールド樹脂114を用いて、トランスファーモールド法によりHEMTチップ100を樹脂封止し、リードフレーム112を切り離す。以上により、ディスクリートパッケージが形成される。

【0052】

(第2の実施形態)

本実施形態では、化合物半導体装置として、AlGaN/GaNの高電子移動度ダイオード(以下、単にAlGaN/GaN・ダイオードと記す。)を開示する。

図10〜図12は、第2の実施形態によるAlGaN/GaN・ダイオードの製造方法を工程順に示す概略断面図である。

【0053】

先ず、図10(a)に示すように、成長用基板として例えばSi基板1上に、化合物半導体積層構造21を形成する。成長用基板としては、Si基板の代わりに、サファイア基板、GaAs基板、SiC基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

化合物半導体積層構造21は、バッファ層21a、電子走行層21b、中間層(スペーサ層)21c、電子供給層21d、p型キャップ層21e、及びn型キャップ層21fを有して構成される。

【0054】

詳細には、Si基板1上に、例えばMOVPE法により、以下の各化合物半導体を成長する。MOVPE法の代わりに、MBE法等を用いても良い。

SiC基板21上に、バッファ層21a、電子走行層21b、中間層21c、電子供給層21d、p型キャップ層21e、及びn型キャップ層21fとなる各化合物半導体を順次成長する。バッファ層21aは、Si基板1上に、AlNを0.1μm程度の厚みに成長することで形成される。電子走行層21bは、i−GaNを1μm程度〜3μm程度の厚みに成長することで形成される。中間層21cは、i−AlGaNを5nm程度の厚みに成長することで形成される。電子供給層21dは、n−AlGaNを30nm程度の厚みに成長することで形成される。中間層21cは形成しない場合もある。電子供給層は、i−AlGaNを形成するようにしても良い。

【0055】

p型キャップ層21eは、p−GaNを、例えば10nm程度〜1000nm程度に成長することで形成される。10nmよりも薄いと、所期の2DEGの減少効果が得られなくなる。1000nmよりも厚いと、2DEGが減少しすぎて、オン抵抗が上昇してしまう。従って、p型キャップ層21eを10nm程度〜1000nm程度に形成することにより、十分な2DEGの減少効果を得るも、オン抵抗の減少を抑制することができる。本実施形態では、p型キャップ層21eのp−GaNは200nm程度の厚みに形成される。

n型キャップ層21fは、p型キャップ層21eとの関係で、n−GaNを例えば5nm程度〜500nm程度、ここでは100nm程度の厚みに成長することで形成される。

【0056】

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH3)ガスの混合ガスを用いる。AlGaNの成長には、原料ガスとしてTMAlガス、TMGaガス及びNH3ガスの混合ガスを用いる。成長する化合物半導体層に応じて、TMAlガス、TMGaガスの供給の有無及び流量を適宜設定する。共通原料であるNH3ガスの流量は、100sccm〜10slm程度とする。また、成長圧力は50Torr〜300Torr程度、成長温度は1000℃〜1200℃程度とする。

【0057】

AlGaN、GaNをn型として成長する際、即ち電子供給層21d(n−AlGaN)、n型キャップ層21f(n−GaN)の形成には、n型不純物をAlGaN、GaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン(SiH4)ガスを所定の流量で原料ガスに添加し、AlGaN、GaNにSiをドーピングする。Siのドーピング濃度は、1×1018/cm3程度〜1×1020/cm3程度、例えば2×1018/cm3程度とする。

【0058】

GaNをp型として成長する際、即ちp型キャップ層21e(p−GaN)の形成には、p型不純物、例えばMg,Cから選ばれたものをGaNの原料ガスに添加する。本実施形態では、p型不純物としてMgを用いる。Mgを所定の流量で原料ガスに添加し、GaNにMgをドーピングする。Mgのドーピング濃度は、例えば1×1016/cm3程度〜1×1021/cm3程度とする。ドーピング濃度が1×1016/cm3程度よりも低いと、十分なp型とならない。1×1021/cm3程度よりも高いと、結晶性が崩れ、十分な特性が得られなくなる。従って、Mgのドーピング濃度を1×1016/cm3程度〜1×1021/cm3程度とすることにより、十分な特性の得られるp型半導体となる。

【0059】

形成された化合物半導体積層構造21では、電子走行層21bの電子供給層21dとの界面(正確には、中間層21cとの界面。以下、GaN/AlGaN界面と記す。)には、GaNの格子定数とAlGaNの格子定数との差に起因した歪みによるピエゾ分極が生じる。このピエゾ分極の効果と、電子走行層21b及び電子供給層21dの自発分極の効果とが相俟って、GaN/AlGaN界面に高い電子濃度の2次元電子ガス(2DEG)が発生する。

【0060】

化合物半導体積層構造21を形成した後に、p型キャップ層21eを、700℃程度で30分間程度、アニール処理する。

【0061】

続いて、図10(b)〜図11(c)に示すように、n型キャップ層2fを所期形状にエッチング加工する。

詳細には、先ず、図10(b)に示すように、n型キャップ層2f上にレジストを塗布し、リソグラフィーにより加工する。これにより、n型キャップ層2fの表面のアノード電極の形成予定位置よりもカソード電極の形成予定位置に偏倚した所定部位を露出させる開口20Aaを有するレジストマスク20Aが形成される。

【0062】

次に、図10(c)に示すように、レジストマスク20Aを用い、Cl2ガスをエッチングガスとして用いて、RIEによりn型キャップ層21fをエッチング加工する。これにより、n型キャップ層21fに、p型キャップ層21eの表面の所定部位を露出させる開口21faが形成される。

レジストマスク20Aは、アッシング処理又は所定の薬液を用いたウェット処理により、除去される。

【0063】

n型キャップ層21fに開口21faが形成された化合物半導体積層構造21において、開口21faではn型キャップ層21fのn−GaNが存在しない。そのため、p型キャップ層2eのp−GaNにより、GaN/AlGaN界面の開口2faの下方に相当する部位では、図示のように2DEGが殆ど消失し、例えば所定の少量だけ存在する。

【0064】

次に、図11(a)に示すように、開口21faを埋め込むようにn型キャップ層21f上にレジストを塗布し、リソグラフィーにより加工する。これにより、n型キャップ層21fの表面の開口21faに隣接するアノード電極の形成予定位置側の所定部位を露出させる開口20Baを有するレジストマスク20Bが形成される。

【0065】

次に、図11(b)に示すように、レジストマスク20Bを用い、Cl2ガスをエッチングガスとして用いて、RIEによりn型キャップ層21fをエッチング加工する。これにより、n型キャップ層21fの所定部位が、所期の厚みに薄化される。この薄化部分21fbは、AlGaN/GaN・ダイオードにおける2DEG量の所期の制御を考慮して、n型キャップ層21fの厚みの半分程度、例えば50nm程度の厚みとされる。

【0066】

n型キャップ層21fに薄化部分21fbが形成された化合物半導体積層構造21において、薄化部分21fbではn型キャップ層21fのその他の部分(開口21faは除く)よりもn−GaNが薄い。そのため、p型キャップ層21eのp−GaNにより、GaN/AlGaN界面の薄化部分21fbの下方に相当する部位では、図示のように、薄化部分21fbの薄化に相当する分だけ2DEGが減少する。

レジストマスク20Bは、アッシング処理又は所定の薬液を用いたウェット処理により、除去される。

【0067】

次に、図11(c)に示すように、化合物半導体積層構造21の表面におけるカソード電極及びアノード電極の形成予定位置に電極用リセス21A,21Bを形成する。

このレジストマスクを用いて、電子供給層21dの表面が露出するまで、n型キャップ層21f及びp型キャップ層21eの各電極形成予定位置をドライエッチングして除去する。これにより、電子供給層21dの表面の各電極形成予定位置を露出する電極用リセス21A,21Bが形成される。このとき、n型キャップ層21fは、n型キャップ層21f上に階段形状に残存する。エッチング条件としては、Ar等の不活性ガス及びCl2等の塩素系ガスをエッチングガスとして用い、例えばCl2を流量30sccm、圧力を2Pa、RF投入電力を20Wとする。なお、電極用リセス2A,2Bは、例えば電子供給層2d以降までエッチングして形成しても良い。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0068】

以上により、n型キャップ層21fは、p型キャップ層21e上で階段形状に残存する。p型キャップ層21eにおいて、2DEGは、n型キャップ層21fの厚みに対応して変調されている。即ち、p型キャップ層21eの電極用リセス2A側の端部から電極用リセス2B側の端部へ向かうについて、2DEGの濃度が段階的に増加している。このように、カソード電極側では2DEGの濃度を低く、アノード電極側では2DEGの濃度を高く分布させる(カソード電極側からアノード電極側へ2DEGの濃度を徐々に高く分布させる)ことにより、所期の高耐圧のAlGaN/GaN・ダイオードが実現する。

【0069】

続いて、図12(a)に示すように、カソード電極23を形成する。

詳細には、先ず、カソード電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、電極用リセス21Aを露出させる開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電極材料として、例えばTa/Alを、例えば蒸着法により、電極用リセス2Aを露出させる開口内を含むレジストマスク上に堆積する。Taの厚みは20nm程度、Alの厚みは200nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したTa/Alを除去する。以上により、電極用リセス21Aを電極材料の一部で埋め込むカソード電極23が形成される。

【0070】

続いて、図12(b)に示すように、アノード電極24を形成する。

詳細には、先ず、アノード電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体積層構造2上に塗布し、電極用リセス21Bを露出させる開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電極材料として、例えばNiを、例えば蒸着法により、電極用リセス2Bを露出させる開口内を含むレジストマスク上に堆積する。Niの厚みは30nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したNiを除去する。以上により、電極用リセス21Bを電極材料の一部で埋め込むアノード電極24が形成される。

【0071】

しかる後、カソード電極23、アノード電極24の電気的接続、カソード電極23、アノード電極24の各パッドの形成等の諸工程を経て、本実施形態によるAlGaN/GaN・ダイオードが形成される。

【0072】

本実施形態によるAlGaN/GaN・ダイオードでは、2DEGの濃度を制御するために、p−GaNのキャップ層をエッチングしたり、p−GaNを再成長することなく、p型キャップ層21eはそのままでその上のn型キャップ層21fを適宜エッチング加工する。これにより、n型キャップ層21fの厚みでp型キャップ層21eのp型不純物(ここではMg)の量を実効的にコントロールし、容易且つ確実に、2DEGの濃度を制御しつつ、所期の高耐圧が実現する。

【0073】

ここで、本実施形態によるAlGaN/GaN・ダイオードの諸特性について調べた諸実験について説明する。本実施形態の比較例として、n−GaNのn型キャップ層上にp−GaNを成長し、p−GaNの不要部分をエッチング除去した後、Mg濃度の異なるp−GaNを再成長し、一括熱アニール処理を行なって作製したAlGaN/GaN・ダイオードを例示する。

【0074】

実験1では、アノード−カソード間順電圧Vacとアノード電流Iaとの関係について調べた。実験結果を図13に示す。本実施形態では、比較例とは異なり、動作時において非動作時と殆ど変わらない波形を示している。この結果から、本実施形態では、比較例に比して動作時の電流低減を抑止する大幅な改善が確認された。

【0075】

実験2では、アノード−カソード間に逆電圧を印加し続け、破壊が起こるまでの時間について調べた。ここでは、温度200℃でVacを600Vとした。実験結果を図14に示す。この結果から、本実施形態では、比較例に比して破壊までの時間が増加し、デバイスの信頼性が向上することが確認された。

【0076】

以上説明したように、本実施形態によれば、n型キャップ層2fと共にp型キャップ層2eを用い、動作時におけるオン抵抗の増加を抑え、また作製時にp−GaNの再成長をすることなく、実効的にp型不純物のドーピング量が容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧のAlGaN/GaN・ダイオードが実現する。

【0077】

本実施形態によるAlGaN/GaN・ダイオードは、いわゆるディスクリートパッケージに適用される。

このディスクリートパッケージでは、本実施形態によるAlGaN/GaN・ダイオードのチップが搭載される。以下、本実施形態によるAlGaN/GaN・のダイオードチップ(以下、ダイオードチップと言う)のディスクリートパッケージについて例示する。

【0078】

ダイオードチップの概略構成を図15に示す。

ダイオードチップ200では、その表面に、上述したAlGaN/GaN・ダイオードのダイオード領域201と、カソード電極が接続されたカソードパッド202と、アノード電極が接続されたアノードパッド203とが設けられている。

【0079】

図16は、ディスクリートパッケージを示す概略平面図である。

ディスクリートパッケージを作製するには、先ず、ダイオードチップ200を、ハンダ等のダイアタッチ剤211を用いてリードフレーム212に固定する。リードフレーム212と別体として、カソードリード212a及びアノードリード212bがリードフレーム212から離間して配置される。

【0080】

続いて、Alワイヤ213を用いたボンディングにより、カソードパッド202とカソードリード212a、アノードパッド203とアノードリード212bをそれぞれ電気的に接続する。

その後、モールド樹脂214を用いて、トランスファーモールド法によりダイオードチップ200を樹脂封止し、リードフレーム212を切り離す。以上により、ディスクリートパッケージが形成される。

【0081】

(第3の実施形態)

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMT又は第2の実施形態によるAlGaN/GaN・ダイオード、或いは双方を備えたPFC(Power Factor Correction)回路を開示する。

図17は、PFC回路を示す結線図である。

【0082】

PFC回路30は、スイッチ素子(トランジスタ)31と、ダイオード32と、チョークコイル33と、コンデンサ34,35と、ダイオードブリッジ36と、交流電源(AC)37とを備えて構成される。スイッチ素子31に、第1の実施形態によるAlGaN/GaN・HEMTが適用される。又は、ダイオード32に、第2の実施形態によるAlGaN/GaN・ダイオードが適用される。或いは、スイッチ素子31に第1の実施形態によるAlGaN/GaN・HEMTが、ダイオード32に第2の実施形態によるAlGaN/GaN・ダイオードがそれぞれ適用される。また、ダイオードブリッジ36にも第2の実施形態によるAlGaN/GaN・ダイオードを適用しても良い。

【0083】

PFC回路30では、スイッチ素子31のドレイン電極と、ダイオード32のアノード端子及びチョークコイル33の一端子とが接続される。スイッチ素子31のソース電極と、コンデンサ34の一端子及びコンデンサ35の一端子とが接続される。コンデンサ34の他端子とチョークコイル33の他端子とが接続される。コンデンサ35の他端子とダイオード32のカソード端子とが接続される。コンデンサ34の両端子間には、ダイオードブリッジ36を介してAC37が接続される。コンデンサ35の両端子間には、直流電源(DC)が接続される。なお、スイッチ素子31には不図示のPFCコントローラが接続される。

【0084】

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMT及び第2の実施形態によるAlGaN/GaN・ダイオードの一方又は双方をPFC回路30に適用する。これにより、信頼性の高いPFC回路30が実現する。

【0085】

(第4の実施形態)

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMT、更には第2の実施形態によるAlGaN/GaN・ダイオードを備えた電源装置を開示する。

図18は、第4の実施形態による電源装置の概略構成を示す結線図である。

【0086】

本実施形態による電源装置は、高圧の一次側回路41及び低圧の二次側回路42と、一次側回路41と二次側回路42との間に配設されるトランス43とを備えて構成される。

一次側回路41は、第3の実施形態によるPFC回路30と、PFC回路30のコンデンサ35の両端子間に接続されたインバータ回路、例えばフルブリッジインバータ回路40とを有している。フルブリッジインバータ回路40は、複数(ここでは4つ)のスイッチ素子44a,44b,44c,44dを備えて構成される。

二次側回路42は、複数(ここでは3つ)のスイッチ素子45a,45b,45cを備えて構成される。

【0087】

本実施形態では、一次側回路41を構成するPFC回路が第3の実施形態によるPFC回路30であると共に、フルブリッジインバータ回路40のスイッチ素子44a,44b,44c,44dが、第1の実施形態によるAlGaN/GaN・HEMTとされている。一方、二次側回路42のスイッチ素子45a,45b,45cは、シリコンを用いた通常のMIS・FETとされている。

【0088】

第1の実施形態及びその諸変形例から選ばれたAlGaN/GaN・HEMTでは、第1の実施形態で説明したように、フィールドプレート電極の下方でpn接合が形成される。これにより、フィールドプレート電極がアノード、ドレイン電極がカソードとなる保護ダイオードの機能が付与される。本実施形態では、このAlGaN/GaN・HEMTをPFC回路30のスイッチ素子31及びフルブリッジインバータ回路40のスイッチ素子44a,44b,44c,44dに適用している。そのため、一次側回路41において、スイッチ素子31,44a,44b,44c,44dにサージ電圧が生じても、保護ダイオードの整流作用により、スイッチ素子31,44a,44b,44c,44dの破壊が抑止される。このように、大きなアバランシェ耐量が確保され、デバイス動作の安定化に寄与する。

【0089】

本実施形態では、第3の実施形態によるPFC回路30と、第1の実施形態によるAlGaN/GaN・HEMT、更には第2の実施形態によるAlGaN/GaN・ダイオードとを、高圧回路である一次側回路41に適用する。これにより、信頼性の高い大電力の電源装置が実現する。

【0090】

(第5の実施形態)

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMTを備えた高周波増幅器を開示する。

図19は、第5の実施形態による高周波増幅器の概略構成を示す結線図である。

【0091】

本実施形態による高周波増幅器は、ディジタル・プレディストーション回路51と、ミキサー52a,52bと、パワーアンプ53とを備えて構成される。

ディジタル・プレディストーション回路51は、入力信号の非線形歪みを補償するものである。ミキサー52aは、非線形歪みが補償された入力信号と交流信号をミキシングするものである。パワーアンプ53は、交流信号とミキシングされた入力信号を増幅するものであり、第1の実施形態によるAlGaN/GaN・HEMTを有している。なお図19では、例えばスイッチの切り替えにより、出力側の信号をミキサー52bで交流信号とミキシングしてディジタル・プレディストーション回路51に送出できる構成とされている。

【0092】

本実施形態では、第1の実施形態によるAlGaN/GaN・HEMTを高周波増幅器に適用する。これにより、信頼性の高い高耐圧の高周波増幅器が実現する。

【0093】

(他の実施形態)

第1の実施形態では、化合物半導体装置としてAlGaN/GaN・HEMTを例示した。化合物半導体装置としては、AlGaN/GaN・HEMT以外にも、以下のようなHEMTに適用できる。

また、第2の実施形態では、化合物半導体装置としてAlGaN/GaN・ダイオードを例示した。化合物半導体装置としては、AlGaN/GaN・ダイオード以外にも、以下のような高電子移動度ダイオードに適用できる。

【0094】

・その他の装置例1

本例では、化合物半導体装置として、InAlN/GaN・HEMT、InAlN/GaN・ダイオードを開示する。

InAlNとGaNは、組成によって格子定数を近くすることが可能な化合物半導体である。この場合、上記した第1及び第2の実施形態では、電子走行層がi−GaN、中間層がAlN、電子供給層がn−InAlN、p型キャップ層がp−GaN、n型キャップ層がn−GaNで形成される。また、この場合のピエゾ分極がほとんど発生しないため、2次元電子ガスは主にInAlNの自発分極により発生する。

【0095】

本例によれば、上述したAlGaN/GaN・HEMT、AlGaN/GaN・ダイオードと同様に、n型化合物半導体層と共にp型化合物半導体層を用い、化合物半導体層の再成長をすることなく、実効的に第2導電型のドーピング量が容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧のInAlN/GaN・HEMT、InAlN/GaN・ダイオードが実現する。

【0096】

・その他の装置例2

本例では、化合物半導体装置として、InAlGaN/GaN・HEMT、InAlGaN/GaN・ダイオードを開示する。

GaNとInAlGaNは、後者の方が前者よりも組成によって格子定数を小さくすることができる化合物半導体である。この場合、上記した第1及び第2の実施形態では、電子走行層がi−GaN、中間層がi−InAlGaN、電子供給層がn−InAlGaN、p型キャップ層がp−GaN、n型キャップ層がn−GaNで形成される。

【0097】

本例によれば、上述したAlGaN/GaN・HEMT、AlGaN/GaN・ダイオードと同様に、n型化合物半導体層と共にp型化合物半導体層を用い、化合物半導体層の再成長をすることなく、実効的に第2導電型のドーピング量が容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧のInAlGaN/GaN・HEMT、InAlGaN/GaN・ダイオードが実現する。

【0098】

以下、化合物半導体装置及びその製造方法、並びに電源装置及び高周波増幅器の諸態様を付記としてまとめて記載する。

【0099】

(付記1)第1の極性を有する第1の化合物半導体層と、

前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、

前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層と

を含み、

前記第3の化合物半導体層は、厚みの異なる部位を有することを特徴とする化合物半導体装置。

【0100】

(付記2)前記第1の極性は、負の極性であることを特徴とする付記1に記載の化合物半導体装置。

【0101】

(付記3)前記第3の化合物半導体層は、貫通口が形成されており、

前記貫通口を埋め込むゲート電極を更に含むことを特徴とする付記1又は2に記載の化合物半導体装置。

【0102】

(付記4)前記第3の化合物半導体層上に形成されたフィールドプレート電極を更に含むことを特徴とする付記1〜3のいずれか1項に記載の化合物半導体装置。

【0103】

(付記5)前記フィールドプレート電極は、前記第3の化合物半導体層の薄い部位に形成されていることを特徴とする付記4に記載の化合物半導体装置。

【0104】

(付記6)前記第1の化合物半導体層の上方で前記第3の化合物半導体層の両側に形成された一対の電極を更に含み、

前記第3の化合物半導体層は、一方の前記電極側が薄く、他方の前記電極側が一方の前記電極側よりも厚く形成されていることを特徴とする付記1又は2に記載の化合物半導体装置。

【0105】

(付記7)第1の極性を有する第1の化合物半導体層を形成する工程と、

前記第1の半導体層の上方に、第2の極性を有する第2の化合物半導体層を形成する工程と、

前記第2の半導体層の上方に、第2の極性を有する第3の化合物半導体層を形成する工程と、

前記第3の化合物半導体層に、厚みの異なる部位を形成する工程と

を含むことを特徴とする化合物半導体装置の製造方法。

【0106】

(付記8)前記第1の極性は、負の極性であることを特徴とする付記7に記載の化合物半導体装置の製造方法。

【0107】

(付記9)前記第3の化合物半導体層に貫通口を形成し、

前記貫通口を埋め込むゲート電極を形成する工程を更に含むことを特徴とする付記7又は8に記載の化合物半導体装置の製造方法。

【0108】

(付記10)前記第3の化合物半導体層上にフィールドプレート電極を形成する工程を更に含むことを特徴とする付記7〜9のいずれか1項に記載の化合物半導体装置の製造方法。

【0109】

(付記11)前記フィールドプレート電極を、前記第3の化合物半導体層の薄い部位に形成することを特徴とする付記10に記載の化合物半導体装置の製造方法。

【0110】

(付記12)前記第1の化合物半導体層の上方で前記第3の化合物半導体層の両側に一対の電極を形成する工程を更に含み、

前記第3の化合物半導体層を、一方の前記電極側が薄く、他方の前記電極側が一方の前記電極側よりも厚く形成することを特徴とする付記7又は8に記載の化合物半導体装置の製造方法。

【0111】

(付記13)変圧器と、前記変圧器を挟んで高圧回路及び低圧回路とを備えた電源装置であって、

前記高圧回路はトランジスタ及びダイオードを有しており、

前記トランジスタ及び前記ダイオードの少なくも一方は、

第1の極性を有する第1の化合物半導体層と、

前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、

前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層と

を含み、

前記第3の化合物半導体層は、厚みの異なる部位を有することを特徴とする電源装置。

【0112】

(付記14)入力した高周波電圧を増幅して出力する高周波増幅器であって、

トランジスタを有しており、

前記トランジスタは、

第1の極性を有する第1の化合物半導体層と、

前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、

前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層と

を含み、

前記第3の化合物半導体層は、厚みの異なる部位を有することを特徴とする高周波増幅器。

【符号の説明】

【0113】

1 Si基板

2,21 化合物半導体積層構造

2a,21a バッファ層

2b,21b 電子走行層

2c,21c 中間層

2d,21d 電子供給層

2e,21e p型キャップ層

2f,21f n型キャップ層

2fa,21fa 開口

2fb,21fb 薄化部分

2A,2B,21A,21B 電極用リセス

3 素子分離構造

4 ソース電極

5 ドレイン電極

6 ゲート電極

7 フィールドプレート電極

10A,10B,20A,20B レジストマスク

10Aa,10Ba,20Aa,20Ba 開口

23 カソード電極

24 アノード電極

30 PFC回路

31,44a,44b,44c,44d,45a,45b,45c スイッチ素子

32 ダイオード

33 チョークコイル

34,35 コンデンサ

36 ダイオードブリッジ

40 フルブリッジインバータ回路

41 一次側回路

42 二次側回路

43 トランス

51 ディジタル・プレディストーション回路

52a,52b ミキサー

53 パワーアンプ

100 HEMTチップ

101 トランジスタ領域

102 ドレインパッド

103 ゲートパッド

104 ソースパッド

111,211 ダイアタッチ剤

112,212 リードフレーム

112a ドレインリード

112b ゲートリード

112c ソースリード

113,213 Alワイヤ

114,214 モールド樹脂

200 ダイオードチップ

201 ダイオード領域

202 カソードパッド

203 アノードパッド

212a カソードリード

212b アノードリード

【特許請求の範囲】

【請求項1】

第1の極性を有する第1の化合物半導体層と、

前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、

前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層と

を含み、

前記第3の化合物半導体層は、厚みの異なる部位を有することを特徴とする化合物半導体装置。

【請求項2】

前記第1の極性は、負の極性であることを特徴とする請求項1に記載の化合物半導体装置。

【請求項3】

前記第3の化合物半導体層は、貫通口が形成されており、

前記貫通口を埋め込むゲート電極を更に含むことを特徴とする請求項1又は2に記載の化合物半導体装置。

【請求項4】

前記第3の化合物半導体層上に形成されたフィールドプレート電極を更に含み、

前記フィールドプレート電極は、前記第3の化合物半導体層の薄い部位に形成されていることを特徴とする請求項1〜3のいずれか1項に記載の化合物半導体装置。

【請求項5】

前記第1の化合物半導体層の上方で前記第3の化合物半導体層の両側に形成された一対の電極を更に含み、

前記第3の化合物半導体層は、一方の前記電極側が薄く、他方の前記電極側が一方の前記電極側よりも厚く形成されていることを特徴とする請求項1又は2に記載の化合物半導体装置。

【請求項6】

第1の極性を有する第1の化合物半導体層を形成する工程と、

前記第1の半導体層の上方に、第2の極性を有する第2の化合物半導体層を形成する工程と、

前記第2の半導体層の上方に、第2の極性を有する第3の化合物半導体層を形成する工程と、

前記第3の化合物半導体層に、厚みの異なる部位を形成する工程と

を含むことを特徴とする化合物半導体装置の製造方法。

【請求項7】

前記第1の極性は、負の極性であることを特徴とする請求項6に記載の化合物半導体装置の製造方法。

【請求項8】

前記第3の化合物半導体層に貫通口を形成し、

前記貫通口を埋め込むゲート電極を形成する工程を更に含むことを特徴とする請求項6又は7に記載の化合物半導体装置の製造方法。

【請求項9】

前記第3の化合物半導体層上にフィールドプレート電極を形成する工程を更に含み、

前記フィールドプレート電極を、前記第3の化合物半導体層の薄い部位に形成することを特徴とする請求項6〜8のいずれか1項に記載の化合物半導体装置の製造方法。

【請求項10】

前記第1の化合物半導体層の上方で前記第3の化合物半導体層の両側に一対の電極を形成する工程を更に含み、

前記第3の化合物半導体層を、一方の前記電極側が薄く、他方の前記電極側が一方の前記電極側よりも厚く形成することを特徴とする請求項6又は7に記載の化合物半導体装置の製造方法。

【請求項1】

第1の極性を有する第1の化合物半導体層と、

前記第1の半導体層の上方に形成された第2の極性を有する第2の化合物半導体層と、

前記第2の半導体層の上方に形成された第1の極性を有する第3の化合物半導体層と

を含み、

前記第3の化合物半導体層は、厚みの異なる部位を有することを特徴とする化合物半導体装置。

【請求項2】

前記第1の極性は、負の極性であることを特徴とする請求項1に記載の化合物半導体装置。

【請求項3】

前記第3の化合物半導体層は、貫通口が形成されており、

前記貫通口を埋め込むゲート電極を更に含むことを特徴とする請求項1又は2に記載の化合物半導体装置。

【請求項4】

前記第3の化合物半導体層上に形成されたフィールドプレート電極を更に含み、

前記フィールドプレート電極は、前記第3の化合物半導体層の薄い部位に形成されていることを特徴とする請求項1〜3のいずれか1項に記載の化合物半導体装置。

【請求項5】

前記第1の化合物半導体層の上方で前記第3の化合物半導体層の両側に形成された一対の電極を更に含み、

前記第3の化合物半導体層は、一方の前記電極側が薄く、他方の前記電極側が一方の前記電極側よりも厚く形成されていることを特徴とする請求項1又は2に記載の化合物半導体装置。

【請求項6】

第1の極性を有する第1の化合物半導体層を形成する工程と、

前記第1の半導体層の上方に、第2の極性を有する第2の化合物半導体層を形成する工程と、

前記第2の半導体層の上方に、第2の極性を有する第3の化合物半導体層を形成する工程と、

前記第3の化合物半導体層に、厚みの異なる部位を形成する工程と

を含むことを特徴とする化合物半導体装置の製造方法。

【請求項7】

前記第1の極性は、負の極性であることを特徴とする請求項6に記載の化合物半導体装置の製造方法。

【請求項8】

前記第3の化合物半導体層に貫通口を形成し、

前記貫通口を埋め込むゲート電極を形成する工程を更に含むことを特徴とする請求項6又は7に記載の化合物半導体装置の製造方法。

【請求項9】

前記第3の化合物半導体層上にフィールドプレート電極を形成する工程を更に含み、

前記フィールドプレート電極を、前記第3の化合物半導体層の薄い部位に形成することを特徴とする請求項6〜8のいずれか1項に記載の化合物半導体装置の製造方法。

【請求項10】

前記第1の化合物半導体層の上方で前記第3の化合物半導体層の両側に一対の電極を形成する工程を更に含み、

前記第3の化合物半導体層を、一方の前記電極側が薄く、他方の前記電極側が一方の前記電極側よりも厚く形成することを特徴とする請求項6又は7に記載の化合物半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−74280(P2013−74280A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−214723(P2011−214723)

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]