化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、化合物半導体装置及びその製造方法に関する。

【背景技術】

【0002】

窒化物半導体装置は、高い飽和電子速度及びワイドバンドギャップ等の特徴を利用し、高耐圧及び高出力の半導体デバイスとしての開発が活発に行われている。窒化物半導体デバイスとしては、電界効果トランジスタ、特に高電子移動度トランジスタ(High Electron Mobility Transistor:HEMT)についての報告が数多くなされている。特に、GaNを電子走行層として、AlGaNを電子供給層として用いたAlGaN/GaN・HEMTが注目されている。AlGaN/GaN・HEMTでは、GaNとAlGaNとの格子定数差に起因した歪みがAlGaNに生じる。これにより発生したピエゾ分極及びAlGaNの自発分極により、高濃度の2次元電子ガス(2DEG)が得られる。そのため、高耐圧及び高出力が実現できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−359256号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

AlGaN/GaN・HEMT等の高出力高周波用の窒化物半導体装置では、高電圧下で動作させる際の問題点の1つとして、電流コラプス現象が挙げられる。この電流コラプスは、高電圧印加によりオン抵抗が増大する現象のことを指し、電子が半導体結晶中や半導体/絶縁膜界面等にトラップされ、その領域の2DEG濃度が減少することにより起こるとされている。電流コラプス現象を抑制するための1つの手法として、フィールドプレート構造が広く知られている。例えば、ゲート電極をいわゆるオーバーハング形状に形成することにより、電流コラプス現象の抑制に効果があることが知られている。

【0005】

しかしながら、上記のフィールドプレート構造のみでは充分に電流コラプス現象を抑制することは難しく、特に高電圧動作時に顕著に電流コラプスが起きてしまう問題点があり、更なる電流コラプス抑制手法が望まれている。

【0006】

本発明は、上記の課題に鑑みてなされたものであり、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

化合物半導体装置の一態様は、化合物半導体層と、開口を有し、前記化合物半導体層上を覆う保護膜と、前記開口を埋め込み、前記化合物半導体層上に乗り上げる形状の電極と

を含み、前記保護膜は、酸素非含有の下層絶縁膜と、酸素含有の上層絶縁膜との積層構造を有しており、前記開口は、前記下層絶縁膜に形成された第1の開口と、前記上層絶縁膜に形成された前記第1の開口よりも幅広の第2の開口とが連通してなる。

【0008】

化合物半導体装置の製造方法の一態様は、化合物半導体層上を覆うように、酸素非含有の下層絶縁膜と酸素含有の上層絶縁膜との積層構造を有する保護膜を形成する工程と、前記下層絶縁膜に第1の開口を、前記上層絶縁膜に前記第1の開口よりも幅広の第2の開口を、前記第1の開口と前記第2の開口とが連通するように形成する工程と、前記開口を埋め込み、前記化合物半導体層上に乗り上げる形状に電極を形成する工程とを含む。

【発明の効果】

【0009】

上記の諸態様によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置が得られる。

【図面の簡単な説明】

【0010】

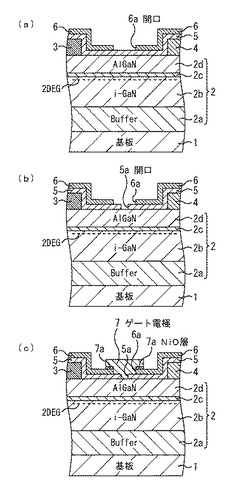

【図1】第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図2】図1に引き続き、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図3】第1の実施形態によるAlGaN/GaN・HEMTの電流−電圧特性について調べた実験結果を示す特性図である。

【図4】第2の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図5】第3の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図6】第4の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図7】図6に引き続き、第4の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図8】第5の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図9】図8に引き続き、第5の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図10】第6の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図11】図10に引き続き、第6の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図12】第7の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図13】図12に引き続き、第7の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図14】第8の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図15】図14に引き続き、第8の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図16】第9の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図17】図16に引き続き、第9の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図18】第10の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図19】図18に引き続き、第10の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図20】第11の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図21】図20に引き続き、第11の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図22】第12の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図23】図22に引き続き、第12の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図24】第13の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図25】図24に引き続き、第13の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図26】第14の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図27】第15の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図28】図27に引き続き、第15の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図29】第16の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図30】図29に引き続き、第16の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図31】第17の実施形態による電源装置の概略構成を示す結線図である。

【図32】第18の実施形態による高周波増幅器の概略構成を示す結線図である。

【発明を実施するための形態】

【0011】

以下、諸実施形態について図面を参照して詳細に説明する。以下の諸実施形態では、化合物半導体装置の構成について、その製造方法と共に説明する。

なお、以下の図面において、図示の便宜上、相対的に正確な大きさ及び厚みに示していない構成部材がある。

【0012】

(第1の実施形態)

本実施形態では、化合物半導体装置としてショットキー型のAlGaN/GaN・HEMTを開示する。

図1及び図2は、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【0013】

先ず、図1(a)に示すように、成長用基板として例えば半絶縁性のSiC基板1上に、化合物半導体の積層構造である化合物半導体層2を形成する。成長用基板としては、SiC基板の代わりに、Si基板、サファイア基板、GaAs基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

化合物半導体層2は、バッファ層2a、電子走行層2b、中間層2c、及び電子供給層2dを有して構成される。

【0014】

完成したAlGaN/GaN・HEMTでは、その動作時において、電子走行層2bの電子供給層2d(正確には中間層2c)との界面近傍に2次元電子ガス(2DEG)が発生する。この2DEGは、電子走行層2b及び電子供給層2dの自発分極と相俟って、電子走行層2bの化合物半導体(ここではGaN)と電子供給層2dの化合物半導体(ここではAlGaN)との格子定数の相違に起因した歪みによるピエゾ分極に基づいて生成される。

【0015】

詳細には、SiC基板1上に、例えば有機金属気相成長(MOVPE:Metal Organic Vapor Phase Epitaxy)法により、以下の各化合物半導体を成長する。MOVPE法の代わりに、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法等を用いても良い。

SiC基板1上に、バッファ層2a、電子走行層2b、中間層2c、及び電子供給層2dとなる各化合物半導体を順次成長する。バッファ層2aは、Si基板1上に、AlNを0.1μm程度の厚みに成長することで形成される。電子走行層2bは、i(インテンショナリ・アンドープ)−GaNを1μm程度〜3μm程度の厚みに成長することで形成される。中間層2cは、i−AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2dは、n−AlGaNを30nm程度の厚みに成長することで形成される。中間層2cは形成しない場合もある。電子供給層は、i−AlGaNを形成するようにしても良い。

【0016】

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH3)ガスの混合ガスを用いる。AlGaNの成長には、原料ガスとしてTMAlガス、TMGaガス及びNH3ガスの混合ガスを用いる。成長する化合物半導体層に応じて、TMAlガス、TMGaガスの供給の有無及び流量を適宜設定する。共通原料であるNH3ガスの流量は、100sccm〜10slm程度とする。また、成長圧力は50Torr〜300Torr程度、成長温度は1000℃〜1200℃程度とする。

【0017】

AlGaNをn型として成長する際、即ち電子供給層2d(n−AlGaN)の形成には、n型不純物をAlGaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン(SiH4)ガスを所定の流量で原料ガスに添加し、AlGaNにSiをドーピングする。Siのドーピング濃度は、1×1018/cm3程度〜1×1020/cm3程度、例えば2×1018/cm3程度とする。

【0018】

続いて、素子分離構造を形成する。

詳細には、化合物半導体層2の素子分離領域に例えばアルゴン(Ar)を注入する。これにより、化合物半導体層2及びSiC基板1の表層部分に素子分離構造が形成される。素子分離構造により、化合物半導体層2上で活性領域が画定される。

なお、素子分離は、上記の注入法の代わりに、例えばSTI(Shallow Trench Isolation)法を用いて行っても良い。

【0019】

続いて、図1(b)に示すように、ソース電極3及びドレイン電極4を形成する。

電極材料として例えばTa/Al(下層がTa、上層がAl)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体層2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/Alを堆積する。Taの厚みは20nm程度、Alの厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/Alを除去する。その後、SiC基板1を、例えば窒素雰囲気中において400℃〜1000℃、例えば550℃程度で熱処理し、残存したTa/Alを電子供給層2dとオーミックコンタクトさせる。以上により、Ta/Alからなるソース電極3及びドレイン電極4が形成される。

【0020】

続いて、図1(c)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiON膜6との積層構造とされる。

【0021】

詳細には、化合物半導体層2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiONを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiON膜6を形成する。以上により、SiN膜5及びSiON膜6が積層されてなるパッシベーション膜が形成される。

【0022】

続いて、図2(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiON膜6のゲート電極の形成予定位置に開口6aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0023】

続いて、図2(b)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6の開口6aは、SiN膜5の開口5aよりも幅広となる。開口5a,6aが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0024】

続いて、図2(c)に示すように、ゲート電極7を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極7が形成される。

【0025】

ゲート電極7は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極7のNiとの接触部分では、SiON膜6の酸素とゲート電極7のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層7aが形成される。

【0026】

しかる後、ソース電極3及びドレイン電極4、ゲート電極7の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0027】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極7が形成される。この構成では、ゲート電極7は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0028】

更に本実施形態では、SiON膜6の酸素とゲート電極7のオーバーハング部分のNiとが反応してNiO層7aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極7のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極7中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層7aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0029】

ここで、本実施形態によるAlGaN/GaN・HEMTの電流−電圧特性について調べた実験について説明する。本実施形態の比較例として、パッシベーション膜がSiNの単層からなる従来のAlGaN/GaN・HEMTを例示する。

実験結果を図3に示す。(a)が比較例、(b)が本実施形態である。比較例では、50Vのバイアスストレスにより、オン抵抗が増大しており、電流コラプスが大きい。これに対して本実施形態では、オン抵抗の増加が非常に小さく、効果的に電流コラプスを抑制できることが確認された。

【0030】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0031】

(第2の実施形態)

以下、第2の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図4は、第2の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0032】

先ず、第1の実施形態の図1(a)〜図2(a)の諸工程を経て、図4(a)に示すように、SiON膜6に開口6aを形成する。

を形成する。

【0033】

続いて、図4(b)に示すように、SiON膜6及び電子供給層2dに溝11を形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用い、SiN膜5及び電子供給層2dの表層まで、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層2d及びSiN膜5のゲート電極の形成予定位置に、SiN膜5を貫通して電子供給層2dの表層まで掘る溝11が形成される。SiON膜6の開口6aは、溝11よりも幅広となる。溝11及び開口6aが連通し、ゲート電極を形成するための電極溝が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0034】

続いて、図4(c)に示すように、ゲート電極12を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを溝11及び開口6a内を含むSiON膜6上に塗布し、溝11及び開口6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、溝11及び開口6a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極12が形成される。

【0035】

ゲート電極12は、溝11及び開口6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極12のNiとの接触部分では、SiON膜6の酸素とゲート電極12のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層7aが形成される。

【0036】

しかる後、ソース電極3及びドレイン電極4、ゲート電極12の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0037】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。電子供給層2d及びSiN膜5の溝11と、開口5aよりも幅広のSiON膜6の開口6aとが連通し、溝11及び開口6aからなる電極溝内を埋め込むようにオーバーハング形状のゲート電極12が形成される。この構成では、ゲート電極12は、溝11を充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0038】

更に本実施形態では、SiON膜6の酸素とゲート電極12のオーバーハング部分のNiとが反応してNiO層12aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極12のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極12中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層12aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0039】

更に本実施形態では、溝11の一環として電子供給層2dにも溝部が形成され、ゲート電極12の最下部が当該溝部に形成される。これにより、電源のオフ時にゲート電流が流れない、いわゆるノーマリ・オフの実現に寄与すると共に、ゲート電極12における電界集中が更に緩和される。

【0040】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0041】

(第3の実施形態)

以下、第3の実施形態によるMIS型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図5は、第3の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0042】

先ず、第1の実施形態の図1(a)〜図2(a)の諸工程を経て、図5(a)に示すように、SiON膜6に開口6aを形成する。

を形成する。

【0043】

続いて、図5(b)に示すように、ゲート電極13を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口6a内を含むSiON膜6上に塗布し、開口6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口6a内をゲートメタルで埋め込むように、化合物半導体層2上でSiN膜5を介してゲート電極13が形成される。SiN膜5は、パッシベーション膜であると共にゲート絶縁膜としても機能する。

【0044】

ゲート電極13は、開口6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極13のNiとの接触部分では、SiON膜6の酸素とゲート電極13のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層13aが形成される。

【0045】

しかる後、ソース電極3及びドレイン電極4、ゲート電極13の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

【0046】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5により化合物半導体層2の表面から離間しているため、当該表面に対して影響を及ぼす懸念はない。SiON膜6の開口6a内を埋め込むようにオーバーハング形状のゲート電極13が形成される。この構成では、ゲート電極13は、開口6aを充填する部分及びオーバーハング部分の徐々に幅広となる多段構造(ここでは2段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0047】

更に本実施形態では、SiON膜6の酸素とゲート電極13のオーバーハング部分のNiとが反応してNiO層13aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極13のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極13中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層13aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0048】

更に本実施形態では、2層構造のパッシベーション膜において、下層のSiN膜5は、パッシベーション膜であると共に、ゲート絶縁膜としても機能する。この構成では、2層構造のパッシベーション膜とは別にゲート絶縁膜を形成する工程が削減すると共に、所期のMIS型のAlGaN/GaN・HEMTが実現する。

【0049】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0050】

(第4の実施形態)

以下、第4の実施形態によるMIS型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図6及び図7は、第4の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0051】

先ず、第1の実施形態の図1(a),(b)の諸工程を経て、図6(a)に示すように、化合物半導体層2上にソース電極3及びドレイン電極4を形成する。

【0052】

続いて、図6(b)に示すように、ゲート絶縁膜14を形成する。

詳細には、化合物半導体積層構造2上に絶縁材料として、酸素非含有の絶縁物、例えばAlNを堆積する。AlNは、例えば原子層堆積法(Atomic Layer Deposition:ALD法)により、厚みが膜厚2nm〜100nm程度、ここでは例えば10nm程度となるように、AlNを堆積する。これにより、ゲート絶縁膜14が形成される。

【0053】

なお、AlNの堆積は、ALD法の代わりに、例えばプラズマCVD法又はスパッタ法等で行うようにしても良い。また、AlNを堆積する代わりに、Alの窒化物を用いても良い。それ以外にも、Si,Hf,Zr,Ti,Ta,Wの窒化物、或いはこれらから適宜に選択して多層に堆積して、ゲート絶縁膜を形成しても良い。

【0054】

続いて、図6(c)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiON膜6との積層構造とされる。

【0055】

詳細には、ゲート絶縁膜14上にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiONを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiON膜6を形成する。以上により、SiN膜5及びSiON膜6が積層されてなるパッシベーション膜が形成される。

【0056】

続いて、図7(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiON膜6のゲート電極の形成予定位置に開口6aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0057】

続いて、図7(b)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6の開口6aは、SiN膜5の開口5aよりも幅広となる。開口5a,6aが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0058】

続いて、図7(c)に示すように、ゲート電極15を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6a内をゲートメタルで埋め込むように、化合物半導体層2上でゲート絶縁膜14を介してゲート電極15が形成される。

【0059】

ゲート電極15は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極15のNiとの接触部分では、SiON膜6の酸素とゲート電極15のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層15aが形成される。

【0060】

しかる後、ソース電極3及びドレイン電極4、ゲート電極15の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

【0061】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適であり、SiN膜5がAlNのゲート絶縁膜14と共に主に保護膜としての機能を果たす。酸素含有のSiON膜6はゲート絶縁膜14及びSiN膜5により化合物半導体層2の表面から離間しているため、当該表面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極15が形成される。この構成では、ゲート電極15は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0062】

更に本実施形態では、SiON膜6の酸素とゲート電極15のオーバーハング部分のNiとが反応してNiO層15aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極15のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極15中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層15aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0063】

更に本実施形態では、ゲート絶縁膜14は、ゲート絶縁膜であると共にパッシベーション膜としても機能し、所期のMIS型のAlGaN/GaN・HEMTが実現する。

【0064】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0065】

(第5の実施形態)

以下、第5の実施形態によるMIS型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図8及び図9は、第5の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0066】

先ず、第1の実施形態の図1(a),(b)の諸工程を経て、化合物半導体層2上にソース電極3及びドレイン電極4を形成する。

【0067】

続いて、図8(a)に示すように、電子供給層2dに溝2daを形成する。

詳細には、電子供給層2d上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層2dのゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層2dの表層を、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層2dの表層におけるゲート電極の形成予定位置に溝11が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0068】

続いて、図8(b)に示すように、ゲート絶縁膜14を形成する。

詳細には、溝11の内壁面を含む化合物半導体積層構造2上に絶縁材料として、酸素非含有の絶縁物、例えばAlNを堆積する。AlNは、例えば原子層堆積法(Atomic Layer Deposition:ALD法)により、厚みが膜厚2nm〜100nm程度、ここでは例えば10nm程度となるように、AlNを堆積する。これにより、ゲート絶縁膜14が形成される。

【0069】

なお、AlNの堆積は、ALD法の代わりに、例えばプラズマCVD法又はスパッタ法等で行うようにしても良い。また、AlNを堆積する代わりに、Alの窒化物を用いても良い。それ以外にも、Si,Hf,Zr,Ti,Ta,Wの窒化物、或いはこれらから適宜に選択して多層に堆積して、ゲート絶縁膜を形成しても良い。

【0070】

続いて、図8(c)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiON膜6との積層構造とされる。

【0071】

詳細には、ゲート絶縁膜14上にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiONを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiON膜6を形成する。以上により、SiN膜5及びSiON膜6が積層されてなるパッシベーション膜が形成される。

【0072】

続いて、図9(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiON膜6のゲート電極の形成予定位置に開口6aが形成される。開口6aは、電子供給層2dの溝2daよりも幅広とされる。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0073】

続いて、図9(b)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6の開口6aは、SiN膜5の開口5aよりも幅広となる。ゲート絶縁膜14を介した溝2da、開口5a,6aが連通し、ゲート電極を形成するための電極溝が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0074】

続いて、図9(c)に示すように、ゲート電極16を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、電極溝を含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、電極溝内をゲートメタルで埋め込むように、化合物半導体層2上でゲート絶縁膜14を介してゲート電極16が形成される。

【0075】

ゲート電極16は、ゲート絶縁膜14を介した溝2da、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極16のNiとの接触部分では、SiON膜6の酸素とゲート電極16のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層16aが形成される。

【0076】

しかる後、ソース電極3及びドレイン電極4、ゲート電極16の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

【0077】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適であり、SiN膜5がAlNのゲート絶縁膜14と共に主に保護膜としての機能を果たす。酸素含有のSiON膜6はゲート絶縁膜14及びSiN膜5により化合物半導体層2の表面から離間しているため、当該表面に対して影響を及ぼす懸念はない。電子供給層2dの溝2daと、SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、溝2da及び開口5a,6aからなる電極溝内を埋め込むようにオーバーハング形状のゲート電極16が形成される。この構成では、ゲート電極16は、溝2daをゲート絶縁膜14を介して充填する部分、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは4段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0078】

更に本実施形態では、SiON膜6の酸素とゲート電極16のオーバーハング部分のNiとが反応してNiO層16aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極16のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極16中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層16aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0079】

更に本実施形態では、電子供給層2dに溝2daが形成され、ゲート電極16の最下部が当該溝部に形成される。これにより、電源のオフ時にゲート電流が流れない、いわゆるノーマリ・オフの実現に寄与すると共に、ゲート電極16における電界集中が更に緩和される。

【0080】

更に本実施形態では、ゲート絶縁膜14は、ゲート絶縁膜であると共にパッシベーション膜としても機能し、所期のMIS型のAlGaN/GaN・HEMTが実現する。

【0081】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0082】

(第6の実施形態)

本実施形態では、化合物半導体装置としてショットキー型のAlGaN/GaN・HEMTを開示する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図10及び図11は、第6の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0083】

先ず、第1の実施形態の図1(a),(b)の諸工程を経て、図10(a)に示すように、化合物半導体層2上にソース電極3及びドレイン電極4を形成する。

【0084】

続いて、図10(b)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではNiO膜17との積層構造とされる。

【0085】

詳細には、化合物半導体層2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にNiOを、スパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、NiO膜17を形成する。以上により、SiN膜5及びNiO膜17が積層されてなるパッシベーション膜が形成される。

【0086】

続いて、図10(c)に示すように、NiO膜17に開口17aを形成する。

詳細には、NiO膜17の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、NiO膜17のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、NiO膜17を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、NiO膜17と共にSiN膜5の表層を若干エッチングしても構わない。これにより、NiO膜17のゲート電極の形成予定位置に開口17aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0087】

続いて、図11(a)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口17aから露出するSiN膜5上を含むNiO膜17の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口17a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。NiO膜17の開口17aは、SiN膜5の開口5aよりも幅広となる。開口5a,17aが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0088】

続いて、図11(b)に示すように、ゲート電極18を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,17a内を含むNiO膜17上に塗布し、開口5a,17aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,17a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極18が形成される。

ゲート電極18は、開口5a,6a内を埋め込みNiO膜17上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

【0089】

しかる後、ソース電極3及びドレイン電極4、ゲート電極18の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0090】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のNiO膜17との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。NiO膜17はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のNiO膜17の開口17aとが連通し、開口5a,17aからなる開口内を埋め込むようにオーバーハング形状のゲート電極18が形成される。この構成では、ゲート電極18は、開口5aを充填する部分、開口17aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0091】

更に本実施形態では、オーバーハング部分のNiの下面には、NiO膜17が接触している。NiOはp型酸化物半導体として機能する。ゲート電極18のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極18中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に接触するp型酸化物半導体であるNiOの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0092】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0093】

(第7の実施形態)

以下、第7の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図12及び図13は、第7の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0094】

先ず、第1の実施形態の図1(a)〜図1(c)の諸工程を経て、図12(a)に示すように、SiN膜5及びSiON膜6を形成する。

を形成する。

【0095】

続いて、図12(b)に示すように、SiON膜6を加工して、開口6Aaを有するSiON片6Aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置の周辺のみを覆う帯状のレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、ゲート電極の形成予定位置の周辺のみを覆い、ゲート電極の形成予定位置に開口6Aaを有する帯状にSiON膜6が残存し、SiON片6Aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0096】

続いて、図13(a)に示すように、SiN膜5に開口5aを形成する。

詳細には、SiON片6A上を含むSiN膜5の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6Aa内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON片6Aの開口6Aaは、SiN膜5の開口5aよりも幅広となる。開口5a,6Aaが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0097】

続いて、図13(b)に示すように、ゲート電極19を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6Aa内を含むSiON片6A上及びSiN膜5上に塗布し、開口5a,6Aaを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6Aa内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極19が形成される。

【0098】

ゲート電極19は、開口5a,6Aa内を埋め込みSiON片6A上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON片6Aにおけるゲート電極19のNiとの接触部分では、SiON片6Aの酸素とゲート電極19のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層19aが形成される。

【0099】

しかる後、ソース電極3及びドレイン電極4、ゲート電極19の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0100】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5上に酸素含有のSiON片6Aが形成されて構成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON片6AはSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON片6Aの開口6Aaとが連通し、開口5a,6Aaからなる開口内を埋め込むようにオーバーハング形状のゲート電極19が形成される。この構成では、ゲート電極19は、開口5aを充填する部分、開口6Aaを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0101】

更に本実施形態では、SiON片6Aの酸素とゲート電極19のオーバーハング部分のNiとが反応してNiO層19aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極19のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極19中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層19aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0102】

更に本実施形態では、SiON片6Aは、SiN膜5上で、ゲート電極19のオーバーハング部分の周辺のみを覆い、開口6Aaを有する帯状にSiONが残存してなるものであり、ゲート端の部位以外全てSiONが除去されている。これにより、SiON、SiON/SiN界面を介したリーク電流成分、及び容量成分が大幅に低減する。

【0103】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0104】

(第8の実施形態)

以下、第8の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図14及び図15は、第8の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0105】

先ず、第1の実施形態の図1(a),(b)の諸工程を経て、図14(a)に示すように、化合物半導体層2上にソース電極3及びドレイン電極4を形成する。

【0106】

続いて、図14(b)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではNiO膜21との積層構造とされる。

【0107】

詳細には、化合物半導体層2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にNiOを、スパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、NiO膜21を形成する。以上により、SiN膜5及びNiO膜21が積層されてなるパッシベーション膜が形成される。

【0108】

続いて、図14(c)に示すように、NiO膜21を加工して、開口21Aaを有するNiO片21Aを形成する。

詳細には、NiO膜21の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、NiO膜21のゲート電極の形成予定位置の周辺のみを覆う帯状のレジストマスクが形成される。

このレジストマスクを用いて、NiO膜21を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、NiO膜21と共にSiN膜5の表層を若干エッチングしても構わない。これにより、ゲート電極の形成予定位置の周辺のみを覆い、ゲート電極の形成予定位置に開口21Aaを有する帯状にNiO膜21が残存し、NiO片21Aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0109】

続いて、図15(a)に示すように、SiN膜5に開口5aを形成する。

詳細には、NiO片21A上を含むSiN膜5の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口21Aa内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。NiO片21Aの開口21Aaは、SiN膜5の開口5aよりも幅広となる。開口5a,21Aaが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0110】

続いて、図15(b)に示すように、ゲート電極22を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,21Aa内を含むNiO片21A上及びSiN膜5上に塗布し、開口5a,21Aaを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,21Aa内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極22が形成される。

ゲート電極22は、開口5a,21Aa内を埋め込みNiO片21A上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。

【0111】

しかる後、ソース電極3及びドレイン電極4、ゲート電極22の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0112】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5上に酸素含有のNiO片21Aが形成されて構成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のNiO片21AはSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のNiO片21Aの開口21Aaとが連通し、開口5a,21Aaからなる開口内を埋め込むようにオーバーハング形状のゲート電極22が形成される。この構成では、ゲート電極22は、開口5aを充填する部分、開口21Aaを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0113】

更に本実施形態では、オーバーハング部分のNiの下面には、NiO片21Aが接触している。NiOはp型酸化物半導体として機能する。ゲート電極22のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極22中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に接触するp型酸化物半導体であるNiOの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0114】

更に本実施形態では、NiO片21Aは、ゲート電極22のオーバーハング部分の周辺のみを覆い、開口21Aaを有する帯状にNiOが残存してなるものであり、ゲート端の部位以外全てSiONが除去されている。これにより、NiO、NiO/SiN界面を介したリーク電流成分、及び容量成分が大幅に低減する。

【0115】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0116】

(第9の実施形態)

以下、第9の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図16及び図17は、第9の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0117】

先ず、第1の実施形態の図1(a)〜図1(c)の諸工程を経て、図16(a)に示すように、SiN膜5及びSiON膜6を形成する。

【0118】

続いて、図16(b)に示すように、SiON膜6を加工して、SiON膜6をドレイン電極4側のみに残してSiON層6Bを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のドレイン電極4側のみを覆うレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、ドレイン電極4側のみを覆うようにSiON膜6が残存し、SiON層6Bが形成される。ここで、SiON層6Bの端部はゲート電極の形成予定位置のドレイン電極4側の端部となり、この端部からソース電極3側に広がる領域を開口6Baと称する。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0119】

続いて、図17(a)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6Baから露出するSiN膜5上を含むSiON層6Bの全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6BaにおけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON層6Bの開口6Baの端部は、SiN膜5の開口5aのドレイン電極4側の端部よりもドレイン電極4側へ偏倚して形成される。開口5a,6Baが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0120】

続いて、図17(b)に示すように、ゲート電極23を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストをSiON層6B上及び開口5a内を含むSiN膜5上に塗布し、開口5aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極23が形成される。

【0121】

ゲート電極23は、開口5a内を埋め込み、開口6Baの端部を超えてSiON層6A上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON層6B表面の開口6Baの端部周辺におけるゲート電極23のNiとの接触部分では、SiON膜6の酸素とゲート電極23のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層23aが形成される。

【0122】

しかる後、ソース電極3及びドレイン電極4、ゲート電極23の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0123】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON層6Aとの積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON層6AはSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aのドレイン電極4側の端部よりもドレイン電極4側へ偏倚した端部を有するSiON層6Bの開口6Baとが連通し、開口5aを埋め込み開口6Baの端部を超えてSiON層6A上に乗り上げるオーバーハング形状のゲート電極23が形成される。この構成では、ゲート電極23は、開口5aを充填する部分、開口5aのドレイン電極4側の端部と開口6Baの端部との間を充填する部分、開口6Baの端部を超えてSiON層6A上に乗り上げるオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0124】

更に本実施形態では、SiON層6Bの酸素とゲート電極23のオーバーハング部分のNiとが反応してNiO層23aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極23のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極23中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層23aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0125】

更に本実施形態では、SiON層6Bは、SiN膜5上で、ドレイン電極4側のみを覆うようにSiONが残存してなるものであり、ゲート電極23とドレイン電極4との間以外全てSiONが除去されている。これにより、ゲート電極23とソース電極3との間における抵抗増加によるソース抵抗の増加を抑制することが可能となる。

【0126】

(第10の実施形態)

以下、第10の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図18及び図19は、第10の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0127】

先ず、第1の実施形態の図1(a)〜図1(c)の諸工程を経て、図18(a)に示すように、SiN膜5及びSiON膜6を形成する。

を形成する。

【0128】

続いて、図18(b)に示すように、SiON膜6の表層に酸素リッチ膜24を形成する。

詳細には、SiON膜6の表面に酸素プラズマ処理を施す。これにより、SiON膜6の表層が酸化され、当該表層のみにSiONで酸素含有率の高い酸素リッチ膜24が形成される。

【0129】

続いて、図18(c)に示すように、酸素リッチ膜24及びSiON膜6に開口25を形成する。

詳細には、酸素リッチ膜24の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、酸素リッチ膜24のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、酸素リッチ膜24及びSiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、酸素リッチ膜24及びSiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、酸素リッチ膜24及びSiON膜6のゲート電極の形成予定位置に開口25が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0130】

続いて、図19(a)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口25から露出するSiN膜5上を含む酸素リッチ膜24の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口25内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6及び酸素リッチ膜24の開口25は、SiN膜5の開口5aよりも幅広となる。開口5a,25が連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0131】

続いて、図19(b)に示すように、ゲート電極26を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,25内を含む酸素リッチ膜24上に塗布し、開口5a,25を含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,25内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極26が形成される。

【0132】

ゲート電極26は、開口5a,25内を埋め込み酸素リッチ膜24上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。酸素リッチ膜24表面の開口25の周辺におけるゲート電極26のNiとの接触部分では、酸素リッチ膜24の酸素とゲート電極26のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層26aが形成される。

【0133】

しかる後、ソース電極3及びドレイン電極4、ゲート電極26の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0134】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、表層に酸素リッチ膜24が形成された酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6(及び酸素リッチ膜24)はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6及び酸素リッチ膜24の開口25とが連通し、開口5a,25からなる開口内を埋め込むようにオーバーハング形状のゲート電極26が形成される。この構成では、ゲート電極26は、開口5aを充填する部分、開口25を充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0135】

更に本実施形態では、酸素リッチ膜24の酸素とゲート電極26のオーバーハング部分のNiとが反応してNiO層26aが形成される。オーバーハング部分のNiは酸素含有率の高い酸素リッチ膜24と接触することから、Niの酸化が促進される。NiOはp型酸化物半導体として機能する。ゲート電極26のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極26中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層26aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、酸素リッチ膜24の存在と相俟って、電流コラプス現象の更なる抑制が達成される。

【0136】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0137】

(第11の実施形態)

以下、第11の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図20及び図21は、第11の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0138】

先ず、第1の実施形態の図1(a)〜図1(c)の諸工程を経て、図20(a)に示すように、SiN膜5及びSiON膜6を形成する。

を形成する。

【0139】

続いて、図20(b)に示すように、SiON膜6には開口6bを、SiN膜5には開口5aを、両開口を略同一の幅に同時形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口27aを有するレジストマスク27が形成される。

レジストマスク27を用いて、SiON膜6及びSiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、ゲート電極の形成予定位置に、SiON膜6には開口6bが、SiN膜5には開口5aが、両開口の幅が略同一に同時形成される。

【0140】

続いて、図21(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、引き続きレジストマスク27を用いて、例えばバッファードフッ酸(BHF)を用いたウェットエッチングを行う。本実施形態では、SiN膜5とSiON膜6とでBHFに対するエッチング速度が異なり、後者の方が前者よりもエッチング速度が速くなるように膜質が選択される。これにより、SiN膜5は殆どエッチングされず開口5aの幅は変わらないのに対して、SiON膜6はエッチングされて開口6bの幅が拡張され、開口5aよりも幅広の開口6aが形成される。

レジストマスク27は、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0141】

続いて、図21(b)に示すように、ゲート電極28を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極28が形成される。

【0142】

ゲート電極28は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極28のNiとの接触部分では、SiON膜6の酸素とゲート電極28のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層28aが形成される。

【0143】

しかる後、ソース電極3及びドレイン電極4、ゲート電極28の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0144】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極28が形成される。この構成では、ゲート電極28は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0145】

更に本実施形態では、SiON膜6の酸素とゲート電極28のオーバーハング部分のNiとが反応してNiO層28aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極28のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極28中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層28aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0146】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0147】

(第12の実施形態)

以下、第12の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図22及び図23は、第12の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0148】

先ず、第1の実施形態の図1(a)〜図1(c)の諸工程を経て、図22(a)に示すように、SiN膜5及びSiON膜6を形成する。

を形成する。

【0149】

続いて、図22(b)に示すように、SiON膜6には開口6bを、SiN膜5には凹部5bを、両者を略同一の幅に同時形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口29aを有するレジストマスク29が形成される。

レジストマスク29を用いて、SiON膜6及びSiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。ドライエッチングは、SiN膜5の途中まで、例えばSiN膜5が5nm程度の厚みだけ残るように行う。これにより、ゲート電極の形成予定位置に、SiON膜6には開口6bが、SiN膜5には凹部5bが、両者の幅が略同一に同時形成される。

【0150】

続いて、図23(a)に示すように、SiON膜6には開口6aを、SiN膜5には開口5aをそれぞれ形成する。

詳細には、引き続きレジストマスク29を用いて、例えばバッファードフッ酸(BHF)を用いたウェットエッチングを行う。本実施形態では、SiN膜5とSiON膜6とでBHFに対するエッチング速度が異なり、後者の方が前者よりもエッチング速度が速くなるように膜質が選択される。これにより、SiN膜5は若干エッチングのエッチングにより電子供給層2dの表面の一部を露出する開口5aが形成され、SiON膜6はエッチングにより開口6bの幅が拡張され、開口5aよりも幅広の開口6aが形成される。

レジストマスク29は、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0151】

続いて、図23(b)に示すように、ゲート電極31を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極31が形成される。

【0152】

ゲート電極31は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極31のNiとの接触部分では、SiON膜6の酸素とゲート電極31のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層31aが形成される。

【0153】

しかる後、ソース電極3及びドレイン電極4、ゲート電極31の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0154】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極31が形成される。この構成では、ゲート電極31は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0155】

更に本実施形態では、SiON膜6の酸素とゲート電極31のオーバーハング部分のNiとが反応してNiO層31aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極31のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極31中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層31aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0156】

更に本実施形態では、SiON膜6及びSiN膜5のドライエッチングの際に、SiN膜5を薄く残してショットキー面となる化合物半導体層2の表面を露出させないようにする。これにより、ショットキー面のドライエッチングによるダメージが大幅に低減する。

【0157】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0158】

(第13の実施形態)

以下、第13の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図24及び図25は、第13の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0159】

先ず、第1の実施形態の図1(a),(b)の諸工程を経て、図24(a)に示すように、化合物半導体層2上にソース電極3及びドレイン電極4を形成する。

【0160】

続いて、図24(b)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiO2膜32との積層構造とされる。

【0161】

詳細には、化合物半導体層2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiO2を、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiO2膜32を形成する。以上により、SiN膜5及びSiO2膜32が積層されてなるパッシベーション膜が形成される。

【0162】

続いて、図24(c)に示すように、SiO2膜32に開口32aを形成する。

詳細には、SiO2膜32の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiO2膜32のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiO2膜32を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiO2膜32と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiO2膜32のゲート電極の形成予定位置に開口32aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0163】

続いて、図25(a)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiO2膜32の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiO2膜32の開口32aは、SiN膜5の開口5aよりも幅広となる。開口5a,32aが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0164】

続いて、図25(b)に示すように、ゲート電極33を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,32a内を含むSiO2膜32上に塗布し、開口5a,32aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,32a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極33が形成される。

【0165】

ゲート電極33は、開口5a,32a内を埋め込みSiO2膜32上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiO2膜32表面の開口32aの周辺におけるゲート電極33のNiとの接触部分では、SiO2膜32の酸素とゲート電極33のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層33aが形成される。

【0166】

しかる後、ソース電極3及びドレイン電極4、ゲート電極33の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0167】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有率の高いSiO2膜32との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiO2膜32はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiO2膜32の開口32aとが連通し、開口5a,32aからなる開口内を埋め込むようにオーバーハング形状のゲート電極33が形成される。この構成では、ゲート電極33は、開口5aを充填する部分、開口32aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0168】

更に本実施形態では、SiO2膜32の酸素とゲート電極33のオーバーハング部分のNiとが反応してNiO層33aが形成される。オーバーハング部分のNiは酸素含有率の高いSiO2膜32と接触することから、Niの酸化が促進される。NiOはp型酸化物半導体として機能する。ゲート電極33のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極33中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層33aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、SiO2膜32の存在と相俟って、電流コラプス現象の更なる抑制が達成される。

【0169】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0170】

(第14の実施形態)

以下、第14の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図26は、第14の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0171】

先ず、第1の実施形態の図1(a)〜図2(b)の諸工程を経て、図26(a)に示すように、SiN膜5に開口5aを形成する。

【0172】

続いて、図26(b)に示すように、ゲート電極34を形成する。

電極材料として例えばCuを用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Cuを堆積する。Cuの厚みは300nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したCuを除去する。これにより、開口5a,6a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極34が形成される。

【0173】

ゲート電極34は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるCuにより、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極34との接触部分では、SiON膜6の酸素とゲート電極34のオーバーハング部分のCuとが反応し、薄い酸化膜であるCuO層34aが形成される。

【0174】

しかる後、ソース電極3及びドレイン電極4、ゲート電極34の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0175】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極34が形成される。この構成では、ゲート電極34は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0176】

更に本実施形態では、SiON膜6の酸素とゲート電極34のオーバーハング部分のCuとが反応してCuO層34aが形成される。CuOはp型酸化物半導体として機能する。ゲート電極34のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極34中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるCuO層34aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0177】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0178】

(第15の実施形態)

以下、第15の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図27及び図28は、第15の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【0179】

先ず、図27(a)に示すように、成長用基板として例えば半絶縁性のSiC基板1上に、化合物半導体の積層構造である化合物半導体層10を形成する。成長用基板としては、SiC基板の代わりに、Si基板、サファイア基板、GaAs基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

化合物半導体層10は、バッファ層2a、電子走行層2b、中間層2c、電子供給層2d、及びキャップ層2eを有して構成される。

【0180】

完成したAlGaN/GaN・HEMTでは、その動作時において、電子走行層2bの電子供給層2d(正確には中間層2c)との界面近傍に2次元電子ガス(2DEG)が発生する。この2DEGは、電子走行層2b及び電子供給層2dの自発分極と相俟って、電子走行層2bの化合物半導体(ここではGaN)と電子供給層2dの化合物半導体(ここではAlGaN)との格子定数の相違に起因した歪みによるピエゾ分極に基づいて生成される。

【0181】

詳細には、SiC基板1上に、例えばMOVPE法により、以下の各化合物半導体を成長する。MOVPE法の代わりに、MBE法等を用いても良い。

SiC基板1上に、バッファ層2a、電子走行層2b、中間層2c、電子供給層2d、及びキャップ層2eとなる各化合物半導体を順次成長する。バッファ層2aは、Si基板1上に、AlNを0.1μm程度の厚みに成長することで形成される。電子走行層2bは、i−GaNを1μm程度〜3μm程度の厚みに成長することで形成される。中間層2cは、i−AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2dは、n−AlGaNを30nm程度の厚みに成長することで形成される。キャップ層2eは、n−GaNを10nm程度の厚みに成長することで形成される。中間層2cは形成しない場合もある。電子供給層は、i−AlGaNを形成するようにしても良い。

【0182】

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH3)ガスの混合ガスを用いる。AlGaNの成長には、原料ガスとしてTMAlガス、TMGaガス及びNH3ガスの混合ガスを用いる。成長する化合物半導体層に応じて、TMAlガス、TMGaガスの供給の有無及び流量を適宜設定する。共通原料であるNH3ガスの流量は、100sccm〜10slm程度とする。また、成長圧力は50Torr〜300Torr程度、成長温度は1000℃〜1200℃程度とする。

【0183】

AlGaN,GaNをn型として成長する際、即ち電子供給層2d(n−AlGaN)及びキャップ層2e(n−GaN)の形成には、n型不純物をAlGaN,GaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン(SiH4)ガスを所定の流量で原料ガスに添加し、AlGaN,GaNにSiをドーピングする。Siのドーピング濃度は、1×1018/cm3程度〜1×1020/cm3程度、例えば2×1018/cm3程度とする。

【0184】

続いて、素子分離構造を形成する。

詳細には、化合物半導体層10の素子分離領域に例えばアルゴン(Ar)を注入する。これにより、化合物半導体層10及びSiC基板1の表層部分に素子分離構造が形成される。素子分離構造により、化合物半導体層10上で活性領域が画定される。

なお、素子分離は、上記の注入法の代わりに、例えばSTI(Shallow Trench Isolation)法を用いて行っても良い。

【0185】

続いて、図27(b)に示すように、ソース電極3及びドレイン電極4を形成する。

詳細には、先ず、化合物半導体層10の表面におけるソース電極及びドレイン電極の形成予定位置(電極形成予定位置)に電極溝2eA,2eBを形成する。

化合物半導体層10の表面にレジストを塗布する。レジストをリソグラフィーにより加工し、レジストに、電極形成予定位置に相当する化合物半導体層10の表面を露出する開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

【0186】

このレジストマスクを用いて、電子供給層2dの表面が露出するまで、キャップ層2eの電極形成予定位置をドライエッチングして除去する。これにより、電子供給層2dの表面の電極形成予定位置を露出する電極溝2eA,2eBが形成される。エッチング条件としては、Ar等の不活性ガス及びCl2等の塩素系ガスをエッチングガスとして用い、例えばCl2を流量30sccm、圧力を2Pa、RF投入電力を20Wとする。なお、電極溝2eA,2eBは、キャップ層2eの途中までエッチングして形成しても、また電子供給層2d以降までエッチングして形成しても良い。

レジストマスクは、灰化処理等により除去される。

【0187】

ソース電極及びドレイン電極を形成するためのレジストマスクを形成する。ここでは、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体層10上に塗布し、電極溝2eA,2eBを露出する開口を形成する。以上により、当該開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電極材料として、例えばTa/Al(下層がTa、上層がAl)を、例えば蒸着法により、電極溝2eA,2eBを露出する開口内を含むレジストマスク上に堆積する。Taの厚みは20nm程度、Alの厚みは200nm程度とする。リフトオフ法により、レジストマスク及びその上に堆積したTa/Alを除去する。その後、SiC基板1を、例えば窒素雰囲気中において400℃〜1000℃程度の温度、例えば550℃程度で熱処理し、残存したTa/Alを電子供給層2dとオーミックコンタクトさせる。Ta/Alの電子供給層2dとのオーミックコンタクトが得られるのであれば、熱処理が不要な場合もある。以上により、電極溝2eA,2eBを電極材料の一部で埋め込むソース電極3及びドレイン電極4が形成される。

【0188】

続いて、図27(c)に示すように、化合物半導体層10の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiON膜6との積層構造とされる。

【0189】

詳細には、化合物半導体層10の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiONを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiON膜6を形成する。以上により、SiN膜5及びSiON膜6が積層されてなるパッシベーション膜が形成される。

【0190】

続いて、図28(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiON膜6のゲート電極の形成予定位置に開口6aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0191】

続いて、図28(b)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6の開口6aは、SiN膜5の開口5aよりも幅広となる。開口5a,6aが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0192】

続いて、図28(c)に示すように、ゲート電極35を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6a内をゲートメタルで埋め込み化合物半導体層10の表面とショットキー接触する、ゲート電極35が形成される。

【0193】

ゲート電極35は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極35のNiとの接触部分では、SiON膜6の酸素とゲート電極35のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層35aが形成される。

【0194】

しかる後、ソース電極3及びドレイン電極4、ゲート電極35の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0195】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層10の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極35が形成される。この構成では、ゲート電極35は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0196】

更に本実施形態では、SiON膜6の酸素とゲート電極35のオーバーハング部分のNiとが反応してNiO層35aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極35のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極35中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層35aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0197】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0198】

(第16の実施形態)

以下、第16の実施形態によるショットキー型のInAlN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図29及び図30は、第16の実施形態によるInAlN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【0199】

先ず、図29(a)に示すように、成長用基板として例えば半絶縁性のSiC基板1上に、化合物半導体の積層構造である化合物半導体層20を形成する。成長用基板としては、SiC基板の代わりに、Si基板、サファイア基板、GaAs基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

化合物半導体層20は、バッファ層20a、電子走行層20b、中間層20c、及び電子供給層20dを有して構成される。

【0200】

完成したInAlN/GaN・HEMTでは、その動作時において、電子走行層20bの電子供給層20d(正確には中間層20c)との界面近傍に2次元電子ガス(2DEG)が発生する。InAlN/GaN・HEMTでは、ピエゾ分極は殆ど発生しないが、電子供給層20dのInAlNが強い自発分極を有しており、電子走行層20bの自発分極と相俟って、主に当該自発分極に基づいて2DEGが生成される。

【0201】

詳細には、SiC基板1上に、例えばMOVPE法により、以下の各化合物半導体を成長する。MOVPE法の代わりに、MBE法等を用いても良い。

SiC基板1上に、バッファ層20a、電子走行層20b、中間層20c、及び電子供給層20dとなる各化合物半導体を順次成長する。バッファ層20aは、Si基板1上に、AlNを0.1μm程度の厚みに成長することで形成される。電子走行層20bは、i−GaNを1μm程度〜3μm程度の厚みに成長することで形成される。中間層20cは、i−InAlNを5nm程度の厚みに成長することで形成される。電子供給層20dは、i−InAlNを30nm程度の厚みに成長することで形成される。中間層20cは形成しない場合もある。

【0202】

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH3)ガスの混合ガスを用いる。InAlNの成長には、原料ガスとしてトリメチルインジウム(TMIn)ガス、TMAlガス、及びNH3ガスの混合ガスを用いる。成長する化合物半導体層に応じて、TMGaガス、TMInガス、TMAlガスの供給の有無及び流量を適宜設定する。共通原料であるNH3ガスの流量は、100sccm〜10slm程度とする。また、成長圧力は50Torr〜300Torr程度、成長温度は1000℃〜1200℃程度とする。

【0203】

続いて、素子分離構造を形成する。

詳細には、化合物半導体層2の素子分離領域に例えばアルゴン(Ar)を注入する。これにより、化合物半導体層2及びSiC基板1の表層部分に素子分離構造が形成される。素子分離構造により、化合物半導体層2上で活性領域が画定される。

なお、素子分離は、上記の注入法の代わりに、例えばSTI(Shallow Trench Isolation)法を用いて行っても良い。

【0204】

続いて、図29(b)に示すように、ソース電極36及びドレイン電極37を形成する。

電極材料として例えばTa/Al(下層がTa、上層がAl)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体層20上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/Alを堆積する。Taの厚みは20nm程度、Alの厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/Alを除去する。その後、SiC基板1を、例えば窒素雰囲気中において400℃〜1000℃、例えば550℃程度で熱処理し、残存したTa/Alを電子供給層20dとオーミックコンタクトさせる。以上により、Ta/Alからなるソース電極36及びドレイン電極37が形成される。

【0205】

続いて、図29(c)に示すように、化合物半導体層20の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiON膜6との積層構造とされる。

【0206】

詳細には、化合物半導体層20の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiONを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiON膜6を形成する。以上により、SiN膜5及びSiON膜6が積層されてなるパッシベーション膜が形成される。

【0207】

続いて、図30(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiON膜6のゲート電極の形成予定位置に開口6aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0208】

続いて、図30(b)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6の開口6aは、SiN膜5の開口5aよりも幅広となる。開口5a,6aが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0209】

続いて、図30(c)に示すように、ゲート電極38を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6a内をゲートメタルで埋め込み化合物半導体層20の表面とショットキー接触する、ゲート電極38が形成される。

【0210】

ゲート電極38は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極38のNiとの接触部分では、SiON膜6の酸素とゲート電極38のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層38aが形成される。

【0211】

しかる後、ソース電極3及びドレイン電極4、ゲート電極38の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0212】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層20の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極38が形成される。この構成では、ゲート電極38は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0213】

更に本実施形態では、SiON膜6の酸素とゲート電極38のオーバーハング部分のNiとが反応してNiO層38aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極38のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極38中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層38aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0214】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いInAlN/GaN・HEMTが得られる。

【0215】

なお、上記の諸実施形態では、パッシベーション膜を下層絶縁膜と上層絶縁膜との2層構造とした場合を例示したが、これに限定されるものではない。化合物半導体層と接触する膜が酸素非含有の絶縁膜であり、ゲート電極のオーバーハング部分と接触する膜が酸素含有の絶縁膜であれば、パッシベーション膜を3層以上の多層構造に形成しても良い。

【0216】

また、上記の諸実施形態では、パッシベーション膜を構成する酸素含有の上層絶縁膜として、Al2O3膜を用いても良い。

また、AlGaN/GaN・HEMT、InAlN/GaN・HEMT以外に、例えば、電子供給層をi−InAlGaNで形成する等としたInAlGaN/GaN・HEMT等にも適用できる。

【0217】

また、上記の諸実施形態における化合物半導体のエピタキシャル構造は一例であり、電界効果トランジスタであれば他の如何なる構造でも適用可能である。

また、上記の諸実施形態におけるソース電極及びドレイン電極の層構造は一例であり、単層・多層を問わず他の層構造であっても問題なく、また各電極の形成方法についても、一例であり、他の如何なる形成方法でも問題ない。

【0218】

(第17の実施形態)

本実施形態では、第1〜第15の実施形態によるAlGaN/GaN・HEMTから選ばれた1種、又は第16の実施形態によるInAlN/GaN・HEMTを備えた電源装置を開示する。

図31は、第17の実施形態による電源装置の概略構成を示す結線図である。

【0219】

本実施形態による電源装置は、高圧の一次側回路41及び低圧の二次側回路42と、一次側回路41と二次側回路42との間に配設されるトランス43とを備えて構成される。

一次側回路41は、交流電源44と、いわゆるブリッジ整流回路45と、複数(ここでは4つ)のスイッチング素子46a,46b,46c,46dとを備えて構成される。また、ブリッジ整流回路45は、スイッチング素子46eを有している。

二次側回路42は、複数(ここでは3つ)のスイッチング素子47a,47b,47cを備えて構成される。

【0220】

本実施形態では、一次側回路41のスイッチング素子46a,46b,46c,46d,46eが、第1〜第15の実施形態によるAlGaN/GaN・HEMTから選ばれた1種、又は第16の実施形態によるInAlN/GaN・HEMTとされている。一方、二次側回路42のスイッチング素子47a,47b,47cは、シリコンを用いた通常のMIS・FETとされている。

【0221】

本実施形態では、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMT又はInAlN/GaN・HEMTを、高圧回路に適用する。これにより、信頼性の高い大電力の電源回路が実現する。

【0222】

(第18の実施形態)

本実施形態では、第1〜第15の実施形態によるAlGaN/GaN・HEMTから選ばれた1種、又は第16の実施形態によるInAlN/GaN・HEMTを適用した高周波増幅器を開示する。

図32は、第18の実施形態による高周波増幅器の概略構成を示す結線図である。

【0223】

本実施形態による高周波増幅器は、ディジタル・プレディストーション回路51と、ミキサー52a,52bと、パワーアンプ53とを備えて構成される。

ディジタル・プレディストーション回路51は、入力信号の非線形歪みを補償するものである。ミキサー52aは、非線形歪みが補償された入力信号と交流信号をミキシングするものである。パワーアンプ53は、交流信号とミキシングされた入力信号を増幅するものであり、第1〜第15の実施形態によるAlGaN/GaN・HEMTから選ばれた1種、又は第16の実施形態によるInAlN/GaN・HEMTを有している。なお図32では、例えばスイッチの切り替えにより、出力側の信号をミキサー52bで交流信号とミキシングしてディジタル・プレディストーション回路51に送出できる構成とされている。

【0224】

本実施形態では、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMT又はInAlN/GaN・HEMTを、高周波増幅器に適用する。これにより、信頼性の高い高耐圧の高周波増幅器が実現する。

【0225】

以下、化合物半導体装置及びその製造方法の諸態様を付記としてまとめて記載する。

【0226】

(付記1)化合物半導体層と、

開口を有し、前記化合物半導体層上を覆う保護膜と、

前記開口を埋め込み、前記化合物半導体層上に乗り上げる形状の電極と

を含み、

前記保護膜は、酸素非含有の下層絶縁膜と、酸素含有の上層絶縁膜との積層構造を有しており、

前記開口は、前記下層絶縁膜に形成された第1の開口と、前記上層絶縁膜に形成された前記第1の開口よりも幅広の第2の開口とが連通してなることを特徴とする化合物半導体装置。

【0227】

(付記2)前記上層絶縁膜と前記電極との間に、両者が反応してなる酸化膜が形成されていることを特徴とする付記1に記載の化合物半導体装置。

【0228】

(付記3)前記酸化膜は、NiO又はCuOであることを特徴とする付記2に記載の化合物半導体装置。

【0229】

(付記4)前記上層絶縁膜は、SiON,SiO2,Al2O3から選ばれた少なくとも1種であることを特徴とする付記1〜3のいずれか1項に記載の化合物半導体装置。

【0230】

(付記5)前記上層絶縁膜は、NiOを含むことを特徴とする付記1に記載の化合物半導体装置。

【0231】

(付記6)前記上層絶縁膜は、前記電極の下部周辺のみに設けられていることを特徴とする付記1〜5のいずれか1項に記載の化合物半導体装置。

【0232】

(付記7)前記上層絶縁膜は、前記電極の片側のみに設けられていることを特徴とする付記1〜6のいずれか1項に記載の化合物半導体装置。

【0233】

(付記8)前記化合物半導体層の表層に、前記第1の開口と連通する溝が形成されており、

前記溝及び前記開口を埋め込むように前記電極が形成されていることを特徴とする付記1〜7のいずれか1項に記載の化合物半導体装置。

【0234】

(付記9)前記上層絶縁膜は、その表層に他の部分よりも酸素含有率の高い薄膜が形成されていることを特徴とする付記1〜8のいずれか1項に記載の化合物半導体装置。

【0235】

(付記10)化合物半導体層上を覆うように、酸素非含有の下層絶縁膜と酸素含有の上層絶縁膜との積層構造を有する保護膜を形成する工程と、

前記下層絶縁膜に第1の開口を、前記上層絶縁膜に前記第1の開口よりも幅広の第2の開口を、前記第1の開口と前記第2の開口とが連通するように形成する工程と、

前記開口を埋め込み、前記化合物半導体層上に乗り上げる形状に電極を形成する工程と

を含むことを特徴とする化合物半導体装置の製造方法。

【0236】

(付記11)前記上層絶縁膜と前記電極との間に、両者が反応してなる酸化膜が形成されることを特徴とする付記10に記載の化合物半導体装置の製造方法。

【0237】

(付記12)前記酸化膜は、NiO又はCuOであることを特徴とする付記11に記載の化合物半導体装置の製造方法。

【0238】

(付記13)前記上層絶縁膜は、SiON,SiO2,Al2O3から選ばれた少なくとも1種であることを特徴とする付記10〜12のいずれか1項に記載の化合物半導体装置の製造方法。

【0239】

(付記14)前記上層絶縁膜は、NiOを含むことを特徴とする付記10に記載の化合物半導体装置の製造方法。

【0240】

(付記15)前記上層絶縁膜は、前記電極の下部周辺のみに設けられていることを特徴とする付記10〜14のいずれか1項に記載の化合物半導体装置の製造方法。

【0241】

(付記16)前記上層絶縁膜は、前記電極の片側のみに設けられていることを特徴とする付記10〜15のいずれか1項に記載の化合物半導体装置の製造方法。

【0242】

(付記17)前記第1の開口の形成に用いたマスクを引き続き用い、前記下層絶縁膜と前記上層絶縁膜とのエッチング速度の相違を利用したウェットエッチングにより前記第2の開口を形成することを特徴とする付記10〜15のいずれか1項に記載の化合物半導体装置の製造方法。

【0243】

(付記18)前記化合物半導体層の表層に、前記第1の開口と連通する溝を形成し、

前記溝及び前記開口を埋め込むように前記電極を形成することを特徴とする付記10〜15のいずれか1項に記載の化合物半導体装置の製造方法。

【0244】

(付記19)変圧器と、前記変圧器を挟んで高圧回路及び低圧回路とを備えた電源回路であって、

前記高圧回路はトランジスタを有しており、

前記トランジスタは、

化合物半導体層と、

開口を有し、前記化合物半導体層上を覆う保護膜と、

前記開口を埋め込み、前記化合物半導体層上に乗り上げる形状の電極と

を含み、

前記保護膜は、酸素非含有の下層絶縁膜と、酸素含有の上層絶縁膜との積層構造を有しており、

前記開口は、前記下層絶縁膜に形成された第1の開口と、前記上層絶縁膜に形成された前記第1の開口よりも幅広の第2の開口とが連通してなることを特徴とする電源回路。

【0245】

(付記20)入力した高周波電圧を増幅して出力する高周波増幅器であって、

トランジスタを有しており、

化合物半導体層と、

開口を有し、前記化合物半導体層上を覆う保護膜と、

前記開口を埋め込み、前記化合物半導体層上に乗り上げる形状の電極と

を含み、

前記保護膜は、酸素非含有の下層絶縁膜と、酸素含有の上層絶縁膜との積層構造を有しており、

前記開口は、前記下層絶縁膜に形成された第1の開口と、前記上層絶縁膜に形成された前記第1の開口よりも幅広の第2の開口とが連通してなることを特徴とする高周波増幅器。

【符号の説明】

【0246】

1 SiC基板

2,20 化合物半導体層

2a,20a バッファ層

2b,20b 電子走行層

2c,20c 中間層

2d,20d 電子供給層

2da 溝

2eA,2eB 電極溝

2e キャップ層

3,36 ソース電極

4,37 ドレイン電極

5 SiN膜

5a,6a,6b,17a,6Aa,6Ba,21Aa,25,27a,29a,32a 開口

5b 凹部

6 SiON膜

6A SiON片

6B SiON層

7,12,13,15,16,18,19,22,23,26,28,31,33,34,35,38 ゲート電極

7a,12a,13a,15a,16a,19a,22a,23a,26a,28a,31a,33a,35a,38a NiO層

11 溝

14 ゲート絶縁膜

17,21 NiO膜

21A NiO片

24 酸素リッチ膜

27,29 レジストマスク

32 SiO2膜

34a CuO層

41 一次側回路

42 二次側回路

43 トランス

44 交流電源

45 ブリッジ整流回路

46a,46b,46c,46d,46e,47a,47b,47c スイッチング素子

51 ディジタル・プレディストーション回路

52a,52b ミキサー

53 パワーアンプ

【技術分野】

【0001】

本発明は、化合物半導体装置及びその製造方法に関する。

【背景技術】

【0002】

窒化物半導体装置は、高い飽和電子速度及びワイドバンドギャップ等の特徴を利用し、高耐圧及び高出力の半導体デバイスとしての開発が活発に行われている。窒化物半導体デバイスとしては、電界効果トランジスタ、特に高電子移動度トランジスタ(High Electron Mobility Transistor:HEMT)についての報告が数多くなされている。特に、GaNを電子走行層として、AlGaNを電子供給層として用いたAlGaN/GaN・HEMTが注目されている。AlGaN/GaN・HEMTでは、GaNとAlGaNとの格子定数差に起因した歪みがAlGaNに生じる。これにより発生したピエゾ分極及びAlGaNの自発分極により、高濃度の2次元電子ガス(2DEG)が得られる。そのため、高耐圧及び高出力が実現できる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2002−359256号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

AlGaN/GaN・HEMT等の高出力高周波用の窒化物半導体装置では、高電圧下で動作させる際の問題点の1つとして、電流コラプス現象が挙げられる。この電流コラプスは、高電圧印加によりオン抵抗が増大する現象のことを指し、電子が半導体結晶中や半導体/絶縁膜界面等にトラップされ、その領域の2DEG濃度が減少することにより起こるとされている。電流コラプス現象を抑制するための1つの手法として、フィールドプレート構造が広く知られている。例えば、ゲート電極をいわゆるオーバーハング形状に形成することにより、電流コラプス現象の抑制に効果があることが知られている。

【0005】

しかしながら、上記のフィールドプレート構造のみでは充分に電流コラプス現象を抑制することは難しく、特に高電圧動作時に顕著に電流コラプスが起きてしまう問題点があり、更なる電流コラプス抑制手法が望まれている。

【0006】

本発明は、上記の課題に鑑みてなされたものであり、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

化合物半導体装置の一態様は、化合物半導体層と、開口を有し、前記化合物半導体層上を覆う保護膜と、前記開口を埋め込み、前記化合物半導体層上に乗り上げる形状の電極と

を含み、前記保護膜は、酸素非含有の下層絶縁膜と、酸素含有の上層絶縁膜との積層構造を有しており、前記開口は、前記下層絶縁膜に形成された第1の開口と、前記上層絶縁膜に形成された前記第1の開口よりも幅広の第2の開口とが連通してなる。

【0008】

化合物半導体装置の製造方法の一態様は、化合物半導体層上を覆うように、酸素非含有の下層絶縁膜と酸素含有の上層絶縁膜との積層構造を有する保護膜を形成する工程と、前記下層絶縁膜に第1の開口を、前記上層絶縁膜に前記第1の開口よりも幅広の第2の開口を、前記第1の開口と前記第2の開口とが連通するように形成する工程と、前記開口を埋め込み、前記化合物半導体層上に乗り上げる形状に電極を形成する工程とを含む。

【発明の効果】

【0009】

上記の諸態様によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置が得られる。

【図面の簡単な説明】

【0010】

【図1】第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図2】図1に引き続き、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【図3】第1の実施形態によるAlGaN/GaN・HEMTの電流−電圧特性について調べた実験結果を示す特性図である。

【図4】第2の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図5】第3の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図6】第4の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図7】図6に引き続き、第4の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図8】第5の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図9】図8に引き続き、第5の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図10】第6の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図11】図10に引き続き、第6の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図12】第7の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図13】図12に引き続き、第7の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図14】第8の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図15】図14に引き続き、第8の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図16】第9の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図17】図16に引き続き、第9の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図18】第10の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図19】図18に引き続き、第10の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図20】第11の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図21】図20に引き続き、第11の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図22】第12の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図23】図22に引き続き、第12の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図24】第13の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図25】図24に引き続き、第13の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図26】第14の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図27】第15の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図28】図27に引き続き、第15の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図29】第16の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図30】図29に引き続き、第16の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【図31】第17の実施形態による電源装置の概略構成を示す結線図である。

【図32】第18の実施形態による高周波増幅器の概略構成を示す結線図である。

【発明を実施するための形態】

【0011】

以下、諸実施形態について図面を参照して詳細に説明する。以下の諸実施形態では、化合物半導体装置の構成について、その製造方法と共に説明する。

なお、以下の図面において、図示の便宜上、相対的に正確な大きさ及び厚みに示していない構成部材がある。

【0012】

(第1の実施形態)

本実施形態では、化合物半導体装置としてショットキー型のAlGaN/GaN・HEMTを開示する。

図1及び図2は、第1の実施形態によるAlGaN/GaN・HEMTの製造方法を工程順に示す概略断面図である。

【0013】

先ず、図1(a)に示すように、成長用基板として例えば半絶縁性のSiC基板1上に、化合物半導体の積層構造である化合物半導体層2を形成する。成長用基板としては、SiC基板の代わりに、Si基板、サファイア基板、GaAs基板、GaN基板等を用いても良い。また、基板の導電性としては、半絶縁性、導電性を問わない。

化合物半導体層2は、バッファ層2a、電子走行層2b、中間層2c、及び電子供給層2dを有して構成される。

【0014】

完成したAlGaN/GaN・HEMTでは、その動作時において、電子走行層2bの電子供給層2d(正確には中間層2c)との界面近傍に2次元電子ガス(2DEG)が発生する。この2DEGは、電子走行層2b及び電子供給層2dの自発分極と相俟って、電子走行層2bの化合物半導体(ここではGaN)と電子供給層2dの化合物半導体(ここではAlGaN)との格子定数の相違に起因した歪みによるピエゾ分極に基づいて生成される。

【0015】

詳細には、SiC基板1上に、例えば有機金属気相成長(MOVPE:Metal Organic Vapor Phase Epitaxy)法により、以下の各化合物半導体を成長する。MOVPE法の代わりに、分子線エピタキシー(MBE:Molecular Beam Epitaxy)法等を用いても良い。

SiC基板1上に、バッファ層2a、電子走行層2b、中間層2c、及び電子供給層2dとなる各化合物半導体を順次成長する。バッファ層2aは、Si基板1上に、AlNを0.1μm程度の厚みに成長することで形成される。電子走行層2bは、i(インテンショナリ・アンドープ)−GaNを1μm程度〜3μm程度の厚みに成長することで形成される。中間層2cは、i−AlGaNを5nm程度の厚みに成長することで形成される。電子供給層2dは、n−AlGaNを30nm程度の厚みに成長することで形成される。中間層2cは形成しない場合もある。電子供給層は、i−AlGaNを形成するようにしても良い。

【0016】

GaNの成長には、原料ガスとしてGa源であるトリメチルガリウム(TMGa)ガス及びアンモニア(NH3)ガスの混合ガスを用いる。AlGaNの成長には、原料ガスとしてTMAlガス、TMGaガス及びNH3ガスの混合ガスを用いる。成長する化合物半導体層に応じて、TMAlガス、TMGaガスの供給の有無及び流量を適宜設定する。共通原料であるNH3ガスの流量は、100sccm〜10slm程度とする。また、成長圧力は50Torr〜300Torr程度、成長温度は1000℃〜1200℃程度とする。

【0017】

AlGaNをn型として成長する際、即ち電子供給層2d(n−AlGaN)の形成には、n型不純物をAlGaNの原料ガスに添加する。ここでは、例えばSiを含む例えばシラン(SiH4)ガスを所定の流量で原料ガスに添加し、AlGaNにSiをドーピングする。Siのドーピング濃度は、1×1018/cm3程度〜1×1020/cm3程度、例えば2×1018/cm3程度とする。

【0018】

続いて、素子分離構造を形成する。

詳細には、化合物半導体層2の素子分離領域に例えばアルゴン(Ar)を注入する。これにより、化合物半導体層2及びSiC基板1の表層部分に素子分離構造が形成される。素子分離構造により、化合物半導体層2上で活性領域が画定される。

なお、素子分離は、上記の注入法の代わりに、例えばSTI(Shallow Trench Isolation)法を用いて行っても良い。

【0019】

続いて、図1(b)に示すように、ソース電極3及びドレイン電極4を形成する。

電極材料として例えばTa/Al(下層がTa、上層がAl)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを化合物半導体層2上に塗布し、ソース電極及びドレイン電極の各形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ta/Alを堆積する。Taの厚みは20nm程度、Alの厚みは200nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したTa/Alを除去する。その後、SiC基板1を、例えば窒素雰囲気中において400℃〜1000℃、例えば550℃程度で熱処理し、残存したTa/Alを電子供給層2dとオーミックコンタクトさせる。以上により、Ta/Alからなるソース電極3及びドレイン電極4が形成される。

【0020】

続いて、図1(c)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiON膜6との積層構造とされる。

【0021】

詳細には、化合物半導体層2の全面にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiONを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiON膜6を形成する。以上により、SiN膜5及びSiON膜6が積層されてなるパッシベーション膜が形成される。

【0022】

続いて、図2(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiON膜6のゲート電極の形成予定位置に開口6aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0023】

続いて、図2(b)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6の開口6aは、SiN膜5の開口5aよりも幅広となる。開口5a,6aが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0024】

続いて、図2(c)に示すように、ゲート電極7を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極7が形成される。

【0025】

ゲート電極7は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極7のNiとの接触部分では、SiON膜6の酸素とゲート電極7のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層7aが形成される。

【0026】

しかる後、ソース電極3及びドレイン電極4、ゲート電極7の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0027】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極7が形成される。この構成では、ゲート電極7は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0028】

更に本実施形態では、SiON膜6の酸素とゲート電極7のオーバーハング部分のNiとが反応してNiO層7aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極7のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極7中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層7aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0029】

ここで、本実施形態によるAlGaN/GaN・HEMTの電流−電圧特性について調べた実験について説明する。本実施形態の比較例として、パッシベーション膜がSiNの単層からなる従来のAlGaN/GaN・HEMTを例示する。

実験結果を図3に示す。(a)が比較例、(b)が本実施形態である。比較例では、50Vのバイアスストレスにより、オン抵抗が増大しており、電流コラプスが大きい。これに対して本実施形態では、オン抵抗の増加が非常に小さく、効果的に電流コラプスを抑制できることが確認された。

【0030】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0031】

(第2の実施形態)

以下、第2の実施形態によるショットキー型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図4は、第2の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0032】

先ず、第1の実施形態の図1(a)〜図2(a)の諸工程を経て、図4(a)に示すように、SiON膜6に開口6aを形成する。

を形成する。

【0033】

続いて、図4(b)に示すように、SiON膜6及び電子供給層2dに溝11を形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用い、SiN膜5及び電子供給層2dの表層まで、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層2d及びSiN膜5のゲート電極の形成予定位置に、SiN膜5を貫通して電子供給層2dの表層まで掘る溝11が形成される。SiON膜6の開口6aは、溝11よりも幅広となる。溝11及び開口6aが連通し、ゲート電極を形成するための電極溝が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0034】

続いて、図4(c)に示すように、ゲート電極12を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを溝11及び開口6a内を含むSiON膜6上に塗布し、溝11及び開口6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、溝11及び開口6a内をゲートメタルで埋め込み化合物半導体層2の表面とショットキー接触する、ゲート電極12が形成される。

【0035】

ゲート電極12は、溝11及び開口6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極12のNiとの接触部分では、SiON膜6の酸素とゲート電極12のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層7aが形成される。

【0036】

しかる後、ソース電極3及びドレイン電極4、ゲート電極12の電気的接続等の諸工程を経て、ショットキー型のAlGaN/GaN・HEMTが形成される。

【0037】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。ショットキー面となる化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5によりショットキー面から離間しているため、ショットキー面に対して影響を及ぼす懸念はない。電子供給層2d及びSiN膜5の溝11と、開口5aよりも幅広のSiON膜6の開口6aとが連通し、溝11及び開口6aからなる電極溝内を埋め込むようにオーバーハング形状のゲート電極12が形成される。この構成では、ゲート電極12は、溝11を充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0038】

更に本実施形態では、SiON膜6の酸素とゲート電極12のオーバーハング部分のNiとが反応してNiO層12aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極12のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極12中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層12aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0039】

更に本実施形態では、溝11の一環として電子供給層2dにも溝部が形成され、ゲート電極12の最下部が当該溝部に形成される。これにより、電源のオフ時にゲート電流が流れない、いわゆるノーマリ・オフの実現に寄与すると共に、ゲート電極12における電界集中が更に緩和される。

【0040】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0041】

(第3の実施形態)

以下、第3の実施形態によるMIS型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図5は、第3の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0042】

先ず、第1の実施形態の図1(a)〜図2(a)の諸工程を経て、図5(a)に示すように、SiON膜6に開口6aを形成する。

を形成する。

【0043】

続いて、図5(b)に示すように、ゲート電極13を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口6a内を含むSiON膜6上に塗布し、開口6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口6a内をゲートメタルで埋め込むように、化合物半導体層2上でSiN膜5を介してゲート電極13が形成される。SiN膜5は、パッシベーション膜であると共にゲート絶縁膜としても機能する。

【0044】

ゲート電極13は、開口6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極13のNiとの接触部分では、SiON膜6の酸素とゲート電極13のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層13aが形成される。

【0045】

しかる後、ソース電極3及びドレイン電極4、ゲート電極13の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

【0046】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適である。化合物半導体層2の表面は、酸素非含有のSiN膜5で直接的に覆われており、SiN膜5が主に保護膜としての機能を果たす。酸素含有のSiON膜6はSiN膜5により化合物半導体層2の表面から離間しているため、当該表面に対して影響を及ぼす懸念はない。SiON膜6の開口6a内を埋め込むようにオーバーハング形状のゲート電極13が形成される。この構成では、ゲート電極13は、開口6aを充填する部分及びオーバーハング部分の徐々に幅広となる多段構造(ここでは2段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0047】

更に本実施形態では、SiON膜6の酸素とゲート電極13のオーバーハング部分のNiとが反応してNiO層13aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極13のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極13中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層13aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0048】

更に本実施形態では、2層構造のパッシベーション膜において、下層のSiN膜5は、パッシベーション膜であると共に、ゲート絶縁膜としても機能する。この構成では、2層構造のパッシベーション膜とは別にゲート絶縁膜を形成する工程が削減すると共に、所期のMIS型のAlGaN/GaN・HEMTが実現する。

【0049】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0050】

(第4の実施形態)

以下、第4の実施形態によるMIS型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図6及び図7は、第4の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0051】

先ず、第1の実施形態の図1(a),(b)の諸工程を経て、図6(a)に示すように、化合物半導体層2上にソース電極3及びドレイン電極4を形成する。

【0052】

続いて、図6(b)に示すように、ゲート絶縁膜14を形成する。

詳細には、化合物半導体積層構造2上に絶縁材料として、酸素非含有の絶縁物、例えばAlNを堆積する。AlNは、例えば原子層堆積法(Atomic Layer Deposition:ALD法)により、厚みが膜厚2nm〜100nm程度、ここでは例えば10nm程度となるように、AlNを堆積する。これにより、ゲート絶縁膜14が形成される。

【0053】

なお、AlNの堆積は、ALD法の代わりに、例えばプラズマCVD法又はスパッタ法等で行うようにしても良い。また、AlNを堆積する代わりに、Alの窒化物を用いても良い。それ以外にも、Si,Hf,Zr,Ti,Ta,Wの窒化物、或いはこれらから適宜に選択して多層に堆積して、ゲート絶縁膜を形成しても良い。

【0054】

続いて、図6(c)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiON膜6との積層構造とされる。

【0055】

詳細には、ゲート絶縁膜14上にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiONを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiON膜6を形成する。以上により、SiN膜5及びSiON膜6が積層されてなるパッシベーション膜が形成される。

【0056】

続いて、図7(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiON膜6のゲート電極の形成予定位置に開口6aが形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0057】

続いて、図7(b)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6の開口6aは、SiN膜5の開口5aよりも幅広となる。開口5a,6aが連通し、ゲート電極を形成するための開口が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0058】

続いて、図7(c)に示すように、ゲート電極15を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、開口5a,6aを含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、開口5a,6a内をゲートメタルで埋め込むように、化合物半導体層2上でゲート絶縁膜14を介してゲート電極15が形成される。

【0059】

ゲート電極15は、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極15のNiとの接触部分では、SiON膜6の酸素とゲート電極15のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層15aが形成される。

【0060】

しかる後、ソース電極3及びドレイン電極4、ゲート電極15の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

【0061】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適であり、SiN膜5がAlNのゲート絶縁膜14と共に主に保護膜としての機能を果たす。酸素含有のSiON膜6はゲート絶縁膜14及びSiN膜5により化合物半導体層2の表面から離間しているため、当該表面に対して影響を及ぼす懸念はない。SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、開口5a,6aからなる開口内を埋め込むようにオーバーハング形状のゲート電極15が形成される。この構成では、ゲート電極15は、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは3段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0062】

更に本実施形態では、SiON膜6の酸素とゲート電極15のオーバーハング部分のNiとが反応してNiO層15aが形成される。NiOはp型酸化物半導体として機能する。ゲート電極15のオーバーハング部分は、多段構造の最上段に位置し、ゲート電極15中で、ドレイン電極4に最も近接した部分であって、最も大きな電界集中が発生する。このオーバーハング部分に形成されたp型酸化物半導体であるNiO層15aの存在により、オーバーハング部分の横方向抵抗が増加し、ゲート端の電界強度が大幅に緩和する。以上により、電流コラプス現象が抑制される。

【0063】

更に本実施形態では、ゲート絶縁膜14は、ゲート絶縁膜であると共にパッシベーション膜としても機能し、所期のMIS型のAlGaN/GaN・HEMTが実現する。

【0064】

以上説明したように、本実施形態によれば、高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高いAlGaN/GaN・HEMTが得られる。

【0065】

(第5の実施形態)

以下、第5の実施形態によるMIS型のAlGaN/GaN・HEMTについて説明する。なお、第1の実施形態によるAlGaN/GaN・HEMTと同様の構成部材等については、同符号を付して詳しい説明を省略する。

図8及び図9は、第5の実施形態によるAlGaN/GaN・HEMTの製造方法における主要工程を示す概略断面図である。

【0066】

先ず、第1の実施形態の図1(a),(b)の諸工程を経て、化合物半導体層2上にソース電極3及びドレイン電極4を形成する。

【0067】

続いて、図8(a)に示すように、電子供給層2dに溝2daを形成する。

詳細には、電子供給層2d上にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、電子供給層2dのゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、電子供給層2dの表層を、例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、電子供給層2dの表層におけるゲート電極の形成予定位置に溝11が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0068】

続いて、図8(b)に示すように、ゲート絶縁膜14を形成する。

詳細には、溝11の内壁面を含む化合物半導体積層構造2上に絶縁材料として、酸素非含有の絶縁物、例えばAlNを堆積する。AlNは、例えば原子層堆積法(Atomic Layer Deposition:ALD法)により、厚みが膜厚2nm〜100nm程度、ここでは例えば10nm程度となるように、AlNを堆積する。これにより、ゲート絶縁膜14が形成される。

【0069】

なお、AlNの堆積は、ALD法の代わりに、例えばプラズマCVD法又はスパッタ法等で行うようにしても良い。また、AlNを堆積する代わりに、Alの窒化物を用いても良い。それ以外にも、Si,Hf,Zr,Ti,Ta,Wの窒化物、或いはこれらから適宜に選択して多層に堆積して、ゲート絶縁膜を形成しても良い。

【0070】

続いて、図8(c)に示すように、化合物半導体層2の表面を保護するパッシベーション膜を形成する。

パッシベーション膜は、酸素を含有しない(酸素非含有の)下層絶縁膜、ここではSiN(Si3N4)膜5と、酸素を含有する(酸素含有の)上層絶縁膜、ここではSiON膜6との積層構造とされる。

【0071】

詳細には、ゲート絶縁膜14上にSiNを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiN膜5を形成する。引き続き、SiN膜5上にSiONを、プラズマCVD法又はスパッタ法等により例えば2nm程度〜200nm、例えば20nm程度の厚みに堆積し、SiON膜6を形成する。以上により、SiN膜5及びSiON膜6が積層されてなるパッシベーション膜が形成される。

【0072】

続いて、図9(a)に示すように、SiON膜6に開口6aを形成する。

詳細には、SiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、SiON膜6のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiON膜6を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。このとき、SiON膜6と共にSiN膜5の表層を若干エッチングしても構わない。これにより、SiON膜6のゲート電極の形成予定位置に開口6aが形成される。開口6aは、電子供給層2dの溝2daよりも幅広とされる。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0073】

続いて、図9(b)に示すように、SiN膜5に開口5aを形成する。

詳細には、開口6aから露出するSiN膜5上を含むSiON膜6の全面にレジストを塗布し、リソグラフィーによりレジストを加工する。これにより、開口6a内におけるSiN膜5のゲート電極の形成予定位置を露出する開口を有するレジストマスクが形成される。

このレジストマスクを用いて、SiN膜5を例えばフッ素系ガスをエッチングガスとして用いてドライエッチングする。これにより、SiN膜5のゲート電極の形成予定位置に開口5aが形成される。SiON膜6の開口6aは、SiN膜5の開口5aよりも幅広となる。ゲート絶縁膜14を介した溝2da、開口5a,6aが連通し、ゲート電極を形成するための電極溝が形成される。

レジストマスクは、アッシング処理又は所定の薬液を用いたウェット処理により除去される。

【0074】

続いて、図9(c)に示すように、ゲート電極16を形成する。

電極材料として例えばNi/Au(下層がNi、上層がAu)を用いる。電極形成には、蒸着法及びリフトオフ法に適した例えば庇構造2層レジストを用いる。このレジストを開口5a,6a内を含むSiON膜6上に塗布し、電極溝を含むゲート電極の形成予定位置を開口するレジストマスクを形成する。このレジストマスクを用いて、例えば蒸着法により、Ni/Auを堆積する。Niの厚みは30nm程度、Auの厚みは400nm程度とする。リフトオフ法により、庇構造のレジストマスク及びその上に堆積したNi/Auを除去する。これにより、電極溝内をゲートメタルで埋め込むように、化合物半導体層2上でゲート絶縁膜14を介してゲート電極16が形成される。

【0075】

ゲート電極16は、ゲート絶縁膜14を介した溝2da、開口5a,6a内を埋め込みSiON膜6上に乗り上げるNiと、Ni上に堆積したAuとから、いわゆるオーバーハング形状に形成される。SiON膜6表面の開口6aの周辺におけるゲート電極16のNiとの接触部分では、SiON膜6の酸素とゲート電極16のオーバーハング部分のNiとが反応し、薄い酸化膜であるNiO層16aが形成される。

【0076】

しかる後、ソース電極3及びドレイン電極4、ゲート電極16の電気的接続等の諸工程を経て、MIS型のAlGaN/GaN・HEMTが形成される。

【0077】

本実施形態では、パッシベーション膜が酸素非含有のSiN膜5と、酸素含有のSiON膜6との積層構造に形成されている。パッシベーション膜としては、界面準位の少ない酸素非含有の絶縁膜が好適であり、SiN膜5がAlNのゲート絶縁膜14と共に主に保護膜としての機能を果たす。酸素含有のSiON膜6はゲート絶縁膜14及びSiN膜5により化合物半導体層2の表面から離間しているため、当該表面に対して影響を及ぼす懸念はない。電子供給層2dの溝2daと、SiN膜5の開口5aと、開口5aよりも幅広のSiON膜6の開口6aとが連通し、溝2da及び開口5a,6aからなる電極溝内を埋め込むようにオーバーハング形状のゲート電極16が形成される。この構成では、ゲート電極16は、溝2daをゲート絶縁膜14を介して充填する部分、開口5aを充填する部分、開口6aを充填する部分、及びオーバーハング部分の徐々に幅広となる多段構造(ここでは4段構造)に形成され、高電圧動作時の電界集中点が分散される。

【0078】