半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマーク終端部への応力集中により基板にクラックが発生することを軽減する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体ウェハ、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

複数の半導体チップを積層して高機能を実現した半導体装置では、半導体チップを貫通するようにして設けられた貫通電極(Through Silicon Via、以下、TSVと記載する場合がある)によって、上下の半導体チップを電気的に接続する構造が用いられる。このような半導体チップでは、TSVと素子領域とを絶縁分離することや、近隣のTSV間容量を低減することを目的として、TSVの周囲を絶縁体で囲んだ絶縁リング構造が用いられることがある。

【0003】

特許文献1(特開2009−111061号公報)には、絶縁リングを備えた貫通電極を有する半導体装置の製造方法が開示されている。ここには、最初に絶縁リングを形成し(ビアファースト)、素子形成〜配線形成を経て、最後にTSVを形成する(ビアラスト)工程が開示されている。より詳しくは、まず、シリコン基板の素子形成面側から深さ方向にリング状のトレンチを掘り、このトレンチを絶縁膜で埋め込むことで絶縁リングを形成する。その後、基板表面への素子形成、配線層形成および表面電極形成工程などを経た後、シリコン基板を裏面側から研削して薄板化する。このとき絶縁リングの底部が基板裏面から露出するまで裏面研削することで、絶縁リングがシリコン基板を表面から裏面まで貫通した構造となる。そして、絶縁リングの内側に、シリコン基板を貫通するように、裏面側から裏面電極を形成することによりTSVを形成する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−111061号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記の方法とは異なり、絶縁リング等をビアファーストで形成せず、素子分離領域(フィールド)を形成する工程が基板に施す最初の工程であれば、当該素子分離領域の基板上での位置を調整する必要は無い。すなわち、素子分離領域の形成時には、基板上に他の部材が形成されていないため、これらの部材に対して素子分離領域の位置合わせを行う必要が無い。

【0006】

一方、上記のように、ビアファーストで既に絶縁リングが形成された基板上に素子分離領域を形成する場合、当該素子分離領域は基板上での位置を調整して(位置合わせして)形成する必要がある。即ち、絶縁リング形成の後、基板に対して素子分離領域用のパターニングをする前に、フォトリソグラフィに用いるアライメントマークを形成しておく必要がある。

【0007】

しかしながら、従来の方法では、アライメントマーク用のトレンチが深く、その幅が狭いため、トレンチ内に絶縁膜を埋設させると内部にシームやボイドが発生する場合があった。アライメントマーク用のトレンチはラインアンドスペース形状で形成するため、シームやボイドなどの埋設不良箇所に応力が集中して、この部分を起点に基板内にクラックが発生する場合があった。このクラックは素子領域にまで達することがあり、この場合、製造歩留まりが低下することとなっていた。

【課題を解決するための手段】

【0008】

一実施形態は、

基板の第1の主面に、前記第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する工程と、

前記第1及び第2の溝を埋め込むように、絶縁膜を形成する工程と、

前記絶縁膜を形成する工程の後、前記基板の第1の主面にフォトレジスト膜を形成する工程と、

前記絶縁膜で埋め込まれた前記第2の溝の前記基板上での位置を基準として位置合わせした第1のパターンを、前記フォトレジスト膜に転写する工程と、

前記絶縁膜で埋め込まれた環状の前記第1の溝の内側に位置する前記基板に、前記基板を厚さ方向に貫通する貫通電極を形成する工程と、

を有することを特徴とする半導体装置の製造方法に関する。

【0009】

他の実施形態は、

基板と、

前記基板を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が環状となる絶縁リングと、

前記基板を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が終端部を有さない形状となるアライメントマークと、

前記環状の絶縁リングの内側に位置する前記基板内に、前記基板を厚さ方向に貫通するように設けられた貫通電極と、

を有することを特徴とする半導体ウェハに関する。

【0010】

他の実施形態は、

基板と、

前記基板のチップ領域を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が環状となる絶縁リングと、

前記基板のチップ領域を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が終端部を有さない形状となるアライメントマークと、

前記環状の絶縁リングの内側に位置する前記チップ領域内に、前記基板を厚さ方向に貫通するように設けられた貫通電極と、

を有することを特徴とする半導体装置に関する。

【発明の効果】

【0011】

終端部を含まない形状のアライメントマークを形成する。これにより、アライメントマーク終端部への応力集中によって基板にクラックが発生することを軽減できる。

【図面の簡単な説明】

【0012】

【図1】本発明者が検討した方法を表す図である。

【図2】本発明者が検討した方法を表す図である。

【図3】本発明者が検討した方法を表す図である。

【図4】第1実施例の半導体装置を表す図である。

【図5】第1実施例の半導体装置の製造方法を表すフローチャートである。

【図6】第1実施例の半導体装置の製造方法を表す図である。

【図7】第1実施例の半導体装置の製造方法を表す図である。

【図8】第1実施例の半導体装置の製造方法を表す図である。

【図9】第1実施例の半導体装置の製造方法を表す図である。

【図10】第1実施例の半導体装置の製造方法を表す図である。

【図11】第1実施例の半導体装置の製造方法を表す図である。

【図12】第1実施例の半導体装置の製造方法を表す図である。

【図13】第1実施例の半導体装置の製造方法を表す図である。

【図14】第1実施例の半導体装置の製造方法を表す図である。

【図15】第1実施例の半導体装置の製造方法を表す図である。

【図16】第1実施例の第1変形例を表す図である。

【図17】第1実施例の第2変形例を表す図である。

【図18】第1実施例の第3変形例を表す図である。

【発明を実施するための形態】

【0013】

特開2005−217071号公報には、チップ積層時の位置合わせ基準となるアライメントマークを、TSV本体を形成する工程によって同時に形成する方法が開示されている。より詳しくは、ウェハから切り出した複数のチップを互いに積層する際、位置合わせのずれを起こさないよう、ボンディング装置にチップの位置を認識させるためのアライメントマークとして、TSVと同様の基板を貫通する導電材料を用いて構成し、TSV形成工程時に同時に形成するという技術である。

【0014】

そこで、本発明者は、上記技術の応用例として、素子形成工程の最初の工程であるSTI(フィールド)パターンを転写する工程(フォトリソグラフィ工程)の際に、位置合わせの基準となるアライメントマークを、絶縁リングと同時に形成する方法について、事前に検討した。通常、半導体装置の構成要素が何も形成されていないウェハ上に最初にSTIを形成する場合、いかなる要素に対しても位置合わせをする必要が無いので、STI形成工程においてアライメントマークは必要無い。また、STI形成工程の後の工程においては、STI形成工程で同時に形成したアライメントマークを基準に位置合わせすれば良い。

【0015】

一方、本願で対象にする構造は、TSVの周囲を囲む絶縁リングを最初に形成した後(ビアファースト)、素子形成工程に入る。従って、この絶縁リングに対してSTIを位置合わせするためのアライメントマーク(フィールド合わせマーク)が必要となり、これを形成する方法として上述の技術を検討した。本発明者が検討したフィールド合わせマークは、リソグラフィ工程の際に認識できるよう、絶縁溝がラインアンドスペース(L/S)状に配列した形状である。

【0016】

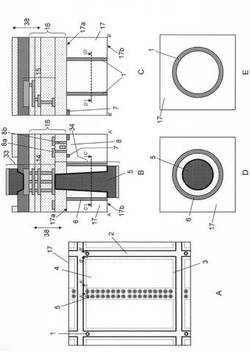

以下では、図1〜3を参照して、本発明者が検討した半導体装置及びその製造方法を説明する。なお、各図において適宜、一部の構造を省略し、重要な構造のみを示す。図1Aに示すように、この半導体装置は、半導体基板17上にスクライブ領域2に囲まれたチップ領域3を有する。チップ領域3には素子領域4と貫通電極5が設けられ、スクライブ領域2にはアライメントマーク1が設けられている。図1Bは図1Aの貫通電極5近傍のA’−A’方向の断面図、図1Cは図1Aのアライメントマーク1の一部のB’−B’方向の断面図を表す。図1Bに示すように、貫通電極5は表面電極33、配線層14及び裏面電極34から構成される。配線層14及び裏面電極34の一部は、層間絶縁膜16を貫通している。チップ領域3には、貫通電極5を囲むように環状の絶縁リング6が設けられており、貫通電極5をトランジスタ等の他の素子8から絶縁分離している。素子8は、コンタクトプラグ8bを介して配線8aに接続されている。図1Cに示すように、スクライブ領域2には、アライメントマーク1が設けられている。アライメントマーク1の上方の層間絶縁膜16内には配線層15が設けられている。絶縁リング6とアライメントマーク1の、基板厚み方向38における長さは同じとなっている。また、チップ領域3及びスクライブ領域2には、素子分離領域(STI)7が設けられている。

【0017】

図2及び3は、図1の半導体装置の絶縁リング6及びアライメントマーク1の形成工程を表したものであり、説明を簡略化するため、その他の部分については示していない。なお、図2及び3において、A図は図1Bの絶縁リング6の形成工程、B図は図1Cのアライメントマーク1の形成工程、C図はA図の点線で囲まれた部分Pの拡大図、D図はB図の点線で囲まれた部分Qの拡大図を表す。また、図3Eは、第1の主面17aにおけるアライメントマーク1全体の上面図を表す。

【0018】

図2に示すように、シリコン半導体基板17の表面上にフォトレジスト膜20を形成した後、リソグラフィー技術により、フォトレジスト膜20にパターンを形成する。続いて、フォトレジスト膜20をマスクに用いて、半導体基板17のドライエッチングを行う。これにより、環状のトレンチ(絶縁リング用のトレンチ)32と、アライメントマーク用のトレンチ25を同時に形成する。アライメントマーク用のトレンチ25は、第1の主面17aに対向して見た形状が、トレンチ25の幅方向25bに一定のピッチで複数のトレンチ25が配列されたラインアンドスペース(L/S)形状に形成される。

【0019】

図3に示すように、フォトレジスト膜20を除去した後、両トレンチ25、32を同時に絶縁膜26で埋め込む。ここでは、絶縁膜26として、TEOS(Tetra EthOxy Silane;Si(OC2H5)4)を原料に用いたCVD法(化学気相成長法)で形成したNSG(None−doped Silicate Glass)膜を用いる。これにより、絶縁リング6と、アライメントマーク1を形成する。

【0020】

ここで、絶縁リング用トレンチ32と同様に形成したアライメントマーク用トレンチ25は深さが深く(〜40μm)、幅が広い(〜2μm)ため、埋設性が低く、絶縁膜26内にシームやボイド56を生じ得る。特に、複数のトレンチ25がL/S状に配列したアライメントマーク1では、シーム等56はトレンチ25の幅方向25bにおける中央部付近に形成され、トレンチの延在方向50に延在して、トレンチの終端部25aで終了する。このため、シーム等56の終端に当たるトレンチ終端部25aでは応力が集中し、この終端部25aを起点にして半導体基板17にクラック57を生じさせることが、本発明者の検証により分かった。このようなクラック57は素子領域4にまで達することもあり、製造歩留まりの低下の一原因となる。このように、本検討例の製造方法には改善の余地があることが分かった。

【0021】

そこで、本発明者は、上記クラック57の発生を防止する方法を検討した。この結果、トレンチの終端部が存在しないようにアライメントマーク用のトレンチ25を形成すれば、クラック57の発生を防止できることを発見した。すなわち、本発明では、平面視で、終端部が存在しないように半導体基板17の一部を囲む閉じた形状のアライメントマーク用のトレンチ25を形成する。このため、トレンチ25を埋め込んだ絶縁膜26内にシームやボイド56等の埋設不良が発生した場合であっても、トレンチ25の終端部に応力が集中して半導体基板17にクラック57が発生することを低減できる。この結果、製造歩留まりを向上させることができる。

【0022】

以下に、図面を参照して、本発明を説明する。なお、これらの実施例は、本発明のより一層の深い理解のために示される具体例であって、本発明は、これらの具体例に何ら限定されるものではない。

【0023】

(第1実施例)

図4及び5は、第1実施例の製造方法により製造した半導体装置を表す図である。図4Aに示すように、この半導体装置は、半導体基板17上にスクライブ領域(裁断領域)2に囲まれたチップ領域3を有する。チップ領域3には素子領域4と貫通電極5が設けられている。後述するように、この貫通電極5を介して、複数の半導体チップを電気的に接続できるようになっている。また、スクライブ領域2にはアライメントマーク1が設けられている。

【0024】

図4Bは図4Aの貫通電極5近傍のA’−A’方向の断面図、図4Cは図4Aのアライメントマーク1近傍のB’−B’方向の断面図、図4Dは図4BのC’−C’方向での水平断面図、図4Eは図4CのD’−D’方向での水平断面図を表す。

【0025】

図4B、4Dに示すように、貫通電極5は表面電極33、配線層14及び裏面電極34から構成される。配線層14及び裏面電極34の一部は、層間絶縁膜16を貫通している。チップ領域3には、第1の主面17aに対向して見た場合に環状の絶縁リング6が設けられている。絶縁リング6は、第1の主面17aから半導体基板17の厚み方向38に伸長して、第2の主面17bまで半導体基板17内を貫通して設けられている。また、絶縁リング6は、貫通電極5を囲むように設けられており、貫通電極5を他の素子8から絶縁分離している。図4C及び4Eに示すように、スクライブ領域2には、第1の主面17aに対向して見た形状が、環状のアライメントマーク1が設けられている。半導体基板17の厚み方向38において、アライメントマーク1は、絶縁リング6と同じ深さとなっている。また、アライメントマーク1の上方の層間絶縁膜16内には配線層15が設けられている。素子領域4及びスクライブ領域2には、素子分離領域(STI)7が設けられている。

【0026】

図5〜15は、本実施例の半導体装置の製造方法を説明する図である。以下、これらの図面を参照して、本実施例の製造方法を説明する。なお、図5は本実施例の製造方法を表すフローチャートである。図6〜14において、A図は図4Bに対応する断面図、B図は図4Cに対応する断面図、C図はB図を第1の主面17aに対向する方向から見た上面図を表す。なお、図7Cにおいて、トレンチ25はその位置関係が明確となるように透視図として示されている。図15Aは複数の半導体チップを積層した状態を表す断面図、図15Bは図15Aの点線で囲まれた部分51の拡大図を表す。

【0027】

図6に示すように、シリコン半導体基板17の表面上に、フォトレジスト膜20を形成する。リソグラフィー技術により、フォトレジスト膜20内に絶縁リング及びアライメントマーク用のパターンを形成する。このフォトレジスト膜20のパターンを用いて半導体基板17のドライエッチングを行う。これにより、絶縁リング用のトレンチ(第1の溝)32およびアライメントマーク用のトレンチ(第2の溝)25を形成する(図5のS11)。本実施例では、絶縁リング用のトレンチ(第1の溝)32は第1の主面17aに対向して見た形状が環状であり、深さ40μm、幅2μm、リング径20μmとする。絶縁リング用のトレンチ32の寸法は特に限定されないが、例えば、深さ30〜50μm、幅1〜3μm、リング径15〜30μmとすることができる。

【0028】

また、アライメントマーク用のトレンチ25(第2の溝)は、第1の主面17aに対向して見た形状が環状である。アライメントマーク用のトレンチ25は絶縁リング用のトレンチ32と同一工程により形成するので、両者の深さは同一となる(上記の例では、40μm)。また、アライメントマーク用のトレンチ25の幅およびパターン径は、アライメントマークを検出するマークセンサーの検出可能寸法によって決まる。ここでは、アライメントマークがウェハ上で占有する面積を極力小さくするために、マークセンサーの検出可能寸法の下限に近い寸法(幅、パターン径)が望ましい。従って、アライメントマーク用パターンの寸法は、上記の絶縁リング用パターンの寸法と同程度かそれよりも小さく設定される。アライメントマーク用のトレンチ25の溝幅が小さい場合、埋設不良に起因した応力の集中が生じ易い。

【0029】

また、図3Eを用いて説明したように、アライメントマーク1をL/Sの繰り返しパターンで構成した場合、溝幅が絶縁リング6と同程度であっても、応力の集中が生じ易いことが分かっている。例えば、図3Eを用いて説明した形状のアライメントマーク1では、L/Sの幅(幅方向25bの長さ)が約2μm(ピッチ約4μm)、ライン長(延在方向50の長さ)が約35〜45μm、ライン数18本としたときに、絶縁膜26の埋設後の工程において応力集中に起因したクラック57が発生することが分かっている(トレンチ25の深さは絶縁リング6と同じ約40μm)。

【0030】

図7に示すように、フォトレジスト膜20を除去する。TEOS(Tetra EthOxy Silane;Si(OC2H5)4)を原料に用いたCVD法により、半導体基板17上にNSG(None−doped Silicate Glass)膜26を形成する(以下、この膜26をTEOS−NSG膜と呼ぶ)。このような堆積法によって形成するTEOS−NSG膜26の膜厚(半導体基板17上の膜厚)は、トレンチ25、32を完全に埋設するという観点からトレンチ25、32の幅の1/2以上の膜厚である。また、TEOS−NSG膜26を用いたのは、高アスペクト比のトレンチ25、32を埋設する際に、極力ボイドが発生しないようにするために、カバレッジ性が良好でコンフォーマルに形成できるからである。同様の効果を奏する場合、絶縁膜26として他の材料を用いても良い。

【0031】

図8に示すように、後の研磨工程で、半導体基板17上のTEOS−NSG膜26を除去する際のCMP負荷を減らすため、ウェットエッチングによりTEOS−NSG膜26の膜厚を低減する。この際、アライメントマーク用のトレンチ25内に形成したTEOS−NSG膜26内にはシームが発生する場合がある。この場合にそのままTEOS−NSG膜26をウェットエッチングするとTEOS−NSG膜26内のシームが深化してしまう。そのため、アライメントマーク用のトレンチ25上のTEOS−NSG膜26はフォトレジスト膜20などの保護膜で保護した状態でウェットエッチングを行う。

【0032】

上記図2及び3で検討したように、アライメントマーク用トレンチ25内に絶縁膜26を埋設させると、その内部にシームやボイド56を生じ得る。特に、複数のトレンチをラインアンドスペース状に配列したアライメントマーク用のトレンチ25を形成すると、シームやボイド56はトレンチの幅方向25bにおける中央部付近に形成され、平面視した場合のトレンチの延在方向50と同じ方向に延在する。このシーム等56は、トレンチの延在方向50の終端部25aで終了するため、トレンチ終端部25aに応力が集中し易くなる。この結果、上記検討した構造では、図7のTEOS−NSG膜26の成膜時や図8のウェットエッチング時に、この終端部25aを起点にして半導体基板17にクラック57を生じさせることとなる。このようなクラック57が素子領域4にまで達すると、製造歩留まりの低下の一原因となる。

【0033】

これに対して、本実施例では、アライメントマーク用のトレンチ25を、平面視で終端部が存在しないように、半導体基板17の一部を囲む閉じた形状として形成する。アライメントマーク用のトレンチ25内に埋設したTEOS−NSG膜26内にシームやボイドの埋設不良が発生した場合であっても、シーム等はトレンチの幅方向25bにおける中央部付近に形成される。このため、平面視した場合に、シーム等は終端部が存在しない閉じた形状となるように形成される。従って、上記ラインアンドスペース状のトレンチを形成して図7のTEOS−NSG膜26の成膜や図8のウェットエッチングを行った場合のように、シーム等の終端部であるトレンチ終端部25aに応力が集中すること、を防止できる。この結果、トレンチ終端部25aを起点とするクラック57の発生を低減して、製造歩留まりを向上させることができる。

【0034】

図9に示すように、フォトレジスト膜20を除去した後、950℃で60分間、熱処理を行い、TEOS−NSG膜26の脱ガス処理を行う。次に、化学機械研磨法(CMP法)により、半導体基板17の第1の主面17a上のTEOS−NSG膜26を除去することで、絶縁リング6及びアライメントマーク1を完成させる(図5のS12)。

【0035】

図10に示すように、半導体基板17上にフォトレジスト膜20を形成する。リソグラフィー技術により、STI用のフィールドパターンを、フォトレジスト膜20に転写して第1のパターン29を形成する。この際、本実施例では、上記のようにして形成したアライメントマーク1を、STI用のフィールドパターンの位置合わせマークとして用いることができる。即ち、上記アライメントマーク1の半導体基板17上での位置を基準として位置合わせしたフィールドパターンをフォトレジスト膜20に転写することで、フォトリソグラフィの位置合わせのずれを低減できる。

【0036】

フォトレジスト膜20の第1のパターン29を用いて、半導体基板17をエッチングする。これにより、図11に示すように、STI用のトレンチ7aを形成する(図5のS21)。この後、フォトレジスト膜20を除去する。半導体基板17上に酸化シリコン膜、窒化シリコン膜等の絶縁膜を埋設させた後、絶縁膜に対してCMP処理を施す。これにより、STI(素子分離領域)7を形成する(図5のS22)。

【0037】

図12に示すように、半導体基板17の活性領域30に、トランジスタ等の素子8を形成する(図5のS23)。半導体基板17上に数段階に分けて層間絶縁膜16を形成する。層間絶縁膜16を形成する途中の工程で、トランジスタ8の不純物拡散層に到達するコンタクトプラグ8b、配線8a、絶縁リング6で囲まれた半導体基板17内の領域の上方に配線層14、アライメントマーク1近傍に配線層15を形成する。配線層14は、後の工程で形成する表面電極33、裏面電極34と接続するためのパッドとして機能する。配線層14は、アルミニウム(Al)や銅(Cu)等からなる複数の配線14a〜14dと、複数の配線間を接続するタングステン等の金属膜からなる複数のコンタクトプラグ14e〜14gとからなる。また、配線層15は、複数の配線15a〜15dと、複数の配線間を接続する複数のコンタクトプラグ15e〜15gとからなる。

【0038】

図13に示すように、配線層14を覆うように層間絶縁膜16上に、シリコン酸窒化膜(SiON)36aと、ポリイミド膜(パッシべーション膜)36bからなる保護膜36を形成する。次に、配線層14の上面を露出させるように保護膜36内に第1の開口33aを形成する。スパッタにより、第1の開口33aを含む保護膜36上にシード膜11を形成する。保護膜36上にフォトレジスト膜(図示していない)を形成した後、パターニングを行って、第1の開口33a内に設けたシード膜11を露出させる。電界メッキ法により、露出したシード膜11上に順に銅バンプ13、及び半田膜12を形成する。保護膜36上のフォトレジスト膜を除去した後、露出したシード膜11を除去する。このシード膜11、銅バンプ13、及び半田膜12から表面電極33が構成される(図5のS3)。

【0039】

図14に示すように、半導体基板17の表面電極33を設けた側に、接着層(図示していない)を介して支持基板(図示していない)を設ける。この後、半導体基板17の第1の主面17aと厚さ方向に対向する第2の主面17bを例えば、775μmから40〜50μmの厚さまで薄膜化する(図5のS4)。この研削工程により、半導体基板17の第2の主面17b側には、予め形成した絶縁リング6及びアライメントマーク1の底部が露出する。半導体基板17の第2の主面17b側から、配線層14が露出するように、環状の絶縁リング6の内側に位置する半導体基板17に対して異方性ドライエッチングを行う。この際、半導体基板17を貫通すると共に、層間絶縁膜16の一部内に伸長する第2の開口34aを形成する。次に、スパッタ法により、半導体基板17の第2の主面17b上の全面に、チタン(Ti)膜及び銅(Cu)膜を積層させて、シード膜10を形成する。半導体基板17の第2の主面17b上に、第2の開口34aと同じ位置に第3の開口を有するフォトレジストパターン(図示していない)を形成する。電気めっき法により、第3の開口内に順に銅バンプ19、及びSnAg膜等の半田膜9を形成する。このシード膜10、銅バンプ19、及び半田膜9の3層により、裏面電極34が形成される。次に、フォトレジストパターンを除去した後、露出したシード膜10の部分を除去する(図5のS5)。

【0040】

この後、リフローにより、半田膜9の表面を凸状とする。接着層及び支持基板を除去する。以上のようにして、図4に示す半導体装置を得る。この半導体装置では、スクライブ領域2で区画された各チップ領域3に、半導体基板17を貫通するように貫通電極5が設けられている。貫通電極5は、上端および下端に接続用のバンプ(表面電極33、裏面電極34)を備えており、後述するように、複数の半導体チップを積層する際に貫通電極5を介して上下に配置された半導体チップ間が電気的に接続される。貫通電極5は、半導体基板17を貫通する貫通プラグ(表面電極33、裏面電極34)と、半導体基板17上の複数の層間絶縁膜16を貫通する配線層14で構成されている。貫通電極5の半導体基板17を貫通する部分は、環状の絶縁リング6で囲まれており、他の素子8等とは絶縁分離されている。

【0041】

次に、スクライブ領域(裁断領域)2に沿って半導体基板17のスクライブを行う(図5のS6)。これにより、半導体基板17を個片化して半導体チップを形成する。

【0042】

図15に示すように、異なる半導体チップ40の表面電極33と裏面電極34が互いに接するようにして、複数の半導体チップ40をマウントする。リフローにより、各半導体チップ40の表面電極33と裏面電極34の半田膜9、12を接合する。半導体チップ40間にアンダーフィル41を充填した後、複数の半導体チップ40を、パッケージ基板42上にマウントする。この後、モールドレジン43によってモールドすることにより、本実施例の半導体装置が完成する(図5のS7)。

【0043】

本実施例の半導体装置としては、例えば、DRAM、SRAM、フラッシュメモリ等の記憶デバイスや、MPU、DSP等の演算処理デバイスを挙げることができる。

【0044】

以上のように、本実施例では、図7の工程で、アライメントマーク用のトレンチ25内に埋設させたTEOS−NSG膜26内にシームやボイドが生じ得る。しかし、このような場合であっても、アライメントマーク用のトレンチ25は半導体基板17の第1の主面17aに対向して見た場合に、半導体基板17の一部を囲む環状に形成され、終端部が存在しない。シームやボイドはトレンチの幅方向25bにおける中央部付近に形成されるため、トレンチ25の形状と同様に、シームやボイドも平面視した場合に半導体基板17の一部の領域を囲むように閉じた形状に形成され、終端部が存在しない。一般的に、シーム等はその終端部に応力が集中するため、上記のようにシーム等の終端部を無くすことによって、シーム等終端部への応力集中を防止することができる。この結果、図7のTEOS−NSG膜26の成膜時や図8のウェットエッチング時などに、このシーム等の終端部を起点とした半導体基板17のクラック発生を低減して、製造歩留まりを向上させることができる。

【0045】

なお、本実施例では、環状のアライメントマーク用のトレンチ25を形成したが、アライメントマーク用のトレンチ25は環状に限定されない。すなわち、アライメントマーク用のトレンチ(第2の溝)25は、半導体基板17の第1の主面17aに対向する方向から見た場合に(平面視で)、半導体基板17の一部を囲む閉じた形状となっていれば、その形状は特に限定されない。このような形状では、アライメントマーク用のトレンチ(第2の溝)に終端部が存在しないため、上記と同様に、半導体基板17に終端部を起点としたクラックが発生することを低減することができる。また、アライメントマーク用のトレンチ(第2の溝)25の形状は終端部が存在せず実用上、STI7の位置合わせ時にフィールド合わせマークとして使用可能な形状であれば特に限定されず、平面視において直線、曲線で構成される形状とすることができる。本実施例では、スクライブ領域2上の1箇所につき1つのアライメントマーク1を形成したが、アライメントマーク1を形成する位置及び数は、適宜、変更することが可能である。

【0046】

本実施例では、アライメントマーク1はSTI7の位置合わせ時にフィールド合わせマークとして使用した。アライメントマーク1は、STI7の位置合わせに加えて他の構造の位置合わせ用のフィールド合わせマークとして使用することも可能である。例えば、図14の工程において、第2の開口34aを形成する際の位置合わせ用のフィールド合わせマークとして使用することができる。

【0047】

また、本実施例では、絶縁リング用のトレンチ32及びアライメントマーク用のトレンチ25を埋設する絶縁膜として、TEOS−NSG膜26を例示したが、トレンチ25、32を埋設する材料はこれに限定されない。アライメントマーク1のように深く、幅広いトレンチ25を絶縁膜で埋設する場合、TEOS−NSG膜でなくとも埋設不良によりシームやボイドを生じ易い。従って、本発明は、TEOS−NSG膜26に限定されず、他の絶縁膜でトレンチ25を埋め込む工程に適用して同様に効果的である。一方、TEOS−NSG膜26を用いた場合、焼き締め(Degas)のための熱処理が必要となる。TEOS−NSG膜26はこの熱処理により膜収縮を起こし、シームが拡大することがある。従って、TEOS−NSG膜26によってトレンチ25を埋め込む工程に対しては、本願発明を適用してより効果的であると言える。

【0048】

(第1変形例)

上記第1実施例では、平面視において、スクライブ領域2上の1箇所につき真円状のアライメントマーク1を1つ形成したが、本変形例は1箇所につき、平面視形状が真円とは異なる円状の複数のアライメントマーク1を設ける点が異なる。図16は、本変形例で形成したアライメントマーク1を示す図であり、図16A及びBはそれぞれ、第1実施例の図4C及び4Eに相当する断面図である。図16に示すように、本変形例では、平面視で複数の円状のアライメントマーク1が設けられている。このように、アライメントマーク1が平面視で図16Bのような円状であっても、アライメントマーク1の終端部が存在しないため、第1実施例と同様に、終端部を起点とするクラックの発生を防止することができる。

【0049】

なお、本変形例のアライメントマーク1は、平面視形状や数以外は第1実施例のアライメントマーク1と同じである。このため、第1実施例の図6の工程において、本変形例のアライメントマーク1の数及び形状となるように、アライメントマーク用のトレンチ25を形成する以外は、第1実施例と同様の工程により、半導体装置を形成することができる。

【0050】

また、アライメントマーク1の形状は、平面視した場合に終端部が存在しない閉じた形状であれば、第1実施例及び第1変形例で示した形状に限定されない。アライメントマーク1の形状としては例えば平面視で、矩形、正方形、直線、曲線を含む形状等の閉じた形状とすることができる。

【0051】

(第2変形例)

上記第1実施例では、TEOS−NSG膜26の1層からなるアライメントマーク1を形成したが、本変形例は窒化シリコン膜26a及びTEOS−NSG膜26bの2層からなるアライメントマーク1及び絶縁リング6を形成する点が異なる。以下、第1実施例と異なる工程を中心に、本変形例の製造工程を説明する。

【0052】

まず、第1実施例の図6の工程を実施する。第1実施例の図7の工程の代わりに、絶縁リング用のトレンチ32及びアライメントマーク用のトレンチ25を埋め込むように、半導体基板17上の全面に薄い窒化シリコン膜26a及びTEOS−NSG膜26bを形成する。

【0053】

次に、第1実施例の図8の工程と同様に、絶縁リング用のトレンチ32及びアライメントマーク用のトレンチ25上にフォトレジスト膜20を形成した後、フォトレジスト膜20をマスクに用いて窒化シリコン膜26a及びTEOS−NSG膜26bのウェットエッチングを行う。

【0054】

図17に示すように、半導体基板17上の窒化シリコン膜26aをストッパに用いてTEOS−NSG膜26bに対してCMP処理を行う。なお、図17A、17B及び17Cはそれぞれ、第1実施例の図9A、9B及び9Cに相当する断面を表す。

【0055】

これ以降は、第1実施例の図10〜15の工程を実施する。なお、図10以降の工程において、必要な場合は、半導体基板17の第1の主面17a上の窒化シリコン膜26aの一部又は全部を除去しても良い。

【0056】

(第3変形例)

上記第1実施例では、半導体基板17のスクライブ領域2にアライメントマーク1を形成したが、本変形例は半導体基板17のスクライブ領域2以外の領域にアライメントマーク1を形成する点が異なる。

【0057】

図18Aは、半導体基板17の非有効ショット領域45にアライメントマーク1を設けた例を表す平面図である。半導体基板17には、後の工程でリソグラフィーの露光等を行うことにより半導体装置が形成される半導体チップからなる複数の有効ショット領域(図18Aにおいて斜線で表示された領域)46と、半導体装置が形成されない非有効ショット領域(図18Aにおいて白色の領域)45が存在する。非有効ショット領域45とは、正常な半導体装置のパターン形成ができない半導体チップが位置する領域を指す。すなわち、半導体基板17は円形で構成され、半導体チップは矩形で構成されるため半導体基板17の終端部に掛かった半導体チップでは、一部が半導体基板17からはみ出してしまい、パターン形成ができない状態となる。半導体装置の設計が完了した時点で半導体チップのサイズが決まるので、半導体基板17において非有効ショット領域45となる位置は予め把握することができる。半導体基板17の終端部にパターン形成を繰り返すと、異物発生の原因となるので、非有効ショット領域45にはパターンを形成しない。したがって、非有効ショット領域45は半導体装置の製造に寄与しない無駄な領域となる。本変形例では、上記の無駄な領域となる非有効ショット領域45を利用してアライメントマーク1を形成することにより、有効ショット領域46内にアライメントマーク1用の領域を確保する必要がなくなり、微細化に対応した半導体装置とすることができる。なお、アライメントマーク1を形成する非有効ショット領域45の数及び位置は図18Aの例に限定されず、適宜、所望の数及び位置の非有効ショット領域45にアライメントマーク1を形成することができる。

【0058】

図18Bは、他の例を示す図であり、半導体基板17のチップ領域3内にアライメントマーク1を形成する例を示した図であり、第1実施例の図4Aに対応する図面である。図18Bに示すように、アライメントマーク1はチップ領域3内に形成しても良い。また、チップ領域3内のアライメントマーク1の形成位置及び数は、図18Bの例に限定されるわけではなく、所望の数のアライメントマーク1を、チップ領域3内の所望の位置に形成することができる。

【符号の説明】

【0059】

1 アライメントマーク

2 スクライブ領域

3 チップ領域

4 素子領域

5 貫通電極

6 絶縁リング

7 素子分離領域(STI)

7a 素子分離領域用のトレンチ

8 素子

8a 配線層

8b コンタクトプラグ

9、12 半田膜

10、11 シード膜

13、19 銅バンプ

14、15 配線層

14a〜14d、15a〜15d 配線

14e〜14g、15e〜15g コンタクトプラグ

16 層間絶縁膜

17 半導体基板

17a 第1の主面

17b 第2の主面

20 フォトレジスト膜

25 アライメントマーク用のトレンチ

25a トレンチの終端部

25b アライメントマーク用のトレンチの幅方向

26 絶縁膜

26a 窒化シリコン膜

26b TEOS−NSG膜

29 第1のパターン

30 活性領域

32 絶縁リング用のトレンチ

33 表面電極

33a 第1の開口

34 裏面電極

34a 第2の開口

36 保護膜

36a シリコン酸窒化膜(SiON)

36b ポリイミド膜(パッシべーション膜)

38 半導体基板の厚み方向

40 半導体チップ

41 アンダーフィル

42 パッケージ基板

43 モールドレジン

45 非有効ショット領域

46 有効ショット領域

50 トレンチの延在方向

56 シーム、ボイド

57 クラック

【技術分野】

【0001】

本発明は、半導体ウェハ、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

複数の半導体チップを積層して高機能を実現した半導体装置では、半導体チップを貫通するようにして設けられた貫通電極(Through Silicon Via、以下、TSVと記載する場合がある)によって、上下の半導体チップを電気的に接続する構造が用いられる。このような半導体チップでは、TSVと素子領域とを絶縁分離することや、近隣のTSV間容量を低減することを目的として、TSVの周囲を絶縁体で囲んだ絶縁リング構造が用いられることがある。

【0003】

特許文献1(特開2009−111061号公報)には、絶縁リングを備えた貫通電極を有する半導体装置の製造方法が開示されている。ここには、最初に絶縁リングを形成し(ビアファースト)、素子形成〜配線形成を経て、最後にTSVを形成する(ビアラスト)工程が開示されている。より詳しくは、まず、シリコン基板の素子形成面側から深さ方向にリング状のトレンチを掘り、このトレンチを絶縁膜で埋め込むことで絶縁リングを形成する。その後、基板表面への素子形成、配線層形成および表面電極形成工程などを経た後、シリコン基板を裏面側から研削して薄板化する。このとき絶縁リングの底部が基板裏面から露出するまで裏面研削することで、絶縁リングがシリコン基板を表面から裏面まで貫通した構造となる。そして、絶縁リングの内側に、シリコン基板を貫通するように、裏面側から裏面電極を形成することによりTSVを形成する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009−111061号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記の方法とは異なり、絶縁リング等をビアファーストで形成せず、素子分離領域(フィールド)を形成する工程が基板に施す最初の工程であれば、当該素子分離領域の基板上での位置を調整する必要は無い。すなわち、素子分離領域の形成時には、基板上に他の部材が形成されていないため、これらの部材に対して素子分離領域の位置合わせを行う必要が無い。

【0006】

一方、上記のように、ビアファーストで既に絶縁リングが形成された基板上に素子分離領域を形成する場合、当該素子分離領域は基板上での位置を調整して(位置合わせして)形成する必要がある。即ち、絶縁リング形成の後、基板に対して素子分離領域用のパターニングをする前に、フォトリソグラフィに用いるアライメントマークを形成しておく必要がある。

【0007】

しかしながら、従来の方法では、アライメントマーク用のトレンチが深く、その幅が狭いため、トレンチ内に絶縁膜を埋設させると内部にシームやボイドが発生する場合があった。アライメントマーク用のトレンチはラインアンドスペース形状で形成するため、シームやボイドなどの埋設不良箇所に応力が集中して、この部分を起点に基板内にクラックが発生する場合があった。このクラックは素子領域にまで達することがあり、この場合、製造歩留まりが低下することとなっていた。

【課題を解決するための手段】

【0008】

一実施形態は、

基板の第1の主面に、前記第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する工程と、

前記第1及び第2の溝を埋め込むように、絶縁膜を形成する工程と、

前記絶縁膜を形成する工程の後、前記基板の第1の主面にフォトレジスト膜を形成する工程と、

前記絶縁膜で埋め込まれた前記第2の溝の前記基板上での位置を基準として位置合わせした第1のパターンを、前記フォトレジスト膜に転写する工程と、

前記絶縁膜で埋め込まれた環状の前記第1の溝の内側に位置する前記基板に、前記基板を厚さ方向に貫通する貫通電極を形成する工程と、

を有することを特徴とする半導体装置の製造方法に関する。

【0009】

他の実施形態は、

基板と、

前記基板を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が環状となる絶縁リングと、

前記基板を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が終端部を有さない形状となるアライメントマークと、

前記環状の絶縁リングの内側に位置する前記基板内に、前記基板を厚さ方向に貫通するように設けられた貫通電極と、

を有することを特徴とする半導体ウェハに関する。

【0010】

他の実施形態は、

基板と、

前記基板のチップ領域を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が環状となる絶縁リングと、

前記基板のチップ領域を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が終端部を有さない形状となるアライメントマークと、

前記環状の絶縁リングの内側に位置する前記チップ領域内に、前記基板を厚さ方向に貫通するように設けられた貫通電極と、

を有することを特徴とする半導体装置に関する。

【発明の効果】

【0011】

終端部を含まない形状のアライメントマークを形成する。これにより、アライメントマーク終端部への応力集中によって基板にクラックが発生することを軽減できる。

【図面の簡単な説明】

【0012】

【図1】本発明者が検討した方法を表す図である。

【図2】本発明者が検討した方法を表す図である。

【図3】本発明者が検討した方法を表す図である。

【図4】第1実施例の半導体装置を表す図である。

【図5】第1実施例の半導体装置の製造方法を表すフローチャートである。

【図6】第1実施例の半導体装置の製造方法を表す図である。

【図7】第1実施例の半導体装置の製造方法を表す図である。

【図8】第1実施例の半導体装置の製造方法を表す図である。

【図9】第1実施例の半導体装置の製造方法を表す図である。

【図10】第1実施例の半導体装置の製造方法を表す図である。

【図11】第1実施例の半導体装置の製造方法を表す図である。

【図12】第1実施例の半導体装置の製造方法を表す図である。

【図13】第1実施例の半導体装置の製造方法を表す図である。

【図14】第1実施例の半導体装置の製造方法を表す図である。

【図15】第1実施例の半導体装置の製造方法を表す図である。

【図16】第1実施例の第1変形例を表す図である。

【図17】第1実施例の第2変形例を表す図である。

【図18】第1実施例の第3変形例を表す図である。

【発明を実施するための形態】

【0013】

特開2005−217071号公報には、チップ積層時の位置合わせ基準となるアライメントマークを、TSV本体を形成する工程によって同時に形成する方法が開示されている。より詳しくは、ウェハから切り出した複数のチップを互いに積層する際、位置合わせのずれを起こさないよう、ボンディング装置にチップの位置を認識させるためのアライメントマークとして、TSVと同様の基板を貫通する導電材料を用いて構成し、TSV形成工程時に同時に形成するという技術である。

【0014】

そこで、本発明者は、上記技術の応用例として、素子形成工程の最初の工程であるSTI(フィールド)パターンを転写する工程(フォトリソグラフィ工程)の際に、位置合わせの基準となるアライメントマークを、絶縁リングと同時に形成する方法について、事前に検討した。通常、半導体装置の構成要素が何も形成されていないウェハ上に最初にSTIを形成する場合、いかなる要素に対しても位置合わせをする必要が無いので、STI形成工程においてアライメントマークは必要無い。また、STI形成工程の後の工程においては、STI形成工程で同時に形成したアライメントマークを基準に位置合わせすれば良い。

【0015】

一方、本願で対象にする構造は、TSVの周囲を囲む絶縁リングを最初に形成した後(ビアファースト)、素子形成工程に入る。従って、この絶縁リングに対してSTIを位置合わせするためのアライメントマーク(フィールド合わせマーク)が必要となり、これを形成する方法として上述の技術を検討した。本発明者が検討したフィールド合わせマークは、リソグラフィ工程の際に認識できるよう、絶縁溝がラインアンドスペース(L/S)状に配列した形状である。

【0016】

以下では、図1〜3を参照して、本発明者が検討した半導体装置及びその製造方法を説明する。なお、各図において適宜、一部の構造を省略し、重要な構造のみを示す。図1Aに示すように、この半導体装置は、半導体基板17上にスクライブ領域2に囲まれたチップ領域3を有する。チップ領域3には素子領域4と貫通電極5が設けられ、スクライブ領域2にはアライメントマーク1が設けられている。図1Bは図1Aの貫通電極5近傍のA’−A’方向の断面図、図1Cは図1Aのアライメントマーク1の一部のB’−B’方向の断面図を表す。図1Bに示すように、貫通電極5は表面電極33、配線層14及び裏面電極34から構成される。配線層14及び裏面電極34の一部は、層間絶縁膜16を貫通している。チップ領域3には、貫通電極5を囲むように環状の絶縁リング6が設けられており、貫通電極5をトランジスタ等の他の素子8から絶縁分離している。素子8は、コンタクトプラグ8bを介して配線8aに接続されている。図1Cに示すように、スクライブ領域2には、アライメントマーク1が設けられている。アライメントマーク1の上方の層間絶縁膜16内には配線層15が設けられている。絶縁リング6とアライメントマーク1の、基板厚み方向38における長さは同じとなっている。また、チップ領域3及びスクライブ領域2には、素子分離領域(STI)7が設けられている。

【0017】

図2及び3は、図1の半導体装置の絶縁リング6及びアライメントマーク1の形成工程を表したものであり、説明を簡略化するため、その他の部分については示していない。なお、図2及び3において、A図は図1Bの絶縁リング6の形成工程、B図は図1Cのアライメントマーク1の形成工程、C図はA図の点線で囲まれた部分Pの拡大図、D図はB図の点線で囲まれた部分Qの拡大図を表す。また、図3Eは、第1の主面17aにおけるアライメントマーク1全体の上面図を表す。

【0018】

図2に示すように、シリコン半導体基板17の表面上にフォトレジスト膜20を形成した後、リソグラフィー技術により、フォトレジスト膜20にパターンを形成する。続いて、フォトレジスト膜20をマスクに用いて、半導体基板17のドライエッチングを行う。これにより、環状のトレンチ(絶縁リング用のトレンチ)32と、アライメントマーク用のトレンチ25を同時に形成する。アライメントマーク用のトレンチ25は、第1の主面17aに対向して見た形状が、トレンチ25の幅方向25bに一定のピッチで複数のトレンチ25が配列されたラインアンドスペース(L/S)形状に形成される。

【0019】

図3に示すように、フォトレジスト膜20を除去した後、両トレンチ25、32を同時に絶縁膜26で埋め込む。ここでは、絶縁膜26として、TEOS(Tetra EthOxy Silane;Si(OC2H5)4)を原料に用いたCVD法(化学気相成長法)で形成したNSG(None−doped Silicate Glass)膜を用いる。これにより、絶縁リング6と、アライメントマーク1を形成する。

【0020】

ここで、絶縁リング用トレンチ32と同様に形成したアライメントマーク用トレンチ25は深さが深く(〜40μm)、幅が広い(〜2μm)ため、埋設性が低く、絶縁膜26内にシームやボイド56を生じ得る。特に、複数のトレンチ25がL/S状に配列したアライメントマーク1では、シーム等56はトレンチ25の幅方向25bにおける中央部付近に形成され、トレンチの延在方向50に延在して、トレンチの終端部25aで終了する。このため、シーム等56の終端に当たるトレンチ終端部25aでは応力が集中し、この終端部25aを起点にして半導体基板17にクラック57を生じさせることが、本発明者の検証により分かった。このようなクラック57は素子領域4にまで達することもあり、製造歩留まりの低下の一原因となる。このように、本検討例の製造方法には改善の余地があることが分かった。

【0021】

そこで、本発明者は、上記クラック57の発生を防止する方法を検討した。この結果、トレンチの終端部が存在しないようにアライメントマーク用のトレンチ25を形成すれば、クラック57の発生を防止できることを発見した。すなわち、本発明では、平面視で、終端部が存在しないように半導体基板17の一部を囲む閉じた形状のアライメントマーク用のトレンチ25を形成する。このため、トレンチ25を埋め込んだ絶縁膜26内にシームやボイド56等の埋設不良が発生した場合であっても、トレンチ25の終端部に応力が集中して半導体基板17にクラック57が発生することを低減できる。この結果、製造歩留まりを向上させることができる。

【0022】

以下に、図面を参照して、本発明を説明する。なお、これらの実施例は、本発明のより一層の深い理解のために示される具体例であって、本発明は、これらの具体例に何ら限定されるものではない。

【0023】

(第1実施例)

図4及び5は、第1実施例の製造方法により製造した半導体装置を表す図である。図4Aに示すように、この半導体装置は、半導体基板17上にスクライブ領域(裁断領域)2に囲まれたチップ領域3を有する。チップ領域3には素子領域4と貫通電極5が設けられている。後述するように、この貫通電極5を介して、複数の半導体チップを電気的に接続できるようになっている。また、スクライブ領域2にはアライメントマーク1が設けられている。

【0024】

図4Bは図4Aの貫通電極5近傍のA’−A’方向の断面図、図4Cは図4Aのアライメントマーク1近傍のB’−B’方向の断面図、図4Dは図4BのC’−C’方向での水平断面図、図4Eは図4CのD’−D’方向での水平断面図を表す。

【0025】

図4B、4Dに示すように、貫通電極5は表面電極33、配線層14及び裏面電極34から構成される。配線層14及び裏面電極34の一部は、層間絶縁膜16を貫通している。チップ領域3には、第1の主面17aに対向して見た場合に環状の絶縁リング6が設けられている。絶縁リング6は、第1の主面17aから半導体基板17の厚み方向38に伸長して、第2の主面17bまで半導体基板17内を貫通して設けられている。また、絶縁リング6は、貫通電極5を囲むように設けられており、貫通電極5を他の素子8から絶縁分離している。図4C及び4Eに示すように、スクライブ領域2には、第1の主面17aに対向して見た形状が、環状のアライメントマーク1が設けられている。半導体基板17の厚み方向38において、アライメントマーク1は、絶縁リング6と同じ深さとなっている。また、アライメントマーク1の上方の層間絶縁膜16内には配線層15が設けられている。素子領域4及びスクライブ領域2には、素子分離領域(STI)7が設けられている。

【0026】

図5〜15は、本実施例の半導体装置の製造方法を説明する図である。以下、これらの図面を参照して、本実施例の製造方法を説明する。なお、図5は本実施例の製造方法を表すフローチャートである。図6〜14において、A図は図4Bに対応する断面図、B図は図4Cに対応する断面図、C図はB図を第1の主面17aに対向する方向から見た上面図を表す。なお、図7Cにおいて、トレンチ25はその位置関係が明確となるように透視図として示されている。図15Aは複数の半導体チップを積層した状態を表す断面図、図15Bは図15Aの点線で囲まれた部分51の拡大図を表す。

【0027】

図6に示すように、シリコン半導体基板17の表面上に、フォトレジスト膜20を形成する。リソグラフィー技術により、フォトレジスト膜20内に絶縁リング及びアライメントマーク用のパターンを形成する。このフォトレジスト膜20のパターンを用いて半導体基板17のドライエッチングを行う。これにより、絶縁リング用のトレンチ(第1の溝)32およびアライメントマーク用のトレンチ(第2の溝)25を形成する(図5のS11)。本実施例では、絶縁リング用のトレンチ(第1の溝)32は第1の主面17aに対向して見た形状が環状であり、深さ40μm、幅2μm、リング径20μmとする。絶縁リング用のトレンチ32の寸法は特に限定されないが、例えば、深さ30〜50μm、幅1〜3μm、リング径15〜30μmとすることができる。

【0028】

また、アライメントマーク用のトレンチ25(第2の溝)は、第1の主面17aに対向して見た形状が環状である。アライメントマーク用のトレンチ25は絶縁リング用のトレンチ32と同一工程により形成するので、両者の深さは同一となる(上記の例では、40μm)。また、アライメントマーク用のトレンチ25の幅およびパターン径は、アライメントマークを検出するマークセンサーの検出可能寸法によって決まる。ここでは、アライメントマークがウェハ上で占有する面積を極力小さくするために、マークセンサーの検出可能寸法の下限に近い寸法(幅、パターン径)が望ましい。従って、アライメントマーク用パターンの寸法は、上記の絶縁リング用パターンの寸法と同程度かそれよりも小さく設定される。アライメントマーク用のトレンチ25の溝幅が小さい場合、埋設不良に起因した応力の集中が生じ易い。

【0029】

また、図3Eを用いて説明したように、アライメントマーク1をL/Sの繰り返しパターンで構成した場合、溝幅が絶縁リング6と同程度であっても、応力の集中が生じ易いことが分かっている。例えば、図3Eを用いて説明した形状のアライメントマーク1では、L/Sの幅(幅方向25bの長さ)が約2μm(ピッチ約4μm)、ライン長(延在方向50の長さ)が約35〜45μm、ライン数18本としたときに、絶縁膜26の埋設後の工程において応力集中に起因したクラック57が発生することが分かっている(トレンチ25の深さは絶縁リング6と同じ約40μm)。

【0030】

図7に示すように、フォトレジスト膜20を除去する。TEOS(Tetra EthOxy Silane;Si(OC2H5)4)を原料に用いたCVD法により、半導体基板17上にNSG(None−doped Silicate Glass)膜26を形成する(以下、この膜26をTEOS−NSG膜と呼ぶ)。このような堆積法によって形成するTEOS−NSG膜26の膜厚(半導体基板17上の膜厚)は、トレンチ25、32を完全に埋設するという観点からトレンチ25、32の幅の1/2以上の膜厚である。また、TEOS−NSG膜26を用いたのは、高アスペクト比のトレンチ25、32を埋設する際に、極力ボイドが発生しないようにするために、カバレッジ性が良好でコンフォーマルに形成できるからである。同様の効果を奏する場合、絶縁膜26として他の材料を用いても良い。

【0031】

図8に示すように、後の研磨工程で、半導体基板17上のTEOS−NSG膜26を除去する際のCMP負荷を減らすため、ウェットエッチングによりTEOS−NSG膜26の膜厚を低減する。この際、アライメントマーク用のトレンチ25内に形成したTEOS−NSG膜26内にはシームが発生する場合がある。この場合にそのままTEOS−NSG膜26をウェットエッチングするとTEOS−NSG膜26内のシームが深化してしまう。そのため、アライメントマーク用のトレンチ25上のTEOS−NSG膜26はフォトレジスト膜20などの保護膜で保護した状態でウェットエッチングを行う。

【0032】

上記図2及び3で検討したように、アライメントマーク用トレンチ25内に絶縁膜26を埋設させると、その内部にシームやボイド56を生じ得る。特に、複数のトレンチをラインアンドスペース状に配列したアライメントマーク用のトレンチ25を形成すると、シームやボイド56はトレンチの幅方向25bにおける中央部付近に形成され、平面視した場合のトレンチの延在方向50と同じ方向に延在する。このシーム等56は、トレンチの延在方向50の終端部25aで終了するため、トレンチ終端部25aに応力が集中し易くなる。この結果、上記検討した構造では、図7のTEOS−NSG膜26の成膜時や図8のウェットエッチング時に、この終端部25aを起点にして半導体基板17にクラック57を生じさせることとなる。このようなクラック57が素子領域4にまで達すると、製造歩留まりの低下の一原因となる。

【0033】

これに対して、本実施例では、アライメントマーク用のトレンチ25を、平面視で終端部が存在しないように、半導体基板17の一部を囲む閉じた形状として形成する。アライメントマーク用のトレンチ25内に埋設したTEOS−NSG膜26内にシームやボイドの埋設不良が発生した場合であっても、シーム等はトレンチの幅方向25bにおける中央部付近に形成される。このため、平面視した場合に、シーム等は終端部が存在しない閉じた形状となるように形成される。従って、上記ラインアンドスペース状のトレンチを形成して図7のTEOS−NSG膜26の成膜や図8のウェットエッチングを行った場合のように、シーム等の終端部であるトレンチ終端部25aに応力が集中すること、を防止できる。この結果、トレンチ終端部25aを起点とするクラック57の発生を低減して、製造歩留まりを向上させることができる。

【0034】

図9に示すように、フォトレジスト膜20を除去した後、950℃で60分間、熱処理を行い、TEOS−NSG膜26の脱ガス処理を行う。次に、化学機械研磨法(CMP法)により、半導体基板17の第1の主面17a上のTEOS−NSG膜26を除去することで、絶縁リング6及びアライメントマーク1を完成させる(図5のS12)。

【0035】

図10に示すように、半導体基板17上にフォトレジスト膜20を形成する。リソグラフィー技術により、STI用のフィールドパターンを、フォトレジスト膜20に転写して第1のパターン29を形成する。この際、本実施例では、上記のようにして形成したアライメントマーク1を、STI用のフィールドパターンの位置合わせマークとして用いることができる。即ち、上記アライメントマーク1の半導体基板17上での位置を基準として位置合わせしたフィールドパターンをフォトレジスト膜20に転写することで、フォトリソグラフィの位置合わせのずれを低減できる。

【0036】

フォトレジスト膜20の第1のパターン29を用いて、半導体基板17をエッチングする。これにより、図11に示すように、STI用のトレンチ7aを形成する(図5のS21)。この後、フォトレジスト膜20を除去する。半導体基板17上に酸化シリコン膜、窒化シリコン膜等の絶縁膜を埋設させた後、絶縁膜に対してCMP処理を施す。これにより、STI(素子分離領域)7を形成する(図5のS22)。

【0037】

図12に示すように、半導体基板17の活性領域30に、トランジスタ等の素子8を形成する(図5のS23)。半導体基板17上に数段階に分けて層間絶縁膜16を形成する。層間絶縁膜16を形成する途中の工程で、トランジスタ8の不純物拡散層に到達するコンタクトプラグ8b、配線8a、絶縁リング6で囲まれた半導体基板17内の領域の上方に配線層14、アライメントマーク1近傍に配線層15を形成する。配線層14は、後の工程で形成する表面電極33、裏面電極34と接続するためのパッドとして機能する。配線層14は、アルミニウム(Al)や銅(Cu)等からなる複数の配線14a〜14dと、複数の配線間を接続するタングステン等の金属膜からなる複数のコンタクトプラグ14e〜14gとからなる。また、配線層15は、複数の配線15a〜15dと、複数の配線間を接続する複数のコンタクトプラグ15e〜15gとからなる。

【0038】

図13に示すように、配線層14を覆うように層間絶縁膜16上に、シリコン酸窒化膜(SiON)36aと、ポリイミド膜(パッシべーション膜)36bからなる保護膜36を形成する。次に、配線層14の上面を露出させるように保護膜36内に第1の開口33aを形成する。スパッタにより、第1の開口33aを含む保護膜36上にシード膜11を形成する。保護膜36上にフォトレジスト膜(図示していない)を形成した後、パターニングを行って、第1の開口33a内に設けたシード膜11を露出させる。電界メッキ法により、露出したシード膜11上に順に銅バンプ13、及び半田膜12を形成する。保護膜36上のフォトレジスト膜を除去した後、露出したシード膜11を除去する。このシード膜11、銅バンプ13、及び半田膜12から表面電極33が構成される(図5のS3)。

【0039】

図14に示すように、半導体基板17の表面電極33を設けた側に、接着層(図示していない)を介して支持基板(図示していない)を設ける。この後、半導体基板17の第1の主面17aと厚さ方向に対向する第2の主面17bを例えば、775μmから40〜50μmの厚さまで薄膜化する(図5のS4)。この研削工程により、半導体基板17の第2の主面17b側には、予め形成した絶縁リング6及びアライメントマーク1の底部が露出する。半導体基板17の第2の主面17b側から、配線層14が露出するように、環状の絶縁リング6の内側に位置する半導体基板17に対して異方性ドライエッチングを行う。この際、半導体基板17を貫通すると共に、層間絶縁膜16の一部内に伸長する第2の開口34aを形成する。次に、スパッタ法により、半導体基板17の第2の主面17b上の全面に、チタン(Ti)膜及び銅(Cu)膜を積層させて、シード膜10を形成する。半導体基板17の第2の主面17b上に、第2の開口34aと同じ位置に第3の開口を有するフォトレジストパターン(図示していない)を形成する。電気めっき法により、第3の開口内に順に銅バンプ19、及びSnAg膜等の半田膜9を形成する。このシード膜10、銅バンプ19、及び半田膜9の3層により、裏面電極34が形成される。次に、フォトレジストパターンを除去した後、露出したシード膜10の部分を除去する(図5のS5)。

【0040】

この後、リフローにより、半田膜9の表面を凸状とする。接着層及び支持基板を除去する。以上のようにして、図4に示す半導体装置を得る。この半導体装置では、スクライブ領域2で区画された各チップ領域3に、半導体基板17を貫通するように貫通電極5が設けられている。貫通電極5は、上端および下端に接続用のバンプ(表面電極33、裏面電極34)を備えており、後述するように、複数の半導体チップを積層する際に貫通電極5を介して上下に配置された半導体チップ間が電気的に接続される。貫通電極5は、半導体基板17を貫通する貫通プラグ(表面電極33、裏面電極34)と、半導体基板17上の複数の層間絶縁膜16を貫通する配線層14で構成されている。貫通電極5の半導体基板17を貫通する部分は、環状の絶縁リング6で囲まれており、他の素子8等とは絶縁分離されている。

【0041】

次に、スクライブ領域(裁断領域)2に沿って半導体基板17のスクライブを行う(図5のS6)。これにより、半導体基板17を個片化して半導体チップを形成する。

【0042】

図15に示すように、異なる半導体チップ40の表面電極33と裏面電極34が互いに接するようにして、複数の半導体チップ40をマウントする。リフローにより、各半導体チップ40の表面電極33と裏面電極34の半田膜9、12を接合する。半導体チップ40間にアンダーフィル41を充填した後、複数の半導体チップ40を、パッケージ基板42上にマウントする。この後、モールドレジン43によってモールドすることにより、本実施例の半導体装置が完成する(図5のS7)。

【0043】

本実施例の半導体装置としては、例えば、DRAM、SRAM、フラッシュメモリ等の記憶デバイスや、MPU、DSP等の演算処理デバイスを挙げることができる。

【0044】

以上のように、本実施例では、図7の工程で、アライメントマーク用のトレンチ25内に埋設させたTEOS−NSG膜26内にシームやボイドが生じ得る。しかし、このような場合であっても、アライメントマーク用のトレンチ25は半導体基板17の第1の主面17aに対向して見た場合に、半導体基板17の一部を囲む環状に形成され、終端部が存在しない。シームやボイドはトレンチの幅方向25bにおける中央部付近に形成されるため、トレンチ25の形状と同様に、シームやボイドも平面視した場合に半導体基板17の一部の領域を囲むように閉じた形状に形成され、終端部が存在しない。一般的に、シーム等はその終端部に応力が集中するため、上記のようにシーム等の終端部を無くすことによって、シーム等終端部への応力集中を防止することができる。この結果、図7のTEOS−NSG膜26の成膜時や図8のウェットエッチング時などに、このシーム等の終端部を起点とした半導体基板17のクラック発生を低減して、製造歩留まりを向上させることができる。

【0045】

なお、本実施例では、環状のアライメントマーク用のトレンチ25を形成したが、アライメントマーク用のトレンチ25は環状に限定されない。すなわち、アライメントマーク用のトレンチ(第2の溝)25は、半導体基板17の第1の主面17aに対向する方向から見た場合に(平面視で)、半導体基板17の一部を囲む閉じた形状となっていれば、その形状は特に限定されない。このような形状では、アライメントマーク用のトレンチ(第2の溝)に終端部が存在しないため、上記と同様に、半導体基板17に終端部を起点としたクラックが発生することを低減することができる。また、アライメントマーク用のトレンチ(第2の溝)25の形状は終端部が存在せず実用上、STI7の位置合わせ時にフィールド合わせマークとして使用可能な形状であれば特に限定されず、平面視において直線、曲線で構成される形状とすることができる。本実施例では、スクライブ領域2上の1箇所につき1つのアライメントマーク1を形成したが、アライメントマーク1を形成する位置及び数は、適宜、変更することが可能である。

【0046】

本実施例では、アライメントマーク1はSTI7の位置合わせ時にフィールド合わせマークとして使用した。アライメントマーク1は、STI7の位置合わせに加えて他の構造の位置合わせ用のフィールド合わせマークとして使用することも可能である。例えば、図14の工程において、第2の開口34aを形成する際の位置合わせ用のフィールド合わせマークとして使用することができる。

【0047】

また、本実施例では、絶縁リング用のトレンチ32及びアライメントマーク用のトレンチ25を埋設する絶縁膜として、TEOS−NSG膜26を例示したが、トレンチ25、32を埋設する材料はこれに限定されない。アライメントマーク1のように深く、幅広いトレンチ25を絶縁膜で埋設する場合、TEOS−NSG膜でなくとも埋設不良によりシームやボイドを生じ易い。従って、本発明は、TEOS−NSG膜26に限定されず、他の絶縁膜でトレンチ25を埋め込む工程に適用して同様に効果的である。一方、TEOS−NSG膜26を用いた場合、焼き締め(Degas)のための熱処理が必要となる。TEOS−NSG膜26はこの熱処理により膜収縮を起こし、シームが拡大することがある。従って、TEOS−NSG膜26によってトレンチ25を埋め込む工程に対しては、本願発明を適用してより効果的であると言える。

【0048】

(第1変形例)

上記第1実施例では、平面視において、スクライブ領域2上の1箇所につき真円状のアライメントマーク1を1つ形成したが、本変形例は1箇所につき、平面視形状が真円とは異なる円状の複数のアライメントマーク1を設ける点が異なる。図16は、本変形例で形成したアライメントマーク1を示す図であり、図16A及びBはそれぞれ、第1実施例の図4C及び4Eに相当する断面図である。図16に示すように、本変形例では、平面視で複数の円状のアライメントマーク1が設けられている。このように、アライメントマーク1が平面視で図16Bのような円状であっても、アライメントマーク1の終端部が存在しないため、第1実施例と同様に、終端部を起点とするクラックの発生を防止することができる。

【0049】

なお、本変形例のアライメントマーク1は、平面視形状や数以外は第1実施例のアライメントマーク1と同じである。このため、第1実施例の図6の工程において、本変形例のアライメントマーク1の数及び形状となるように、アライメントマーク用のトレンチ25を形成する以外は、第1実施例と同様の工程により、半導体装置を形成することができる。

【0050】

また、アライメントマーク1の形状は、平面視した場合に終端部が存在しない閉じた形状であれば、第1実施例及び第1変形例で示した形状に限定されない。アライメントマーク1の形状としては例えば平面視で、矩形、正方形、直線、曲線を含む形状等の閉じた形状とすることができる。

【0051】

(第2変形例)

上記第1実施例では、TEOS−NSG膜26の1層からなるアライメントマーク1を形成したが、本変形例は窒化シリコン膜26a及びTEOS−NSG膜26bの2層からなるアライメントマーク1及び絶縁リング6を形成する点が異なる。以下、第1実施例と異なる工程を中心に、本変形例の製造工程を説明する。

【0052】

まず、第1実施例の図6の工程を実施する。第1実施例の図7の工程の代わりに、絶縁リング用のトレンチ32及びアライメントマーク用のトレンチ25を埋め込むように、半導体基板17上の全面に薄い窒化シリコン膜26a及びTEOS−NSG膜26bを形成する。

【0053】

次に、第1実施例の図8の工程と同様に、絶縁リング用のトレンチ32及びアライメントマーク用のトレンチ25上にフォトレジスト膜20を形成した後、フォトレジスト膜20をマスクに用いて窒化シリコン膜26a及びTEOS−NSG膜26bのウェットエッチングを行う。

【0054】

図17に示すように、半導体基板17上の窒化シリコン膜26aをストッパに用いてTEOS−NSG膜26bに対してCMP処理を行う。なお、図17A、17B及び17Cはそれぞれ、第1実施例の図9A、9B及び9Cに相当する断面を表す。

【0055】

これ以降は、第1実施例の図10〜15の工程を実施する。なお、図10以降の工程において、必要な場合は、半導体基板17の第1の主面17a上の窒化シリコン膜26aの一部又は全部を除去しても良い。

【0056】

(第3変形例)

上記第1実施例では、半導体基板17のスクライブ領域2にアライメントマーク1を形成したが、本変形例は半導体基板17のスクライブ領域2以外の領域にアライメントマーク1を形成する点が異なる。

【0057】

図18Aは、半導体基板17の非有効ショット領域45にアライメントマーク1を設けた例を表す平面図である。半導体基板17には、後の工程でリソグラフィーの露光等を行うことにより半導体装置が形成される半導体チップからなる複数の有効ショット領域(図18Aにおいて斜線で表示された領域)46と、半導体装置が形成されない非有効ショット領域(図18Aにおいて白色の領域)45が存在する。非有効ショット領域45とは、正常な半導体装置のパターン形成ができない半導体チップが位置する領域を指す。すなわち、半導体基板17は円形で構成され、半導体チップは矩形で構成されるため半導体基板17の終端部に掛かった半導体チップでは、一部が半導体基板17からはみ出してしまい、パターン形成ができない状態となる。半導体装置の設計が完了した時点で半導体チップのサイズが決まるので、半導体基板17において非有効ショット領域45となる位置は予め把握することができる。半導体基板17の終端部にパターン形成を繰り返すと、異物発生の原因となるので、非有効ショット領域45にはパターンを形成しない。したがって、非有効ショット領域45は半導体装置の製造に寄与しない無駄な領域となる。本変形例では、上記の無駄な領域となる非有効ショット領域45を利用してアライメントマーク1を形成することにより、有効ショット領域46内にアライメントマーク1用の領域を確保する必要がなくなり、微細化に対応した半導体装置とすることができる。なお、アライメントマーク1を形成する非有効ショット領域45の数及び位置は図18Aの例に限定されず、適宜、所望の数及び位置の非有効ショット領域45にアライメントマーク1を形成することができる。

【0058】

図18Bは、他の例を示す図であり、半導体基板17のチップ領域3内にアライメントマーク1を形成する例を示した図であり、第1実施例の図4Aに対応する図面である。図18Bに示すように、アライメントマーク1はチップ領域3内に形成しても良い。また、チップ領域3内のアライメントマーク1の形成位置及び数は、図18Bの例に限定されるわけではなく、所望の数のアライメントマーク1を、チップ領域3内の所望の位置に形成することができる。

【符号の説明】

【0059】

1 アライメントマーク

2 スクライブ領域

3 チップ領域

4 素子領域

5 貫通電極

6 絶縁リング

7 素子分離領域(STI)

7a 素子分離領域用のトレンチ

8 素子

8a 配線層

8b コンタクトプラグ

9、12 半田膜

10、11 シード膜

13、19 銅バンプ

14、15 配線層

14a〜14d、15a〜15d 配線

14e〜14g、15e〜15g コンタクトプラグ

16 層間絶縁膜

17 半導体基板

17a 第1の主面

17b 第2の主面

20 フォトレジスト膜

25 アライメントマーク用のトレンチ

25a トレンチの終端部

25b アライメントマーク用のトレンチの幅方向

26 絶縁膜

26a 窒化シリコン膜

26b TEOS−NSG膜

29 第1のパターン

30 活性領域

32 絶縁リング用のトレンチ

33 表面電極

33a 第1の開口

34 裏面電極

34a 第2の開口

36 保護膜

36a シリコン酸窒化膜(SiON)

36b ポリイミド膜(パッシべーション膜)

38 半導体基板の厚み方向

40 半導体チップ

41 アンダーフィル

42 パッケージ基板

43 モールドレジン

45 非有効ショット領域

46 有効ショット領域

50 トレンチの延在方向

56 シーム、ボイド

57 クラック

【特許請求の範囲】

【請求項1】

基板の第1の主面に、前記第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する工程と、

前記第1及び第2の溝を埋め込むように、絶縁膜を形成する工程と、

前記絶縁膜を形成する工程の後、前記基板の第1の主面にフォトレジスト膜を形成する工程と、

前記絶縁膜で埋め込まれた前記第2の溝の前記基板上での位置を基準として位置合わせした第1のパターンを、前記フォトレジスト膜に転写する工程と、

前記絶縁膜で埋め込まれた環状の前記第1の溝の内側に位置する前記基板に、前記基板を厚さ方向に貫通する貫通電極を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記第2の溝は、前記第1の主面に対向して見た形状が環状、矩形または正方形であることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記絶縁膜を形成する工程の後、前記貫通電極を形成する工程の前に、

前記基板の第1の主面と厚さ方向に対向する第2の主面側から前記基板を研削して、前記絶縁膜で埋め込まれた前記第1及び第2の溝の底部が露出するまで前記基板の厚さを減ずる工程を更に有することを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記絶縁膜を形成する工程では、TEOSを原料に用いた化学気相成長法により、前記第1の溝と前記第2の溝とを埋め込むように前記絶縁膜を形成することを特徴とする請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記絶縁膜を形成する工程は、

前記第1の溝と前記第2の溝の内壁面上に窒化シリコン膜を形成する工程と、

TEOSを原料に用いた化学気相成長法により、前記第1の溝と前記第2の溝とを埋め込むように絶縁膜を形成する工程と、

を有することを特徴とする請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記絶縁膜を形成する工程の後に、

前記第1の溝と前記第2の溝上の前記絶縁膜上にマスクが位置するようにマスクパターンを形成する工程と、

前記マスクパターンを用いたエッチングにより、前記基板の第1の主面が露出しないように前記絶縁膜の一部を除去する工程と、

前記マスクパターンを除去した後、前記絶縁膜を平坦化する工程と、

を更に有することを特徴とする請求項1〜5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記フォトレジスト膜に転写した前記第1のパターンを用いて、前記基板の第1の主面に素子分離領域を形成する工程を更に有することを特徴とする請求項1〜6のいずれか1項に記載の半導体装置の製造方法。

【請求項8】

前記基板を裁断領域に沿って切断することで、前記基板を個片化する工程を更に有し、

前記第1及び第2の溝を形成する工程では、前記基板の前記裁断領域に前記第2の溝を形成することを特徴とする請求項1〜7のいずれか1項に記載の半導体装置の製造方法。

【請求項9】

基板と、

前記基板を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が環状となる絶縁リングと、

前記基板を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が終端部を有さない形状となるアライメントマークと、

前記環状の絶縁リングの内側に位置する前記基板内に、前記基板を厚さ方向に貫通するように設けられた貫通電極と、

を有することを特徴とする半導体ウェハ。

【請求項10】

前記アライメントマークは、前記第1の主面に対向して見た形状が環状、矩形または正方形であることを特徴とする請求項9に記載の半導体ウェハ。

【請求項11】

前記絶縁リングとアライメントマークは、NSG膜(None−doped Silicate Glass)を含む材料からなることを特徴とする請求項9又は10に記載の半導体ウェハ。

【請求項12】

更に、前記基板の第1の主面に素子分離領域を有することを特徴とする請求項9〜11のいずれか1項に記載の半導体ウェハ。

【請求項13】

前記アライメントマークは、前記基板の裁断領域、チップ領域又は非有効ショット領域に形成されていることを特徴とする請求項9〜12のいずれか1項に記載の半導体ウェハ。

【請求項14】

基板と、

前記基板のチップ領域を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が環状となる絶縁リングと、

前記基板のチップ領域を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が終端部を有さない形状となるアライメントマークと、

前記環状の絶縁リングの内側に位置する前記チップ領域内に、前記基板を厚さ方向に貫通するように設けられた貫通電極と、

を有することを特徴とする半導体装置。

【請求項15】

前記アライメントマークは、前記第1の主面に対向して見た形状が環状、矩形または正方形であることを特徴とする請求項14に記載の半導体装置。

【請求項16】

前記絶縁リングとアライメントマークは、NSG膜(None−doped Silicate Glass)を含む材料からなることを特徴とする請求項14又は15に記載の半導体装置。

【請求項17】

更に、前記基板の第1の主面に素子分離領域を有することを特徴とする請求項14〜16のいずれか1項に記載の半導体装置。

【請求項1】

基板の第1の主面に、前記第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する工程と、

前記第1及び第2の溝を埋め込むように、絶縁膜を形成する工程と、

前記絶縁膜を形成する工程の後、前記基板の第1の主面にフォトレジスト膜を形成する工程と、

前記絶縁膜で埋め込まれた前記第2の溝の前記基板上での位置を基準として位置合わせした第1のパターンを、前記フォトレジスト膜に転写する工程と、

前記絶縁膜で埋め込まれた環状の前記第1の溝の内側に位置する前記基板に、前記基板を厚さ方向に貫通する貫通電極を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項2】

前記第2の溝は、前記第1の主面に対向して見た形状が環状、矩形または正方形であることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項3】

前記絶縁膜を形成する工程の後、前記貫通電極を形成する工程の前に、

前記基板の第1の主面と厚さ方向に対向する第2の主面側から前記基板を研削して、前記絶縁膜で埋め込まれた前記第1及び第2の溝の底部が露出するまで前記基板の厚さを減ずる工程を更に有することを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記絶縁膜を形成する工程では、TEOSを原料に用いた化学気相成長法により、前記第1の溝と前記第2の溝とを埋め込むように前記絶縁膜を形成することを特徴とする請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記絶縁膜を形成する工程は、

前記第1の溝と前記第2の溝の内壁面上に窒化シリコン膜を形成する工程と、

TEOSを原料に用いた化学気相成長法により、前記第1の溝と前記第2の溝とを埋め込むように絶縁膜を形成する工程と、

を有することを特徴とする請求項1〜3のいずれか1項に記載の半導体装置の製造方法。

【請求項6】

前記絶縁膜を形成する工程の後に、

前記第1の溝と前記第2の溝上の前記絶縁膜上にマスクが位置するようにマスクパターンを形成する工程と、

前記マスクパターンを用いたエッチングにより、前記基板の第1の主面が露出しないように前記絶縁膜の一部を除去する工程と、

前記マスクパターンを除去した後、前記絶縁膜を平坦化する工程と、

を更に有することを特徴とする請求項1〜5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記フォトレジスト膜に転写した前記第1のパターンを用いて、前記基板の第1の主面に素子分離領域を形成する工程を更に有することを特徴とする請求項1〜6のいずれか1項に記載の半導体装置の製造方法。

【請求項8】

前記基板を裁断領域に沿って切断することで、前記基板を個片化する工程を更に有し、

前記第1及び第2の溝を形成する工程では、前記基板の前記裁断領域に前記第2の溝を形成することを特徴とする請求項1〜7のいずれか1項に記載の半導体装置の製造方法。

【請求項9】

基板と、

前記基板を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が環状となる絶縁リングと、

前記基板を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が終端部を有さない形状となるアライメントマークと、

前記環状の絶縁リングの内側に位置する前記基板内に、前記基板を厚さ方向に貫通するように設けられた貫通電極と、

を有することを特徴とする半導体ウェハ。

【請求項10】

前記アライメントマークは、前記第1の主面に対向して見た形状が環状、矩形または正方形であることを特徴とする請求項9に記載の半導体ウェハ。

【請求項11】

前記絶縁リングとアライメントマークは、NSG膜(None−doped Silicate Glass)を含む材料からなることを特徴とする請求項9又は10に記載の半導体ウェハ。

【請求項12】

更に、前記基板の第1の主面に素子分離領域を有することを特徴とする請求項9〜11のいずれか1項に記載の半導体ウェハ。

【請求項13】

前記アライメントマークは、前記基板の裁断領域、チップ領域又は非有効ショット領域に形成されていることを特徴とする請求項9〜12のいずれか1項に記載の半導体ウェハ。

【請求項14】

基板と、

前記基板のチップ領域を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が環状となる絶縁リングと、

前記基板のチップ領域を厚さ方向に貫通すると共に、前記基板の第1の主面に対向して見た形状が終端部を有さない形状となるアライメントマークと、

前記環状の絶縁リングの内側に位置する前記チップ領域内に、前記基板を厚さ方向に貫通するように設けられた貫通電極と、

を有することを特徴とする半導体装置。

【請求項15】

前記アライメントマークは、前記第1の主面に対向して見た形状が環状、矩形または正方形であることを特徴とする請求項14に記載の半導体装置。

【請求項16】

前記絶縁リングとアライメントマークは、NSG膜(None−doped Silicate Glass)を含む材料からなることを特徴とする請求項14又は15に記載の半導体装置。

【請求項17】

更に、前記基板の第1の主面に素子分離領域を有することを特徴とする請求項14〜16のいずれか1項に記載の半導体装置。

【図2】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図16】

【図18】

【図1】

【図4】

【図13】

【図14】

【図15】

【図17】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図16】

【図18】

【図1】

【図4】

【図13】

【図14】

【図15】

【図17】

【公開番号】特開2013−98308(P2013−98308A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−238940(P2011−238940)

【出願日】平成23年10月31日(2011.10.31)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月31日(2011.10.31)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]