半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に半導体製造に関し、詳しくは、半導体基板上に銅を電気めっきすることにより填込銅相互接続部を形成する方法に関する。

【背景技術】

【0002】

現在、半導体装置は、より高い性能を得るためにより高い電流密度を必要とする。また、装置の寸法は、このようにより高い電流密度を伝える場合にますます問題とされるような幾何学形状にまで小さくなりつつある。当技術においては、より高い電流密度と幾何学形状の縮小とに対応しつつ、同時に、エレクトロマイグレーション(electromigration)に対する充分なレベルの耐性、金属空隙化の軽減、ウェハ製造処理量の改善を維持しながら、なおかつ他の一般的な信頼性の問題を回避しなければならない。アルミニウムは、成熟した集積回路(IC)相互接続材料であるが、銅はIC相互接続部に用いるには比較的新しい材料である。

【0003】

基板上に銅(Cu)を付着する方法で最も有望な方法の一つに、電気めっきなどのめっき法の利用があげられる。電気めっきした銅は、集積回路(IC)用途に利用されるとアルミニウムに比べていくつかの利点を持つ。大きな利点は、銅がアルミニウム系の材料よりも抵抗が低いことで、そのために、より高周波の動作が可能になる。さらに、銅はエレクトロマイグレーション(EM)に関わる従来の問題に対する耐性がアルミニウムよりも高い。銅を利用する際のエレクトロマイグレーションに対する耐性が増大することで、半導体装置の信頼性に対する全体的な改善がなされる。これは、時間の経過と共により高い電流密度を持ち、さらに/あるいはEMに対する耐性が低い回路は、その金属製相互接続部に空隙または開路を形成する傾向があるためである。このような空隙または開路によって、装置が現場で、あるいはバーンイン中に壊滅的な故障を起こすことがある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平11−097393号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、ICの製造プロセスに銅を統合することによっても、新たな問題が起こり、これは信頼性あるいは大量生産に関しては、いかなる手段によっても完全に最適化できない。たとえば、印加電流または電位がきわめて高い電気めっき漕を用いてアスペクト比の高い開口部内にあまりに急激に銅を付着すると、実質的には直流(DC)モードにおいてのみ、銅相互接続部に空隙領域またはキーホールが形成されるという問題が起こる。このようなめっき条件においては、付着された銅は実際には、開口部の上部で剥がれて、増分的に付着される銅膜内に銅で囲まれた空気の領域すなわち空隙が形成される。また、銅の高電流密度でのDCモードのめっきにより、付着速度が高くなり、めっきされたCu薄膜内への不純物の電気めっきが良好に取り込まれないために、エレクトロマイグレーション(EM)に対する耐性が劣化した銅膜となる。

【0006】

さらに、銅を効率よく電気めっきするには、下層の薄膜の品質が大いに関係する。下層の銅シード膜が均一に付着しなかったり、不充分な量のシード材料を有する領域を含んでいると、銅はこれらの領域に均一に付着しなかったりして、ICの歩留まりおよびICの信頼性の少なくとも一つを低下させることがある。通常、下層のシード層品質に対する銅めっきの感度は、処理量の小さい低DCめっき法を用いると大きくなる。従って、高DC法が用いられようと低DC法が用いられようと、最終的な構造には一つ以上の重大な銅のめっきの問題が避けられないように思われる。

【0007】

そのため、充分な製造処理量を維持しつつ、同時に空隙の形成を軽減するか、あるいはなくすることができ、エレクトロマイグレーション(EM)に対する耐性を改善することができ、均一性を改善することができるなどの利点を有する銅相互接続部の電気めっき方法が半導体産業において必要とされる。

【0008】

電気めっきの信頼性、性能および歩留まりの問題に加えて、銅を付着するための従来の方法は、一定時間の付着を用いて基板上に銅を電気めっきすることを一般的に必要とする。通常、試験ウェハが一定の条件下で電気めっきチャンバ内で処理され、このプロセスが仕様または制御制約内で動作するか否かが判断される。システムがその制限内で動作する場合は、一定の時間の間に、後続の製品ウェハの一定時間付着処理を開始することができる。この試験ウェハプロセス制御方法は、後続の製品ウェハが、付着条件が時間が経過しても変わらないままでいるという希望的前提のもとに、仕様または制御制限内にあることを想定する。

【0009】

試験ウェハを処理し、試験ウェハが良好な結果を得る静的条件を決定し、継続してうまく行くという希望のもとでこれらの条件によりウェハを静的に処理するという方法全体が、時間の浪費であり、信頼性も乏しく、また高価でもある。従って、リアルタイムに電気めっきをその場で終了させる(エンドポイント動作する)ことができる、あるいは監視して、めっき動作をめっき中はコンピュータにより動的に制御することができる銅電気めっきシステムを提供することが有益である。これにより、試験ウェハの利用とウェハの廃棄が削減され、処理量がさらに最適化され、薄膜性能が改善される。

【0010】

本発明の目的は、アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供することにある。

【課題を解決するための手段】

【0011】

上記問題点を解決するために、本発明は、ウェハ上に銅層を形成する方法であって、ウェハを電気めっきチャンバ内に配置する段階であって、ウェハが上部誘電体面と、上部誘電体面の下方の平坦な表面に配置される底部トレンチ面と、底部トレンチ面下方の平坦な表面に配置される底部ビア面とを有する二重填込相互接続開口部を有し、電気めっきチャンバが少なくとも一つの電気コンタクトを通じてウェハに接続される制御システムを有し、制御システムがウェハに電力を提供する、段階と、第1期間の間、ウェハに対する電力を正にパルス化する段階と、第1期間に続く第2期間の間、ウェハに対する電力を負にパルス化する段階と、第2期間に続く第3期間の間、ウェハに対する電力を正にパルス化する段階とを備えることを要旨とする。

【0012】

一般に、本発明は銅電気めっきチャンバの陰極および陽極の少なくとも一つを制御して、銅電気めっき動作を介して半導体ウェハ上に形成される銅(CuまたはCu合金)相互接続部の品質を高めるための方法および装置である。パルス化された正および負の少なくとも一つの電流波形の様々なシーケンスが、銅電気めっきチャンバの陰極および陽極の少なくとも一つに供給される種々の随意の直流(DC)バイアス期間を包含することと共に、銅の均一性、銅のエレクトロマイグレーション(EM)に対する耐性、めっき処理量、銅空隙、銅の粒子構造やその他同様の特性の一つ以上に悪影響を与えうることがわかっている。

【図面の簡単な説明】

【0013】

【図1】銅材料を半導体ウェハ上に電気めっきするために用いられる電気めっきチャンバとそれに関連するコンピュータ制御システムを、断面図および電気ブロック図に混合して示す。

【図2】図1の陰極アセンブリ(すなわちウェハ、ターンテーブルおよびクランプ)の上面図である。

【図3】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図4】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図5】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図6】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図7】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図8】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図9】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図10】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図11】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図12】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図13】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【発明を実施するための形態】

【0014】

本明細書に教示される改善された銅電気めっき法は、本明細書の図1ないし図13を特定的に参照することにより、より良く理解頂けよう。

図1は、電気めっきシステムまたはチャンバ10の断面図である。チャンバ10は、チャンバ10の動作を電気的、化学的および機械的に制御するために用いられるコンピュータ制御システム34のブロック図に結合される。システム10は、チャンバ・アセンブリまたはハウジング11を具備する。ハウジング11は、時間の経過と共にチャンバ10から過剰な電気めっき流体を排出するための一つ以上の流出口22を有する。システム10は、流入するめっき流体19を受け入れるための流入口24を有する内カップ12をさらに具備する。この流体19には、増白剤、担体、レベラや同様のめっき添加剤のうち1種以上が含まれる。カップ12には、中央拡散器13が含まれることがある。拡散器13は、一般に、陽極14と、チャンバ10のウェハ20または陰極アセンブリとの間に多少の絶縁を行うために用いられる。図1の陰極は、ウェハ20、クランプ18やターンテーブル16のうち一つ以上を集合的に示す。また、拡散器13は、ウェハ20に対する流体の乱れを軽減し、溶液中の不純物/濃度の均一性または分布を改善するために用いられる。

【0015】

陽極14は、カップ12の底部と拡散器13との間にあり、図1には明示されない電源から電力を供給される。図1の陰極と陽極の両方の制御は、同一のコンピュータ34により行っても、異なるコンピュータにより行ってもよいことに注目されたい。陽極14は、一般に、めっき動作中に静止DCバイアスにより制御されるが、本明細書に教示される陽極14は、パルス化された直流(DC)により制御することも、あるいは、電気めっき期間中に時間の経過と共に、DCおよびパルス化電流(I)の少なくとも一つまたは電圧(V)との間で切り替えて、電気めっき速度(すなわち処理量)を変更したり、銅薄膜の粒子寸法に影響を与えたり、あるいは電気めっき銅薄膜のその他の特性またはプロセスを改変することもできる。本明細書においては、DC、電力、電圧および電流を交換可能に用いることができるが、それはこれらの要因すべてが電力に多少の関連を持つためである。

【0016】

従って、本明細書においては陰極の電気制御が教示される(図8ないし図13)が、これらの方法を一定の環境において図1の陽極に一般的に適応することができるということに注目することが重要である。システム10は、ターンテーブル16と一つ以上のクランプ・フィンガまたはリング18を有するヘッド15をさらに具備する。アセンブリ全体(ウェハ20、クランプ18およびテーブル16の内一つ以上を含む)が、システム10の陰極として電力を供給される。陰極アセンブリの構成部品は、通常、このようなバイアスが可能な白金または白金チタンで作られる。ターンテーブル16は、通常は、機械、コンピュータやモータで制御されており、めっき中のウェハの回転を可能にするが、この回転は特定のめっき動作中には必ずしも必要ではない。

【0017】

陰極(たとえば、ウェハ20、クランプ18およびターンテーブル16のうち一つ以上)は、図1の制御システム34を用いて電力を供給されたり、さらに/あるいは電気的に監視される。制御システム34は、任意の種類のコンピュータ制御装置であるが、一般的には、ある種の中央処理装置(CPU)26である。CPU26は、スイッチまたは論理32を制御し、これにより、一つ以上の電源28から陰極にどのようにして、いつ電流や電圧(すなわち電力)が提供されるかを制御する。電源28(一つ以上の電源の場合もある)は、直流(DC)レベルの電力または広範囲の電流や電圧レベルのパルス化DC波形を提供することができる。さらに、電源28は、鋸歯電力波形、正弦波形、対数波形、指数波形などの交流(AC)波形や、その他の種類の電力/時間制御を図1の陰極に与えるよう設計することができる。また、電源28は、オンタイムまたはオフタイムの異なる電力強度やデューティ・サイクルを有する方形波波形を提供することもできる。さらに、電源28は、負または正の極性あるいはそれらの組み合わせのいずれにおいても、これらの波形または電流/電圧/電力レベルのうち任意のものを提供することができる。この電力は、電源28を介して図1のクランプ18に送られる。

【0018】

電力を供給するために用いられるのと同じクランプ18は、電気めっきの監視を実行するためにエンドポイント検出センサに随時結合されるのと同じクランプである。別の形態においては、制御のために回路30によってのみ結合され、電源28により制御のためにではなく結合される、電源専用のエンドポイント・クランプまたはプローブ18を用いて、ウェハ20の電気特性を定期的または継続的に監視して、その場での電気めっき制御を行うことができる。一方で、電源28に結合される他のクランプ18がウェハ20の電気めっきバイアスを実行する。

【0019】

クランプ18または他のコンタクト機構を通じて、装置30がいかに機能するかの例として、センサ30またはそれに制御される電源がウェハ20に一定の電圧を印加し、それに由来する電流を測定する。それから得られるI−Vデータを用いて、増分的に付着するCu薄膜の抵抗値Rを決定することができ、それによってRの推定値がR=σl/Aを介してCu薄膜の厚みに相関される。I,Vを用いてRを決定することができるが、Cuの導電率(σ)または抵抗率の逆数が既知であり、さらに任意の二つのエンドポイント測定クランプ18の間の有効長(l)はチャンバの設計により一定であるので、Aだけが唯一の変数となる。Aは、電流が流れる断面積であり、付着するCu薄膜の厚み(t)の直接的な関数である。従って、Aが増大すると、この増大は厚みが対応して増大することによるものであり、それによって、RをAにマッピングしてエンドポイント検出に対応することができる。

【0020】

別の形態においては、回路30がウェハ20に一定の電流(I)を印加してそれに由来する電圧(V)を測定することもできる。このI−VまたはV−Iプロセスを同じクランプ18内に電源28と共に時間多重したり、あるいは別々の専用エンドポイント・クランプ18に付属させることもできる。時間の経過によるウェハ20の電気特性を測定することにより、ユニット30は、電気めっきのプロセスをいつ終了させるかを正確に決定することができる。これは、時間の経過と共にウェハ上に付着される導電性銅薄膜の厚みを測定されるウェハ抵抗値またはその他の被測定電気特性に容易に相関することができるためである。また、ウェハ20をウェハ表面全体で、あるいはいくつかの異なる対の個別に配置されるクランプ18の間で、複数の方向から監視することができる。これにより、ウェハ全体の抵抗値の二次元マップ(すなわち電気めっき厚の2-Dマップ)をコンピュータにより得ることができ、CuまたはCu合金の電気めっき中にリアルタイムの均一性データを生成することができる。このような均一性情報はCPU26が用いて、付着中の電力20を最適化し均一性を改善することができる。あるいは、均一性データを用いて、保守または修理のために機械を随時停止させることができる。

【0021】

従って、システム10の動作中に、めっき液19が流入口24を通じてカップ12内に入り、流出口22から出る。陽極14が酸化され、銅が制御システム34により与えられる信号を介して陰極上にめっきされる。めっき中は、制御システム34が陰極および陽極の少なくとも一つの電力を制御し(すなわち時間の経過と共に電流および電圧の少なくとも一つの供給を選択的に変更することにより)、ウェハ20上に付着される銅の品質と特性とを改善する。めっきプロセスのエンドポイント検出およびさらなる制御を、エンドポイント・センサおよび回路構成30を用いてその場で実行することもできる。

【0022】

要するに、陽極14、クランプ・フィンガ18および基板ウェハ20(すなわち陰極)は、一つ以上の制御システム34を用いてバイアスされ、基板20に銅でめっきをする。このとき、コンピュータ・システム34を介して要素14,18および20の少なくとも一つをバイアスする方法は、ウェハ処理量、銅空隙形成の軽減または削除、Cuピンチオフの軽減、薄膜均一性の改善やエレクトロマイグレーション(EM)に対する耐性の改善のうち一つ以上に大きな影響を与える。一般に、本明細書の図8ないし図13に後述される、一つ以上の電気めっき陰極バイアス法を用いると、薄膜特性の改善、信頼性の改善や性能の強化が達成されることがわかっている。

【0023】

図2は、図1において断面図として前述された陰極アセンブリの上面図である。図2は、ウェハ20、ターンテーブル/ヘッドプレート16および6個のクランプ18を示す。図2には6個のクランプが図示されるが、図2の6個のフィンガ・クランプの代わりに一つの大きなクランプ・リングを用いることも可能であることに留意されたい。また、図2のウェハ20の周縁表面の回りに任意の数(たとえば3個、10個、40個、100個など)のフィンガ・クランプを用いることもできる。図2は、図2の6個のクランプのうち、任意の二つ以上のクランプの間でエンドポイント電気データが得て、時間の経過と共にウェハ20の種々の地点または経路に形成される銅の厚みを表す二次元めっき均一性マップを導くことができることを示す。異なる位置により多くのクランプが用いられると、均一性マップの解像度がより高くなることは明白である。図1および図2は一種の電気めっきシステムを示し、それにより、多くの異なる構造または要素を図1および図2のシステムに追加または削除することができる。一方で、図1および図2を本明細書の図3ないし図13の教義と組み合わせて充分に活用することもできる。

【0024】

一般に、図1および図2に示されるシステムを用いて、図3ないし図7に示されるのと同様に、ウェハ20上に時間の経過と共に銅またはその他の金属材料を電気めっきすることができる。このような銅または金属めっきは、図8ないし図13に関して本明細書に説明される一つ以上の方法を用いて、図1の陰極に(および/または図1の陽極14にも)電力を供給することによって実行することができる。半導体ウェハ上に改善された銅の一重填込(single inlaid)や二重填込(dual inlaid)相互接続部を形成するために用いられる特定の方法は、以下の図3ないし図13を詳細に参照することにより、さらに良く理解頂けよう。

【0025】

図3ないし図7は、時間の経過と共に銅電気めっき材料により形成される二重填込集積回路(IC)構造を断面図に示す。この電気めっきは、図1および図2に図示される装置またはそれに類似の装置を用いることにより実行される。図3は、半導体構造100(たとえば、より大型のウェハ20上に形成される多くの構造のうちの一つ)を示す。半導体構造100は、一つ以上の基層102を備える。基層102は、通常、好ましくは半導体ウェハである基板を具備する。図3の層102の底または基部として設けられる基板材料は、シリコン、ゲルマニウム・シリコン、ガリウム・ヒ素、ゲルマニウム、その他のIII-V族化合物、シリコン・カーバイド、絶縁体上シリコン(SOI:silicon on insulator)材料または同様の基板材料のうちの一つまたはそれ以上である。

【0026】

この基板材料上に図3の領域102が形成される。領域102は、通常、フォトリソグラフィック・パターニングおよび選択的エッチングされて、基板材料上やその中に半導体装置を形成する導電層、半導体層および誘電体層の少なくとも一つの混合物である。たとえば、領域102は、窒化シリコン、二酸化シリコン、テトラエチルオルトシリケート(TEOS:tetraethylorthosilicate)ガラス、ボロホスホシリケート・ガラス(BPSG:borophosphosilicate glass)、低k材料、キセロゲルなど、種々の酸化物や窒化物のうち一つ以上を含むことがある。領域102には、ゲルマニウム・シリコン、多結晶シリコン、非晶質シリコン、ドーピング多結晶シリコンおよび同様の材料などの半導体層が含まれることもある。これらの可能性のある層に加えて、多層領域102には、耐火性シリサイド、耐火金属、アルミニウム、銅、タングステン、これら材料の合金、導電性窒化物、導電性酸化物または同様の金属構造などの導電性または金属層が含まれることもある。

【0027】

図3の層102上に、このような金属相互接続構造104を二つ図示する。一つの形態では、領域104は填込銅相互接続部であり、図3の装置100の導電性相互接続部を形成する。他の形態では、層104は、一つ以上のアルミニウムやタングステン領域である。一般に、相互接続部104は、図3の層102内部または下方に形成される種々のアクティブおよびパッシブの少なくとも一つの電気構成部品を電気的に相互接続するために配置される。

【0028】

層102、104上に、エッチ・ストップ層106がある。エッチ・ストップ層は、一般に窒化シリコン層、酸窒化物層または高シリコン窒化シリコン層である。エッチ・ストップ層106上には、レベル間誘電体(ILD:interlevel dielectric)部分108があり、これは、テトラエチルオルトシリケート(TEOS)ガラス、フッ素ドーピングTEOS(f-TEOS)、オゾンTEOS、ホスホシリケート・ガラス(PSG:phosphosilicate glass)、ボロホスホシリケート・ガラス(BPSG)、低k誘電体材料、窒化物、スピンオンガラス(SOG:spin on glass)またはその複合物のうち一つ以上の材料で形成されるのが一般的である。層108上には第2エッチ・ストップ層110があり、これも反射防止皮膜(ARC:anti-reflectivecoating)として機能し、層106に関して上述されたのと同じ材料で作成されるのが一般的である。ある形態では、層106.110は、酸窒化シリコン、窒化シリコン、高シリコン窒化シリコンや同様の誘電性材料の複合物である。層110上には、別のILD層112があり、これは上記の層108と類似の層である。

【0029】

図3は、層106〜112が一つ以上のリソグラフィック・パターニングおよびエッチ・プロセスによりリソグラフィック・パターニングおよびエッチングされて、填込または二重填込構造を形成する様子を示す。図3は、特に、層108を貫通して形成される少なくとも二つのビアと、層112を貫通して形成される一つ以上のトレンチ領域とを有する二重填込構造を示すが、層112内のトレンチ領域は図3の層108内の二つのビア間を接続する。図3の二重填込トレンチ構造は、底部トレンチ面117と、誘電体層112の上面である上部誘電体面115と、金属相互接続領域104の露出上面である底部ビア面119とを有する。

【0030】

図3は、二重填込トレンチ構造内および上部誘電体面115上にバリア層114が形成される様子を示す。一般に、層115は、1000オングストローム未満の厚みを有する層であり、銅が隣接する誘電領域112、108内に拡散して悪影響を与えることを防ぐことのできる任意の材料で作られる。詳しくは、銅バリア層として用いられる材料には、窒化タンタル(TaN)、窒化チタン(TiN)、チタン・タングステン(Ti/W)、それらの複合物や同様の材料などがある。場合によっては、誘電体材料108,112が選択または表面処理されて、バリア層が全然必要とされないか、あるいはそれによって層108,112の表面部分そのものがバリアとして働くこともある。

【0031】

図3は、銅、金属または銅合金シード層116が、任意のバリア層114の上面に形成される様子を示す。ある形態では、層116はスパタリングまたは物理的蒸着(PVD:physical vapor deposition)により形成される銅層である。別の形態では、層116は化学蒸着(CVD:chemical vapor deposition)を用いて形成される。場合によっては、PVDプロセスとCVDプロセスを組み合わせて用いることもある。いずれの場合も、層116は、銅によって構成される層であるのが一般的であり、通常2500オングストローム未満の厚みを有する。無電解めっきなど他の方法を用いて図3のシード層116を形成することができることに留意されたい。

【0032】

図3に示されるように、一般的なPVDプロセスは二重填込相互接続構造の全露出面および隅部上で完全に均一または同形ではないシード層116を形成しやすい。実験により、PVDシード層116には、図3に図示されるようにシード空乏部116aが通常は含まれることがわかっている。シード空乏部116aは、シード材料をほとんどあるいは全然含まない露出相互接続面の領域である。領域116aにシード材料が含まれない場合、これは普通は、少なくとも部分的に互いに分断された銅の不連続な塊または島である。シード空乏部116aは、図3に示されるように、底部トレンチ面117と底部ビア面119との間に位置する側壁上に最も起こりやすいことが実験的にわかっている。

【0033】

図3には、より薄いシード部116bも示される。より薄いシード領域116bは、一般的には連続した薄膜(領域116aのように島または塊ではなく)であるが、上部誘電体面115上のシード層の大半の他の部分よりも薄いシード層領域である。領域116bは、一般に、上部誘電体面115と底部ビア面119との間のトレンチ構造の側壁部分や底部トレンチ面117と底部ビア面119との間の側壁表面部分上に発生する。また、底部ビア面119を覆うシード層部分は、上部誘電体面115上に形成されるシード層の厚みより通常は薄いことがわかっている。図3では、より厚いシード層部分と厚い隅部116cをPVDシード層116内に形成することができることも示される。

【0034】

一般に、領域116a,116b,116cの形成は、図4ないし図7に示されるように、後の電気めっき動作を複雑にすることがある。電気めっきシステムの陰極をバイアスするための異なる方法により、図3の領域116a,116b,116cが存在することで起こる種々の悪影響を防ぐことができることがわかっている。領域116a,116b,116cに由来するめっき上の不利益を軽減することがわかっている特定の電流、電圧および電力波形の少なくとも一つを、図8ないし図13に関して以下に特定的に図示および説明する。

【0035】

図3に示される構造100の形成後、ウェハ20(構造100を含む)が図1および図2に示されるシステム10内に配置される。このウェハ20は、次に図1に示されるように電気めっき液19に露出される。液19への露出中は、図8ないし図13のうちの一つ以上またはそれらの組み合わせにおいて示すように、制御システム34が(一つ以上のクランプ18を介して)ウェハ20に供給される電力、電流または電圧の量を制御して、本明細書の図4ないし図7を通じてウェハ20上に増分的に形成される電気めっき銅薄膜の品質を改善する。

【0036】

詳しくは、図4は、図3に示される二重填込トレンチ構造の表面全体に亘り実行される銅電気めっき動作の開始段階を示す。図4においては、ウェハ20上に増分的に銅(Cu)層118aを電気めっきするために、高電力電気めっきプロセスが用いられている。図4が電気めっき中の初期の時間帯に比較的高レベルの電力を図1および図2のシステム10内で陰極(ウェハ20)に与えると結果が得られる高電力電気めっきプロセスである。高電力電気めっきプロセスは、図3に示されるシード層116の表面上に高速の銅付着を行う。高い付着速度に加えて、高電力付着プロセスにより、シード層を欠くあるいはシード層成分が実質的に少ないシード空乏部116a(図3参照)上へのめっきが容易になる。低電力の電気めっきプロセスでは、図3のこれらのシード空乏部116aを充分にめっきせず(すなわち低電力めっきでは受認可能な速度でこれらの領域にめっきしない)、そのため銅相互接続部内に空隙が形成されることが実験的にわかっている。従って、ここでは高電力の初期めっき期間を用いて、図3のシード空乏部116aが存在しても銅相互接続部の品質を改善し、さらに初期のCu付着をより高速にすることにより処理量を改善する。シード層116と新規に電気めっきされた銅層118aとは破線で隔てられており、特に、シード層116が銅であり電気めっき層118aも銅である場合に、シード層とその上の電気めっき層の間の接合が、走査電子顕微鏡(SEM:scanning electron microscope)断面において識別することが不可能であることを示す。

【0037】

高電力電気めっき期間の上記のような利点にも関わらず、高電力めっき期間は一般的に、エレクトロマイグレーション(EM)に対する充分なレベルの耐性を改善または提供するために、窒素、炭素およびイオウなどの不純物を充分にCu薄膜内に取り込むことがない。従って、図4の領域118aは希望するほどにはEMに対して耐性をもたないことが多い。さらに、図4に示されるように、高電力めっき期間があまりに長い間維持されると、図3のより厚い領域116cの存在により、結局は、銅相互接続構造内にピンチオフまたは空隙ができてしまう。言い換えると、高電力電気めっきは表面116c上にあまりに迅速にめっきするので、図3の二つの隣接領域116cはビアが埋まる前に一緒にめっきしてしまって、ピンチオフが起こることがわかっている。ピンチオフによりビア領域付近の相互接続構造内に空隙すなわち欠如が起こる。従って、高電力サイクルを用いる銅の電気めっきは、処理量を改善しシード空乏部116aの存在を補償するが、高電力のプロセスが初期期間にあまりに長い間続くと、ピンチオフおよび空隙が起こりEM耐性が低下すると判断された。

【0038】

高電力電気めっきプロセスには問題があったので、低電力電気めっきで上記の問題が解決できるか否かが検証された。実験の結果、電気めっき処理の間に最初に用いられた低電力電気めっきプロセス(以下、初期段階と呼ぶ)は、図3のシード空乏部116a上に充分にめっきすることはできなかったが、銅薄膜内への不純物の取り込み(たとえばイオウ、窒素、炭素など)が改善され、それによって最終的な銅薄膜におけるエレクトロマイグレーション(EM)に対する耐性が改善されたことがわかった。従って、低電力初期処理は、空乏領域116aの存在がシード形成において全体的に回避できれば有益である。このような領域116aは、シード層116がPVD層ではなくCVDシード層であれば全体的に回避することができる。従って、低電力電気めっき初期動作は、特に、図3の空乏領域116aの発生を大幅に低減するCVDシード層が用いられるならば、場合によっては有利である。

【0039】

低電力電気めっきの上記の利点とは対照的に、環境によっては電気めっきの初期段階における低電力期間が、図1のシステムを用いても充分なウェハ処理量を提供しないことがある。また、低電力プロセスの付着速度が高電力プロセスより低くても、領域116c上で図4に図示されるほど付着の均一性が改良されない。従って、低電力電気めっき処理も高電力電気めっき処理も、図3の領域116cの存在により、填込ビア領域内にピンチオフおよび空隙を最終的に起こすこともある。そのため、付着中に低電力と高電力の電気めっきを交互に行った電気めっきプロセスは、空乏領域116aを解決し処理量を高めるという高電力の利点を保持しつつ、EM耐性の改善された特性という低電力の利点を備えることがわかっている。しかし、低電力/高電力の電気めっきプロセスを組み合わせて形成される相互接続部も、依然としてピンチオフを起こす可能性がある。従って、高電力の種々のサイクルを低電力の種々のサイクルと組み合わせることにより、改善された銅相互接続構造を形成することができ、それにより処理量、シード空乏部空隙耐性およびエレクトロマイグレーション(EM)耐性のバランスを取る、すなわち時間と経過と共に最適化することができるが、空隙は依然として問題であることが認識された。そのために、高電力/低電力を組み合わせためっきサイクルを採用した後でもピンチオフにより起こる空隙の問題を解決するためには、めっきプロセスに対してさらに改良を加えることが必要であると認識された。

【0040】

図4は、高い正の電力サイクルと低い正の電力サイクルを交互に実行することにより形成して電気めっきを開始しても、領域116c上に空隙が依然として起こりやすい様子を示す。このような空隙を排除または軽減するためには、負にパルス化された電力(交流(AC)、パルス化DCまたは直流(DC)のいずれかを介して)を図1のウェハ20に対して、1回以上、上記の正の高電力サイクルと低電力サイクルとの間の種々の間隔において印加するべきであるということがわかった。ウェハ20にある種の負の電力サイクルを定期的にまたは随時印加することにより、図4に示す層118aのピンチオフ「危険」部分を構造から効果的に排除することができることがわかった。領域116cのこのような負の電力サイクル修正を図5内の結果として得られた層118bにより示す。一般に、負の電力を図1のシステム10の陰極に印加することにより、電気めっきプロセスが反転され、すでにウェハ上に付着された電気めっき材料がウェハから除去すなわちスパタリングされる。この負の電力除去段階の間、電気めっき材料は領域116aおよび116bの少なくとも一つの上のめっきを介して形成された厚いほうの領域(電流密度が低いほうの領域)からよりも・層118aの厚いほうの(電力密度が高いほうの)領域(たとえば領域116c)から、より高速で除去される。全体的な結果は、シード116上に、図5に示すようなより同形の増分層118bが形成される。従って、図4の高電力正電力や低電力正電力サイクルと組み合わせて負の電力サイクルを用いると、より厚い領域116cの存在を補償する逆めっき特性を利用することにより相互接続開口部内に空隙を起こす可能性が、大幅に小さくなる。言い換えると、負の電力を銅付着中に特定の間隔で供給することで、電気めっき均一性特性を改変することがわかり、適切な順序で実行すれば(種々の適切な順序に関しては図8ないし図13を参照)、相互接続開口部内の空隙を軽減できる可能性がある。

【0041】

図6は、高電力ACおよびDC正サイクルの少なくとも一つと低電力ACおよびDC正サイクルの少なくとも一つを交互に、さらに補正用負ACおよびDCサイクルの少なくとも一つを随時加えて、最終的に図3の相互接続構造を最適な方法で電気めっきおよび充填する様子を示す。従って、この最適充填は図6の銅層118cにより示される。銅付着中に、様々な正高、正低および負電力サイクルと極性を特定的に実行する方法は、相互接続の品質を最適化することがわかっているが、これについては本明細書の図8ないし図13において、より詳細に説明する。一般に、本明細書に教示されるシステム10に電力を供給する方法により、種々の領域116a,116b,116cのうち一つ以上の領域を有するシード層116から歩留まりと品質とを改善して、相互接続部がめっきされる。従って、図1のシステム10の陰極に対する電位、電力または電流強度ならびに極性(すなわち負または正)を時間の経過と共に制御し交代することにより、エレクトロマイグレーション(EM)に対する耐性を改善し、均一性を強化し、ピンチオフを軽減または除去し、ウェハ処理量を増大し、空隙を作らずに、図7の全面めっき層118を形成することができる。

【0042】

図7は、電気めっきプロセスのある時点において、銅118cが相互接続開口部を完全に充填する様子を示す。空隙の危険性がなくなった後は、急速な高電力DC電気めっきサイクルを開始して、それにより処理量を高めることができる。従って、図7において既存の銅材料118c上に付着された銅材料118dが、高電力、正D C電気めっきプロセスまたはその他の高処理量波形を用いて付着される。その結果、相互接続開口部を完全に充填し、集積回路(IC)産業において大量の高い歩留まりでの用途に関して最適化され改善されている銅薄膜が得られる。また、ここでの一つ以上のプロセス・サイクルとして、ビア内ではより速い速度で付着し、上部誘電体面115上では低い存在しない速度で付着する、ボトムアップ充填プロセスを用いることも可能である。このようなボトムアップ充填サイクルを用いると、本明細書に教示されるように改善された銅相互接続部の製造を行うこともできる。

【0043】

図3ないし図7は、電気めっき中に図1のチャンバ10の陰極および陽極の少なくとも一つに印加される電力の種類、強度および極性を制御することにより、エレクトロマイグレーション(EM)耐性を改善し、ウェハ処理量を充分にとり、空隙およびピンチオフを大幅に軽減して半導体ウェハ上に銅相互接続部を形成することができることを示す。

【0044】

図8ないし図13は、図3ないし図7に関して前述された種々の改良結果の一つ以上を得るために、制御システム34を介して図1の陰極に与えられる特定の電力シーケンスを示す。

【0045】

詳しくは、図8は、図1の陰極(すなわちウェハ20)が電気的に制御され、図3ないし図7に関して説明された改善された銅相互接続部の形成を行うための、一つの可能なシーケンスを図示する。図8はXY図であり、縦のY軸は電流(I)をアンペアで、横のX軸は時間を秒で表す。図8は、縦軸の電流を示すが、本発明の精神および範囲から逸脱することなく、Y軸として電流、電流密度、電圧または電力のいずれかを図示することができるということに注目することが重要である。言い換えると、本明細書で用いられる場合に、電流、電流密度、電圧または電力は、一般的に交換可能な数量または用語である。

【0046】

図8は、図3に示されるようなシード空乏部116aを持たない化学蒸着(CVD)シード層116と共に利用すると最適な陰極電力シーケンスを示す。CVD付着シード層は、物理的蒸着(PVD)またはスパタリング・プロセスを用いて形成されるシード層と比較して、シード空乏部116aを起こしにくいことが実験的にわかっている。このような空乏部116aが起こりにくいために、低電圧正DC初期段階/サイクル201を図8の左側に示すように用いる。低電圧初期段階201は、より多くの量の不純物を電気めっき銅薄膜内に取り込み、それによってエレクトロマイグレーション(EM)耐性が改善されるので、CVDシードについては有益である。

【0047】

一般に、通常の電気めっきプロセスに関して、初期段階201は約0.5ないし3アンペアの間の正DC電流を利用する。図8は、段階201の期間の間は電流が1アンペアに設定されることを特に図示する。一般に、この初期段階201は、継続時間にして数秒から約1分間の間は継続することができる。

【0048】

ある程度の銅材料がウェハ20上に付着される初期段階201が終了すると、正のパルス化電力段階212が開始される。図8は、正のオン電流202とオフ電流204の交互期間が、期間212の間にウェハ20に対して図1のコントローラ34によって与えられる様子を示す。期間212には、一つ以上のオンまたはオフのパルスが含まれ、一般的には約1ミリ秒(ms)から1秒の間継続する。好適な実施例においては、期間212における正パルス202のオン期間202は継続時間にして約7.5ミリ秒であり、期間212におけるオフ期間204は継続時間にして約0.5ミリ秒である。他の継続時間または他のデューティ・サイクルを図8のオン・パルス(202)とオフ・パルス(204)に関して用いることができることに留意することが重要である。図8は、サイクル212のオン期間202の間に提供される電流または電力レベルが約6アンペアであることを示す。一般に、期間212のオン期間202の間の電力レベルは、期間201の間の電力レベルよりも高くすべきである。このように、電力を高くすることにより、図1の溶液19内の添加剤がめっき中に充分に活性化される。しかし、オン期間202中の電力レベルは、添加剤により得られる有益な機能が禁止されるほど大きくしてはならない。このために、期間212における図8の電力レベルは、溶液19の組成と、使用される電気めっきシステムの種類とにより可変する。

【0049】

初期段階201と正パルス電力段階212の後で、ウェハ20は図8上に示される図4内のものと同様の形状を示す。従って、これまでに付着された銅または銅合金材料は、一般に、高い全体付着速度で付着されているが、相互接続開口部内に複合シードおよび上層の電気めっき層が非同形的に付着されるように付着された可能性が高い。前述のように、この非同形的な正電力付着が続くと、銅相互接続部はピンチオフに伴う空隙の問題をはるかに起こしやすくなる。さらに、低電力初期段階201は、空乏部116aがあると(PVDシード層に関しては可能性が高い)、その上にめっきすることが困難になる。領域116aが存在する場合は、サイクル201を用いる代わりに期間212を交互に用いて、領域116a上に最初にめっきする。しかし、低電力プロセスを用いると、不純物の取り込みが一般的に改善されるので、可能であれば初期段階201を用いると、エレクトロマイグレーション(EM)に対する耐性がそれに応じて改善される。

【0050】

期間201および212の少なくとも一つに対する長期の露出に伴う空隙を最小限に抑えるために、正パルス化期間212を結果的に終了させて、負パルス化期間214を開始する(図8の中央を参照)。負パルス化期間214の総合的な継続時間は、一般に約0.2ミリ秒から1秒の間である。図8において、負パルス化期間214がウェハ表面から銅を剥離すなわち除去する。銅は、ウェハの銅層の高電流密度(厚い)部分からより高い速度で除去される。この銅除去により、複合シードおよびめっき済みの銅薄膜の側壁プロフィルが平らになり、図4に示される「ピンチオフ」の危険性を減らし、図5に関して図示および説明されたより均一な電気めっき銅薄膜プロフィルを生み出す。

【0051】

銅の全体的な正の厚みがウェハ20の上に期間の間に形成されるようにするためには、期間212の間に付着される銅の量は、期間214の間に除去される銅材料の量よりも一般的に多くなければならない。従って、期間212を期間214よりも継続時間が長くするか、さらに/あるいは、期間212は期間214の間に与えられる電力の絶対値よりも大きな平均的絶対値の電力をウェハに与えなければならない。期間214に関しては、期間214の総合的なオン時間206は約0.5ミリ秒であり、オフ期間208は約0.5ミリ秒である。しかし、付着される銅の全体量が時間に亘り除去される銅の量を超えていれば、期間214において任意のパルスのデューティ・サイクルまたは継続時間を用いることができる。

【0052】

また、図8は、オン期間206の間の負パルスの強度が、約負の4アンペアであり、付着される銅がこの期間中に除去される銅の量を超えていれば、電源が許すだけの大きさとすることができる様子を示す。一般に、銅を除去して、図5に全体が示されるプロフィルを作成することができれば、任意の強度の負パルス電流を用いることができる。従って、他のデューティ・サイクル、他の切換周波数、同期または非同期のオン/オフ・パルス、継続時間と電力レベルの可変する他のパルスなどを図8ないし図13において本明細書に教示されるパルス化期間の間に用いることができる。

【0053】

負パルス化期間214が終了すると、図5に図示されるのと同様の相互接続開口部が図1のシステム内に出現する。少なくとも1回の正パルス化期間212と1回の負パルス化期間214の後で、図1の制御システム34は任意の回数の同期または非同期順序で任意の回数だけ、サイクル212と214の間で交代を続行する。従って、正と負のパルス化サイクル212,214の任意の組み合わせ、順序および回数の少なくとも一つを用いて、本明細書に教示される相互接続開口部を充填することができる。一般に、図6の構造が空隙を起こさない方法で、前述の目標の厚みまで充分に形成されるようにするために充分な回数の正と負のパルス化サイクル212,214が実行される。

【0054】

図6の相互接続開口部が図8の期間201,212,214の任意の組み合わせを用いて充分に充填された後は、処理量の観点から、図8の右側の期間210により示されるように、ウェハ20に高いDC電位で給電することが望ましい。期間210の間は高電力DC電位を用いることにより、銅層の最上部(たとえば図7の領域118d)が空隙の危険を起こさずに高速で付着されて、それにより処理量が改善される。

【0055】

図8の期間210が終了すると、ウェハ20が図1のシステムから取り出されて、化学機械研磨(CMP:chemical mechanical polishing)動作に移され、空隙が軽減または除去され、信頼性が改善され、さらに/あるいは性能が強化された二重填込相互接続構造の形成が終了する。図8のプロセスは、本明細書に教示される他のプロセスと同様に、現在は、集積回路(IC)の基板上で複数の個別の積層された冶金層上に順次実行することができる(たとえば、この方法を用いてIC上に7層以上の銅相互接続部を作成することができる)。

【0056】

図8のプロセスにおいて、低電力DCの長期間である初期段階201だけでは、シード層116を形成するためにPVDプロセスを用いた際に現れやすいシード空乏部116a上にめっきするには充分とは限らないことが発見された。シード層116の領域116aが適切に電気めっきされないと、望ましくない側壁空隙が図3ないし図7の相互接続構造のビア部分に形成することがある。従って、領域116aがPVD付着シード層内に起こりやすいので、図9の電力シーケンスは、PVDシード層116と共に用いる場合には、図8よりも適していることが多い。しかし、図8または図9のプロセスのいずれも、任意の方法で形成される任意のシード層116と共に用いることもできる。

【0057】

図9は、増大DC電流サイクル254,256を用いて銅層を付着する前に、高電力正パルス化サイクルを用いる初期段階252の利用を示す。高電力正パルス化サイクルの初期期間252を用いて、図3のシード空乏部116a上に有効に電気めっきを行うことができることがわかった。この期間252は図3に示される空乏シード部116a,116b上への銅の成長のための核形成段階として機能する。数ミリ秒から数秒の期間の後で、図8に前述された随意の負パルス化期間214を間欠的に用いて正パルス化期間252の中で空隙が形成される確率を小さくすることができる。段階252による正パルス化処理(それに混合される随意の負パルス化を含む)の後で、低電力正DC電流が期間254の間ウェハ20に印加される。これは薄膜成長段階として機能し、図8の初期段階201と同様に作用する。

【0058】

図9の期間254などの低電力電気めっき期間により、より大量の不純物(たとえばイオウ、炭素および窒素)が銅薄膜内に取り込まれて、それによってエレクトロマイグレーション(EM)に対する耐性が改善されることがわかった。低電力正DCプロセスはシード空乏部116a上にめっきするには不充分であり、場合によっては空隙を作り出すことがわかっているが、1期間以上の低電力正DC処理期間254を用いて(1回以上の正パルス化電力制御シーケンスにより形成される)図5の構造の上部にめっきすることは有益である。これは、一般にエレクトロマイグレーション耐性が改善されるためである。空隙や銅空乏部の危険性はパルス化時間シーケンス252によってすでに克服されているので、空隙および空乏部が期間254の間に起こり悪影響を及ぼすことはない。

【0059】

しかし、期間254の間の電気めっきによりエレクトロマイグレーション(EM)耐性は改善されるが、期間254の間の電気めっきによりきわめて低速でウェハ20の表面上に銅がめっきされる。従って、処理量を高めるには、図9のプロセスを、図9の期間256により示される高電力正DC処理段階まで最終的には進行させて、それにより処理量を補い、なおかつ期間254によるエレクトロマイグレーション上の利点を利用することができるようにする。また、より高い不純物濃度が電気めっきの後で必要になる場合は、付着後にこれらの不純物を銅薄膜内にイオン注入して熱アニーリングすることができる。従って、図1の制御システム35が図1の陰極および陽極の少なくとも一つを制御する図9に示されるプロセスにより、半導体ウェハ上に図7に図示されるのと同様の改善された二重填込銅相互接続構造が得られる。この場合も、図9に示される特定の電流、電圧、期間およびデューティ・サイクル・オン/オフ・パルス幅および均一性などを調整して、可変するめっき漕組成物および装置に対応したり、さらに/あるいは可変する処理結果を生み出すことができることに注目することが重要である。

【0060】

図10は、図8および図9に関して前述されたパルス化時間シーケンス252,212,214などの任意のものと置き換えるために用いられるパルス化時間シーケンス268を示す。さらに、時間シーケンス268を、本明細書において電気めっきに用いられる任意の他の種類のDCおよびACの少なくとも一つの正および負の少なくとも一つの電力時間シーケンスと共に組み合わせて用いることができる。図10では、シーケンス268が可変する継続時間や可変する電流強度のオン・パルスによって構成されることを示す。前述のように、高電力パルスおよび低電力パルスは、材料を充分にめっきする能力に変動があり、図3の領域116a,116b,116c上での核形成およびその後の横方向の薄膜成長に影響を与え、処理量、エレクトロマイグレーション(EM)耐性、空隙の軽減、粒子構造などに対する効果が変動する。従って、より短い高電力オン・パルス262とより長い低電力オン・パルス266とを組み合わせてオフ期間264により隔てることが、ある用途においては有益であることが発見された。図10に示される電力シーケンスは、負パルス・シーケンス、DCシーケンス、ACシーケンス、パルス化DCシーケンスまたは任意の可能な他のシーケンスと組み合わせて、二重填込相互接続開口部内に改善された方法で銅をめっきすることができる。この場合も、本明細書に教示される他の図面と同様に、特定のデューティ・サイクル、電流範囲、継続時間などは、機械によりあるいはプロセスにより本明細書の精神および範囲から逸脱せずに変わることがある。

【0061】

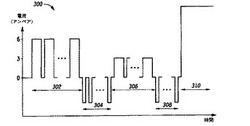

図11は、図1のシステム10と共に用いることのできる、さらに別の電力シーケンスを示す。図11は、高電力正パルス化期間302を用いて、速い付着速度でシード空乏部116a上に有効に初期のめっきを行うことができる様子を示す。図11に示される期間304と同様の負パルス期間の間に随意に散在する1回以上の期間302の後で、低電力正パルス化期間306を用いて、より低速でめっきを続けながら、なおかつ、より大量の不純物(炭素、窒素やイオウなど)を同材料内に取り込み、エレクトロマイグレーション(EM)耐性を改善する。

【0062】

図11に示されるように、高電力正パルス期間302と低電力正パルス期間306とは、図11に示される等価のあるいは異なる低電力パルス化シーケンス304または308によって隔てることができる。一般に、正電力シーケンス306に続く負電力シーケンス308は、高電力正期間302に続く期間304よりも継続時間が短く、全体の集積電力が小さい。これは、期間306では、期間302よりもウェハ20の表面上に付着される材料が少ないためで、それによって後の負電力期間中に除去する必要のある材料が少なくなり、空隙の軽減や均一性の改善が可能になることは明らかである。また、期間302は、負パルスが混在する一つ以上の順方向パルスを有し、期間304も一つ以上の反転期間によって構成される。さらに、図11は、図8にも示されるように、高電力DC動作が電気めっき動作の終点付近で始まり、システム10のウェハ処理量を改善することができることを示す。従って、図11の高電力DC期間310が電気めっき動作の終点で用いられる(図7を参照)。

【0063】

図12は、図8ないし図11に前述された期間のうち、任意の期間に関して用いることのできる別の電力期間352を示す。図12のオフ期間356と、事実上図8ないし図11に示されるすべてのオフ期間とを設けることにより、電気めっき動作が行われた後で図1の溶液19を回復させることができる。言い換えると、種々の期間のオン・パルスにより、溶液10内でウェハ20に近接して位置する(境界層)銅がウェハ上に付着する。これにより、溶液10内のめっき表面付近に、めっき材料と添加剤とを持たない領域が作成される。めっき表面付近でこのような欠乏領域(すなわち漕19内における濃度の傾斜)が銅によって回復できるようにするために、オフ・サイクルを用いて、溶液内の材料を高濃度の領域(バルク)から低濃度の領域(ウェハ表面または境界層)まで拡散させる。高いアスペクト比の開口部内にめっきする場合にこれは特に重要である。これについては、以下に説明する。

【0064】

図12は、電力シーケンス352のデューティ・サイクルが、オン期間354がオフ・サイクル356と等しいかそれよりも短くなることを示す。この種のデューティ・サイクルはきわめて小さなビア(たとえば0.2マイクロメートル未満)またはきわめて大きなアスペクト比を持つビア(8マイクロメートルのトレンチ深さと0.5マイクロメートルのトレンチ幅を持つトレンチ・キャパシタなど)において必要になることがある。開口部の寸法およびアスペクト比の少なくとも一つのために、不純物、添加剤または銅が溶液内を通り、これらの材料がめっきプロセスの結果として欠乏する領域間で拡散するのに、より長い時間がかかることがある。このような場合は、より長い相対オフ時間356が設けられて、極端に小さい幾何学形状のあるいは大きなアスペクト比の開口部が、銅薄膜の品質に大きな影響を及ぼすことなくこれらの材料の欠乏から充分に回復できるようにする。図12のプロセスを、X線リソグラフィ、位相シフト、SCALPALまたはEビーム・リソグラフィなどの高度なリソグラフィが銅相互接続または銅電極の形成に関して用いられるような一つ以上の用途において用いられることが予想される。この「長いオフ時間」の周期的サイクルとは0.1マイクロメートルのビアまたは0.1マイクロメートル未満のビアや深さと幅の比が6:1以上のアスペクト比開口部に関して特に必要とされると考えられる。

【0065】

図13は、二つの可能な電気めっきシステム(システムAおよびシステムB)の動作を示す。いずれのシステムAまたはB(あるいは図13に明記される概念に準じて形成される別のシステム)を用いても、その場でエンドポイント検出またはプロセス制御を行いながら銅またはその他任意の冶金材料を任意の基板上に電気めっきすることができる。このエンドポイント法およびシステムは、図1ないし図12に示される波形のうち任意のものと組み合わせて用いることができ、また図1のシステム10を用いて実行することができる。

【0066】

詳しくは、図13の上部はシステムAを示す。システムAは図1に示されるシステム10と同様のもので、エンドポイント検出、データ収集および現場制御に用いられるのと同じクランプ18を通じて電力がウェハ20に供給される。言い換えると、図8ないし図12の一つ以上のサイクル201,212,214,210,252,254,256,268などをウェハ20に適応し、断続的に中断することにより、エンドポイント検出動作を同じクランプ18上で開始する。従って、システムAを時間多重エンドポイント検出システムと呼び、これにより一定のクランプ18を電気めっきおよびエンドポイント/プロセス現場検出の両方の間の電力のために用いる。

【0067】

このような時間多重システムの動作の一例として、図13のシステムAは正パルス化電力シーケンス502を実行し、その後直ちに負パルス化電力シーケンス504を実行するものとして図示される。これらの電力シーケンスは、図1および図2に示される一つ以上のクランプ18を通じて実行される。これらのサイクル502,504の一つ以上を実行した後で、電源28は図1のスイッチ32を介してクランプ18から切り離される。この時点で、エンドポイント・センサ30がスイッチ32によりクランプ18に接続される。CPU26の制御下でスイッチ32により可動化されるこの接続により、エンドポイント検出動作506が図13において実行される。

【0068】

期間506において、電圧や電流が一つ上のクランプの両端に印加や検出され、ウェハ20上の銅めっきの抵抗がウェハ20上に形成された銅の充分な厚みを示すが否かが判断される。また、多くのプローブ/コンタクト点の両端での多方向二次元探査が期間506においてウェハ20の表面全体で行われる。従って、期間506により、ウェハ上の種々の点の間の材料の均一性または厚みが判定され、このデータはデータベース作成のために格納することができ、あるいは二次元描写されて、ウェハ間のバイアスに関する均一性を追跡することができる。また、この均一性データをCPU26によって処理して、後で電源28によりウェハ20に対して提供される電力をクランプ毎に改変することができ、それによって均一性を電気めっき動作において現場で改善することができる。

【0069】

さらに、期間506のエンドポイント動作は電気めっき動作をいつ停止するかを検出するために行うのではなく、電気めっき動作が1通りの動作をいつ停止して、別の動作をいつ開始すべきかを検出するために用いることができる。たとえば、期間506のエンドポイント検出を用いて、二つの期間502,504の反復循環を、異なるデューティ・サイクルまたは電圧/電流レベルを持つ他の期間508,510の循環に変更すべきかを判断することができる。また、エンドポイント検出512を用いて、図13に示すパルス化動作からDC動作516への切替をいつ行うべきかを判断することができる。言い換えると、図13の期間512を用いて、ウェハ20が図6に示される点にいつ到達したかを検出し、材料を急速に付着するための図13の期間516のプロセスをいつ変更して、図7の構造に到達すべきかを検出することができる。さらに、エンドポイント検出を用いて、新たな添加剤を溶液19にいつ添加すべきか、システム10または溶液19の条件をいつ変更すべきかを判断することができる。一例として、ウィンドウ506,512で得られるデータに基づく、増白剤、抑制剤またはその他の添加剤の流量を増量したり、流量を減量したり、あるいは漕19への供給から完全に排除することができる。もちろん、最も有用な方式においては、506,512などのエンドポイント検出ウィンドウを任意の電気めっきプロセスの終点で用いて、電気めっき動作を終了すべきとき(たとえば期間516の終点)を決定することができる。

【0070】

図13は、これも図1に示されるものと類似であるが、上記のシステムAとは異なるシステムBも示す。図13のシステムBにおいては、一部のクランプ18は電源28のある種の切替制御下に恒久的に結合されており、他のクランプ18はエンドポイント・コントローラ30の制御下に恒久的に結合される。このシステムB(連続監視システムと称する)を用いると、パルス化動作522〜534を開始して、図13の動作536などのDC動作を、電源28に接続されるクランプ18を介する割り込みなしに続けることができる。波形522,524,526,528,530,532,534,536を介するこれらのクランプ18を通じてウェハ20に電力を供給するのと時間的に平行に、図1の他のクランプ18を用いて、図13に示される期間520により、均一性、付着速度、不純物レベルおよびエンドポイント・パラメータの少なくとも一つを監視することができる。

【0071】

従って、図13のシステム10のエンドポイント検出は、図13の期間520により示されるように継続することも、あるいは図13のエンドポイント期間506,512により示されるように時間多重すなわち割り込みを行いながら実行することも、あるはその両方を行うこともできる。エンドポイント検出動作は図8ないし図12に前述される波形のうち任意の波形の任意の場所、あるいは図8ないし図12に示される任意の波形の間に配置することもできることに注目することが重要である。エンドポイント動作は、種々のパルス化サイクルの「オフ」サイクル中に低電流および低電圧検出により自動的に行うこともできる。さらに、図13または図1には特定的には図示されないが、本明細書で説明するエンドポイント動作をロボット制御の下で2チャンバ・システムにおいて実行することもできる。電気めっきをシステム10に類似の第1チャンバ内で行うことができる。しかし、システム10には電気めっきチャンバに近接して別のチャンバが含まれ、それによってロボットはウェハを電気めっきチャンバとエンドポイント検出(4点プローブ・チャンバなど)との間で往復させることができる。これは、エンドポイント条件が第2チャンバで検出されるまで続く。

【0072】

本発明は、特定の実施例に関して説明されたが、さらなる改良および改善が当業者には可能であろう。従って、本発明は、添付の請求項に定義される本発明の精神および範囲から逸脱しないこれらすべての改良を包含することを理解頂きたい。

【符号の説明】

【0073】

10…電気めっきシステム、11…ハウジング、12…内カップ、13…拡散器、14…陽極、15…ヘッド、16…ターンテーブル、18…クランプ、19…溶液、20…ウェハ、22…流出口、24…流入口、26…CPU(中央処理装置)、28…電源、30…エンドポイント・センサ、32…スイッチ、34…制御システム。

【技術分野】

【0001】

本発明は、一般に半導体製造に関し、詳しくは、半導体基板上に銅を電気めっきすることにより填込銅相互接続部を形成する方法に関する。

【背景技術】

【0002】

現在、半導体装置は、より高い性能を得るためにより高い電流密度を必要とする。また、装置の寸法は、このようにより高い電流密度を伝える場合にますます問題とされるような幾何学形状にまで小さくなりつつある。当技術においては、より高い電流密度と幾何学形状の縮小とに対応しつつ、同時に、エレクトロマイグレーション(electromigration)に対する充分なレベルの耐性、金属空隙化の軽減、ウェハ製造処理量の改善を維持しながら、なおかつ他の一般的な信頼性の問題を回避しなければならない。アルミニウムは、成熟した集積回路(IC)相互接続材料であるが、銅はIC相互接続部に用いるには比較的新しい材料である。

【0003】

基板上に銅(Cu)を付着する方法で最も有望な方法の一つに、電気めっきなどのめっき法の利用があげられる。電気めっきした銅は、集積回路(IC)用途に利用されるとアルミニウムに比べていくつかの利点を持つ。大きな利点は、銅がアルミニウム系の材料よりも抵抗が低いことで、そのために、より高周波の動作が可能になる。さらに、銅はエレクトロマイグレーション(EM)に関わる従来の問題に対する耐性がアルミニウムよりも高い。銅を利用する際のエレクトロマイグレーションに対する耐性が増大することで、半導体装置の信頼性に対する全体的な改善がなされる。これは、時間の経過と共により高い電流密度を持ち、さらに/あるいはEMに対する耐性が低い回路は、その金属製相互接続部に空隙または開路を形成する傾向があるためである。このような空隙または開路によって、装置が現場で、あるいはバーンイン中に壊滅的な故障を起こすことがある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平11−097393号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、ICの製造プロセスに銅を統合することによっても、新たな問題が起こり、これは信頼性あるいは大量生産に関しては、いかなる手段によっても完全に最適化できない。たとえば、印加電流または電位がきわめて高い電気めっき漕を用いてアスペクト比の高い開口部内にあまりに急激に銅を付着すると、実質的には直流(DC)モードにおいてのみ、銅相互接続部に空隙領域またはキーホールが形成されるという問題が起こる。このようなめっき条件においては、付着された銅は実際には、開口部の上部で剥がれて、増分的に付着される銅膜内に銅で囲まれた空気の領域すなわち空隙が形成される。また、銅の高電流密度でのDCモードのめっきにより、付着速度が高くなり、めっきされたCu薄膜内への不純物の電気めっきが良好に取り込まれないために、エレクトロマイグレーション(EM)に対する耐性が劣化した銅膜となる。

【0006】

さらに、銅を効率よく電気めっきするには、下層の薄膜の品質が大いに関係する。下層の銅シード膜が均一に付着しなかったり、不充分な量のシード材料を有する領域を含んでいると、銅はこれらの領域に均一に付着しなかったりして、ICの歩留まりおよびICの信頼性の少なくとも一つを低下させることがある。通常、下層のシード層品質に対する銅めっきの感度は、処理量の小さい低DCめっき法を用いると大きくなる。従って、高DC法が用いられようと低DC法が用いられようと、最終的な構造には一つ以上の重大な銅のめっきの問題が避けられないように思われる。

【0007】

そのため、充分な製造処理量を維持しつつ、同時に空隙の形成を軽減するか、あるいはなくすることができ、エレクトロマイグレーション(EM)に対する耐性を改善することができ、均一性を改善することができるなどの利点を有する銅相互接続部の電気めっき方法が半導体産業において必要とされる。

【0008】

電気めっきの信頼性、性能および歩留まりの問題に加えて、銅を付着するための従来の方法は、一定時間の付着を用いて基板上に銅を電気めっきすることを一般的に必要とする。通常、試験ウェハが一定の条件下で電気めっきチャンバ内で処理され、このプロセスが仕様または制御制約内で動作するか否かが判断される。システムがその制限内で動作する場合は、一定の時間の間に、後続の製品ウェハの一定時間付着処理を開始することができる。この試験ウェハプロセス制御方法は、後続の製品ウェハが、付着条件が時間が経過しても変わらないままでいるという希望的前提のもとに、仕様または制御制限内にあることを想定する。

【0009】

試験ウェハを処理し、試験ウェハが良好な結果を得る静的条件を決定し、継続してうまく行くという希望のもとでこれらの条件によりウェハを静的に処理するという方法全体が、時間の浪費であり、信頼性も乏しく、また高価でもある。従って、リアルタイムに電気めっきをその場で終了させる(エンドポイント動作する)ことができる、あるいは監視して、めっき動作をめっき中はコンピュータにより動的に制御することができる銅電気めっきシステムを提供することが有益である。これにより、試験ウェハの利用とウェハの廃棄が削減され、処理量がさらに最適化され、薄膜性能が改善される。

【0010】

本発明の目的は、アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供することにある。

【課題を解決するための手段】

【0011】

上記問題点を解決するために、本発明は、ウェハ上に銅層を形成する方法であって、ウェハを電気めっきチャンバ内に配置する段階であって、ウェハが上部誘電体面と、上部誘電体面の下方の平坦な表面に配置される底部トレンチ面と、底部トレンチ面下方の平坦な表面に配置される底部ビア面とを有する二重填込相互接続開口部を有し、電気めっきチャンバが少なくとも一つの電気コンタクトを通じてウェハに接続される制御システムを有し、制御システムがウェハに電力を提供する、段階と、第1期間の間、ウェハに対する電力を正にパルス化する段階と、第1期間に続く第2期間の間、ウェハに対する電力を負にパルス化する段階と、第2期間に続く第3期間の間、ウェハに対する電力を正にパルス化する段階とを備えることを要旨とする。

【0012】

一般に、本発明は銅電気めっきチャンバの陰極および陽極の少なくとも一つを制御して、銅電気めっき動作を介して半導体ウェハ上に形成される銅(CuまたはCu合金)相互接続部の品質を高めるための方法および装置である。パルス化された正および負の少なくとも一つの電流波形の様々なシーケンスが、銅電気めっきチャンバの陰極および陽極の少なくとも一つに供給される種々の随意の直流(DC)バイアス期間を包含することと共に、銅の均一性、銅のエレクトロマイグレーション(EM)に対する耐性、めっき処理量、銅空隙、銅の粒子構造やその他同様の特性の一つ以上に悪影響を与えうることがわかっている。

【図面の簡単な説明】

【0013】

【図1】銅材料を半導体ウェハ上に電気めっきするために用いられる電気めっきチャンバとそれに関連するコンピュータ制御システムを、断面図および電気ブロック図に混合して示す。

【図2】図1の陰極アセンブリ(すなわちウェハ、ターンテーブルおよびクランプ)の上面図である。

【図3】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図4】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図5】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図6】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図7】図1および図2のシステムを用いて二重填込構造内に銅を増分的に電気めっきする方法を、断面図に示す。

【図8】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図9】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図10】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図11】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図12】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【図13】銅の電気めっきの間に、図1の電気めっきチャンバの陰極アセンブリが制御されて、従来技術によるものよりも銅相互接続部の品質を改善する異なる方法をXY時間線内に示す。

【発明を実施するための形態】

【0014】

本明細書に教示される改善された銅電気めっき法は、本明細書の図1ないし図13を特定的に参照することにより、より良く理解頂けよう。

図1は、電気めっきシステムまたはチャンバ10の断面図である。チャンバ10は、チャンバ10の動作を電気的、化学的および機械的に制御するために用いられるコンピュータ制御システム34のブロック図に結合される。システム10は、チャンバ・アセンブリまたはハウジング11を具備する。ハウジング11は、時間の経過と共にチャンバ10から過剰な電気めっき流体を排出するための一つ以上の流出口22を有する。システム10は、流入するめっき流体19を受け入れるための流入口24を有する内カップ12をさらに具備する。この流体19には、増白剤、担体、レベラや同様のめっき添加剤のうち1種以上が含まれる。カップ12には、中央拡散器13が含まれることがある。拡散器13は、一般に、陽極14と、チャンバ10のウェハ20または陰極アセンブリとの間に多少の絶縁を行うために用いられる。図1の陰極は、ウェハ20、クランプ18やターンテーブル16のうち一つ以上を集合的に示す。また、拡散器13は、ウェハ20に対する流体の乱れを軽減し、溶液中の不純物/濃度の均一性または分布を改善するために用いられる。

【0015】

陽極14は、カップ12の底部と拡散器13との間にあり、図1には明示されない電源から電力を供給される。図1の陰極と陽極の両方の制御は、同一のコンピュータ34により行っても、異なるコンピュータにより行ってもよいことに注目されたい。陽極14は、一般に、めっき動作中に静止DCバイアスにより制御されるが、本明細書に教示される陽極14は、パルス化された直流(DC)により制御することも、あるいは、電気めっき期間中に時間の経過と共に、DCおよびパルス化電流(I)の少なくとも一つまたは電圧(V)との間で切り替えて、電気めっき速度(すなわち処理量)を変更したり、銅薄膜の粒子寸法に影響を与えたり、あるいは電気めっき銅薄膜のその他の特性またはプロセスを改変することもできる。本明細書においては、DC、電力、電圧および電流を交換可能に用いることができるが、それはこれらの要因すべてが電力に多少の関連を持つためである。

【0016】

従って、本明細書においては陰極の電気制御が教示される(図8ないし図13)が、これらの方法を一定の環境において図1の陽極に一般的に適応することができるということに注目することが重要である。システム10は、ターンテーブル16と一つ以上のクランプ・フィンガまたはリング18を有するヘッド15をさらに具備する。アセンブリ全体(ウェハ20、クランプ18およびテーブル16の内一つ以上を含む)が、システム10の陰極として電力を供給される。陰極アセンブリの構成部品は、通常、このようなバイアスが可能な白金または白金チタンで作られる。ターンテーブル16は、通常は、機械、コンピュータやモータで制御されており、めっき中のウェハの回転を可能にするが、この回転は特定のめっき動作中には必ずしも必要ではない。

【0017】

陰極(たとえば、ウェハ20、クランプ18およびターンテーブル16のうち一つ以上)は、図1の制御システム34を用いて電力を供給されたり、さらに/あるいは電気的に監視される。制御システム34は、任意の種類のコンピュータ制御装置であるが、一般的には、ある種の中央処理装置(CPU)26である。CPU26は、スイッチまたは論理32を制御し、これにより、一つ以上の電源28から陰極にどのようにして、いつ電流や電圧(すなわち電力)が提供されるかを制御する。電源28(一つ以上の電源の場合もある)は、直流(DC)レベルの電力または広範囲の電流や電圧レベルのパルス化DC波形を提供することができる。さらに、電源28は、鋸歯電力波形、正弦波形、対数波形、指数波形などの交流(AC)波形や、その他の種類の電力/時間制御を図1の陰極に与えるよう設計することができる。また、電源28は、オンタイムまたはオフタイムの異なる電力強度やデューティ・サイクルを有する方形波波形を提供することもできる。さらに、電源28は、負または正の極性あるいはそれらの組み合わせのいずれにおいても、これらの波形または電流/電圧/電力レベルのうち任意のものを提供することができる。この電力は、電源28を介して図1のクランプ18に送られる。

【0018】

電力を供給するために用いられるのと同じクランプ18は、電気めっきの監視を実行するためにエンドポイント検出センサに随時結合されるのと同じクランプである。別の形態においては、制御のために回路30によってのみ結合され、電源28により制御のためにではなく結合される、電源専用のエンドポイント・クランプまたはプローブ18を用いて、ウェハ20の電気特性を定期的または継続的に監視して、その場での電気めっき制御を行うことができる。一方で、電源28に結合される他のクランプ18がウェハ20の電気めっきバイアスを実行する。

【0019】

クランプ18または他のコンタクト機構を通じて、装置30がいかに機能するかの例として、センサ30またはそれに制御される電源がウェハ20に一定の電圧を印加し、それに由来する電流を測定する。それから得られるI−Vデータを用いて、増分的に付着するCu薄膜の抵抗値Rを決定することができ、それによってRの推定値がR=σl/Aを介してCu薄膜の厚みに相関される。I,Vを用いてRを決定することができるが、Cuの導電率(σ)または抵抗率の逆数が既知であり、さらに任意の二つのエンドポイント測定クランプ18の間の有効長(l)はチャンバの設計により一定であるので、Aだけが唯一の変数となる。Aは、電流が流れる断面積であり、付着するCu薄膜の厚み(t)の直接的な関数である。従って、Aが増大すると、この増大は厚みが対応して増大することによるものであり、それによって、RをAにマッピングしてエンドポイント検出に対応することができる。

【0020】

別の形態においては、回路30がウェハ20に一定の電流(I)を印加してそれに由来する電圧(V)を測定することもできる。このI−VまたはV−Iプロセスを同じクランプ18内に電源28と共に時間多重したり、あるいは別々の専用エンドポイント・クランプ18に付属させることもできる。時間の経過によるウェハ20の電気特性を測定することにより、ユニット30は、電気めっきのプロセスをいつ終了させるかを正確に決定することができる。これは、時間の経過と共にウェハ上に付着される導電性銅薄膜の厚みを測定されるウェハ抵抗値またはその他の被測定電気特性に容易に相関することができるためである。また、ウェハ20をウェハ表面全体で、あるいはいくつかの異なる対の個別に配置されるクランプ18の間で、複数の方向から監視することができる。これにより、ウェハ全体の抵抗値の二次元マップ(すなわち電気めっき厚の2-Dマップ)をコンピュータにより得ることができ、CuまたはCu合金の電気めっき中にリアルタイムの均一性データを生成することができる。このような均一性情報はCPU26が用いて、付着中の電力20を最適化し均一性を改善することができる。あるいは、均一性データを用いて、保守または修理のために機械を随時停止させることができる。

【0021】

従って、システム10の動作中に、めっき液19が流入口24を通じてカップ12内に入り、流出口22から出る。陽極14が酸化され、銅が制御システム34により与えられる信号を介して陰極上にめっきされる。めっき中は、制御システム34が陰極および陽極の少なくとも一つの電力を制御し(すなわち時間の経過と共に電流および電圧の少なくとも一つの供給を選択的に変更することにより)、ウェハ20上に付着される銅の品質と特性とを改善する。めっきプロセスのエンドポイント検出およびさらなる制御を、エンドポイント・センサおよび回路構成30を用いてその場で実行することもできる。

【0022】

要するに、陽極14、クランプ・フィンガ18および基板ウェハ20(すなわち陰極)は、一つ以上の制御システム34を用いてバイアスされ、基板20に銅でめっきをする。このとき、コンピュータ・システム34を介して要素14,18および20の少なくとも一つをバイアスする方法は、ウェハ処理量、銅空隙形成の軽減または削除、Cuピンチオフの軽減、薄膜均一性の改善やエレクトロマイグレーション(EM)に対する耐性の改善のうち一つ以上に大きな影響を与える。一般に、本明細書の図8ないし図13に後述される、一つ以上の電気めっき陰極バイアス法を用いると、薄膜特性の改善、信頼性の改善や性能の強化が達成されることがわかっている。

【0023】

図2は、図1において断面図として前述された陰極アセンブリの上面図である。図2は、ウェハ20、ターンテーブル/ヘッドプレート16および6個のクランプ18を示す。図2には6個のクランプが図示されるが、図2の6個のフィンガ・クランプの代わりに一つの大きなクランプ・リングを用いることも可能であることに留意されたい。また、図2のウェハ20の周縁表面の回りに任意の数(たとえば3個、10個、40個、100個など)のフィンガ・クランプを用いることもできる。図2は、図2の6個のクランプのうち、任意の二つ以上のクランプの間でエンドポイント電気データが得て、時間の経過と共にウェハ20の種々の地点または経路に形成される銅の厚みを表す二次元めっき均一性マップを導くことができることを示す。異なる位置により多くのクランプが用いられると、均一性マップの解像度がより高くなることは明白である。図1および図2は一種の電気めっきシステムを示し、それにより、多くの異なる構造または要素を図1および図2のシステムに追加または削除することができる。一方で、図1および図2を本明細書の図3ないし図13の教義と組み合わせて充分に活用することもできる。

【0024】

一般に、図1および図2に示されるシステムを用いて、図3ないし図7に示されるのと同様に、ウェハ20上に時間の経過と共に銅またはその他の金属材料を電気めっきすることができる。このような銅または金属めっきは、図8ないし図13に関して本明細書に説明される一つ以上の方法を用いて、図1の陰極に(および/または図1の陽極14にも)電力を供給することによって実行することができる。半導体ウェハ上に改善された銅の一重填込(single inlaid)や二重填込(dual inlaid)相互接続部を形成するために用いられる特定の方法は、以下の図3ないし図13を詳細に参照することにより、さらに良く理解頂けよう。

【0025】

図3ないし図7は、時間の経過と共に銅電気めっき材料により形成される二重填込集積回路(IC)構造を断面図に示す。この電気めっきは、図1および図2に図示される装置またはそれに類似の装置を用いることにより実行される。図3は、半導体構造100(たとえば、より大型のウェハ20上に形成される多くの構造のうちの一つ)を示す。半導体構造100は、一つ以上の基層102を備える。基層102は、通常、好ましくは半導体ウェハである基板を具備する。図3の層102の底または基部として設けられる基板材料は、シリコン、ゲルマニウム・シリコン、ガリウム・ヒ素、ゲルマニウム、その他のIII-V族化合物、シリコン・カーバイド、絶縁体上シリコン(SOI:silicon on insulator)材料または同様の基板材料のうちの一つまたはそれ以上である。

【0026】

この基板材料上に図3の領域102が形成される。領域102は、通常、フォトリソグラフィック・パターニングおよび選択的エッチングされて、基板材料上やその中に半導体装置を形成する導電層、半導体層および誘電体層の少なくとも一つの混合物である。たとえば、領域102は、窒化シリコン、二酸化シリコン、テトラエチルオルトシリケート(TEOS:tetraethylorthosilicate)ガラス、ボロホスホシリケート・ガラス(BPSG:borophosphosilicate glass)、低k材料、キセロゲルなど、種々の酸化物や窒化物のうち一つ以上を含むことがある。領域102には、ゲルマニウム・シリコン、多結晶シリコン、非晶質シリコン、ドーピング多結晶シリコンおよび同様の材料などの半導体層が含まれることもある。これらの可能性のある層に加えて、多層領域102には、耐火性シリサイド、耐火金属、アルミニウム、銅、タングステン、これら材料の合金、導電性窒化物、導電性酸化物または同様の金属構造などの導電性または金属層が含まれることもある。

【0027】

図3の層102上に、このような金属相互接続構造104を二つ図示する。一つの形態では、領域104は填込銅相互接続部であり、図3の装置100の導電性相互接続部を形成する。他の形態では、層104は、一つ以上のアルミニウムやタングステン領域である。一般に、相互接続部104は、図3の層102内部または下方に形成される種々のアクティブおよびパッシブの少なくとも一つの電気構成部品を電気的に相互接続するために配置される。

【0028】

層102、104上に、エッチ・ストップ層106がある。エッチ・ストップ層は、一般に窒化シリコン層、酸窒化物層または高シリコン窒化シリコン層である。エッチ・ストップ層106上には、レベル間誘電体(ILD:interlevel dielectric)部分108があり、これは、テトラエチルオルトシリケート(TEOS)ガラス、フッ素ドーピングTEOS(f-TEOS)、オゾンTEOS、ホスホシリケート・ガラス(PSG:phosphosilicate glass)、ボロホスホシリケート・ガラス(BPSG)、低k誘電体材料、窒化物、スピンオンガラス(SOG:spin on glass)またはその複合物のうち一つ以上の材料で形成されるのが一般的である。層108上には第2エッチ・ストップ層110があり、これも反射防止皮膜(ARC:anti-reflectivecoating)として機能し、層106に関して上述されたのと同じ材料で作成されるのが一般的である。ある形態では、層106.110は、酸窒化シリコン、窒化シリコン、高シリコン窒化シリコンや同様の誘電性材料の複合物である。層110上には、別のILD層112があり、これは上記の層108と類似の層である。

【0029】

図3は、層106〜112が一つ以上のリソグラフィック・パターニングおよびエッチ・プロセスによりリソグラフィック・パターニングおよびエッチングされて、填込または二重填込構造を形成する様子を示す。図3は、特に、層108を貫通して形成される少なくとも二つのビアと、層112を貫通して形成される一つ以上のトレンチ領域とを有する二重填込構造を示すが、層112内のトレンチ領域は図3の層108内の二つのビア間を接続する。図3の二重填込トレンチ構造は、底部トレンチ面117と、誘電体層112の上面である上部誘電体面115と、金属相互接続領域104の露出上面である底部ビア面119とを有する。

【0030】

図3は、二重填込トレンチ構造内および上部誘電体面115上にバリア層114が形成される様子を示す。一般に、層115は、1000オングストローム未満の厚みを有する層であり、銅が隣接する誘電領域112、108内に拡散して悪影響を与えることを防ぐことのできる任意の材料で作られる。詳しくは、銅バリア層として用いられる材料には、窒化タンタル(TaN)、窒化チタン(TiN)、チタン・タングステン(Ti/W)、それらの複合物や同様の材料などがある。場合によっては、誘電体材料108,112が選択または表面処理されて、バリア層が全然必要とされないか、あるいはそれによって層108,112の表面部分そのものがバリアとして働くこともある。

【0031】

図3は、銅、金属または銅合金シード層116が、任意のバリア層114の上面に形成される様子を示す。ある形態では、層116はスパタリングまたは物理的蒸着(PVD:physical vapor deposition)により形成される銅層である。別の形態では、層116は化学蒸着(CVD:chemical vapor deposition)を用いて形成される。場合によっては、PVDプロセスとCVDプロセスを組み合わせて用いることもある。いずれの場合も、層116は、銅によって構成される層であるのが一般的であり、通常2500オングストローム未満の厚みを有する。無電解めっきなど他の方法を用いて図3のシード層116を形成することができることに留意されたい。

【0032】

図3に示されるように、一般的なPVDプロセスは二重填込相互接続構造の全露出面および隅部上で完全に均一または同形ではないシード層116を形成しやすい。実験により、PVDシード層116には、図3に図示されるようにシード空乏部116aが通常は含まれることがわかっている。シード空乏部116aは、シード材料をほとんどあるいは全然含まない露出相互接続面の領域である。領域116aにシード材料が含まれない場合、これは普通は、少なくとも部分的に互いに分断された銅の不連続な塊または島である。シード空乏部116aは、図3に示されるように、底部トレンチ面117と底部ビア面119との間に位置する側壁上に最も起こりやすいことが実験的にわかっている。

【0033】

図3には、より薄いシード部116bも示される。より薄いシード領域116bは、一般的には連続した薄膜(領域116aのように島または塊ではなく)であるが、上部誘電体面115上のシード層の大半の他の部分よりも薄いシード層領域である。領域116bは、一般に、上部誘電体面115と底部ビア面119との間のトレンチ構造の側壁部分や底部トレンチ面117と底部ビア面119との間の側壁表面部分上に発生する。また、底部ビア面119を覆うシード層部分は、上部誘電体面115上に形成されるシード層の厚みより通常は薄いことがわかっている。図3では、より厚いシード層部分と厚い隅部116cをPVDシード層116内に形成することができることも示される。

【0034】

一般に、領域116a,116b,116cの形成は、図4ないし図7に示されるように、後の電気めっき動作を複雑にすることがある。電気めっきシステムの陰極をバイアスするための異なる方法により、図3の領域116a,116b,116cが存在することで起こる種々の悪影響を防ぐことができることがわかっている。領域116a,116b,116cに由来するめっき上の不利益を軽減することがわかっている特定の電流、電圧および電力波形の少なくとも一つを、図8ないし図13に関して以下に特定的に図示および説明する。

【0035】

図3に示される構造100の形成後、ウェハ20(構造100を含む)が図1および図2に示されるシステム10内に配置される。このウェハ20は、次に図1に示されるように電気めっき液19に露出される。液19への露出中は、図8ないし図13のうちの一つ以上またはそれらの組み合わせにおいて示すように、制御システム34が(一つ以上のクランプ18を介して)ウェハ20に供給される電力、電流または電圧の量を制御して、本明細書の図4ないし図7を通じてウェハ20上に増分的に形成される電気めっき銅薄膜の品質を改善する。

【0036】

詳しくは、図4は、図3に示される二重填込トレンチ構造の表面全体に亘り実行される銅電気めっき動作の開始段階を示す。図4においては、ウェハ20上に増分的に銅(Cu)層118aを電気めっきするために、高電力電気めっきプロセスが用いられている。図4が電気めっき中の初期の時間帯に比較的高レベルの電力を図1および図2のシステム10内で陰極(ウェハ20)に与えると結果が得られる高電力電気めっきプロセスである。高電力電気めっきプロセスは、図3に示されるシード層116の表面上に高速の銅付着を行う。高い付着速度に加えて、高電力付着プロセスにより、シード層を欠くあるいはシード層成分が実質的に少ないシード空乏部116a(図3参照)上へのめっきが容易になる。低電力の電気めっきプロセスでは、図3のこれらのシード空乏部116aを充分にめっきせず(すなわち低電力めっきでは受認可能な速度でこれらの領域にめっきしない)、そのため銅相互接続部内に空隙が形成されることが実験的にわかっている。従って、ここでは高電力の初期めっき期間を用いて、図3のシード空乏部116aが存在しても銅相互接続部の品質を改善し、さらに初期のCu付着をより高速にすることにより処理量を改善する。シード層116と新規に電気めっきされた銅層118aとは破線で隔てられており、特に、シード層116が銅であり電気めっき層118aも銅である場合に、シード層とその上の電気めっき層の間の接合が、走査電子顕微鏡(SEM:scanning electron microscope)断面において識別することが不可能であることを示す。

【0037】

高電力電気めっき期間の上記のような利点にも関わらず、高電力めっき期間は一般的に、エレクトロマイグレーション(EM)に対する充分なレベルの耐性を改善または提供するために、窒素、炭素およびイオウなどの不純物を充分にCu薄膜内に取り込むことがない。従って、図4の領域118aは希望するほどにはEMに対して耐性をもたないことが多い。さらに、図4に示されるように、高電力めっき期間があまりに長い間維持されると、図3のより厚い領域116cの存在により、結局は、銅相互接続構造内にピンチオフまたは空隙ができてしまう。言い換えると、高電力電気めっきは表面116c上にあまりに迅速にめっきするので、図3の二つの隣接領域116cはビアが埋まる前に一緒にめっきしてしまって、ピンチオフが起こることがわかっている。ピンチオフによりビア領域付近の相互接続構造内に空隙すなわち欠如が起こる。従って、高電力サイクルを用いる銅の電気めっきは、処理量を改善しシード空乏部116aの存在を補償するが、高電力のプロセスが初期期間にあまりに長い間続くと、ピンチオフおよび空隙が起こりEM耐性が低下すると判断された。

【0038】

高電力電気めっきプロセスには問題があったので、低電力電気めっきで上記の問題が解決できるか否かが検証された。実験の結果、電気めっき処理の間に最初に用いられた低電力電気めっきプロセス(以下、初期段階と呼ぶ)は、図3のシード空乏部116a上に充分にめっきすることはできなかったが、銅薄膜内への不純物の取り込み(たとえばイオウ、窒素、炭素など)が改善され、それによって最終的な銅薄膜におけるエレクトロマイグレーション(EM)に対する耐性が改善されたことがわかった。従って、低電力初期処理は、空乏領域116aの存在がシード形成において全体的に回避できれば有益である。このような領域116aは、シード層116がPVD層ではなくCVDシード層であれば全体的に回避することができる。従って、低電力電気めっき初期動作は、特に、図3の空乏領域116aの発生を大幅に低減するCVDシード層が用いられるならば、場合によっては有利である。

【0039】

低電力電気めっきの上記の利点とは対照的に、環境によっては電気めっきの初期段階における低電力期間が、図1のシステムを用いても充分なウェハ処理量を提供しないことがある。また、低電力プロセスの付着速度が高電力プロセスより低くても、領域116c上で図4に図示されるほど付着の均一性が改良されない。従って、低電力電気めっき処理も高電力電気めっき処理も、図3の領域116cの存在により、填込ビア領域内にピンチオフおよび空隙を最終的に起こすこともある。そのため、付着中に低電力と高電力の電気めっきを交互に行った電気めっきプロセスは、空乏領域116aを解決し処理量を高めるという高電力の利点を保持しつつ、EM耐性の改善された特性という低電力の利点を備えることがわかっている。しかし、低電力/高電力の電気めっきプロセスを組み合わせて形成される相互接続部も、依然としてピンチオフを起こす可能性がある。従って、高電力の種々のサイクルを低電力の種々のサイクルと組み合わせることにより、改善された銅相互接続構造を形成することができ、それにより処理量、シード空乏部空隙耐性およびエレクトロマイグレーション(EM)耐性のバランスを取る、すなわち時間と経過と共に最適化することができるが、空隙は依然として問題であることが認識された。そのために、高電力/低電力を組み合わせためっきサイクルを採用した後でもピンチオフにより起こる空隙の問題を解決するためには、めっきプロセスに対してさらに改良を加えることが必要であると認識された。

【0040】

図4は、高い正の電力サイクルと低い正の電力サイクルを交互に実行することにより形成して電気めっきを開始しても、領域116c上に空隙が依然として起こりやすい様子を示す。このような空隙を排除または軽減するためには、負にパルス化された電力(交流(AC)、パルス化DCまたは直流(DC)のいずれかを介して)を図1のウェハ20に対して、1回以上、上記の正の高電力サイクルと低電力サイクルとの間の種々の間隔において印加するべきであるということがわかった。ウェハ20にある種の負の電力サイクルを定期的にまたは随時印加することにより、図4に示す層118aのピンチオフ「危険」部分を構造から効果的に排除することができることがわかった。領域116cのこのような負の電力サイクル修正を図5内の結果として得られた層118bにより示す。一般に、負の電力を図1のシステム10の陰極に印加することにより、電気めっきプロセスが反転され、すでにウェハ上に付着された電気めっき材料がウェハから除去すなわちスパタリングされる。この負の電力除去段階の間、電気めっき材料は領域116aおよび116bの少なくとも一つの上のめっきを介して形成された厚いほうの領域(電流密度が低いほうの領域)からよりも・層118aの厚いほうの(電力密度が高いほうの)領域(たとえば領域116c)から、より高速で除去される。全体的な結果は、シード116上に、図5に示すようなより同形の増分層118bが形成される。従って、図4の高電力正電力や低電力正電力サイクルと組み合わせて負の電力サイクルを用いると、より厚い領域116cの存在を補償する逆めっき特性を利用することにより相互接続開口部内に空隙を起こす可能性が、大幅に小さくなる。言い換えると、負の電力を銅付着中に特定の間隔で供給することで、電気めっき均一性特性を改変することがわかり、適切な順序で実行すれば(種々の適切な順序に関しては図8ないし図13を参照)、相互接続開口部内の空隙を軽減できる可能性がある。

【0041】

図6は、高電力ACおよびDC正サイクルの少なくとも一つと低電力ACおよびDC正サイクルの少なくとも一つを交互に、さらに補正用負ACおよびDCサイクルの少なくとも一つを随時加えて、最終的に図3の相互接続構造を最適な方法で電気めっきおよび充填する様子を示す。従って、この最適充填は図6の銅層118cにより示される。銅付着中に、様々な正高、正低および負電力サイクルと極性を特定的に実行する方法は、相互接続の品質を最適化することがわかっているが、これについては本明細書の図8ないし図13において、より詳細に説明する。一般に、本明細書に教示されるシステム10に電力を供給する方法により、種々の領域116a,116b,116cのうち一つ以上の領域を有するシード層116から歩留まりと品質とを改善して、相互接続部がめっきされる。従って、図1のシステム10の陰極に対する電位、電力または電流強度ならびに極性(すなわち負または正)を時間の経過と共に制御し交代することにより、エレクトロマイグレーション(EM)に対する耐性を改善し、均一性を強化し、ピンチオフを軽減または除去し、ウェハ処理量を増大し、空隙を作らずに、図7の全面めっき層118を形成することができる。

【0042】

図7は、電気めっきプロセスのある時点において、銅118cが相互接続開口部を完全に充填する様子を示す。空隙の危険性がなくなった後は、急速な高電力DC電気めっきサイクルを開始して、それにより処理量を高めることができる。従って、図7において既存の銅材料118c上に付着された銅材料118dが、高電力、正D C電気めっきプロセスまたはその他の高処理量波形を用いて付着される。その結果、相互接続開口部を完全に充填し、集積回路(IC)産業において大量の高い歩留まりでの用途に関して最適化され改善されている銅薄膜が得られる。また、ここでの一つ以上のプロセス・サイクルとして、ビア内ではより速い速度で付着し、上部誘電体面115上では低い存在しない速度で付着する、ボトムアップ充填プロセスを用いることも可能である。このようなボトムアップ充填サイクルを用いると、本明細書に教示されるように改善された銅相互接続部の製造を行うこともできる。

【0043】

図3ないし図7は、電気めっき中に図1のチャンバ10の陰極および陽極の少なくとも一つに印加される電力の種類、強度および極性を制御することにより、エレクトロマイグレーション(EM)耐性を改善し、ウェハ処理量を充分にとり、空隙およびピンチオフを大幅に軽減して半導体ウェハ上に銅相互接続部を形成することができることを示す。

【0044】

図8ないし図13は、図3ないし図7に関して前述された種々の改良結果の一つ以上を得るために、制御システム34を介して図1の陰極に与えられる特定の電力シーケンスを示す。

【0045】

詳しくは、図8は、図1の陰極(すなわちウェハ20)が電気的に制御され、図3ないし図7に関して説明された改善された銅相互接続部の形成を行うための、一つの可能なシーケンスを図示する。図8はXY図であり、縦のY軸は電流(I)をアンペアで、横のX軸は時間を秒で表す。図8は、縦軸の電流を示すが、本発明の精神および範囲から逸脱することなく、Y軸として電流、電流密度、電圧または電力のいずれかを図示することができるということに注目することが重要である。言い換えると、本明細書で用いられる場合に、電流、電流密度、電圧または電力は、一般的に交換可能な数量または用語である。

【0046】

図8は、図3に示されるようなシード空乏部116aを持たない化学蒸着(CVD)シード層116と共に利用すると最適な陰極電力シーケンスを示す。CVD付着シード層は、物理的蒸着(PVD)またはスパタリング・プロセスを用いて形成されるシード層と比較して、シード空乏部116aを起こしにくいことが実験的にわかっている。このような空乏部116aが起こりにくいために、低電圧正DC初期段階/サイクル201を図8の左側に示すように用いる。低電圧初期段階201は、より多くの量の不純物を電気めっき銅薄膜内に取り込み、それによってエレクトロマイグレーション(EM)耐性が改善されるので、CVDシードについては有益である。

【0047】

一般に、通常の電気めっきプロセスに関して、初期段階201は約0.5ないし3アンペアの間の正DC電流を利用する。図8は、段階201の期間の間は電流が1アンペアに設定されることを特に図示する。一般に、この初期段階201は、継続時間にして数秒から約1分間の間は継続することができる。

【0048】

ある程度の銅材料がウェハ20上に付着される初期段階201が終了すると、正のパルス化電力段階212が開始される。図8は、正のオン電流202とオフ電流204の交互期間が、期間212の間にウェハ20に対して図1のコントローラ34によって与えられる様子を示す。期間212には、一つ以上のオンまたはオフのパルスが含まれ、一般的には約1ミリ秒(ms)から1秒の間継続する。好適な実施例においては、期間212における正パルス202のオン期間202は継続時間にして約7.5ミリ秒であり、期間212におけるオフ期間204は継続時間にして約0.5ミリ秒である。他の継続時間または他のデューティ・サイクルを図8のオン・パルス(202)とオフ・パルス(204)に関して用いることができることに留意することが重要である。図8は、サイクル212のオン期間202の間に提供される電流または電力レベルが約6アンペアであることを示す。一般に、期間212のオン期間202の間の電力レベルは、期間201の間の電力レベルよりも高くすべきである。このように、電力を高くすることにより、図1の溶液19内の添加剤がめっき中に充分に活性化される。しかし、オン期間202中の電力レベルは、添加剤により得られる有益な機能が禁止されるほど大きくしてはならない。このために、期間212における図8の電力レベルは、溶液19の組成と、使用される電気めっきシステムの種類とにより可変する。

【0049】

初期段階201と正パルス電力段階212の後で、ウェハ20は図8上に示される図4内のものと同様の形状を示す。従って、これまでに付着された銅または銅合金材料は、一般に、高い全体付着速度で付着されているが、相互接続開口部内に複合シードおよび上層の電気めっき層が非同形的に付着されるように付着された可能性が高い。前述のように、この非同形的な正電力付着が続くと、銅相互接続部はピンチオフに伴う空隙の問題をはるかに起こしやすくなる。さらに、低電力初期段階201は、空乏部116aがあると(PVDシード層に関しては可能性が高い)、その上にめっきすることが困難になる。領域116aが存在する場合は、サイクル201を用いる代わりに期間212を交互に用いて、領域116a上に最初にめっきする。しかし、低電力プロセスを用いると、不純物の取り込みが一般的に改善されるので、可能であれば初期段階201を用いると、エレクトロマイグレーション(EM)に対する耐性がそれに応じて改善される。

【0050】

期間201および212の少なくとも一つに対する長期の露出に伴う空隙を最小限に抑えるために、正パルス化期間212を結果的に終了させて、負パルス化期間214を開始する(図8の中央を参照)。負パルス化期間214の総合的な継続時間は、一般に約0.2ミリ秒から1秒の間である。図8において、負パルス化期間214がウェハ表面から銅を剥離すなわち除去する。銅は、ウェハの銅層の高電流密度(厚い)部分からより高い速度で除去される。この銅除去により、複合シードおよびめっき済みの銅薄膜の側壁プロフィルが平らになり、図4に示される「ピンチオフ」の危険性を減らし、図5に関して図示および説明されたより均一な電気めっき銅薄膜プロフィルを生み出す。

【0051】

銅の全体的な正の厚みがウェハ20の上に期間の間に形成されるようにするためには、期間212の間に付着される銅の量は、期間214の間に除去される銅材料の量よりも一般的に多くなければならない。従って、期間212を期間214よりも継続時間が長くするか、さらに/あるいは、期間212は期間214の間に与えられる電力の絶対値よりも大きな平均的絶対値の電力をウェハに与えなければならない。期間214に関しては、期間214の総合的なオン時間206は約0.5ミリ秒であり、オフ期間208は約0.5ミリ秒である。しかし、付着される銅の全体量が時間に亘り除去される銅の量を超えていれば、期間214において任意のパルスのデューティ・サイクルまたは継続時間を用いることができる。

【0052】

また、図8は、オン期間206の間の負パルスの強度が、約負の4アンペアであり、付着される銅がこの期間中に除去される銅の量を超えていれば、電源が許すだけの大きさとすることができる様子を示す。一般に、銅を除去して、図5に全体が示されるプロフィルを作成することができれば、任意の強度の負パルス電流を用いることができる。従って、他のデューティ・サイクル、他の切換周波数、同期または非同期のオン/オフ・パルス、継続時間と電力レベルの可変する他のパルスなどを図8ないし図13において本明細書に教示されるパルス化期間の間に用いることができる。

【0053】

負パルス化期間214が終了すると、図5に図示されるのと同様の相互接続開口部が図1のシステム内に出現する。少なくとも1回の正パルス化期間212と1回の負パルス化期間214の後で、図1の制御システム34は任意の回数の同期または非同期順序で任意の回数だけ、サイクル212と214の間で交代を続行する。従って、正と負のパルス化サイクル212,214の任意の組み合わせ、順序および回数の少なくとも一つを用いて、本明細書に教示される相互接続開口部を充填することができる。一般に、図6の構造が空隙を起こさない方法で、前述の目標の厚みまで充分に形成されるようにするために充分な回数の正と負のパルス化サイクル212,214が実行される。

【0054】

図6の相互接続開口部が図8の期間201,212,214の任意の組み合わせを用いて充分に充填された後は、処理量の観点から、図8の右側の期間210により示されるように、ウェハ20に高いDC電位で給電することが望ましい。期間210の間は高電力DC電位を用いることにより、銅層の最上部(たとえば図7の領域118d)が空隙の危険を起こさずに高速で付着されて、それにより処理量が改善される。

【0055】

図8の期間210が終了すると、ウェハ20が図1のシステムから取り出されて、化学機械研磨(CMP:chemical mechanical polishing)動作に移され、空隙が軽減または除去され、信頼性が改善され、さらに/あるいは性能が強化された二重填込相互接続構造の形成が終了する。図8のプロセスは、本明細書に教示される他のプロセスと同様に、現在は、集積回路(IC)の基板上で複数の個別の積層された冶金層上に順次実行することができる(たとえば、この方法を用いてIC上に7層以上の銅相互接続部を作成することができる)。

【0056】

図8のプロセスにおいて、低電力DCの長期間である初期段階201だけでは、シード層116を形成するためにPVDプロセスを用いた際に現れやすいシード空乏部116a上にめっきするには充分とは限らないことが発見された。シード層116の領域116aが適切に電気めっきされないと、望ましくない側壁空隙が図3ないし図7の相互接続構造のビア部分に形成することがある。従って、領域116aがPVD付着シード層内に起こりやすいので、図9の電力シーケンスは、PVDシード層116と共に用いる場合には、図8よりも適していることが多い。しかし、図8または図9のプロセスのいずれも、任意の方法で形成される任意のシード層116と共に用いることもできる。

【0057】

図9は、増大DC電流サイクル254,256を用いて銅層を付着する前に、高電力正パルス化サイクルを用いる初期段階252の利用を示す。高電力正パルス化サイクルの初期期間252を用いて、図3のシード空乏部116a上に有効に電気めっきを行うことができることがわかった。この期間252は図3に示される空乏シード部116a,116b上への銅の成長のための核形成段階として機能する。数ミリ秒から数秒の期間の後で、図8に前述された随意の負パルス化期間214を間欠的に用いて正パルス化期間252の中で空隙が形成される確率を小さくすることができる。段階252による正パルス化処理(それに混合される随意の負パルス化を含む)の後で、低電力正DC電流が期間254の間ウェハ20に印加される。これは薄膜成長段階として機能し、図8の初期段階201と同様に作用する。

【0058】

図9の期間254などの低電力電気めっき期間により、より大量の不純物(たとえばイオウ、炭素および窒素)が銅薄膜内に取り込まれて、それによってエレクトロマイグレーション(EM)に対する耐性が改善されることがわかった。低電力正DCプロセスはシード空乏部116a上にめっきするには不充分であり、場合によっては空隙を作り出すことがわかっているが、1期間以上の低電力正DC処理期間254を用いて(1回以上の正パルス化電力制御シーケンスにより形成される)図5の構造の上部にめっきすることは有益である。これは、一般にエレクトロマイグレーション耐性が改善されるためである。空隙や銅空乏部の危険性はパルス化時間シーケンス252によってすでに克服されているので、空隙および空乏部が期間254の間に起こり悪影響を及ぼすことはない。

【0059】

しかし、期間254の間の電気めっきによりエレクトロマイグレーション(EM)耐性は改善されるが、期間254の間の電気めっきによりきわめて低速でウェハ20の表面上に銅がめっきされる。従って、処理量を高めるには、図9のプロセスを、図9の期間256により示される高電力正DC処理段階まで最終的には進行させて、それにより処理量を補い、なおかつ期間254によるエレクトロマイグレーション上の利点を利用することができるようにする。また、より高い不純物濃度が電気めっきの後で必要になる場合は、付着後にこれらの不純物を銅薄膜内にイオン注入して熱アニーリングすることができる。従って、図1の制御システム35が図1の陰極および陽極の少なくとも一つを制御する図9に示されるプロセスにより、半導体ウェハ上に図7に図示されるのと同様の改善された二重填込銅相互接続構造が得られる。この場合も、図9に示される特定の電流、電圧、期間およびデューティ・サイクル・オン/オフ・パルス幅および均一性などを調整して、可変するめっき漕組成物および装置に対応したり、さらに/あるいは可変する処理結果を生み出すことができることに注目することが重要である。

【0060】

図10は、図8および図9に関して前述されたパルス化時間シーケンス252,212,214などの任意のものと置き換えるために用いられるパルス化時間シーケンス268を示す。さらに、時間シーケンス268を、本明細書において電気めっきに用いられる任意の他の種類のDCおよびACの少なくとも一つの正および負の少なくとも一つの電力時間シーケンスと共に組み合わせて用いることができる。図10では、シーケンス268が可変する継続時間や可変する電流強度のオン・パルスによって構成されることを示す。前述のように、高電力パルスおよび低電力パルスは、材料を充分にめっきする能力に変動があり、図3の領域116a,116b,116c上での核形成およびその後の横方向の薄膜成長に影響を与え、処理量、エレクトロマイグレーション(EM)耐性、空隙の軽減、粒子構造などに対する効果が変動する。従って、より短い高電力オン・パルス262とより長い低電力オン・パルス266とを組み合わせてオフ期間264により隔てることが、ある用途においては有益であることが発見された。図10に示される電力シーケンスは、負パルス・シーケンス、DCシーケンス、ACシーケンス、パルス化DCシーケンスまたは任意の可能な他のシーケンスと組み合わせて、二重填込相互接続開口部内に改善された方法で銅をめっきすることができる。この場合も、本明細書に教示される他の図面と同様に、特定のデューティ・サイクル、電流範囲、継続時間などは、機械によりあるいはプロセスにより本明細書の精神および範囲から逸脱せずに変わることがある。

【0061】

図11は、図1のシステム10と共に用いることのできる、さらに別の電力シーケンスを示す。図11は、高電力正パルス化期間302を用いて、速い付着速度でシード空乏部116a上に有効に初期のめっきを行うことができる様子を示す。図11に示される期間304と同様の負パルス期間の間に随意に散在する1回以上の期間302の後で、低電力正パルス化期間306を用いて、より低速でめっきを続けながら、なおかつ、より大量の不純物(炭素、窒素やイオウなど)を同材料内に取り込み、エレクトロマイグレーション(EM)耐性を改善する。

【0062】

図11に示されるように、高電力正パルス期間302と低電力正パルス期間306とは、図11に示される等価のあるいは異なる低電力パルス化シーケンス304または308によって隔てることができる。一般に、正電力シーケンス306に続く負電力シーケンス308は、高電力正期間302に続く期間304よりも継続時間が短く、全体の集積電力が小さい。これは、期間306では、期間302よりもウェハ20の表面上に付着される材料が少ないためで、それによって後の負電力期間中に除去する必要のある材料が少なくなり、空隙の軽減や均一性の改善が可能になることは明らかである。また、期間302は、負パルスが混在する一つ以上の順方向パルスを有し、期間304も一つ以上の反転期間によって構成される。さらに、図11は、図8にも示されるように、高電力DC動作が電気めっき動作の終点付近で始まり、システム10のウェハ処理量を改善することができることを示す。従って、図11の高電力DC期間310が電気めっき動作の終点で用いられる(図7を参照)。

【0063】

図12は、図8ないし図11に前述された期間のうち、任意の期間に関して用いることのできる別の電力期間352を示す。図12のオフ期間356と、事実上図8ないし図11に示されるすべてのオフ期間とを設けることにより、電気めっき動作が行われた後で図1の溶液19を回復させることができる。言い換えると、種々の期間のオン・パルスにより、溶液10内でウェハ20に近接して位置する(境界層)銅がウェハ上に付着する。これにより、溶液10内のめっき表面付近に、めっき材料と添加剤とを持たない領域が作成される。めっき表面付近でこのような欠乏領域(すなわち漕19内における濃度の傾斜)が銅によって回復できるようにするために、オフ・サイクルを用いて、溶液内の材料を高濃度の領域(バルク)から低濃度の領域(ウェハ表面または境界層)まで拡散させる。高いアスペクト比の開口部内にめっきする場合にこれは特に重要である。これについては、以下に説明する。

【0064】

図12は、電力シーケンス352のデューティ・サイクルが、オン期間354がオフ・サイクル356と等しいかそれよりも短くなることを示す。この種のデューティ・サイクルはきわめて小さなビア(たとえば0.2マイクロメートル未満)またはきわめて大きなアスペクト比を持つビア(8マイクロメートルのトレンチ深さと0.5マイクロメートルのトレンチ幅を持つトレンチ・キャパシタなど)において必要になることがある。開口部の寸法およびアスペクト比の少なくとも一つのために、不純物、添加剤または銅が溶液内を通り、これらの材料がめっきプロセスの結果として欠乏する領域間で拡散するのに、より長い時間がかかることがある。このような場合は、より長い相対オフ時間356が設けられて、極端に小さい幾何学形状のあるいは大きなアスペクト比の開口部が、銅薄膜の品質に大きな影響を及ぼすことなくこれらの材料の欠乏から充分に回復できるようにする。図12のプロセスを、X線リソグラフィ、位相シフト、SCALPALまたはEビーム・リソグラフィなどの高度なリソグラフィが銅相互接続または銅電極の形成に関して用いられるような一つ以上の用途において用いられることが予想される。この「長いオフ時間」の周期的サイクルとは0.1マイクロメートルのビアまたは0.1マイクロメートル未満のビアや深さと幅の比が6:1以上のアスペクト比開口部に関して特に必要とされると考えられる。

【0065】

図13は、二つの可能な電気めっきシステム(システムAおよびシステムB)の動作を示す。いずれのシステムAまたはB(あるいは図13に明記される概念に準じて形成される別のシステム)を用いても、その場でエンドポイント検出またはプロセス制御を行いながら銅またはその他任意の冶金材料を任意の基板上に電気めっきすることができる。このエンドポイント法およびシステムは、図1ないし図12に示される波形のうち任意のものと組み合わせて用いることができ、また図1のシステム10を用いて実行することができる。

【0066】

詳しくは、図13の上部はシステムAを示す。システムAは図1に示されるシステム10と同様のもので、エンドポイント検出、データ収集および現場制御に用いられるのと同じクランプ18を通じて電力がウェハ20に供給される。言い換えると、図8ないし図12の一つ以上のサイクル201,212,214,210,252,254,256,268などをウェハ20に適応し、断続的に中断することにより、エンドポイント検出動作を同じクランプ18上で開始する。従って、システムAを時間多重エンドポイント検出システムと呼び、これにより一定のクランプ18を電気めっきおよびエンドポイント/プロセス現場検出の両方の間の電力のために用いる。

【0067】

このような時間多重システムの動作の一例として、図13のシステムAは正パルス化電力シーケンス502を実行し、その後直ちに負パルス化電力シーケンス504を実行するものとして図示される。これらの電力シーケンスは、図1および図2に示される一つ以上のクランプ18を通じて実行される。これらのサイクル502,504の一つ以上を実行した後で、電源28は図1のスイッチ32を介してクランプ18から切り離される。この時点で、エンドポイント・センサ30がスイッチ32によりクランプ18に接続される。CPU26の制御下でスイッチ32により可動化されるこの接続により、エンドポイント検出動作506が図13において実行される。

【0068】

期間506において、電圧や電流が一つ上のクランプの両端に印加や検出され、ウェハ20上の銅めっきの抵抗がウェハ20上に形成された銅の充分な厚みを示すが否かが判断される。また、多くのプローブ/コンタクト点の両端での多方向二次元探査が期間506においてウェハ20の表面全体で行われる。従って、期間506により、ウェハ上の種々の点の間の材料の均一性または厚みが判定され、このデータはデータベース作成のために格納することができ、あるいは二次元描写されて、ウェハ間のバイアスに関する均一性を追跡することができる。また、この均一性データをCPU26によって処理して、後で電源28によりウェハ20に対して提供される電力をクランプ毎に改変することができ、それによって均一性を電気めっき動作において現場で改善することができる。

【0069】

さらに、期間506のエンドポイント動作は電気めっき動作をいつ停止するかを検出するために行うのではなく、電気めっき動作が1通りの動作をいつ停止して、別の動作をいつ開始すべきかを検出するために用いることができる。たとえば、期間506のエンドポイント検出を用いて、二つの期間502,504の反復循環を、異なるデューティ・サイクルまたは電圧/電流レベルを持つ他の期間508,510の循環に変更すべきかを判断することができる。また、エンドポイント検出512を用いて、図13に示すパルス化動作からDC動作516への切替をいつ行うべきかを判断することができる。言い換えると、図13の期間512を用いて、ウェハ20が図6に示される点にいつ到達したかを検出し、材料を急速に付着するための図13の期間516のプロセスをいつ変更して、図7の構造に到達すべきかを検出することができる。さらに、エンドポイント検出を用いて、新たな添加剤を溶液19にいつ添加すべきか、システム10または溶液19の条件をいつ変更すべきかを判断することができる。一例として、ウィンドウ506,512で得られるデータに基づく、増白剤、抑制剤またはその他の添加剤の流量を増量したり、流量を減量したり、あるいは漕19への供給から完全に排除することができる。もちろん、最も有用な方式においては、506,512などのエンドポイント検出ウィンドウを任意の電気めっきプロセスの終点で用いて、電気めっき動作を終了すべきとき(たとえば期間516の終点)を決定することができる。

【0070】

図13は、これも図1に示されるものと類似であるが、上記のシステムAとは異なるシステムBも示す。図13のシステムBにおいては、一部のクランプ18は電源28のある種の切替制御下に恒久的に結合されており、他のクランプ18はエンドポイント・コントローラ30の制御下に恒久的に結合される。このシステムB(連続監視システムと称する)を用いると、パルス化動作522〜534を開始して、図13の動作536などのDC動作を、電源28に接続されるクランプ18を介する割り込みなしに続けることができる。波形522,524,526,528,530,532,534,536を介するこれらのクランプ18を通じてウェハ20に電力を供給するのと時間的に平行に、図1の他のクランプ18を用いて、図13に示される期間520により、均一性、付着速度、不純物レベルおよびエンドポイント・パラメータの少なくとも一つを監視することができる。

【0071】

従って、図13のシステム10のエンドポイント検出は、図13の期間520により示されるように継続することも、あるいは図13のエンドポイント期間506,512により示されるように時間多重すなわち割り込みを行いながら実行することも、あるはその両方を行うこともできる。エンドポイント検出動作は図8ないし図12に前述される波形のうち任意の波形の任意の場所、あるいは図8ないし図12に示される任意の波形の間に配置することもできることに注目することが重要である。エンドポイント動作は、種々のパルス化サイクルの「オフ」サイクル中に低電流および低電圧検出により自動的に行うこともできる。さらに、図13または図1には特定的には図示されないが、本明細書で説明するエンドポイント動作をロボット制御の下で2チャンバ・システムにおいて実行することもできる。電気めっきをシステム10に類似の第1チャンバ内で行うことができる。しかし、システム10には電気めっきチャンバに近接して別のチャンバが含まれ、それによってロボットはウェハを電気めっきチャンバとエンドポイント検出(4点プローブ・チャンバなど)との間で往復させることができる。これは、エンドポイント条件が第2チャンバで検出されるまで続く。

【0072】

本発明は、特定の実施例に関して説明されたが、さらなる改良および改善が当業者には可能であろう。従って、本発明は、添付の請求項に定義される本発明の精神および範囲から逸脱しないこれらすべての改良を包含することを理解頂きたい。

【符号の説明】

【0073】

10…電気めっきシステム、11…ハウジング、12…内カップ、13…拡散器、14…陽極、15…ヘッド、16…ターンテーブル、18…クランプ、19…溶液、20…ウェハ、22…流出口、24…流入口、26…CPU(中央処理装置)、28…電源、30…エンドポイント・センサ、32…スイッチ、34…制御システム。

【特許請求の範囲】

【請求項1】

ウェハ(20)上に銅層を形成する方法であって、

制御システム(34)を有する電気めっきチャンバ(10)内に前記ウェハ(20)を配置する段階であって、前記制御システム(34)が少なくとも一つの電気コンタクト(18)を通じて前記ウェハ(20)に電気的に接続され、前記制御システム(34)が前記ウェハ(20)に電力を提供する、段階と、

第1期間(302)の間に前記ウェハ(20)に対する第1電力を正にパルス化する段階であって、前記第1電力の正パルス化が第1電力レベルにおけるオン期間と第2電力レベルにおけるオフ期間とからなる、段階と、

前記第1期間に続く第2期間(304)の間に前記ウェハ(20)に対する第2電力を負にパルス化する段階であって、第2電力の負パルス化が第3電力レベルにおけるオン期間と第4電力レベルにおけるオフ期間とからなる、段階と、

前記第2期間(304)に続く第3期間(306)の間に前記ウェハ(20)に対する第3電力を正にパルス化する段階であって、前記第3電力の正パルス化が第5電力レベルにおけるオン期間と第6電力レベルにおけるオフ期間とからなり、前記第5電力レベルが前記第1電力レベルよりも小さい、段階と

を備えることを特徴とする方法。

【請求項2】

ウェハ(20)上に銅層を形成する方法であって、

前記ウェハ(20)を電気めっきチャンバ(10)内に配置する段階であって、前記ウェハ(20)が上部誘電体面(115)と、前記上部誘電体面(115)の下方の平坦な表面に配置される底部トレンチ面(117)と、前記底部トレンチ面(117)下方の平坦な表面に配置される底部ビア面(119)とを有する二重填込相互接続開口部を有し、前記電気めっきチャンバ(10)が少なくとも一つの電気コンタクト(18)を通じて前記ウェハ(20)に接続される制御システム(34)を有し、前記制御システム(34)が前記ウェハ(20)に電力を提供する、段階と、

第1期間の間、前記ウェハ(20)に対する電力を正にパルス化する段階と、

前記第1期間に続く第2期間の間、前記ウェハ(20)に対する電力を負にパルス化する段階と、

前記第2期間に続く第3期間の間、前記ウェハ(20)に対する電力を正にパルス化する段階と

を備えることを特徴とする方法。

【請求項1】

ウェハ(20)上に銅層を形成する方法であって、

制御システム(34)を有する電気めっきチャンバ(10)内に前記ウェハ(20)を配置する段階であって、前記制御システム(34)が少なくとも一つの電気コンタクト(18)を通じて前記ウェハ(20)に電気的に接続され、前記制御システム(34)が前記ウェハ(20)に電力を提供する、段階と、

第1期間(302)の間に前記ウェハ(20)に対する第1電力を正にパルス化する段階であって、前記第1電力の正パルス化が第1電力レベルにおけるオン期間と第2電力レベルにおけるオフ期間とからなる、段階と、

前記第1期間に続く第2期間(304)の間に前記ウェハ(20)に対する第2電力を負にパルス化する段階であって、第2電力の負パルス化が第3電力レベルにおけるオン期間と第4電力レベルにおけるオフ期間とからなる、段階と、

前記第2期間(304)に続く第3期間(306)の間に前記ウェハ(20)に対する第3電力を正にパルス化する段階であって、前記第3電力の正パルス化が第5電力レベルにおけるオン期間と第6電力レベルにおけるオフ期間とからなり、前記第5電力レベルが前記第1電力レベルよりも小さい、段階と

を備えることを特徴とする方法。

【請求項2】

ウェハ(20)上に銅層を形成する方法であって、

前記ウェハ(20)を電気めっきチャンバ(10)内に配置する段階であって、前記ウェハ(20)が上部誘電体面(115)と、前記上部誘電体面(115)の下方の平坦な表面に配置される底部トレンチ面(117)と、前記底部トレンチ面(117)下方の平坦な表面に配置される底部ビア面(119)とを有する二重填込相互接続開口部を有し、前記電気めっきチャンバ(10)が少なくとも一つの電気コンタクト(18)を通じて前記ウェハ(20)に接続される制御システム(34)を有し、前記制御システム(34)が前記ウェハ(20)に電力を提供する、段階と、

第1期間の間、前記ウェハ(20)に対する電力を正にパルス化する段階と、

前記第1期間に続く第2期間の間、前記ウェハ(20)に対する電力を負にパルス化する段階と、

前記第2期間に続く第3期間の間、前記ウェハ(20)に対する電力を正にパルス化する段階と

を備えることを特徴とする方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2011−66447(P2011−66447A)

【公開日】平成23年3月31日(2011.3.31)

【国際特許分類】

【出願番号】特願2010−281416(P2010−281416)

【出願日】平成22年12月17日(2010.12.17)

【分割の表示】特願2000−128669(P2000−128669)の分割

【原出願日】平成12年4月28日(2000.4.28)

【出願人】(504199127)フリースケール セミコンダクター インコーポレイテッド (806)

【Fターム(参考)】

【公開日】平成23年3月31日(2011.3.31)

【国際特許分類】

【出願日】平成22年12月17日(2010.12.17)

【分割の表示】特願2000−128669(P2000−128669)の分割

【原出願日】平成12年4月28日(2000.4.28)

【出願人】(504199127)フリースケール セミコンダクター インコーポレイテッド (806)

【Fターム(参考)】

[ Back to top ]