半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ヒューズ素子を有する半導体チップが形成される半導体ウエハ、半導体装置、および、半導体装置の製造方法に関する。

【背景技術】

【0002】

DRAM(Dynamic Random Access Memory)などの半導体装置に搭載される半導体チップおいては、種々の用途に対して、ヒューズ素子が用いられる。

【0003】

例えば、正常に動作しない不良メモリセルが見つかると、その不良メモリセルを冗長メモリセルに置換するとともに、不良メモリセルのアドレスを記憶し、そのアドレスへのアクセス要求があった場合には、置換した冗長メモリセルにアクセスすることで、不良メモリセルの救済が行われる。ここで、不良メモリセルのアドレスの記憶にヒューズ素子からなるヒューズ回路が用いられる。

【0004】

また、同等の特性を有する複数の半導体チップが、半導体ウエハ上に同一の工程を経て製造されるが、内部デバイスの特性のばらつきなどにより、半導体チップ間で内部電圧レベルや動作タイミングなどの特性がばらつくことがある。ここで、半導体チップ間の特性のばらつきの調整にヒューズ回路が用いられる。

【0005】

特許文献1(特開2003−036690号公報)には、メタルなどの配線を有し、その配線へのレーザー照射による切断により導通状態から非導通状態へと変化するレーザーヒューズからなるレーザーヒューズ回路およびレーザーヒューズ回路に不良メモリセルのアドレスを記憶させるための内部回路について開示されている。また、特許文献1には、レーザーヒューズ回路と内部回路が形成される領域を区画し、レーザーヒューズ回路を半導体チップが形成されるチップ領域に形成し、内部回路を半導体チップの形成後に切削されるダイシング領域に形成する技術が開示されている。ヒューズ回路に不良メモリセルのアドレスを記憶させた後は不要となる内部回路をダイシング領域に形成することで、半導体チップのチップ面積を削減することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−036690号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

レーザーヒューズには、配線にレーザー照射を行うためのヒューズ窓が設けられている。ヒューズ窓とその周辺の領域には、レーザーが遮られないように、信号線などの他の配線を通すことができないため、特許文献1に開示の技術においては、半導体チップのチップ面積の削減を十分に図ることができないという問題がある。

【0008】

なお、近年、レーザーヒューズに代わり、絶縁膜を有し、その絶縁膜への電圧印加による絶縁破壊により非導通状態から導通状態へと変化するヒューズ素子であるアンチヒューズが用いられることがある。アンチヒューズを用いた場合には、ヒューズ窓を設ける必要が無く、チップ面積を削減することができる。しかし、アンチヒューズを用いる場合、一般に、半導体ウエハ上の半導体チップに不良メモリセルのアドレスなどを入力して記憶させる工程は、テスタ装置により行われる。テスタ装置は、不良メモリセルのアドレスに対応するアンチヒューズを導通状態とするため、テスタ装置に対して半導体チップ毎の不良メモリセルのアドレスを入力する作業が必要となり、時間がかかるという問題がある。

【課題を解決するための手段】

【0009】

本発明の半導体ウエハは、

半導体チップが形成される複数のチップ領域と、前記複数のチップ領域を区画するダイシング領域と、からなる半導体ウエハであって、

前記チップ領域に形成され、絶縁膜を有し、電圧の印加による前記絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズを有するアンチヒューズ回路と、

前記ダイシング領域に前記複数のアンチヒューズの各々に対応して形成され、配線を有し、レーザー照射による前記配線の切断により非導通状態となる複数のレーザーヒューズを有するレーザーヒューズ回路と、

前記複数のアンチヒューズのうち、前記半導体チップへの入力に応じて非導通状態とされたレーザーヒューズに対応する前記アンチヒューズの有する前記絶縁膜に、電源からの電圧を印加させて、前記アンチヒューズを導通状態とする制御回路と、を有する。

【0010】

本発明の半導体装置は、

上述した半導体ウエハにおけるダイシング領域を切削することで分離された半導体チップを搭載する。

【0011】

本発明の半導体装置の製造方法は、

半導体チップが搭載される半導体装置の製造方法であって、

前記半導体チップが製造される半導体ウエハ上の複数のチップ領域のそれぞれに、絶縁膜を有し、電圧の印加による前記絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズからなるアンチヒューズ回路を形成する工程と、

前記複数のチップ領域を区画するダイシング領域に、前記複数のアンチヒューズの各々に対応して、配線を有し、レーザー照射による前記配線の切断により非導通状態となる複数のレーザーヒューズからなるレーザーヒューズ回路を形成する工程と、

前記半導体チップへの入力に応じて、前記レーザーヒューズが有する配線へのレーザー照射を行い、前記レーザーヒューズを非導通状態とする工程と、

前記非導通状態であるレーザーヒューズに対応する前記アンチヒューズが有する前記絶縁膜に、電源からの電圧を印加させて、前記アンチヒューズを導通状態とする工程と、

前記ダイシング領域を切削して、前記チップ領域に形成された前記半導体チップを分離する工程と、を有する。

【発明の効果】

【0012】

本発明によれば、半導体ウエハのチップ領域にアンチヒューズ回路が形成され、ダイシング領域にレーザーヒューズ回路が形成され、半導体チップへの入力に応じて配線が切断されたレーザーヒューズに対応するアンチヒューズの絶縁膜の絶縁破壊が行われる。

【0013】

そのため、チップ領域にはレーザーヒューズ回路が形成されることがないので、チップ面積を削減することができる。また、半導体チップへの入力に応じてレーザーヒューズの配線の切断が最初に行われるため、入力に要する時間の増大を抑制することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の第1の実施形態の半導体ウエハの上面図である。

【図2】図1に示す領域Aの拡大図である。

【図3】図3に示すチップ領域およびダイシング領域の拡大図である。

【図4A】関連する半導体チップにおけるレーザーヒューズの配置の一例を示す図である。

【図4B】図3に示すレーザーヒューズ回路におけるレーザーヒューズの配置の一例を示す図である。

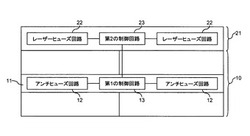

【図5】図3に示すレーザーヒューズ回路の構成を示す回路図である。

【図6】図5に示すレーザーヒューズ回路から出力されるレーザーヒューズカット信号のタイミングチャートである。

【図7】図3に示す各部の構成を示すブロック図である。

【図8A】関連する半導体チップの形成後の工程を示す図である。

【図8B】関連する半導体チップの形成後の工程を示す図である。

【図8C】本発明に係る半導体チップの形成後の工程を示す図である。

【図9】本発明に係る仕様と関連する仕様との比較を示す図である。

【図10】関連する半導体チップの構成を示す図である。

【図11】本発明の第2の実施形態におけるチップ領域および対応するダイシング領域の拡大図である。

【発明を実施するための形態】

【0015】

以下に、本発明を実施するための形態について図面を参照して説明する。

【0016】

(第1の実施形態)

図1は、本発明の第1の実施形態の半導体ウエハ1の上面図である。

【0017】

図1に示すように、半導体ウエハ1上の複数のチップ領域10のそれぞれに、DRAMなどの半導体装置に搭載される半導体チップが形成される。

【0018】

図2は、図1に示す領域Aの拡大図である。

【0019】

図2に示すように、複数のチップ領域10がダイシング領域20により区画されている。チップ領域10への半導体チップの形成後、ダイシング領域20は切削され、半導体チップが分離される。

【0020】

チップ領域10には、絶縁膜を有し、その絶縁膜への電圧印加による絶縁破壊により、非導通状態から導通状態へと変化する複数のアンチヒューズを含むアンチヒューズ回路が形成される。以下では、アンチヒューズ回路が形成されるチップ領域10内の領域をアンチヒューズ領域11と称する。また、チップ領域10のうち、アンチヒューズ領域11以外の領域には、例えば、メモリセルが形成される。

【0021】

ダイシング領域20には、メタルなどの配線を有し、その配線へのレーザー照射による切断により、導通状態から非導通状態へと変化する複数のレーザーヒューズを含むレーザーヒューズ回路が、各チップ領域10に対応して形成される。以下では、レーザーヒューズ回路が形成される領域をレーザーヒューズ領域21と称する。なお、図2においては、チップ領域10に対応して、そのチップ領域10の上側にレーザーヒューズ領域21が形成される例を示している。

【0022】

図3は、チップ領域10および対応するレーザーヒューズ領域21の拡大図である。

【0023】

図3に示すように、チップ領域10内のアンチヒューズ領域11には、アンチヒューズ回路12と第1の制御回路13とが形成される。また、レーザーヒューズ領域21には、レーザーヒューズ回路22と第2の制御回路23とが形成される。

【0024】

アンチヒューズ回路12は、複数のアンチヒューズを有する。

【0025】

第1の制御回路13は、第2の制御回路23から出力される、半導体チップへの入力に応じて配線の切断が行われたレーザーヒューズを示すレーザーヒューズカット信号の出力に応じて、図3においては不図示の電源回路による、アンチヒューズ回路12に含まれるアンチヒューズの絶縁膜への電圧の印加を制御する。

【0026】

レーザーヒューズ回路22は、アンチヒューズ回路12に含まれる複数のアンチヒューズの各々に1対1に対応する複数のレーザーヒューズを有する。

【0027】

なお、以下では、アンチヒューズの絶縁膜に電圧を印加して絶縁破壊を起こし、アンチヒューズを非導通状態から導通状態へと変化させること、および、レーザーヒューズの配線にレーザーを照射して切断し、レーザーヒューズを導通状態から非導通状態へと変化させることを、トリミングを行うと称する。

【0028】

第2の制御回路23は、トリミングが行われたレーザーヒューズを示すレーザーヒューズカット信号を第1の制御回路13に出力する。

【0029】

図4Aは、チップ領域内に形成されたレーザーヒューズ回路におけるレーザーヒューズの配置の一例を示す図である。また、図4Bは、本実施形態のレーザーヒューズ回路22におけるレーザーヒューズの配置の一例を示す図である。

【0030】

上述したように、レーザーヒューズのヒューズ窓とその周辺の領域には配線を通すことができないため、レーザーヒューズ間の間隔を小さくして、ヒューズ窓の間隔も小さくすることが、チップ面積を削減するためには好ましい。しかし、ヒューズ窓の間隔が小さくなると、レーザー照射の精度が高いレーザー装置が必要となり、そのようなレーザー装置を用意するには多額の設備投資が必要となるため、コスト面からレーザーヒューズ間の距離を縮小するのは難しい。そのため、チップ領域内にレーザーヒューズを形成する場合には、図4Aに示すように、レーザー装置によるレーザー照射が可能な範囲で、レーザーヒューズ24間の距離が小さくなるように配置される。

【0031】

一方、本実施形態においては、レーザーヒューズ24はダイシング領域20に形成されるため、チップ面積には影響しない。そのため、図4Bに示すように、レーザーヒューズ24間の距離を拡げることができ、レーザー照射の精度の高いレーザー装置が不要となるので、設備投資のコストを抑えることができる。

【0032】

図5は、レーザーヒューズ回路22の構成を示す回路図である。

【0033】

図5に示すレーザーヒューズ回路22は、レーザーヒューズ24−0〜24−11と、N型トランジスタ25−0〜25−11と、P型トランジスタ26と、を有する。

【0034】

レーザーヒューズ24−0は、一端がP型トランジスタ26のドレインに接続され、多端がN型トランジスタ25−0のソースに接続される。

【0035】

N型トランジスタ25−0は、レーザーヒューズ24−0に対応して設けられ、ゲートには図5においては不図示の第2の制御回路23が接続されてヒューズ選択信号が入力され、ソースにはレーザーヒューズ24−0の多端が接続され、ドレインにはグランドが接続される。

【0036】

なお、レーザーヒューズ24−1〜24−11のそれぞれに対応して、N型トランジスタ25−1〜25−11がそれぞれ設けられている。レーザーヒューズ24−1〜24−11と対応するN型トランジスタ25−1〜25−11およびP型トランジスタ26との接続関係は、レーザーヒューズ24−0とN型トランジスタ25−0およびP型トランジスタ26との接続関係と同様であるため、説明を省略する。

【0037】

P型トランジスタ26は、ゲートには第2の制御回路23が接続されてNOR接点イニシャル信号が入力され、ソースには電源が接続され、ドレインにはレーザーヒューズ24−0〜24−11の一端が接続される。P型トランジスタ26のドレインとレーザーヒューズ24−0〜24−11の一端との接点(NOR接点)の電位に応じたレーザーヒューズカット信号が、第2の制御回路23を介して、図5においては不図示の第1の制御回路13に出力される。

【0038】

図6は、レーザーヒューズカット信号のタイミングチャートである。なお、図6においては、図5に示すレーザーヒューズ24−2,24−6,24−10のトリミングが行われているものとする。

【0039】

第2の制御回路23には、クロック(CLK)信号が入力される。

【0040】

第2の制御回路23は、CLK信号の入力に応じてNOR接点イニシャライズ信号およびヒューズ選択信号をLowレベルまたはHighレベルとし、NOR接点イニシャライズ信号をP型トランジスタ26のゲートに入力し、ヒューズ選択信号をN型トランジスタ25−0〜25−11に出力する。なお、以下では、N型トランジスタ25−0に対応し、N型トランジスタ25−0のゲートに入力されるヒューズ選択信号をヒューズ選択信号(0)と称し、N型トランジスタ25−1に対応し、N型トランジスタ25−1のゲートに入力されるヒューズ選択信号をヒューズ選択信号(1)と称し、以下、同様にして、N型トランジスタ25−11に対応し、N型トランジスタ25−11のゲートに入力されるヒューズ選択信号をヒューズ選択信号(11)と称する。

【0041】

時刻t1において、第2の制御回路23は、LowレベルのNOR接点イニシャライズ信号をP型トランジスタ26のゲートに入力し、Lowレベルのヒューズ選択信号(0)からヒューズ選択信号(11)を対応するN型トランジスタ25−0〜25−11のゲートに入力する。

【0042】

LowレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオンとなる。また、Lowレベルのヒューズ選択信号がゲートに入力されることで、N型トランジスタ25−0〜25−11はオフとなり、NOR接点の電位が初期化される。

【0043】

時刻t2において、第2の制御回路23は、NOR接点イニシャライズ信号をLowレベルからHighレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、ヒューズ選択信号(0)をLowレベルからHighレベルとし、N型トランジスタ25−0のゲートに入力するとともに、Lowレベルのヒューズ選択信号(1)からヒューズ選択信号(11)を対応するN型トランジスタ25−1〜25−11のゲートに入力する。

【0044】

HighレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオフとなる。また、Highレベルのヒューズ選択信号(0)がゲートに入力されることで、N型トランジスタ25−0はオンとなり、Lowレベルのヒューズ選択信号が入力されることで、N型トランジスタ25−1〜25−11はオフとなる。ここで、N型トランジスタ25−0に対応するレーザーヒューズ24−0は導通状態であり、また、N型トランジスタ25−0のドレインにはグランドが接続されているため、NOR接点の電位はLowレベルとなる。したがって、Lowレベルのレーザーヒューズカット信号が出力される。

【0045】

時刻t3において、第2の制御回路23は、NOR接点イニシャライズ信号をHighレベルからLowレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、Lowレベルのヒューズ選択信号(0)からヒューズ選択信号(11)を対応するN型トランジスタ25−0〜25−11のゲートに入力する。

【0046】

LowレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオンとなる。また、Lowレベルのヒューズ選択信号がゲートに入力されることで、N型トランジスタ25−0〜25−11はオフとなり、NOR接点の電位が初期化される。

【0047】

時刻t4において、第2の制御回路23は、NOR接点イニシャライズ信号をLowレベルからHighレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、ヒューズ選択信号(1)をLowレベルからHighレベルとし、N型トランジスタ25−1のゲートに入力するとともに、Lowレベルのヒューズ選択信号(0)およびヒューズ選択信号(2)からヒューズ選択信号(11)を対応するN型トランジスタ25−0およびN型トランジスタ25−2〜25−11のゲートに入力する。

【0048】

HighレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオフとなる。また、Highレベルのヒューズ選択信号(1)がゲートに入力されることで、N型トランジスタ25−1はオンとなり、Lowレベルのヒューズ選択信号が入力されることで、N型トランジスタ25−0,25−2〜25−11はオフとなる。ここで、N型トランジスタ25−1に対応するレーザーヒューズ24−1は導通状態であり、また、N型トランジスタ25−1のドレインにはグランドが接続されているため、NOR接点の電位はLowレベルとなる。したがって、Lowレベルのレーザーヒューズカット信号が出力される。

【0049】

時刻t5において、第2の制御回路23は、NOR接点イニシャライズ信号をHighレベルからLowレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、Lowレベルのヒューズ選択信号(0)からヒューズ選択信号(11)を対応するN型トランジスタ25−0〜25−11のゲートに入力する。

【0050】

LowレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオンとなる。また、Lowレベルのヒューズ選択信号がゲートに入力されることで、N型トランジスタ25−0〜25−11はオフとなり、NOR接点の電位が初期化される。

【0051】

時刻t6において、第2の制御回路23は、NOR接点イニシャライズ信号をLowレベルからHighレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、ヒューズ選択信号(2)をLowレベルからHighレベルとし、N型トランジスタ25−2のゲートに入力するとともに、Lowレベルのヒューズ選択信号(0)、ヒューズ選択信号(1)、および、ヒューズ選択信号(3)からヒューズ選択信号(11)を対応するN型トランジスタ25−0,25−1,25−3〜25−11のゲートに入力する。

【0052】

HighレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオフとなる。また、Highレベルのヒューズ選択信号(2)がゲートに入力されることで、N型トランジスタ25−2はオンとなり、Lowレベルのヒューズ選択信号が入力されることで、N型トランジスタ25−0,25−1,25−3〜15−11はオフとなる。ここで、N型トランジスタ25−2に対応するレーザーヒューズ24−2は非導通状態である。そのため、NOR接点の電位はHighレベルとなる。したがって、Highレベルのレーザーヒューズカット信号が出力される。

【0053】

時刻t7において、第2の制御回路23は、NOR接点イニシャライズ信号をHighレベルからLowレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、Lowレベルのヒューズ選択信号(0)からヒューズ選択信号(11)を対応するN型トランジスタ25−0〜25−11のゲートに入力する。

【0054】

LowレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオンとなる。また、Lowレベルのヒューズ選択信号がゲートに入力されることで、N型トランジスタ25−0〜25−11はオフとなり、NOR接点の電位が初期化される。

【0055】

以下、同様にして、N型トランジスタ25−3〜25−11それぞれのゲートに、Highレベルのヒューズ選択信号が順に入力される。対応するレーザーヒューズ24が非導通状態である場合には、Highレベルのレーザーヒューズカット信号が出力されるため、レーザーヒューズカット信号の出力をモニタすることで、どのレーザーヒューズ24がトリミングされたかが分かる。

【0056】

図7は、図3に示す各部の構成をより詳細に示す図である。

【0057】

レーザーヒューズ回路22は、レーザーヒューズ24−0〜24−6を有する。なお、図7においては、図5に示すN型トランジスタ25、P型トランジスタ26などについては記載を省略する。

【0058】

アンチヒューズ回路12は、アンチヒューズ14−0〜14−6を有する。ここで、アンチヒューズ14−0はレーザーヒューズ24−0に対応して設けられ、アンチヒューズ14−1はレーザーヒューズ24−1に対応して設けられ、以下、同様にして、アンチヒューズ14−6はレーザーヒューズ24−6に対応して設けられる。すなわち、アンチヒューズ回路12は、レーザーヒューズ回路22が有する複数のレーザーヒューズの各々に1対1に対応する複数のアンチヒューズを有する。

【0059】

第1の制御回路13は、選択制御回路15と、アンチヒューズ回路選択レコーダー16と、アドレスエンコード回路17と、を有する。また、第2の制御回路23は、レーザーヒューズ回路選択レコーダー27を有する。

【0060】

選択制御回路15は、クロック信号およびテスト対象となるレーザーヒューズ回路22を示すヒューズ選択テスト信号を、レーザーヒューズ回路選択レコーダー27、アンチヒューズ回路選択レコーダー16、および、アドレスエンコード回路17に出力する。また、選択制御回路15は、ヒューズ選択テスト信号に示されるレーザーヒューズ回路22に対応するアンチヒューズ回路14に含まれるアンチヒューズ14−0〜14−6にAF STORE信号を入力する。

【0061】

レーザーヒューズ回路選択レコーダー27は、クロック信号およびヒューズ選択テスト信号が入力されると、図3に示す複数のレーザーヒューズ回路22のうち、ヒューズ選択テスト信号に示されるレーザーヒューズ回路22に含まれるレーザーヒューズ24−0〜24−6にレーザーヒューズ回路セット選択信号を入力する。

【0062】

また、レーザーヒューズ回路選択レコーダー27は、クロック信号の入力に応じて、レーザーヒューズ24−0〜24−6のそれぞれに対応する、図7においては不図示のN型トランジスタ25のゲートにヒューズ選択信号を入力する。ここで、レーザーヒューズ回路選択レコーダー27は、レーザーヒューズ24−0から順に、各レーザーヒューズ24に対応するN型トランジスタ25のゲートに入力するヒューズ選択信号の論理レベルをクロック毎に変えて入力する。ヒューズ選択信号および図7においては記載を省略したNOR接点イニシャライズ信号の入力に応じて、ヒューズ回路22からは、レーザーヒューズがトリミングされているか否かに応じて論理レベルの異なるレーザーヒューズカット信号が出力される。

【0063】

アンチヒューズ回路選択レコーダー16は、ヒューズ選択テスト信号に示されるレーザーヒューズ回路22に含まれるレーザーヒューズ24に対応するアンチヒューズ14にアンチヒューズ回路セット選択信号を出力する。

【0064】

アドレスエンコード回路17は、レーザーヒューズ回路22から出力されるレーザーヒューズカット信号に示されるトリミングが行われたレーザーヒューズ24に対応するアンチヒューズ14にアドレス信号を出力する。

【0065】

AF STORE信号およびアドレス信号が入力されたアンチヒューズ14においては、絶縁膜に電圧が印加され、トリミングが行われる。

【0066】

次に、チップ領域にレーザーヒューズ回路を有する半導体チップを形成した場合(従来仕様1)、チップ領域にアンチヒューズ回路を有する半導体チップを形成した場合(従来仕様2)、および、ダイシング領域にレーザーヒューズ回路を形成し、チップ領域にアンチヒューズ回路を有する半導体チップを形成した場合(本発明に係る仕様)のそれぞれについて、半導体チップの形成後の工程について説明する。

【0067】

まず、従来仕様1に係る半導体チップの形成後の工程について、図8Aを参照して説明する。

【0068】

半導体チップの形成後、ウエハ状態のまま、高温雰囲気中で熱的ストレスおよび電気的ストレスを各半導体チップに印加して不良を加速判別するWLBI(Wafer Lebel Burn In)工程が行われる(ステップS101)。

【0069】

次に、テスト対象の半導体チップにプローブを介して所定の電気信号を入力することにより、半導体チップのメモリセルから不良メモリセルを検出し、不良メモリセルのアドレスを特定するWT(Wafer Test)工程が行われる(ステップS102)。

【0070】

次に、特定した不良メモリセルのアドレスを半導体チップに入力してレーザーヒューズ回路に記憶させるために、不良メモリセルのアドレスに対応するレーザーヒューズをトリミングするレーザーヒューズトリミング工程が行われる(ステップS103)。

【0071】

次に、半導体ウエハにおけるダイシング領域を切削するダイシング工程が行われ(ステップS104)、半導体チップが分離される。ダイシング工程の後、分離された各半導体チップが良品か不良品かを判別する単体判別工程が行われる(ステップS105)。

【0072】

次に、従来仕様2に係る半導体チップの形成後の工程について、図8Bを参照して説明する。なお、図8Bにおいて、図8Aと同様の処理については同じ符号を付し、説明を省略する。

【0073】

WT工程が行われた後、特定した不良メモリセルのアドレスを半導体チップに入力してアンチヒューズ回路に記憶させるために、アンチヒューズをトリミングするアンチヒューズトリミング工程が行われる(ステップS201)。ステップS201でのアンチヒューズトリミング工程においては、アンチヒューズのトリミングを行うテスタ装置に不良メモリセルのアドレスを入力し、その入力に応じてアンチヒューズのトリミングが行われる。ここで、一般に、テスタ装置には半導体チップ毎にしか不良メモリセルのアドレスの入力を行うことができない。そのため、アンチヒューズトリミング工程は半導体チップ装置毎にしか行うことができず、図8Aに示すレーザーヒューズトリミング工程と比較して時間がかかる。

【0074】

アンチヒューズトリミング工程の後、ダイシング工程および単体選別工程が行われる。

【0075】

次に、本発明に係る仕様に係る半導体チップの形成後の工程について、図8Cを参照して説明する。なお、図8Cにおいて、図8Aおよび図8Bと同様処理については同じ符号を付し、説明を省略する。

【0076】

WT工程の後、特定した不良メモリセルのアドレスを、ダイシング領域21に形成されたレーザーヒューズ回路22に記憶させるために、レーザーヒューズをトリミングするレーザーヒューズトリミング工程が行われる(ステップS301)。

【0077】

次に、アンチヒューズ回路12に含まれるアンチヒューズのうち、レーザーヒューズカット信号に示されるレーザーヒューズに対応するアンチヒューズをトリミングするアンチヒューズトリミング工程が行われる(ステップS302)。

【0078】

上述したように、ステップS301のレーザーヒューズトリミング工程においては、半導体チップ毎の不良メモリセルのアドレスの入力は不要であり、また、ステップS302のアンチヒューズトリミング工程においては、レーザーヒューズトリミング工程でトリミングされたレーザーヒューズに対応するアンチヒューズをトリミングするものであるため、上述したテスタ装置への不良メモリセルのアドレスの入力などが不要である。そのため、本発明に係る仕様においては、従来仕様2と比較して、アンチヒューズ回路がチップ領域に形成されている点では共通するが、アンチヒューズ回路に不良メモリセルのアドレスを記憶させる際の時間を短くすることができる。

【0079】

アンチヒューズトリミング工程の後、ダイシング工程および単体選別工程が行われる。

【0080】

図9は、従来仕様1および従来仕様2と本発明に係る仕様との比較を示す図である。

【0081】

チップ面積に関しては、従来仕様2および本発明に係る仕様においては、従来仕様1のようにレーザーヒューズのヒューズ窓とその周辺の領域には配線を通すことができないという制約が無いため、チップ面積の削減を図ることができる。なお、本発明に係る仕様においては、従来仕様2と比較して、チップ領域に11に第1の制御回路13を設ける必要があるため、若干、チップ面積が大きくなる。

【0082】

トリミング工程に関しては、従来仕様1および従来仕様2においては、図8Aに示すステップS103のレーザーヒューズトリミング工程、あるいは、図8Bに示すステップS201のアンチヒューズトリミング工程の1つの工程で済むのに対し、本発明に係る仕様においては、図8Cに示すステップS301のレーザーヒューズトリミング工程およびステップS302のアンチヒューズトリミング工程の2つの工程が必要となる。

【0083】

トリミング時間に関しては、従来仕様1および本発明に係る仕様においては、従来仕様2のように不良メモリセルのアドレスのテスタ装置への入力を半導体チップ毎に行う必要が無いため、トリミング時間を小さくすることができる。なお、本発明に係る仕様においては、従来仕様1と比較して、レーザーヒューズをトリミングして、不良メモリセルのアドレスを記憶させた後、トリミングしたレーザーヒューズに対応するアンチヒューズをトリミングする必要があるため、若干、トリミング時間が長くなる。

【0084】

テストコストに関しても、従来仕様1および本発明に係る仕様においては、従来仕様2のようにテスタ装置を用いて半導体装置毎にテストを行う必要が無いため、テストコストを小さくすることができる。

【0085】

設備投資に関しては、従来仕様1においては、チップ面積を小さくするためにレーザーヒューズ間の間隔を小さくすると、ヒューズ窓の間隔も小さくなり、レーザー照射の精度の高いレーザー装置が必要となるため、多額の設備投資が必要となる。従来仕様2においては、アンチヒューズをトリミングするための制御は単純であるため、安価なテスタ装置を用いてトリミングすることが可能であり、設備投資を抑制することができる。また、本発明に係る仕様においては、ダイシング領域にレーザーヒューズ回路が形成されているため、レーザーヒューズ間の間隔を小さくする必要がなくなり、レーザー装置に求められるレーザー照射の精度も高くない。そのため、安価なレーザー装置を用いることが可能となり、設備投資を抑制することができる。

【0086】

上述したように、本発明に係る仕様においては、チップ面積を小さくすることができるとともに、トリミング時間、テストコスト、設備投資なども小さくすることができるので、総合的に見て、従来仕様1および従来仕様2と比較して、半導体チップのデバイスコストを小さくすることができる。

【0087】

このように本実施形態によれば、半導体ウエハのチップ領域10に複数のアンチヒューズ14からなるアンチヒューズ回路12を形成し、ダイシング領域20に複数のアンチヒューズ14の各々に対応する複数のレーザーヒューズ24からなるレーザーヒューズ回路24を形成し、半導体チップへの入力に応じてトリミングが行われたレーザーヒューズ24に対応するアンチヒューズ14のトリミングが行われた後に、ダイシング領域20を切削して半導体チップを製造する。

【0088】

そのため、チップ領域にはレーザーヒューズ回路22が形成されることがないので、チップ面積を削減することができる。また、レーザーヒューズ回路22はダイシング領域に形成されているため、レーザーヒューズ24間の間隔を拡げることができ、レーザー照射の精度が高くない安価なレーザー装置を用いることができるので、設備投資を抑制することができる。また、レーザーヒューズ24のトリミングを行って不良メモリセルのアドレスを記憶させた後、トリミングされたレーザーヒューズ24に対応するアンチヒューズ14のトリミングを行うため、不良メモリセルのアドレスのテスタ装置への入力を半導体チップ毎に行う必要がなくなり、半導体チップへの入力を記憶させるのに要する時間を削減することができる。

【0089】

(第2の実施形態)

アンチヒューズを有する半導体チップにおいては、アンチヒューズの絶縁膜に電圧を印加して絶縁破壊を起こすために、半導体チップを動作させるために用いられる電源回路とは異なる特殊電源回路や特殊電源回路からアンチヒューズの絶縁膜に電圧を印加するための特殊電源パッドが、チップ領域に設けられることがある。

【0090】

図10は、特殊電源回路および特殊電源回路を有する半導体チップの構成の一例を示す図である。

【0091】

図10に示す半導体チップは、チップ領域10内に、メモリバンク31と、X−Fuse回路32と、Y−Fuse回路33と、特殊電源回路34と、特殊電源パッド35と、を有する。

【0092】

メモリバンク31は、複数のメモリセルがアレイ状に配置された構成を有する。

【0093】

X−Fuse回路32は、複数のアンチヒューズ14からなり、各メモリバンク31に対応して設けられている。X−Fuse回路32は、対応するメモリバンク31における不良メモリセルのロウアドレスを記憶する。

【0094】

Y−Fuse回路33は、複数のアンチヒューズ14からなり、各メモリバンク31に対応して設けられている。Y−Fuse回路33は、対応するメモリバンク31における不良メモリセルのカラムアドレスを記憶する。

【0095】

特殊電源回路34は、X−Fuse回路32およびY−Fuse回路33に含まれるアンチヒューズの絶縁膜に、特殊電源パッド35を介して印加する電圧を供給する。

【0096】

図10に示すように、特殊電源回路34および特殊電源パッド35は、チップ領域10内に形成されているが、アンチヒューズ14のトリミングが行われた後は、不要となる。

【0097】

そこで、本実施形態においては、図11に示すように、特殊電源回路34などをチップ領域10ではなく、ダイシング領域に20設ける。

【0098】

図11は、本発明の第2の実施形態におけるチップ領域10およびダイシング領域20の拡大図である。なお、図11において、図10と同様の構成については同じ符号を付し、説明を省略する。また、図11においては、第1の制御回路13、レーザーヒューズ回路22、第2の制御回路23などについては記載を省略する。

【0099】

図11に示すように、本実施形態においては、特殊電源回路34がダイシング領域20に形成される。特殊電源回路34をダイシング領域に形成することで、チップ面積の削減を図ることができる。

【0100】

なお、図11においては、特殊電源回路34だけをダイシング領域20に形成する例を用いて説明したが、特殊電源パッド35についても、ダイシング領域20に形成することで、さらにチップ面積の削減を図ることができる。

【0101】

このように本実施形態によれは、半導体ウエハのダイシング領域に、アンチヒューズ14の絶縁膜に電圧を印加するための特殊電源回路34、特殊電源パッド35を設ける。

【0102】

アンチヒューズ14のトリミングが行われた後は、特殊電源回路34や特殊電源パッド35は不要となるため、これらをダイシング領域20に設けることで、チップ面積の削減を図ることができる。

【0103】

なお、本実施形態においては、アンチヒューズ14のトリミングを行うための特殊電源回路34や特殊電源パッド35をダイシング領域20に設ける例を用いて説明したが、これに限られるものではない。例えば、WLBI工程において、半導体チップに電気的なストレスを印加するための電源回路や電源パッドなども、WLBI工程が終了した後は不要となるので、ダイシング領域に設けることで、半導体チップのチップ面積の削減を図ることができる。

【符号の説明】

【0104】

1 半導体ウエハ

10 チップ領域

11 アンチヒューズ領域

12 アンチヒューズ回路

13 第1の制御回路

14 アンチヒューズ

15 選択制御回路

16 アンチヒューズ回路選択レコーダー

17 アドレスエンコード回路

20 ダイシング領域

21 レーザーヒューズ領域

22 レーザーヒューズ回路

23 第2の制御回路

24,24−0〜24−11 レーザーヒューズ

25,25−0〜25−11 N型トランジスタ

26 P型トランジスタ

27 レーザーヒューズ回路選択レコーダー

31 メモリバンク

32 X−Fuse回路

33 Y−Fuse回路

34 特殊電源回路

35 特殊電源パッド

【技術分野】

【0001】

本発明は、ヒューズ素子を有する半導体チップが形成される半導体ウエハ、半導体装置、および、半導体装置の製造方法に関する。

【背景技術】

【0002】

DRAM(Dynamic Random Access Memory)などの半導体装置に搭載される半導体チップおいては、種々の用途に対して、ヒューズ素子が用いられる。

【0003】

例えば、正常に動作しない不良メモリセルが見つかると、その不良メモリセルを冗長メモリセルに置換するとともに、不良メモリセルのアドレスを記憶し、そのアドレスへのアクセス要求があった場合には、置換した冗長メモリセルにアクセスすることで、不良メモリセルの救済が行われる。ここで、不良メモリセルのアドレスの記憶にヒューズ素子からなるヒューズ回路が用いられる。

【0004】

また、同等の特性を有する複数の半導体チップが、半導体ウエハ上に同一の工程を経て製造されるが、内部デバイスの特性のばらつきなどにより、半導体チップ間で内部電圧レベルや動作タイミングなどの特性がばらつくことがある。ここで、半導体チップ間の特性のばらつきの調整にヒューズ回路が用いられる。

【0005】

特許文献1(特開2003−036690号公報)には、メタルなどの配線を有し、その配線へのレーザー照射による切断により導通状態から非導通状態へと変化するレーザーヒューズからなるレーザーヒューズ回路およびレーザーヒューズ回路に不良メモリセルのアドレスを記憶させるための内部回路について開示されている。また、特許文献1には、レーザーヒューズ回路と内部回路が形成される領域を区画し、レーザーヒューズ回路を半導体チップが形成されるチップ領域に形成し、内部回路を半導体チップの形成後に切削されるダイシング領域に形成する技術が開示されている。ヒューズ回路に不良メモリセルのアドレスを記憶させた後は不要となる内部回路をダイシング領域に形成することで、半導体チップのチップ面積を削減することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−036690号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

レーザーヒューズには、配線にレーザー照射を行うためのヒューズ窓が設けられている。ヒューズ窓とその周辺の領域には、レーザーが遮られないように、信号線などの他の配線を通すことができないため、特許文献1に開示の技術においては、半導体チップのチップ面積の削減を十分に図ることができないという問題がある。

【0008】

なお、近年、レーザーヒューズに代わり、絶縁膜を有し、その絶縁膜への電圧印加による絶縁破壊により非導通状態から導通状態へと変化するヒューズ素子であるアンチヒューズが用いられることがある。アンチヒューズを用いた場合には、ヒューズ窓を設ける必要が無く、チップ面積を削減することができる。しかし、アンチヒューズを用いる場合、一般に、半導体ウエハ上の半導体チップに不良メモリセルのアドレスなどを入力して記憶させる工程は、テスタ装置により行われる。テスタ装置は、不良メモリセルのアドレスに対応するアンチヒューズを導通状態とするため、テスタ装置に対して半導体チップ毎の不良メモリセルのアドレスを入力する作業が必要となり、時間がかかるという問題がある。

【課題を解決するための手段】

【0009】

本発明の半導体ウエハは、

半導体チップが形成される複数のチップ領域と、前記複数のチップ領域を区画するダイシング領域と、からなる半導体ウエハであって、

前記チップ領域に形成され、絶縁膜を有し、電圧の印加による前記絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズを有するアンチヒューズ回路と、

前記ダイシング領域に前記複数のアンチヒューズの各々に対応して形成され、配線を有し、レーザー照射による前記配線の切断により非導通状態となる複数のレーザーヒューズを有するレーザーヒューズ回路と、

前記複数のアンチヒューズのうち、前記半導体チップへの入力に応じて非導通状態とされたレーザーヒューズに対応する前記アンチヒューズの有する前記絶縁膜に、電源からの電圧を印加させて、前記アンチヒューズを導通状態とする制御回路と、を有する。

【0010】

本発明の半導体装置は、

上述した半導体ウエハにおけるダイシング領域を切削することで分離された半導体チップを搭載する。

【0011】

本発明の半導体装置の製造方法は、

半導体チップが搭載される半導体装置の製造方法であって、

前記半導体チップが製造される半導体ウエハ上の複数のチップ領域のそれぞれに、絶縁膜を有し、電圧の印加による前記絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズからなるアンチヒューズ回路を形成する工程と、

前記複数のチップ領域を区画するダイシング領域に、前記複数のアンチヒューズの各々に対応して、配線を有し、レーザー照射による前記配線の切断により非導通状態となる複数のレーザーヒューズからなるレーザーヒューズ回路を形成する工程と、

前記半導体チップへの入力に応じて、前記レーザーヒューズが有する配線へのレーザー照射を行い、前記レーザーヒューズを非導通状態とする工程と、

前記非導通状態であるレーザーヒューズに対応する前記アンチヒューズが有する前記絶縁膜に、電源からの電圧を印加させて、前記アンチヒューズを導通状態とする工程と、

前記ダイシング領域を切削して、前記チップ領域に形成された前記半導体チップを分離する工程と、を有する。

【発明の効果】

【0012】

本発明によれば、半導体ウエハのチップ領域にアンチヒューズ回路が形成され、ダイシング領域にレーザーヒューズ回路が形成され、半導体チップへの入力に応じて配線が切断されたレーザーヒューズに対応するアンチヒューズの絶縁膜の絶縁破壊が行われる。

【0013】

そのため、チップ領域にはレーザーヒューズ回路が形成されることがないので、チップ面積を削減することができる。また、半導体チップへの入力に応じてレーザーヒューズの配線の切断が最初に行われるため、入力に要する時間の増大を抑制することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の第1の実施形態の半導体ウエハの上面図である。

【図2】図1に示す領域Aの拡大図である。

【図3】図3に示すチップ領域およびダイシング領域の拡大図である。

【図4A】関連する半導体チップにおけるレーザーヒューズの配置の一例を示す図である。

【図4B】図3に示すレーザーヒューズ回路におけるレーザーヒューズの配置の一例を示す図である。

【図5】図3に示すレーザーヒューズ回路の構成を示す回路図である。

【図6】図5に示すレーザーヒューズ回路から出力されるレーザーヒューズカット信号のタイミングチャートである。

【図7】図3に示す各部の構成を示すブロック図である。

【図8A】関連する半導体チップの形成後の工程を示す図である。

【図8B】関連する半導体チップの形成後の工程を示す図である。

【図8C】本発明に係る半導体チップの形成後の工程を示す図である。

【図9】本発明に係る仕様と関連する仕様との比較を示す図である。

【図10】関連する半導体チップの構成を示す図である。

【図11】本発明の第2の実施形態におけるチップ領域および対応するダイシング領域の拡大図である。

【発明を実施するための形態】

【0015】

以下に、本発明を実施するための形態について図面を参照して説明する。

【0016】

(第1の実施形態)

図1は、本発明の第1の実施形態の半導体ウエハ1の上面図である。

【0017】

図1に示すように、半導体ウエハ1上の複数のチップ領域10のそれぞれに、DRAMなどの半導体装置に搭載される半導体チップが形成される。

【0018】

図2は、図1に示す領域Aの拡大図である。

【0019】

図2に示すように、複数のチップ領域10がダイシング領域20により区画されている。チップ領域10への半導体チップの形成後、ダイシング領域20は切削され、半導体チップが分離される。

【0020】

チップ領域10には、絶縁膜を有し、その絶縁膜への電圧印加による絶縁破壊により、非導通状態から導通状態へと変化する複数のアンチヒューズを含むアンチヒューズ回路が形成される。以下では、アンチヒューズ回路が形成されるチップ領域10内の領域をアンチヒューズ領域11と称する。また、チップ領域10のうち、アンチヒューズ領域11以外の領域には、例えば、メモリセルが形成される。

【0021】

ダイシング領域20には、メタルなどの配線を有し、その配線へのレーザー照射による切断により、導通状態から非導通状態へと変化する複数のレーザーヒューズを含むレーザーヒューズ回路が、各チップ領域10に対応して形成される。以下では、レーザーヒューズ回路が形成される領域をレーザーヒューズ領域21と称する。なお、図2においては、チップ領域10に対応して、そのチップ領域10の上側にレーザーヒューズ領域21が形成される例を示している。

【0022】

図3は、チップ領域10および対応するレーザーヒューズ領域21の拡大図である。

【0023】

図3に示すように、チップ領域10内のアンチヒューズ領域11には、アンチヒューズ回路12と第1の制御回路13とが形成される。また、レーザーヒューズ領域21には、レーザーヒューズ回路22と第2の制御回路23とが形成される。

【0024】

アンチヒューズ回路12は、複数のアンチヒューズを有する。

【0025】

第1の制御回路13は、第2の制御回路23から出力される、半導体チップへの入力に応じて配線の切断が行われたレーザーヒューズを示すレーザーヒューズカット信号の出力に応じて、図3においては不図示の電源回路による、アンチヒューズ回路12に含まれるアンチヒューズの絶縁膜への電圧の印加を制御する。

【0026】

レーザーヒューズ回路22は、アンチヒューズ回路12に含まれる複数のアンチヒューズの各々に1対1に対応する複数のレーザーヒューズを有する。

【0027】

なお、以下では、アンチヒューズの絶縁膜に電圧を印加して絶縁破壊を起こし、アンチヒューズを非導通状態から導通状態へと変化させること、および、レーザーヒューズの配線にレーザーを照射して切断し、レーザーヒューズを導通状態から非導通状態へと変化させることを、トリミングを行うと称する。

【0028】

第2の制御回路23は、トリミングが行われたレーザーヒューズを示すレーザーヒューズカット信号を第1の制御回路13に出力する。

【0029】

図4Aは、チップ領域内に形成されたレーザーヒューズ回路におけるレーザーヒューズの配置の一例を示す図である。また、図4Bは、本実施形態のレーザーヒューズ回路22におけるレーザーヒューズの配置の一例を示す図である。

【0030】

上述したように、レーザーヒューズのヒューズ窓とその周辺の領域には配線を通すことができないため、レーザーヒューズ間の間隔を小さくして、ヒューズ窓の間隔も小さくすることが、チップ面積を削減するためには好ましい。しかし、ヒューズ窓の間隔が小さくなると、レーザー照射の精度が高いレーザー装置が必要となり、そのようなレーザー装置を用意するには多額の設備投資が必要となるため、コスト面からレーザーヒューズ間の距離を縮小するのは難しい。そのため、チップ領域内にレーザーヒューズを形成する場合には、図4Aに示すように、レーザー装置によるレーザー照射が可能な範囲で、レーザーヒューズ24間の距離が小さくなるように配置される。

【0031】

一方、本実施形態においては、レーザーヒューズ24はダイシング領域20に形成されるため、チップ面積には影響しない。そのため、図4Bに示すように、レーザーヒューズ24間の距離を拡げることができ、レーザー照射の精度の高いレーザー装置が不要となるので、設備投資のコストを抑えることができる。

【0032】

図5は、レーザーヒューズ回路22の構成を示す回路図である。

【0033】

図5に示すレーザーヒューズ回路22は、レーザーヒューズ24−0〜24−11と、N型トランジスタ25−0〜25−11と、P型トランジスタ26と、を有する。

【0034】

レーザーヒューズ24−0は、一端がP型トランジスタ26のドレインに接続され、多端がN型トランジスタ25−0のソースに接続される。

【0035】

N型トランジスタ25−0は、レーザーヒューズ24−0に対応して設けられ、ゲートには図5においては不図示の第2の制御回路23が接続されてヒューズ選択信号が入力され、ソースにはレーザーヒューズ24−0の多端が接続され、ドレインにはグランドが接続される。

【0036】

なお、レーザーヒューズ24−1〜24−11のそれぞれに対応して、N型トランジスタ25−1〜25−11がそれぞれ設けられている。レーザーヒューズ24−1〜24−11と対応するN型トランジスタ25−1〜25−11およびP型トランジスタ26との接続関係は、レーザーヒューズ24−0とN型トランジスタ25−0およびP型トランジスタ26との接続関係と同様であるため、説明を省略する。

【0037】

P型トランジスタ26は、ゲートには第2の制御回路23が接続されてNOR接点イニシャル信号が入力され、ソースには電源が接続され、ドレインにはレーザーヒューズ24−0〜24−11の一端が接続される。P型トランジスタ26のドレインとレーザーヒューズ24−0〜24−11の一端との接点(NOR接点)の電位に応じたレーザーヒューズカット信号が、第2の制御回路23を介して、図5においては不図示の第1の制御回路13に出力される。

【0038】

図6は、レーザーヒューズカット信号のタイミングチャートである。なお、図6においては、図5に示すレーザーヒューズ24−2,24−6,24−10のトリミングが行われているものとする。

【0039】

第2の制御回路23には、クロック(CLK)信号が入力される。

【0040】

第2の制御回路23は、CLK信号の入力に応じてNOR接点イニシャライズ信号およびヒューズ選択信号をLowレベルまたはHighレベルとし、NOR接点イニシャライズ信号をP型トランジスタ26のゲートに入力し、ヒューズ選択信号をN型トランジスタ25−0〜25−11に出力する。なお、以下では、N型トランジスタ25−0に対応し、N型トランジスタ25−0のゲートに入力されるヒューズ選択信号をヒューズ選択信号(0)と称し、N型トランジスタ25−1に対応し、N型トランジスタ25−1のゲートに入力されるヒューズ選択信号をヒューズ選択信号(1)と称し、以下、同様にして、N型トランジスタ25−11に対応し、N型トランジスタ25−11のゲートに入力されるヒューズ選択信号をヒューズ選択信号(11)と称する。

【0041】

時刻t1において、第2の制御回路23は、LowレベルのNOR接点イニシャライズ信号をP型トランジスタ26のゲートに入力し、Lowレベルのヒューズ選択信号(0)からヒューズ選択信号(11)を対応するN型トランジスタ25−0〜25−11のゲートに入力する。

【0042】

LowレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオンとなる。また、Lowレベルのヒューズ選択信号がゲートに入力されることで、N型トランジスタ25−0〜25−11はオフとなり、NOR接点の電位が初期化される。

【0043】

時刻t2において、第2の制御回路23は、NOR接点イニシャライズ信号をLowレベルからHighレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、ヒューズ選択信号(0)をLowレベルからHighレベルとし、N型トランジスタ25−0のゲートに入力するとともに、Lowレベルのヒューズ選択信号(1)からヒューズ選択信号(11)を対応するN型トランジスタ25−1〜25−11のゲートに入力する。

【0044】

HighレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオフとなる。また、Highレベルのヒューズ選択信号(0)がゲートに入力されることで、N型トランジスタ25−0はオンとなり、Lowレベルのヒューズ選択信号が入力されることで、N型トランジスタ25−1〜25−11はオフとなる。ここで、N型トランジスタ25−0に対応するレーザーヒューズ24−0は導通状態であり、また、N型トランジスタ25−0のドレインにはグランドが接続されているため、NOR接点の電位はLowレベルとなる。したがって、Lowレベルのレーザーヒューズカット信号が出力される。

【0045】

時刻t3において、第2の制御回路23は、NOR接点イニシャライズ信号をHighレベルからLowレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、Lowレベルのヒューズ選択信号(0)からヒューズ選択信号(11)を対応するN型トランジスタ25−0〜25−11のゲートに入力する。

【0046】

LowレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオンとなる。また、Lowレベルのヒューズ選択信号がゲートに入力されることで、N型トランジスタ25−0〜25−11はオフとなり、NOR接点の電位が初期化される。

【0047】

時刻t4において、第2の制御回路23は、NOR接点イニシャライズ信号をLowレベルからHighレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、ヒューズ選択信号(1)をLowレベルからHighレベルとし、N型トランジスタ25−1のゲートに入力するとともに、Lowレベルのヒューズ選択信号(0)およびヒューズ選択信号(2)からヒューズ選択信号(11)を対応するN型トランジスタ25−0およびN型トランジスタ25−2〜25−11のゲートに入力する。

【0048】

HighレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオフとなる。また、Highレベルのヒューズ選択信号(1)がゲートに入力されることで、N型トランジスタ25−1はオンとなり、Lowレベルのヒューズ選択信号が入力されることで、N型トランジスタ25−0,25−2〜25−11はオフとなる。ここで、N型トランジスタ25−1に対応するレーザーヒューズ24−1は導通状態であり、また、N型トランジスタ25−1のドレインにはグランドが接続されているため、NOR接点の電位はLowレベルとなる。したがって、Lowレベルのレーザーヒューズカット信号が出力される。

【0049】

時刻t5において、第2の制御回路23は、NOR接点イニシャライズ信号をHighレベルからLowレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、Lowレベルのヒューズ選択信号(0)からヒューズ選択信号(11)を対応するN型トランジスタ25−0〜25−11のゲートに入力する。

【0050】

LowレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオンとなる。また、Lowレベルのヒューズ選択信号がゲートに入力されることで、N型トランジスタ25−0〜25−11はオフとなり、NOR接点の電位が初期化される。

【0051】

時刻t6において、第2の制御回路23は、NOR接点イニシャライズ信号をLowレベルからHighレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、ヒューズ選択信号(2)をLowレベルからHighレベルとし、N型トランジスタ25−2のゲートに入力するとともに、Lowレベルのヒューズ選択信号(0)、ヒューズ選択信号(1)、および、ヒューズ選択信号(3)からヒューズ選択信号(11)を対応するN型トランジスタ25−0,25−1,25−3〜25−11のゲートに入力する。

【0052】

HighレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオフとなる。また、Highレベルのヒューズ選択信号(2)がゲートに入力されることで、N型トランジスタ25−2はオンとなり、Lowレベルのヒューズ選択信号が入力されることで、N型トランジスタ25−0,25−1,25−3〜15−11はオフとなる。ここで、N型トランジスタ25−2に対応するレーザーヒューズ24−2は非導通状態である。そのため、NOR接点の電位はHighレベルとなる。したがって、Highレベルのレーザーヒューズカット信号が出力される。

【0053】

時刻t7において、第2の制御回路23は、NOR接点イニシャライズ信号をHighレベルからLowレベルとし、P型トランジスタ26のゲートに入力する。また、第2の制御回路23は、Lowレベルのヒューズ選択信号(0)からヒューズ選択信号(11)を対応するN型トランジスタ25−0〜25−11のゲートに入力する。

【0054】

LowレベルのNOR接点イニシャライズ信号がゲートに入力されることで、P型トランジスタ26はオンとなる。また、Lowレベルのヒューズ選択信号がゲートに入力されることで、N型トランジスタ25−0〜25−11はオフとなり、NOR接点の電位が初期化される。

【0055】

以下、同様にして、N型トランジスタ25−3〜25−11それぞれのゲートに、Highレベルのヒューズ選択信号が順に入力される。対応するレーザーヒューズ24が非導通状態である場合には、Highレベルのレーザーヒューズカット信号が出力されるため、レーザーヒューズカット信号の出力をモニタすることで、どのレーザーヒューズ24がトリミングされたかが分かる。

【0056】

図7は、図3に示す各部の構成をより詳細に示す図である。

【0057】

レーザーヒューズ回路22は、レーザーヒューズ24−0〜24−6を有する。なお、図7においては、図5に示すN型トランジスタ25、P型トランジスタ26などについては記載を省略する。

【0058】

アンチヒューズ回路12は、アンチヒューズ14−0〜14−6を有する。ここで、アンチヒューズ14−0はレーザーヒューズ24−0に対応して設けられ、アンチヒューズ14−1はレーザーヒューズ24−1に対応して設けられ、以下、同様にして、アンチヒューズ14−6はレーザーヒューズ24−6に対応して設けられる。すなわち、アンチヒューズ回路12は、レーザーヒューズ回路22が有する複数のレーザーヒューズの各々に1対1に対応する複数のアンチヒューズを有する。

【0059】

第1の制御回路13は、選択制御回路15と、アンチヒューズ回路選択レコーダー16と、アドレスエンコード回路17と、を有する。また、第2の制御回路23は、レーザーヒューズ回路選択レコーダー27を有する。

【0060】

選択制御回路15は、クロック信号およびテスト対象となるレーザーヒューズ回路22を示すヒューズ選択テスト信号を、レーザーヒューズ回路選択レコーダー27、アンチヒューズ回路選択レコーダー16、および、アドレスエンコード回路17に出力する。また、選択制御回路15は、ヒューズ選択テスト信号に示されるレーザーヒューズ回路22に対応するアンチヒューズ回路14に含まれるアンチヒューズ14−0〜14−6にAF STORE信号を入力する。

【0061】

レーザーヒューズ回路選択レコーダー27は、クロック信号およびヒューズ選択テスト信号が入力されると、図3に示す複数のレーザーヒューズ回路22のうち、ヒューズ選択テスト信号に示されるレーザーヒューズ回路22に含まれるレーザーヒューズ24−0〜24−6にレーザーヒューズ回路セット選択信号を入力する。

【0062】

また、レーザーヒューズ回路選択レコーダー27は、クロック信号の入力に応じて、レーザーヒューズ24−0〜24−6のそれぞれに対応する、図7においては不図示のN型トランジスタ25のゲートにヒューズ選択信号を入力する。ここで、レーザーヒューズ回路選択レコーダー27は、レーザーヒューズ24−0から順に、各レーザーヒューズ24に対応するN型トランジスタ25のゲートに入力するヒューズ選択信号の論理レベルをクロック毎に変えて入力する。ヒューズ選択信号および図7においては記載を省略したNOR接点イニシャライズ信号の入力に応じて、ヒューズ回路22からは、レーザーヒューズがトリミングされているか否かに応じて論理レベルの異なるレーザーヒューズカット信号が出力される。

【0063】

アンチヒューズ回路選択レコーダー16は、ヒューズ選択テスト信号に示されるレーザーヒューズ回路22に含まれるレーザーヒューズ24に対応するアンチヒューズ14にアンチヒューズ回路セット選択信号を出力する。

【0064】

アドレスエンコード回路17は、レーザーヒューズ回路22から出力されるレーザーヒューズカット信号に示されるトリミングが行われたレーザーヒューズ24に対応するアンチヒューズ14にアドレス信号を出力する。

【0065】

AF STORE信号およびアドレス信号が入力されたアンチヒューズ14においては、絶縁膜に電圧が印加され、トリミングが行われる。

【0066】

次に、チップ領域にレーザーヒューズ回路を有する半導体チップを形成した場合(従来仕様1)、チップ領域にアンチヒューズ回路を有する半導体チップを形成した場合(従来仕様2)、および、ダイシング領域にレーザーヒューズ回路を形成し、チップ領域にアンチヒューズ回路を有する半導体チップを形成した場合(本発明に係る仕様)のそれぞれについて、半導体チップの形成後の工程について説明する。

【0067】

まず、従来仕様1に係る半導体チップの形成後の工程について、図8Aを参照して説明する。

【0068】

半導体チップの形成後、ウエハ状態のまま、高温雰囲気中で熱的ストレスおよび電気的ストレスを各半導体チップに印加して不良を加速判別するWLBI(Wafer Lebel Burn In)工程が行われる(ステップS101)。

【0069】

次に、テスト対象の半導体チップにプローブを介して所定の電気信号を入力することにより、半導体チップのメモリセルから不良メモリセルを検出し、不良メモリセルのアドレスを特定するWT(Wafer Test)工程が行われる(ステップS102)。

【0070】

次に、特定した不良メモリセルのアドレスを半導体チップに入力してレーザーヒューズ回路に記憶させるために、不良メモリセルのアドレスに対応するレーザーヒューズをトリミングするレーザーヒューズトリミング工程が行われる(ステップS103)。

【0071】

次に、半導体ウエハにおけるダイシング領域を切削するダイシング工程が行われ(ステップS104)、半導体チップが分離される。ダイシング工程の後、分離された各半導体チップが良品か不良品かを判別する単体判別工程が行われる(ステップS105)。

【0072】

次に、従来仕様2に係る半導体チップの形成後の工程について、図8Bを参照して説明する。なお、図8Bにおいて、図8Aと同様の処理については同じ符号を付し、説明を省略する。

【0073】

WT工程が行われた後、特定した不良メモリセルのアドレスを半導体チップに入力してアンチヒューズ回路に記憶させるために、アンチヒューズをトリミングするアンチヒューズトリミング工程が行われる(ステップS201)。ステップS201でのアンチヒューズトリミング工程においては、アンチヒューズのトリミングを行うテスタ装置に不良メモリセルのアドレスを入力し、その入力に応じてアンチヒューズのトリミングが行われる。ここで、一般に、テスタ装置には半導体チップ毎にしか不良メモリセルのアドレスの入力を行うことができない。そのため、アンチヒューズトリミング工程は半導体チップ装置毎にしか行うことができず、図8Aに示すレーザーヒューズトリミング工程と比較して時間がかかる。

【0074】

アンチヒューズトリミング工程の後、ダイシング工程および単体選別工程が行われる。

【0075】

次に、本発明に係る仕様に係る半導体チップの形成後の工程について、図8Cを参照して説明する。なお、図8Cにおいて、図8Aおよび図8Bと同様処理については同じ符号を付し、説明を省略する。

【0076】

WT工程の後、特定した不良メモリセルのアドレスを、ダイシング領域21に形成されたレーザーヒューズ回路22に記憶させるために、レーザーヒューズをトリミングするレーザーヒューズトリミング工程が行われる(ステップS301)。

【0077】

次に、アンチヒューズ回路12に含まれるアンチヒューズのうち、レーザーヒューズカット信号に示されるレーザーヒューズに対応するアンチヒューズをトリミングするアンチヒューズトリミング工程が行われる(ステップS302)。

【0078】

上述したように、ステップS301のレーザーヒューズトリミング工程においては、半導体チップ毎の不良メモリセルのアドレスの入力は不要であり、また、ステップS302のアンチヒューズトリミング工程においては、レーザーヒューズトリミング工程でトリミングされたレーザーヒューズに対応するアンチヒューズをトリミングするものであるため、上述したテスタ装置への不良メモリセルのアドレスの入力などが不要である。そのため、本発明に係る仕様においては、従来仕様2と比較して、アンチヒューズ回路がチップ領域に形成されている点では共通するが、アンチヒューズ回路に不良メモリセルのアドレスを記憶させる際の時間を短くすることができる。

【0079】

アンチヒューズトリミング工程の後、ダイシング工程および単体選別工程が行われる。

【0080】

図9は、従来仕様1および従来仕様2と本発明に係る仕様との比較を示す図である。

【0081】

チップ面積に関しては、従来仕様2および本発明に係る仕様においては、従来仕様1のようにレーザーヒューズのヒューズ窓とその周辺の領域には配線を通すことができないという制約が無いため、チップ面積の削減を図ることができる。なお、本発明に係る仕様においては、従来仕様2と比較して、チップ領域に11に第1の制御回路13を設ける必要があるため、若干、チップ面積が大きくなる。

【0082】

トリミング工程に関しては、従来仕様1および従来仕様2においては、図8Aに示すステップS103のレーザーヒューズトリミング工程、あるいは、図8Bに示すステップS201のアンチヒューズトリミング工程の1つの工程で済むのに対し、本発明に係る仕様においては、図8Cに示すステップS301のレーザーヒューズトリミング工程およびステップS302のアンチヒューズトリミング工程の2つの工程が必要となる。

【0083】

トリミング時間に関しては、従来仕様1および本発明に係る仕様においては、従来仕様2のように不良メモリセルのアドレスのテスタ装置への入力を半導体チップ毎に行う必要が無いため、トリミング時間を小さくすることができる。なお、本発明に係る仕様においては、従来仕様1と比較して、レーザーヒューズをトリミングして、不良メモリセルのアドレスを記憶させた後、トリミングしたレーザーヒューズに対応するアンチヒューズをトリミングする必要があるため、若干、トリミング時間が長くなる。

【0084】

テストコストに関しても、従来仕様1および本発明に係る仕様においては、従来仕様2のようにテスタ装置を用いて半導体装置毎にテストを行う必要が無いため、テストコストを小さくすることができる。

【0085】

設備投資に関しては、従来仕様1においては、チップ面積を小さくするためにレーザーヒューズ間の間隔を小さくすると、ヒューズ窓の間隔も小さくなり、レーザー照射の精度の高いレーザー装置が必要となるため、多額の設備投資が必要となる。従来仕様2においては、アンチヒューズをトリミングするための制御は単純であるため、安価なテスタ装置を用いてトリミングすることが可能であり、設備投資を抑制することができる。また、本発明に係る仕様においては、ダイシング領域にレーザーヒューズ回路が形成されているため、レーザーヒューズ間の間隔を小さくする必要がなくなり、レーザー装置に求められるレーザー照射の精度も高くない。そのため、安価なレーザー装置を用いることが可能となり、設備投資を抑制することができる。

【0086】

上述したように、本発明に係る仕様においては、チップ面積を小さくすることができるとともに、トリミング時間、テストコスト、設備投資なども小さくすることができるので、総合的に見て、従来仕様1および従来仕様2と比較して、半導体チップのデバイスコストを小さくすることができる。

【0087】

このように本実施形態によれば、半導体ウエハのチップ領域10に複数のアンチヒューズ14からなるアンチヒューズ回路12を形成し、ダイシング領域20に複数のアンチヒューズ14の各々に対応する複数のレーザーヒューズ24からなるレーザーヒューズ回路24を形成し、半導体チップへの入力に応じてトリミングが行われたレーザーヒューズ24に対応するアンチヒューズ14のトリミングが行われた後に、ダイシング領域20を切削して半導体チップを製造する。

【0088】

そのため、チップ領域にはレーザーヒューズ回路22が形成されることがないので、チップ面積を削減することができる。また、レーザーヒューズ回路22はダイシング領域に形成されているため、レーザーヒューズ24間の間隔を拡げることができ、レーザー照射の精度が高くない安価なレーザー装置を用いることができるので、設備投資を抑制することができる。また、レーザーヒューズ24のトリミングを行って不良メモリセルのアドレスを記憶させた後、トリミングされたレーザーヒューズ24に対応するアンチヒューズ14のトリミングを行うため、不良メモリセルのアドレスのテスタ装置への入力を半導体チップ毎に行う必要がなくなり、半導体チップへの入力を記憶させるのに要する時間を削減することができる。

【0089】

(第2の実施形態)

アンチヒューズを有する半導体チップにおいては、アンチヒューズの絶縁膜に電圧を印加して絶縁破壊を起こすために、半導体チップを動作させるために用いられる電源回路とは異なる特殊電源回路や特殊電源回路からアンチヒューズの絶縁膜に電圧を印加するための特殊電源パッドが、チップ領域に設けられることがある。

【0090】

図10は、特殊電源回路および特殊電源回路を有する半導体チップの構成の一例を示す図である。

【0091】

図10に示す半導体チップは、チップ領域10内に、メモリバンク31と、X−Fuse回路32と、Y−Fuse回路33と、特殊電源回路34と、特殊電源パッド35と、を有する。

【0092】

メモリバンク31は、複数のメモリセルがアレイ状に配置された構成を有する。

【0093】

X−Fuse回路32は、複数のアンチヒューズ14からなり、各メモリバンク31に対応して設けられている。X−Fuse回路32は、対応するメモリバンク31における不良メモリセルのロウアドレスを記憶する。

【0094】

Y−Fuse回路33は、複数のアンチヒューズ14からなり、各メモリバンク31に対応して設けられている。Y−Fuse回路33は、対応するメモリバンク31における不良メモリセルのカラムアドレスを記憶する。

【0095】

特殊電源回路34は、X−Fuse回路32およびY−Fuse回路33に含まれるアンチヒューズの絶縁膜に、特殊電源パッド35を介して印加する電圧を供給する。

【0096】

図10に示すように、特殊電源回路34および特殊電源パッド35は、チップ領域10内に形成されているが、アンチヒューズ14のトリミングが行われた後は、不要となる。

【0097】

そこで、本実施形態においては、図11に示すように、特殊電源回路34などをチップ領域10ではなく、ダイシング領域に20設ける。

【0098】

図11は、本発明の第2の実施形態におけるチップ領域10およびダイシング領域20の拡大図である。なお、図11において、図10と同様の構成については同じ符号を付し、説明を省略する。また、図11においては、第1の制御回路13、レーザーヒューズ回路22、第2の制御回路23などについては記載を省略する。

【0099】

図11に示すように、本実施形態においては、特殊電源回路34がダイシング領域20に形成される。特殊電源回路34をダイシング領域に形成することで、チップ面積の削減を図ることができる。

【0100】

なお、図11においては、特殊電源回路34だけをダイシング領域20に形成する例を用いて説明したが、特殊電源パッド35についても、ダイシング領域20に形成することで、さらにチップ面積の削減を図ることができる。

【0101】

このように本実施形態によれは、半導体ウエハのダイシング領域に、アンチヒューズ14の絶縁膜に電圧を印加するための特殊電源回路34、特殊電源パッド35を設ける。

【0102】

アンチヒューズ14のトリミングが行われた後は、特殊電源回路34や特殊電源パッド35は不要となるため、これらをダイシング領域20に設けることで、チップ面積の削減を図ることができる。

【0103】

なお、本実施形態においては、アンチヒューズ14のトリミングを行うための特殊電源回路34や特殊電源パッド35をダイシング領域20に設ける例を用いて説明したが、これに限られるものではない。例えば、WLBI工程において、半導体チップに電気的なストレスを印加するための電源回路や電源パッドなども、WLBI工程が終了した後は不要となるので、ダイシング領域に設けることで、半導体チップのチップ面積の削減を図ることができる。

【符号の説明】

【0104】

1 半導体ウエハ

10 チップ領域

11 アンチヒューズ領域

12 アンチヒューズ回路

13 第1の制御回路

14 アンチヒューズ

15 選択制御回路

16 アンチヒューズ回路選択レコーダー

17 アドレスエンコード回路

20 ダイシング領域

21 レーザーヒューズ領域

22 レーザーヒューズ回路

23 第2の制御回路

24,24−0〜24−11 レーザーヒューズ

25,25−0〜25−11 N型トランジスタ

26 P型トランジスタ

27 レーザーヒューズ回路選択レコーダー

31 メモリバンク

32 X−Fuse回路

33 Y−Fuse回路

34 特殊電源回路

35 特殊電源パッド

【特許請求の範囲】

【請求項1】

半導体チップが形成される複数のチップ領域と、前記複数のチップ領域を区画するダイシング領域と、からなる半導体ウエハであって、

前記チップ領域に形成され、絶縁膜を有し、電圧の印加による前記絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズを有するアンチヒューズ回路と、

前記ダイシング領域に前記複数のアンチヒューズの各々に対応して形成され、配線を有し、レーザー照射による前記配線の切断により非導通状態となる複数のレーザーヒューズを有するレーザーヒューズ回路と、

前記複数のアンチヒューズのうち、前記半導体チップへの入力に応じて非導通状態とされたレーザーヒューズに対応する前記アンチヒューズの有する前記絶縁膜に、電源からの電圧を印加させて、前記アンチヒューズを導通状態とする制御回路と、を有することを特徴とする半導体ウエハ。

【請求項2】

請求項1記載の半導体ウエハであって、

前記電源は、前記ダイシング領域に形成されることを特徴とする半導体ウエハ。

【請求項3】

請求項1または2記載の半導体ウエハであって、

前記ダイシング領域に形成され、前記電源から前記アンチヒューズ素子の有する前記絶縁膜への電圧の印加を行うための電源パッドを有することを特徴とする半導体ウエハ。

【請求項4】

請求項1から3のいずれか1項に記載の前記ダイシング領域を切削することで分離された前記半導体チップを搭載する半導体装置。

【請求項5】

半導体チップが搭載される半導体装置の製造方法であって、

前記半導体チップが製造される半導体ウエハ上の複数のチップ領域のそれぞれに、絶縁膜を有し、電圧の印加による前記絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズからなるアンチヒューズ回路を形成する工程と、

前記複数のチップ領域を区画するダイシング領域に、前記複数のアンチヒューズの各々に対応して、配線を有し、レーザー照射による前記配線の切断により非導通状態となる複数のレーザーヒューズからなるレーザーヒューズ回路を形成する工程と、

前記半導体チップへの入力に応じて、前記レーザーヒューズが有する配線へのレーザー照射を行い、前記レーザーヒューズを非導通状態とする工程と、

前記非導通状態であるレーザーヒューズに対応する前記アンチヒューズが有する前記絶縁膜に、電源からの電圧を印加させて、前記アンチヒューズを導通状態とする工程と、

前記ダイシング領域を切削して、前記チップ領域に形成された前記半導体チップを分離する工程と、を有することを特徴とする半導体装置の製造方法。

【請求項1】

半導体チップが形成される複数のチップ領域と、前記複数のチップ領域を区画するダイシング領域と、からなる半導体ウエハであって、

前記チップ領域に形成され、絶縁膜を有し、電圧の印加による前記絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズを有するアンチヒューズ回路と、

前記ダイシング領域に前記複数のアンチヒューズの各々に対応して形成され、配線を有し、レーザー照射による前記配線の切断により非導通状態となる複数のレーザーヒューズを有するレーザーヒューズ回路と、

前記複数のアンチヒューズのうち、前記半導体チップへの入力に応じて非導通状態とされたレーザーヒューズに対応する前記アンチヒューズの有する前記絶縁膜に、電源からの電圧を印加させて、前記アンチヒューズを導通状態とする制御回路と、を有することを特徴とする半導体ウエハ。

【請求項2】

請求項1記載の半導体ウエハであって、

前記電源は、前記ダイシング領域に形成されることを特徴とする半導体ウエハ。

【請求項3】

請求項1または2記載の半導体ウエハであって、

前記ダイシング領域に形成され、前記電源から前記アンチヒューズ素子の有する前記絶縁膜への電圧の印加を行うための電源パッドを有することを特徴とする半導体ウエハ。

【請求項4】

請求項1から3のいずれか1項に記載の前記ダイシング領域を切削することで分離された前記半導体チップを搭載する半導体装置。

【請求項5】

半導体チップが搭載される半導体装置の製造方法であって、

前記半導体チップが製造される半導体ウエハ上の複数のチップ領域のそれぞれに、絶縁膜を有し、電圧の印加による前記絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズからなるアンチヒューズ回路を形成する工程と、

前記複数のチップ領域を区画するダイシング領域に、前記複数のアンチヒューズの各々に対応して、配線を有し、レーザー照射による前記配線の切断により非導通状態となる複数のレーザーヒューズからなるレーザーヒューズ回路を形成する工程と、

前記半導体チップへの入力に応じて、前記レーザーヒューズが有する配線へのレーザー照射を行い、前記レーザーヒューズを非導通状態とする工程と、

前記非導通状態であるレーザーヒューズに対応する前記アンチヒューズが有する前記絶縁膜に、電源からの電圧を印加させて、前記アンチヒューズを導通状態とする工程と、

前記ダイシング領域を切削して、前記チップ領域に形成された前記半導体チップを分離する工程と、を有することを特徴とする半導体装置の製造方法。

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図8A】

【図8B】

【図8C】

【図9】

【図10】

【図11】

【図1】

【図3】

【図4A】

【図4B】

【図5】

【図6】

【図7】

【図8A】

【図8B】

【図8C】

【図9】

【図10】

【図11】

【図1】

【公開番号】特開2013−84327(P2013−84327A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−224904(P2011−224904)

【出願日】平成23年10月12日(2011.10.12)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月12日(2011.10.12)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]