半導体ウエハの製造方法

【課題】 従来の超接合構造のウエハの製造方法は、半導体ウエハの厚み方向に多段階にエピタキシャル層を形成する工程とイオン注入工程が必要となり、工程数が多くなる。また、pn接合面は、波状となり、空乏層の広がりが均一になりにくい問題がある。一方、一部のピラー状の半導体層を斜めイオン注入で形成する方法の場合、超接合構造を多数配置することが困難である。

【解決手段】 半導体基板上に、n型エピタキシャル層形成とエッチングおよびp型エピタキシャル層形成とエッチングを交互に、少なくとも3回以上行い、全ての半導体層をエピタキシャル層で形成する。これにより、各半導体層の不純物濃度プロファイルを均一にでき、pn接合面をウエハ表面に対して垂直に形成できる。更に各半導体層の幅を狭く形成できるので、不純物濃度が高められるため高耐圧、且つ低抵抗が実現できる。

【解決手段】 半導体基板上に、n型エピタキシャル層形成とエッチングおよびp型エピタキシャル層形成とエッチングを交互に、少なくとも3回以上行い、全ての半導体層をエピタキシャル層で形成する。これにより、各半導体層の不純物濃度プロファイルを均一にでき、pn接合面をウエハ表面に対して垂直に形成できる。更に各半導体層の幅を狭く形成できるので、不純物濃度が高められるため高耐圧、且つ低抵抗が実現できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体ウエハの製造方法に係り、特に高耐圧で低オン抵抗を実現する半導体ウエハの製造工程の短縮化、および特性向上を実現する半導体ウエハの製造方法に関する。

【背景技術】

【0002】

高耐圧で低オン抵抗を実現するシリコン半導体ウエハとして、ピラー状にp型半導体領域とn型半導体領域を設けて、ウエハ表面に対して垂直に、複数のpn接合を形成したウエハ構造が知られている(例えば特許文献1参照)。

【0003】

これらは、p型半導体領域とn型半導体領域の不純物濃度および幅が所望の値に選択することにより、逆方向電圧印加時にはpn接合で高耐圧を実現できる。以下このような構造を、超接合(スーパージャンクション)構造と称して説明する。

【0004】

図7および図8を参照して超接合構造のウエハの製造方法の一例を説明する。

【0005】

図7を参照して、n+型半導体基板11を準備し、この表面に例えばn型半導体層(エピタキシャル層)12’を6μm程度積層する。所定の間隔で開口したマスクを設けてp型不純物を注入し、p型半導体領域13’を形成する(図7(A))。

【0006】

そしてn型半導体層12’の積層(エピタキシャル成長)工程と、p型不純物の注入工程を例えば7回程度繰り返し、所望の厚み(例えば42μm程度)の多段エピタキシャル層を形成し、最後にp型不純物を拡散し、ピラー状のn型半導体領域12と、p型半導体領域13とが交互に配置された超接合構造のウエハ20を形成する(図7(B))。

【0007】

また、以下の方法も知られている。

【0008】

図8を参照して、例えばn+型半導体基板21上にn型半導体層(エピタキシャル層)22を所望の厚みに積層し、n型半導体層がピラー状に残存するように複数のトレンチ23を形成する(図8(A))。その後、トレンチ23側壁に露出したn型半導体層22に、p型不純物の斜めイオン注入を行い、ピラー状のp型半導体領域24を設ける(図8(B))。更にp型半導体領域24間に絶縁膜25を埋め込み、超接合構造のウエハ30を得る(図8(C))。

【特許文献1】国際公開第02/067333号パンフレット

【発明の開示】

【発明が解決しようとする課題】

【0009】

図7の如く、超接合構造を有するウエハを得る従来の方法は、半導体ウエハの厚み方向に多段階にエピタキシャル層を形成する工程とイオン注入・拡散工程が必要となり、非常に工程数が多くなる問題がある。

【0010】

また、ピラー状の半導体領域は、実際には不純物の拡散領域を多層に積層した形状であるので、ピラーの側面(pn接合面)は、波状となり、空乏層の広がりが厳密には均一になりにくい問題がある。

【0011】

一方、図8の如く、一部のピラー状の半導体層を斜めイオン注入で形成する方法の場合、イオン注入で形成された、例えばp型半導体層の不純物プロファイルを、ウエハ垂直方向に均一にするために図8(A)のように溝の幅を広げる必要がある。そのため超接合構造を多数配置することは困難である。

【課題を解決するための手段】

【0012】

本発明はかかる課題に鑑みてなされ、第1に、一導電型半導体基板を準備し、該半導体基板上に第1のエピタキシャル層を形成する工程と、前記第1のエピタキシャル層に、トレンチを複数形成し、第1半導体層を形成する工程と、前記第1のエピタキシャル層と異なる導電型の第2エピタキシャル層を形成する工程と、前記第2エピタキシャル層を全面異方性エッチングして前記第1半導体層に隣接する第2半導体層を形成する工程と、前記第1のエピタキシャル層と同導電型の第3のエピタキシャル層を形成する工程と、前記第3のエピタキシャル層を全面異方性エッチングし、前記第2半導体層に隣接する第3の半導体層を形成する工程と、を具備し、半導体ウエハ表面に対して垂直方向に複数のpn接合を形成することにより解決するものである。

【発明の効果】

【0013】

本発明によれば、以下の効果が得られる。

【0014】

第1に、超接合を形成するp型半導体層およびn型半導体層の全てが、エピタキシャル成長により形成されるので、半導体ウエハの表面に対して垂直方向に不純物濃度プロファイルの均一な、p型半導体層およびn型半導体層が繰り返し配置される構造を実現できる。これにより、空乏層の広がりが均一な超接合を有する半導体ウエハの製造方法を提供できる。

【0015】

第2に、超接合を形成する半導体層は全てエピタキシャル層であるので、pn接合面を、半導体ウエハの表面に対して垂直に形成できる。半導体ウエハの厚み方向に、多段階にエピタキシャル層の形成とイオン注入を繰り返して形成した超接合構造の場合には、pn接合面が実際には波状となり、空乏層の広がりが厳密には均一になりにくい問題がある。しかし、本実施形態ではpn接合面は半導体ウエハ表面に対して垂直面となり、これによっても空乏層の広がりを均一にすることができる。

【0016】

第3に、超接合を形成する全ての半導体層が、エピタキシャル成長により形成されるので、複数のpn接合が存在する半導体ウエハの断面における、各半導体層の幅(短辺の長さ)を所望の値に形成することができる。

【0017】

つまり、それぞれの半導体層の幅を従来より低減することも可能となる。半導体層の幅を狭めることにより、各半導体層中に広がる空乏層がピンチオフする幅も狭くなる。つまり、同じ耐圧を維持する場合には、半導体層の幅を狭めることにより各半導体層の不純物濃度を高めることができる。従って、順方向電圧印加時に電流経路となる半導体ウエハの抵抗をより低減できる。

【0018】

第4に、半導体ウエハの厚み方向に多段階にエピタキシャル成長とイオン注入を行って複数のpn接合を形成する従来方法と比較して、半導体ウエハの製造工程を削減できる。

【発明を実施するための最良の形態】

【0019】

本発明の実施の形態を、図1から図6を参照して、半導体基板がn型シリコン半導体基板の場合を例に、詳細に説明する。

【0020】

本発明の半導体ウエハの製造方法は、一導電型半導体基板を準備し、該半導体基板上に第1のエピタキシャル層を形成する工程と、前記第1のエピタキシャル層に、トレンチを複数形成し、第1半導体層を形成する工程と、前記第1のエピタキシャル層と異なる導電型の第2エピタキシャル層を形成する工程と、前記第2エピタキシャル層を全面異方性エッチングして前記第1半導体層に隣接する第2半導体層を形成する工程と、前記第1のエピタキシャル層と同導電型の第3のエピタキシャル層を形成する工程と、前記第3のエピタキシャル層を全面異方性エッチングし、前記第2半導体層に隣接する第3の半導体層を形成する工程と、から構成される。

【0021】

第1工程(図1):一導電型半導体基板を準備し、半導体基板上に第1のエピタキシャル層を形成する工程。

【0022】

まず、不純物濃度が1×1020cm−3程度の高濃度のn型シリコン半導体基板1を準備する。半導体基板1上に、エピタキシャル成長法により、第1のエピタキシャル層としてn型エピタキシャル層2’を形成する。本工程におけるn型エピタキシャル層2’の厚みが、半導体ウエハの超接合の厚みとなる。n型エピタキシャル層2’の不純物濃度は例えば1×1016cm−3程度であり、厚みは例えば、40μm程度である。

【0023】

第2工程(図2):第1のエピタキシャル層に、トレンチを複数形成し、第1半導体層を形成する工程。

【0024】

n型エピタキシャル層2’表面に、所望の開口幅のマスクを設けて、n型エピタキシャル層2’をドライエッチングする(図2(A))。

【0025】

これにより、例えば半導体基板1が露出する深さのトレンチ3を複数形成する。ドライエッチングは半導体基板1が露出するまで行っても良いし、n型エピタキシャル層2’がトレンチ3の底部に残っても良い。本実施形態では、以下半導体基板1が露出する場合を示す。

【0026】

トレンチ3の開口幅Wtはいずれも例えば30μm程度である。これにより、図2に示す断面において互いに離間した、複数の例えばピラー状のn型の第1半導体層2が形成される。半導体ウエハの表面におけるパターンでストライプ状でもよい。第1半導体層2の幅W1は例えば8μm程度である(図2(B))。

【0027】

トレンチ3形成後、例えば1100℃で10分の熱酸化を行い、その後その熱酸化膜をウェットエッチングにより除去し、トレンチエッチングによるダメージ層を除去する。

【0028】

第3工程(図3):第1のエピタキシャル層と異なる導電型の第2エピタキシャル層を形成する工程。

【0029】

半導体基板1上に、エピタキシャル成長法により、第1のエピタキシャル層2’(第1半導体層2)とは逆導電型の第2のエピタキシャル層(p型エピタキシャル層)4’を形成する。なお、第2工程で第1のエピタキシャル層(n型エピタキシャル層2’)がトレンチ3の底部に残っている場合は、残ったn型エピタキシャル層2’上にp型エピタキシャル層4’を形成する。p型エピタキシャル層4’の不純物濃度は例えば1×1016cm−3程度である。

【0030】

p型エピタキシャル層4’は、ピラー状の第1半導体層2の側面及び上面と、ここでは第1半導体層2間に露出した半導体基板1上を覆って形成される。また、p型エピタキシャル層4’は第1半導体層2の側面における厚み(半導体基板1の水平方向の厚みd1)と、第1半導体層2の上面または半導体基板1表面における厚みd2がほぼ同等となる。

【0031】

第4工程(図4):第2エピタキシャル層を全面異方性エッチングして第1半導体層に隣接する第2半導体層を形成する工程。

【0032】

p型エピタキシャル層4’をマスクを設けずに全面異方性エッチングする。第1半導体層2間の半導体基板1が露出するまでエッチングすることにより、第1半導体層2上面を覆うp型エピタキシャル層4’も除去されて第1半導体層2上面が露出する。なお第2工程で、第1のエピタキシャル層2’がトレンチ3の底部に残っている場合は、残った第1のエピタキシャル層2’が露出するまでエッチングする。この場合最終構造においても、トレンチ3の底部に第1のエピタキシャル層2’が残存する。

【0033】

一方、第1半導体層2の側面のp型エピタキシャル層4’は除去されず、これにより、第1半導体層2の両側に隣接する、ピラー状のp型の第2半導体層4が形成される。第2半導体層4の幅W2は、p型エピタキシャル層4’の厚みd1(=d2)であり、ここでは8μm程度とする。尚、特性に応じて、第1半導体層2の幅W1と、第2半導体層4の幅W2は適宜選択可能である。幅を狭くすると不純物濃度を高くするため、高耐圧、且つ低抵抗が実現できる。

【0034】

尚、本実施形態では、本工程において隣り合う(対向する)第2半導体層4間に、トレンチ状の空間部Sが形成される。

【0035】

第5工程(図5):第1のエピタキシャル層と同導電型の第3のエピタキシャル層を形成する工程。

【0036】

更に、半導体基板1上に、エピタキシャル成長法により、第1のエピタキシャル層2’と同導電型の第3のエピタキシャル層(n型エピタキシャル層)5’を形成する。n型エピタキシャル層5’の不純物濃度は例えば1×1016cm−3程度であり、厚みd3は8μm程度である。

【0037】

n型エピタキシャル層5’は、ピラー状の第2半導体層4の側面及び上面と、第1半導体層2の上面を覆って形成される。そして、隣り合う第2半導体層4間にはn型エピタキシャル層5’が埋め込まれる。つまりこの場合では、n型エピタキシャル層5’の厚みd3を、隣り合う第2半導体層4間(最後に形成されたトレンチ状の空間部S(図4参照))の距離の2分の1の厚みにすることで、第2半導体層4間にn型エピタキシャル層5’が埋め込まれる。本実施形態では、第3のエピタキシャル層3’が空間部S(図4参照)に埋め込まれた場合を示した。しかし、空間部Sに第3のエピタキシャル層3’を(完全)に埋め込む必要はなく、厚みd3を空間部Sの幅の2分の1にしなくても良い。すなわち空間部Sに隙間が残ったままでもよい。

【0038】

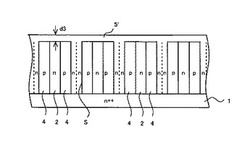

第6工程(図6):第3のエピタキシャル層を全面異方性エッチングし、第2半導体層に隣接する第3の半導体層を形成する工程。

【0039】

n型エピタキシャル層5’をマスクを設けずに全面異方性エッチングする。第1半導体層2および第2半導体層4上面が露出するまでエッチングすることにより、第2半導体層4の両側に隣接する、ピラー状のn型の第3半導体層5が形成される。第3半導体層5の幅W3は、第1半導体層2の幅W1と同等である。つまり、第2工程において、第1半導体層2(第3半導体層)の幅W1および第2半導体層4の幅W2を考慮して、トレンチ3の幅Wtを適切に選択することにより、全てのピラー状の半導体層をエピタキシャル層によって形成することができる。

【0040】

これにより、半導体ウエハ表面に対して垂直方向に複数のpn接合(p型半導体層とn型半導体層による超接合)を有する、すなわち超接合構造の半導体ウエハ10を形成できる。

【0041】

また、本実施形態では、第1半導体層2、第2半導体層4、および第3半導体層5は、エピタキシャル成長法により形成でき、その厚みは自由に制御できる。従って、第1〜第3のエピタキシャル層2’、4’、5’の厚みを薄く形成することも可能である。これにより、第1半導体層2、第2半導体層4、および第3半導体層5は、それぞれ、図6に示す断面、すなわち半導体ウエハ10の複数のpn接合が露出する断面における長辺:短辺のアスペクト比を10:1等にすることもできる。これはすなわち、第1半導体層2、第2半導体層4、および第3半導体層5は、半導体ウエハ10の厚み方向の長さ(長辺)に対して、幅W1、W2、W3(短辺)が非常に薄いことを意味する。

【0042】

各半導体層の幅W1、W2、W3が狭い場合、不純物濃度を高くするため、臨界電界強度が高くなり、高耐圧、且つ低抵抗が実現できる。

【0043】

また、第1〜第3半導体層2、4、5は全てエピタキシャル層であるので、半導体ウエハ10の深さ方向の不純物濃度プロファイルが均一となり、イオン注入によって形成した超接合構造の場合と比較して、空乏層の広がりを均一にできる。

【0044】

更に、第1〜第3半導体層2、4、5は全てエピタキシャル層であるので、pn接合面を、半導体ウエハ10の表面に対して垂直に形成できる。図7に示す如く、半導体ウエハの厚み方向に、多段階にエピタキシャル層の形成とイオン注入を繰り返して形成した超接合構造の場合には、pn接合面が実際には波状となり、空乏層の広がりが厳密には均一になりにくい問題がある。しかし、本実施形態ではpn接合面は半導体ウエハ表面に対して垂直面となり、これによっても空乏層の広がりを均一にすることができる。

【0045】

尚、図6において、第2半導体層4間に第3半導体層5が埋設され、半導体ウエハ10が完成する場合を例に説明したが、トレンチ3の開口幅Wtが広い場合は、更に繰り返してピラー状の半導体層を形成してもよい。

【0046】

つまり、上記の第3工程から第6工程の繰り返しにより、他のエピタキシャル層(たとえばp型エピタキシャル層)を形成する工程と、当該エピタキシャル層をエッチング工程を繰り返し、他のピラー状の半導体層を交互に隣接して形成する。

【0047】

つまり、第3半導体層5を形成した後、p型エピタキシャル層を形成してp型エピタキシャル層をエッチングし、他のピラー状のp型半導体層を形成する。更にn型エピタキシャル層を形成してn型エピタキシャル層をエッチングし、他のピラー状のn型半導体層を形成してもよく、これらが交互になるように更にp型半導体層とn型半導体層を形成してもよい。

【0048】

なお第2工程で、第1のエピタキシャル層2’がトレンチ3の底部に残っている場合はそれ以降の工程でピラー状のp型半導体層またはピラー状のn型半導体層を形成する際には、トレンチ3の底部に残った第1のエピタキシャル層2’が露出するまでエッチングする。

【0049】

このように、本実施形態の半導体ウエハの製造方法は、半導体基板1上に、n型エピタキシャル層形成とエッチングおよびp型エピタキシャル層形成とエッチングを交互に、少なくとも3回以上行い、全てのピラー状の半導体層をエピタキシャル層で形成するものである。

【0050】

全てのピラー状の半導体層はエピタキシャル層によって形成されるので、それらの幅を所望の幅に形成できる。つまり、各半導体層の幅を狭めることも可能となり、不純物濃度を高めることができるため、高耐圧且つ低抵抗が実現できる。

【0051】

また、各半導体層の不純物濃度プロファイルが均一となり、pn接合面が半導体ウエハ10表面に対して垂直に形成されるので、空乏層の広がりを均一にでき、超接合構造の特性を十分に生かせる半導体ウエハの製造方法を提供できる。

【0052】

以上、本実施形態では、半導体基板1としてn型シリコン半導体基板を用いた場合を例に説明したが、p型シリコン半導体基板であってもよい。また、第1工程でn型半導体層(エピタキシャル層)を形成した場合を例に説明したが、これがp型半導体層であっても同様に実施できる。

【図面の簡単な説明】

【0053】

【図1】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図2】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図3】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図4】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図5】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図6】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図7】従来の半導体ウエハの製造方法を説明する断面図である。

【図8】従来の半導体ウエハの製造方法を説明する断面図である。

【符号の説明】

【0054】

1 半導体基板

2’ 第1のエピタキシャル層

2 第1半導体層

3 トレンチ

4’ 第2のエピタキシャル層

4 第2半導体層

5’ 第3のエピタキシャル層

5 第3半導体層

M マスク

W1 第1半導体層幅

W2 第2半導体層幅

Wt トレンチ幅

d1、d2 第2のエピタキシャル層厚み

d3 第3のエピタキシャル層厚み

e’ 他のエピタキシャル層

e 他の半導体層

【技術分野】

【0001】

本発明は、半導体ウエハの製造方法に係り、特に高耐圧で低オン抵抗を実現する半導体ウエハの製造工程の短縮化、および特性向上を実現する半導体ウエハの製造方法に関する。

【背景技術】

【0002】

高耐圧で低オン抵抗を実現するシリコン半導体ウエハとして、ピラー状にp型半導体領域とn型半導体領域を設けて、ウエハ表面に対して垂直に、複数のpn接合を形成したウエハ構造が知られている(例えば特許文献1参照)。

【0003】

これらは、p型半導体領域とn型半導体領域の不純物濃度および幅が所望の値に選択することにより、逆方向電圧印加時にはpn接合で高耐圧を実現できる。以下このような構造を、超接合(スーパージャンクション)構造と称して説明する。

【0004】

図7および図8を参照して超接合構造のウエハの製造方法の一例を説明する。

【0005】

図7を参照して、n+型半導体基板11を準備し、この表面に例えばn型半導体層(エピタキシャル層)12’を6μm程度積層する。所定の間隔で開口したマスクを設けてp型不純物を注入し、p型半導体領域13’を形成する(図7(A))。

【0006】

そしてn型半導体層12’の積層(エピタキシャル成長)工程と、p型不純物の注入工程を例えば7回程度繰り返し、所望の厚み(例えば42μm程度)の多段エピタキシャル層を形成し、最後にp型不純物を拡散し、ピラー状のn型半導体領域12と、p型半導体領域13とが交互に配置された超接合構造のウエハ20を形成する(図7(B))。

【0007】

また、以下の方法も知られている。

【0008】

図8を参照して、例えばn+型半導体基板21上にn型半導体層(エピタキシャル層)22を所望の厚みに積層し、n型半導体層がピラー状に残存するように複数のトレンチ23を形成する(図8(A))。その後、トレンチ23側壁に露出したn型半導体層22に、p型不純物の斜めイオン注入を行い、ピラー状のp型半導体領域24を設ける(図8(B))。更にp型半導体領域24間に絶縁膜25を埋め込み、超接合構造のウエハ30を得る(図8(C))。

【特許文献1】国際公開第02/067333号パンフレット

【発明の開示】

【発明が解決しようとする課題】

【0009】

図7の如く、超接合構造を有するウエハを得る従来の方法は、半導体ウエハの厚み方向に多段階にエピタキシャル層を形成する工程とイオン注入・拡散工程が必要となり、非常に工程数が多くなる問題がある。

【0010】

また、ピラー状の半導体領域は、実際には不純物の拡散領域を多層に積層した形状であるので、ピラーの側面(pn接合面)は、波状となり、空乏層の広がりが厳密には均一になりにくい問題がある。

【0011】

一方、図8の如く、一部のピラー状の半導体層を斜めイオン注入で形成する方法の場合、イオン注入で形成された、例えばp型半導体層の不純物プロファイルを、ウエハ垂直方向に均一にするために図8(A)のように溝の幅を広げる必要がある。そのため超接合構造を多数配置することは困難である。

【課題を解決するための手段】

【0012】

本発明はかかる課題に鑑みてなされ、第1に、一導電型半導体基板を準備し、該半導体基板上に第1のエピタキシャル層を形成する工程と、前記第1のエピタキシャル層に、トレンチを複数形成し、第1半導体層を形成する工程と、前記第1のエピタキシャル層と異なる導電型の第2エピタキシャル層を形成する工程と、前記第2エピタキシャル層を全面異方性エッチングして前記第1半導体層に隣接する第2半導体層を形成する工程と、前記第1のエピタキシャル層と同導電型の第3のエピタキシャル層を形成する工程と、前記第3のエピタキシャル層を全面異方性エッチングし、前記第2半導体層に隣接する第3の半導体層を形成する工程と、を具備し、半導体ウエハ表面に対して垂直方向に複数のpn接合を形成することにより解決するものである。

【発明の効果】

【0013】

本発明によれば、以下の効果が得られる。

【0014】

第1に、超接合を形成するp型半導体層およびn型半導体層の全てが、エピタキシャル成長により形成されるので、半導体ウエハの表面に対して垂直方向に不純物濃度プロファイルの均一な、p型半導体層およびn型半導体層が繰り返し配置される構造を実現できる。これにより、空乏層の広がりが均一な超接合を有する半導体ウエハの製造方法を提供できる。

【0015】

第2に、超接合を形成する半導体層は全てエピタキシャル層であるので、pn接合面を、半導体ウエハの表面に対して垂直に形成できる。半導体ウエハの厚み方向に、多段階にエピタキシャル層の形成とイオン注入を繰り返して形成した超接合構造の場合には、pn接合面が実際には波状となり、空乏層の広がりが厳密には均一になりにくい問題がある。しかし、本実施形態ではpn接合面は半導体ウエハ表面に対して垂直面となり、これによっても空乏層の広がりを均一にすることができる。

【0016】

第3に、超接合を形成する全ての半導体層が、エピタキシャル成長により形成されるので、複数のpn接合が存在する半導体ウエハの断面における、各半導体層の幅(短辺の長さ)を所望の値に形成することができる。

【0017】

つまり、それぞれの半導体層の幅を従来より低減することも可能となる。半導体層の幅を狭めることにより、各半導体層中に広がる空乏層がピンチオフする幅も狭くなる。つまり、同じ耐圧を維持する場合には、半導体層の幅を狭めることにより各半導体層の不純物濃度を高めることができる。従って、順方向電圧印加時に電流経路となる半導体ウエハの抵抗をより低減できる。

【0018】

第4に、半導体ウエハの厚み方向に多段階にエピタキシャル成長とイオン注入を行って複数のpn接合を形成する従来方法と比較して、半導体ウエハの製造工程を削減できる。

【発明を実施するための最良の形態】

【0019】

本発明の実施の形態を、図1から図6を参照して、半導体基板がn型シリコン半導体基板の場合を例に、詳細に説明する。

【0020】

本発明の半導体ウエハの製造方法は、一導電型半導体基板を準備し、該半導体基板上に第1のエピタキシャル層を形成する工程と、前記第1のエピタキシャル層に、トレンチを複数形成し、第1半導体層を形成する工程と、前記第1のエピタキシャル層と異なる導電型の第2エピタキシャル層を形成する工程と、前記第2エピタキシャル層を全面異方性エッチングして前記第1半導体層に隣接する第2半導体層を形成する工程と、前記第1のエピタキシャル層と同導電型の第3のエピタキシャル層を形成する工程と、前記第3のエピタキシャル層を全面異方性エッチングし、前記第2半導体層に隣接する第3の半導体層を形成する工程と、から構成される。

【0021】

第1工程(図1):一導電型半導体基板を準備し、半導体基板上に第1のエピタキシャル層を形成する工程。

【0022】

まず、不純物濃度が1×1020cm−3程度の高濃度のn型シリコン半導体基板1を準備する。半導体基板1上に、エピタキシャル成長法により、第1のエピタキシャル層としてn型エピタキシャル層2’を形成する。本工程におけるn型エピタキシャル層2’の厚みが、半導体ウエハの超接合の厚みとなる。n型エピタキシャル層2’の不純物濃度は例えば1×1016cm−3程度であり、厚みは例えば、40μm程度である。

【0023】

第2工程(図2):第1のエピタキシャル層に、トレンチを複数形成し、第1半導体層を形成する工程。

【0024】

n型エピタキシャル層2’表面に、所望の開口幅のマスクを設けて、n型エピタキシャル層2’をドライエッチングする(図2(A))。

【0025】

これにより、例えば半導体基板1が露出する深さのトレンチ3を複数形成する。ドライエッチングは半導体基板1が露出するまで行っても良いし、n型エピタキシャル層2’がトレンチ3の底部に残っても良い。本実施形態では、以下半導体基板1が露出する場合を示す。

【0026】

トレンチ3の開口幅Wtはいずれも例えば30μm程度である。これにより、図2に示す断面において互いに離間した、複数の例えばピラー状のn型の第1半導体層2が形成される。半導体ウエハの表面におけるパターンでストライプ状でもよい。第1半導体層2の幅W1は例えば8μm程度である(図2(B))。

【0027】

トレンチ3形成後、例えば1100℃で10分の熱酸化を行い、その後その熱酸化膜をウェットエッチングにより除去し、トレンチエッチングによるダメージ層を除去する。

【0028】

第3工程(図3):第1のエピタキシャル層と異なる導電型の第2エピタキシャル層を形成する工程。

【0029】

半導体基板1上に、エピタキシャル成長法により、第1のエピタキシャル層2’(第1半導体層2)とは逆導電型の第2のエピタキシャル層(p型エピタキシャル層)4’を形成する。なお、第2工程で第1のエピタキシャル層(n型エピタキシャル層2’)がトレンチ3の底部に残っている場合は、残ったn型エピタキシャル層2’上にp型エピタキシャル層4’を形成する。p型エピタキシャル層4’の不純物濃度は例えば1×1016cm−3程度である。

【0030】

p型エピタキシャル層4’は、ピラー状の第1半導体層2の側面及び上面と、ここでは第1半導体層2間に露出した半導体基板1上を覆って形成される。また、p型エピタキシャル層4’は第1半導体層2の側面における厚み(半導体基板1の水平方向の厚みd1)と、第1半導体層2の上面または半導体基板1表面における厚みd2がほぼ同等となる。

【0031】

第4工程(図4):第2エピタキシャル層を全面異方性エッチングして第1半導体層に隣接する第2半導体層を形成する工程。

【0032】

p型エピタキシャル層4’をマスクを設けずに全面異方性エッチングする。第1半導体層2間の半導体基板1が露出するまでエッチングすることにより、第1半導体層2上面を覆うp型エピタキシャル層4’も除去されて第1半導体層2上面が露出する。なお第2工程で、第1のエピタキシャル層2’がトレンチ3の底部に残っている場合は、残った第1のエピタキシャル層2’が露出するまでエッチングする。この場合最終構造においても、トレンチ3の底部に第1のエピタキシャル層2’が残存する。

【0033】

一方、第1半導体層2の側面のp型エピタキシャル層4’は除去されず、これにより、第1半導体層2の両側に隣接する、ピラー状のp型の第2半導体層4が形成される。第2半導体層4の幅W2は、p型エピタキシャル層4’の厚みd1(=d2)であり、ここでは8μm程度とする。尚、特性に応じて、第1半導体層2の幅W1と、第2半導体層4の幅W2は適宜選択可能である。幅を狭くすると不純物濃度を高くするため、高耐圧、且つ低抵抗が実現できる。

【0034】

尚、本実施形態では、本工程において隣り合う(対向する)第2半導体層4間に、トレンチ状の空間部Sが形成される。

【0035】

第5工程(図5):第1のエピタキシャル層と同導電型の第3のエピタキシャル層を形成する工程。

【0036】

更に、半導体基板1上に、エピタキシャル成長法により、第1のエピタキシャル層2’と同導電型の第3のエピタキシャル層(n型エピタキシャル層)5’を形成する。n型エピタキシャル層5’の不純物濃度は例えば1×1016cm−3程度であり、厚みd3は8μm程度である。

【0037】

n型エピタキシャル層5’は、ピラー状の第2半導体層4の側面及び上面と、第1半導体層2の上面を覆って形成される。そして、隣り合う第2半導体層4間にはn型エピタキシャル層5’が埋め込まれる。つまりこの場合では、n型エピタキシャル層5’の厚みd3を、隣り合う第2半導体層4間(最後に形成されたトレンチ状の空間部S(図4参照))の距離の2分の1の厚みにすることで、第2半導体層4間にn型エピタキシャル層5’が埋め込まれる。本実施形態では、第3のエピタキシャル層3’が空間部S(図4参照)に埋め込まれた場合を示した。しかし、空間部Sに第3のエピタキシャル層3’を(完全)に埋め込む必要はなく、厚みd3を空間部Sの幅の2分の1にしなくても良い。すなわち空間部Sに隙間が残ったままでもよい。

【0038】

第6工程(図6):第3のエピタキシャル層を全面異方性エッチングし、第2半導体層に隣接する第3の半導体層を形成する工程。

【0039】

n型エピタキシャル層5’をマスクを設けずに全面異方性エッチングする。第1半導体層2および第2半導体層4上面が露出するまでエッチングすることにより、第2半導体層4の両側に隣接する、ピラー状のn型の第3半導体層5が形成される。第3半導体層5の幅W3は、第1半導体層2の幅W1と同等である。つまり、第2工程において、第1半導体層2(第3半導体層)の幅W1および第2半導体層4の幅W2を考慮して、トレンチ3の幅Wtを適切に選択することにより、全てのピラー状の半導体層をエピタキシャル層によって形成することができる。

【0040】

これにより、半導体ウエハ表面に対して垂直方向に複数のpn接合(p型半導体層とn型半導体層による超接合)を有する、すなわち超接合構造の半導体ウエハ10を形成できる。

【0041】

また、本実施形態では、第1半導体層2、第2半導体層4、および第3半導体層5は、エピタキシャル成長法により形成でき、その厚みは自由に制御できる。従って、第1〜第3のエピタキシャル層2’、4’、5’の厚みを薄く形成することも可能である。これにより、第1半導体層2、第2半導体層4、および第3半導体層5は、それぞれ、図6に示す断面、すなわち半導体ウエハ10の複数のpn接合が露出する断面における長辺:短辺のアスペクト比を10:1等にすることもできる。これはすなわち、第1半導体層2、第2半導体層4、および第3半導体層5は、半導体ウエハ10の厚み方向の長さ(長辺)に対して、幅W1、W2、W3(短辺)が非常に薄いことを意味する。

【0042】

各半導体層の幅W1、W2、W3が狭い場合、不純物濃度を高くするため、臨界電界強度が高くなり、高耐圧、且つ低抵抗が実現できる。

【0043】

また、第1〜第3半導体層2、4、5は全てエピタキシャル層であるので、半導体ウエハ10の深さ方向の不純物濃度プロファイルが均一となり、イオン注入によって形成した超接合構造の場合と比較して、空乏層の広がりを均一にできる。

【0044】

更に、第1〜第3半導体層2、4、5は全てエピタキシャル層であるので、pn接合面を、半導体ウエハ10の表面に対して垂直に形成できる。図7に示す如く、半導体ウエハの厚み方向に、多段階にエピタキシャル層の形成とイオン注入を繰り返して形成した超接合構造の場合には、pn接合面が実際には波状となり、空乏層の広がりが厳密には均一になりにくい問題がある。しかし、本実施形態ではpn接合面は半導体ウエハ表面に対して垂直面となり、これによっても空乏層の広がりを均一にすることができる。

【0045】

尚、図6において、第2半導体層4間に第3半導体層5が埋設され、半導体ウエハ10が完成する場合を例に説明したが、トレンチ3の開口幅Wtが広い場合は、更に繰り返してピラー状の半導体層を形成してもよい。

【0046】

つまり、上記の第3工程から第6工程の繰り返しにより、他のエピタキシャル層(たとえばp型エピタキシャル層)を形成する工程と、当該エピタキシャル層をエッチング工程を繰り返し、他のピラー状の半導体層を交互に隣接して形成する。

【0047】

つまり、第3半導体層5を形成した後、p型エピタキシャル層を形成してp型エピタキシャル層をエッチングし、他のピラー状のp型半導体層を形成する。更にn型エピタキシャル層を形成してn型エピタキシャル層をエッチングし、他のピラー状のn型半導体層を形成してもよく、これらが交互になるように更にp型半導体層とn型半導体層を形成してもよい。

【0048】

なお第2工程で、第1のエピタキシャル層2’がトレンチ3の底部に残っている場合はそれ以降の工程でピラー状のp型半導体層またはピラー状のn型半導体層を形成する際には、トレンチ3の底部に残った第1のエピタキシャル層2’が露出するまでエッチングする。

【0049】

このように、本実施形態の半導体ウエハの製造方法は、半導体基板1上に、n型エピタキシャル層形成とエッチングおよびp型エピタキシャル層形成とエッチングを交互に、少なくとも3回以上行い、全てのピラー状の半導体層をエピタキシャル層で形成するものである。

【0050】

全てのピラー状の半導体層はエピタキシャル層によって形成されるので、それらの幅を所望の幅に形成できる。つまり、各半導体層の幅を狭めることも可能となり、不純物濃度を高めることができるため、高耐圧且つ低抵抗が実現できる。

【0051】

また、各半導体層の不純物濃度プロファイルが均一となり、pn接合面が半導体ウエハ10表面に対して垂直に形成されるので、空乏層の広がりを均一にでき、超接合構造の特性を十分に生かせる半導体ウエハの製造方法を提供できる。

【0052】

以上、本実施形態では、半導体基板1としてn型シリコン半導体基板を用いた場合を例に説明したが、p型シリコン半導体基板であってもよい。また、第1工程でn型半導体層(エピタキシャル層)を形成した場合を例に説明したが、これがp型半導体層であっても同様に実施できる。

【図面の簡単な説明】

【0053】

【図1】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図2】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図3】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図4】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図5】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図6】本発明の実施形態における半導体ウエハの製造方法を説明する断面図である。

【図7】従来の半導体ウエハの製造方法を説明する断面図である。

【図8】従来の半導体ウエハの製造方法を説明する断面図である。

【符号の説明】

【0054】

1 半導体基板

2’ 第1のエピタキシャル層

2 第1半導体層

3 トレンチ

4’ 第2のエピタキシャル層

4 第2半導体層

5’ 第3のエピタキシャル層

5 第3半導体層

M マスク

W1 第1半導体層幅

W2 第2半導体層幅

Wt トレンチ幅

d1、d2 第2のエピタキシャル層厚み

d3 第3のエピタキシャル層厚み

e’ 他のエピタキシャル層

e 他の半導体層

【特許請求の範囲】

【請求項1】

一導電型半導体基板を準備し、該半導体基板上に第1のエピタキシャル層を形成する工程と、

前記第1のエピタキシャル層にトレンチを複数形成し、第1半導体層を形成する工程と、

前記第1のエピタキシャル層と異なる導電型の第2エピタキシャル層を形成する工程と、

前記第2エピタキシャル層を全面異方性エッチングして前記第1半導体層に隣接する第2半導体層を形成する工程と、

前記第1のエピタキシャル層と同導電型の第3のエピタキシャル層を形成する工程と、

前記第3のエピタキシャル層を全面異方性エッチングし、前記第2半導体層に隣接する第3の半導体層を形成する工程と、を具備し、

半導体ウエハ表面に対して垂直方向に複数のpn接合を形成することを特徴とする半導体ウエハの製造方法。

【請求項2】

前記トレンチ形成後、熱酸化によりダメージ層を除去することを特徴とする請求項1に記載の半導体ウエハの製造方法。

【請求項3】

他のエピタキシャル層を形成する工程と、該他のエピタキシャル層の全面異方性エッチングを行う工程とを有し、導電型が交互になるように互いに隣接する他の半導体層を形成することを特徴とする請求項1に記載の半導体ウエハの製造方法。

【請求項4】

前記第1半導体層、前記第2半導体層、前記第3半導体層および前記他の半導体層は、前記半導体ウエハ表面に対して垂直方向に不純物濃度プロファイルが均一であることを特徴とする請求項3に記載の半導体ウエハの製造方法。

【請求項1】

一導電型半導体基板を準備し、該半導体基板上に第1のエピタキシャル層を形成する工程と、

前記第1のエピタキシャル層にトレンチを複数形成し、第1半導体層を形成する工程と、

前記第1のエピタキシャル層と異なる導電型の第2エピタキシャル層を形成する工程と、

前記第2エピタキシャル層を全面異方性エッチングして前記第1半導体層に隣接する第2半導体層を形成する工程と、

前記第1のエピタキシャル層と同導電型の第3のエピタキシャル層を形成する工程と、

前記第3のエピタキシャル層を全面異方性エッチングし、前記第2半導体層に隣接する第3の半導体層を形成する工程と、を具備し、

半導体ウエハ表面に対して垂直方向に複数のpn接合を形成することを特徴とする半導体ウエハの製造方法。

【請求項2】

前記トレンチ形成後、熱酸化によりダメージ層を除去することを特徴とする請求項1に記載の半導体ウエハの製造方法。

【請求項3】

他のエピタキシャル層を形成する工程と、該他のエピタキシャル層の全面異方性エッチングを行う工程とを有し、導電型が交互になるように互いに隣接する他の半導体層を形成することを特徴とする請求項1に記載の半導体ウエハの製造方法。

【請求項4】

前記第1半導体層、前記第2半導体層、前記第3半導体層および前記他の半導体層は、前記半導体ウエハ表面に対して垂直方向に不純物濃度プロファイルが均一であることを特徴とする請求項3に記載の半導体ウエハの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2009−71060(P2009−71060A)

【公開日】平成21年4月2日(2009.4.2)

【国際特許分類】

【出願番号】特願2007−238290(P2007−238290)

【出願日】平成19年9月13日(2007.9.13)

【出願人】(000001889)三洋電機株式会社 (18,308)

【出願人】(506227884)三洋半導体株式会社 (1,155)

【Fターム(参考)】

【公開日】平成21年4月2日(2009.4.2)

【国際特許分類】

【出願日】平成19年9月13日(2007.9.13)

【出願人】(000001889)三洋電機株式会社 (18,308)

【出願人】(506227884)三洋半導体株式会社 (1,155)

【Fターム(参考)】

[ Back to top ]