半導体ウエハ及び半導体装置並びに半導体装置の製造方法

【課題】ダイシング工程におけるチッピング不良を低減させる。

【解決手段】一面側に複数の回路素子3が形成され、この回路素子が形成された領域間に第一スクライブライン領域R1が設けられたウエハ状の半導体基板2と、この半導体基板の他面2bから半導体基板の一面2aまで貫通する貫通孔7と、この貫通孔の内面及び半導体基板の他面側に形成された絶縁膜5と、この絶縁膜上に形成された配線6とを備えた半導体ウエハにおいて、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域R2が設けられている半導体ウエハを提供する。

【解決手段】一面側に複数の回路素子3が形成され、この回路素子が形成された領域間に第一スクライブライン領域R1が設けられたウエハ状の半導体基板2と、この半導体基板の他面2bから半導体基板の一面2aまで貫通する貫通孔7と、この貫通孔の内面及び半導体基板の他面側に形成された絶縁膜5と、この絶縁膜上に形成された配線6とを備えた半導体ウエハにおいて、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域R2が設けられている半導体ウエハを提供する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、絶縁膜で被覆された半導体基板を用いた半導体ウエハ及び半導体装置並びに半導体装置の製造方法に係り、特に、ダイシング工程における絶縁膜の剥がれを防ぐ半導体ウエハ及び半導体装置並びに半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、半導体パッケージ、例えば、シリコンチップを樹脂により封止した、いわゆるデュアル・インライン・パッケージ(Dual Inline Package、DIP)やクァド・フラット・パッケージ(Quad Flat Package、QFP)では、樹脂パッケージの側面部や周辺部に金属リードを配置した周辺端子配置型が主流であった。

【0003】

これに対し、近年広く普及している半導体パッケージ構造として、たとえばボールグリットアレイ(Ball Grid Array、BGA)がある。これは、パッケージの平坦な表面に半田バンプと呼ばれる電極を二次元的に配置した構造を有しているため、DIPやQFPと比較して高密度な実装が可能となる。このため、BGAはコンピュータのCPUやメモリなどのパッケージとして使われている。従来のBGAタイプの半導体パッケージは、パッケージサイズがチップサイズよりも大きいが、なかでもパッケージをほとんどチップサイズに近い大きさにまで小型化したパッケージはチップスケールパッケージ(Chip Scale Package、CSP)と呼ばれ、電子機器の小型軽量化に大きく貢献している。

【0004】

BGAタイプの半導体パッケージは、回路を形成したウエハ基板を切断し、その半導体チップをインターポーザと呼ばれる基板に搭載してパッケージを完成させるもので、パターニングされたインターポーザが必要である上に、個々に半導体チップを個別にインターポーザに実装する工程が必要である。このため、専用の材料や製造装置を用いなければならず、コストが高くなるという欠点があった。

【0005】

これに対し、CSP、特に「ウエハレベルCSP」と呼ばれる製法においては、このウエハ基板上に、絶縁樹脂層、再配線層、封止樹脂層、はんだバンプ等を形成し、最終工程において半導体ウエハを所定のチップ寸法に切断することでパッケージ構造を具備した半導体装置を得ることができる(例えば、特許文献1参照)。したがって、パッケージ構造をウエハ状の半導体基板上に一括形成するため、従来のようにインターポーザを必要とせず、またウエハ状態で加工するので専用の装置を必要としない。このため製造効率が高く、コスト面の不利は低減している。

【0006】

ウエハレベルCSPによる半導体ウエハより得られる半導体装置は、ウエハ全面にパッケージ加工を施した後にダイシングして個片化することから、個片化したチップそのものの大きさが、パッケージの施された半導体装置となり、実装基板に対して最小投影面積を有する半導体装置を得ることが可能となる。また、配線距離が従来のパッケージよりも短く、配線の寄生容量も小さい。

【0007】

上記ウエハレベルCSPを採用した半導体装置の製造工程のうち、半導体ウエハを個片かするダイシング工程は、ダイシングブレードを用いて、スクライブライン領域を切削することにより行う。ダイシング時は、回路素子内部に機械的欠陥が生じるのを防ぐために、ダイシングブレードの回転速度や、ダイシング速度(ウエハとダイシングブレードの相対速度)等を調整するなどの制御が行われる。

【0008】

また、半導体装置のさらなる小型化を実現する技術として、貫通電極(Through-Silicon Via、TSV)を用いたウエハレベルCSPが提案されてきている。貫通電極は従来のワイヤーボンディングに代わるものであり、半導体装置の内部に垂直に形成した貫通孔を導電性を有する金属で充填することによって電極として利用するものである。貫通電極の技術は、ワイヤーボンディングによって接続する従来の手法と比較して、配線距離を大幅に短縮できるため、半導体装置の高速化、省電力化、小型化に寄与する。

これら優れた特徴は、現在急速に進んでいる実装の高密度化や、情報処理速度の高速化が実現できるという点において非常に優位である。

【0009】

従来の貫通電極を用いた半導体ウエハとしては、例えば特許文献2に記載されたものがある。図7(a)は、従来の半導体ウエハ100の断面を示す図である。

従来の半導体ウエハ100は、Si(シリコン)からなるウエハ状の半導体基板102の一面側102aに回路素子103が設けられているとともに、半導体基板102の他面102bから一面102aに貫通する貫通孔107が設けられている。貫通孔107の内面及び半導体基板102少なくとも他面側102bには、絶縁膜105が形成されている。絶縁膜105上には配線106が形成されており、これにより貫通電極120を構成している。

【0010】

符号104は、前記貫通電極120と電気的に接続される電極パッドであり、パッシベーション層108によって被覆されている。符号109は、半導体基板102の他面側102bにおいて、回路素子領域を被覆する保護層である。以上の半導体素子が、接着層111によってガラスからなる支持基板110に接合されている。

符号15は、ダイシング工程において、半導体装置100を保持するためのダイシングテープである。

【0011】

半導体基板102の一面側102aには、第一スクライブライン領域R10が設けられており、他面側102bには、ダイシング工程において、保護層109を巻き込むのを防ぐため、第二スクライブライン領域R11が設けられている。第二スクライブライン領域R11においては、前記保護層109がスクライブラインLに沿って除去されているとともに、予めスクライブラインLに沿った溝130が形成されており、これにより、ダイシングを容易にし、ダイシング工程における回路素子103の破損を防ぐ構成となっている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2002−280476号公報

【特許文献2】特開平5−152435号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

図7(b)は、上記構成の半導体ウエハ100のダイシング工程の際、ダイシングブレードBが挿入された状態を示す断面図である。

この図に示すように、従来の半導体ウエハ100に対してダイシングを行う場合、第二スクライブライン領域R11に絶縁膜105が存在しているため、ダイシングブレードBが絶縁膜105に接触した際、絶縁膜105の剥がれ(符号C1で示す)が生じる不具合があった。

図8は、従来の半導体ウエハ100をダイシングブレードBによってダイシングした後の、ダイシングライン付近の上面図である。絶縁膜105の剥がれは、ダイシングラインLから、貫通電極120や回路素子が形成されている方向へ生じており、これらが回路素子の領域に達することで、半導体装置100に不良が発生する原因となる。

【0014】

この発明は、このような事情を考慮してなされたもので、その目的は、ダイシング工程における半導体ウエハを構成する絶縁膜の剥がれを防ぐことを可能にする半導体ウエハ及び半導体装置並びに半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0015】

上記課題に対し、本発明の以下の手段により解決を図る。

すなわち、本発明の請求項1に係る発明は、一面側に複数の回路素子が形成され、該回路素子が形成された領域間に第一スクライブライン領域が設けられたウエハ状の半導体基板と、前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔と、前記貫通孔の内面及び前記半導体基板の他面側に形成された絶縁膜と、前記絶縁膜上に形成された配線とを備えた半導体ウエハであって、前記半導体基板の他面側に形成された前記絶縁膜には、前記第一スクライブライン領域に沿って該絶縁膜が離間した領域である第二スクライブライン領域が設けられていることを特徴とする半導体ウエハである。

また、本発明の請求項2に係る発明は、前記第一スクライブライン領域の幅をR1、前記第二スクライブライン領域の幅をR2とすると、R1>R2なる関係を満たすことを特徴とする請求項1に記載の半導体ウエハである。

また、本発明の請求項3に係る発明は、前記第二スクライブライン領域に沿って前記半導体基板に凹部が形成されていることを特徴とする請求項1または2に記載の半導体ウエハである。

【0016】

また、本発明の請求項4に係る発明は、半導体ウエハをスクライブラインにそって切削し個片化された半導体装置であって、一面側に回路素子が形成された半導体基板と、前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔と、前記貫通孔の内面及び前記半導体基板の他面側に形成された絶縁膜と、前記絶縁膜上に形成された配線とを備え、前記絶縁膜は、個片化において形成された切削面より内側に位置していることを特徴とする半導体装置である。

【0017】

また、本発明の請求項5に係る発明は、一面側に複数の回路素子が形成され、該回路素子が形成された領域間に第一スクライブライン領域が設けられたウエハ状の半導体基板を準備する工程と、前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔を形成する貫通孔形成工程と、前記貫通孔の内面及び前記半導体基板の他面側に絶縁膜を形成する絶縁膜形成工程と、前記絶縁膜上に配線を形成する配線形成工程と、前記半導体基板の他面側に、前記回路素子が形成された領域を個々に被覆する保護層を形成し、前記保護層間に第二スクライブライン領域を設ける保護層形成工程と、前記保護層形成後に、前記第二スクライブライン領域に露呈した前記絶縁膜を除去する絶縁膜除去工程と、前記半導体ウエハをスクライブラインに沿って他面側から切削し個片化するダイシング工程と、を備える半導体装置の製造方法である。

また、本発明の請求項6に係る発明は、前記第一スクライブライン領域の幅をR1、前記第二スクライブライン領域の幅をR2とすると、R1>R2なる関係を満たすことを特徴とする請求項5に記載の半導体装置の製造方法である。

さらに、本発明の請求項7に係る発明は、前記絶縁膜除去工程を行うとともに、前記第二スクライブライン領域に沿って前記半導体基板に凹部を形成することを特徴とする請求項5または6に記載の半導体装置の製造方法である。

【発明の効果】

【0018】

本発明における半導体ウエハによれば、半導体ウエハを構成する半導体基板の一面側に第一スクライブライン領域を設け、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域を設けた。ゆえに、ダイシング工程における絶縁膜の剥がれを防ぐことができるという効果が得られる。

【0019】

本発明における半導体装置によれば、半導体基板の一面側及び他面側それぞれの絶縁膜端部が、半導体装置の端部より離間した構成となっているため、絶縁膜がダイシングによって半導体基板の端部に生じた応力の影響を受けず、よって、絶縁膜が剥れる不良を低減できる。また、半導体装置の端部に外部応力が生じた際も、絶縁膜にその影響が及ぶことを防ぐことができる。

【0020】

本発明における半導体装置の製造方法は、半導体基板の他面側に回路素子が形成された領域を個々に被覆する保護層を形成し、保護層間に第二スクライブライン領域を設ける保護層形成工程と、保護層形成後に、第二スクライブライン領域に露呈した絶縁膜を除去する絶縁膜除去工程と備えている。ゆえに、ダイシング工程における絶縁膜の剥がれを防ぐことができるという効果が得られる。

【図面の簡単な説明】

【0021】

【図1】本発明の第一実施形態に係る半導体ウエハの平面図である。

【図2】図1のA−A線に沿う断面図である。

【図3】本発明に係る半導体ウエハのダイシング工程を示す断面図であり、(a)は、ダイシング前、(b)はダイシング中を示す図である。

【図4】ダイシングによって個片化された半導体装置の断面図である。

【図5】絶縁膜の除去工程を順に説明する図である。

【図6】本発明の第二実施形態に係る半導体ウエハの部分断面図である。

【図7】従来の半導体ウエハのダイシング工程を示す断面図であり、(a)は、ダイシング前、(b)はダイシング中を示す図である。

【図8】従来の半導体ウエハをダイシングした際の上面図である。

【発明を実施するための形態】

【0022】

<第一実施形態>

以下、本発明の実施の形態を図面を参照して詳細に説明する。

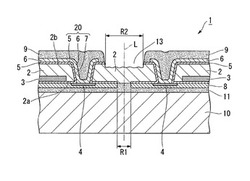

図1は、本発明の半導体ウエハの実施形態を示す平面図であり、半導体装置に個片化される前の半導体ウエハ1を示すものである。図2は、図1のA−A線に沿う断面図であり、スクライブラインL周辺を示すものである。

図1に示すように、本発明の半導体ウエハ1は、所定のスクライブラインLに沿って切断されることで、複数の半導体装置へと個片化される。半導体ウエハ1上のスクライブラインLによって画定された領域に、回路素子11が形成されている。また、符号20は回路素子領域に形成された貫通電極である。

【0023】

図2において、符号1は半導体ウエハ、2は半導体基板、3は回路素子、4は電極パッド、5は絶縁膜、6は配線、7は貫通孔、8はパッシベーション層、9は保護層、10は支持基板、11は接着層を示している。貫通電極20は、絶縁膜5、配線6、及び貫通孔7から構成されている。

【0024】

この半導体ウエハ1では、図2に示すように、貫通電極20等が設けられてなる半導体基板2が、接着層11によって支持基板10に接合されている。

半導体基板2の一面側2aには電極パッド4が設けられている。半導体基板2には、電極パッド4が設けられた部分に、他面2bから一面2aにわたって貫通孔7が形成されている。また、電極パッド4が設けられている面は、パッシベーション層8によって保護されている。

【0025】

また、半導体基板2の両面および貫通孔7の内面には絶縁膜5が設けられている。絶縁膜は、例えばSiO2、SiN、又は樹脂膜である。さらに、絶縁膜5上であって、貫通孔7内面及び半導体基板2の他面2b側には、配線6が形成されている。この配線6は、電極パッド4と電気的に接続されている。

そして、半導体ウエハ2の他面2bは、保護層9で被覆されている。なお、保護層9は必ずしも必要ではなく、貫通電極20や配線6を露出する形態としてもよい。

【0026】

半導体基板2は、例えば、シリコンやGaAs等の半導体基板である。

支持基板10は、熱膨張率が半導体基板2に近い材料が望ましい。

接着層11をなす接着剤としては、電気絶縁性を有する材料からなるものが用いられる。接着層105をなす接着剤としては、例えばポリイミド樹脂、エポキシ樹脂、ベンゾシクロブタン(BCB)樹脂などが望ましい。

【0027】

回路素子3は、例えばメモリ、IC、撮像素子、MEMS素子などの半導体機能素子などである。前記配線は、Cu、Al、Ni、Ag、Pb、Sn、Au、Co、Cr、Ti、TiW等の導体(各種の金属や合金等)から形成された配線層である。配線層としての回路素子3の形成方法は、特に限定されるものではなく、例えばスパッタリング法、蒸着法、めっき法等、あるいはこれらの2つ以上の方法の組み合わせが挙げられる。また、配線層としての回路素子3は、単層の導体層でも、多層の導体層を積層したものでもよい。また、配線層のパターニングには、フォトリソグラフィ技術が好適に用いられる。

【0028】

符号Lは、半導体ウエハ1をダイシング加工する際の参照されるスクライブラインである。

半導体基板2の一面側2aには、第一スクライブライン領域R1が設けられている。スクライブライン領域とは、この領域をダイシングブレードで切削することによって、個々の半導体装置に分離するためのものである。図2おいて符号R1は、第一スクライブライン領域の幅を示すものである。半導体基板2の一面側2aにおいて、絶縁膜5は、スクライブラインLに沿って第一スクライブライン領域R1の幅だけ離間した領域を有している。つまり、一面側2aにおいて、第一スクライブライン領域R1には絶縁膜5が設けられていない。また、第一スクライブライン領域R1の中心線は、スクライブラインLと一致している。

【0029】

半導体基板2の他面側2bには、第一スクライブライン領域R1と比較して、やや大なる幅を有する第二スクライブライン領域R2が設けられている。第二スクライブライン領域R2においては、スクライブラインLに沿って保護層9は形成されていない。

本発明の半導体ウエハ1は、半導体基板2の他面側2bに形成されている絶縁膜5に関しても、スクライブラインLに沿って離間した領域を備えている。離間幅は第二スクライブライン領域R2と同一である。つまり、他面側2bにおいて、第二スクライブライン領域R2には絶縁膜5が設けられていない。

また、第二スクライブライン領域R2の中心線は、スクライブライン領域Lと一致している。すなわち、第一スクライブライン領域R1の中心線と、第二スクライブライン領域R2の中心線は、一致している。

【0030】

さらに、第二スクライブライン領域R2においては、半導体基板2に凹部13が設けられている。凹部13は、半導体基板2の他面2bに対して、所定深さに亘って半導体基板2の表面が削られた部位である。つまり、第二スクライブライン領域R2においては、半導体基板2には他面2bに対して段差が設けられており、半導体基板2は他の領域と比較して、基板厚さが薄くなっている。

段差の高さが大きくなるほど、切削する領域における半導体基板厚さが薄くなるので、容易にダイシングすることができる。ひいては、ダイシング時におけるチッピング不良を低減することができる。

【0031】

次に、図3を参照して、半導体ウエハ2をスクライブラインLに沿って切断し個片化するダイシング工程について説明する。

半導体ウエハ1のダイシング工程においては、半導体ウエハの他面側の前面にダイシングテープ15に貼り付け、半導体ウエハ1全体をフレーム(図示せず)に固定して行う。ダイシングテープ15としては、例えば、紫外線を照射することによって粘性が変化するUVテープを使用することができる。

【0032】

次に、ダイシングブレードBを用いて、スクライブラインLに沿って半導体ウエハ1を切削する。

半導体ウエハ1を切断することによって、半導体ウエハ1は個々の半導体装置に分離される。ダイシングテープ15は、紫外線を照射するなどして粘着力を失わせた上で、半導体装置をダイシングテープ15から取り外す。

図3(b)からも明らかなように、第二スクライブライン領域R2は、ダイシングブレードBの幅に対して、やや大なる幅を有している。つまり、ダイシングブレードBの端面に対して、保護層9及び絶縁膜5は、所定寸法離間している。具体的には、ダイシングブレードBの幅70μmに対して、スクライブライン領域R2の幅を140μm程度とすることが好ましい。

また、第一スクライブライン領域R1に関しては、幅を100μmとすることが好ましい。

【0033】

以上の工程を経て、図4に示すような、半導体装置50を製作することができる。図4からも明らかなように、半導体装置を構成する半導体基板の両面に形成されている絶縁膜の端部は、半導体装置の端部50aに対して、所定距離を隔てて離間している。

具体的には、半導体基板2の一面側2aに形成されている絶縁膜5の端部と半導体装置50の端面50aとの距離D1は15μmである。また、半導体基板2の他面側2bに形成されている絶縁膜5の端部と半導体装置50の端面50aとの距離D2は35μmである。

【0034】

次に、図5を参照して、本発明の第二スクライブライン領域R2の形成方法について説明する。図5は、本発明の半導体ウエハ1の部分断面図であり、特に、第二スクライブライン領域R2が設けられている箇所を拡大した図である。

【0035】

第二スクライブライン領域R2の形成にあたっては、まず、厚さT1を有する保護層9aを形成する(図5(a))。保護層9aの厚さT1は、最終的に所望する保護層9の厚みに応じて適宜決定される。このような形状の保護層9aは、感光性樹脂を用いたフォトリソグラフィ技術で製作できる。又は非感光性樹脂をパターンエッチングすることでも製作できる。

【0036】

次に、図5(b)に示すように、半導体ウエハ1の他面側に対してエッチングを行う。このエッチングは、反応ガスとしてCF系のエッチングガスを導入してプラズマを発生させて行う。この工程は、前記保護層9aの形成の際に発生したスカムを除去すると共に、保護層9a、絶縁膜5、及び半導体基板2をエッチングにより所定厚さに亘って削るものである。図5(b)の二点差線がエッチング前の保護層9aの表面を示すものである。

このエッチングによって、図5(a)に示した工程によって形成された保護層9aがエッチングされると同時に、絶縁膜5及び半導体基板2がエッチングされる。

【0037】

最終的に、図5(c)に示すように、スクライブライン領域R2が形成される。スクライブライン領域R2においては、スクライブライン領域Lに沿って保護層9及び絶縁膜5が形成されておらず、かつ、半導体基板2に対して段差部が設けられた凹部13が形成される。

【0038】

本発明の第一実施形態に係る半導体ウエハ2は、上記したような構成の第二スクライブライン領域R2を設けたことが特徴である。第二スクライブライン領域R2において、絶縁膜5を設けない構成としたことによって、ダイシング工程において、絶縁膜5剥がれる不具合を低減することができる。

さらに、本発明の第一実施形態に係る半導体ウエハ1によれば、第二スクライブライン領域R2に凹部13を設けたことによって、第二スクライブライン領域R2における半導体基板2の厚さが薄くなるため、ダイシング工程における半導体基板2のチッピング不良を低減することができる。

【0039】

<第二実施形態>

図6は、本発明の第二実施形態に係る半導体ウエハを示す部分断面図であり、第一実施形態の図2に対応する図である。

第二実施形態は、第一実施形態と比較して、第一スクライブライン領域、及び第二スクライブライン領域の幅が異なっている。

【0040】

第二実施形態に係る半導体ウエハ1bは、第一実施形態に係る半導体ウエハ1と略同様の製造方法で製作することができる。

第二実施形態に係る半導体ウエハ1bは、ダイシング工程において、他面側2bに設けられたスクライブライン領域R2bに沿って切削を行う。これにより、ダイシングブレードの位置決めが容易になり、ダイシングの際、ダイシングブレードが一面側2aのスクライブライン領域R1bから外れて、絶縁膜5と接触する不具合を回避することができる。

【産業上の利用可能性】

【0041】

本発明は、基板上に絶縁膜を備え、ダイシング工程によって分離される貫通電極を備えた半導体装置に広く適用可能である。

【符号の説明】

【0042】

1…半導体ウエハ、2…半導体基板、3…回路素子、4…電極パッド、5…絶縁膜、6…配線、7…貫通孔、8…パッシベーション層、9…保護層、10…支持基板、11…接着層、13…凹部、15…ダイシングテープ、20…貫通電極、50…半導体装置。

【技術分野】

【0001】

本発明は、絶縁膜で被覆された半導体基板を用いた半導体ウエハ及び半導体装置並びに半導体装置の製造方法に係り、特に、ダイシング工程における絶縁膜の剥がれを防ぐ半導体ウエハ及び半導体装置並びに半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、半導体パッケージ、例えば、シリコンチップを樹脂により封止した、いわゆるデュアル・インライン・パッケージ(Dual Inline Package、DIP)やクァド・フラット・パッケージ(Quad Flat Package、QFP)では、樹脂パッケージの側面部や周辺部に金属リードを配置した周辺端子配置型が主流であった。

【0003】

これに対し、近年広く普及している半導体パッケージ構造として、たとえばボールグリットアレイ(Ball Grid Array、BGA)がある。これは、パッケージの平坦な表面に半田バンプと呼ばれる電極を二次元的に配置した構造を有しているため、DIPやQFPと比較して高密度な実装が可能となる。このため、BGAはコンピュータのCPUやメモリなどのパッケージとして使われている。従来のBGAタイプの半導体パッケージは、パッケージサイズがチップサイズよりも大きいが、なかでもパッケージをほとんどチップサイズに近い大きさにまで小型化したパッケージはチップスケールパッケージ(Chip Scale Package、CSP)と呼ばれ、電子機器の小型軽量化に大きく貢献している。

【0004】

BGAタイプの半導体パッケージは、回路を形成したウエハ基板を切断し、その半導体チップをインターポーザと呼ばれる基板に搭載してパッケージを完成させるもので、パターニングされたインターポーザが必要である上に、個々に半導体チップを個別にインターポーザに実装する工程が必要である。このため、専用の材料や製造装置を用いなければならず、コストが高くなるという欠点があった。

【0005】

これに対し、CSP、特に「ウエハレベルCSP」と呼ばれる製法においては、このウエハ基板上に、絶縁樹脂層、再配線層、封止樹脂層、はんだバンプ等を形成し、最終工程において半導体ウエハを所定のチップ寸法に切断することでパッケージ構造を具備した半導体装置を得ることができる(例えば、特許文献1参照)。したがって、パッケージ構造をウエハ状の半導体基板上に一括形成するため、従来のようにインターポーザを必要とせず、またウエハ状態で加工するので専用の装置を必要としない。このため製造効率が高く、コスト面の不利は低減している。

【0006】

ウエハレベルCSPによる半導体ウエハより得られる半導体装置は、ウエハ全面にパッケージ加工を施した後にダイシングして個片化することから、個片化したチップそのものの大きさが、パッケージの施された半導体装置となり、実装基板に対して最小投影面積を有する半導体装置を得ることが可能となる。また、配線距離が従来のパッケージよりも短く、配線の寄生容量も小さい。

【0007】

上記ウエハレベルCSPを採用した半導体装置の製造工程のうち、半導体ウエハを個片かするダイシング工程は、ダイシングブレードを用いて、スクライブライン領域を切削することにより行う。ダイシング時は、回路素子内部に機械的欠陥が生じるのを防ぐために、ダイシングブレードの回転速度や、ダイシング速度(ウエハとダイシングブレードの相対速度)等を調整するなどの制御が行われる。

【0008】

また、半導体装置のさらなる小型化を実現する技術として、貫通電極(Through-Silicon Via、TSV)を用いたウエハレベルCSPが提案されてきている。貫通電極は従来のワイヤーボンディングに代わるものであり、半導体装置の内部に垂直に形成した貫通孔を導電性を有する金属で充填することによって電極として利用するものである。貫通電極の技術は、ワイヤーボンディングによって接続する従来の手法と比較して、配線距離を大幅に短縮できるため、半導体装置の高速化、省電力化、小型化に寄与する。

これら優れた特徴は、現在急速に進んでいる実装の高密度化や、情報処理速度の高速化が実現できるという点において非常に優位である。

【0009】

従来の貫通電極を用いた半導体ウエハとしては、例えば特許文献2に記載されたものがある。図7(a)は、従来の半導体ウエハ100の断面を示す図である。

従来の半導体ウエハ100は、Si(シリコン)からなるウエハ状の半導体基板102の一面側102aに回路素子103が設けられているとともに、半導体基板102の他面102bから一面102aに貫通する貫通孔107が設けられている。貫通孔107の内面及び半導体基板102少なくとも他面側102bには、絶縁膜105が形成されている。絶縁膜105上には配線106が形成されており、これにより貫通電極120を構成している。

【0010】

符号104は、前記貫通電極120と電気的に接続される電極パッドであり、パッシベーション層108によって被覆されている。符号109は、半導体基板102の他面側102bにおいて、回路素子領域を被覆する保護層である。以上の半導体素子が、接着層111によってガラスからなる支持基板110に接合されている。

符号15は、ダイシング工程において、半導体装置100を保持するためのダイシングテープである。

【0011】

半導体基板102の一面側102aには、第一スクライブライン領域R10が設けられており、他面側102bには、ダイシング工程において、保護層109を巻き込むのを防ぐため、第二スクライブライン領域R11が設けられている。第二スクライブライン領域R11においては、前記保護層109がスクライブラインLに沿って除去されているとともに、予めスクライブラインLに沿った溝130が形成されており、これにより、ダイシングを容易にし、ダイシング工程における回路素子103の破損を防ぐ構成となっている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2002−280476号公報

【特許文献2】特開平5−152435号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

図7(b)は、上記構成の半導体ウエハ100のダイシング工程の際、ダイシングブレードBが挿入された状態を示す断面図である。

この図に示すように、従来の半導体ウエハ100に対してダイシングを行う場合、第二スクライブライン領域R11に絶縁膜105が存在しているため、ダイシングブレードBが絶縁膜105に接触した際、絶縁膜105の剥がれ(符号C1で示す)が生じる不具合があった。

図8は、従来の半導体ウエハ100をダイシングブレードBによってダイシングした後の、ダイシングライン付近の上面図である。絶縁膜105の剥がれは、ダイシングラインLから、貫通電極120や回路素子が形成されている方向へ生じており、これらが回路素子の領域に達することで、半導体装置100に不良が発生する原因となる。

【0014】

この発明は、このような事情を考慮してなされたもので、その目的は、ダイシング工程における半導体ウエハを構成する絶縁膜の剥がれを防ぐことを可能にする半導体ウエハ及び半導体装置並びに半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0015】

上記課題に対し、本発明の以下の手段により解決を図る。

すなわち、本発明の請求項1に係る発明は、一面側に複数の回路素子が形成され、該回路素子が形成された領域間に第一スクライブライン領域が設けられたウエハ状の半導体基板と、前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔と、前記貫通孔の内面及び前記半導体基板の他面側に形成された絶縁膜と、前記絶縁膜上に形成された配線とを備えた半導体ウエハであって、前記半導体基板の他面側に形成された前記絶縁膜には、前記第一スクライブライン領域に沿って該絶縁膜が離間した領域である第二スクライブライン領域が設けられていることを特徴とする半導体ウエハである。

また、本発明の請求項2に係る発明は、前記第一スクライブライン領域の幅をR1、前記第二スクライブライン領域の幅をR2とすると、R1>R2なる関係を満たすことを特徴とする請求項1に記載の半導体ウエハである。

また、本発明の請求項3に係る発明は、前記第二スクライブライン領域に沿って前記半導体基板に凹部が形成されていることを特徴とする請求項1または2に記載の半導体ウエハである。

【0016】

また、本発明の請求項4に係る発明は、半導体ウエハをスクライブラインにそって切削し個片化された半導体装置であって、一面側に回路素子が形成された半導体基板と、前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔と、前記貫通孔の内面及び前記半導体基板の他面側に形成された絶縁膜と、前記絶縁膜上に形成された配線とを備え、前記絶縁膜は、個片化において形成された切削面より内側に位置していることを特徴とする半導体装置である。

【0017】

また、本発明の請求項5に係る発明は、一面側に複数の回路素子が形成され、該回路素子が形成された領域間に第一スクライブライン領域が設けられたウエハ状の半導体基板を準備する工程と、前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔を形成する貫通孔形成工程と、前記貫通孔の内面及び前記半導体基板の他面側に絶縁膜を形成する絶縁膜形成工程と、前記絶縁膜上に配線を形成する配線形成工程と、前記半導体基板の他面側に、前記回路素子が形成された領域を個々に被覆する保護層を形成し、前記保護層間に第二スクライブライン領域を設ける保護層形成工程と、前記保護層形成後に、前記第二スクライブライン領域に露呈した前記絶縁膜を除去する絶縁膜除去工程と、前記半導体ウエハをスクライブラインに沿って他面側から切削し個片化するダイシング工程と、を備える半導体装置の製造方法である。

また、本発明の請求項6に係る発明は、前記第一スクライブライン領域の幅をR1、前記第二スクライブライン領域の幅をR2とすると、R1>R2なる関係を満たすことを特徴とする請求項5に記載の半導体装置の製造方法である。

さらに、本発明の請求項7に係る発明は、前記絶縁膜除去工程を行うとともに、前記第二スクライブライン領域に沿って前記半導体基板に凹部を形成することを特徴とする請求項5または6に記載の半導体装置の製造方法である。

【発明の効果】

【0018】

本発明における半導体ウエハによれば、半導体ウエハを構成する半導体基板の一面側に第一スクライブライン領域を設け、半導体基板の他面側に形成された絶縁膜に、第一スクライブライン領域に沿って絶縁膜が離間した領域である第二スクライブライン領域を設けた。ゆえに、ダイシング工程における絶縁膜の剥がれを防ぐことができるという効果が得られる。

【0019】

本発明における半導体装置によれば、半導体基板の一面側及び他面側それぞれの絶縁膜端部が、半導体装置の端部より離間した構成となっているため、絶縁膜がダイシングによって半導体基板の端部に生じた応力の影響を受けず、よって、絶縁膜が剥れる不良を低減できる。また、半導体装置の端部に外部応力が生じた際も、絶縁膜にその影響が及ぶことを防ぐことができる。

【0020】

本発明における半導体装置の製造方法は、半導体基板の他面側に回路素子が形成された領域を個々に被覆する保護層を形成し、保護層間に第二スクライブライン領域を設ける保護層形成工程と、保護層形成後に、第二スクライブライン領域に露呈した絶縁膜を除去する絶縁膜除去工程と備えている。ゆえに、ダイシング工程における絶縁膜の剥がれを防ぐことができるという効果が得られる。

【図面の簡単な説明】

【0021】

【図1】本発明の第一実施形態に係る半導体ウエハの平面図である。

【図2】図1のA−A線に沿う断面図である。

【図3】本発明に係る半導体ウエハのダイシング工程を示す断面図であり、(a)は、ダイシング前、(b)はダイシング中を示す図である。

【図4】ダイシングによって個片化された半導体装置の断面図である。

【図5】絶縁膜の除去工程を順に説明する図である。

【図6】本発明の第二実施形態に係る半導体ウエハの部分断面図である。

【図7】従来の半導体ウエハのダイシング工程を示す断面図であり、(a)は、ダイシング前、(b)はダイシング中を示す図である。

【図8】従来の半導体ウエハをダイシングした際の上面図である。

【発明を実施するための形態】

【0022】

<第一実施形態>

以下、本発明の実施の形態を図面を参照して詳細に説明する。

図1は、本発明の半導体ウエハの実施形態を示す平面図であり、半導体装置に個片化される前の半導体ウエハ1を示すものである。図2は、図1のA−A線に沿う断面図であり、スクライブラインL周辺を示すものである。

図1に示すように、本発明の半導体ウエハ1は、所定のスクライブラインLに沿って切断されることで、複数の半導体装置へと個片化される。半導体ウエハ1上のスクライブラインLによって画定された領域に、回路素子11が形成されている。また、符号20は回路素子領域に形成された貫通電極である。

【0023】

図2において、符号1は半導体ウエハ、2は半導体基板、3は回路素子、4は電極パッド、5は絶縁膜、6は配線、7は貫通孔、8はパッシベーション層、9は保護層、10は支持基板、11は接着層を示している。貫通電極20は、絶縁膜5、配線6、及び貫通孔7から構成されている。

【0024】

この半導体ウエハ1では、図2に示すように、貫通電極20等が設けられてなる半導体基板2が、接着層11によって支持基板10に接合されている。

半導体基板2の一面側2aには電極パッド4が設けられている。半導体基板2には、電極パッド4が設けられた部分に、他面2bから一面2aにわたって貫通孔7が形成されている。また、電極パッド4が設けられている面は、パッシベーション層8によって保護されている。

【0025】

また、半導体基板2の両面および貫通孔7の内面には絶縁膜5が設けられている。絶縁膜は、例えばSiO2、SiN、又は樹脂膜である。さらに、絶縁膜5上であって、貫通孔7内面及び半導体基板2の他面2b側には、配線6が形成されている。この配線6は、電極パッド4と電気的に接続されている。

そして、半導体ウエハ2の他面2bは、保護層9で被覆されている。なお、保護層9は必ずしも必要ではなく、貫通電極20や配線6を露出する形態としてもよい。

【0026】

半導体基板2は、例えば、シリコンやGaAs等の半導体基板である。

支持基板10は、熱膨張率が半導体基板2に近い材料が望ましい。

接着層11をなす接着剤としては、電気絶縁性を有する材料からなるものが用いられる。接着層105をなす接着剤としては、例えばポリイミド樹脂、エポキシ樹脂、ベンゾシクロブタン(BCB)樹脂などが望ましい。

【0027】

回路素子3は、例えばメモリ、IC、撮像素子、MEMS素子などの半導体機能素子などである。前記配線は、Cu、Al、Ni、Ag、Pb、Sn、Au、Co、Cr、Ti、TiW等の導体(各種の金属や合金等)から形成された配線層である。配線層としての回路素子3の形成方法は、特に限定されるものではなく、例えばスパッタリング法、蒸着法、めっき法等、あるいはこれらの2つ以上の方法の組み合わせが挙げられる。また、配線層としての回路素子3は、単層の導体層でも、多層の導体層を積層したものでもよい。また、配線層のパターニングには、フォトリソグラフィ技術が好適に用いられる。

【0028】

符号Lは、半導体ウエハ1をダイシング加工する際の参照されるスクライブラインである。

半導体基板2の一面側2aには、第一スクライブライン領域R1が設けられている。スクライブライン領域とは、この領域をダイシングブレードで切削することによって、個々の半導体装置に分離するためのものである。図2おいて符号R1は、第一スクライブライン領域の幅を示すものである。半導体基板2の一面側2aにおいて、絶縁膜5は、スクライブラインLに沿って第一スクライブライン領域R1の幅だけ離間した領域を有している。つまり、一面側2aにおいて、第一スクライブライン領域R1には絶縁膜5が設けられていない。また、第一スクライブライン領域R1の中心線は、スクライブラインLと一致している。

【0029】

半導体基板2の他面側2bには、第一スクライブライン領域R1と比較して、やや大なる幅を有する第二スクライブライン領域R2が設けられている。第二スクライブライン領域R2においては、スクライブラインLに沿って保護層9は形成されていない。

本発明の半導体ウエハ1は、半導体基板2の他面側2bに形成されている絶縁膜5に関しても、スクライブラインLに沿って離間した領域を備えている。離間幅は第二スクライブライン領域R2と同一である。つまり、他面側2bにおいて、第二スクライブライン領域R2には絶縁膜5が設けられていない。

また、第二スクライブライン領域R2の中心線は、スクライブライン領域Lと一致している。すなわち、第一スクライブライン領域R1の中心線と、第二スクライブライン領域R2の中心線は、一致している。

【0030】

さらに、第二スクライブライン領域R2においては、半導体基板2に凹部13が設けられている。凹部13は、半導体基板2の他面2bに対して、所定深さに亘って半導体基板2の表面が削られた部位である。つまり、第二スクライブライン領域R2においては、半導体基板2には他面2bに対して段差が設けられており、半導体基板2は他の領域と比較して、基板厚さが薄くなっている。

段差の高さが大きくなるほど、切削する領域における半導体基板厚さが薄くなるので、容易にダイシングすることができる。ひいては、ダイシング時におけるチッピング不良を低減することができる。

【0031】

次に、図3を参照して、半導体ウエハ2をスクライブラインLに沿って切断し個片化するダイシング工程について説明する。

半導体ウエハ1のダイシング工程においては、半導体ウエハの他面側の前面にダイシングテープ15に貼り付け、半導体ウエハ1全体をフレーム(図示せず)に固定して行う。ダイシングテープ15としては、例えば、紫外線を照射することによって粘性が変化するUVテープを使用することができる。

【0032】

次に、ダイシングブレードBを用いて、スクライブラインLに沿って半導体ウエハ1を切削する。

半導体ウエハ1を切断することによって、半導体ウエハ1は個々の半導体装置に分離される。ダイシングテープ15は、紫外線を照射するなどして粘着力を失わせた上で、半導体装置をダイシングテープ15から取り外す。

図3(b)からも明らかなように、第二スクライブライン領域R2は、ダイシングブレードBの幅に対して、やや大なる幅を有している。つまり、ダイシングブレードBの端面に対して、保護層9及び絶縁膜5は、所定寸法離間している。具体的には、ダイシングブレードBの幅70μmに対して、スクライブライン領域R2の幅を140μm程度とすることが好ましい。

また、第一スクライブライン領域R1に関しては、幅を100μmとすることが好ましい。

【0033】

以上の工程を経て、図4に示すような、半導体装置50を製作することができる。図4からも明らかなように、半導体装置を構成する半導体基板の両面に形成されている絶縁膜の端部は、半導体装置の端部50aに対して、所定距離を隔てて離間している。

具体的には、半導体基板2の一面側2aに形成されている絶縁膜5の端部と半導体装置50の端面50aとの距離D1は15μmである。また、半導体基板2の他面側2bに形成されている絶縁膜5の端部と半導体装置50の端面50aとの距離D2は35μmである。

【0034】

次に、図5を参照して、本発明の第二スクライブライン領域R2の形成方法について説明する。図5は、本発明の半導体ウエハ1の部分断面図であり、特に、第二スクライブライン領域R2が設けられている箇所を拡大した図である。

【0035】

第二スクライブライン領域R2の形成にあたっては、まず、厚さT1を有する保護層9aを形成する(図5(a))。保護層9aの厚さT1は、最終的に所望する保護層9の厚みに応じて適宜決定される。このような形状の保護層9aは、感光性樹脂を用いたフォトリソグラフィ技術で製作できる。又は非感光性樹脂をパターンエッチングすることでも製作できる。

【0036】

次に、図5(b)に示すように、半導体ウエハ1の他面側に対してエッチングを行う。このエッチングは、反応ガスとしてCF系のエッチングガスを導入してプラズマを発生させて行う。この工程は、前記保護層9aの形成の際に発生したスカムを除去すると共に、保護層9a、絶縁膜5、及び半導体基板2をエッチングにより所定厚さに亘って削るものである。図5(b)の二点差線がエッチング前の保護層9aの表面を示すものである。

このエッチングによって、図5(a)に示した工程によって形成された保護層9aがエッチングされると同時に、絶縁膜5及び半導体基板2がエッチングされる。

【0037】

最終的に、図5(c)に示すように、スクライブライン領域R2が形成される。スクライブライン領域R2においては、スクライブライン領域Lに沿って保護層9及び絶縁膜5が形成されておらず、かつ、半導体基板2に対して段差部が設けられた凹部13が形成される。

【0038】

本発明の第一実施形態に係る半導体ウエハ2は、上記したような構成の第二スクライブライン領域R2を設けたことが特徴である。第二スクライブライン領域R2において、絶縁膜5を設けない構成としたことによって、ダイシング工程において、絶縁膜5剥がれる不具合を低減することができる。

さらに、本発明の第一実施形態に係る半導体ウエハ1によれば、第二スクライブライン領域R2に凹部13を設けたことによって、第二スクライブライン領域R2における半導体基板2の厚さが薄くなるため、ダイシング工程における半導体基板2のチッピング不良を低減することができる。

【0039】

<第二実施形態>

図6は、本発明の第二実施形態に係る半導体ウエハを示す部分断面図であり、第一実施形態の図2に対応する図である。

第二実施形態は、第一実施形態と比較して、第一スクライブライン領域、及び第二スクライブライン領域の幅が異なっている。

【0040】

第二実施形態に係る半導体ウエハ1bは、第一実施形態に係る半導体ウエハ1と略同様の製造方法で製作することができる。

第二実施形態に係る半導体ウエハ1bは、ダイシング工程において、他面側2bに設けられたスクライブライン領域R2bに沿って切削を行う。これにより、ダイシングブレードの位置決めが容易になり、ダイシングの際、ダイシングブレードが一面側2aのスクライブライン領域R1bから外れて、絶縁膜5と接触する不具合を回避することができる。

【産業上の利用可能性】

【0041】

本発明は、基板上に絶縁膜を備え、ダイシング工程によって分離される貫通電極を備えた半導体装置に広く適用可能である。

【符号の説明】

【0042】

1…半導体ウエハ、2…半導体基板、3…回路素子、4…電極パッド、5…絶縁膜、6…配線、7…貫通孔、8…パッシベーション層、9…保護層、10…支持基板、11…接着層、13…凹部、15…ダイシングテープ、20…貫通電極、50…半導体装置。

【特許請求の範囲】

【請求項1】

一面側に複数の回路素子が形成され、該回路素子が形成された領域間に第一スクライブライン領域が設けられたウエハ状の半導体基板と、

前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔と、

前記貫通孔の内面及び前記半導体基板の他面側に形成された絶縁膜と、

前記絶縁膜上に形成された配線とを備えた半導体ウエハであって、

前記半導体基板の他面側に形成された前記絶縁膜には、前記第一スクライブライン領域に沿って該絶縁膜が離間した領域である第二スクライブライン領域が設けられていることを特徴とする半導体ウエハ。

【請求項2】

前記第一スクライブライン領域の幅をR1、

前記第二スクライブライン領域の幅をR2とすると、

R1>R2なる関係を満たすことを特徴とする請求項1に記載の半導体ウエハ。

【請求項3】

前記第二スクライブライン領域に沿って前記半導体基板に凹部が形成されていることを特徴とする請求項1または2に記載の半導体ウエハ。

【請求項4】

半導体ウエハをスクライブラインに沿って切削し個片化された半導体装置であって、

一面側に回路素子が形成された半導体基板と、

前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔と、

前記貫通孔の内面及び前記半導体基板の他面側に形成された絶縁膜と、

前記絶縁膜上に形成された配線とを備え、

前記絶縁膜は、個片化において形成された切削面より内側に位置していることを特徴とする半導体装置。

【請求項5】

一面側に複数の回路素子が形成され、該回路素子が形成された領域間に第一スクライブライン領域が設けられたウエハ状の半導体基板を準備する工程と、

前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔を形成する貫通孔形成工程と、

前記貫通孔の内面及び前記半導体基板の他面側に絶縁膜を形成する絶縁膜形成工程と、

前記絶縁膜上に配線を形成する配線形成工程と、

前記半導体基板の他面側に、前記回路素子が形成された領域を個々に被覆する保護層を形成し、前記保護層間に第二スクライブライン領域を設ける保護層形成工程と、

前記保護層形成後に、前記第二スクライブライン領域に露呈した前記絶縁膜を除去する絶縁膜除去工程と、

前記半導体ウエハをスクライブラインに沿って他面側から切削し個片化するダイシング工程と、

を備える半導体装置の製造方法。

【請求項6】

前記第一スクライブライン領域の幅をR1、

前記第二スクライブライン領域の幅をR2とすると、

R1>R2なる関係を満たすことを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記絶縁膜除去工程を行うとともに、前記第二スクライブライン領域に沿って前記半導体基板に凹部を形成することを特徴とする請求項5または6に記載の半導体装置の製造方法。

【請求項1】

一面側に複数の回路素子が形成され、該回路素子が形成された領域間に第一スクライブライン領域が設けられたウエハ状の半導体基板と、

前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔と、

前記貫通孔の内面及び前記半導体基板の他面側に形成された絶縁膜と、

前記絶縁膜上に形成された配線とを備えた半導体ウエハであって、

前記半導体基板の他面側に形成された前記絶縁膜には、前記第一スクライブライン領域に沿って該絶縁膜が離間した領域である第二スクライブライン領域が設けられていることを特徴とする半導体ウエハ。

【請求項2】

前記第一スクライブライン領域の幅をR1、

前記第二スクライブライン領域の幅をR2とすると、

R1>R2なる関係を満たすことを特徴とする請求項1に記載の半導体ウエハ。

【請求項3】

前記第二スクライブライン領域に沿って前記半導体基板に凹部が形成されていることを特徴とする請求項1または2に記載の半導体ウエハ。

【請求項4】

半導体ウエハをスクライブラインに沿って切削し個片化された半導体装置であって、

一面側に回路素子が形成された半導体基板と、

前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔と、

前記貫通孔の内面及び前記半導体基板の他面側に形成された絶縁膜と、

前記絶縁膜上に形成された配線とを備え、

前記絶縁膜は、個片化において形成された切削面より内側に位置していることを特徴とする半導体装置。

【請求項5】

一面側に複数の回路素子が形成され、該回路素子が形成された領域間に第一スクライブライン領域が設けられたウエハ状の半導体基板を準備する工程と、

前記半導体基板の他面から前記半導体基板の一面まで貫通する貫通孔を形成する貫通孔形成工程と、

前記貫通孔の内面及び前記半導体基板の他面側に絶縁膜を形成する絶縁膜形成工程と、

前記絶縁膜上に配線を形成する配線形成工程と、

前記半導体基板の他面側に、前記回路素子が形成された領域を個々に被覆する保護層を形成し、前記保護層間に第二スクライブライン領域を設ける保護層形成工程と、

前記保護層形成後に、前記第二スクライブライン領域に露呈した前記絶縁膜を除去する絶縁膜除去工程と、

前記半導体ウエハをスクライブラインに沿って他面側から切削し個片化するダイシング工程と、

を備える半導体装置の製造方法。

【請求項6】

前記第一スクライブライン領域の幅をR1、

前記第二スクライブライン領域の幅をR2とすると、

R1>R2なる関係を満たすことを特徴とする請求項5に記載の半導体装置の製造方法。

【請求項7】

前記絶縁膜除去工程を行うとともに、前記第二スクライブライン領域に沿って前記半導体基板に凹部を形成することを特徴とする請求項5または6に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−65582(P2013−65582A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2009−296880(P2009−296880)

【出願日】平成21年12月28日(2009.12.28)

【出願人】(000005186)株式会社フジクラ (4,463)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成21年12月28日(2009.12.28)

【出願人】(000005186)株式会社フジクラ (4,463)

【Fターム(参考)】

[ Back to top ]