半導体ウエハ積層体の製造方法および製造システム

【課題】ウエハトゥウエハ積層法によって製造される半導体チップ積層体の歩留りを改善する。

【解決手段】第1の半導体チップ11が複数形成された第1種の半導体ウエハ10、および第2の半導体チップ31が複数形成された第2種の半導体ウエハ30が積層してなる半導体ウエハ積層体の製造方法であって、前記第1の半導体チップ各々の物理的または電気的特性が既知である前記第1種の半導体ウエハを複数用意し、前記第2の半導体チップ各々の物理的または電気的特性が既知である前記第2種の半導体ウエハを複数用意し、前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う。

【解決手段】第1の半導体チップ11が複数形成された第1種の半導体ウエハ10、および第2の半導体チップ31が複数形成された第2種の半導体ウエハ30が積層してなる半導体ウエハ積層体の製造方法であって、前記第1の半導体チップ各々の物理的または電気的特性が既知である前記第1種の半導体ウエハを複数用意し、前記第2の半導体チップ各々の物理的または電気的特性が既知である前記第2種の半導体ウエハを複数用意し、前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体ウエハ積層体の製造方法および製造システムに関する。

【背景技術】

【0002】

電子機器に搭載される集積回路素子の高速化、小型化および低コスト化が進められている。集積回路素子は、所定の機能を果たす複数の半導体チップを積層し、その積層された半導体チップ(半導体チップ積層体)をモールド樹脂等によりパッケージングして製造することができる(たとえば特許文献1)。

【0003】

半導体チップは、ウエハと呼ばれる半導体基板の表面に光学処理等を施すことにより形成される。たとえば、直径300mmのウエハ上に、数百〜数千個の半導体チップを形成することができる。

【0004】

半導体チップ積層体を得る方法には、たとえばチップトゥチップ積層法やウエハトゥウエハ積層法などがある。チップトゥチップ積層法とは、複数の半導体チップが形成された各種ウエハをそれぞれ単一の半導体チップに分割した後に、その分割された各種半導体チップを積層して半導体チップ積層体を得る方法である。ウエハトゥウエハ積層法とは、複数の半導体チップが形成された各種ウエハを積層した後に、その積層されたウエハ(ウエハ積層体)を分割して半導体チップ積層体を得る方法である。ウエハトゥウエハ積層法は、チップトゥチップ積層法よりも生産性が高く、製造される集積回路素子の低コスト化に貢献しうる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−53081号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ウエハトゥウエハ積層法の生産性は、さらに改善される必要がある。本発明の目的は、ウエハトゥウエハ積層法によって製造される半導体チップ積層体の歩留りを改善することにある。

【課題を解決するための手段】

【0007】

本発明の一観点によれば、第1の半導体チップが複数形成された第1種の半導体ウエハ、および第2の半導体チップが複数形成された第2種の半導体ウエハが積層してなる半導体ウエハ積層体の製造方法であって、前記第1の半導体チップ各々の物理的または電気的特性が既知である前記第1種の半導体ウエハを複数用意し、前記第2の半導体チップ各々の物理的または電気的特性が既知である前記第2種の半導体ウエハを複数用意し、前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う半導体ウエハ積層体の製造方法、が提供される。

【0008】

本発明の他の観点によれば、第1の半導体チップが複数形成された第1種の半導体ウエハ、および第2の半導体チップが複数形成された第2種の半導体ウエハが積層してなる半導体ウエハ積層体の製造システムであって、前記第1種の半導体ウエハに形成された第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハに形成された第2の半導体チップ各々の物理的または電気的特性を測定する測定装置と、前記測定装置によって測定された前記第1種の半導体ウエハにおける前記第1の半導体チップ各々の物理的または電気的特性、および複数の前記第2種の半導体ウエハにおける前記第2の半導体チップ各々の物理的または電気的特性を、複数の前記第1種および第2種の半導体ウエハに対して記憶する記憶装置と、前記記憶装置に記憶された前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う演算装置と、を含む半導体ウエハ積層体の製造システム、が提供される。

【発明の効果】

【0009】

ウエハトゥウエハ積層法によって製造される半導体チップ積層体の歩留りが改善される。

【図面の簡単な説明】

【0010】

【図1】図1Aは、複数種類の半導体ウエハを積層し、半導体ウエハ積層体を形成する様子を示す概略斜視図であり、図1Bは、複数種類の半導体ウエハを積層し、各種半導体ウエハに形成された半導体チップを相互に電気的に接続した様子の一部を示す概略断面図である。

【図2】図2A〜図2Dは、それぞれ半導体ウエハ10a〜40aにおける半導体チップ11〜41の不良分布を示す平面図であり、図2Eは、半導体ウエハ10a〜40aを積層した半導体ウエハ積層体50aにおける半導体チップ積層体53の不良分布を示す平面図である。

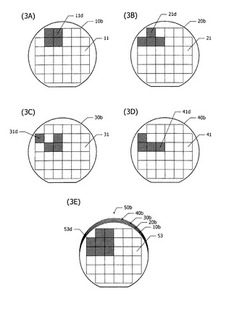

【図3】図3A〜図3Dは、それぞれ半導体ウエハ10b〜40bにおける半導体チップ11〜41の不良分布を示す平面図であり、図3Eは、半導体ウエハ10b〜40bを積層した半導体ウエハ積層体50bにおける半導体チップ積層体53の不良分布を示す平面図である。

【図4】図4は、実施例による半導体ウエハ積層体の製造システムを概略的に示すダイアグラムである。

【図5】図5Aおよび図5Bは、演算装置による第1の処理を概略的に示すダイアグラムである。

【図6】図6Aおよび図6Bは、演算装置による第2の処理を概略的に示すダイアグラムである。

【図7】図7Aおよび図7Bは、演算装置による他の処理を概略的に示すダイアグラムである。

【発明を実施するための形態】

【0011】

図1Aは、複数種類の半導体ウエハを積層し、半導体ウエハ積層体を形成する様子を示す概略斜視図である。半導体ウエハ積層体50は、たとえば、シリコン基板から構成される半導体ウエハを2〜5枚程度積層して形成され、その厚みは10μm〜50μm程度である。図1Aには、例として4枚の半導体ウエハ10,20,30,40を積層する場合を示す。半導体ウエハ10〜40には、それぞれ半導体チップ11,21,31,41が複数形成されている(図1Aでは半導体チップ31,41は図示していない)。半導体チップ11〜41各々には、たとえば、CPU(central processing unit),DRAM(dynamic random access memory),フラッシュメモリなどの集積回路が形成される。半導体ウエハ10〜40各々は、たとえば直径が300mm程度であり、数百〜数千個の半導体チップ11〜41が形成されている。なお、図1Aでは、便宜的に、半導体チップのサイズを実際のサイズよりも大きく示している。

【0012】

図1Bは、複数種類の半導体ウエハを積層し、各種半導体ウエハに形成された半導体チップを相互に電気的に接続した様子の一部を示す概略断面図である。

【0013】

半導体ウエハ10に形成される半導体チップ11は、たとえば半導体素子層12および配線層13を含む。半導体素子層12には、MOSトランジスタ等の半導体素子が複数形成されている。配線層13には、半導体素子層12に形成された複数の半導体素子を相互に電気的に接続する配線が形成されている。これにより、半導体チップ11は、所定の機能を果たす集積回路として動作する。

【0014】

半導体チップ11は、さらに、半導体チップ11を貫通して設けられる複数の電極端子51、および複数の電極端子51各々と導通し、半導体チップ11の両面に設けられる複数の電極パッドないし半田バンプ52を含む。単一の半導体チップ11には、たとえば数万個の電極端子51が形成されうる。なお、この電極端子51は、TSV(through silicon via)と呼ばれることがある。

【0015】

半導体ウエハ20〜40は、半導体ウエハ10と同様の構成を有し、それぞれ半導体素子層22〜42,配線層22〜24,電極端子51,半田バンプ52を含む構成である。半導体ウエハ10〜40は積層され、半導体ウエハ10〜40各々の両面に形成された半田バンプ52を介して相互に電気的に接続される。これにより、半導体ウエハ積層体50が形成される。

【0016】

さらに、形成された半導体ウエハ積層体50を個々の積層された半導体チップ11〜41に分割することにより、半導体チップ積層体53を得ることができる。半導体チップ積層体53は、半導体チップ11〜41が相互に協働して、所定の機能を果たすデバイスとして動作する。半導体チップ11〜41が、たとえば、それぞれイメージングセンサ回路、アナログーデジタル変換回路、レジスタ回路およびプロセッサ回路として機能する集積回路である場合、半導体チップ積層体53は、イメージングセンサデバイスとして動作する。

【0017】

半導体ウエハには、製造装置のバラつきなどによって、少なからず不良の半導体チップが形成されうる。また、その不良の半導体チップが形成される位置・分布は、製造される半導体ウエハごとに異なる可能性がある。半導体チップ積層体は、それを構成する複数の半導体チップが協働することによって、所定の機能を果たすデバイスとして動作する。したがって、複数の半導体チップのいずれか1つの半導体チップが適正に動作しないような場合には、半導体チップ積層体も適正に動作しえず、その半導体チップ積層体は不良品となる。

【0018】

図2A〜図2Dは、それぞれ半導体ウエハ10a〜40aにおける半導体チップ11〜41の不良分布を示す平面図である。ここで、半導体ウエハ10a〜40a各々には、32個の半導体チップ11〜41が形成され、32個の半導体チップうち4個の不良半導体チップ11d〜41d(不良チップ)が形成されているものとする。つまり、半導体ウエハ10a〜40a各々の不良率は4/32である。図中において、ウエハ内に形成された不良チップは斜線で示されている。

【0019】

図2Aに示すように、半導体ウエハ10aには、不良チップ11dがウエハ左上方に集中して分布しているものとする。図2Bに示すように、半導体ウエハ20aには、不良チップ21dがウエハ右上方に集中して分布しているものとする。図2Cに示すように、半導体ウエハ30aには、不良チップ31dがウエハ左下方に集中して分布しているものとする。図2Dに示すように、半導体ウエハ40aには、不良チップ41dがウエハ右下方に集中して分布しているものとする。

【0020】

このような不良チップ分布を有する半導体ウエハ10a〜40aを積層して、半導体ウエハ積層体50a、さらに半導体チップ積層体53を形成する。形成される半導体チップ積層体53各々は、それを構成する半導体チップ11〜41の少なくとも1つの半導体チップが不良チップである場合には、不良と見なされる。

【0021】

図2Eは、図2A〜図2Dに示す半導体ウエハ10a〜40aを積層した半導体ウエハ積層体50aにおける半導体チップ積層体53の不良分布を示す平面図である。図2A〜図2Dに示す半導体ウエハ10a〜40aを積層して半導体ウエハ積層体50aを形成した場合、この半導体ウエハ積層体50の不良率は、半導体ウエハ10a〜40a各々の不良率の単純な総和となり、16/32となる。

【0022】

図3A〜図3Dは、それぞれ半導体ウエハ10b〜40bにおける半導体チップ11〜41の不良分布を示す平面図である。ここで、半導体ウエハ10b〜40b各々の不良率は、図2A〜図2Dと同様に、4/32であるものとする。ただし、図2A〜2Dに示す不良チップ分布とは異なり、半導体ウエハ10b〜40bのいずれの半導体ウエハにおいても、不良チップ11d〜41dがウエハ左上方に集中して分布しているものとする。

【0023】

図3Eは、図3A〜図3Dに示す半導体ウエハ10b〜40bを積層した半導体ウエハ積層体50bにおける半導体チップ積層体53の不良分布を示す平面図である。図3A〜図3Dに示す半導体ウエハ10b〜40bを積層して半導体ウエハ積層体50bを形成した場合、この半導体ウエハ積層体50bの不良率は、8/32となる。図2A〜図2Dに示す半導体ウエハ10a〜40aを積層する場合よりも、形成される半導体チップ積層体の不良率は低くなる。このように、各種半導体ウエハに形成される不良チップ同士をより多く積層させる、つまりウエハ内の同じような位置に不良チップ分布を有する半導体ウエハ同士を積層させることにより、不良品である半導体チップ積層体を減らし、良品である半導体チップ積層体をより多く得ることができるようになる。

【0024】

たとえば、半導体チップ各々の構造が複雑であり、かつ、半導体チップの実装密度も高い半導体ウエハの歩留りは、おおよそ70〜80%程度である。無作為に抽出された歩留り70〜80%程度の半導体ウエハを4枚積層して形成される半導体ウエハ積層体の積層歩留りは、24〜41%程度となる。一方、ウエハ内の同じような位置に不良チップ分布を有する半導体ウエハを選定して形成される半導体ウエハ積層体の積層歩留りは、理想的には単一の半導体ウエハの歩留りと同等である70〜80%程度にすることが可能である。

【0025】

以下、半導体ウエハ積層体の歩留りを改善することができる製造方法および製造システムについて、具体的に説明する。

【0026】

図4は、実施例による半導体ウエハ積層体の製造システムを概略的に示すダイアグラムである。なお、以下では、2種類の半導体ウエハからなる半導体ウエハ積層体を3つ形成する場合について説明する。

【0027】

実施例による導体ウエハ積層体の製造システムは、測定装置61、記憶装置62および演算装置63を含む構成である。

【0028】

測定装置61は、第1種の半導体ウエハ10a〜10c各々に形成される複数の半導体チップ11(図1Aないし図1B)の物理的または電気的な特性、および第2種の半導体ウエハ20a〜20c各々に形成される複数の半導体チップ21(図1Aないし図1B)の物理的または電気的な特性を測定する。半導体チップ11,21の物理的特性とは、たとえば、半導体素子層12,22(図1B)ないし配線層13,23(図1B)の層厚や、配線層13,23に形成される配線の幅、半導体チップ11,21に含まれる格子欠陥密度などである。また、半導体チップ11,21の電気的特性とは、たとえば、半導体チップ11,21に形成される集積回路の各回路ブロックにおける電流・電圧値(電気的な短絡・開放を含む)や、動作クロック周波数特性などである。

【0029】

測定装置61によって測定された半導体ウエハ10a〜10c各々における半導体チップ11各々の特性データ、および半導体ウエハ20a〜20c各々における半導体チップ21各々の特性データは、記憶装置62に転送される。なお、測定装置61は、半導体ウエハ10a〜10cを測定する測定装置と、半導体ウエハ20a〜20cを測定する測定装置と、を別々に構成した測定装置であってもかまわない。また、半導体チップの物理的特性を測定する測定装置と、電気的特性を測定する測定装置と、を別々に構成した測定装置であってもかまわないし、半導体ウエハないし半導体チップのその他の特性・性能を測定する測定装置を別途設けてもかまわない。

【0030】

記憶装置62は、測定装置61によって測定された半導体ウエハ10a〜10c各々における半導体チップ11各々の特性データ、および半導体ウエハ20a〜20c各々における半導体チップ21各々の特性データを記憶する。記憶装置62は、たとえば、HDD(hard disk drive)やフラッシュメモリなどを用いることができる。記憶装置62に記憶された各半導体ウエハの特性データは、演算装置63などの外部機器から読み出すことができる。

【0031】

演算装置63は、記憶装置62に記憶された半導体ウエハ10a〜10c各々における半導体チップ11各々の特性データ、および半導体ウエハ20a〜20c各々における半導体チップ21各々の特性データに基づいて、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20c各々の不良チップ分布を算出する。さらに、演算装置63は、算出された半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20c各々の不良チップ分布に基づいて、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの選定を行う。その際、演算装置63は、たとえば、最終的に形成される複数の半導体ウエハ積層体の歩留りが最も高くなるように、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せを選定する。演算装置63は、たとえばパーソナルコンピュータ(PC)などを用いることができる。

【0032】

半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cは、その後、演算装置63によって選定された組合せで、ウエハ積層装置64により積層される。このようにして、半導体ウエハ積層体50a〜50cが製造される。

【0033】

次に、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せを最適化する演算装置63の第1の処理について説明する。

【0034】

図5Aは、第1種の半導体ウエハ10aおよび第2種の半導体ウエハ20aの不良チップ分布を示す平面図である。また、半導体ウエハ10aおよび半導体ウエハ20aを積層させた際に形成される半導体ウエハ積層体50の不良分布を示す平面図である。

【0035】

演算装置63は、記憶装置62に記憶された半導体ウエハ10a〜10c各々における半導体チップ11各々の特性データに基づいて、半導体ウエハ10a〜10c各々の不良チップ分布を算出する。たとえば、演算装置63は、図5Aに示す半導体ウエハ10aのように、電気的短絡・開放等により適正に動作しない半導体チップ11dに数値0のフラグをたて、それ以外の半導体チップ11gに数値1のフラグをたてる。

【0036】

同様に、演算装置63は、記憶装置62に記憶された半導体ウエハ20a〜20c各々における半導体チップ21各々の特性データに基づいて、半導体ウエハ20a〜20c各々の不良チップ分布を算出する。たとえば、演算装置63は、図5Aに示す半導体ウエハ20aのように、たとえば電気的短絡・開放等により適正に動作しない半導体チップ21dに数値0のフラグをたて、それ以外の半導体チップ21gに数値1のフラグをたてる。

【0037】

さらに、演算装置63は、図5Aに示す半導体ウエハ積層体50のように、半導体ウエハ10aと半導体ウエハ20aとを積層して形成される半導体チップ積層体53各々に、それを構成する半導体チップ11,21に付されたフラグを積算したフラグをたてる。このとき、フラグが0となる半導体チップ積層体53は不良品の半導体チップ積層体53dとなり、フラグが1となる半導体チップ積層体53は良品の半導体チップ積層体53gとなる。

【0038】

演算装置63は、さらに、半導体チップ積層体53各々に付されたフラグの累計を算出する。つまり、半導体ウエハ10aおよび半導体ウエハ20aを積層したときに、半導体チップ11各々のフラグと、半導体チップ11各々にそれぞれ重畳する半導体チップ21各々のフラグと、を積算したフラグの累計を算出する。図5Aに示す半導体ウエハ積層体50におけるフラグの累計は、25である。ここで、半導体ウエハ10aおよび半導体ウエハ20aを積層させた半導体ウエハ積層体50の半導体チップ積層体53各々に付されたフラグの累計を、半導体ウエハ10aおよび半導体ウエハ20aの良品累計値C11と呼ぶこととする。

【0039】

演算装置63は、以上のような処理を、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cのすべてのペアに対して行い、各ペアの良品累計値を算出する。半導体ウエハ10aおよび半導体ウエハ20a〜20c各々の良品累計値を、それぞれC11,C12,C13とする。半導体ウエハ10bおよび半導体ウエハ20a〜20c各々の良品累計値を、それぞれC21,C22,C23とする。半導体ウエハ10cおよび半導体ウエハ20a〜20c各々の良品累計値を、それぞれC31,C32,C33とする。

【0040】

図5Bに、積層されうる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せP1〜P6を示す。演算装置63は、積層されうる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せP1〜P6各々に対して、良品累計値の総和S1〜S6を算出する。演算装置63は、良品累計値の総和が最大となる組合せで、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの選定を行う。

【0041】

演算装置63がこのような処理を行うことにより、半導体ウエハを無作為に抽出して半導体ウエハ積層体を形成する場合よりも、歩留りを改善することができる。なお、2種類以上の半導体ウエハを積層させて3つ以上の半導体ウエハ積層体を形成するような場合でも、組合せの場合の数は大きくなるが、上記と同様の方法により、各種半導体ウエハの最適化された組合せを選定することは可能である。一度に照合を行う各種半導体ウエハの枚数は、たとえば各種半導体ウエハの生産ロットに対応する枚数(たとえば25枚)とすればよい。

【0042】

次に、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せを最適化する演算装置63の第2の処理について説明する。

【0043】

図6Aおよび図6Bは、第1種の半導体ウエハ10a〜10cおよび第2種の半導体ウエハ20a〜20cの不良チップ分布を示す平面図である。演算装置63は、上記に示した第1の処理と同様に、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20c各々の不良チップ分布を算出する。

【0044】

演算装置63は、第1種および第2種の半導体ウエハのどちらか一方、たとえば第1種の半導体ウエハ10a〜10cの中から、半導体チップ11各々に付されたフラグの累計が最も大きい第1種の半導体ウエハを選定する。図6Aに示す半導体ウエハ10a〜10cにおいて、フラグの累計はそれぞれ27,28,30である。したがって、フラグの累計が30である半導体ウエハ10cを選定する。

【0045】

次に、演算装置63は、第2種の半導体ウエハ20a〜20cの中から、半導体ウエハ10cと積層させたときに、良品累計値が最も大きくなる第2種の半導体ウエハを選定する。半導体ウエハ10cおよび半導体20a〜20c各々の良品累計値は、それぞれ26,26,28となる。したがって、良品累計値が28となる半導体ウエハ20cを選定する。選定された半導体ウエハ10cおよび半導体ウエハ20cにより、半導体ウエハ積層体を形成する。

【0046】

次に、演算装置63は、半導体ウエハ10cおよび半導体ウエハ20cを除いた半導体ウエハに対して同様の処理を行う。つまり、図6Bに示すように、半導体ウエハ10a,10bの中から、フラグの累計が大きい半導体ウエハ10bを選定し、半導体ウエハ20a,20bの中から、半導体ウエハ10bと積層したときに良品累計値が大きくなる半導体ウエハ20aを選定する。選定された半導体ウエハ10bおよび半導体ウエハ20aにより、半導体ウエハ積層体を形成する。また、残った半導体ウエハ10aおよび半導体ウエハ20bにより、半導体ウエハ積層体を形成する。

【0047】

このような処理においても、半導体ウエハを無作為に抽出して半導体ウエハ積層体を形成する場合よりも、歩留りを改善することができる。なお、以上では、不良品と判定した半導体チップに0のフラグをたて、良品と判定した半導体チップに1のフラグをたてたが、逆に不良品と判定した半導体チップに1のフラグをたて、良品と判定した半導体チップに0のフラグをたてて、各種半導体ウエハの最適な組合せを算出してもかまわない。また、半導体チップに付す数値は、0および1以外の数値でもよい。

【0048】

以上では、半導体ウエハに形成される半導体チップ単位で、良品/不良品の判定を行ったが、半導体ウエハ内の領域単位で、良品領域/不良品領域の判定を行ってもかまわない。また、良品領域/不良品領域を、要求されている物理的または電気的特性を満足する規格内領域/要求されている物理的または電気的特性を満足しない規格外領域として判定を行ってもかまわない。以下に、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せを最適化する演算装置63の他の処理について説明する。

【0049】

図7Aは、第1種の半導体ウエハ10aおよび第2種の半導体ウエハ20aの規格外領域を示す平面図である。また、半導体ウエハ10aおよび半導体ウエハ20aを積層させた際に形成される半導体ウエハ積層体50の不良領域を示す平面図である。

【0050】

演算装置63は、記憶装置62に記憶された複数の半導体ウエハ10a〜10c各々における半導体チップの特性データ、および要求されている物理的または電気的特性に基づいて、半導体ウエハ10a〜10c各々に対し、所定の特性分布を有する領域を画定する。演算装置63は、たとえば、図7Aに示す半導体ウエハ10aのように、要求されている物理的または電気的特性を満足しない半導体チップが形成されている領域を規格外領域15として画定する。

【0051】

同様に、演算装置63は、記憶装置62に記憶された複数の半導体ウエハ20a〜20c各々における半導体チップの特性データ、および要求されている物理的または電気的特性に基づいて、半導体ウエハ20a〜20c各々に対し、所定の特性分布を有する領域を画定する。たとえば、演算装置63は、図7Aに示す半導体ウエハ20aのように、要求されている物理的または電気的特性を満足しない半導体チップが形成されている領域を規格外領域25として画定する。

【0052】

なお、規格外領域15,25とは、たとえば、半導体素子層12,22(図1B)ないし配線層13,23(図1B)の層厚や、配線層13,23(図1B)に形成される配線の幅、半導体チップ11,21に含まれる格子欠陥密度などが、要求されている規格から外れている領域である。

【0053】

さらに、演算装置63は、図7Aに示す半導体ウエハ積層体50のように、半導体ウエハ10aと半導体ウエハ20aとを積層させた際の規格外領域15,25を合成した不良領域55を画定する。以降、上記第1の処理と同じように、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cのすべてのペアに対して不良領域を画定し、不良領域の面積の総和が最小となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う。このような処理においても、半導体ウエハを無作為に抽出して半導体ウエハ積層体を形成する場合よりも、規格を満たす半導体チップ積層体をより多く抽出することが可能となる。

【0054】

図7Bは、第1種の半導体ウエハ10a〜10cおよび第2種の半導体ウエハ20a〜20cにおける所定の特性分布を示す平面図である。演算装置63は、複数の第1種および第2種の半導体ウエハ各々に対して、規格外領域15,25を画定した後、上記第2の処理と同じように、積層させる第1種および第2種の半導体ウエハの選定を行ってもよい。つまり、図7Bに示すように、第1種の半導体ウエハ10a〜10cから規格外領域15の面積が最小である半導体ウエハ10cを選定し、その後、半導体ウエハ10cと積層させたときに不良領域の面積が最小になる半導体ウエハ20cを選定する。このような処理を繰り返し行い、積層させる第1種および第2種の半導体ウエハの選定を行う。このような処理においても、半導体ウエハを無作為に抽出して半導体ウエハ積層体を形成する場合よりも、規格を満たす半導体チップ積層体をより多く抽出することが可能となる。なお、上記では、ウエハ内において要求された規格を満足しない規格外領域を画定したが、要求された規格を満足する規格内領域を画定して、第1種および第2種の半導体ウエハの最適な組合せを選定してもかまわない。

【0055】

以上、実施例を用いて本発明を説明したが、本発明はこれら実施例に制限されるものではない。たとえば、実施例では、オリエンテーションフラットが形成された半導体ウエハについて説明したが、ノッチが形成された半導体ウエハを用いてもかまわない。その他、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0056】

10 第1種の半導体ウエハ、

11 第1の半導体チップ、

12 第1の半導体素子層、

13 第1の配線層、

15 第1の規格外領域、

20 第2種の半導体ウエハ、

21 第2の半導体ウエハ、

22 第2の半導体素子層、

23 第2の配線層、

25 第2の規格外領域、

30 第3種の半導体ウエハ、

31 第3の半導体チップ、

32 第3の半導体素子層、

33 第3の配線層、

40 第4種の半導体ウエハ、

41 第4の半導体チップ、

42 第4の半導体素子層、

43 第4の配線層、

50 半導体ウエハ積層体、

51 電極端子、

52 半田バンプ、

53 半導体チップ積層体、

55 不良領域、

61 測定装置、

62 記憶装置、

63 演算装置、

64 ウエハ積層装置。

【技術分野】

【0001】

本発明は、半導体ウエハ積層体の製造方法および製造システムに関する。

【背景技術】

【0002】

電子機器に搭載される集積回路素子の高速化、小型化および低コスト化が進められている。集積回路素子は、所定の機能を果たす複数の半導体チップを積層し、その積層された半導体チップ(半導体チップ積層体)をモールド樹脂等によりパッケージングして製造することができる(たとえば特許文献1)。

【0003】

半導体チップは、ウエハと呼ばれる半導体基板の表面に光学処理等を施すことにより形成される。たとえば、直径300mmのウエハ上に、数百〜数千個の半導体チップを形成することができる。

【0004】

半導体チップ積層体を得る方法には、たとえばチップトゥチップ積層法やウエハトゥウエハ積層法などがある。チップトゥチップ積層法とは、複数の半導体チップが形成された各種ウエハをそれぞれ単一の半導体チップに分割した後に、その分割された各種半導体チップを積層して半導体チップ積層体を得る方法である。ウエハトゥウエハ積層法とは、複数の半導体チップが形成された各種ウエハを積層した後に、その積層されたウエハ(ウエハ積層体)を分割して半導体チップ積層体を得る方法である。ウエハトゥウエハ積層法は、チップトゥチップ積層法よりも生産性が高く、製造される集積回路素子の低コスト化に貢献しうる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−53081号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ウエハトゥウエハ積層法の生産性は、さらに改善される必要がある。本発明の目的は、ウエハトゥウエハ積層法によって製造される半導体チップ積層体の歩留りを改善することにある。

【課題を解決するための手段】

【0007】

本発明の一観点によれば、第1の半導体チップが複数形成された第1種の半導体ウエハ、および第2の半導体チップが複数形成された第2種の半導体ウエハが積層してなる半導体ウエハ積層体の製造方法であって、前記第1の半導体チップ各々の物理的または電気的特性が既知である前記第1種の半導体ウエハを複数用意し、前記第2の半導体チップ各々の物理的または電気的特性が既知である前記第2種の半導体ウエハを複数用意し、前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う半導体ウエハ積層体の製造方法、が提供される。

【0008】

本発明の他の観点によれば、第1の半導体チップが複数形成された第1種の半導体ウエハ、および第2の半導体チップが複数形成された第2種の半導体ウエハが積層してなる半導体ウエハ積層体の製造システムであって、前記第1種の半導体ウエハに形成された第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハに形成された第2の半導体チップ各々の物理的または電気的特性を測定する測定装置と、前記測定装置によって測定された前記第1種の半導体ウエハにおける前記第1の半導体チップ各々の物理的または電気的特性、および複数の前記第2種の半導体ウエハにおける前記第2の半導体チップ各々の物理的または電気的特性を、複数の前記第1種および第2種の半導体ウエハに対して記憶する記憶装置と、前記記憶装置に記憶された前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う演算装置と、を含む半導体ウエハ積層体の製造システム、が提供される。

【発明の効果】

【0009】

ウエハトゥウエハ積層法によって製造される半導体チップ積層体の歩留りが改善される。

【図面の簡単な説明】

【0010】

【図1】図1Aは、複数種類の半導体ウエハを積層し、半導体ウエハ積層体を形成する様子を示す概略斜視図であり、図1Bは、複数種類の半導体ウエハを積層し、各種半導体ウエハに形成された半導体チップを相互に電気的に接続した様子の一部を示す概略断面図である。

【図2】図2A〜図2Dは、それぞれ半導体ウエハ10a〜40aにおける半導体チップ11〜41の不良分布を示す平面図であり、図2Eは、半導体ウエハ10a〜40aを積層した半導体ウエハ積層体50aにおける半導体チップ積層体53の不良分布を示す平面図である。

【図3】図3A〜図3Dは、それぞれ半導体ウエハ10b〜40bにおける半導体チップ11〜41の不良分布を示す平面図であり、図3Eは、半導体ウエハ10b〜40bを積層した半導体ウエハ積層体50bにおける半導体チップ積層体53の不良分布を示す平面図である。

【図4】図4は、実施例による半導体ウエハ積層体の製造システムを概略的に示すダイアグラムである。

【図5】図5Aおよび図5Bは、演算装置による第1の処理を概略的に示すダイアグラムである。

【図6】図6Aおよび図6Bは、演算装置による第2の処理を概略的に示すダイアグラムである。

【図7】図7Aおよび図7Bは、演算装置による他の処理を概略的に示すダイアグラムである。

【発明を実施するための形態】

【0011】

図1Aは、複数種類の半導体ウエハを積層し、半導体ウエハ積層体を形成する様子を示す概略斜視図である。半導体ウエハ積層体50は、たとえば、シリコン基板から構成される半導体ウエハを2〜5枚程度積層して形成され、その厚みは10μm〜50μm程度である。図1Aには、例として4枚の半導体ウエハ10,20,30,40を積層する場合を示す。半導体ウエハ10〜40には、それぞれ半導体チップ11,21,31,41が複数形成されている(図1Aでは半導体チップ31,41は図示していない)。半導体チップ11〜41各々には、たとえば、CPU(central processing unit),DRAM(dynamic random access memory),フラッシュメモリなどの集積回路が形成される。半導体ウエハ10〜40各々は、たとえば直径が300mm程度であり、数百〜数千個の半導体チップ11〜41が形成されている。なお、図1Aでは、便宜的に、半導体チップのサイズを実際のサイズよりも大きく示している。

【0012】

図1Bは、複数種類の半導体ウエハを積層し、各種半導体ウエハに形成された半導体チップを相互に電気的に接続した様子の一部を示す概略断面図である。

【0013】

半導体ウエハ10に形成される半導体チップ11は、たとえば半導体素子層12および配線層13を含む。半導体素子層12には、MOSトランジスタ等の半導体素子が複数形成されている。配線層13には、半導体素子層12に形成された複数の半導体素子を相互に電気的に接続する配線が形成されている。これにより、半導体チップ11は、所定の機能を果たす集積回路として動作する。

【0014】

半導体チップ11は、さらに、半導体チップ11を貫通して設けられる複数の電極端子51、および複数の電極端子51各々と導通し、半導体チップ11の両面に設けられる複数の電極パッドないし半田バンプ52を含む。単一の半導体チップ11には、たとえば数万個の電極端子51が形成されうる。なお、この電極端子51は、TSV(through silicon via)と呼ばれることがある。

【0015】

半導体ウエハ20〜40は、半導体ウエハ10と同様の構成を有し、それぞれ半導体素子層22〜42,配線層22〜24,電極端子51,半田バンプ52を含む構成である。半導体ウエハ10〜40は積層され、半導体ウエハ10〜40各々の両面に形成された半田バンプ52を介して相互に電気的に接続される。これにより、半導体ウエハ積層体50が形成される。

【0016】

さらに、形成された半導体ウエハ積層体50を個々の積層された半導体チップ11〜41に分割することにより、半導体チップ積層体53を得ることができる。半導体チップ積層体53は、半導体チップ11〜41が相互に協働して、所定の機能を果たすデバイスとして動作する。半導体チップ11〜41が、たとえば、それぞれイメージングセンサ回路、アナログーデジタル変換回路、レジスタ回路およびプロセッサ回路として機能する集積回路である場合、半導体チップ積層体53は、イメージングセンサデバイスとして動作する。

【0017】

半導体ウエハには、製造装置のバラつきなどによって、少なからず不良の半導体チップが形成されうる。また、その不良の半導体チップが形成される位置・分布は、製造される半導体ウエハごとに異なる可能性がある。半導体チップ積層体は、それを構成する複数の半導体チップが協働することによって、所定の機能を果たすデバイスとして動作する。したがって、複数の半導体チップのいずれか1つの半導体チップが適正に動作しないような場合には、半導体チップ積層体も適正に動作しえず、その半導体チップ積層体は不良品となる。

【0018】

図2A〜図2Dは、それぞれ半導体ウエハ10a〜40aにおける半導体チップ11〜41の不良分布を示す平面図である。ここで、半導体ウエハ10a〜40a各々には、32個の半導体チップ11〜41が形成され、32個の半導体チップうち4個の不良半導体チップ11d〜41d(不良チップ)が形成されているものとする。つまり、半導体ウエハ10a〜40a各々の不良率は4/32である。図中において、ウエハ内に形成された不良チップは斜線で示されている。

【0019】

図2Aに示すように、半導体ウエハ10aには、不良チップ11dがウエハ左上方に集中して分布しているものとする。図2Bに示すように、半導体ウエハ20aには、不良チップ21dがウエハ右上方に集中して分布しているものとする。図2Cに示すように、半導体ウエハ30aには、不良チップ31dがウエハ左下方に集中して分布しているものとする。図2Dに示すように、半導体ウエハ40aには、不良チップ41dがウエハ右下方に集中して分布しているものとする。

【0020】

このような不良チップ分布を有する半導体ウエハ10a〜40aを積層して、半導体ウエハ積層体50a、さらに半導体チップ積層体53を形成する。形成される半導体チップ積層体53各々は、それを構成する半導体チップ11〜41の少なくとも1つの半導体チップが不良チップである場合には、不良と見なされる。

【0021】

図2Eは、図2A〜図2Dに示す半導体ウエハ10a〜40aを積層した半導体ウエハ積層体50aにおける半導体チップ積層体53の不良分布を示す平面図である。図2A〜図2Dに示す半導体ウエハ10a〜40aを積層して半導体ウエハ積層体50aを形成した場合、この半導体ウエハ積層体50の不良率は、半導体ウエハ10a〜40a各々の不良率の単純な総和となり、16/32となる。

【0022】

図3A〜図3Dは、それぞれ半導体ウエハ10b〜40bにおける半導体チップ11〜41の不良分布を示す平面図である。ここで、半導体ウエハ10b〜40b各々の不良率は、図2A〜図2Dと同様に、4/32であるものとする。ただし、図2A〜2Dに示す不良チップ分布とは異なり、半導体ウエハ10b〜40bのいずれの半導体ウエハにおいても、不良チップ11d〜41dがウエハ左上方に集中して分布しているものとする。

【0023】

図3Eは、図3A〜図3Dに示す半導体ウエハ10b〜40bを積層した半導体ウエハ積層体50bにおける半導体チップ積層体53の不良分布を示す平面図である。図3A〜図3Dに示す半導体ウエハ10b〜40bを積層して半導体ウエハ積層体50bを形成した場合、この半導体ウエハ積層体50bの不良率は、8/32となる。図2A〜図2Dに示す半導体ウエハ10a〜40aを積層する場合よりも、形成される半導体チップ積層体の不良率は低くなる。このように、各種半導体ウエハに形成される不良チップ同士をより多く積層させる、つまりウエハ内の同じような位置に不良チップ分布を有する半導体ウエハ同士を積層させることにより、不良品である半導体チップ積層体を減らし、良品である半導体チップ積層体をより多く得ることができるようになる。

【0024】

たとえば、半導体チップ各々の構造が複雑であり、かつ、半導体チップの実装密度も高い半導体ウエハの歩留りは、おおよそ70〜80%程度である。無作為に抽出された歩留り70〜80%程度の半導体ウエハを4枚積層して形成される半導体ウエハ積層体の積層歩留りは、24〜41%程度となる。一方、ウエハ内の同じような位置に不良チップ分布を有する半導体ウエハを選定して形成される半導体ウエハ積層体の積層歩留りは、理想的には単一の半導体ウエハの歩留りと同等である70〜80%程度にすることが可能である。

【0025】

以下、半導体ウエハ積層体の歩留りを改善することができる製造方法および製造システムについて、具体的に説明する。

【0026】

図4は、実施例による半導体ウエハ積層体の製造システムを概略的に示すダイアグラムである。なお、以下では、2種類の半導体ウエハからなる半導体ウエハ積層体を3つ形成する場合について説明する。

【0027】

実施例による導体ウエハ積層体の製造システムは、測定装置61、記憶装置62および演算装置63を含む構成である。

【0028】

測定装置61は、第1種の半導体ウエハ10a〜10c各々に形成される複数の半導体チップ11(図1Aないし図1B)の物理的または電気的な特性、および第2種の半導体ウエハ20a〜20c各々に形成される複数の半導体チップ21(図1Aないし図1B)の物理的または電気的な特性を測定する。半導体チップ11,21の物理的特性とは、たとえば、半導体素子層12,22(図1B)ないし配線層13,23(図1B)の層厚や、配線層13,23に形成される配線の幅、半導体チップ11,21に含まれる格子欠陥密度などである。また、半導体チップ11,21の電気的特性とは、たとえば、半導体チップ11,21に形成される集積回路の各回路ブロックにおける電流・電圧値(電気的な短絡・開放を含む)や、動作クロック周波数特性などである。

【0029】

測定装置61によって測定された半導体ウエハ10a〜10c各々における半導体チップ11各々の特性データ、および半導体ウエハ20a〜20c各々における半導体チップ21各々の特性データは、記憶装置62に転送される。なお、測定装置61は、半導体ウエハ10a〜10cを測定する測定装置と、半導体ウエハ20a〜20cを測定する測定装置と、を別々に構成した測定装置であってもかまわない。また、半導体チップの物理的特性を測定する測定装置と、電気的特性を測定する測定装置と、を別々に構成した測定装置であってもかまわないし、半導体ウエハないし半導体チップのその他の特性・性能を測定する測定装置を別途設けてもかまわない。

【0030】

記憶装置62は、測定装置61によって測定された半導体ウエハ10a〜10c各々における半導体チップ11各々の特性データ、および半導体ウエハ20a〜20c各々における半導体チップ21各々の特性データを記憶する。記憶装置62は、たとえば、HDD(hard disk drive)やフラッシュメモリなどを用いることができる。記憶装置62に記憶された各半導体ウエハの特性データは、演算装置63などの外部機器から読み出すことができる。

【0031】

演算装置63は、記憶装置62に記憶された半導体ウエハ10a〜10c各々における半導体チップ11各々の特性データ、および半導体ウエハ20a〜20c各々における半導体チップ21各々の特性データに基づいて、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20c各々の不良チップ分布を算出する。さらに、演算装置63は、算出された半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20c各々の不良チップ分布に基づいて、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの選定を行う。その際、演算装置63は、たとえば、最終的に形成される複数の半導体ウエハ積層体の歩留りが最も高くなるように、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せを選定する。演算装置63は、たとえばパーソナルコンピュータ(PC)などを用いることができる。

【0032】

半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cは、その後、演算装置63によって選定された組合せで、ウエハ積層装置64により積層される。このようにして、半導体ウエハ積層体50a〜50cが製造される。

【0033】

次に、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せを最適化する演算装置63の第1の処理について説明する。

【0034】

図5Aは、第1種の半導体ウエハ10aおよび第2種の半導体ウエハ20aの不良チップ分布を示す平面図である。また、半導体ウエハ10aおよび半導体ウエハ20aを積層させた際に形成される半導体ウエハ積層体50の不良分布を示す平面図である。

【0035】

演算装置63は、記憶装置62に記憶された半導体ウエハ10a〜10c各々における半導体チップ11各々の特性データに基づいて、半導体ウエハ10a〜10c各々の不良チップ分布を算出する。たとえば、演算装置63は、図5Aに示す半導体ウエハ10aのように、電気的短絡・開放等により適正に動作しない半導体チップ11dに数値0のフラグをたて、それ以外の半導体チップ11gに数値1のフラグをたてる。

【0036】

同様に、演算装置63は、記憶装置62に記憶された半導体ウエハ20a〜20c各々における半導体チップ21各々の特性データに基づいて、半導体ウエハ20a〜20c各々の不良チップ分布を算出する。たとえば、演算装置63は、図5Aに示す半導体ウエハ20aのように、たとえば電気的短絡・開放等により適正に動作しない半導体チップ21dに数値0のフラグをたて、それ以外の半導体チップ21gに数値1のフラグをたてる。

【0037】

さらに、演算装置63は、図5Aに示す半導体ウエハ積層体50のように、半導体ウエハ10aと半導体ウエハ20aとを積層して形成される半導体チップ積層体53各々に、それを構成する半導体チップ11,21に付されたフラグを積算したフラグをたてる。このとき、フラグが0となる半導体チップ積層体53は不良品の半導体チップ積層体53dとなり、フラグが1となる半導体チップ積層体53は良品の半導体チップ積層体53gとなる。

【0038】

演算装置63は、さらに、半導体チップ積層体53各々に付されたフラグの累計を算出する。つまり、半導体ウエハ10aおよび半導体ウエハ20aを積層したときに、半導体チップ11各々のフラグと、半導体チップ11各々にそれぞれ重畳する半導体チップ21各々のフラグと、を積算したフラグの累計を算出する。図5Aに示す半導体ウエハ積層体50におけるフラグの累計は、25である。ここで、半導体ウエハ10aおよび半導体ウエハ20aを積層させた半導体ウエハ積層体50の半導体チップ積層体53各々に付されたフラグの累計を、半導体ウエハ10aおよび半導体ウエハ20aの良品累計値C11と呼ぶこととする。

【0039】

演算装置63は、以上のような処理を、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cのすべてのペアに対して行い、各ペアの良品累計値を算出する。半導体ウエハ10aおよび半導体ウエハ20a〜20c各々の良品累計値を、それぞれC11,C12,C13とする。半導体ウエハ10bおよび半導体ウエハ20a〜20c各々の良品累計値を、それぞれC21,C22,C23とする。半導体ウエハ10cおよび半導体ウエハ20a〜20c各々の良品累計値を、それぞれC31,C32,C33とする。

【0040】

図5Bに、積層されうる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せP1〜P6を示す。演算装置63は、積層されうる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せP1〜P6各々に対して、良品累計値の総和S1〜S6を算出する。演算装置63は、良品累計値の総和が最大となる組合せで、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの選定を行う。

【0041】

演算装置63がこのような処理を行うことにより、半導体ウエハを無作為に抽出して半導体ウエハ積層体を形成する場合よりも、歩留りを改善することができる。なお、2種類以上の半導体ウエハを積層させて3つ以上の半導体ウエハ積層体を形成するような場合でも、組合せの場合の数は大きくなるが、上記と同様の方法により、各種半導体ウエハの最適化された組合せを選定することは可能である。一度に照合を行う各種半導体ウエハの枚数は、たとえば各種半導体ウエハの生産ロットに対応する枚数(たとえば25枚)とすればよい。

【0042】

次に、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せを最適化する演算装置63の第2の処理について説明する。

【0043】

図6Aおよび図6Bは、第1種の半導体ウエハ10a〜10cおよび第2種の半導体ウエハ20a〜20cの不良チップ分布を示す平面図である。演算装置63は、上記に示した第1の処理と同様に、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20c各々の不良チップ分布を算出する。

【0044】

演算装置63は、第1種および第2種の半導体ウエハのどちらか一方、たとえば第1種の半導体ウエハ10a〜10cの中から、半導体チップ11各々に付されたフラグの累計が最も大きい第1種の半導体ウエハを選定する。図6Aに示す半導体ウエハ10a〜10cにおいて、フラグの累計はそれぞれ27,28,30である。したがって、フラグの累計が30である半導体ウエハ10cを選定する。

【0045】

次に、演算装置63は、第2種の半導体ウエハ20a〜20cの中から、半導体ウエハ10cと積層させたときに、良品累計値が最も大きくなる第2種の半導体ウエハを選定する。半導体ウエハ10cおよび半導体20a〜20c各々の良品累計値は、それぞれ26,26,28となる。したがって、良品累計値が28となる半導体ウエハ20cを選定する。選定された半導体ウエハ10cおよび半導体ウエハ20cにより、半導体ウエハ積層体を形成する。

【0046】

次に、演算装置63は、半導体ウエハ10cおよび半導体ウエハ20cを除いた半導体ウエハに対して同様の処理を行う。つまり、図6Bに示すように、半導体ウエハ10a,10bの中から、フラグの累計が大きい半導体ウエハ10bを選定し、半導体ウエハ20a,20bの中から、半導体ウエハ10bと積層したときに良品累計値が大きくなる半導体ウエハ20aを選定する。選定された半導体ウエハ10bおよび半導体ウエハ20aにより、半導体ウエハ積層体を形成する。また、残った半導体ウエハ10aおよび半導体ウエハ20bにより、半導体ウエハ積層体を形成する。

【0047】

このような処理においても、半導体ウエハを無作為に抽出して半導体ウエハ積層体を形成する場合よりも、歩留りを改善することができる。なお、以上では、不良品と判定した半導体チップに0のフラグをたて、良品と判定した半導体チップに1のフラグをたてたが、逆に不良品と判定した半導体チップに1のフラグをたて、良品と判定した半導体チップに0のフラグをたてて、各種半導体ウエハの最適な組合せを算出してもかまわない。また、半導体チップに付す数値は、0および1以外の数値でもよい。

【0048】

以上では、半導体ウエハに形成される半導体チップ単位で、良品/不良品の判定を行ったが、半導体ウエハ内の領域単位で、良品領域/不良品領域の判定を行ってもかまわない。また、良品領域/不良品領域を、要求されている物理的または電気的特性を満足する規格内領域/要求されている物理的または電気的特性を満足しない規格外領域として判定を行ってもかまわない。以下に、積層させる半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cの組合せを最適化する演算装置63の他の処理について説明する。

【0049】

図7Aは、第1種の半導体ウエハ10aおよび第2種の半導体ウエハ20aの規格外領域を示す平面図である。また、半導体ウエハ10aおよび半導体ウエハ20aを積層させた際に形成される半導体ウエハ積層体50の不良領域を示す平面図である。

【0050】

演算装置63は、記憶装置62に記憶された複数の半導体ウエハ10a〜10c各々における半導体チップの特性データ、および要求されている物理的または電気的特性に基づいて、半導体ウエハ10a〜10c各々に対し、所定の特性分布を有する領域を画定する。演算装置63は、たとえば、図7Aに示す半導体ウエハ10aのように、要求されている物理的または電気的特性を満足しない半導体チップが形成されている領域を規格外領域15として画定する。

【0051】

同様に、演算装置63は、記憶装置62に記憶された複数の半導体ウエハ20a〜20c各々における半導体チップの特性データ、および要求されている物理的または電気的特性に基づいて、半導体ウエハ20a〜20c各々に対し、所定の特性分布を有する領域を画定する。たとえば、演算装置63は、図7Aに示す半導体ウエハ20aのように、要求されている物理的または電気的特性を満足しない半導体チップが形成されている領域を規格外領域25として画定する。

【0052】

なお、規格外領域15,25とは、たとえば、半導体素子層12,22(図1B)ないし配線層13,23(図1B)の層厚や、配線層13,23(図1B)に形成される配線の幅、半導体チップ11,21に含まれる格子欠陥密度などが、要求されている規格から外れている領域である。

【0053】

さらに、演算装置63は、図7Aに示す半導体ウエハ積層体50のように、半導体ウエハ10aと半導体ウエハ20aとを積層させた際の規格外領域15,25を合成した不良領域55を画定する。以降、上記第1の処理と同じように、半導体ウエハ10a〜10cおよび半導体ウエハ20a〜20cのすべてのペアに対して不良領域を画定し、不良領域の面積の総和が最小となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う。このような処理においても、半導体ウエハを無作為に抽出して半導体ウエハ積層体を形成する場合よりも、規格を満たす半導体チップ積層体をより多く抽出することが可能となる。

【0054】

図7Bは、第1種の半導体ウエハ10a〜10cおよび第2種の半導体ウエハ20a〜20cにおける所定の特性分布を示す平面図である。演算装置63は、複数の第1種および第2種の半導体ウエハ各々に対して、規格外領域15,25を画定した後、上記第2の処理と同じように、積層させる第1種および第2種の半導体ウエハの選定を行ってもよい。つまり、図7Bに示すように、第1種の半導体ウエハ10a〜10cから規格外領域15の面積が最小である半導体ウエハ10cを選定し、その後、半導体ウエハ10cと積層させたときに不良領域の面積が最小になる半導体ウエハ20cを選定する。このような処理を繰り返し行い、積層させる第1種および第2種の半導体ウエハの選定を行う。このような処理においても、半導体ウエハを無作為に抽出して半導体ウエハ積層体を形成する場合よりも、規格を満たす半導体チップ積層体をより多く抽出することが可能となる。なお、上記では、ウエハ内において要求された規格を満足しない規格外領域を画定したが、要求された規格を満足する規格内領域を画定して、第1種および第2種の半導体ウエハの最適な組合せを選定してもかまわない。

【0055】

以上、実施例を用いて本発明を説明したが、本発明はこれら実施例に制限されるものではない。たとえば、実施例では、オリエンテーションフラットが形成された半導体ウエハについて説明したが、ノッチが形成された半導体ウエハを用いてもかまわない。その他、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0056】

10 第1種の半導体ウエハ、

11 第1の半導体チップ、

12 第1の半導体素子層、

13 第1の配線層、

15 第1の規格外領域、

20 第2種の半導体ウエハ、

21 第2の半導体ウエハ、

22 第2の半導体素子層、

23 第2の配線層、

25 第2の規格外領域、

30 第3種の半導体ウエハ、

31 第3の半導体チップ、

32 第3の半導体素子層、

33 第3の配線層、

40 第4種の半導体ウエハ、

41 第4の半導体チップ、

42 第4の半導体素子層、

43 第4の配線層、

50 半導体ウエハ積層体、

51 電極端子、

52 半田バンプ、

53 半導体チップ積層体、

55 不良領域、

61 測定装置、

62 記憶装置、

63 演算装置、

64 ウエハ積層装置。

【特許請求の範囲】

【請求項1】

第1の半導体チップが複数形成された第1種の半導体ウエハ、および第2の半導体チップが複数形成された第2種の半導体ウエハが積層してなる半導体ウエハ積層体の製造方法であって、

前記第1の半導体チップ各々の物理的または電気的特性が既知である前記第1種の半導体ウエハを複数用意し、

前記第2の半導体チップ各々の物理的または電気的特性が既知である前記第2種の半導体ウエハを複数用意し、

前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う、

半導体ウエハ積層体の製造方法。

【請求項2】

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップが形成されている領域を第1の規格外領域とし、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップが形成されている領域を第2の規格外領域とし、

前記第1種および第2種の半導体ウエハを積層させた際の前記第1および第2の規格外領域を合成した領域を不良領域としたとき、

前記複数の第1種および第2種の半導体ウエハの中から、前記不良領域の面積の総和が最小となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う請求項1記載の半導体ウエハ積層体の製造方法。

【請求項3】

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップが形成されている領域を第1の規格外領域とし、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップが形成されている領域を第2の規格外領域とし、

前記第1種および第2種の半導体ウエハを積層させた際の前記第1および第2の規格外領域を合成した領域を不良領域としたとき、

前記複数の第1種の半導体ウエハの中から、前記第1の規格外領域の面積が最小である第1種の半導体ウエハを、第1種の最良半導体ウエハとして選定し、

前記複数の第2種の半導体ウエハの中から、前記第1種の最良半導体ウエハと積層させた際に、前記不良領域の面積が最小となる第2種の半導体ウエハを選定する請求項1記載の半導体ウエハ積層体の製造方法。

【請求項4】

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップに数値0を付し、該数値0を付した第1の半導体チップ以外の前記第1の半導体チップに0よりも大きい有限の数値を付し、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップに数値0を付し、該数値0を付した第2の半導体チップ以外の前記第2の半導体チップに0よりも大きい有限の数値を付し、

前記第1種および第2種の半導体ウエハを積層させた際、前記第1の半導体チップ各々に付された数値と、前記第1の半導体チップ各々に重畳する前記第2の半導体チップ各々に付された数値と、をそれぞれ積算した数値の累計を良品累計値としたとき、

前記複数の第1種および第2種の半導体ウエハの中から、前記良品累計値の総和が最大となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う請求項1記載の半導体ウエハ積層体の製造方法。

【請求項5】

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップに数値0を付し、該数値0を付した第1の半導体チップ以外の前記第1の半導体チップに0よりも大きい有限の数値を付し、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップに数値0を付し、該数値0を付した第2の半導体チップ以外の前記第2の半導体チップに0よりも大きい有限の数値を付し、

前記第1種および第2種の半導体ウエハを積層させた際、前記第1の半導体チップ各々に付された数値と、前記第1の半導体チップ各々に重畳する前記第2の半導体チップ各々に付された数値と、をそれぞれ積算した数値の累計を良品累計値としたとき、

前記複数の第1種の半導体ウエハの中から、前記第1の半導体チップ各々に付された数値の総和が最大となる第1種の半導体ウエハを、第1種の最良半導体ウエハとして選定し、

前記複数の第2種の半導体ウエハの中から、前記第1種の最良半導体ウエハと積層した際に、前記良品累計値が最大となる第2種の半導体ウエハを選定する請求項1記載の半導体ウエハ積層体の製造方法。

【請求項6】

第1の半導体チップが複数形成された第1種の半導体ウエハ、および第2の半導体チップが複数形成された第2種の半導体ウエハが積層してなる半導体ウエハ積層体の製造システムであって、

前記第1種の半導体ウエハに形成された第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハに形成された第2の半導体チップ各々の物理的または電気的特性を測定する測定装置と、

前記測定装置によって測定された前記第1種の半導体ウエハにおける前記第1の半導体チップ各々の物理的または電気的特性、および複数の前記第2種の半導体ウエハにおける前記第2の半導体チップ各々の物理的または電気的特性を、複数の前記第1種および第2種の半導体ウエハに対して記憶する記憶装置と、

前記記憶装置に記憶された前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う演算装置と、

を含む半導体ウエハ積層体の製造システム。

【請求項7】

前記演算装置は、

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップが形成されている領域を第1の規格外領域とし、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップが形成されている領域を第2の規格外領域とし、

前記第1種および第2種の半導体ウエハを積層させた際の前記第1および第2の規格外領域を合成した領域を不良領域としたとき、

前記複数の第1種および第2種の半導体ウエハの中から、前記不良領域の面積の総和が最小となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う請求項6記載の半導体ウエハ積層体の製造システム。

【請求項8】

前記演算装置は、

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップが形成されている領域を第1の規格外領域とし、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップが形成されている領域を第2の規格外領域とし、

前記第1種および第2種の半導体ウエハを積層させた際の前記第1および第2の規格外領域を合成した領域を不良領域としたとき、

前記複数の第1種の半導体ウエハの中から、前記第1の規格外領域の面積が最小である第1種の半導体ウエハを、第1種の最良半導体ウエハとして選定し、

前記複数の第2種の半導体ウエハの中から、前記第1種の最良半導体ウエハと積層させた際に、前記不良領域の面積が最小となる第2種の半導体ウエハを選定する請求項6記載の半導体ウエハ積層体の製造システム。

【請求項9】

前記演算装置は、

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップに数値0を付し、該数値0を付した第1の半導体チップ以外の前記第1の半導体チップに0よりも大きい有限の数値を付し、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップに数値0を付し、該数値0を付した第2の半導体チップ以外の前記第2の半導体チップに0よりも大きい有限の数値を付し、

前記第1種および第2種の半導体ウエハを積層させた際、前記第1の半導体チップ各々に付された数値と、前記第1の半導体チップ各々に重畳する前記第2の半導体チップ各々に付された数値と、をそれぞれ積算した数値の累計を良品累計値としたとき、

前記複数の第1種および第2種の半導体ウエハの中から、前記良品累計値の総和が最大となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う請求項6記載の半導体ウエハ積層体の製造システム。

【請求項10】

前記演算装置は、

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップに数値0を付し、該数値0を付した第1の半導体チップ以外の前記第1の半導体チップに0よりも大きい有限の数値を付し、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップに数値0を付し、該数値0を付した第2の半導体チップ以外の前記第2の半導体チップに0よりも大きい有限の数値を付し、

前記第1種および第2種の半導体ウエハを積層させた際、前記第1の半導体チップ各々に付された数値と、前記第1の半導体チップ各々に重畳する前記第2の半導体チップ各々に付された数値と、をそれぞれ積算した数値の累計を良品累計値としたとき、

前記複数の第1種の半導体ウエハの中から、前記第1の半導体チップ各々に付された数値の総和が最大となる第1種の半導体ウエハを、第1種の最良半導体ウエハとして選定し、

前記複数の第2種の半導体ウエハの中から、前記第1種の最良半導体ウエハと積層した際に、前記良品累計値が最大となる第2種の半導体ウエハを選定する請求項6記載の半導体ウエハ積層体の製造システム。

【請求項1】

第1の半導体チップが複数形成された第1種の半導体ウエハ、および第2の半導体チップが複数形成された第2種の半導体ウエハが積層してなる半導体ウエハ積層体の製造方法であって、

前記第1の半導体チップ各々の物理的または電気的特性が既知である前記第1種の半導体ウエハを複数用意し、

前記第2の半導体チップ各々の物理的または電気的特性が既知である前記第2種の半導体ウエハを複数用意し、

前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う、

半導体ウエハ積層体の製造方法。

【請求項2】

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップが形成されている領域を第1の規格外領域とし、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップが形成されている領域を第2の規格外領域とし、

前記第1種および第2種の半導体ウエハを積層させた際の前記第1および第2の規格外領域を合成した領域を不良領域としたとき、

前記複数の第1種および第2種の半導体ウエハの中から、前記不良領域の面積の総和が最小となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う請求項1記載の半導体ウエハ積層体の製造方法。

【請求項3】

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップが形成されている領域を第1の規格外領域とし、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップが形成されている領域を第2の規格外領域とし、

前記第1種および第2種の半導体ウエハを積層させた際の前記第1および第2の規格外領域を合成した領域を不良領域としたとき、

前記複数の第1種の半導体ウエハの中から、前記第1の規格外領域の面積が最小である第1種の半導体ウエハを、第1種の最良半導体ウエハとして選定し、

前記複数の第2種の半導体ウエハの中から、前記第1種の最良半導体ウエハと積層させた際に、前記不良領域の面積が最小となる第2種の半導体ウエハを選定する請求項1記載の半導体ウエハ積層体の製造方法。

【請求項4】

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップに数値0を付し、該数値0を付した第1の半導体チップ以外の前記第1の半導体チップに0よりも大きい有限の数値を付し、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップに数値0を付し、該数値0を付した第2の半導体チップ以外の前記第2の半導体チップに0よりも大きい有限の数値を付し、

前記第1種および第2種の半導体ウエハを積層させた際、前記第1の半導体チップ各々に付された数値と、前記第1の半導体チップ各々に重畳する前記第2の半導体チップ各々に付された数値と、をそれぞれ積算した数値の累計を良品累計値としたとき、

前記複数の第1種および第2種の半導体ウエハの中から、前記良品累計値の総和が最大となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う請求項1記載の半導体ウエハ積層体の製造方法。

【請求項5】

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップに数値0を付し、該数値0を付した第1の半導体チップ以外の前記第1の半導体チップに0よりも大きい有限の数値を付し、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップに数値0を付し、該数値0を付した第2の半導体チップ以外の前記第2の半導体チップに0よりも大きい有限の数値を付し、

前記第1種および第2種の半導体ウエハを積層させた際、前記第1の半導体チップ各々に付された数値と、前記第1の半導体チップ各々に重畳する前記第2の半導体チップ各々に付された数値と、をそれぞれ積算した数値の累計を良品累計値としたとき、

前記複数の第1種の半導体ウエハの中から、前記第1の半導体チップ各々に付された数値の総和が最大となる第1種の半導体ウエハを、第1種の最良半導体ウエハとして選定し、

前記複数の第2種の半導体ウエハの中から、前記第1種の最良半導体ウエハと積層した際に、前記良品累計値が最大となる第2種の半導体ウエハを選定する請求項1記載の半導体ウエハ積層体の製造方法。

【請求項6】

第1の半導体チップが複数形成された第1種の半導体ウエハ、および第2の半導体チップが複数形成された第2種の半導体ウエハが積層してなる半導体ウエハ積層体の製造システムであって、

前記第1種の半導体ウエハに形成された第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハに形成された第2の半導体チップ各々の物理的または電気的特性を測定する測定装置と、

前記測定装置によって測定された前記第1種の半導体ウエハにおける前記第1の半導体チップ各々の物理的または電気的特性、および複数の前記第2種の半導体ウエハにおける前記第2の半導体チップ各々の物理的または電気的特性を、複数の前記第1種および第2種の半導体ウエハに対して記憶する記憶装置と、

前記記憶装置に記憶された前記第1種の半導体ウエハ各々における前記第1の半導体チップ各々の物理的または電気的特性、および前記第2種の半導体ウエハ各々における前記第2の半導体チップ各々の物理的または電気的特性に基づいて、前記複数の第1種および第2種の半導体ウエハの中から、積層させる第1種および第2種の半導体ウエハの選定を行う演算装置と、

を含む半導体ウエハ積層体の製造システム。

【請求項7】

前記演算装置は、

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップが形成されている領域を第1の規格外領域とし、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップが形成されている領域を第2の規格外領域とし、

前記第1種および第2種の半導体ウエハを積層させた際の前記第1および第2の規格外領域を合成した領域を不良領域としたとき、

前記複数の第1種および第2種の半導体ウエハの中から、前記不良領域の面積の総和が最小となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う請求項6記載の半導体ウエハ積層体の製造システム。

【請求項8】

前記演算装置は、

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップが形成されている領域を第1の規格外領域とし、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップが形成されている領域を第2の規格外領域とし、

前記第1種および第2種の半導体ウエハを積層させた際の前記第1および第2の規格外領域を合成した領域を不良領域としたとき、

前記複数の第1種の半導体ウエハの中から、前記第1の規格外領域の面積が最小である第1種の半導体ウエハを、第1種の最良半導体ウエハとして選定し、

前記複数の第2種の半導体ウエハの中から、前記第1種の最良半導体ウエハと積層させた際に、前記不良領域の面積が最小となる第2種の半導体ウエハを選定する請求項6記載の半導体ウエハ積層体の製造システム。

【請求項9】

前記演算装置は、

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップに数値0を付し、該数値0を付した第1の半導体チップ以外の前記第1の半導体チップに0よりも大きい有限の数値を付し、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップに数値0を付し、該数値0を付した第2の半導体チップ以外の前記第2の半導体チップに0よりも大きい有限の数値を付し、

前記第1種および第2種の半導体ウエハを積層させた際、前記第1の半導体チップ各々に付された数値と、前記第1の半導体チップ各々に重畳する前記第2の半導体チップ各々に付された数値と、をそれぞれ積算した数値の累計を良品累計値としたとき、

前記複数の第1種および第2種の半導体ウエハの中から、前記良品累計値の総和が最大となる組合せで、積層させる第1種および第2種の半導体ウエハの選定を行う請求項6記載の半導体ウエハ積層体の製造システム。

【請求項10】

前記演算装置は、

前記第1種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第1の半導体チップに数値0を付し、該数値0を付した第1の半導体チップ以外の前記第1の半導体チップに0よりも大きい有限の数値を付し、

前記第2種の半導体ウエハにおいて、所定の物理的または電気的特性から外れた前記第2の半導体チップに数値0を付し、該数値0を付した第2の半導体チップ以外の前記第2の半導体チップに0よりも大きい有限の数値を付し、

前記第1種および第2種の半導体ウエハを積層させた際、前記第1の半導体チップ各々に付された数値と、前記第1の半導体チップ各々に重畳する前記第2の半導体チップ各々に付された数値と、をそれぞれ積算した数値の累計を良品累計値としたとき、

前記複数の第1種の半導体ウエハの中から、前記第1の半導体チップ各々に付された数値の総和が最大となる第1種の半導体ウエハを、第1種の最良半導体ウエハとして選定し、

前記複数の第2種の半導体ウエハの中から、前記第1種の最良半導体ウエハと積層した際に、前記良品累計値が最大となる第2種の半導体ウエハを選定する請求項6記載の半導体ウエハ積層体の製造システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−115349(P2013−115349A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−262299(P2011−262299)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

[ Back to top ]