半導体スイッチおよび電力変換装置

【課題】主素子の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する半導体スイッチを提供する。

【解決手段】逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子1と、主素子1に比べ耐圧が低い逆流防止素子3と、主素子1の負極と逆流防止素子3の負極とを接続して主素子1の正極を正極端子とし、逆流防止素子3の正極を負極端子とし、正極端子と負極端子間に負極端子から正極端子に向かう方向が順方向となるように接続し、主素子1と同等の耐圧を有する高速還流ダイオード4と、主素子1の正極に正電圧が印加される方向に接続し、少なくとも主素子1の耐圧より低い電圧パルスを発生するとともに主素子1又は逆流防止素子3がオフする時期と略同期して電圧パルスを出力する予備電圧印加回路5と、を備えた半導体スイッチ。

【解決手段】逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子1と、主素子1に比べ耐圧が低い逆流防止素子3と、主素子1の負極と逆流防止素子3の負極とを接続して主素子1の正極を正極端子とし、逆流防止素子3の正極を負極端子とし、正極端子と負極端子間に負極端子から正極端子に向かう方向が順方向となるように接続し、主素子1と同等の耐圧を有する高速還流ダイオード4と、主素子1の正極に正電圧が印加される方向に接続し、少なくとも主素子1の耐圧より低い電圧パルスを発生するとともに主素子1又は逆流防止素子3がオフする時期と略同期して電圧パルスを出力する予備電圧印加回路5と、を備えた半導体スイッチ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体スイッチおよび電力変換装置に関する。

【背景技術】

【0002】

従来、主回路のスイッチング素子に還流ダイオードが逆並列接続された構成の電力変換回路においては、還流ダイオードの逆回復電流が流れることで生じる損失の低減する半導体スイッチおよびその半導体スイッチを備えた電力変換装置が望まれている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−193839号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

スイッチング素子に高速還流ダイオードが逆並列接続された半導体スイッチにおいて、主電流が逆方向に流れている時に半導体スイッチをオフした際(主素子と補助素子とをオフした際)、主素子の両端間に残留する電圧は、主素子と補助素子と高速還流ダイオードを結ぶ回路ループのインダクタンス値と、主電流の大きさの積で定まる。回路ループのインダクタンスは、半導体スイッチのスイッチング速度を高速にしたければ、出来るだけ小さく設計する必要があり、このため、主素子に残留する電圧は、数V未満の微小な値になってしまう場合があった。

【0005】

ここで、主素子オフ中の主素子の出力静電容量について、考慮する必要がある。例えば、このような半導体スイッチング素子の特性として、オフ中に印加されている残留電圧が低いと、非常に大きい静電容量を内蔵する特性を有している。これは、出力端子電圧が低いと接合部分の空乏層の厚みが薄いため、非常に大きな静電容量を有するためである。

【0006】

このように大きな静電容量時、直流主回路に2個の半導体スイッチを直列接続したブリッジ回路において、相補的に動作するもう一方の半導体スイッチがターンオンすると、この大きな静電容量に向かって充電電流が流れこむ。回路インピーダンスが非常に小さいため、この充電電流は、短絡的な大電流となり、大きな損失を発生させてしまう可能性があった。

【0007】

本発明の実施形態は、上述した事情を鑑みて成されたものであって、主素子の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する半導体スイッチを提供することを目的とする。

【課題を解決するための手段】

【0008】

実施形態によれば、逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子と、前記主素子に比べ耐圧が低い逆流防止素子と、前記主素子の負極と前記逆流防止素子の負極とを接続して前記主素子の正極を正極端子とし、前記逆流防止素子の正極を負極端子とし、前記正極端子と前記負極端子間に前記負極端子から前記正極端子に向かう方向が順方向となるように接続し、前記主素子と同等の耐圧を有する高速還流ダイオードと、前記主素子の正極に正電圧が印加される方向に接続し、少なくとも前記主素子の耐圧より低い電圧パルスを発生するとともに前記主素子又は前記逆流防止素子がオフする時期と略同期して前記電圧パルスを出力する予備電圧印加回路と、を備えた半導体スイッチが提供される。

【図面の簡単な説明】

【0009】

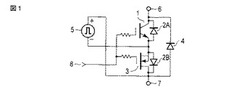

【図1】図1は、第1実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図2】図2は、第1実施形態の半導体スイッチの他の構成例を概略的に示す図である。

【図3】図3は、第1実施形態の半導体スイッチの他の構成例を概略的に示す図である。

【図4】図4は、第2実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図5】図5は、第3実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図6】図6は、第4実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図7】図7は、第5実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図8】図8は、スーパージャンクション型MOSFETの容量特性の一例を示す図である。

【図9】図9は、スーパージャンクション型MOSFETの出力充電電荷特性の一例を示す図である。

【図10】図10は、微細化スーパージャンクション型MOSFETの容量特性の一例を示す図である。

【図11】図11は、第6実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図12】図12は、第7実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図13】図13は、第8実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図14】図14は、主素子と逆流防止素子とのオン/オフのタイミングの一例を説明するための図である。

【図15】図15は、第9実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図16】図16は、第10実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図17】図17は、一実施形態の電力変換装置の一構成例を概略的に示す図である。

【発明を実施するための形態】

【0010】

以下、実施形態に係る半導体スイッチについて、図面を参照して説明する。

【0011】

図1は、第1実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチは、主素子1と、逆流防止素子としての補助素子3と、高速還流ダイオード4と、予備電圧印加回路5と、を備えている。

【0012】

主素子1は電圧駆動型スイッチング素子であって、例えば600Vの耐圧を有するIGBT(絶縁ゲートバイポーラトランジスタ:Insulated Gate Bipolar Transistor)を適用することができる。このIGBTには、逆導通ダイオード2Aを逆並列接続し、逆導通性能を持たせている。主素子1の耐圧は、好ましくは100V以上、より好ましくは200V以上、さらに好ましくは250V以上の実現可能な電圧である、通常は250V以上の耐圧を有する素子を用いる。

【0013】

補助素子3は電圧駆動型スイッチング素子であって、例えば50Vの耐圧を有するMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)を適用することができる。補助素子3は主素子1よりも低耐圧である。このように、補助素子3に十分低い耐圧のMOSFETを用いる事で、補助素子3の導通抵抗を低くでき、かつ、補助素子3の半導体チップを小さくできる。一般に、MOSFETの導通抵抗は、素子耐圧の2.5乗に比例する事が知られており、補助素子3の素子耐圧を低くする事で、導通抵抗低減(導通損失低減)と、チップ面積低減(コストアップ低減)とを同時に満たす事が出来る。

【0014】

高速還流ダイオード4は、主素子1と同等の例えば600Vの耐圧を有し、主素子1に逆並列接続している逆導通ダイオード2Aに比べ、チップ面積が小さく、順方向の電圧降下は高いけれども、逆回復特性に優れた特性のものを用いる。なお、高速還流ダイオード4は、主素子1と同等あるいは主素子1の耐圧以上の耐圧を有していればよく、同等の耐圧のものに限定されるものではない。また、ダイオードは、一般的に耐圧が高くなる程、逆回復特性が悪化する特性を有する。従って、高速還流ダイオード4は、例えば、逆回復が高速な反面、低耐圧ダイオードを複数個直列に接続して構成しても良い。導通時の電圧降下が増えてしまうが、高速還流ダイオード4には、主電流が負極端子7から正極端子6に向かって流れている時のデッドタイム期間中にしか通流しないので、その通流時間比率は短く、増大する導通損失も僅かなものである。

【0015】

また、高速還流ダイオード4に、珪素より禁制帯の広い半導体材料(例えば、炭化珪素、窒化ガリウム、砒化ガリウム、ダイアモンドなど)からなるダイオードを適用して構成しても良い。珪素より禁制帯の広い半導体のダイオードを用いる事で、より高耐圧で、かつ、逆回復の高速な特性を得る事ができる。また、禁制帯の広い半導体材料は、珪素半導体より高価であるが、高速還流ダイオード4は、デッドタイムの短時間のみ通流するため、小チップ面積で済むのでコストアップを低く抑えることができる。

【0016】

予備電圧印加回路5は、補助素子3と並列で、補助素子3の正極に正電圧が印加される方向に接続される。例えば補助素子3がオフする時期よりも主素子1がオフする時期が遅い場合には、予備電圧印加回路5は、主素子1のゲート駆動信号がオフする時期と同期して、補助素子3の耐圧より低い電圧パルス、例えば、30Vの電圧パルスを出力する。

【0017】

主素子1の負極であるエミッタと補助素子3のソース端子とを接続し、主素子1の正極であるコレクタを正極端子6とし、補助素子3のドレイン端子を負極端子7とし、負極端子7から正極端子6に向かって、主素子1および補助素子3と並列な高速還流ダイオード4を接続する。

【0018】

主素子1と補助素子3とのゲート端子は、それぞれの素子に適当なゲート抵抗を介してそれぞれのゲート端子に共通のゲート駆動電圧8と接続する。ゲート駆動電圧8は、主素子1と補助素子3とのゲート端子に接続されたゲート抵抗を介して印加され、主素子1と補助素子3とは同期してオンおよびオフするように構成されている。

【0019】

このように構成された本実施形態において、主電流が逆方向、即ち負極端子7から正極端子6に向かって流れている時には、主電流は、負極端子7→補助素子3→逆導通ダイオード2A→正極端子6の経路で、通流している。この時、主素子1及び補助素子3がオフすると、補助素子3がオフすることで、主電流は、負極端子7→高速還流ダイオード4→正極端子6の経路に転流する。従って、正極端子6の経路に転流する時期は補助素子3がオフしてから所定の時間が経過した後である。この転流した時点で、予備電圧印加回路5から、30Vのパルスを出力すると、高速還流ダイオード4が導通しているので、30Vのパルス電圧は、主素子1のコレクタ−エミッタ間に印加される。この時、高速還流ダイオード4の順方向電圧降下分(通常1〜2V)は、僅かに電圧が低下する。従って、主素子1の出力端子には、凡そ28〜29Vの電圧が印加される。

【0020】

また、補助素子3の出力にも30Vのパルス電圧は、印加される。この間に、予備電圧印加回路5から出力される電力は、主素子1と補助素子3との出力端子電圧の充電に要する電力のみに限定され、外部主回路に流出しないため、少ない出力電力で済む。

【0021】

高耐圧の主素子の場合、主回路電圧に比べて十分低い電圧を印加するだけで、出力接合容量が急速に低下する特性を示すことが知られている。主素子1には、凡そ28〜29Vの電圧が印加されるため主素子1の出力接合容量は低くなっており、相補的に動作するもう一方の半導体スイッチがターンオンした際の短絡的大電流を抑制できる。

【0022】

一方、主電流が順方向、即ち正極端子6から負極端子7に向かって流れている時には、主素子1及び補助素子3がオフすると、主素子1が電流の遮断を行うので、オフした瞬間に主電圧(通常200〜400V程度)が主素子1の両端間に印加される。この場合には、予備電圧印加回路5から、30Vの電圧パルスを発生しても、主電圧より十分低いので、高速還流ダイオード4が逆阻止しており、予備電圧印加回路5からの主素子1への充電電流は流れない。したがって、予備電圧印加回路5からの電力は、主として補助素子3を充電するために消費され、極僅かなものとなる。

【0023】

上記のように本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0024】

図2は、上記半導体スイッチの変形例を示す回路図である。この例では、主素子1に寄生ダイオード2Bを含むMOSFETを適用し、補助素子(逆流防止素子)3としてダイオードを用いている。補助素子3は、正極端子6から負極端子7へ向かう方向を順方向として主素子1のエミッタと負極端子7との間に接続されている。すなわち、補助素子3がダイオードの場合、そのアノードが主素子1の負極と接続しカソードが負極端子7となる。

【0025】

主素子1にMOSFETを適用する場合、MOSFETには寄生ダイオード2Bが生じてしまうため、負極端子7から正極端子6への逆流を防止するために補助素子3としてダイオードを接続することが効果的である。なお、主素子1にIGBTを適用する場合にも、IGBTに逆導通ダイオード2Aを付加する場合には、同様に逆流防止のために補助素子3としてダイオードを接続すると、同様の効果を得ることができる。

【0026】

図2に示す半導体スイッチは、補助素子3の構成以外は上述の第1実施形態の半導体スイッチと同様の構成である。この変形例の半導体スイッチも上述の第1実施形態の半導体スイッチと同様の効果、すなわち、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0027】

図3は、上記半導体スイッチの他の変形例を示す回路図である。この例では、予備電圧印加回路5は主素子1と並列で、ダイオード(第2ダイオード)4´を介して主素子1の正極に正電圧が印加される方向に接続される。ダイオード4´は、例えば高速還流ダイオード4と同等の高耐圧の高速ダイオードである。なお、ダイオード4´は、主素子1と同等あるいは主素子1の耐圧以上の耐圧を有していればよく、同等の耐圧のものに限定されるものではない。予備電圧印加回路5は、主素子1及び補助素子3がオフしたタイミングで、少なくとも主素子1の耐圧より低い電圧パルスを発生する。

【0028】

図3に示す半導体スイッチは、上記予備電圧印加回路5の構成以外は上述の第1実施形態の半導体スイッチと同様の構成である。この変形例の半導体スイッチも上述の第1実施形態の半導体スイッチと同様の効果、すなわち、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0029】

次に、第2実施形態の半導体スイッチについて図面を参照して説明する。なお、以下の説明において同様の機能を有する構成については同一の符号を付して詳細な説明を省略する。

【0030】

図4は、第2実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチは、第1実施形態の半導体スイッチに対して、主素子1と補助素子3との直列接続の位置関係を入れ替えた構成である。この場合、主素子1と補助素子3とのゲートは、別の電位で駆動する必要があり、フォトカプラ(図示せず)などの絶縁手段で絶縁する必要がある。図4に示す場合では、主素子1のゲートはゲート駆動電圧8Aにより駆動され、補助素子3のゲートはゲート駆動電圧8Bにより駆動される。ゲート駆動電圧8A、8Bは、別々の直流電圧源に接続されたアンプから出力される。

【0031】

なお、補助素子3のゲート駆動電源は、本実施形態の半導体スイッチの高電位側に同種の半導体スイッチがある変換回路の場合には、高電位側の主素子1のゲート駆動電源を利用することができる。上記以外の構成は上述の第1実施形態の半導体スイッチと同様である。

【0032】

本実施形態の半導体スイッチにおいても、主電流が逆方向、即ち負極端子7から正極端子6に向かって流れている時には、主電流は負極端子7→逆導通ダイオード2A→補助素子3→正極端子6の経路で通流している。この時、主素子1及び補助素子3がオフすると、補助素子3がオフすることで、主電流は負極端子7→高速還流ダイオード4→正極端子6の経路に転流する。この転流した時点で、予備電圧印加回路5から30Vのパルスを出力すると、高速還流ダイオード4が導通しているので、30Vのパルス電圧は主素子1のコレクタ−エミッタ間に印加される。この時、高速還流ダイオード4の順方向電圧降下分(通常1〜2V)は、僅かに電圧が低下する。従って、主素子1の出力端子には、凡そ28〜29Vの電圧が印加される。

【0033】

また、補助素子3の出力にも30Vのパルス電圧は印加される。この間に、予備電圧印加回路5から出力される電力は、主素子1と補助素子3の出力端子電圧の充電に要する電力のみに限定され、外部主回路に流出しないため、少ない出力電力で済む。

【0034】

一方、主電流が順方向、即ち正極端子6から、負極端子7に向かって流れている時には、主素子1及び補助素子3がオフすると、主素子1が電流の遮断を行うので、オフした瞬間に主電圧(通常200〜400V程度)が主素子1の両端間に印加される。この場合には、予備電圧印加回路5から、30Vの電圧パルスを発生しても、主電圧より十分低いので、高速還流ダイオード4が逆阻止しており、予備電圧印加回路5からの主素子1への充電電流は流れない。したがって、予備電圧印加回路5からの電力は、主として補助素子3を充電するために、消費され、極僅かなものとなる。

【0035】

上記のように、本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0036】

次に、第3実施形態の半導体スイッチについて図面を参照して説明する。

図5は、第3実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチにおいて、主素子1にはMOSFET(例えば600Vの耐圧)を適用している。主素子1には、逆導通性能を有する寄生ダイオード2Bが内蔵している。また、予備電圧印加回路5は、直流電圧源11とスイッチ12とを直列接続して構成している。スイッチ12は例えば小型半導体スイッチである。本実施形態の半導体スイッチは上記以外の構成は上述の第1実施形態の半導体スイッチと同様である。

【0037】

本実施形態において、主素子1に低抵抗のMOSFETを適用する事で、主素子1の導通抵抗に補助素子3の導通抵抗分が加算される事になるが、補助素子3の耐圧を十分低く選定する事で、第1実施形態の半導体スイッチと同様に、補助素子3の導通抵抗は非常に少なくて済むため、加算された導通抵抗の増加分は極めて僅かで済む。

【0038】

また、主電流が逆方向に流れる際にも、主素子1及び補助素子3がオン状態であれば、主電流は、高速還流ダイオード4を流れず、低抵抗な主素子1と補助素子3との直列回路の方を通流する。

【0039】

この結果、本実施形態の半導体スイッチによれば、主素子1にIGBTを適用した第1実施形態の半導体スイッチに比べて、順方向及び逆方向に通電する際の導通損失を低減する事ができる。

【0040】

上記のように、本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0041】

次に、第4実施形態の半導体スイッチについて図面を参照して説明する。

図6は、第4実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチでは、予備電圧印加回路5は、直流電圧源11とスイッチ12とを直列接続して構成している。スイッチ12は、小型半導体スイッチとしてのpチャネル型MOSFETを適用している。以下本実施形態の説明においてスイッチ12をpチャネル型MOSFET12として説明する。

【0042】

pチャネル型MOSFET12のゲートへは、ゲート電圧レベルシフター13と適当なゲート抵抗を介して共通のゲート駆動電圧8から接続される。ゲート電圧レベルシフター13は、pチャネル型MOSFET12のソース電位が、主素子1のエミッタ電位または、補助素子3のソース電位に対して、直流電圧源11の電圧だけ高いため、この電位差をかさ上げしてゲート電位を合わせる為に必要となる。従って、ゲート電圧レベルシフター13の電位シフト値は、凡そ、直流電圧源11の電圧と等しく、直流電圧源11の電圧に連動して定まる値である。なお、ゲート電圧レベルシフター13は、コンデンサと、そのコンデンサへの充電回路の組合せで構成することも可能である。本実施形態の半導体スイッチは上記以外の構成は上述の第1実施形態の半導体スイッチと同様である。

【0043】

本実施形態の半導体スイッチにおいて、pチャネル型MOSFET12のゲート電位は、そのソース電位より低くなることでオンする。逆に、主素子1及び補助素子3のゲートは、電位が低くなる事でオフする。従って、pチャネル型MOSFET12は、主素子1、及び補助素子3がオフ状態となるとオンするように動作し、主素子1がオフした時期に主素子1に直流電圧源11の電圧を印加させる事ができる。

【0044】

すなわち、本実施形態によれば、上述の第1実施形態の半導体スイッチと同じ効果を、唯一の共通のゲート駆動電圧8から制御する事が可能となり、構成を単純化することができる。

【0045】

上記のように、本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0046】

次に、第5実施形態の半導体スイッチについて図面を参照して説明する。

図7は、第5実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチにおいて、予備電圧印加回路5は、直流電圧源としてパルス電圧源9と、絶縁トランス15を介してパルス電圧源9から電圧が印加される逆流防止ダイオード16とを有している。絶縁トランス15の一次回路にはパルス電圧源9が接続され、二次回路は逆流防止ダイオード16を介して補助素子3と並列接続されている。本実施形態の半導体スイッチは上記以外の構成は上述の第3実施形態の半導体スイッチと同様である。

【0047】

本実施形態の半導体スイッチにおいて、パルス電圧源9は、異なる電位からの電力の供給が可能となり、例えば、共通の制御電源から、変換器を構成する複数の同類の半導体スイッチへの電力の供給ができ、電源の共通化が可能となる。

【0048】

すなわち、本実施形態によれば、上述の第3実施形態の半導体スイッチと同じ効果を奏するとともに、予備電圧印加に要する電力を共通の電源から供給する事が可能となり、別々に電源を設ける必要がなくなる。従って、半導体スイッチの構成を単純化することができる。

【0049】

また、共通の制御回路からのパルス電圧発生が可能となり、よりタイミング精度の高いパルスを発生することが可能となる。従って、本実施形態の半導体スイッチによれば、最適なタイミングで必要最小限のパルス電圧発生でき、消費電力の節約が可能になる。

【0050】

上記のように、本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0051】

次に、上述の第3実施形態および第5実施形態の半導体スイッチの特性の一例について説明する。

【0052】

図8は、スーパージャンクション型MOSFETの容量特性の一例を示す図である。

図8は、主素子1に適用可能である600V耐圧のスーパージャンクション構造を有する縦型MOSFETの容量特性例を示している。図8において、横軸は、主素子1の出力端子電圧であるドレイン−ソース間電圧(Vds)を表しており、縦軸が静電容量値を示している。

【0053】

出力容量(Coss)の特性に注目すると、出力端子電圧が非常に低い0V近傍では、高い値を示しているが、出力端子電圧の上昇に伴って急速に低減する特性を示している。例えば、出力端子電圧が50Vまで上昇すれば、出力容量は凡そ1/40まで低減する。これは、印加電圧が低い場合には、空乏層が、まだ、薄いために、スーパージャンクション構造による折り畳まれた広い面積を持ってしまうために、大きな静電容量値を示しているけれども、印加電圧がある程度以上加わって、空乏層が厚くなると、スーパージャンクション構造由来の折り畳まれた面ではなく、平坦化された絶縁面となるため、大幅に面積の低下が生じる事によりもたらされる。

【0054】

図9は、このような出力容量特性を出力電圧の上昇に伴って主素子1に充電されていく電荷特性(Qoss)として表した図である。図9においても、横軸は、主素子1の出力端子電圧であるドレイン−ソース間電圧(Vds)を表しており、図8の容量特性を横軸のVdsで、積分して求めた特性である。

【0055】

もし、出力容量がVdsに因らずに一定の静電容量値を示す特性であれば、図9の特性は、原点から数直線的に上昇する特性を示す筈であるが、図9を見ると、ドレイン−ソース間電圧(Vds)が低い領域で急速な上昇を示し、50Vにて、凡そ0.63[μC]まで上昇し、主回路電圧を280Vの変換器での適用を想定すると、90%の電荷注入が完了している。

【0056】

すなわち、主素子1がスーパージャンクション構造を有する縦型MOSFETの場合には、低い電圧を印加するだけで、出力静電容量の大幅な低下が実現できる。

【0057】

したがって、この場合、主素子1の出力静電容量を大幅に低減し、接合容量充電電流に起因するターンオン損失の効果的な低減を可能にする。

【0058】

次に、上述の第3実施形態および第5実施形態の半導体スイッチの他の特性例について説明する。

【0059】

図10は、微細化したスーパージャンクション構造を有する縦型MOSFETの容量特性例を示している。図10において、横軸は、主素子1の出力端子電圧であるドレイン−ソース間電圧(Vds)を表しており、縦軸が静電容量値(対数メモリ)を示している。

【0060】

図10において、図8に示した一般的なスーパージャンクションMOSFETの出力容量特性と比較すると、ドレイン−ソース間電圧(Vds)がより低い電圧値にて、急低下する特性が見られる。このような特性は、スーパージャンクション構造のアスペクト比が高い場合に見られ、主素子1の耐圧600Vの1/30程度の微小電圧(約20V)を出力端子に印加するだけで、出力容量が1/100以下に急激に低下する特性を示す。

【0061】

すなわち、主素子1が微細化したスーパージャンクション構造を有する縦型MOSFETの場合には、より低い予備電圧を印加印加するだけで、主素子1の出力静電容量を大幅に低減し、接合容量充電電流に起因するターンオン損失の効果的な低減を可能にする。

【0062】

上記図8乃至図10に主素子1の特性の一例を示したが、耐圧の1/20以下の微小電圧を出力端子に印加する事で、出力容量が1/10以下に低下する特性を有するMOSFETを上述の実施形態の半導体スイッチにおいて主素子1として採用することにより、より効果的に主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0063】

次に、第6実施形態の半導体スイッチについて図面を参照して説明する。

図11は、第6実施形態の半導体スイッチの一構成例を概略的に示す回路図である。図11において、主素子1には、MOSFET(例えば600Vの耐圧)を適用する。主素子1には、逆導通性能を有する寄生ダイオード2Bが内蔵している。また、主素子1には、逆並列に高速ダイオード17を接続している。本実施形態の半導体スイッチは上記の構成以外は上述の第3実施形態と同様である。

【0064】

本実施形態の半導体スイッチにおいて、主電流が逆方向に流れている時にその電流値が大きくなると主素子1のオン抵抗では、十分電圧降下を低く維持できなくなる。この場合、寄生ダイオード2Bへ電流が分流すると、MOSFETの寄生ダイオード2Bにキャリアが蓄積し、逆回復特性が悪化する。この時、予備電圧印加回路5は、MOSFETの寄生ダイオード2Bの蓄積キャリアを排出するために、余分な電力を注入する必要が生じる。

【0065】

本実施形態の半導体スイッチの構成では、主素子1に逆並列接続した高速ダイオード17にも電流が分流するため、MOSFETの寄生ダイオード2Bへの分流電流を軽減でき、逆回復特性の低下を減らす事が可能となり、その結果、予備電圧印加回路5の消費電力も低く抑える事が可能となる。

【0066】

すなわち、本実施形態の半導体スイッチによれば、逆方向主電流が大きくなっても、主素子1であるMOSFETの寄生ダイオード2Bの逆回復に要する余分な電力の注入を減らす事ができる。

【0067】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0068】

次に、第7実施形態の半導体スイッチについて図面を参照して説明する。

図12は、第7実施形態の半導体スイッチの一構成例を概略的に示す回路図である。図12において、主素子1には、MOSFET(例えば600Vの耐圧)を適用する。主素子1には、逆導通性能を有する寄生ダイオード2Bが内蔵している。

【0069】

ゲート駆動アンプ18はゲート制御信号20を受信し、電流増幅してゲート駆動電圧8を出力する。それらの電力は、ゲート駆動電源19から供給する。ゲート駆動電源19は、予備電圧印加回路5の直流電圧源11への電力供給も担う。本実施形態では、予備電圧印加回路5の直流電圧源11としてコンデンサを適用している。ゲート駆動電源19と予備電圧印加回路5との間には抵抗器が挿入され、ゲート駆動電源19の変動を抑制するとともに、ゲート駆動電源19からの電流が流れることを防止している。本実施形態の半導体スイッチは上記の構成以外は上述の第4実施形態と同様である。

【0070】

本実施形態の半導体スイッチにおいて、主素子1及び補助素子3のゲート駆動電力と、小型半導体スイッチであるpチャネル型MOSFET12のゲート駆動電力と、予備電圧印加回路5の直流電圧源11の電力供給とが、全てゲート駆動電源19により統一化され、電源の単一化が得られる。

【0071】

すなわち、本実施形態の半導体スイッチによれば、ゲート駆動電源19と予備電圧印加電源5との共通化が図られ、回路を単純化することができる。

【0072】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0073】

次に、第8実施形態の半導体スイッチについて図面を参照して説明する。

図13は、第8実施形態の半導体スイッチの一構成例を概略的に示す回路図である。図13において、ゲート駆動電源19から、予備電圧印加回路5の直流電圧源11への電力供給の経路に、2個のダイオードと1個のコンデンサを含む昇圧回路21を介している。2個のダイオードは電力供給経路に直列に並んで挿入され、2つのダイオードとゲート駆動アンプ18の出力ラインとの間にコンデンサが接続されている。昇圧回路21は、ゲート駆動電源19から出力された電圧を昇圧して直流電圧源11へ出力する。本実施形態の半導体スイッチは上記の構成以外は上述の第4実施形態と同様である。なお、昇圧回路21のコンデンサとゲート駆動アンプの出力ラインとの間には充電電流の抑制およびアンプ保護のために抵抗が挿入されている。

【0074】

このように構成された本実施形態の半導体スイッチにおいて、例えばゲート駆動電源19が10V〜15Vである場合に、直流電圧源11は昇圧回路21のコンデンサおよびゲート駆動電圧源19により充電されるため約2倍の20V〜25Vとなる。すなわち、本実施形態の半導体スイッチによれば、予備電圧印加回路5の直流電圧源11の電圧を高くすることができるので、出力容量を低減するために十分な電圧が確保できる。

【0075】

すなわち、本実施形態の半導体スイッチによれば、主電流が逆方向に還流している時に半導体スイッチング素子をオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0076】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0077】

次に、上記実施形態の半導体スイッチの主素子1および補助素子3の駆動方法について波形図を用いて説明する。

【0078】

図14は、ゲート駆動アンプ18の出力電圧波形と、主素子1及び補助素子3のゲート電圧波形との一例を示す図である。なお、図14では主素子1および補助素子3がMOSFETの場合について示している。本実施形態において、主素子1のゲート駆動電圧と補助素子3のゲート駆動電圧とは、同一のゲート駆動アンプ18から出力し、主素子1のターンオフの瞬間が補助素子3のターンオフの瞬間よりも遅くなるように制御する制御手段としてのゲート抵抗を挿入している。具体的には、主素子1のターンオフの瞬間が、補助素子3のターンオフの瞬間よりも遅くなるように、両者のゲート抵抗を調節している。すなわち、補助素子3のゲート抵抗は主素子1のゲート抵抗よりも小さくなっている。なお、主素子1のターンオフの瞬間が、補助素子3のターンオフの瞬間よりも遅くなるように制御する制御手段はゲート抵抗に限定されるものではなく、主素子1のゲートとソースとの間にコンデンサを挿入してもよい。制御手段として挿入したコンデンサの容量を調節することにより主素子1がターンオフするタイミングを調節することができる。

【0079】

この結果、図14の波形図に示すように、ゲート駆動アンプ18の出力電圧波形のオフ指令時間からの遅延時間が主素子1の方が補助素子3よりも遅くなるようになっている。このため、主素子1は補助素子3がターンオフした後にターンオフすることとなり、逆方向電流を遮断する際に主素子1の寄生ダイオード2Bへの電流分流を抑制する事ができる。従って、本実施形態の予備電圧印加回路5から、MOSFETの寄生ダイオード2Bの蓄積キャリアを排出するために、注入する余分な電力を抑制する事が可能となる。

【0080】

すなわち、本実施形態の半導体スイッチによれば、主素子1であるMOSFETの寄生ダイオード2Bの逆回復に要する余分な電力の注入を抑制する事ができる。

【0081】

次に、第9実施形態の半導体スイッチについて図面を参照して説明する。

図15は、第9実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチは、補助素子3のドレイン端子とソース端子間に、並列に接続されたコンデンサ22をさらに有している。コンデンサ22は高周波特性が良いものであって、インダクタンス(L)および抵抗(R)が小さいものが好ましい。本実施形態の半導体スイッチは上記の構成以外は上述の第8実施形態と同様である。

【0082】

本実施形態の半導体スイッチにおいて、主電流が逆方向、即ち負極端子7から、正極端子6に向かって流れている時に、転流が完了するまでの瞬間に、補助素子3のドレインとソース間に一時的にサージ電圧が印加される。主素子1と、補助素子3と、高速還流ダイオードを巡る配線インダクタンスが大きくなるに従って、このサージ電圧も増大する。また、主電流の増大に伴ってもサージ電圧が増大する。更に、補助素子3の出力接合容量が小さくてもサージ電圧が大きくなる。また、高速還流ダイオード4の順方向導通性能が回復するまでの遅れ時間によっても、このサージ電圧は増大する。また、補助素子3のゲート抵抗を小さくして、ゲート電圧の低減レートが高速になってもこのサージ電圧は増大する。

【0083】

この様に、主電流が逆方向に流れている時にゲートオフに移行した瞬間に補助素子3の両端間で発生するサージ電圧は、様々な要因から増大する。そこで、本実施形態では、補助素子3の両端にコンデンサ22を付加し、サージ電圧にてコンデンサ22を充電することによりサージ電圧を吸収している。また、この時、コンデンサ22に充電された電圧は、高速還流ダイオード4を通流して転流が完了すると、主素子1に対し、逆方向の電圧を印加する事になり、一瞬オンしそうになった主素子1に内蔵している寄生ダイオード2Bに対し、完全に逆回復させるための電圧を与える事になり、相補的に動作するもう一方の半導体スイッチがオンする前に、主素子1に内蔵している寄生ダイオード2Bの逆回復を確実に完了させる事ができる。

【0084】

すなわち、本実施形態の半導体スイッチによれば、補助素子3に発生するサージ電圧を抑制する事ができ、補助素子3のチップ面積を小さくでき、より安価に構成可能になる。

【0085】

また、本実施形態の半導体スイッチによれば、配線インダクタンスがある程度高くても良くなるため、配線インダクタンスを減す方策(例えば配線本数の増大等)を施す必要がなくなる。これによっても、半導体スイッチを安価に構成可能になる。

【0086】

また、本実施形態の半導体スイッチによれば、補助素子3で生じるサージ電圧の発生を気にしなくても済むため、補助素子3のゲート抵抗を小さくしてゲートオフを高速にでき、デッドタイムを短く出来るため、スイッチング損失も低減できる。その結果として、高速スイッチングが可能な半導体スイッチを提供することができる。

【0087】

また、主素子1であるMOSFETの寄生ダイオード2Bの逆回復に要する余分な電力の注入を抑制する事ができる。

【0088】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0089】

次に、第10実施形態の半導体スイッチについて図面を参照して説明する。

図16は、第10実施形態の半導体スイッチの一構成例を概略的に示す回路図である。図16において、補助素子3のソース端子からドレイン端子に向かって補助ダイオード23を並列接続する。補助ダイオード23は、珪素半導体材料によるショットキーバリアダイオードを適用する。本実施形態の半導体スイッチは上記の構成以外は上述の第9実施形態と同様である。

【0090】

本実施形態の半導体スイッチにおいて、主電流が順方向に流れている際に、主電流が大きくなった場合に、補助素子の導通抵抗だけでは、電圧降下が十分低くならなくても、並列に接続した補助ダイオード23に主電流が分流するため、電圧降下を低く抑える事が出来る。

【0091】

本実施形態の半導体スイッチによれば、主電流が大きくなった場合にも電圧降下を少なく出来、損失を減らすことができる。これにより、主電流として流す事ができる許容最大電流を高くできる。

【0092】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0093】

図17は、一実施形態に係る半導体スイッチを適用して構成された電力変換装置の一例である第1電力変換装置の回路構成を示した回路図である。

【0094】

第1電力変換装置は、図17に示されるように、直流主電源100から伸びる正側直流母線200および負側直流母線300の間に、半導体スイッチを2つ直列接続して構成するブリッジを、2組配置した単相ブリッジ回路である。各ブリッジの正側の半導体スイッチと負側の半導体スイッチとの間の接続点が出力端子a、bである。

【0095】

なお、半導体スイッチには、上記第1実施形態乃至第10実施形態のいずれかの半導体スイッチを採用することが可能であるとともに、各実施形態の構成について種々の省略、置き換え、変更した半導体スイッチを採用することも可能である。図17に示す例では、主素子1および補助素子3にMOSFETを採用したものであって、第9実施形態と同様に補助素子3のドレイン端子とソース端子間に並列に接続されたコンデンサ22をさらに有している。予備電圧印加回路5は、第3実施形態と同様に、直流電圧源11とスイッチ12とを直列接続して構成している。

【0096】

このように構成される第1電力変換装置では、導通電圧が非常に低く、しかも高速スイッチングが可能な半導体スイッチを配置することで、高効率(低損失)で、安価で、高速スイッチングが可能な電力変換装置を実現することができる。

【0097】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0098】

1…主素子、2A…逆導通ダイオード、2B…寄生ダイオード、3…補助素子(逆流防止素子)、4…高速還流ダイオード、4´…ダイオード(第2ダイオード)、5…予備電圧印加回路、6…正極端子、7…負極端子、8…ゲート駆動電圧、9…パルス電圧源、11…直流電圧源、12…スイッチ、13…ゲート電圧レベルシフター、15…絶縁トランス、16…逆流防止ダイオード、17…高速ダイオード、18…ゲート駆動アンプ、19…ゲート駆動電源、21…昇圧回路、22…コンデンサ、23…補助ダイオード。

【技術分野】

【0001】

本発明の実施形態は、半導体スイッチおよび電力変換装置に関する。

【背景技術】

【0002】

従来、主回路のスイッチング素子に還流ダイオードが逆並列接続された構成の電力変換回路においては、還流ダイオードの逆回復電流が流れることで生じる損失の低減する半導体スイッチおよびその半導体スイッチを備えた電力変換装置が望まれている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−193839号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

スイッチング素子に高速還流ダイオードが逆並列接続された半導体スイッチにおいて、主電流が逆方向に流れている時に半導体スイッチをオフした際(主素子と補助素子とをオフした際)、主素子の両端間に残留する電圧は、主素子と補助素子と高速還流ダイオードを結ぶ回路ループのインダクタンス値と、主電流の大きさの積で定まる。回路ループのインダクタンスは、半導体スイッチのスイッチング速度を高速にしたければ、出来るだけ小さく設計する必要があり、このため、主素子に残留する電圧は、数V未満の微小な値になってしまう場合があった。

【0005】

ここで、主素子オフ中の主素子の出力静電容量について、考慮する必要がある。例えば、このような半導体スイッチング素子の特性として、オフ中に印加されている残留電圧が低いと、非常に大きい静電容量を内蔵する特性を有している。これは、出力端子電圧が低いと接合部分の空乏層の厚みが薄いため、非常に大きな静電容量を有するためである。

【0006】

このように大きな静電容量時、直流主回路に2個の半導体スイッチを直列接続したブリッジ回路において、相補的に動作するもう一方の半導体スイッチがターンオンすると、この大きな静電容量に向かって充電電流が流れこむ。回路インピーダンスが非常に小さいため、この充電電流は、短絡的な大電流となり、大きな損失を発生させてしまう可能性があった。

【0007】

本発明の実施形態は、上述した事情を鑑みて成されたものであって、主素子の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する半導体スイッチを提供することを目的とする。

【課題を解決するための手段】

【0008】

実施形態によれば、逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子と、前記主素子に比べ耐圧が低い逆流防止素子と、前記主素子の負極と前記逆流防止素子の負極とを接続して前記主素子の正極を正極端子とし、前記逆流防止素子の正極を負極端子とし、前記正極端子と前記負極端子間に前記負極端子から前記正極端子に向かう方向が順方向となるように接続し、前記主素子と同等の耐圧を有する高速還流ダイオードと、前記主素子の正極に正電圧が印加される方向に接続し、少なくとも前記主素子の耐圧より低い電圧パルスを発生するとともに前記主素子又は前記逆流防止素子がオフする時期と略同期して前記電圧パルスを出力する予備電圧印加回路と、を備えた半導体スイッチが提供される。

【図面の簡単な説明】

【0009】

【図1】図1は、第1実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図2】図2は、第1実施形態の半導体スイッチの他の構成例を概略的に示す図である。

【図3】図3は、第1実施形態の半導体スイッチの他の構成例を概略的に示す図である。

【図4】図4は、第2実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図5】図5は、第3実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図6】図6は、第4実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図7】図7は、第5実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図8】図8は、スーパージャンクション型MOSFETの容量特性の一例を示す図である。

【図9】図9は、スーパージャンクション型MOSFETの出力充電電荷特性の一例を示す図である。

【図10】図10は、微細化スーパージャンクション型MOSFETの容量特性の一例を示す図である。

【図11】図11は、第6実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図12】図12は、第7実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図13】図13は、第8実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図14】図14は、主素子と逆流防止素子とのオン/オフのタイミングの一例を説明するための図である。

【図15】図15は、第9実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図16】図16は、第10実施形態の半導体スイッチの一構成例を概略的に示す図である。

【図17】図17は、一実施形態の電力変換装置の一構成例を概略的に示す図である。

【発明を実施するための形態】

【0010】

以下、実施形態に係る半導体スイッチについて、図面を参照して説明する。

【0011】

図1は、第1実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチは、主素子1と、逆流防止素子としての補助素子3と、高速還流ダイオード4と、予備電圧印加回路5と、を備えている。

【0012】

主素子1は電圧駆動型スイッチング素子であって、例えば600Vの耐圧を有するIGBT(絶縁ゲートバイポーラトランジスタ:Insulated Gate Bipolar Transistor)を適用することができる。このIGBTには、逆導通ダイオード2Aを逆並列接続し、逆導通性能を持たせている。主素子1の耐圧は、好ましくは100V以上、より好ましくは200V以上、さらに好ましくは250V以上の実現可能な電圧である、通常は250V以上の耐圧を有する素子を用いる。

【0013】

補助素子3は電圧駆動型スイッチング素子であって、例えば50Vの耐圧を有するMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)を適用することができる。補助素子3は主素子1よりも低耐圧である。このように、補助素子3に十分低い耐圧のMOSFETを用いる事で、補助素子3の導通抵抗を低くでき、かつ、補助素子3の半導体チップを小さくできる。一般に、MOSFETの導通抵抗は、素子耐圧の2.5乗に比例する事が知られており、補助素子3の素子耐圧を低くする事で、導通抵抗低減(導通損失低減)と、チップ面積低減(コストアップ低減)とを同時に満たす事が出来る。

【0014】

高速還流ダイオード4は、主素子1と同等の例えば600Vの耐圧を有し、主素子1に逆並列接続している逆導通ダイオード2Aに比べ、チップ面積が小さく、順方向の電圧降下は高いけれども、逆回復特性に優れた特性のものを用いる。なお、高速還流ダイオード4は、主素子1と同等あるいは主素子1の耐圧以上の耐圧を有していればよく、同等の耐圧のものに限定されるものではない。また、ダイオードは、一般的に耐圧が高くなる程、逆回復特性が悪化する特性を有する。従って、高速還流ダイオード4は、例えば、逆回復が高速な反面、低耐圧ダイオードを複数個直列に接続して構成しても良い。導通時の電圧降下が増えてしまうが、高速還流ダイオード4には、主電流が負極端子7から正極端子6に向かって流れている時のデッドタイム期間中にしか通流しないので、その通流時間比率は短く、増大する導通損失も僅かなものである。

【0015】

また、高速還流ダイオード4に、珪素より禁制帯の広い半導体材料(例えば、炭化珪素、窒化ガリウム、砒化ガリウム、ダイアモンドなど)からなるダイオードを適用して構成しても良い。珪素より禁制帯の広い半導体のダイオードを用いる事で、より高耐圧で、かつ、逆回復の高速な特性を得る事ができる。また、禁制帯の広い半導体材料は、珪素半導体より高価であるが、高速還流ダイオード4は、デッドタイムの短時間のみ通流するため、小チップ面積で済むのでコストアップを低く抑えることができる。

【0016】

予備電圧印加回路5は、補助素子3と並列で、補助素子3の正極に正電圧が印加される方向に接続される。例えば補助素子3がオフする時期よりも主素子1がオフする時期が遅い場合には、予備電圧印加回路5は、主素子1のゲート駆動信号がオフする時期と同期して、補助素子3の耐圧より低い電圧パルス、例えば、30Vの電圧パルスを出力する。

【0017】

主素子1の負極であるエミッタと補助素子3のソース端子とを接続し、主素子1の正極であるコレクタを正極端子6とし、補助素子3のドレイン端子を負極端子7とし、負極端子7から正極端子6に向かって、主素子1および補助素子3と並列な高速還流ダイオード4を接続する。

【0018】

主素子1と補助素子3とのゲート端子は、それぞれの素子に適当なゲート抵抗を介してそれぞれのゲート端子に共通のゲート駆動電圧8と接続する。ゲート駆動電圧8は、主素子1と補助素子3とのゲート端子に接続されたゲート抵抗を介して印加され、主素子1と補助素子3とは同期してオンおよびオフするように構成されている。

【0019】

このように構成された本実施形態において、主電流が逆方向、即ち負極端子7から正極端子6に向かって流れている時には、主電流は、負極端子7→補助素子3→逆導通ダイオード2A→正極端子6の経路で、通流している。この時、主素子1及び補助素子3がオフすると、補助素子3がオフすることで、主電流は、負極端子7→高速還流ダイオード4→正極端子6の経路に転流する。従って、正極端子6の経路に転流する時期は補助素子3がオフしてから所定の時間が経過した後である。この転流した時点で、予備電圧印加回路5から、30Vのパルスを出力すると、高速還流ダイオード4が導通しているので、30Vのパルス電圧は、主素子1のコレクタ−エミッタ間に印加される。この時、高速還流ダイオード4の順方向電圧降下分(通常1〜2V)は、僅かに電圧が低下する。従って、主素子1の出力端子には、凡そ28〜29Vの電圧が印加される。

【0020】

また、補助素子3の出力にも30Vのパルス電圧は、印加される。この間に、予備電圧印加回路5から出力される電力は、主素子1と補助素子3との出力端子電圧の充電に要する電力のみに限定され、外部主回路に流出しないため、少ない出力電力で済む。

【0021】

高耐圧の主素子の場合、主回路電圧に比べて十分低い電圧を印加するだけで、出力接合容量が急速に低下する特性を示すことが知られている。主素子1には、凡そ28〜29Vの電圧が印加されるため主素子1の出力接合容量は低くなっており、相補的に動作するもう一方の半導体スイッチがターンオンした際の短絡的大電流を抑制できる。

【0022】

一方、主電流が順方向、即ち正極端子6から負極端子7に向かって流れている時には、主素子1及び補助素子3がオフすると、主素子1が電流の遮断を行うので、オフした瞬間に主電圧(通常200〜400V程度)が主素子1の両端間に印加される。この場合には、予備電圧印加回路5から、30Vの電圧パルスを発生しても、主電圧より十分低いので、高速還流ダイオード4が逆阻止しており、予備電圧印加回路5からの主素子1への充電電流は流れない。したがって、予備電圧印加回路5からの電力は、主として補助素子3を充電するために消費され、極僅かなものとなる。

【0023】

上記のように本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0024】

図2は、上記半導体スイッチの変形例を示す回路図である。この例では、主素子1に寄生ダイオード2Bを含むMOSFETを適用し、補助素子(逆流防止素子)3としてダイオードを用いている。補助素子3は、正極端子6から負極端子7へ向かう方向を順方向として主素子1のエミッタと負極端子7との間に接続されている。すなわち、補助素子3がダイオードの場合、そのアノードが主素子1の負極と接続しカソードが負極端子7となる。

【0025】

主素子1にMOSFETを適用する場合、MOSFETには寄生ダイオード2Bが生じてしまうため、負極端子7から正極端子6への逆流を防止するために補助素子3としてダイオードを接続することが効果的である。なお、主素子1にIGBTを適用する場合にも、IGBTに逆導通ダイオード2Aを付加する場合には、同様に逆流防止のために補助素子3としてダイオードを接続すると、同様の効果を得ることができる。

【0026】

図2に示す半導体スイッチは、補助素子3の構成以外は上述の第1実施形態の半導体スイッチと同様の構成である。この変形例の半導体スイッチも上述の第1実施形態の半導体スイッチと同様の効果、すなわち、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0027】

図3は、上記半導体スイッチの他の変形例を示す回路図である。この例では、予備電圧印加回路5は主素子1と並列で、ダイオード(第2ダイオード)4´を介して主素子1の正極に正電圧が印加される方向に接続される。ダイオード4´は、例えば高速還流ダイオード4と同等の高耐圧の高速ダイオードである。なお、ダイオード4´は、主素子1と同等あるいは主素子1の耐圧以上の耐圧を有していればよく、同等の耐圧のものに限定されるものではない。予備電圧印加回路5は、主素子1及び補助素子3がオフしたタイミングで、少なくとも主素子1の耐圧より低い電圧パルスを発生する。

【0028】

図3に示す半導体スイッチは、上記予備電圧印加回路5の構成以外は上述の第1実施形態の半導体スイッチと同様の構成である。この変形例の半導体スイッチも上述の第1実施形態の半導体スイッチと同様の効果、すなわち、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0029】

次に、第2実施形態の半導体スイッチについて図面を参照して説明する。なお、以下の説明において同様の機能を有する構成については同一の符号を付して詳細な説明を省略する。

【0030】

図4は、第2実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチは、第1実施形態の半導体スイッチに対して、主素子1と補助素子3との直列接続の位置関係を入れ替えた構成である。この場合、主素子1と補助素子3とのゲートは、別の電位で駆動する必要があり、フォトカプラ(図示せず)などの絶縁手段で絶縁する必要がある。図4に示す場合では、主素子1のゲートはゲート駆動電圧8Aにより駆動され、補助素子3のゲートはゲート駆動電圧8Bにより駆動される。ゲート駆動電圧8A、8Bは、別々の直流電圧源に接続されたアンプから出力される。

【0031】

なお、補助素子3のゲート駆動電源は、本実施形態の半導体スイッチの高電位側に同種の半導体スイッチがある変換回路の場合には、高電位側の主素子1のゲート駆動電源を利用することができる。上記以外の構成は上述の第1実施形態の半導体スイッチと同様である。

【0032】

本実施形態の半導体スイッチにおいても、主電流が逆方向、即ち負極端子7から正極端子6に向かって流れている時には、主電流は負極端子7→逆導通ダイオード2A→補助素子3→正極端子6の経路で通流している。この時、主素子1及び補助素子3がオフすると、補助素子3がオフすることで、主電流は負極端子7→高速還流ダイオード4→正極端子6の経路に転流する。この転流した時点で、予備電圧印加回路5から30Vのパルスを出力すると、高速還流ダイオード4が導通しているので、30Vのパルス電圧は主素子1のコレクタ−エミッタ間に印加される。この時、高速還流ダイオード4の順方向電圧降下分(通常1〜2V)は、僅かに電圧が低下する。従って、主素子1の出力端子には、凡そ28〜29Vの電圧が印加される。

【0033】

また、補助素子3の出力にも30Vのパルス電圧は印加される。この間に、予備電圧印加回路5から出力される電力は、主素子1と補助素子3の出力端子電圧の充電に要する電力のみに限定され、外部主回路に流出しないため、少ない出力電力で済む。

【0034】

一方、主電流が順方向、即ち正極端子6から、負極端子7に向かって流れている時には、主素子1及び補助素子3がオフすると、主素子1が電流の遮断を行うので、オフした瞬間に主電圧(通常200〜400V程度)が主素子1の両端間に印加される。この場合には、予備電圧印加回路5から、30Vの電圧パルスを発生しても、主電圧より十分低いので、高速還流ダイオード4が逆阻止しており、予備電圧印加回路5からの主素子1への充電電流は流れない。したがって、予備電圧印加回路5からの電力は、主として補助素子3を充電するために、消費され、極僅かなものとなる。

【0035】

上記のように、本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0036】

次に、第3実施形態の半導体スイッチについて図面を参照して説明する。

図5は、第3実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチにおいて、主素子1にはMOSFET(例えば600Vの耐圧)を適用している。主素子1には、逆導通性能を有する寄生ダイオード2Bが内蔵している。また、予備電圧印加回路5は、直流電圧源11とスイッチ12とを直列接続して構成している。スイッチ12は例えば小型半導体スイッチである。本実施形態の半導体スイッチは上記以外の構成は上述の第1実施形態の半導体スイッチと同様である。

【0037】

本実施形態において、主素子1に低抵抗のMOSFETを適用する事で、主素子1の導通抵抗に補助素子3の導通抵抗分が加算される事になるが、補助素子3の耐圧を十分低く選定する事で、第1実施形態の半導体スイッチと同様に、補助素子3の導通抵抗は非常に少なくて済むため、加算された導通抵抗の増加分は極めて僅かで済む。

【0038】

また、主電流が逆方向に流れる際にも、主素子1及び補助素子3がオン状態であれば、主電流は、高速還流ダイオード4を流れず、低抵抗な主素子1と補助素子3との直列回路の方を通流する。

【0039】

この結果、本実施形態の半導体スイッチによれば、主素子1にIGBTを適用した第1実施形態の半導体スイッチに比べて、順方向及び逆方向に通電する際の導通損失を低減する事ができる。

【0040】

上記のように、本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0041】

次に、第4実施形態の半導体スイッチについて図面を参照して説明する。

図6は、第4実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチでは、予備電圧印加回路5は、直流電圧源11とスイッチ12とを直列接続して構成している。スイッチ12は、小型半導体スイッチとしてのpチャネル型MOSFETを適用している。以下本実施形態の説明においてスイッチ12をpチャネル型MOSFET12として説明する。

【0042】

pチャネル型MOSFET12のゲートへは、ゲート電圧レベルシフター13と適当なゲート抵抗を介して共通のゲート駆動電圧8から接続される。ゲート電圧レベルシフター13は、pチャネル型MOSFET12のソース電位が、主素子1のエミッタ電位または、補助素子3のソース電位に対して、直流電圧源11の電圧だけ高いため、この電位差をかさ上げしてゲート電位を合わせる為に必要となる。従って、ゲート電圧レベルシフター13の電位シフト値は、凡そ、直流電圧源11の電圧と等しく、直流電圧源11の電圧に連動して定まる値である。なお、ゲート電圧レベルシフター13は、コンデンサと、そのコンデンサへの充電回路の組合せで構成することも可能である。本実施形態の半導体スイッチは上記以外の構成は上述の第1実施形態の半導体スイッチと同様である。

【0043】

本実施形態の半導体スイッチにおいて、pチャネル型MOSFET12のゲート電位は、そのソース電位より低くなることでオンする。逆に、主素子1及び補助素子3のゲートは、電位が低くなる事でオフする。従って、pチャネル型MOSFET12は、主素子1、及び補助素子3がオフ状態となるとオンするように動作し、主素子1がオフした時期に主素子1に直流電圧源11の電圧を印加させる事ができる。

【0044】

すなわち、本実施形態によれば、上述の第1実施形態の半導体スイッチと同じ効果を、唯一の共通のゲート駆動電圧8から制御する事が可能となり、構成を単純化することができる。

【0045】

上記のように、本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0046】

次に、第5実施形態の半導体スイッチについて図面を参照して説明する。

図7は、第5実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチにおいて、予備電圧印加回路5は、直流電圧源としてパルス電圧源9と、絶縁トランス15を介してパルス電圧源9から電圧が印加される逆流防止ダイオード16とを有している。絶縁トランス15の一次回路にはパルス電圧源9が接続され、二次回路は逆流防止ダイオード16を介して補助素子3と並列接続されている。本実施形態の半導体スイッチは上記以外の構成は上述の第3実施形態の半導体スイッチと同様である。

【0047】

本実施形態の半導体スイッチにおいて、パルス電圧源9は、異なる電位からの電力の供給が可能となり、例えば、共通の制御電源から、変換器を構成する複数の同類の半導体スイッチへの電力の供給ができ、電源の共通化が可能となる。

【0048】

すなわち、本実施形態によれば、上述の第3実施形態の半導体スイッチと同じ効果を奏するとともに、予備電圧印加に要する電力を共通の電源から供給する事が可能となり、別々に電源を設ける必要がなくなる。従って、半導体スイッチの構成を単純化することができる。

【0049】

また、共通の制御回路からのパルス電圧発生が可能となり、よりタイミング精度の高いパルスを発生することが可能となる。従って、本実施形態の半導体スイッチによれば、最適なタイミングで必要最小限のパルス電圧発生でき、消費電力の節約が可能になる。

【0050】

上記のように、本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0051】

次に、上述の第3実施形態および第5実施形態の半導体スイッチの特性の一例について説明する。

【0052】

図8は、スーパージャンクション型MOSFETの容量特性の一例を示す図である。

図8は、主素子1に適用可能である600V耐圧のスーパージャンクション構造を有する縦型MOSFETの容量特性例を示している。図8において、横軸は、主素子1の出力端子電圧であるドレイン−ソース間電圧(Vds)を表しており、縦軸が静電容量値を示している。

【0053】

出力容量(Coss)の特性に注目すると、出力端子電圧が非常に低い0V近傍では、高い値を示しているが、出力端子電圧の上昇に伴って急速に低減する特性を示している。例えば、出力端子電圧が50Vまで上昇すれば、出力容量は凡そ1/40まで低減する。これは、印加電圧が低い場合には、空乏層が、まだ、薄いために、スーパージャンクション構造による折り畳まれた広い面積を持ってしまうために、大きな静電容量値を示しているけれども、印加電圧がある程度以上加わって、空乏層が厚くなると、スーパージャンクション構造由来の折り畳まれた面ではなく、平坦化された絶縁面となるため、大幅に面積の低下が生じる事によりもたらされる。

【0054】

図9は、このような出力容量特性を出力電圧の上昇に伴って主素子1に充電されていく電荷特性(Qoss)として表した図である。図9においても、横軸は、主素子1の出力端子電圧であるドレイン−ソース間電圧(Vds)を表しており、図8の容量特性を横軸のVdsで、積分して求めた特性である。

【0055】

もし、出力容量がVdsに因らずに一定の静電容量値を示す特性であれば、図9の特性は、原点から数直線的に上昇する特性を示す筈であるが、図9を見ると、ドレイン−ソース間電圧(Vds)が低い領域で急速な上昇を示し、50Vにて、凡そ0.63[μC]まで上昇し、主回路電圧を280Vの変換器での適用を想定すると、90%の電荷注入が完了している。

【0056】

すなわち、主素子1がスーパージャンクション構造を有する縦型MOSFETの場合には、低い電圧を印加するだけで、出力静電容量の大幅な低下が実現できる。

【0057】

したがって、この場合、主素子1の出力静電容量を大幅に低減し、接合容量充電電流に起因するターンオン損失の効果的な低減を可能にする。

【0058】

次に、上述の第3実施形態および第5実施形態の半導体スイッチの他の特性例について説明する。

【0059】

図10は、微細化したスーパージャンクション構造を有する縦型MOSFETの容量特性例を示している。図10において、横軸は、主素子1の出力端子電圧であるドレイン−ソース間電圧(Vds)を表しており、縦軸が静電容量値(対数メモリ)を示している。

【0060】

図10において、図8に示した一般的なスーパージャンクションMOSFETの出力容量特性と比較すると、ドレイン−ソース間電圧(Vds)がより低い電圧値にて、急低下する特性が見られる。このような特性は、スーパージャンクション構造のアスペクト比が高い場合に見られ、主素子1の耐圧600Vの1/30程度の微小電圧(約20V)を出力端子に印加するだけで、出力容量が1/100以下に急激に低下する特性を示す。

【0061】

すなわち、主素子1が微細化したスーパージャンクション構造を有する縦型MOSFETの場合には、より低い予備電圧を印加印加するだけで、主素子1の出力静電容量を大幅に低減し、接合容量充電電流に起因するターンオン損失の効果的な低減を可能にする。

【0062】

上記図8乃至図10に主素子1の特性の一例を示したが、耐圧の1/20以下の微小電圧を出力端子に印加する事で、出力容量が1/10以下に低下する特性を有するMOSFETを上述の実施形態の半導体スイッチにおいて主素子1として採用することにより、より効果的に主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0063】

次に、第6実施形態の半導体スイッチについて図面を参照して説明する。

図11は、第6実施形態の半導体スイッチの一構成例を概略的に示す回路図である。図11において、主素子1には、MOSFET(例えば600Vの耐圧)を適用する。主素子1には、逆導通性能を有する寄生ダイオード2Bが内蔵している。また、主素子1には、逆並列に高速ダイオード17を接続している。本実施形態の半導体スイッチは上記の構成以外は上述の第3実施形態と同様である。

【0064】

本実施形態の半導体スイッチにおいて、主電流が逆方向に流れている時にその電流値が大きくなると主素子1のオン抵抗では、十分電圧降下を低く維持できなくなる。この場合、寄生ダイオード2Bへ電流が分流すると、MOSFETの寄生ダイオード2Bにキャリアが蓄積し、逆回復特性が悪化する。この時、予備電圧印加回路5は、MOSFETの寄生ダイオード2Bの蓄積キャリアを排出するために、余分な電力を注入する必要が生じる。

【0065】

本実施形態の半導体スイッチの構成では、主素子1に逆並列接続した高速ダイオード17にも電流が分流するため、MOSFETの寄生ダイオード2Bへの分流電流を軽減でき、逆回復特性の低下を減らす事が可能となり、その結果、予備電圧印加回路5の消費電力も低く抑える事が可能となる。

【0066】

すなわち、本実施形態の半導体スイッチによれば、逆方向主電流が大きくなっても、主素子1であるMOSFETの寄生ダイオード2Bの逆回復に要する余分な電力の注入を減らす事ができる。

【0067】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0068】

次に、第7実施形態の半導体スイッチについて図面を参照して説明する。

図12は、第7実施形態の半導体スイッチの一構成例を概略的に示す回路図である。図12において、主素子1には、MOSFET(例えば600Vの耐圧)を適用する。主素子1には、逆導通性能を有する寄生ダイオード2Bが内蔵している。

【0069】

ゲート駆動アンプ18はゲート制御信号20を受信し、電流増幅してゲート駆動電圧8を出力する。それらの電力は、ゲート駆動電源19から供給する。ゲート駆動電源19は、予備電圧印加回路5の直流電圧源11への電力供給も担う。本実施形態では、予備電圧印加回路5の直流電圧源11としてコンデンサを適用している。ゲート駆動電源19と予備電圧印加回路5との間には抵抗器が挿入され、ゲート駆動電源19の変動を抑制するとともに、ゲート駆動電源19からの電流が流れることを防止している。本実施形態の半導体スイッチは上記の構成以外は上述の第4実施形態と同様である。

【0070】

本実施形態の半導体スイッチにおいて、主素子1及び補助素子3のゲート駆動電力と、小型半導体スイッチであるpチャネル型MOSFET12のゲート駆動電力と、予備電圧印加回路5の直流電圧源11の電力供給とが、全てゲート駆動電源19により統一化され、電源の単一化が得られる。

【0071】

すなわち、本実施形態の半導体スイッチによれば、ゲート駆動電源19と予備電圧印加電源5との共通化が図られ、回路を単純化することができる。

【0072】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0073】

次に、第8実施形態の半導体スイッチについて図面を参照して説明する。

図13は、第8実施形態の半導体スイッチの一構成例を概略的に示す回路図である。図13において、ゲート駆動電源19から、予備電圧印加回路5の直流電圧源11への電力供給の経路に、2個のダイオードと1個のコンデンサを含む昇圧回路21を介している。2個のダイオードは電力供給経路に直列に並んで挿入され、2つのダイオードとゲート駆動アンプ18の出力ラインとの間にコンデンサが接続されている。昇圧回路21は、ゲート駆動電源19から出力された電圧を昇圧して直流電圧源11へ出力する。本実施形態の半導体スイッチは上記の構成以外は上述の第4実施形態と同様である。なお、昇圧回路21のコンデンサとゲート駆動アンプの出力ラインとの間には充電電流の抑制およびアンプ保護のために抵抗が挿入されている。

【0074】

このように構成された本実施形態の半導体スイッチにおいて、例えばゲート駆動電源19が10V〜15Vである場合に、直流電圧源11は昇圧回路21のコンデンサおよびゲート駆動電圧源19により充電されるため約2倍の20V〜25Vとなる。すなわち、本実施形態の半導体スイッチによれば、予備電圧印加回路5の直流電圧源11の電圧を高くすることができるので、出力容量を低減するために十分な電圧が確保できる。

【0075】

すなわち、本実施形態の半導体スイッチによれば、主電流が逆方向に還流している時に半導体スイッチング素子をオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0076】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0077】

次に、上記実施形態の半導体スイッチの主素子1および補助素子3の駆動方法について波形図を用いて説明する。

【0078】

図14は、ゲート駆動アンプ18の出力電圧波形と、主素子1及び補助素子3のゲート電圧波形との一例を示す図である。なお、図14では主素子1および補助素子3がMOSFETの場合について示している。本実施形態において、主素子1のゲート駆動電圧と補助素子3のゲート駆動電圧とは、同一のゲート駆動アンプ18から出力し、主素子1のターンオフの瞬間が補助素子3のターンオフの瞬間よりも遅くなるように制御する制御手段としてのゲート抵抗を挿入している。具体的には、主素子1のターンオフの瞬間が、補助素子3のターンオフの瞬間よりも遅くなるように、両者のゲート抵抗を調節している。すなわち、補助素子3のゲート抵抗は主素子1のゲート抵抗よりも小さくなっている。なお、主素子1のターンオフの瞬間が、補助素子3のターンオフの瞬間よりも遅くなるように制御する制御手段はゲート抵抗に限定されるものではなく、主素子1のゲートとソースとの間にコンデンサを挿入してもよい。制御手段として挿入したコンデンサの容量を調節することにより主素子1がターンオフするタイミングを調節することができる。

【0079】

この結果、図14の波形図に示すように、ゲート駆動アンプ18の出力電圧波形のオフ指令時間からの遅延時間が主素子1の方が補助素子3よりも遅くなるようになっている。このため、主素子1は補助素子3がターンオフした後にターンオフすることとなり、逆方向電流を遮断する際に主素子1の寄生ダイオード2Bへの電流分流を抑制する事ができる。従って、本実施形態の予備電圧印加回路5から、MOSFETの寄生ダイオード2Bの蓄積キャリアを排出するために、注入する余分な電力を抑制する事が可能となる。

【0080】

すなわち、本実施形態の半導体スイッチによれば、主素子1であるMOSFETの寄生ダイオード2Bの逆回復に要する余分な電力の注入を抑制する事ができる。

【0081】

次に、第9実施形態の半導体スイッチについて図面を参照して説明する。

図15は、第9実施形態の半導体スイッチの一構成例を概略的に示す回路図である。本実施形態の半導体スイッチは、補助素子3のドレイン端子とソース端子間に、並列に接続されたコンデンサ22をさらに有している。コンデンサ22は高周波特性が良いものであって、インダクタンス(L)および抵抗(R)が小さいものが好ましい。本実施形態の半導体スイッチは上記の構成以外は上述の第8実施形態と同様である。

【0082】

本実施形態の半導体スイッチにおいて、主電流が逆方向、即ち負極端子7から、正極端子6に向かって流れている時に、転流が完了するまでの瞬間に、補助素子3のドレインとソース間に一時的にサージ電圧が印加される。主素子1と、補助素子3と、高速還流ダイオードを巡る配線インダクタンスが大きくなるに従って、このサージ電圧も増大する。また、主電流の増大に伴ってもサージ電圧が増大する。更に、補助素子3の出力接合容量が小さくてもサージ電圧が大きくなる。また、高速還流ダイオード4の順方向導通性能が回復するまでの遅れ時間によっても、このサージ電圧は増大する。また、補助素子3のゲート抵抗を小さくして、ゲート電圧の低減レートが高速になってもこのサージ電圧は増大する。

【0083】

この様に、主電流が逆方向に流れている時にゲートオフに移行した瞬間に補助素子3の両端間で発生するサージ電圧は、様々な要因から増大する。そこで、本実施形態では、補助素子3の両端にコンデンサ22を付加し、サージ電圧にてコンデンサ22を充電することによりサージ電圧を吸収している。また、この時、コンデンサ22に充電された電圧は、高速還流ダイオード4を通流して転流が完了すると、主素子1に対し、逆方向の電圧を印加する事になり、一瞬オンしそうになった主素子1に内蔵している寄生ダイオード2Bに対し、完全に逆回復させるための電圧を与える事になり、相補的に動作するもう一方の半導体スイッチがオンする前に、主素子1に内蔵している寄生ダイオード2Bの逆回復を確実に完了させる事ができる。

【0084】

すなわち、本実施形態の半導体スイッチによれば、補助素子3に発生するサージ電圧を抑制する事ができ、補助素子3のチップ面積を小さくでき、より安価に構成可能になる。

【0085】

また、本実施形態の半導体スイッチによれば、配線インダクタンスがある程度高くても良くなるため、配線インダクタンスを減す方策(例えば配線本数の増大等)を施す必要がなくなる。これによっても、半導体スイッチを安価に構成可能になる。

【0086】

また、本実施形態の半導体スイッチによれば、補助素子3で生じるサージ電圧の発生を気にしなくても済むため、補助素子3のゲート抵抗を小さくしてゲートオフを高速にでき、デッドタイムを短く出来るため、スイッチング損失も低減できる。その結果として、高速スイッチングが可能な半導体スイッチを提供することができる。

【0087】

また、主素子1であるMOSFETの寄生ダイオード2Bの逆回復に要する余分な電力の注入を抑制する事ができる。

【0088】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0089】

次に、第10実施形態の半導体スイッチについて図面を参照して説明する。

図16は、第10実施形態の半導体スイッチの一構成例を概略的に示す回路図である。図16において、補助素子3のソース端子からドレイン端子に向かって補助ダイオード23を並列接続する。補助ダイオード23は、珪素半導体材料によるショットキーバリアダイオードを適用する。本実施形態の半導体スイッチは上記の構成以外は上述の第9実施形態と同様である。

【0090】

本実施形態の半導体スイッチにおいて、主電流が順方向に流れている際に、主電流が大きくなった場合に、補助素子の導通抵抗だけでは、電圧降下が十分低くならなくても、並列に接続した補助ダイオード23に主電流が分流するため、電圧降下を低く抑える事が出来る。

【0091】

本実施形態の半導体スイッチによれば、主電流が大きくなった場合にも電圧降下を少なく出来、損失を減らすことができる。これにより、主電流として流す事ができる許容最大電流を高くできる。

【0092】

本実施形態によれば、主電流が逆方向に還流している時に半導体スイッチをオフした際、主素子1の両端間に残留する電圧を所定値以上に確保することにより、主素子1の出力静電容量の増大を防止し、接合容量充電電流に起因するターンオン損失を抑制する事ができる。

【0093】

図17は、一実施形態に係る半導体スイッチを適用して構成された電力変換装置の一例である第1電力変換装置の回路構成を示した回路図である。

【0094】

第1電力変換装置は、図17に示されるように、直流主電源100から伸びる正側直流母線200および負側直流母線300の間に、半導体スイッチを2つ直列接続して構成するブリッジを、2組配置した単相ブリッジ回路である。各ブリッジの正側の半導体スイッチと負側の半導体スイッチとの間の接続点が出力端子a、bである。

【0095】

なお、半導体スイッチには、上記第1実施形態乃至第10実施形態のいずれかの半導体スイッチを採用することが可能であるとともに、各実施形態の構成について種々の省略、置き換え、変更した半導体スイッチを採用することも可能である。図17に示す例では、主素子1および補助素子3にMOSFETを採用したものであって、第9実施形態と同様に補助素子3のドレイン端子とソース端子間に並列に接続されたコンデンサ22をさらに有している。予備電圧印加回路5は、第3実施形態と同様に、直流電圧源11とスイッチ12とを直列接続して構成している。

【0096】

このように構成される第1電力変換装置では、導通電圧が非常に低く、しかも高速スイッチングが可能な半導体スイッチを配置することで、高効率(低損失)で、安価で、高速スイッチングが可能な電力変換装置を実現することができる。

【0097】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0098】

1…主素子、2A…逆導通ダイオード、2B…寄生ダイオード、3…補助素子(逆流防止素子)、4…高速還流ダイオード、4´…ダイオード(第2ダイオード)、5…予備電圧印加回路、6…正極端子、7…負極端子、8…ゲート駆動電圧、9…パルス電圧源、11…直流電圧源、12…スイッチ、13…ゲート電圧レベルシフター、15…絶縁トランス、16…逆流防止ダイオード、17…高速ダイオード、18…ゲート駆動アンプ、19…ゲート駆動電源、21…昇圧回路、22…コンデンサ、23…補助ダイオード。

【特許請求の範囲】

【請求項1】

逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子と、

前記主素子に比べ耐圧が低い逆流防止素子と、

前記主素子の負極と前記逆流防止素子の負極とを接続して前記主素子の正極を正極端子とし、前記逆流防止素子の正極を負極端子とし、前記正極端子と前記負極端子間に前記負極端子から前記正極端子に向かう方向が順方向となるように接続し、前記主素子と同等の耐圧を有する高速還流ダイオードと、

前記主素子の正極に正電圧が印加される方向に接続し、少なくとも前記主素子の耐圧より低い電圧パルスを発生するとともに前記主素子がオフする時期と略同期して前記電圧パルスを出力する予備電圧印加回路と、を備えた半導体スイッチ。

【請求項2】

前記逆流防止素子は、前記主素子と略同期してオンおよびオフする電圧駆動型スイッチング素子である請求項1記載の半導体スイッチ。

【請求項3】

前記逆流防止素子はダイオードである請求項1記載の半導体スイッチ。

【請求項4】

前記予備電圧印加回路は、前記逆流防止素子と並列で、前記逆流防止素子の正極および前記高速還流ダイオードを介して前記主素子の正極に正電圧が印加される方向に接続し、前記逆流防止素子の耐圧より低い電圧パルスを発生する請求項1記載の半導体スイッチ。

【請求項5】

前記予備電圧印加回路は、前記主素子と並列に接続され、

前記予備電圧印加回路から前記主素子の正極へ向かう方向が順方向となるように接続され、前記主素子と同等の耐圧を有する第2ダイオードをさらに備える請求項1記載の半導体スイッチ。

【請求項6】

逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子と、

前記主素子に比べ耐圧が低い電圧駆動型スイッチング素子であって、前記主素子と略同一時期にオンおよびオフする逆流防止素子と、

前記主素子と同等の耐圧を有し、前記主素子の正極と前記逆流防止素子の正極とを接続して前記逆流防止素子の負極を正極端子とし、前記主素子の負極を負極端子とし、前記正極端子と前記負極端子間に前記負極端子から前記正極端子に向かう方向が順方向となるように並列接続し、前記主素子と同等の耐圧を有する高速還流ダイオードと、

前記逆流防止素子と並列で、前記逆流防止素子の正極に正電圧が印加される方向に接続され、前記逆流防止素子の耐圧より低い電圧パルスを発生するとともに、前記主素子又は前記逆流防止素子のゲート駆動信号がオフする時期と略同期して前記電圧パルスを出力する半導体スイッチ。

【請求項7】

前記主素子は、MOSFETである請求項1乃至請求項6のいずれか1項記載の半導体スイッチ。

【請求項8】

前記予備電圧印加回路は、直流電圧源と、前記直流電圧源と直列に接続された半導体スイッチとを備える請求項1乃至請求項7のいずれか1項記載の半導体スイッチ。

【請求項9】

前記小型半導体スイッチは、pチャネル型MOSFETである請求項8記載の半導体スイッチ。

【請求項10】

前記予備電圧印加回路は、直流電圧源と、前記直流電圧源が一次回路に接続された絶縁トランスと、前記絶縁トランスの二次回路に接続された逆流防止ダイオードと、を備えている請求項1乃至請求項7のいずれか1項記載の半導体スイッチ。

【請求項11】

前記主素子は、スーパージャンクション構造を有する縦型MOSFETである請求項7記載の半導体スイッチ。

【請求項12】

前記主素子は、出力端子に電圧が印加されていない時に比べ、前記主素子の耐圧の1/20以下の電圧を出力端子に印加する事で、出力容量が1/10以下に低下する特性を有する請求項1乃至請求項11記載の半導体スイッチ。

【請求項13】

前記主素子の正極および負極の両端に、前記主素子の負極から正極に向かう方向を順方向とする高速ダイオードを並列接続して構成される事を特徴とする請求項1乃至請求項12記載の半導体スイッチ。

【請求項14】

前記逆流防止素子は電圧駆動型スイッチング素子であって、

前記予備電圧印加回路の前記直流電圧源は、前記主素子又は前記逆流防止素子のゲート駆動用電源から供給される請求項8乃至請求項10記載の半導体スイッチ。

【請求項15】

前記主素子又は前記逆流防止素子のゲート駆動用電源から、前記予備電圧印加回路の前記直流電圧源への電力供給の経路に配置された昇圧回路をさらに備える請求項14記載の半導体スイッチ。

【請求項16】

前記主素子のゲート駆動電圧と前記逆流防止素子のゲート駆動電圧とは、同一駆動回路から出力し、

前記主素子のゲートと前記逆流防止素子のゲートには前記主素子のターンオフの瞬間が前記逆流防止素子のターンオフの瞬間よりも遅くなるように制御する制御手段をさらに備える請求項1又は請求項6記載の半導体スイッチ。

【請求項17】

前記逆流防止素子の正極および負極の両端間に並列接続されたコンデンサをさらに備える請求項1乃至請求項16のいずれか1項記載の半導体スイッチ。

【請求項18】

前記逆流防止素子の正極および負極の両端に、前記逆流防止素子の負極から正極に向かう方向を順方向とするように並列接続されたダイオードをさらに備える請求項1乃至請求項16のいずれか1項記載の半導体スイッチ。

【請求項19】

直流主電源に2個のスイッチング素子を直列接続して構成されるブリッジ回路を1組又は、複数組を有する電力変換回路であって、

前記電力変換回路に適用する前記スイッチング素子のうち、少なくとも1個は、請求項1乃至請求項18のいずれか1項記載の半導体スイッチであることを特徴とする電力変換装置。

【請求項1】

逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子と、

前記主素子に比べ耐圧が低い逆流防止素子と、

前記主素子の負極と前記逆流防止素子の負極とを接続して前記主素子の正極を正極端子とし、前記逆流防止素子の正極を負極端子とし、前記正極端子と前記負極端子間に前記負極端子から前記正極端子に向かう方向が順方向となるように接続し、前記主素子と同等の耐圧を有する高速還流ダイオードと、

前記主素子の正極に正電圧が印加される方向に接続し、少なくとも前記主素子の耐圧より低い電圧パルスを発生するとともに前記主素子がオフする時期と略同期して前記電圧パルスを出力する予備電圧印加回路と、を備えた半導体スイッチ。

【請求項2】

前記逆流防止素子は、前記主素子と略同期してオンおよびオフする電圧駆動型スイッチング素子である請求項1記載の半導体スイッチ。

【請求項3】

前記逆流防止素子はダイオードである請求項1記載の半導体スイッチ。

【請求項4】

前記予備電圧印加回路は、前記逆流防止素子と並列で、前記逆流防止素子の正極および前記高速還流ダイオードを介して前記主素子の正極に正電圧が印加される方向に接続し、前記逆流防止素子の耐圧より低い電圧パルスを発生する請求項1記載の半導体スイッチ。

【請求項5】

前記予備電圧印加回路は、前記主素子と並列に接続され、

前記予備電圧印加回路から前記主素子の正極へ向かう方向が順方向となるように接続され、前記主素子と同等の耐圧を有する第2ダイオードをさらに備える請求項1記載の半導体スイッチ。

【請求項6】

逆導通性能を有し、高耐圧な電圧駆動型スイッチング素子である主素子と、

前記主素子に比べ耐圧が低い電圧駆動型スイッチング素子であって、前記主素子と略同一時期にオンおよびオフする逆流防止素子と、

前記主素子と同等の耐圧を有し、前記主素子の正極と前記逆流防止素子の正極とを接続して前記逆流防止素子の負極を正極端子とし、前記主素子の負極を負極端子とし、前記正極端子と前記負極端子間に前記負極端子から前記正極端子に向かう方向が順方向となるように並列接続し、前記主素子と同等の耐圧を有する高速還流ダイオードと、

前記逆流防止素子と並列で、前記逆流防止素子の正極に正電圧が印加される方向に接続され、前記逆流防止素子の耐圧より低い電圧パルスを発生するとともに、前記主素子又は前記逆流防止素子のゲート駆動信号がオフする時期と略同期して前記電圧パルスを出力する半導体スイッチ。

【請求項7】

前記主素子は、MOSFETである請求項1乃至請求項6のいずれか1項記載の半導体スイッチ。

【請求項8】

前記予備電圧印加回路は、直流電圧源と、前記直流電圧源と直列に接続された半導体スイッチとを備える請求項1乃至請求項7のいずれか1項記載の半導体スイッチ。

【請求項9】

前記小型半導体スイッチは、pチャネル型MOSFETである請求項8記載の半導体スイッチ。

【請求項10】

前記予備電圧印加回路は、直流電圧源と、前記直流電圧源が一次回路に接続された絶縁トランスと、前記絶縁トランスの二次回路に接続された逆流防止ダイオードと、を備えている請求項1乃至請求項7のいずれか1項記載の半導体スイッチ。

【請求項11】

前記主素子は、スーパージャンクション構造を有する縦型MOSFETである請求項7記載の半導体スイッチ。

【請求項12】

前記主素子は、出力端子に電圧が印加されていない時に比べ、前記主素子の耐圧の1/20以下の電圧を出力端子に印加する事で、出力容量が1/10以下に低下する特性を有する請求項1乃至請求項11記載の半導体スイッチ。

【請求項13】

前記主素子の正極および負極の両端に、前記主素子の負極から正極に向かう方向を順方向とする高速ダイオードを並列接続して構成される事を特徴とする請求項1乃至請求項12記載の半導体スイッチ。

【請求項14】

前記逆流防止素子は電圧駆動型スイッチング素子であって、

前記予備電圧印加回路の前記直流電圧源は、前記主素子又は前記逆流防止素子のゲート駆動用電源から供給される請求項8乃至請求項10記載の半導体スイッチ。

【請求項15】

前記主素子又は前記逆流防止素子のゲート駆動用電源から、前記予備電圧印加回路の前記直流電圧源への電力供給の経路に配置された昇圧回路をさらに備える請求項14記載の半導体スイッチ。

【請求項16】

前記主素子のゲート駆動電圧と前記逆流防止素子のゲート駆動電圧とは、同一駆動回路から出力し、

前記主素子のゲートと前記逆流防止素子のゲートには前記主素子のターンオフの瞬間が前記逆流防止素子のターンオフの瞬間よりも遅くなるように制御する制御手段をさらに備える請求項1又は請求項6記載の半導体スイッチ。

【請求項17】

前記逆流防止素子の正極および負極の両端間に並列接続されたコンデンサをさらに備える請求項1乃至請求項16のいずれか1項記載の半導体スイッチ。

【請求項18】

前記逆流防止素子の正極および負極の両端に、前記逆流防止素子の負極から正極に向かう方向を順方向とするように並列接続されたダイオードをさらに備える請求項1乃至請求項16のいずれか1項記載の半導体スイッチ。

【請求項19】

直流主電源に2個のスイッチング素子を直列接続して構成されるブリッジ回路を1組又は、複数組を有する電力変換回路であって、

前記電力変換回路に適用する前記スイッチング素子のうち、少なくとも1個は、請求項1乃至請求項18のいずれか1項記載の半導体スイッチであることを特徴とする電力変換装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−115933(P2013−115933A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−260321(P2011−260321)

【出願日】平成23年11月29日(2011.11.29)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月29日(2011.11.29)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]