半導体スイッチング回路、及びそれを用いた半導体モジュール並びに電力変換モジュール

【課題】低ゲート消費電力で、高速かつ確実にスイッチング素子をオンオフさせる半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールを提供する。

【解決手段】スイッチング素子1,11を有するスイッチング回路20,21において、容量4,14と抵抗5,15との容量抵抗並列接続回路3,13と、ダイオード直列接続回路7,17とこのダイオードと逆方向に並列に接続されたダイオード8,18とを有するダイオード直列並列接続回路6,16とを有し、スイッチング素子1,11のゲート端子には容量抵抗並列接続回路3,13の一端が接続され、この他端とゲート駆動用回路9の出力端子との間には、ダイオード直列接続回路7,17のダイオードのアノード端子をゲート駆動用回路9側、このカソード端子をスイッチング素子1,11のゲート端子側にして、ダイオード直列並列接続回路6,16が接続されている。

【解決手段】スイッチング素子1,11を有するスイッチング回路20,21において、容量4,14と抵抗5,15との容量抵抗並列接続回路3,13と、ダイオード直列接続回路7,17とこのダイオードと逆方向に並列に接続されたダイオード8,18とを有するダイオード直列並列接続回路6,16とを有し、スイッチング素子1,11のゲート端子には容量抵抗並列接続回路3,13の一端が接続され、この他端とゲート駆動用回路9の出力端子との間には、ダイオード直列接続回路7,17のダイオードのアノード端子をゲート駆動用回路9側、このカソード端子をスイッチング素子1,11のゲート端子側にして、ダイオード直列並列接続回路6,16が接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体スイッチング素子を有する半導体スイッチング回路の技術に関し、特に、この半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールに適用して有効な技術に関する。

【背景技術】

【0002】

半導体スイッチング回路を用いた電力変換モジュールの一例であるインバータ回路に関する技術としては、例えば特開平10−191650号公報(特許文献1)に記載される技術などが挙げられる。この特許文献1には、直流電源の正負端子間に直列に接続され、交互にオン−オフする2つのトランジスタを有するインバータ回路において、この2つのトランジスタにバイポーラトランジスタを使ったハーフブリッジ回路の技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平10−191650号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、現在、直流−交流電力変換回路(インバータ)、交流−直流電力変換回路(コンバータ)や力率改善回路などのパワーエレクトロニクスに使われるスイッチング素子には、シリコンデバイスであるMOS(Metal Oxide Semiconductor)トランジスタ、IGBT(Insulated Gate Bipolar Transistor)が広く使われている。パワーエレクトロニクスにおいては、ゲート駆動回路が故障などの不具合により駆動電圧が出力されない時に、貫通電流によるスイッチング素子、しいてはシステムの故障を防ぐために、閾値電圧が0Vより大きいノーマリオフ特性を持つことが望まれる。

【0005】

シリコン系MOSトランジスタ、IGBTは、通常、5V以上の閾値電圧を持つ。また、スイッチング動作時の導通損失を最小にするため、オン電圧は8V〜15Vであることが多い。よって、現在、市販されているゲート駆動用回路の出力電圧も8V〜15Vのものが多い。一方、接合型トランジスタは、MOSトランジスタやIGBTと比べて低オン抵抗を得やすいが、ゲート−ソース間にダイオードが形成されるため、オン電圧が約1V〜3Vと低い。

【0006】

最近では、SiC(Silicon-Carbide)やGaN(Gallium-Nitride)などのワイドバンドギャップ半導体を使ったスイッチング素子は、シリコンデバイスと比較して高温動作、低オン抵抗、高耐圧を同時達成することができるため、次世代デバイスとして注目を浴びている。しかし、これらのデバイス構造は接合型である場合が多く、オン電圧は約1V〜6Vと低い。市販されているゲート駆動用ICは、出力電圧が高すぎるため、そのままでは利用できない課題を有する。この課題に対して、例えば、ゲート駆動用ICの出力電圧を電圧レギュレータで電圧レベルを変換することは可能ではあるが、電圧レギュレータ用の別電源が必要である。

【0007】

また、前述した特許文献1の図6の回路においては、トランジスタQ14のベースに接続するツェナーダイオードZD12と、トランジスタQ15のベースに接続するツェナーダイオードZD13の向きを逆にすることで、疑似的にオン電圧を変えてトランジスタQ14,Q15が同じタイミングでオン状態になることを防いでいる。ツェナーダイオードZD12とZD13に流れる逆方向電流でトランジスタQ14,Q15を駆動している。ツェナーダイオードの逆方向電流は数μA〜数mA程度と小さいので、駆動できるトランジスタサイズに制限がある。

【0008】

トランジスタQ14,Q15が電界効果型トランジスタの場合、この回路は主回路電圧EをツェナーダイオードZD13で下げる効果があるが、ツェナーダイオードは降伏電圧が大きいため、トランジスタQ15を電圧駆動する場合、ツェナーダイオード1つで最適なオン電圧を与えるのは難しく、抵抗R23に過剰な電圧がかかり消費電力が増える。また、容量C12,C13は突入電流により、トランジスタQ14,Q15の入力容量の充放電を高速にする効果を持つが、ツェナーダイオードZD12,ZD13により電流上限値が制限されるため、高速化を律即している。

【0009】

そこで、本発明は前述した特許文献1を含む従来技術の課題に鑑みてなされたものであり、その代表的な目的は、低ゲート消費電力で、高速かつ確実にスイッチング素子をオンオフさせる半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールを提供することにある。

【0010】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0012】

すなわち、代表的なものの概要は、ドレイン端子、ソース端子、及びゲート端子を有する半導体スイッチング素子を有し、前記半導体スイッチング素子のゲート端子とソース端子との間に、前記半導体スイッチング素子のゲート端子とソース端子との間に印加された電圧または電流によってドレイン端子とソース端子との間の導通及び非導通を制御するゲート駆動回路が接続される半導体スイッチング回路であって、以下のような特徴を有するものである。

【0013】

(1)前記半導体スイッチング回路は、容量素子と抵抗素子とが並列に接続された第1回路と、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路と、前記ダイオード直列接続回路のダイオードと逆方向に、前記ダイオード直列接続回路に並列に接続されたダイオードとを有する第2回路とを有する。そして、前記半導体スイッチング素子のゲート端子には前記第1回路の一端が接続され、前記第1回路の他端と前記ゲート駆動回路の出力端子との間には、前記ダイオード直列接続回路の1つ以上のダイオードのアノード端子を前記ゲート駆動回路側、前記ダイオード直列接続回路の1つ以上のダイオードのカソード端子を前記半導体スイッチング素子のゲート端子側にして、前記第2回路が接続されていることを特徴とする。さらに好適には、前記半導体スイッチング素子は、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタであることを特徴とする。

【0014】

(2)上記(1)の構成に加え、前記第2回路は、前記ダイオード直列接続回路と並列に接続された容量素子をさらに有することを特徴とする。

【0015】

(3)上記(1)または上記(2)の半導体スイッチング回路を用いた半導体モジュール、前記半導体スイッチング回路を用いた電力変換モジュールにも、本発明は適用するものである。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

すなわち、代表的なものによって得られる効果は、低ゲート消費電力で、高速にスイッチング素子をオンオフさせる半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールが実現可能になる。

【図面の簡単な説明】

【0018】

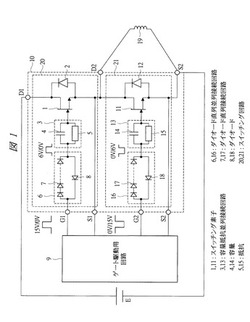

【図1】本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の一例を示す回路図である。

【図2】本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の動作において、コイルに流れる電流と時間との関係の一例を示す図である。

【図3】本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、(a),(b)はスイッチング波形とゲート電流波形のシミュレーション結果の一例を示す図である。

【図4】本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、(a),(b)はこの半導体モジュール(電力変換モジュール)の実装形態の一例を示すレイアウト図である。

【図5】本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の一例を示す回路図である。

【図6】本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、(a),(b)はスイッチング波形とゲート電流波形のシミュレーション結果の一例を示す図である。

【図7】本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、(a),(b)はこの半導体モジュール(電力変換モジュール)の実装形態の一例を示すレイアウト図である。

【発明を実施するための形態】

【0019】

以下の実施の形態においては、便宜上その必要があるときは、複数の実施の形態またはセクションに分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではない。

【0020】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0021】

[本発明の実施の形態の概要]

本発明の実施の形態(一例として、()内に対応する構成要素などを付記)は、ドレイン端子、ソース端子、及びゲート端子を有する半導体スイッチング素子(スイッチング素子1,11)を有し、前記半導体スイッチング素子のゲート端子とソース端子との間に、前記半導体スイッチング素子のゲート端子とソース端子との間に加える電圧または流す電流でドレイン端子とソース端子との間の導通及び非導通を制御するゲート駆動回路(ゲート駆動用回路9)が接続される半導体スイッチング回路(スイッチング回路20,21)であって、以下のような特徴を有するものである。

【0022】

(1)前記半導体スイッチング回路は、容量素子(容量4,14)と抵抗素子(抵抗5,15)とが並列に接続された第1回路(容量抵抗並列接続回路3,13)と、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路(ダイオード直列接続回路7,17)と、前記ダイオード直列接続回路のダイオードと逆方向に、前記ダイオード直列接続回路に並列に接続されたダイオード(ダイオード8,18)とを有する第2回路(ダイオード直列並列接続回路6,16)とを有する。そして、前記半導体スイッチング素子のゲート端子には前記第1回路の一端が接続され、前記第1回路の他端と前記ゲート駆動回路の出力端子との間には、前記ダイオード直列接続回路の1つ以上のダイオードのアノード端子を前記ゲート駆動回路側、前記ダイオード直列接続回路の1つ以上のダイオードのカソード端子を前記半導体スイッチング素子のゲート端子側にして、前記第2回路が接続されていることを特徴とする。さらに好適には、前記半導体スイッチング素子は、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタであることを特徴とする。この半導体スイッチング回路は、後述する第1の実施の形態に対応する。

【0023】

(2)上記(1)の構成に加え、前記第2回路は、前記ダイオード直列接続回路と並列に接続された容量素子(容量22,23)をさらに有することを特徴とする。この半導体スイッチング回路は、後述する第2の実施の形態に対応する。

【0024】

(3)上記(1)または上記(2)の半導体スイッチング回路を用いた半導体モジュール、前記半導体スイッチング回路を用いた電力変換モジュールにも、本発明は適用するものである。

【0025】

以上の本発明の実施の形態の概要に基づいた、本発明の実施の形態に係る半導体スイッチング回路、及び前記半導体スイッチング回路を用いた半導体モジュール、並びに前記半導体スイッチング回路を用いた電力変換モジュールを、以下において図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0026】

[第1の実施の形態]

本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュールを、図1〜図4を用いて説明する。本実施の形態においては、半導体モジュールとして、2つの半導体スイッチング回路を搭載した電力変換モジュールを例に説明する。本発明が適用される半導体モジュールとしては、2つの半導体スイッチング回路を搭載したものの他に、1つの半導体スイッチング回路を搭載したもの、3つ以上の半導体スイッチング回路を搭載したものも含めて半導体モジュールと呼ぶ。

【0027】

<半導体スイッチング回路、及びこれを用いた半導体モジュールの構成>

本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)について、図1を用いて説明する。図1は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の一例を示す回路図である。

【0028】

本実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)10は、第1スイッチング回路20(単にスイッチング回路20とも記す)と、第2スイッチング回路21(単にスイッチング回路21とも記す)とを有して構成される。この半導体モジュール10は、第1スイッチング回路20のソース端子S1と第2スイッチング回路21のドレイン端子D2とが接続されている。

【0029】

この半導体モジュール10には、第1スイッチング回路20のゲート端子G1とソース端子S1との間、第2スイッチング回路21のゲート端子G2とソース端子S2との間にゲート駆動用回路9が接続されている。このゲート駆動用回路9は、第1、第2スイッチング回路20,21のゲート端子G1,G2とソース端子S1,S2との間に加える電圧または流す電流で、ドレイン端子D1,D2とソース端子S1,S2との間の導通及び非導通を制御するものである。また、第2スイッチング回路21のドレイン端子D2とソース端子S2との間には、コイル19が接続されている。また、この半導体モジュール10には、第1スイッチング回路20のドレイン端子D1と第2スイッチング回路21のソース端子S2との間に主回路電圧Eが印加されている。

【0030】

第1スイッチング回路20は、スイッチング素子1、 ダイオード2、容量4と抵抗5とが並列に接続された容量抵抗並列接続回路3、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路7とこのダイオード直列接続回路7のダイオードと逆方向にこのダイオード直列接続回路7に並列に接続されたダイオード8とを有するダイオード直列並列接続回路6から構成される。

【0031】

第2スイッチング回路21も、第1スイッチング回路20と同様に、スイッチング素子11、ダイオード12、容量14と抵抗15とが並列に接続された容量抵抗並列接続回路13、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路17とこのダイオード直列接続回路17のダイオードと逆方向にこのダイオード直列接続回路17に並列に接続されたダイオード18とを有するダイオード直列並列接続回路16から構成される。

【0032】

この半導体モジュール10において、スイッチング回路20,21のスイッチング素子1,11としては、ドレイン、ソース、及びゲートの各端子を有し、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタ、具体的にはオン電圧2.5Vのノーマリオフ型接合FET(Field Effect Transistor)を例にして説明する。このFETとしては、SiCのJFET(Junction FET)、GaNのHEMT(High Electron Mobility Transistor)などが考えられる。

【0033】

このスイッチング回路20においては、スイッチング回路20のスイッチング素子1がオフの時に、ソース電位が上昇しゲート−ソース間の逆方向電圧によりスイッチング素子1が破壊されるのを防ぐために、ソースからドレインに電流を流せるようにダイオード2を接続しており、ゲートには容量4と抵抗5の容量抵抗並列接続回路3の一端が接続されている。容量抵抗並列接続回路3の他端とゲート駆動用回路9はダイオード直列並列接続回路6を介して接続されている。ダイオード直列並列接続回路6は、ゲート駆動用回路9から容量4と抵抗5の容量抵抗並列接続回路3の方向に順方向電流が流れるように接続したダイオード直列接続回路7とこのダイオード直列接続回路7とは並列に容量抵抗並列接続回路3からゲート駆動用回路9の方向に順方向電流が流れるように接続したダイオード8で構成する。すなわち、ダイオード直列接続回路7のダイオードは、アノードがゲート駆動用回路9側に、カソードが容量抵抗並列接続回路3側に接続され、ダイオード8は、逆に、アノードが容量抵抗並列接続回路3側に、カソードがゲート駆動用回路9側に接続されている。

【0034】

同じように、スイッチング回路21においては、スイッチング回路21のスイッチング素子11がオフの時に、ソース電位が上昇しゲート−ソース間の逆方向電圧によりスイッチング素子11が破壊されるのを防ぐために、ソースからドレインに電流を流せるようにダイオード12を接続しており、ゲートには容量14と抵抗15の容量抵抗並列接続回路13の一端が接続されている。容量抵抗並列接続回路13の他端とゲート駆動用回路9はダイオード直列並列接続回路16を介して接続されている。ダイオード直列並列接続回路16は、ゲート駆動用回路9から容量14と抵抗15の容量抵抗並列接続回路13の方向に順方向電流が流れるように接続したダイオード直列接続回路17とこのダイオード直列接続回路17とは並列に容量抵抗並列接続回路13からゲート駆動用回路9の方向に順方向電流が流れるように接続したダイオード18で構成する。

【0035】

主回路電圧Eのプラス端子はスイッチング素子1のドレイン、マイナス端子はスイッチング素子11のソースに接続し、コイル19はスイッチング素子11のドレイン、ソースと並列に接続する。

【0036】

<半導体スイッチング回路の動作>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の動作について、図1を参照しながら、図2を用いて説明する。図2は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の動作において、コイルに流れる電流と時間との関係の一例を示す図である。

【0037】

ゲート駆動用回路9からゲート端子G1−ソース端子S1間に入力される電圧が、例えば0Vから15Vに上昇すると、スイッチング回路20のダイオード直列接続回路7で電圧降下が発生する。例えば、1ダイオード当たりの電圧降下が1V、直列数を9とすると、ダイオード直列並列接続回路6と容量抵抗並列接続回路3の接続点で6Vの電圧が発生し、スイッチング素子1のゲート−ソース間の電圧降下が例えば2.5Vとすると、容量抵抗並列接続回路3の両端には3.5Vの電圧が発生する。この時、容量4によるゲート電位の上昇は抵抗5によるゲート電位の上昇より速いため、過度応答速度が改善されている。この容量4による電流により、スイッチング素子1はゲート−ソース間容量、ゲート−ドレイン間容量を充電しオンする。容量4が充電されると、抵抗5に電流が流れオン定常状態を保持する。

【0038】

この時、スイッチング回路21のスイッチング素子11はデッドタイム確保のため、すでにオフしている。主回路電圧Eはスイッチング素子1を介してコイル19を充電する。この時、コイル19に流れる電流は上昇する。図2には、コイル19に流れる電流I[A]と時間t[s]との関係を示すが、これはt0からt1の期間に相当する。

【0039】

次に、ゲート駆動用回路9からゲート端子G1−ソース端子S1間に入力される電圧が、例えば15Vから0Vに降下すると、スイッチング回路20の容量4に充電されていた電荷はダイオード8を介して放電され、スイッチング素子1のゲート−ソース間容量、ゲート−ドレイン間容量に充電されていた電荷も容量4、ダイオード8を介して放電される。この時の電流は、ゲート駆動用回路9に流れるためにゲート電圧は負電圧を発生し放電時間を短縮するため、過渡応答時間が改善する。その後、オフ定常状態となる。

【0040】

この時、スイッチング素子1,11は両方ともオフしデッドタイムの状態である。コイル19はエネルギーが供給されなくなったため、ダイオード12のアノードからカソード、カソードからコイル19へと循環電流が流れる。

【0041】

次に、ゲート駆動用回路9からゲート端子G2−ソース端子S2間に入力される電圧が、例えば0Vから15Vに上昇すると、スイッチング回路21のダイオード直列接続回路17で電圧降下が発生する。ダイオード直列並列接続回路16と容量抵抗並列接続回路13の接続点で6Vの電圧が発生し、スイッチング素子11のゲート−ソース間の電圧降下が例えば2.5Vとすると、容量抵抗並列接続回路13の両端には3.5Vの電圧が発生する。この時、容量14によるゲート電位の上昇は抵抗15よるゲート電位の上昇より速いため、過度応答速度が改善されている。この容量14による電流により、スイッチング素子11はゲート−ソース間容量、ゲート−ドレイン間容量を充電しオンする。容量14が充電されると、抵抗15に電流が流れオン定常状態を保持する。

【0042】

この時、循環電流はスイッチング素子11のソースからドレインへ、ドレインからコイル19に流れる。これは、図2のt1からt2の期間に相当する。コイル19、ダイオード12、スイッチング素子11の損失が非常に小さいとする。

【0043】

以上の繰り返しで、スイッチング素子1がオン、スイッチング素子11がオフすると、コイル19には更にエネルギーが蓄積され、電流が増加する。これは、図2のt2からt3の期間に相当する。

【0044】

<スイッチング波形とゲート電流波形のシミュレーション結果>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、スイッチング波形とゲート電流波形のシミュレーション結果について、図3を用いて説明する。図3(a)は、図1のドレイン端子D1−ドレイン端子D2(ソース端子S1)間のターンオフ電圧とドレイン端子D2−ソース端子S2間のターンオン電圧のスイッチング波形のシミュレーション結果の一例を示す図であり、図3(b)は、この(a)と同じタイミングにおけるスイッチング素子1とスイッチング素子11のゲート電流波形のシミュレーション結果の一例を示す図である。

【0045】

図3(a),(b)に示すように、ドレイン端子D1−ドレイン端子D2間のターンオフ電圧とドレイン端子D2−ソース端子S2間のターンオン電圧において、立ち上がり、立ち下がりを0%、100%で見ると50nsであることがわかり、この時間内にスイッチング素子1とスイッチング素子11のゲート電流がピークを持ち、電荷を高速充放電していることがわかる。

【0046】

以上のように、スイッチング素子1,11のゲートに接続された容量抵抗並列接続回路3,13の抵抗5,15に過剰な電流を流すことなく、高速かつ確実にオフするスイッチング回路20,21を提供できる。

【0047】

<半導体スイッチング回路を用いた半導体モジュールの実装形態>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の実装形態について、図4を用いて説明する。図4は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の実装形態の一例を示すレイアウト図であり、(a)は表面を、(b)は裏面をそれぞれ示す。この図4は、前述した図1に記載したスイッチング回路20,21を含む半導体モジュール(電力変換モジュール)10を示している。

【0048】

図4に示す半導体モジュール(電力変換モジュール)10は、モジュール基板上に各部品が実装され、これらの各部品は配線パターンに実装して接続されたり、あるいはワイヤボンディングワイヤなどにより接続されて電気的に接続された形態となっている。

【0049】

モジュール基板上の各端子D1,G1,D2,G2,S2は、表面の配線パターンと裏面の配線パターンとがビアホール(一点鎖線の丸印)で接続されている。さらに、これらの端子のうち、各端子D1,D2,S2に接続される配線パターンは、スイッチング素子1,11と接続される部分が広い面積で形成され、この広い面積の部分で表面の配線パターンと裏面の配線パターンとが複数のビアホールで接続されている。特に、広い面積の部分の裏面の配線パターンは、裏面の広さを最大限に利用したベタ配線パターンとなっている。また、モジュール基板の表面には、容量4,14、抵抗5,15、ダイオード直列並列接続回路6,16(ダイオード直列接続回路7,17、ダイオード8,18)の各部品間を接続するための配線パターンなども形成されている。

【0050】

スイッチング素子1,11、容量4,14、抵抗5,15、ダイオード直列接続回路7,17、ダイオード8,18はリード付き部品で構成してもよいが、スイッチング周波数が高い場合、電圧、電流波形の立ち上がり、立ち下がりを高速にする必要がある。この時、寄生成分によりスイッチングノイズが発生しやすいため、図4のように容量4,14、抵抗5,15は面実装部品で構成し、スイッチング素子1,11、ダイオード2,12、ダイオード直列並列接続回路6,16は半導体チップで構成するのが望ましい。スイッチング素子1,11の半導体チップは表面にゲート端子、ソース端子、裏面にドレイン端子、ダイオード2,12の半導体チップは表面にカソード端子、裏面にアノード端子が配置されている。

【0051】

ダイオード直列並列接続回路6,16は、アノード、カソードそれぞれにワイヤをボンディングするボンディングパッドを持つダイオードの直列接続回路を2列搭載しており、ダイオードの個数を選べるようにすることで、変換する電圧レベルを調整できるようにしてある。

【0052】

以上の構成にすることで、スイッチング素子1のゲートとダイオード直列並列接続回路6の間、スイッチング素子11のゲートとダイオード直列並列接続回路16の間を小さい寄生成分で接続することができ、ノイズの少ない高速スイッチングが可能となる。図4中の符号は図1と同じであるため詳細な説明は省略する。

【0053】

<第1の実施の形態の効果>

以上説明した第1の実施の形態によれば、スイッチング素子1,11を有するスイッチング回路20,21は、容量4,14と抵抗5,15とが並列に接続された容量抵抗並列接続回路3,13と、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路7,17とこのダイオード直列接続回路7,17のダイオードと逆方向にこのダイオード直列接続回路7,17に並列に接続されたダイオード8,18とを有するダイオード直列並列接続回路6,16とを有し、スイッチング素子1,11のゲート端子には容量抵抗並列接続回路3,13の一端が接続され、容量抵抗並列接続回路3,13の他端とゲート駆動用回路9の出力端子との間には、ダイオード直列接続回路7,17の1つ以上のダイオードのアノード端子をゲート駆動用回路9側、ダイオード直列接続回路7,17の1つ以上のダイオードのカソード端子をスイッチング素子1,11のゲート端子側にして、ダイオード直列並列接続回路6,16が接続されていることで、ゲート消費電力が低く、確実にスイッチング素子1,11をオンオフさせ、かつ、高速にスイッチング素子1,11をオンオフさせるスイッチング回路20,21、及びそれを用いた半導体モジュール(電力変換モジュール)10を実現することができる。

【0054】

[第2の実施の形態]

本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュールを、図5〜図7を用いて説明する。本実施の形態が上記第1の実施の形態と異なる点は、ダイオード直列並列接続回路6,16が、ダイオード直列接続回路7,17と並列に接続された容量22,23をさらに有する点である。以下、上記第1の実施の形態と異なる点を主に説明し、同じ部分の説明は省略する。

【0055】

<半導体スイッチング回路、及びこれを用いた半導体モジュールの構成>

本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)について、図5を用いて説明する。図5は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の一例を示す回路図である。

【0056】

本実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)10は、上記第1の実施の形態と同様に、第1スイッチング回路20と、第2スイッチング回路21とを有して構成される。特に、第1スイッチング回路20、第2スイッチング回路21において、ダイオード直列接続回路7,17にそれぞれ容量22,23が並列に追加されている。

【0057】

<半導体スイッチング回路の動作>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の動作について、図5を参照しながら、前述した図2を用いて説明する。

【0058】

ゲート駆動用回路9からゲート端子G1−ソース端子S1間に入力される電圧が、例えば0Vから15Vに上昇すると、ダイオード直列接続回路7による電圧降下よりも先に容量22と容量4を介して、スイッチング素子1のゲート−ソース間容量、ゲート−ドレイン間容量への充電が始まる。充電が完了するとスイッチング素子1が完全にオンし、スイッチング回路20のダイオード直列接続回路7で電圧降下が発生する。例えば、1ダイオード当たりの電圧降下が1V、直列数を9とすると、ダイオード直列並列接続回路6と容量抵抗並列接続回路3の接続点で6Vの電圧が発生し、スイッチング素子1のゲート−ソース間の電圧降下が例えば2.5Vとすると、容量抵抗並列接続回路3の両端には3.5Vの電圧が発生し、抵抗5に電流が流れオン定常状態を保持する。

【0059】

この時、スイッチング回路21のスイッチング素子11はデッドタイム確保のため、すでにオフしている。主回路電圧Eはスイッチング素子1を介してコイル19を充電する。この時、コイル19に流れる電流は上昇する。図2には、コイル19に流れる電流と時間との関係を示すが、これはt0からt1の期間に相当する。

【0060】

次に、ゲート駆動用回路9からゲート端子G1−ソース端子S1間に入力される電圧が、例えば15Vから0Vに降下すると、スイッチング回路20の容量22と容量4は放電を始め、スイッチング素子1のゲート−ソース間容量、ゲート−ドレイン間容量に充電されていた電荷も容量22と容量4を介して放電する。この時の電流は、ゲート駆動用回路9に流れるためにゲート電圧は負電圧を発生し放電時間を短縮するため、過渡応答時間が改善する。その後、ダイオード8を介してオフ定常状態となる。

【0061】

この時、スイッチング素子1,11は両方ともオフしデッドタイムの状態である。コイル19はエネルギーが供給されなくなったため、ダイオード12のアノードからカソード、カソードからコイル19に循環電流が流れる。

【0062】

次に、ゲート駆動用回路9からゲート端子G2−ソース端子S2間に入力される電圧が、例えば0Vから15Vに上昇すると、スイッチング回路21の容量23と容量14を介してスイッチング素子11のゲート−ソース間容量、ゲート−ドレイン間容量への充電が始まる。充電が完了するとスイッチング素子11が完全にオンし、スイッチング回路21のダイオード直列接続回路17で電圧降下が発生する。例えば、1ダイオード当たりの電圧降下が1V、直列数が9で、ダイオード直列並列接続回路16と容量抵抗並列接続回路13の接続点で6Vの電圧が発生し、スイッチング素子11のゲート−ソース間の電圧降下が例えば2.5Vとすると、容量抵抗並列接続回路13の両端には3.5Vの電圧が発生し、抵抗15に電流が流れオン定常状態を保持する。

【0063】

この時、循環電流はスイッチング素子11のソースからドレインへ、ドレインからコイル19に流れる。これは、図2のt1からt2の期間に相当する。

【0064】

以上の繰り返しで、スイッチング素子1がオン、スイッチング素子11がオフすると、コイル19には更にエネルギーが蓄積され、電流が増加する。これは、図2のt2〜t3の期間に相当する。

【0065】

<スイッチング波形とゲート電流波形のシミュレーション結果>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、スイッチング波形とゲート電流波形のシミュレーション結果について、図6を用いて説明する。図6(a)は、図5のドレイン端子D1−ドレイン端子D2間のターンオフ電圧とドレイン端子D2−ソース端子S2間のターンオン電圧のスイッチング波形のシミュレーション結果の一例を示す図であり、図6(b)は、この(a)と同じタイミングにおけるスイッチング素子1とスイッチング素子11のゲート電流波形のシミュレーション結果の一例を示す図である。

【0066】

図6(a),(b)に示すように、ドレイン端子D1−ドレイン端子D2間のターンオフ電圧とドレイン端子D2−ソース端子S2間のターンオン電圧において、立ち上がり、立ち下がりを0%、100%で見ると15nsであることがわかり、容量22,23により短い時間に大電流を流しているため、電荷を上記第1の実施の形態で示した図3より高速に充放電していることがわかる。

【0067】

以上のように、スイッチング素子1,11のゲートに接続された容量抵抗並列接続回路3,13の抵抗5,15に過剰な電流を流すことなく、高速かつ確実にオフするスイッチング回路20,21を提供できる。

【0068】

<半導体スイッチング回路を用いた半導体モジュールの実装形態>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の実装形態について、図7を用いて説明する。図7は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の実装形態の一例を示すレイアウト図であり、(a)は表面を、(b)は裏面をそれぞれ示す。この図7は、前述した図5に記載したスイッチング回路20,21を含む半導体モジュール(電力変換モジュール)10を示している。

【0069】

図7に示す半導体モジュール(電力変換モジュール)10は、図4に示した半導体モジュール(電力変換モジュール)10に対して、スイッチング回路20,21のダイオード直列並列接続回路6,16にそれぞれ容量22,23が並列に追加されている。そのために、それぞれのダイオード直列並列接続回路6,16の各端部に接続された配線パターンが延長して形成され、この延長して形成された配線パターン間にそれぞれ容量22,23が実装されている。他の配線パターン、各端子などは、図4に示した半導体モジュール(電力変換モジュール)と同様である。

【0070】

スイッチング素子1,11、容量4,14,22,23、抵抗5,15、ダイオード直列接続回路7,17、ダイオード8,18はリード付き部品で構成してもよいが、スイッチング周波数が高くなると、電圧、電流波形の立ち上がり、立ち下がりを高速にする必要がある。この時、寄生成分によりスイッチングノイズが発生しやすいため、図7のように容量4,14,22,23、抵抗5,15は面実装部品で構成し、スイッチング素子1,11、ダイオード2,12、ダイオード直列並列接続回路6,16は半導体チップで構成するのが望ましい。スイッチング素子1,11の半導体チップは表面にゲート端子、ソース端子、裏面にドレイン端子、ダイオード2,12の半導体チップは表面にカソード端子、裏面にアノード端子が配置されている。図7中の符号は図5と同じであるため詳細な説明は省略する。

【0071】

ダイオード直列並列接続回路6,16は、アノード、カソードそれぞれにワイヤをボンディングするボンディングパッドを持つダイオードの直列接続回路を2列搭載しており、ダイオードの個数を選べるようにすることで、変換する電圧レベルを調整できるようにしてある。容量4,14、容量22,23、抵抗5,15はチップ部品である。

【0072】

以上の構成にすることで、スイッチング素子1のゲートとダイオード直列並列接続回路6の間、スイッチング素子11のゲートとダイオード直列並列接続回路16の間を小さい寄生成分で接続することができ、高速スイッチングが可能となる。

【0073】

<第2の実施の形態の効果>

以上説明した第2の実施の形態によれば、ダイオード直列並列接続回路6,16は、ダイオード直列接続回路7,17と並列に接続された容量22,23をさらに有することで、上記第1の実施の形態の効果に加えて、容量22,23により短い時間に大電流を流して、より一層、電荷を高速に充放電させることができるので、より一層、高速にスイッチング素子1,11をオンオフさせるスイッチング回路20,21、及びそれを用いた半導体モジュール(電力変換モジュール)10を実現することができる。

【0074】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0075】

本発明は、半導体スイッチング素子を有する半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールに利用可能である。

【符号の説明】

【0076】

1,11 スイッチング素子

2,12 ダイオード

3,13 容量抵抗並列接続回路

4,14 容量

5,15 抵抗

6,16 ダイオード直列並列接続回路

7,17 ダイオード直列接続回路

8,18 ダイオード

9 ゲート駆動用回路

10 半導体モジュール

19 コイル

20,21 スイッチング回路

22,23 容量

【技術分野】

【0001】

本発明は、半導体スイッチング素子を有する半導体スイッチング回路の技術に関し、特に、この半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールに適用して有効な技術に関する。

【背景技術】

【0002】

半導体スイッチング回路を用いた電力変換モジュールの一例であるインバータ回路に関する技術としては、例えば特開平10−191650号公報(特許文献1)に記載される技術などが挙げられる。この特許文献1には、直流電源の正負端子間に直列に接続され、交互にオン−オフする2つのトランジスタを有するインバータ回路において、この2つのトランジスタにバイポーラトランジスタを使ったハーフブリッジ回路の技術が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平10−191650号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、現在、直流−交流電力変換回路(インバータ)、交流−直流電力変換回路(コンバータ)や力率改善回路などのパワーエレクトロニクスに使われるスイッチング素子には、シリコンデバイスであるMOS(Metal Oxide Semiconductor)トランジスタ、IGBT(Insulated Gate Bipolar Transistor)が広く使われている。パワーエレクトロニクスにおいては、ゲート駆動回路が故障などの不具合により駆動電圧が出力されない時に、貫通電流によるスイッチング素子、しいてはシステムの故障を防ぐために、閾値電圧が0Vより大きいノーマリオフ特性を持つことが望まれる。

【0005】

シリコン系MOSトランジスタ、IGBTは、通常、5V以上の閾値電圧を持つ。また、スイッチング動作時の導通損失を最小にするため、オン電圧は8V〜15Vであることが多い。よって、現在、市販されているゲート駆動用回路の出力電圧も8V〜15Vのものが多い。一方、接合型トランジスタは、MOSトランジスタやIGBTと比べて低オン抵抗を得やすいが、ゲート−ソース間にダイオードが形成されるため、オン電圧が約1V〜3Vと低い。

【0006】

最近では、SiC(Silicon-Carbide)やGaN(Gallium-Nitride)などのワイドバンドギャップ半導体を使ったスイッチング素子は、シリコンデバイスと比較して高温動作、低オン抵抗、高耐圧を同時達成することができるため、次世代デバイスとして注目を浴びている。しかし、これらのデバイス構造は接合型である場合が多く、オン電圧は約1V〜6Vと低い。市販されているゲート駆動用ICは、出力電圧が高すぎるため、そのままでは利用できない課題を有する。この課題に対して、例えば、ゲート駆動用ICの出力電圧を電圧レギュレータで電圧レベルを変換することは可能ではあるが、電圧レギュレータ用の別電源が必要である。

【0007】

また、前述した特許文献1の図6の回路においては、トランジスタQ14のベースに接続するツェナーダイオードZD12と、トランジスタQ15のベースに接続するツェナーダイオードZD13の向きを逆にすることで、疑似的にオン電圧を変えてトランジスタQ14,Q15が同じタイミングでオン状態になることを防いでいる。ツェナーダイオードZD12とZD13に流れる逆方向電流でトランジスタQ14,Q15を駆動している。ツェナーダイオードの逆方向電流は数μA〜数mA程度と小さいので、駆動できるトランジスタサイズに制限がある。

【0008】

トランジスタQ14,Q15が電界効果型トランジスタの場合、この回路は主回路電圧EをツェナーダイオードZD13で下げる効果があるが、ツェナーダイオードは降伏電圧が大きいため、トランジスタQ15を電圧駆動する場合、ツェナーダイオード1つで最適なオン電圧を与えるのは難しく、抵抗R23に過剰な電圧がかかり消費電力が増える。また、容量C12,C13は突入電流により、トランジスタQ14,Q15の入力容量の充放電を高速にする効果を持つが、ツェナーダイオードZD12,ZD13により電流上限値が制限されるため、高速化を律即している。

【0009】

そこで、本発明は前述した特許文献1を含む従来技術の課題に鑑みてなされたものであり、その代表的な目的は、低ゲート消費電力で、高速かつ確実にスイッチング素子をオンオフさせる半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールを提供することにある。

【0010】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0012】

すなわち、代表的なものの概要は、ドレイン端子、ソース端子、及びゲート端子を有する半導体スイッチング素子を有し、前記半導体スイッチング素子のゲート端子とソース端子との間に、前記半導体スイッチング素子のゲート端子とソース端子との間に印加された電圧または電流によってドレイン端子とソース端子との間の導通及び非導通を制御するゲート駆動回路が接続される半導体スイッチング回路であって、以下のような特徴を有するものである。

【0013】

(1)前記半導体スイッチング回路は、容量素子と抵抗素子とが並列に接続された第1回路と、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路と、前記ダイオード直列接続回路のダイオードと逆方向に、前記ダイオード直列接続回路に並列に接続されたダイオードとを有する第2回路とを有する。そして、前記半導体スイッチング素子のゲート端子には前記第1回路の一端が接続され、前記第1回路の他端と前記ゲート駆動回路の出力端子との間には、前記ダイオード直列接続回路の1つ以上のダイオードのアノード端子を前記ゲート駆動回路側、前記ダイオード直列接続回路の1つ以上のダイオードのカソード端子を前記半導体スイッチング素子のゲート端子側にして、前記第2回路が接続されていることを特徴とする。さらに好適には、前記半導体スイッチング素子は、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタであることを特徴とする。

【0014】

(2)上記(1)の構成に加え、前記第2回路は、前記ダイオード直列接続回路と並列に接続された容量素子をさらに有することを特徴とする。

【0015】

(3)上記(1)または上記(2)の半導体スイッチング回路を用いた半導体モジュール、前記半導体スイッチング回路を用いた電力変換モジュールにも、本発明は適用するものである。

【発明の効果】

【0016】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0017】

すなわち、代表的なものによって得られる効果は、低ゲート消費電力で、高速にスイッチング素子をオンオフさせる半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールが実現可能になる。

【図面の簡単な説明】

【0018】

【図1】本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の一例を示す回路図である。

【図2】本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の動作において、コイルに流れる電流と時間との関係の一例を示す図である。

【図3】本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、(a),(b)はスイッチング波形とゲート電流波形のシミュレーション結果の一例を示す図である。

【図4】本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、(a),(b)はこの半導体モジュール(電力変換モジュール)の実装形態の一例を示すレイアウト図である。

【図5】本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の一例を示す回路図である。

【図6】本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、(a),(b)はスイッチング波形とゲート電流波形のシミュレーション結果の一例を示す図である。

【図7】本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、(a),(b)はこの半導体モジュール(電力変換モジュール)の実装形態の一例を示すレイアウト図である。

【発明を実施するための形態】

【0019】

以下の実施の形態においては、便宜上その必要があるときは、複数の実施の形態またはセクションに分割して説明するが、特に明示した場合を除き、それらは互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等(個数、数値、量、範囲等を含む)に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではない。

【0020】

さらに、以下の実施の形態において、その構成要素(要素ステップ等も含む)は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

【0021】

[本発明の実施の形態の概要]

本発明の実施の形態(一例として、()内に対応する構成要素などを付記)は、ドレイン端子、ソース端子、及びゲート端子を有する半導体スイッチング素子(スイッチング素子1,11)を有し、前記半導体スイッチング素子のゲート端子とソース端子との間に、前記半導体スイッチング素子のゲート端子とソース端子との間に加える電圧または流す電流でドレイン端子とソース端子との間の導通及び非導通を制御するゲート駆動回路(ゲート駆動用回路9)が接続される半導体スイッチング回路(スイッチング回路20,21)であって、以下のような特徴を有するものである。

【0022】

(1)前記半導体スイッチング回路は、容量素子(容量4,14)と抵抗素子(抵抗5,15)とが並列に接続された第1回路(容量抵抗並列接続回路3,13)と、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路(ダイオード直列接続回路7,17)と、前記ダイオード直列接続回路のダイオードと逆方向に、前記ダイオード直列接続回路に並列に接続されたダイオード(ダイオード8,18)とを有する第2回路(ダイオード直列並列接続回路6,16)とを有する。そして、前記半導体スイッチング素子のゲート端子には前記第1回路の一端が接続され、前記第1回路の他端と前記ゲート駆動回路の出力端子との間には、前記ダイオード直列接続回路の1つ以上のダイオードのアノード端子を前記ゲート駆動回路側、前記ダイオード直列接続回路の1つ以上のダイオードのカソード端子を前記半導体スイッチング素子のゲート端子側にして、前記第2回路が接続されていることを特徴とする。さらに好適には、前記半導体スイッチング素子は、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタであることを特徴とする。この半導体スイッチング回路は、後述する第1の実施の形態に対応する。

【0023】

(2)上記(1)の構成に加え、前記第2回路は、前記ダイオード直列接続回路と並列に接続された容量素子(容量22,23)をさらに有することを特徴とする。この半導体スイッチング回路は、後述する第2の実施の形態に対応する。

【0024】

(3)上記(1)または上記(2)の半導体スイッチング回路を用いた半導体モジュール、前記半導体スイッチング回路を用いた電力変換モジュールにも、本発明は適用するものである。

【0025】

以上の本発明の実施の形態の概要に基づいた、本発明の実施の形態に係る半導体スイッチング回路、及び前記半導体スイッチング回路を用いた半導体モジュール、並びに前記半導体スイッチング回路を用いた電力変換モジュールを、以下において図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0026】

[第1の実施の形態]

本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュールを、図1〜図4を用いて説明する。本実施の形態においては、半導体モジュールとして、2つの半導体スイッチング回路を搭載した電力変換モジュールを例に説明する。本発明が適用される半導体モジュールとしては、2つの半導体スイッチング回路を搭載したものの他に、1つの半導体スイッチング回路を搭載したもの、3つ以上の半導体スイッチング回路を搭載したものも含めて半導体モジュールと呼ぶ。

【0027】

<半導体スイッチング回路、及びこれを用いた半導体モジュールの構成>

本発明の第1の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)について、図1を用いて説明する。図1は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の一例を示す回路図である。

【0028】

本実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)10は、第1スイッチング回路20(単にスイッチング回路20とも記す)と、第2スイッチング回路21(単にスイッチング回路21とも記す)とを有して構成される。この半導体モジュール10は、第1スイッチング回路20のソース端子S1と第2スイッチング回路21のドレイン端子D2とが接続されている。

【0029】

この半導体モジュール10には、第1スイッチング回路20のゲート端子G1とソース端子S1との間、第2スイッチング回路21のゲート端子G2とソース端子S2との間にゲート駆動用回路9が接続されている。このゲート駆動用回路9は、第1、第2スイッチング回路20,21のゲート端子G1,G2とソース端子S1,S2との間に加える電圧または流す電流で、ドレイン端子D1,D2とソース端子S1,S2との間の導通及び非導通を制御するものである。また、第2スイッチング回路21のドレイン端子D2とソース端子S2との間には、コイル19が接続されている。また、この半導体モジュール10には、第1スイッチング回路20のドレイン端子D1と第2スイッチング回路21のソース端子S2との間に主回路電圧Eが印加されている。

【0030】

第1スイッチング回路20は、スイッチング素子1、 ダイオード2、容量4と抵抗5とが並列に接続された容量抵抗並列接続回路3、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路7とこのダイオード直列接続回路7のダイオードと逆方向にこのダイオード直列接続回路7に並列に接続されたダイオード8とを有するダイオード直列並列接続回路6から構成される。

【0031】

第2スイッチング回路21も、第1スイッチング回路20と同様に、スイッチング素子11、ダイオード12、容量14と抵抗15とが並列に接続された容量抵抗並列接続回路13、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路17とこのダイオード直列接続回路17のダイオードと逆方向にこのダイオード直列接続回路17に並列に接続されたダイオード18とを有するダイオード直列並列接続回路16から構成される。

【0032】

この半導体モジュール10において、スイッチング回路20,21のスイッチング素子1,11としては、ドレイン、ソース、及びゲートの各端子を有し、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタ、具体的にはオン電圧2.5Vのノーマリオフ型接合FET(Field Effect Transistor)を例にして説明する。このFETとしては、SiCのJFET(Junction FET)、GaNのHEMT(High Electron Mobility Transistor)などが考えられる。

【0033】

このスイッチング回路20においては、スイッチング回路20のスイッチング素子1がオフの時に、ソース電位が上昇しゲート−ソース間の逆方向電圧によりスイッチング素子1が破壊されるのを防ぐために、ソースからドレインに電流を流せるようにダイオード2を接続しており、ゲートには容量4と抵抗5の容量抵抗並列接続回路3の一端が接続されている。容量抵抗並列接続回路3の他端とゲート駆動用回路9はダイオード直列並列接続回路6を介して接続されている。ダイオード直列並列接続回路6は、ゲート駆動用回路9から容量4と抵抗5の容量抵抗並列接続回路3の方向に順方向電流が流れるように接続したダイオード直列接続回路7とこのダイオード直列接続回路7とは並列に容量抵抗並列接続回路3からゲート駆動用回路9の方向に順方向電流が流れるように接続したダイオード8で構成する。すなわち、ダイオード直列接続回路7のダイオードは、アノードがゲート駆動用回路9側に、カソードが容量抵抗並列接続回路3側に接続され、ダイオード8は、逆に、アノードが容量抵抗並列接続回路3側に、カソードがゲート駆動用回路9側に接続されている。

【0034】

同じように、スイッチング回路21においては、スイッチング回路21のスイッチング素子11がオフの時に、ソース電位が上昇しゲート−ソース間の逆方向電圧によりスイッチング素子11が破壊されるのを防ぐために、ソースからドレインに電流を流せるようにダイオード12を接続しており、ゲートには容量14と抵抗15の容量抵抗並列接続回路13の一端が接続されている。容量抵抗並列接続回路13の他端とゲート駆動用回路9はダイオード直列並列接続回路16を介して接続されている。ダイオード直列並列接続回路16は、ゲート駆動用回路9から容量14と抵抗15の容量抵抗並列接続回路13の方向に順方向電流が流れるように接続したダイオード直列接続回路17とこのダイオード直列接続回路17とは並列に容量抵抗並列接続回路13からゲート駆動用回路9の方向に順方向電流が流れるように接続したダイオード18で構成する。

【0035】

主回路電圧Eのプラス端子はスイッチング素子1のドレイン、マイナス端子はスイッチング素子11のソースに接続し、コイル19はスイッチング素子11のドレイン、ソースと並列に接続する。

【0036】

<半導体スイッチング回路の動作>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の動作について、図1を参照しながら、図2を用いて説明する。図2は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の動作において、コイルに流れる電流と時間との関係の一例を示す図である。

【0037】

ゲート駆動用回路9からゲート端子G1−ソース端子S1間に入力される電圧が、例えば0Vから15Vに上昇すると、スイッチング回路20のダイオード直列接続回路7で電圧降下が発生する。例えば、1ダイオード当たりの電圧降下が1V、直列数を9とすると、ダイオード直列並列接続回路6と容量抵抗並列接続回路3の接続点で6Vの電圧が発生し、スイッチング素子1のゲート−ソース間の電圧降下が例えば2.5Vとすると、容量抵抗並列接続回路3の両端には3.5Vの電圧が発生する。この時、容量4によるゲート電位の上昇は抵抗5によるゲート電位の上昇より速いため、過度応答速度が改善されている。この容量4による電流により、スイッチング素子1はゲート−ソース間容量、ゲート−ドレイン間容量を充電しオンする。容量4が充電されると、抵抗5に電流が流れオン定常状態を保持する。

【0038】

この時、スイッチング回路21のスイッチング素子11はデッドタイム確保のため、すでにオフしている。主回路電圧Eはスイッチング素子1を介してコイル19を充電する。この時、コイル19に流れる電流は上昇する。図2には、コイル19に流れる電流I[A]と時間t[s]との関係を示すが、これはt0からt1の期間に相当する。

【0039】

次に、ゲート駆動用回路9からゲート端子G1−ソース端子S1間に入力される電圧が、例えば15Vから0Vに降下すると、スイッチング回路20の容量4に充電されていた電荷はダイオード8を介して放電され、スイッチング素子1のゲート−ソース間容量、ゲート−ドレイン間容量に充電されていた電荷も容量4、ダイオード8を介して放電される。この時の電流は、ゲート駆動用回路9に流れるためにゲート電圧は負電圧を発生し放電時間を短縮するため、過渡応答時間が改善する。その後、オフ定常状態となる。

【0040】

この時、スイッチング素子1,11は両方ともオフしデッドタイムの状態である。コイル19はエネルギーが供給されなくなったため、ダイオード12のアノードからカソード、カソードからコイル19へと循環電流が流れる。

【0041】

次に、ゲート駆動用回路9からゲート端子G2−ソース端子S2間に入力される電圧が、例えば0Vから15Vに上昇すると、スイッチング回路21のダイオード直列接続回路17で電圧降下が発生する。ダイオード直列並列接続回路16と容量抵抗並列接続回路13の接続点で6Vの電圧が発生し、スイッチング素子11のゲート−ソース間の電圧降下が例えば2.5Vとすると、容量抵抗並列接続回路13の両端には3.5Vの電圧が発生する。この時、容量14によるゲート電位の上昇は抵抗15よるゲート電位の上昇より速いため、過度応答速度が改善されている。この容量14による電流により、スイッチング素子11はゲート−ソース間容量、ゲート−ドレイン間容量を充電しオンする。容量14が充電されると、抵抗15に電流が流れオン定常状態を保持する。

【0042】

この時、循環電流はスイッチング素子11のソースからドレインへ、ドレインからコイル19に流れる。これは、図2のt1からt2の期間に相当する。コイル19、ダイオード12、スイッチング素子11の損失が非常に小さいとする。

【0043】

以上の繰り返しで、スイッチング素子1がオン、スイッチング素子11がオフすると、コイル19には更にエネルギーが蓄積され、電流が増加する。これは、図2のt2からt3の期間に相当する。

【0044】

<スイッチング波形とゲート電流波形のシミュレーション結果>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、スイッチング波形とゲート電流波形のシミュレーション結果について、図3を用いて説明する。図3(a)は、図1のドレイン端子D1−ドレイン端子D2(ソース端子S1)間のターンオフ電圧とドレイン端子D2−ソース端子S2間のターンオン電圧のスイッチング波形のシミュレーション結果の一例を示す図であり、図3(b)は、この(a)と同じタイミングにおけるスイッチング素子1とスイッチング素子11のゲート電流波形のシミュレーション結果の一例を示す図である。

【0045】

図3(a),(b)に示すように、ドレイン端子D1−ドレイン端子D2間のターンオフ電圧とドレイン端子D2−ソース端子S2間のターンオン電圧において、立ち上がり、立ち下がりを0%、100%で見ると50nsであることがわかり、この時間内にスイッチング素子1とスイッチング素子11のゲート電流がピークを持ち、電荷を高速充放電していることがわかる。

【0046】

以上のように、スイッチング素子1,11のゲートに接続された容量抵抗並列接続回路3,13の抵抗5,15に過剰な電流を流すことなく、高速かつ確実にオフするスイッチング回路20,21を提供できる。

【0047】

<半導体スイッチング回路を用いた半導体モジュールの実装形態>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の実装形態について、図4を用いて説明する。図4は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の実装形態の一例を示すレイアウト図であり、(a)は表面を、(b)は裏面をそれぞれ示す。この図4は、前述した図1に記載したスイッチング回路20,21を含む半導体モジュール(電力変換モジュール)10を示している。

【0048】

図4に示す半導体モジュール(電力変換モジュール)10は、モジュール基板上に各部品が実装され、これらの各部品は配線パターンに実装して接続されたり、あるいはワイヤボンディングワイヤなどにより接続されて電気的に接続された形態となっている。

【0049】

モジュール基板上の各端子D1,G1,D2,G2,S2は、表面の配線パターンと裏面の配線パターンとがビアホール(一点鎖線の丸印)で接続されている。さらに、これらの端子のうち、各端子D1,D2,S2に接続される配線パターンは、スイッチング素子1,11と接続される部分が広い面積で形成され、この広い面積の部分で表面の配線パターンと裏面の配線パターンとが複数のビアホールで接続されている。特に、広い面積の部分の裏面の配線パターンは、裏面の広さを最大限に利用したベタ配線パターンとなっている。また、モジュール基板の表面には、容量4,14、抵抗5,15、ダイオード直列並列接続回路6,16(ダイオード直列接続回路7,17、ダイオード8,18)の各部品間を接続するための配線パターンなども形成されている。

【0050】

スイッチング素子1,11、容量4,14、抵抗5,15、ダイオード直列接続回路7,17、ダイオード8,18はリード付き部品で構成してもよいが、スイッチング周波数が高い場合、電圧、電流波形の立ち上がり、立ち下がりを高速にする必要がある。この時、寄生成分によりスイッチングノイズが発生しやすいため、図4のように容量4,14、抵抗5,15は面実装部品で構成し、スイッチング素子1,11、ダイオード2,12、ダイオード直列並列接続回路6,16は半導体チップで構成するのが望ましい。スイッチング素子1,11の半導体チップは表面にゲート端子、ソース端子、裏面にドレイン端子、ダイオード2,12の半導体チップは表面にカソード端子、裏面にアノード端子が配置されている。

【0051】

ダイオード直列並列接続回路6,16は、アノード、カソードそれぞれにワイヤをボンディングするボンディングパッドを持つダイオードの直列接続回路を2列搭載しており、ダイオードの個数を選べるようにすることで、変換する電圧レベルを調整できるようにしてある。

【0052】

以上の構成にすることで、スイッチング素子1のゲートとダイオード直列並列接続回路6の間、スイッチング素子11のゲートとダイオード直列並列接続回路16の間を小さい寄生成分で接続することができ、ノイズの少ない高速スイッチングが可能となる。図4中の符号は図1と同じであるため詳細な説明は省略する。

【0053】

<第1の実施の形態の効果>

以上説明した第1の実施の形態によれば、スイッチング素子1,11を有するスイッチング回路20,21は、容量4,14と抵抗5,15とが並列に接続された容量抵抗並列接続回路3,13と、1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路7,17とこのダイオード直列接続回路7,17のダイオードと逆方向にこのダイオード直列接続回路7,17に並列に接続されたダイオード8,18とを有するダイオード直列並列接続回路6,16とを有し、スイッチング素子1,11のゲート端子には容量抵抗並列接続回路3,13の一端が接続され、容量抵抗並列接続回路3,13の他端とゲート駆動用回路9の出力端子との間には、ダイオード直列接続回路7,17の1つ以上のダイオードのアノード端子をゲート駆動用回路9側、ダイオード直列接続回路7,17の1つ以上のダイオードのカソード端子をスイッチング素子1,11のゲート端子側にして、ダイオード直列並列接続回路6,16が接続されていることで、ゲート消費電力が低く、確実にスイッチング素子1,11をオンオフさせ、かつ、高速にスイッチング素子1,11をオンオフさせるスイッチング回路20,21、及びそれを用いた半導体モジュール(電力変換モジュール)10を実現することができる。

【0054】

[第2の実施の形態]

本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュールを、図5〜図7を用いて説明する。本実施の形態が上記第1の実施の形態と異なる点は、ダイオード直列並列接続回路6,16が、ダイオード直列接続回路7,17と並列に接続された容量22,23をさらに有する点である。以下、上記第1の実施の形態と異なる点を主に説明し、同じ部分の説明は省略する。

【0055】

<半導体スイッチング回路、及びこれを用いた半導体モジュールの構成>

本発明の第2の実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)について、図5を用いて説明する。図5は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の一例を示す回路図である。

【0056】

本実施の形態に係る半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)10は、上記第1の実施の形態と同様に、第1スイッチング回路20と、第2スイッチング回路21とを有して構成される。特に、第1スイッチング回路20、第2スイッチング回路21において、ダイオード直列接続回路7,17にそれぞれ容量22,23が並列に追加されている。

【0057】

<半導体スイッチング回路の動作>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の動作について、図5を参照しながら、前述した図2を用いて説明する。

【0058】

ゲート駆動用回路9からゲート端子G1−ソース端子S1間に入力される電圧が、例えば0Vから15Vに上昇すると、ダイオード直列接続回路7による電圧降下よりも先に容量22と容量4を介して、スイッチング素子1のゲート−ソース間容量、ゲート−ドレイン間容量への充電が始まる。充電が完了するとスイッチング素子1が完全にオンし、スイッチング回路20のダイオード直列接続回路7で電圧降下が発生する。例えば、1ダイオード当たりの電圧降下が1V、直列数を9とすると、ダイオード直列並列接続回路6と容量抵抗並列接続回路3の接続点で6Vの電圧が発生し、スイッチング素子1のゲート−ソース間の電圧降下が例えば2.5Vとすると、容量抵抗並列接続回路3の両端には3.5Vの電圧が発生し、抵抗5に電流が流れオン定常状態を保持する。

【0059】

この時、スイッチング回路21のスイッチング素子11はデッドタイム確保のため、すでにオフしている。主回路電圧Eはスイッチング素子1を介してコイル19を充電する。この時、コイル19に流れる電流は上昇する。図2には、コイル19に流れる電流と時間との関係を示すが、これはt0からt1の期間に相当する。

【0060】

次に、ゲート駆動用回路9からゲート端子G1−ソース端子S1間に入力される電圧が、例えば15Vから0Vに降下すると、スイッチング回路20の容量22と容量4は放電を始め、スイッチング素子1のゲート−ソース間容量、ゲート−ドレイン間容量に充電されていた電荷も容量22と容量4を介して放電する。この時の電流は、ゲート駆動用回路9に流れるためにゲート電圧は負電圧を発生し放電時間を短縮するため、過渡応答時間が改善する。その後、ダイオード8を介してオフ定常状態となる。

【0061】

この時、スイッチング素子1,11は両方ともオフしデッドタイムの状態である。コイル19はエネルギーが供給されなくなったため、ダイオード12のアノードからカソード、カソードからコイル19に循環電流が流れる。

【0062】

次に、ゲート駆動用回路9からゲート端子G2−ソース端子S2間に入力される電圧が、例えば0Vから15Vに上昇すると、スイッチング回路21の容量23と容量14を介してスイッチング素子11のゲート−ソース間容量、ゲート−ドレイン間容量への充電が始まる。充電が完了するとスイッチング素子11が完全にオンし、スイッチング回路21のダイオード直列接続回路17で電圧降下が発生する。例えば、1ダイオード当たりの電圧降下が1V、直列数が9で、ダイオード直列並列接続回路16と容量抵抗並列接続回路13の接続点で6Vの電圧が発生し、スイッチング素子11のゲート−ソース間の電圧降下が例えば2.5Vとすると、容量抵抗並列接続回路13の両端には3.5Vの電圧が発生し、抵抗15に電流が流れオン定常状態を保持する。

【0063】

この時、循環電流はスイッチング素子11のソースからドレインへ、ドレインからコイル19に流れる。これは、図2のt1からt2の期間に相当する。

【0064】

以上の繰り返しで、スイッチング素子1がオン、スイッチング素子11がオフすると、コイル19には更にエネルギーが蓄積され、電流が増加する。これは、図2のt2〜t3の期間に相当する。

【0065】

<スイッチング波形とゲート電流波形のシミュレーション結果>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)において、スイッチング波形とゲート電流波形のシミュレーション結果について、図6を用いて説明する。図6(a)は、図5のドレイン端子D1−ドレイン端子D2間のターンオフ電圧とドレイン端子D2−ソース端子S2間のターンオン電圧のスイッチング波形のシミュレーション結果の一例を示す図であり、図6(b)は、この(a)と同じタイミングにおけるスイッチング素子1とスイッチング素子11のゲート電流波形のシミュレーション結果の一例を示す図である。

【0066】

図6(a),(b)に示すように、ドレイン端子D1−ドレイン端子D2間のターンオフ電圧とドレイン端子D2−ソース端子S2間のターンオン電圧において、立ち上がり、立ち下がりを0%、100%で見ると15nsであることがわかり、容量22,23により短い時間に大電流を流しているため、電荷を上記第1の実施の形態で示した図3より高速に充放電していることがわかる。

【0067】

以上のように、スイッチング素子1,11のゲートに接続された容量抵抗並列接続回路3,13の抵抗5,15に過剰な電流を流すことなく、高速かつ確実にオフするスイッチング回路20,21を提供できる。

【0068】

<半導体スイッチング回路を用いた半導体モジュールの実装形態>

前述した半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の実装形態について、図7を用いて説明する。図7は、この半導体スイッチング回路を用いた半導体モジュール(電力変換モジュール)の実装形態の一例を示すレイアウト図であり、(a)は表面を、(b)は裏面をそれぞれ示す。この図7は、前述した図5に記載したスイッチング回路20,21を含む半導体モジュール(電力変換モジュール)10を示している。

【0069】

図7に示す半導体モジュール(電力変換モジュール)10は、図4に示した半導体モジュール(電力変換モジュール)10に対して、スイッチング回路20,21のダイオード直列並列接続回路6,16にそれぞれ容量22,23が並列に追加されている。そのために、それぞれのダイオード直列並列接続回路6,16の各端部に接続された配線パターンが延長して形成され、この延長して形成された配線パターン間にそれぞれ容量22,23が実装されている。他の配線パターン、各端子などは、図4に示した半導体モジュール(電力変換モジュール)と同様である。

【0070】

スイッチング素子1,11、容量4,14,22,23、抵抗5,15、ダイオード直列接続回路7,17、ダイオード8,18はリード付き部品で構成してもよいが、スイッチング周波数が高くなると、電圧、電流波形の立ち上がり、立ち下がりを高速にする必要がある。この時、寄生成分によりスイッチングノイズが発生しやすいため、図7のように容量4,14,22,23、抵抗5,15は面実装部品で構成し、スイッチング素子1,11、ダイオード2,12、ダイオード直列並列接続回路6,16は半導体チップで構成するのが望ましい。スイッチング素子1,11の半導体チップは表面にゲート端子、ソース端子、裏面にドレイン端子、ダイオード2,12の半導体チップは表面にカソード端子、裏面にアノード端子が配置されている。図7中の符号は図5と同じであるため詳細な説明は省略する。

【0071】

ダイオード直列並列接続回路6,16は、アノード、カソードそれぞれにワイヤをボンディングするボンディングパッドを持つダイオードの直列接続回路を2列搭載しており、ダイオードの個数を選べるようにすることで、変換する電圧レベルを調整できるようにしてある。容量4,14、容量22,23、抵抗5,15はチップ部品である。

【0072】

以上の構成にすることで、スイッチング素子1のゲートとダイオード直列並列接続回路6の間、スイッチング素子11のゲートとダイオード直列並列接続回路16の間を小さい寄生成分で接続することができ、高速スイッチングが可能となる。

【0073】

<第2の実施の形態の効果>

以上説明した第2の実施の形態によれば、ダイオード直列並列接続回路6,16は、ダイオード直列接続回路7,17と並列に接続された容量22,23をさらに有することで、上記第1の実施の形態の効果に加えて、容量22,23により短い時間に大電流を流して、より一層、電荷を高速に充放電させることができるので、より一層、高速にスイッチング素子1,11をオンオフさせるスイッチング回路20,21、及びそれを用いた半導体モジュール(電力変換モジュール)10を実現することができる。

【0074】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

【0075】

本発明は、半導体スイッチング素子を有する半導体スイッチング回路、及びそれを用いた半導体モジュール、電力変換モジュールに利用可能である。

【符号の説明】

【0076】

1,11 スイッチング素子

2,12 ダイオード

3,13 容量抵抗並列接続回路

4,14 容量

5,15 抵抗

6,16 ダイオード直列並列接続回路

7,17 ダイオード直列接続回路

8,18 ダイオード

9 ゲート駆動用回路

10 半導体モジュール

19 コイル

20,21 スイッチング回路

22,23 容量

【特許請求の範囲】

【請求項1】

ドレイン端子、ソース端子、及びゲート端子を有する半導体スイッチング素子を有し、

前記半導体スイッチング素子のゲート端子とソース端子との間に、前記半導体スイッチング素子のゲート端子とソース端子との間に印加される電圧または電流によってドレイン端子とソース端子との間の導通及び非導通を制御するゲート駆動回路が接続される半導体スイッチング回路であって、

容量素子と抵抗素子とが並列に接続された第1回路と、

1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路と、

前記ダイオード直列接続回路のダイオードと逆方向に、前記ダイオード直列接続回路に並列に接続されたダイオードとを有する第2回路とを有し、

前記半導体スイッチング素子のゲート端子には前記第1回路の一端が接続され、

前記第1回路の他端と前記ゲート駆動回路の出力端子との間には、前記ダイオード直列接続回路の1つ以上のダイオードのアノード端子を前記ゲート駆動回路側に、前記ダイオード直列接続回路の1つ以上のダイオードのカソード端子を前記半導体スイッチング素子のゲート端子側にして、前記第2回路が接続されることを特徴とする半導体スイッチング回路。

【請求項2】

請求項1記載の半導体スイッチング回路において、

前記半導体スイッチング素子は、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタである

ことを特徴とする半導体スイッチング回路。

【請求項3】

請求項1記載の半導体スイッチング回路を1つ以上搭載している

ことを特徴とする半導体モジュール。

【請求項4】

請求項1記載の半導体スイッチング回路を2つ以上搭載している

ことを特徴とする電力変換モジュール。

【請求項5】

請求項1記載の半導体スイッチング回路において、

前記第2回路は、前記ダイオード直列接続回路と並列に接続された容量素子をさらに有する

ことを特徴とする半導体スイッチング回路。

【請求項6】

請求項5記載の半導体スイッチング回路において、

前記半導体スイッチング素子は、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタである

ことを特徴とする半導体スイッチング回路。

【請求項7】

請求項5記載の半導体スイッチング回路を1つ以上搭載している

ことを特徴とする半導体モジュール。

【請求項8】

請求項5記載の半導体スイッチング回路を2つ以上搭載している

ことを特徴とする電力変換モジュール。

【請求項1】

ドレイン端子、ソース端子、及びゲート端子を有する半導体スイッチング素子を有し、

前記半導体スイッチング素子のゲート端子とソース端子との間に、前記半導体スイッチング素子のゲート端子とソース端子との間に印加される電圧または電流によってドレイン端子とソース端子との間の導通及び非導通を制御するゲート駆動回路が接続される半導体スイッチング回路であって、

容量素子と抵抗素子とが並列に接続された第1回路と、

1つ以上のダイオードが順方向に直列に接続されたダイオード直列接続回路と、

前記ダイオード直列接続回路のダイオードと逆方向に、前記ダイオード直列接続回路に並列に接続されたダイオードとを有する第2回路とを有し、

前記半導体スイッチング素子のゲート端子には前記第1回路の一端が接続され、

前記第1回路の他端と前記ゲート駆動回路の出力端子との間には、前記ダイオード直列接続回路の1つ以上のダイオードのアノード端子を前記ゲート駆動回路側に、前記ダイオード直列接続回路の1つ以上のダイオードのカソード端子を前記半導体スイッチング素子のゲート端子側にして、前記第2回路が接続されることを特徴とする半導体スイッチング回路。

【請求項2】

請求項1記載の半導体スイッチング回路において、

前記半導体スイッチング素子は、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタである

ことを特徴とする半導体スイッチング回路。

【請求項3】

請求項1記載の半導体スイッチング回路を1つ以上搭載している

ことを特徴とする半導体モジュール。

【請求項4】

請求項1記載の半導体スイッチング回路を2つ以上搭載している

ことを特徴とする電力変換モジュール。

【請求項5】

請求項1記載の半導体スイッチング回路において、

前記第2回路は、前記ダイオード直列接続回路と並列に接続された容量素子をさらに有する

ことを特徴とする半導体スイッチング回路。

【請求項6】

請求項5記載の半導体スイッチング回路において、

前記半導体スイッチング素子は、閾値電圧が0V以上であるノーマリオフ特性を持つ接合型電界効果トランジスタである

ことを特徴とする半導体スイッチング回路。

【請求項7】

請求項5記載の半導体スイッチング回路を1つ以上搭載している

ことを特徴とする半導体モジュール。

【請求項8】

請求項5記載の半導体スイッチング回路を2つ以上搭載している

ことを特徴とする電力変換モジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−85409(P2013−85409A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−224553(P2011−224553)

【出願日】平成23年10月12日(2011.10.12)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成23年度、独立行政法人新エネルギー・産業技術総合開発機構、次世代パワーエレクトロニクス技術開発(グリーンITプロジェクト)/SiCパワーデバイスを用いたデータセンタ用サーバ電源技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月12日(2011.10.12)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成23年度、独立行政法人新エネルギー・産業技術総合開発機構、次世代パワーエレクトロニクス技術開発(グリーンITプロジェクト)/SiCパワーデバイスを用いたデータセンタ用サーバ電源技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]