半導体スイッチング素子の駆動回路

【課題】駆動電圧の印加に制限がある半導体スイッチング素子を高い周波数で高速にスイッチングできる駆動回路を提供する。

【解決手段】通電制御回路4が4つのスイッチS1〜S4とスイッチSa1及びSa2とを併せて制御することで、インダクタL1に電流を双方向に通電し、インダクタL1を介して流れる電流によりNチャネルFET1のゲートを充電し、また前記ゲートから放電させる。具体的にはダイオードDa1のカソードとダイオードDa2のアノードとの間に接続されるスイッチS1及びS2の直列回路と、コンデンサC1とコンデンサC2との間に接続され、共通接続点がNチャネルFET1のゲートに接続されるスイッチS3及びS4の直列回路とで構成し、インダクタL1を、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間に接続する。

【解決手段】通電制御回路4が4つのスイッチS1〜S4とスイッチSa1及びSa2とを併せて制御することで、インダクタL1に電流を双方向に通電し、インダクタL1を介して流れる電流によりNチャネルFET1のゲートを充電し、また前記ゲートから放電させる。具体的にはダイオードDa1のカソードとダイオードDa2のアノードとの間に接続されるスイッチS1及びS2の直列回路と、コンデンサC1とコンデンサC2との間に接続され、共通接続点がNチャネルFET1のゲートに接続されるスイッチS3及びS4の直列回路とで構成し、インダクタL1を、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間に接続する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、制御端子に印加する駆動電圧に制限がある駆動対象スイッチング素子を駆動するための駆動回路に関する。

【背景技術】

【0002】

例えばパワーMOSFET等のパワー系スイッチング素子については、動作時の安全性を確保するためノーマリーオフとなるように駆動制御することが求められている。シリコン系のMOSFETに比較すると大幅に低損失化が可能な次世代デバイスである、SiC(炭化ケイ素)−J(ジャンクション)FETやGaN(窒化ガリウム)−FETではノーマリーオフを実現することができる。しかしながら、これらのFETはSiのパワーMOSFETがゲートに10〜20Vの電圧を印加できるのに対し、数V(例えば、2〜3V程度)しか電圧をかけられないものが多い。そのようなデバイスでは高い電圧で駆動することができず、その結果高速にスイッチングさせることが難しい。

【0003】

ゲート電圧を制限する技術として、例えば特許文献1では、ゲート駆動用のトランジスタのエミッタとグランドとの間にゲート抵抗及びツェナーダイオードの直列回路を接続し、両者の共通接続点に静電誘導トランジスタのゲートを接続することで、ツェナー電圧によりゲート電圧をクランプしている。この構成では、静電誘導トランジスタをオンさせている間はツェナーダイオードを介して電流が流れ続けるので、駆動回路における損失が大きく、高周波数帯でのスイッチングに対応できない。

【0004】

また、特許文献2では、ゲート駆動回路として4つのスイッチング素子を用いてHブリッジと同様の回路を構成し、そのブリッジ回路によりインダクタを介してゲート電流を流す構成となっている。これにより、ゲート電圧に依存することなくMOSFETを高速にスイッチングすることが可能となり、駆動回路で発生する損失も小さくなる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3655049号公報(図11等参照)

【特許文献2】特許第4321330号公報(図14等参照)

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献2の構成でも、インダクタの通電電流を増加させるのに時間がかかるため、やはり高い周波数で行うスイッチングに対応できない。

本発明は上記事情に鑑みてなされたものであり、その目的は、駆動電圧の印加に制限があるスイッチング素子を高い周波数で高速にスイッチングできる半導体スイッチング素子の駆動回路を提供することにある。

【課題を解決するための手段】

【0007】

請求項1記載の半導体スイッチング素子の駆動回路によれば、通電制御回路が4つの通電用スイッチング素子と正側及び負側スイッチング素子とを併せて制御することで、インダクタに電流を双方向に通電し、インダクタを介して流れる電流により駆動対象スイッチング素子の制御端子を充電し、また前記制御端子から放電させる。そのために、通電制御回路は、(1)〜(8)の通電経路を形成可能に構成される。

すなわち、駆動対象スイッチング素子をターンオンする場合には、(1)で正側コンデンサを充電し、(2)で駆動用電源と正側コンデンサとを直列に接続して、駆動対象スイッチング素子の制御端子を充電する方向でインダクタに通電すると、(3)でインダクタに蓄積された電磁エネルギーによって駆動対象スイッチング素子の制御端子を充電する。これにより駆動対象スイッチング素子はターンオンする。そして、充電により制御端子の電位が駆動用電源の電圧よりも上昇すると(4)で駆動用電源側に還流電流を流す。

【0008】

一方、駆動対象スイッチング素子をターンオフする場合には、(5)で負側コンデンサを充電し、(6)で駆動用電源と負側コンデンサとを直列に接続し、駆動対象スイッチング素子の制御端子を放電させる方向でインダクタに通電すると、(7)でインダクタに蓄積された電磁エネルギーにより駆動対象スイッチング素子の制御端子から放電させる。これにより駆動対象スイッチング素子はターンオフする。そして、放電により制御端子の電位が駆動用電源の負側端子の電位よりも低下すると(8)で駆動用電源側に還流電流を流す。

【0009】

したがって、駆動対象スイッチング素子をターンオンする場合に、制御端子に過電圧を印加することを回避した上で、駆動用電源と充電した正側コンデンサとを直列に接続して得られる昇圧電圧に応じて流れる電流により、駆動対象スイッチング素子の制御端子を急速に充電して短時間でターンオンさせることができる。また、駆動対象スイッチング素子をターンオフする場合も、駆動用電源と充電した負側コンデンサとを直列に接続して、同様に制御端子から急速に放電させて短時間でターンオフさせることができる。

【0010】

請求項2記載の半導体スイッチング素子の駆動回路によれば、通電制御回路を、正側ダイオードのカソードと負側ダイオードのアノードとの間に接続される第1及び第2スイッチング素子の直列回路と、正側コンデンサと負側コンデンサとの間に接続され、共通接続点が駆動対象スイッチング素子の制御端子に接続される第3及び第4スイッチング素子の直列回路とで構成し、インダクタを、第1及び第2スイッチング素子の共通接続点と、第3及び第4スイッチング素子の共通接続点との間に接続する。このように構成すれば、正側及び負側スイッチング素子と、インダクタに対してHブリッジ状に接続される第1〜第4スイッチング素子のオンオフを制御することで、(1)〜(8)の通電経路を形成できる。

【0011】

請求項3記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を以下のように切り替えることで(1)〜(8)の通電経路を形成する。(0)初期状態を、正側及び負側スイッチング素子がオン,第4スイッチング素子がオンである駆動対象スイッチング素子のターンオフ状態とすると、(1)正側スイッチング素子をターンオフしてから、第3スイッチング素子をターンオンする。これにより、駆動用電源(+),正側ダイオード,正側コンデンサ,第3及び第4スイッチング素子,負側スイッチング素子,駆動用電源(−)の経路で、正側コンデンサが(VG−Vf)に充電される。尚、VGは駆動用電源の電圧,Vfはダイオードの順方向電圧とする。

【0012】

次に、(2)第3スイッチング素子をターンオフしてから、正側スイッチング素子をターンオンし、更に第1スイッチング素子をターンオンすると、駆動用電源(+),正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタ,第4スイッチング素子,負側スイッチング素子,駆動用電源(−)の経路が形成される。これにより、インダクタには(2VG−Vf)の電圧で通電が行われる。

【0013】

この状態から、(3)第4スイッチング素子をターンオフすると、駆動用電源(+),正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタ,駆動対象スイッチング素子の制御端子及び電位基準側出力端子,負側スイッチング素子,駆動用電源(−)の経路が形成される(尚、電位基準側出力端子は、駆動対象スイッチング素子の電圧型によっては駆動用電源の正側端子に接続されることがある)。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流によって充電されて制御端子の電位が上昇し、駆動対象スイッチング素子はターンオン状態に移行する。

【0014】

制御端子の電位Vgsが上昇して(Vgs>VG)になると、インダクタ,第3スイッチング素子の還流ダイオード,正側コンデンサ,第1スイッチング素子,インダクタの経路で還流電流が流れる。したがって、制御端子の電位Vgsは、電源電圧VGによってクランプされる。その状態で、(4)第1スイッチング素子をターンオフ,第3スイッチング素子をターンオンすると、インダクタ,第3スイッチング素子,正側スイッチング素子,駆動用電源,負側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路が形成される。これにより、還流電流は駆動用電源に回生され、インダクタを介して流れる電流がゼロになると、駆動対象スイッチング素子のターンオン動作が完了する。

【0015】

一方、駆動対象スイッチング素子をターンオフさせる場合は、(5)負側スイッチング素子をターンオフしてから、第4スイッチング素子をターンオンする。これにより、駆動用電源(+),正側スイッチング素子,第3及び第4スイッチング素子,負側コンデンサ,負側ダイオード,駆動用電源(−)の経路で、負側コンデンサが(VG−Vf)に充電される。

次に、(6)第4スイッチング素子をターンオフしてから、負側スイッチング素子をターンオンし、更に第2スイッチング素子をターンオンすると、駆動用電源(+),正側スイッチング素子,第3スイッチング素子,インダクタ,第2スイッチング素子,負側コンデンサ,負側スイッチング素子,駆動用電源(−)の経路が形成される。これにより、インダクタには(2VG−Vf)の電圧で、(2)とは逆方向に通電が行われる。

【0016】

この状態から、(7)第3スイッチング素子をターンオフすると、駆動対象スイッチング素子の制御端子,インダクタ,第2スイッチング素子,負側コンデンサ,駆動対象スイッチング素子の電位基準側出力端子となる経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流により放電されて制御端子の電位が低下し、駆動対象スイッチング素子はターンオフ状態に移行する。

【0017】

制御端子の電位Vgsが低下して(Vgs<(駆動用電源(−)の電位)になると、インダクタ,第2スイッチング素子,負側コンデンサ,第4スイッチング素子の還流ダイオード,インダクタとなる経路で還流電流が流れる。したがって、制御端子の電位Vgsは、駆動用電源(−)の電位によってクランプされる。その状態で、(8)第2スイッチング素子をターンオフし、第4スイッチング素子をターンオンすると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側スイッチング素子,駆動用電源,負側スイッチング素子,第4スイッチング素子,インダクタとなる経路が形成される。これにより、還流電流は駆動用電源に回生され、インダクタを介して流れる電流がゼロになると、駆動対象スイッチング素子のターンオフ動作が完了する。

【0018】

請求項4記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を切り替えることで(1)〜(8)の通電経路を形成するが、請求項3と異なる部分を説明する。請求項4では、駆動対象スイッチング素子をターンオンさせる場合、(3)で第1及び第4スイッチング素子をターンオフする。これにより、インダクタ,駆動対象スイッチング素子の制御端子及び電位基準側出力端子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタとなる経路が形成され、駆動対象スイッチング素子はターンオン状態に移行する。この時、負側コンデンサには充電電流が流れるので、その端子電圧は電源電圧VGを超えて上昇する。

【0019】

そして、制御端子の電位Vgsが上昇して(Vgs>VG)になると、インダクタ,第3スイッチング素子の還流ダイオード,正側スイッチング素子,駆動用電源,負側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路が形成される。これにより、還流電流は駆動用電源に回生され、制御端子の電位Vgsは電源電圧VGによってクランプされる。この時も、負側コンデンサには充電電流が流れるので、端子電圧は上昇を続ける。また、続く(4)では第3スイッチング素子だけをターンオンするので、これにより、請求項3の(4)と同じ通電経路が形成される。この時も、負側コンデンサは充電されて端子電圧は上昇を続ける。

【0020】

一方、駆動対象スイッチング素子をターンオフさせる場合は、(7)で第2及び第3スイッチング素子をターンオフする。すると、駆動対象スイッチング素子の制御端子,インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側スイッチング素子,駆動用電源,負側スイッチング素子,駆動対象スイッチング素子の電位基準側出力端子となる経路が形成される。これにより、駆動対象スイッチング素子はターンオフ状態に移行し、還流電流は駆動電源側に回生される。この時、正側コンデンサには充電電流が流れるので、その端子電圧は電源電圧VGを超えて上昇する。

【0021】

そして、制御端子の電位Vgsが<(駆動用電源(−)の電位)になると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側スイッチング素子,駆動用電源,負側スイッチング素子,第3スイッチング素子の還流ダイオード,インダクタとなる経路で還流電流が流れる。したがって、制御端子の電位Vgsは、駆動用電源(−)の電位によってクランプされる。この時も、正側コンデンサには充電電流が流れるので端子電圧は上昇を続ける。その状態で(8)第4スイッチング素子をターンオンすると、請求項3の(8)と同じ通電経路が形成される。この時も、正側コンデンサは充電されて端子電圧は上昇を続ける。

すなわち、請求項4によれば、正側及び負側コンデンサが充電される期間が請求項3より長くなるので、それらの端子電圧を電源電圧VGよりも高くすることができ、それにより駆動対象スイッチング素子のターンオン,ターンオフをより高速に行うことができる。

【0022】

請求項5記載の半導体スイッチング素子の駆動回路によれば、請求項3において(1)〜(8)の通電経路を形成するパターンと、それらのうち(3),(4),(7),(8)の通電経路を(3)’,(4)’,(7)’,(8)’の通電経路に置き換えて形成するパターンとを切り替える。ここで、(3)’,(4)’,(7)’,(8)’の通電経路は、それぞれ請求項4における(3),(4),(7),(8)の通電経路に等しい。すなわち、請求項5では、請求項3における(1)〜(8)の通電経路の形成パターンと、請求項4における(1)〜(8)の通電経路の形成パターンとを切り替えて行う。尚、ここでのパターンの切替えは、前者と後者とを1回以上ずつ交互に実行することを言う。また、必ずしも両者の連続実行回数が等しくなくても良い。これにより、請求項3の放電期間がより長いパターンと、請求項4の充電期間がより長いパターンとを適宜組み合わせて実行することで、必要に応じて正側及び負側コンデンサの端子電圧を駆動電源電圧よりも高くしたり、或いは、前記端子電圧が一定となるように調整できる。

【0023】

請求項6記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を切り替えることで(1)〜(8)の通電経路を形成するが、やはり請求項3と異なる部分を説明する。請求項5では、(4)で第1スイッチング素子をターンオフしてから,第3スイッチング素子をターンオンする。また、(8)では、第2スイッチング素子をターンオフしてから、第4スイッチング素子をターンオンする。

これにより、駆動対象スイッチング素子をターンオンさせる場合の第1スイッチング素子のオン期間,並びに駆動対象スイッチング素子をターンオフさせる場合の第2スイッチング素子のオン期間は、請求項3のケースと、請求項4のケースとの中間となる。したがって、正側及び負側コンデンサが充電される期間が両者の中間になる。

【0024】

そして、請求項7記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(3)の通電経路を形成してから(4)の通電経路において第1スイッチング素子をターンオフさせるまでの期間長と、(7)の通電経路を形成してから(8)の通電経路において第2スイッチング素子をターンオフさせるまでの期間長とを調整することで、正側及び負側コンデンサの端子電圧を調整する。したがって、必要に応じて正側及び負側コンデンサの端子電圧を駆動電源電圧よりも高くしたり、或いは、前記端子電圧が一定となるように調整できる。

【0025】

請求項8記載の半導体スイッチング素子の駆動回路によれば、正側コンデンサと負側コンデンサとを直列に接続する構成とし、通電制御回路は、正側及び負側コンデンサと並列に接続される、第1及び第2スイッチング素子の直列回路と、駆動用電源と並列に接続される第3及び第4スイッチング素子の直列回路とで構成して、インダクタを、第1及び第2スイッチング素子の共通接続点と、第3及び第4スイッチング素子の共通接続点との間に接続する。このように構成すれば、正側及び負側スイッチング素子と、インダクタに対してHブリッジ状に接続された第1〜第4スイッチング素子(但し、第1及び第2スイッチング素子は、それぞれ正側及び負側ダイオードを介して駆動用電源に接続される)のオンオフを制御することで、(1)〜(8)の通電経路を形成できる。

【0026】

請求項9記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(2)の通電経路を形成する前にも(5)の通電経路を形成し、(6)の通電経路を形成する前にも(2)の通電経路を形成する。これにより、駆動対象スイッチング素子のターンオン動作を開始させる場合と、駆動対象スイッチング素子のターンオフ動作を開始させる場合とのそれぞれについて、予め正側及び負側コンデンサを充電することができる。

【0027】

請求項10記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(1)〜(8)の通電経路を形成する。(0)初期状態を、第4スイッチング素子がオンである駆動対象スイッチング素子のターンオフ状態とすると、先ず(1)負側スイッチング素子をオンすることで、駆動用電源(+),正側ダイオード,正側コンデンサ,負側スイッチング素子,駆動用電源(−)となる経路が形成され、正側コンデンサが(VG−Vf)に充電される。

【0028】

次に(5)負側スイッチング素子をターンオフしてから、正側スイッチング素子をターンオンすると、今度は駆動用電源(+),正側スイッチング素子,負側コンデンサ,負側ダイオード,駆動用電源(−)となる経路が形成され、負側コンデンサが(VG−Vf)に充電される。(2)で第1スイッチング素子をターンオンすると、駆動用電源(+),正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタ,第4スイッチング素子,駆動用電源(−)となる経路が形成され、これにより、インダクタには(2VG−Vf)の電圧で通電が行われる。

【0029】

この状態から、(3)第4スイッチング素子をターンオフすると、駆動用電源(+),正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタ,駆動対象スイッチング素子の制御端子及び電位基準側出力端子,駆動用電源(−)の経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流によって充電されて制御端子の電位が上昇し、駆動対象スイッチング素子はターンオン状態に移行する。

制御端子の電位Vgsが上昇して(Vgs>VG)になると、インダクタ,第3スイッチング素子の還流ダイオード,正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタの経路で還流電流が流れる。したがって、制御端子の電位Vgsは、電源電圧VGによってクランプされる。

【0030】

その状態で、(4)正側スイッチング素子及び第1スイッチング素子をターンオフ,第3スイッチング素子をターンオンすると、インダクタ,第3スイッチング素子,駆動用電源,負側ダイオード,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタとなる経路が形成される。これにより、還流電流は駆動用電源に回生され、インダクタを介して流れる電流がゼロになると、駆動対象スイッチング素子のターンオン動作が完了する。

【0031】

一方、駆動対象スイッチング素子をターンオフさせる場合は、(5)正側スイッチング素子をターンオンして負側コンデンサを充電し、次に(2)正側スイッチング素子をターンオフしてから、負側スイッチング素子をターンオンして正側コンデンサを充電する。それから、(6)第2スイッチング素子をターンオンすると、駆動用電源(+),第3スイッチング素子,インダクタ,第2スイッチング素子,負側コンデンサ,負側スイッチング素子,駆動用電源(−)の経路が形成される。これにより、インダクタには(2VG−Vf)の電圧で、(2)とは逆方向に通電が行われる。

この状態から、(7)第3スイッチング素子をターンオフすると、駆動対象スイッチング素子の制御端子,インダクタ,第2スイッチング素子,負側コンデンサ,負側スイッチング素子,駆動対象スイッチング素子の電位基準側出力端子となる経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流により放電されて制御端子の電位が低下し、駆動対象スイッチング素子はターンオフ状態に移行する。

【0032】

制御端子の電位Vgsが低下して(Vgs<(駆動用電源(−)の電位)になると、インダクタ,第2スイッチング素子,負側コンデンサ,負側スイッチング素子,第4スイッチング素子の還流ダイオード,インダクタとなる経路で還流電流が流れる。したがって、制御端子の電位Vgsは、駆動用電源(−)の電位によってクランプされる。その状態で、(8)負側スイッチング素子及び第2スイッチング素子をターンオフ,第4スイッチング素子をターンオンすると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側ダイオード,駆動用電源,第4スイッチング素子,インダクタとなる経路が形成される。これにより、還流電流は駆動用電源に回生され、インダクタを介して流れる電流がゼロになると、駆動対象スイッチング素子のターンオフ動作が完了する。

【0033】

請求項11記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を切り替えることで(1)〜(8)の通電経路を形成するが、請求項10と異なる部分を説明する。請求項11では、(3)で第1及び第4スイッチング素子をターンオフさせる。すると、駆動用電源(+),正側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタ,駆動対象スイッチング素子の制御端子及び電位基準側出力端子,駆動用電源(−)の経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流によって充電されて制御端子の電位が上昇し、駆動対象スイッチング素子はターンオン状態に移行する。

【0034】

制御端子の電位Vgsが上昇して(Vgs>VG)になると、インダクタ,第3スイッチング素子の還流ダイオード,正側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路で還流電流が流れる。したがって、制御端子の電位Vgsは、電源電圧VGによってクランプされる。そして、(4)で正側スイッチング素子をターンオフ,第3スイッチング素子をターンオンさせると、請求項9の(4)と同様の経路が形成される。

【0035】

また、(7)では第2及び第3スイッチング素子をターンオフさせる。すると、駆動対象スイッチング素子の制御端子,インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,負側スイッチング素子,駆動対象スイッチング素子の電位基準側出力端子となる経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流により放電されて制御端子の電位が低下し、駆動対象スイッチング素子はターンオフ状態に移行する。

【0036】

制御端子の電位Vgsが低下して(Vgs<(駆動用電源(−)の電位)になると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,負側スイッチング素子,第4スイッチング素子の還流ダイオード,インダクタとなる経路で還流電流が流れる。したがって、制御端子の電位Vgsは、駆動用電源(−)の電位によってクランプされる。その状態で、(8)負側スイッチング素子をターンオフ,第4スイッチング素子をターンオンすると、請求項9の(8)と同様の経路が形成される。

【0037】

請求項12記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(4)の通電経路の形成した後、インダクタを介して流れる電流がゼロになる時間が経過する以前に(5)の通電経路を形成する。これにより、負側コンデンサを充電する時間がより長くなる。また、(8)の通電経路の形成した後、インダクタを介して流れる電流がゼロになる時間が経過する以前に負側スイッチング素子をターンオンする。これにより、正側コンデンサを充電する時間が請求項11よりも長くなる。したがって、正側及び負側コンデンサの端子電圧をより高くすることができる。

【0038】

請求項13記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(4)の通電経路において正側スイッチング素子をターンオフしてから(5)の通電経路において正側スイッチング素子をターンオンするまでの期間長と、(8)の通電経路において負側スイッチング素子をターンオフしてから次回に行う(1)の通電経路において負側スイッチング素子をターンオンするまでの期間長とを調整することで、正側及び負側コンデンサの端子電圧を調整する。したがって、正側及び負側コンデンサの端子電圧をより高くしたり、一定に維持する等の制御が可能となる。

【0039】

請求項14記載の半導体スイッチング素子の駆動回路によれば、請求項10において(1)〜(8)の通電経路を形成するパターンと、それらのうち(3),(4),(7),(8)の通電経路を(3)’,(4)’,(7)’,(8)’の通電経路に置き換えて形成するパターンとを切り替える。ここで、(3)’,(4)’,(7)’,(8)’の通電経路は、それぞれ請求項11における(3),(4),(7),(8)の通電経路に等しい。すなわち、請求項14では、請求項10における(1)〜(8)の通電経路の形成パターンと、請求項11における(1)〜(8)の通電経路の形成パターンとを切り替えて行う。尚、ここでのパターンの切替えは、前者と後者とを1回以上ずつ交互に実行することを言う。また、必ずしも両者の連続実行回数が等しくなくても良い。これにより、請求項10の放電期間がより長いパターンと、請求項11の充電期間がより長いパターンとを適宜組み合わせて実行することで、必要に応じて正側及び負側コンデンサの端子電圧を駆動電源電圧よりも高くしたり、或いは、前記端子電圧が一定となるように調整できる。

【0040】

請求項15記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を切り替えることで(1)〜(8)の通電経路を形成するが、請求項9と異なる部分を説明する。請求項13では、(4)で第1スイッチング素子をターンオフ,第3スイッチング素子をターンオンする。すると、インダクタ,第3スイッチング素子の,正側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路で還流電流が流れる。したがって、負側コンデンサが充電される。

【0041】

そして、次の(5)では、正側スイッチング素子をターンオフしてから正側スイッチング素子をターンオンする。正側スイッチング素子をターンオフすると、インダクタ,第3スイッチング素子,駆動用電源,負側ダイオード,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路で還流電流が流れる。したがって、この時も負側コンデンサが充電される。その後、コンデンサを介して流れる電流がゼロになった後に正側スイッチング素子をターンオンすれば、続く(2)の経路を形成するために備えることができる。

【0042】

また、(8)では、第2スイッチング素子をターンオフ,第4スイッチング素子をターンオンしてから、負側スイッチング素子をターンオフする。第2スイッチング素子をターンオフ,第4スイッチング素子をターンオンすると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,負側スイッチング素子,第4スイッチング素子の経路で還流電流が流れ、正側コンデンサが充電される。その後、負側スイッチング素子をターンオフすると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側ダイオード,駆動用電源,第4スイッチング素子、インダクタの経路で還流電流が流れ、この時も正側コンデンサが充電される。したがって、正側及び負側コンデンサの端子電圧をより上昇させることができる。

【0043】

請求項16記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(5)の通電経路において正側スイッチング素子をターンオフしてから正側スイッチング素子をターンオンするまでの期間長と、(8)の通電経路において負側スイッチング素子をターンオフしてから、次回に行う(1)の通電経路において負側スイッチング素子をターンオンするまでの期間長とを調整することで、正側及び負側コンデンサの端子電圧を調整する。したがって、正側及び負側コンデンサの端子電圧をより上昇させたり一定に維持する等の制御が可能となる。

【図面の簡単な説明】

【0044】

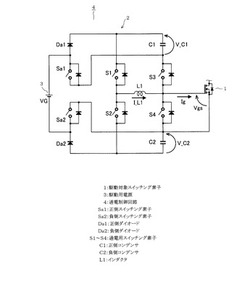

【図1】第1実施例であり、駆動回路の電気的構成を示す図

【図2】タイミングチャート

【図3】NチャネルFETのターンオン時における通電経路の遷移状態を示す図

【図4】同ターンオフ時における図3相当図

【図5】第2実施例を示す図2相当図

【図6】図3の一部相当図

【図7】図4の一部相当図

【図8】インダクタに流れる電流とコンデンサC1,C2の充電電荷.放電電荷との関係を示す図

【図9】第3実施例を示す図2相当図

【図10】図8相当図

【図11】第4実施例を示す図1相当図

【図12】図2相当図

【図13】図3相当図

【図14】図4相当図

【図15】第5実施例を示す図12相当図

【図16】図13の一部相当図

【図17】図14の一部相当図

【図18】第6実施例を示す図12相当図

【図19】図13の一部相当図

【図20】図14の一部相当図

【図21】図8相当図

【図22】第7実施例を示す図12相当図

【図23】図13の一部相当図

【図24】図14の一部相当図

【図25】図8相当図

【発明を実施するための形態】

【0045】

(第1実施例)

以下、第1実施例について図1ないし図4を参照して説明する。図1は、例えばNチャネルFETを駆動するための駆動回路を示す。NチャネルFET1(駆動対象スイッチング素子)は、ドレイン側に図示しない負荷が接続されており、駆動回路2は、NチャネルFET1のゲート−ソース間に接続されている(ローサイド駆動方式)。尚、NチャネルFET1については、FETをMOS構造に限定する意図ではないが、図中では便宜上MOSFETのシンボルで図示している。駆動回路2は、ゲート駆動用電源3により供給される電源VGに基づいて、NチャネルMOSFET2のゲート(制御端子)に対して充放電電流Igを供給する。尚、図1に示すスイッチのシンボルとダイオードとの並列回路は、実体としては例えばNチャネルMOSFET(ダイオードは寄生ダイオード)であるが、説明を簡単にするため上記のシンボルで示している。

【0046】

ゲート駆動用電源3の正側端子は、スイッチSa1(正側スイッチング素子)とダイオードDa1(正側ダイオード)との直列回路の共通接続点(アノード)に接続されており、負側端子は、スイッチSa2(負側スイッチング素子)とダイオードDa2(負側ダイオード)との直列回路の共通接続点(カソード)に接続されている。ダイオードDa1のカソードと、ダイオードDa2のアノードとの間には、スイッチS1及びS2(通電用スイッチング素子)の直列回路と、コンデンサC1(正側コンデンサ),スイッチS3及びS4(通電用スイッチング素子),コンデンサC2(負側コンデンサ)の直列回路とが接続されている。

【0047】

そして、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間には、インダクタL1が接続されている。また、スイッチS3及びS4の共通接続点は、NチャネルFET1のゲートに接続されており、NチャネルFET1のソース(電位基準側出力端子)はゲート駆動用電源3の負側端子に接続されている。スイッチS1〜S4には、それぞれについて並列に、ゲート駆動用電源3の極性に対して逆方向となるダイオード(還流ダイオード)が接続されている。スイッチSa1,Sa2,S1〜S4のオンオフ制御は、図示しない制御回路によって行われる。ここで、スイッチS1〜S4と前記制御回路とが通電制御回路4を構成している。

【0048】

次に、本実施例の作用について図2ないし図4も参照して説明する。図2は、制御回路によって行われるスイッチSa1,Sa2,S1〜S4のオンオフ切替えと、各部の電圧,電流波形を示すタイミングチャートである。また、図3は、NチャネルFET1をターンオンさせる場合のスイッチSa1,Sa2,S1〜S4の切替え順序と、それに伴う電流の流れを示したものである。

【0049】

<NチャネルFET1のターンオン>

図3において、先ず(1)(図2〜図4中の丸数字を、括弧付き数字で示す)初期状態として、スイッチSa1及びSa2,S4がオンしてNチャネルFET1のゲートはゲート駆動用電源3の負側端子の電位(例えば0V,グランド電位)となっており、ターンオフ状態にあるとする。ここから、(2)スイッチSa1をターンオフし、続いて(3)スイッチS3をターンオンすると、ゲート駆動用電源3の正側端子,ダイオードDa1,コンデンサC1,スイッチS3及びS4,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC1が駆動電圧(VG−Vf)に充電される。

【0050】

次に、(4)スイッチS3をターンオフした後、スイッチSa1をターンオンし、(5)更にスイッチS1をターンオンすると、ゲート駆動用電源3の正側端子,スイッチSa1,コンデンサC1,スイッチS1及びS4,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC1がゲート駆動用電源3と直列に接続される。これにより、インダクタL1には電圧(2VG−Vf)が印加され、電流I_L1が増加する。この状態から、(6)スイッチS4をターンオフすると、インダクタンスL1に蓄積された電磁エネルギーも含む電流I_L1がNチャネルFET1のゲートに電流Igとして流れ、当該ゲートを充電する。

【0051】

すると、NチャネルFET1のゲート−ソース間電圧Vgsが上昇し、電圧Vgsが電圧VGよりも上昇すると、(7)電流I_L1はスイッチS3の還流ダイオード,コンデンサC1,スイッチS1を介して流れる。これにより、電圧Vgsは、電圧VGにクランプされる。この状態から、(8)スイッチS1をターンオフし、スイッチS3をターンオンすると、電流I_L1は、スイッチS3及びSa1,ゲート駆動電源3,スイッチSa2,コンデンサC2,スイッチS2の還流ダイオード,インダクタL1の経路で流れ、ゲート駆動電源3側に回生される。そして、(9)電流I_L1がゼロになれば、NチャネルFET1のターンオンが完了する。

【0052】

<NチャネルFET1のターンオフ>

(1)上記のようにNチャネルFET1がターンオンしている状態から、(2)スイッチSa2をターンオフし、(3)更にスイッチS4をターンオンすると、ゲート駆動用電源3の正側端子,スイッチSa1,スイッチS3及びS4,コンデンサC2,ダイオードDa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC2が駆動電圧(VG−Vf)に充電される。

【0053】

次に、(4)スイッチS4をターンオフした後、スイッチSa2をターンオンし、(5)更にスイッチS2をターンオンすると、ゲート駆動用電源3の正側端子,スイッチSa1,スイッチS3及びS2,コンデンサC2,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC2がゲート駆動用電源3と直列に接続される。これにより、インダクタL1には電圧(2VG−Vf)が印加され、NチャネルFET1のターンオン時とは逆の方向に電流I_L1が増加する。この状態から、(6)スイッチS3をターンオフすると、電流I_L1がNチャネルFET1のゲートから電流Igとして流れ、当該ゲートを放電させる。

【0054】

すると、NチャネルFET1のゲート−ソース間電圧Vgsが低下し、電圧Vgs<0Vになると、(7)電流I_L1はスイッチS2,コンデンサC2,スイッチS4の還流ダイオードを介して流れる。これにより、電圧Vgsは0Vにクランプされる。この状態から、(8)スイッチS2をターンオフし、スイッチS4をターンオンすると、電流I_L1は、スイッチS1の還流ダイオード,コンデンサC1,スイッチSa1,ゲート駆動電源3,スイッチSa2,スイッチS4,インダクタL1の経路で流れ、ゲート駆動電源3側に回生される。そして、(9)電流I_L1がゼロになれば、NチャネルFET1のターンオフが完了する。

【0055】

以上のように本実施例によれば、通電制御回路4が4つのスイッチS1〜S4とスイッチSa1及びSa2とを併せて制御することで、インダクタL1に電流を双方向に通電し、インダクタL1を介して流れる電流によりNチャネルFET1のゲートを充電し、また前記ゲートから放電させるようにした。より具体的には、通電制御回路4を、ダイオードDa1のカソードとダイオードDa2のアノードとの間に接続されるスイッチS1及びS2の直列回路と、コンデンサC1とコンデンサC2との間に接続され、共通接続点がNチャネルFET1のゲートに接続されるスイッチS3及びS4の直列回路とで構成し、インダクタL1を、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間に接続する。したがって、スイッチSa1及びSa2と、インダクタL1に対してHブリッジ状に接続されたスイッチS1〜S4のオンオフを制御することで、上述したように請求項1における(1)〜(8)に対応した通電経路を形成できる。

【0056】

(第2実施例)

図5ないし図8は第2実施例を示すものであり、第1実施例と同一部分には同一符号を付して説明を省略し、以下異なる部分について説明する。第2実施例の構成は第1実施例と同様であり、スイッチの一部のオンオフタイミングが異なっている。図5は図2相当図であり、図6,図7は図3,図4の一部相当図である。

【0057】

<NチャネルFET1のターンオン>

図6に示す(6),(8)のスイッチングパターンが第1実施例と相違している。また、(6)のスイッチングパターンが相違することで(7)の通電経路も変化している。(6)では、スイッチS4と共にスイッチS1もターンオフさせている。この時、電流I_L1,NチャネルFET1のゲートを充電する電流Igは、インダクタンスL1,NチャネルFET1のゲート−ソース,コンデンサC2,スイッチS2の還流ダイオードの経路で流れる。これにより、コンデンサC2が充電される。ここで、(1)〜(5)の期間ではコンデンサC2は放電されないため、前記期間のコンデンサC2の端子電圧がVGであれば、(6)において当該端子電圧はVGを超えて上昇する。

【0058】

そして、ゲート−ソース間電圧Vgsが電圧VGよりも上昇すると、(7)電流I_L1はスイッチS3の還流ダイオード,スイッチSa1,ゲート駆動用電源3,スイッチSa2,コンデンサC2,スイッチS2の還流ダイオードを介して流れるので、この時もコンデンサC2が充電される。その結果、図5に示すように、コンデンサC2の電位V_C2は、(7)の期間も上昇を続ける。この状態からスイッチS3をターンオンすれば、図3に示す(8)と同じ状態になる。

【0059】

<NチャネルFET1のターンオフ>

この場合も、図7に示す(6),(8)のスイッチングパターンが第1実施例と相違している。(6)では、スイッチS3と共にスイッチS2もターンオフさせている。この時、電流I_L1,NチャネルFET1のゲートを放電させる電流Igは、インダクタンスL1,スイッチS1の還流ダイオード,コンデンサC1,スイッチSa1,ゲート駆動用電源3,スイッチSa2,NチャネルFET1のソース−ゲートの経路で流れる。これにより、コンデンサC1が充電される。

【0060】

そして、ゲート−ソース間電圧Vgsが0Vよりも低下すると、(7)電流I_L1はスイッチS1の還流ダイオード,コンデンサC1,スイッチSa1,ゲート駆動用電源3,スイッチSa2,スイッチS4の還流ダイオードを介して流れる。したがって、この時もコンデンサC1が充電される。その結果、図5に示すように、コンデンサC1の電位V_C1は電源電圧VGよりも上昇する。この状態からスイッチS4をターンオンすれば、図4に示す(8)と同じ状態になる。

【0061】

ここで、第1実施例と第2実施例との相違について、図8を参照して説明する。図8(a)は図2に示す電流I_L1の波形であり、図8(b)は図5に示す電流I_L1の波形である。第1実施例の場合、ターンオン時における電流I_L1の上昇期間が長く、下降期間が短い。前者(波形で規定される面積,積分量が対応)はコンデンサC1の放電電荷量を規定し、後者はコンデンサC2の充電電荷量を規定する。

一方、ターンオフ時については、負極性の電流I_L1の上昇期間が長く、下降期間が短いが、前者はコンデンサC2の放電電荷量を規定し、後者はコンデンサC1の充電電荷量を規定する。結果として、コンデンサC1,C2の何れについても(放電電荷量)>(充電電荷量)となっており、第1実施例のスイッチングパターンでは、コンデンサC1,C2の端子電圧V_C1,V_C2は低下することになる。

【0062】

第2実施例の場合、ターンオン時における電流I_L1の上昇期間が短く、下降期間が長い。また、ターンオフ時については、負極性の電流I_L1の上昇期間が短く、下降期間が長い。その結果、コンデンサC1,C2の何れについても(放電電荷量)<(充電電荷量)となっており、第2実施例のスイッチングパターンでは、コンデンサC1,C2の端子電圧V_C1,V_C2は上昇することになる。したがって、コンデンサC1,C2の端子電圧V_C1,V_C2を例えば一定に維持する等のように調整するには、第1実施例の制御パターンと第2実施例の制御パターンとを組み合わせる必要がある。それについて、次の第3実施例で説明する。

【0063】

(第3実施例)

図9及び図10は第3実施例を示すものである。図9に示すように、第3実施例では、スイッチS1がターンオフするタイミングが、(6)においてスイッチS4がターンオフするタイミングと、(8)においてスイッチS3がターンオンするタイミングとの間に位置しており、これは、第1実施例よりも長く、第2実施例よりも短くなっている。すなわち、第1実施例では、スイッチS1のターンオフタイミングが(8)に一致しており、第2実施例では同タイミングが(6)に一致している。

これにより、図10に示すように、コンデンサC1、C2の充放電電荷量を調整し、(放電電荷量)≒(充電電荷量)とすることで端子電圧V_C1,V_C2を一定に維持することができる。或いは、例えばある制御周期では、コンデンサC1,C2の充電電荷量をより多くして端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させることも可能となる。

【0064】

また、第3実施例とは異なり、例えば、第1実施例において、NチャネルFET1のターンオン,ターンオフ時に(1)〜(8)の通電経路を形成するパターンと、それらのうちターンオン,ターンオフ時それぞれの(6),(8)の通電経路を、第2実施例の(6),(8)の通電経路に置き換えて形成するパターンとを切り替えて実行しても良い。すなわち、第1実施例における通電経路の形成パターンと、第2実施例における通電経路の形成パターンとを切り替えて行う。尚、ここでのパターンの切替えは、前者と後者とを1回以上ずつ交互に実行することを言う。また、必ずしも両者の連続実行回数が等しくなくても良い。

【0065】

これにより、第1実施例の放電期間がより長いパターンと、第2実施例の充電期間がより長いパターンとを適宜組み合わせて実行することで、必要に応じて端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させたり、或いは端子電圧V_C1,V_C2を一定に維持するように調整することができる。尚、必要であれば、図示しない制御回路に、端子電圧V_C1,V_C2をA/D変換してモニタするような電圧計測手段を設ければ良い。

【0066】

(第4実施例)

図11ないし図14は第4実施例であり、第1実施例と異なる部分について説明する。図11に示す駆動回路11は、駆動回路2と同じ回路素子で構成されているが、それらの接続形態が一部相違している。スイッチS3及びS4の直列回路は、ゲート駆動用電源3の両端に直結されている。また、スイッチSa1及びSa2も直列に接続されており、ダイオードDa1のカソードと、ダイオードDa2のアノードとの間には、コンデンサC1及びC2の直列回路と、スイッチS1及びS2の直列回路とが並列に接続されている。そして、スイッチS1〜S4と図示しない制御回路とが通電制御回路12を構成している。

【0067】

次に、第4実施例の作用について図12ないし図14を参照して説明する。

<NチャネルFET1のターンオン>

図13において、先ず(1)初期状態として、スイッチSa2,S4がオンしてNチャネルFET1のゲートはグランド電位となっており、ターンオフ状態にあるとする。この状態で、コンデンサC1は電圧(VG−Vf)に充電される。ここから、(2)スイッチSa2をターンオフし、スイッチSa1をターンオンすると、コンデンサC2が電圧(VG−Vf)に充電される。

【0068】

次に、(3)スイッチS1をターンオンすると、ゲート駆動用電源3の正側端子,スイッチSa1,コンデンサC1,スイッチS1及びS4,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC1がゲート駆動用電源3と直列に接続される。これにより、インダクタL1には電圧(2VG−Vf)が印加され、電流I_L1が増加する。この状態から、(4)スイッチS4をターンオフすると、インダクタンスL1に蓄積された電磁エネルギーも含む電流I_L1がNチャネルFET1のゲートに電流Igとして流れ、当該ゲートを充電する。

【0069】

すると、NチャネルFET1のゲート−ソース間電圧Vgsが上昇し、電圧Vgsが電圧VGよりも上昇すると、(5)電流I_L1はスイッチS3の還流ダイオード,スイッチSa1,コンデンサC1,スイッチS1を介して流れる。これにより、電圧Vgsは、電圧VGにクランプされる。この状態から、(6)スイッチSa1及びS1をターンオフし、スイッチS3をターンオンすると、電流I_L1は、スイッチS3,ゲート駆動電源3,スイッチSa2の還流ダイオード,コンデンサC2,スイッチS2の還流ダイオード,インダクタL1の経路で流れ、ゲート駆動電源3側に回生される。そして、(7)電流I_L1がゼロになればNチャネルFET1のターンオンが完了し、(8)スイッチSa1をターンオンすれば、コンデンサC2が充電される。

【0070】

<NチャネルFET1のターンオフ>

(1)上記のようにNチャネルFET1がターンオンしてコンデンサC2が充電されている状態から、(2)スイッチSa1をターンオフし、スイッチSa2をターンオフすればコンデンサC1が充電される。それから、(3)更にスイッチS2をターンオンすると、ゲート駆動用電源3の正側端子,スイッチS3及びS2,コンデンサC2,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC2がゲート駆動用電源3と直列に接続される。これにより、インダクタL1には電圧(2VG−Vf)が印加され、NチャネルFET1のターンオン時とは逆の方向に電流I_L1が増加する。この状態から(4)スイッチS3をターンオフすると、電流I_L1がNチャネルFET1のゲートから電流Igとして流れ、当該ゲートを放電させる。

【0071】

NチャネルFET1のゲート−ソース間電圧Vgsが低下し、電圧Vgs<0になると、(5)電流I_L1はスイッチS2,コンデンサC2,スイッチSa2,スイッチS4の還流ダイオードを介して流れる。これにより、電圧Vgsは0Vにクランプされる。この状態から(6)スイッチSa2及びS2をターンオフし、スイッチS4をターンオンすると、電流I_L1は、スイッチS1の還流ダイオード,コンデンサC1,スイッチSa1の還流ダイオード,ゲート駆動電源3,スイッチS4,インダクタL1の経路で流れ、ゲート駆動電源3側に回生される。そして、(7)電流I_L1がゼロになれば、NチャネルFET1のターンオフが完了し、(8)スイッチSa2をターンオンすれば、コンデンサC1が充電状態となる。

【0072】

以上のように第4実施例によれば、コンデンサC1とコンデンサC2とを直列に接続し、通電制御回路12は、コンデンサC1及びC2と並列に接続されるスイッチSa1及びSa2の直列回路と、ゲート駆動用電源3と並列に接続されるスイッチS3及びS4の直列回路とで構成し、インダクタL1を、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間に接続する。このように構成すれば、スイッチSa1及びSa2,S1〜S4のオンオフを制御することで、上述したように請求項1における(1)〜(8)に対応した通電経路を形成できる。

【0073】

(第5実施例)

図15ないし図17は第5実施例を示すものであり、第4実施例と異なる部分のみ説明する。第5実施例の構成は第4実施例と同様であり、スイッチの一部のオンオフタイミングが異なっている。図15は図12相当図であり、図16,図17は図13,図14の一部相当図である。尚、第4実施例の制御パターンは第1実施例に対応し、第5実施例の制御パターンは第2実施例に対応している。

【0074】

<NチャネルFET1のターンオン>

図16に示す(4),(6)のスイッチングパターンが第4実施例と相違している。(4)では、スイッチS4と共にスイッチS1もターンオフさせている。この時、電流I_L1,すなわちNチャネルFET1のゲートを充電する電流Igは、インダクタンスL1,NチャネルFET1のゲート−ソース,ゲート駆動用電源3,スイッチSa1,コンデンサC2,スイッチS3の還流ダイオードの経路で流れる。これにより、コンデンサC2が充電される。

【0075】

そして、ゲート−ソース間電圧Vgsが電圧VGよりも上昇すると、(5)電流I_L1はスイッチS3の還流ダイオード,スイッチSa1,コンデンサC2,スイッチS2の還流ダイオードを介して流れる。したがって、この時もコンデンサC2が充電される。その結果、図15に示すように、コンデンサC2の電位V_C2は、電源電圧VGよりも上昇する。この状態から、(6)スイッチS3をターンオンし、スイッチSa1をターンオフすると、図13の(6)と同じ状態になる。

【0076】

<NチャネルFET1のターンオフ>

この場合も、図17に示す(4),(6)のスイッチングパターンが第4実施例と相違している。(4)では、スイッチS3と共にスイッチS2もターンオフさせている。この時、電流I_L1,すなわちNチャネルFET1のゲートを放電させる電流Igは、インダクタンスL1,スイッチS1の還流ダイオード,コンデンサC1,スイッチSa2,NチャネルFET1のソース−ゲートの経路で流れる。これにより、コンデンサC1が充電される。

【0077】

そして、ゲート−ソース間電圧Vgsが0Vよりも低下すると、(5)電流I_L1は、スイッチS1の還流ダイオード,コンデンサC1,スイッチSa2,スイッチS4の還流ダイオードを介して流れる。したがって、この時もコンデンサC1が充電される。その結果、図15に示すように、コンデンサC1の電位V_C1は、電源電圧VGよりも上昇する。この状態から、(6)スイッチS4をターンオンし、スイッチSa2をターンオフすると、図14の(6)と同じ状態になる。

すなわち、駆動回路11についても、コンデンサC1,C2の端子電圧V_C1,V_C2を一定に維持するには、第3実施例と同様に、第4実施例の制御パターンと第5実施例の制御パターンとを組み合わせる必要がある。それについて、次の第6実施例で説明する。

【0078】

(第6実施例)

図18ないし図21は第6実施例を示すものである。第4実施例の図12では、NチャネルFET1のターンオン時に(6)の状態を維持したまま(7)で電流I_L1がゼロになった後に、(8)でスイッチSa1をターンオンしている。これに対して第6実施例では、(6)の状態から(8)で電流I_L1がゼロの状態になる前に、(7)でスイッチSa1をターンオンする。

この場合図19に示すように、(7)では、インダクタL1,スイッチS3,スイッチSa1,コンデンサC2,スイッチS2の還流ダイオード,インダクタL1の経路で還流電流が流れ、第4実施例の(6)に引き続いて(7)でもコンデンサC2が充電される。したがって、第4実施例よりもコンデンサC2の端子電圧V_C2を上昇させることができる。

【0079】

また、NチャネルFET1のターンオフ時も、(6)の状態から(8)で逆極性の電流I_L1がゼロの状態になる前に、(7)でスイッチSa2をターンオンする。したがって、図20に示すように、インダクタL1,スイッチS1の還流ダイオード,コンデンサC1,スイッチSa2,スイッチS4,インダクタL1の経路で還流電流が流れ、第4実施例の(6)に引き続いて(7)でもコンデンサC1が充電される。これにより、第4実施例では、コンデンサC1及びC2の充電電荷量と放電電荷量との関係が、(充電電荷量)<(放電電荷量)となっていたが、第6実施例では充電電荷量を増加させて両者をほぼ等しくすることが可能となる。

【0080】

すなわち、図21に示すように、NチャネルFET1のターンオン時はスイッチS1をターンオンしてからターンオフするまでの期間長でコンデンサC1の放電電荷量が規定され、上記ターンオフに続いてスイッチSa1をターンオンするまでの期間でコンデンサC2の充電電荷量が規定される。また、NチャネルFET1のターンオフ時はスイッチS2をターンオンしてからターンオフするまでの期間長でコンデンサC2の放電電荷量が規定され、上記ターンオフに続いてスイッチSa2をターンオンするまでの期間でコンデンサC1の充電電荷量が規定される。

【0081】

したがって、例えばスイッチS1,S2のオン期間を固定して、スイッチSa1,Sa2のターンオンタイミングを調整すれば、例えばある制御周期では、コンデンサC1,C2の充電電荷量をより多くして端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させたり、その状態から放電電荷量をより多くして、端子電圧V_C1,V_C2が電源電圧VGを維持するように調整することができる。

【0082】

また、第6実施例とは異なり、例えば、第4実施例において、NチャネルFET1のターンオン,ターンオフ時に(1)〜(8)の通電経路を形成するパターンと、それらのうちターンオン,ターンオフ時それぞれの(4),(6)の通電経路を、第5実施例の(4),(6)の通電経路に置き換えて形成するパターンとを切り替えて実行しても良い。すなわち、第4実施例における通電経路の形成パターンと、第5実施例における通電経路の形成パターンとを切り替えて行う。尚、ここでのパターンの切替えは、前者と後者とを1回以上ずつ交互に実行することを言う。また、必ずしも両者の連続実行回数が等しくなくても良い。

【0083】

これにより、第4実施例の放電期間がより長いパターンと、第5実施例の充電期間がより長いパターンとを適宜組み合わせて実行することで、必要に応じて端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させたり、或いは端子電圧V_C1,V_C2を一定に維持するように調整することができる。

【0084】

(第7実施例)

図22ないし図25は第7実施例であり、第4実施例と異なる部分について説明する。第4実施例では、NチャネルFET1のターンオン時において、(6)でスイッチS1をターンオフ,スイッチS3をターンオンすると同時にスイッチSa1をターンオフしているが、第7実施例では、スイッチSa1のオン状態を維持するように期間を延長している。その結果、図23に示すように、(6)の経路はインダクタL1,スイッチS3,スイッチSa1,コンデンサC2,スイッチS2の還流ダイオード,インダクタL1の経路となり、同様にコンデンサC2を充電する経路となる。その後、(7)でスイッチSa1をターンオフさせれば、第4実施例の(6)と同じ経路になる。

【0085】

また、第4実施例では、NチャネルFET1のターンオフ時において、(6)でスイッチS2をターンオフ,スイッチS4をターンオンすると同時にスイッチSa2をターンオフしているが、第7実施例では、スイッチSa2のオン状態を維持するように期間を延長している。その結果、図24に示すように、(6)の経路はインダクタL1,スイッチS1の還流ダイオード,コンデンサC1,スイッチSa2,スイッチS4,インダクタL1の経路となり、同様にコンデンサC1を充電する経路となる。その後、(7)でスイッチSa2をターンオフさせれば、第4実施例の(6)と同じ経路になる。

【0086】

すなわち、第7実施例では、図25に示すように、NチャネルFET1のターンオン時はスイッチS1をターンオンしてからターンオフするまでの期間長でコンデンサC1の放電電荷量が規定され、上記ターンオフに続いてスイッチSa1をターンオフするまでの期間でコンデンサC2の充電電荷量が規定される。また、NチャネルFET1のターンオフ時はスイッチS2をターンオンしてからターンオフするまでの期間長でコンデンサC2の放電電荷量が規定され、上記ターンオフに続いてスイッチSa2をターンオフするまでの期間でコンデンサC1の充電電荷量が規定される。

【0087】

したがって、第6実施例と同様に例えばスイッチS1,S2のオン期間を固定して、スイッチSa1,Sa2のターンオフタイミングを調整すれば、例えばある制御周期では、コンデンサC1,C2の充電電荷量をより多くして端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させたり、その状態から放電電荷量をより多くして、端子電圧V_C1,V_C2が電源電圧VGを維持するように調整することができる。

【0088】

本発明は上記し又は図面に記載した実施例にのみ限定されるものではなく、以下のような変型又は拡張が可能である。

ゲート駆動用電源3の負側端子の電位は0Vに限らず、正側端子よりも低い電位であれば良い。

スイッチSa1,Sa2,S1〜S4を構成するスイッチング素子については、MOSFETや、バイポーラトランジスタ、その他どのような半導体スイッチング素子であっても良い。

【0089】

駆動対象スイッチング素子については、電圧駆動型のスイッチング素子であれば良い。また、MOSFETやMISFET,JFETやHEMT(High Electron Mobility Transistor)などであっても良い。

また、駆動回路2を構成する場合、スイッチSa1,Sa2については、還流ダイオードを備える必要はない。

【符号の説明】

【0090】

図面中、1はNチャネルFET1(駆動対象スイッチング素子)、2は駆動回路、3はゲート駆動用電源、4は通電制御回路、11は駆動回路、12は通電制御回路、Sa1はスイッチ(正側スイッチング素子)、Sa2はスイッチ(負側スイッチング素子)、Da1はダイオード(正側ダイオード)、Da2はダイオード(負側ダイオード)、S1〜S4はスイッチ(通電用スイッチング素子)、C1はコンデンサ(正側コンデンサ)、C2はコンデンサ(負側コンデンサ)、L1はインダクタを示す。

【技術分野】

【0001】

本発明は、制御端子に印加する駆動電圧に制限がある駆動対象スイッチング素子を駆動するための駆動回路に関する。

【背景技術】

【0002】

例えばパワーMOSFET等のパワー系スイッチング素子については、動作時の安全性を確保するためノーマリーオフとなるように駆動制御することが求められている。シリコン系のMOSFETに比較すると大幅に低損失化が可能な次世代デバイスである、SiC(炭化ケイ素)−J(ジャンクション)FETやGaN(窒化ガリウム)−FETではノーマリーオフを実現することができる。しかしながら、これらのFETはSiのパワーMOSFETがゲートに10〜20Vの電圧を印加できるのに対し、数V(例えば、2〜3V程度)しか電圧をかけられないものが多い。そのようなデバイスでは高い電圧で駆動することができず、その結果高速にスイッチングさせることが難しい。

【0003】

ゲート電圧を制限する技術として、例えば特許文献1では、ゲート駆動用のトランジスタのエミッタとグランドとの間にゲート抵抗及びツェナーダイオードの直列回路を接続し、両者の共通接続点に静電誘導トランジスタのゲートを接続することで、ツェナー電圧によりゲート電圧をクランプしている。この構成では、静電誘導トランジスタをオンさせている間はツェナーダイオードを介して電流が流れ続けるので、駆動回路における損失が大きく、高周波数帯でのスイッチングに対応できない。

【0004】

また、特許文献2では、ゲート駆動回路として4つのスイッチング素子を用いてHブリッジと同様の回路を構成し、そのブリッジ回路によりインダクタを介してゲート電流を流す構成となっている。これにより、ゲート電圧に依存することなくMOSFETを高速にスイッチングすることが可能となり、駆動回路で発生する損失も小さくなる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3655049号公報(図11等参照)

【特許文献2】特許第4321330号公報(図14等参照)

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献2の構成でも、インダクタの通電電流を増加させるのに時間がかかるため、やはり高い周波数で行うスイッチングに対応できない。

本発明は上記事情に鑑みてなされたものであり、その目的は、駆動電圧の印加に制限があるスイッチング素子を高い周波数で高速にスイッチングできる半導体スイッチング素子の駆動回路を提供することにある。

【課題を解決するための手段】

【0007】

請求項1記載の半導体スイッチング素子の駆動回路によれば、通電制御回路が4つの通電用スイッチング素子と正側及び負側スイッチング素子とを併せて制御することで、インダクタに電流を双方向に通電し、インダクタを介して流れる電流により駆動対象スイッチング素子の制御端子を充電し、また前記制御端子から放電させる。そのために、通電制御回路は、(1)〜(8)の通電経路を形成可能に構成される。

すなわち、駆動対象スイッチング素子をターンオンする場合には、(1)で正側コンデンサを充電し、(2)で駆動用電源と正側コンデンサとを直列に接続して、駆動対象スイッチング素子の制御端子を充電する方向でインダクタに通電すると、(3)でインダクタに蓄積された電磁エネルギーによって駆動対象スイッチング素子の制御端子を充電する。これにより駆動対象スイッチング素子はターンオンする。そして、充電により制御端子の電位が駆動用電源の電圧よりも上昇すると(4)で駆動用電源側に還流電流を流す。

【0008】

一方、駆動対象スイッチング素子をターンオフする場合には、(5)で負側コンデンサを充電し、(6)で駆動用電源と負側コンデンサとを直列に接続し、駆動対象スイッチング素子の制御端子を放電させる方向でインダクタに通電すると、(7)でインダクタに蓄積された電磁エネルギーにより駆動対象スイッチング素子の制御端子から放電させる。これにより駆動対象スイッチング素子はターンオフする。そして、放電により制御端子の電位が駆動用電源の負側端子の電位よりも低下すると(8)で駆動用電源側に還流電流を流す。

【0009】

したがって、駆動対象スイッチング素子をターンオンする場合に、制御端子に過電圧を印加することを回避した上で、駆動用電源と充電した正側コンデンサとを直列に接続して得られる昇圧電圧に応じて流れる電流により、駆動対象スイッチング素子の制御端子を急速に充電して短時間でターンオンさせることができる。また、駆動対象スイッチング素子をターンオフする場合も、駆動用電源と充電した負側コンデンサとを直列に接続して、同様に制御端子から急速に放電させて短時間でターンオフさせることができる。

【0010】

請求項2記載の半導体スイッチング素子の駆動回路によれば、通電制御回路を、正側ダイオードのカソードと負側ダイオードのアノードとの間に接続される第1及び第2スイッチング素子の直列回路と、正側コンデンサと負側コンデンサとの間に接続され、共通接続点が駆動対象スイッチング素子の制御端子に接続される第3及び第4スイッチング素子の直列回路とで構成し、インダクタを、第1及び第2スイッチング素子の共通接続点と、第3及び第4スイッチング素子の共通接続点との間に接続する。このように構成すれば、正側及び負側スイッチング素子と、インダクタに対してHブリッジ状に接続される第1〜第4スイッチング素子のオンオフを制御することで、(1)〜(8)の通電経路を形成できる。

【0011】

請求項3記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を以下のように切り替えることで(1)〜(8)の通電経路を形成する。(0)初期状態を、正側及び負側スイッチング素子がオン,第4スイッチング素子がオンである駆動対象スイッチング素子のターンオフ状態とすると、(1)正側スイッチング素子をターンオフしてから、第3スイッチング素子をターンオンする。これにより、駆動用電源(+),正側ダイオード,正側コンデンサ,第3及び第4スイッチング素子,負側スイッチング素子,駆動用電源(−)の経路で、正側コンデンサが(VG−Vf)に充電される。尚、VGは駆動用電源の電圧,Vfはダイオードの順方向電圧とする。

【0012】

次に、(2)第3スイッチング素子をターンオフしてから、正側スイッチング素子をターンオンし、更に第1スイッチング素子をターンオンすると、駆動用電源(+),正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタ,第4スイッチング素子,負側スイッチング素子,駆動用電源(−)の経路が形成される。これにより、インダクタには(2VG−Vf)の電圧で通電が行われる。

【0013】

この状態から、(3)第4スイッチング素子をターンオフすると、駆動用電源(+),正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタ,駆動対象スイッチング素子の制御端子及び電位基準側出力端子,負側スイッチング素子,駆動用電源(−)の経路が形成される(尚、電位基準側出力端子は、駆動対象スイッチング素子の電圧型によっては駆動用電源の正側端子に接続されることがある)。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流によって充電されて制御端子の電位が上昇し、駆動対象スイッチング素子はターンオン状態に移行する。

【0014】

制御端子の電位Vgsが上昇して(Vgs>VG)になると、インダクタ,第3スイッチング素子の還流ダイオード,正側コンデンサ,第1スイッチング素子,インダクタの経路で還流電流が流れる。したがって、制御端子の電位Vgsは、電源電圧VGによってクランプされる。その状態で、(4)第1スイッチング素子をターンオフ,第3スイッチング素子をターンオンすると、インダクタ,第3スイッチング素子,正側スイッチング素子,駆動用電源,負側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路が形成される。これにより、還流電流は駆動用電源に回生され、インダクタを介して流れる電流がゼロになると、駆動対象スイッチング素子のターンオン動作が完了する。

【0015】

一方、駆動対象スイッチング素子をターンオフさせる場合は、(5)負側スイッチング素子をターンオフしてから、第4スイッチング素子をターンオンする。これにより、駆動用電源(+),正側スイッチング素子,第3及び第4スイッチング素子,負側コンデンサ,負側ダイオード,駆動用電源(−)の経路で、負側コンデンサが(VG−Vf)に充電される。

次に、(6)第4スイッチング素子をターンオフしてから、負側スイッチング素子をターンオンし、更に第2スイッチング素子をターンオンすると、駆動用電源(+),正側スイッチング素子,第3スイッチング素子,インダクタ,第2スイッチング素子,負側コンデンサ,負側スイッチング素子,駆動用電源(−)の経路が形成される。これにより、インダクタには(2VG−Vf)の電圧で、(2)とは逆方向に通電が行われる。

【0016】

この状態から、(7)第3スイッチング素子をターンオフすると、駆動対象スイッチング素子の制御端子,インダクタ,第2スイッチング素子,負側コンデンサ,駆動対象スイッチング素子の電位基準側出力端子となる経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流により放電されて制御端子の電位が低下し、駆動対象スイッチング素子はターンオフ状態に移行する。

【0017】

制御端子の電位Vgsが低下して(Vgs<(駆動用電源(−)の電位)になると、インダクタ,第2スイッチング素子,負側コンデンサ,第4スイッチング素子の還流ダイオード,インダクタとなる経路で還流電流が流れる。したがって、制御端子の電位Vgsは、駆動用電源(−)の電位によってクランプされる。その状態で、(8)第2スイッチング素子をターンオフし、第4スイッチング素子をターンオンすると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側スイッチング素子,駆動用電源,負側スイッチング素子,第4スイッチング素子,インダクタとなる経路が形成される。これにより、還流電流は駆動用電源に回生され、インダクタを介して流れる電流がゼロになると、駆動対象スイッチング素子のターンオフ動作が完了する。

【0018】

請求項4記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を切り替えることで(1)〜(8)の通電経路を形成するが、請求項3と異なる部分を説明する。請求項4では、駆動対象スイッチング素子をターンオンさせる場合、(3)で第1及び第4スイッチング素子をターンオフする。これにより、インダクタ,駆動対象スイッチング素子の制御端子及び電位基準側出力端子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタとなる経路が形成され、駆動対象スイッチング素子はターンオン状態に移行する。この時、負側コンデンサには充電電流が流れるので、その端子電圧は電源電圧VGを超えて上昇する。

【0019】

そして、制御端子の電位Vgsが上昇して(Vgs>VG)になると、インダクタ,第3スイッチング素子の還流ダイオード,正側スイッチング素子,駆動用電源,負側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路が形成される。これにより、還流電流は駆動用電源に回生され、制御端子の電位Vgsは電源電圧VGによってクランプされる。この時も、負側コンデンサには充電電流が流れるので、端子電圧は上昇を続ける。また、続く(4)では第3スイッチング素子だけをターンオンするので、これにより、請求項3の(4)と同じ通電経路が形成される。この時も、負側コンデンサは充電されて端子電圧は上昇を続ける。

【0020】

一方、駆動対象スイッチング素子をターンオフさせる場合は、(7)で第2及び第3スイッチング素子をターンオフする。すると、駆動対象スイッチング素子の制御端子,インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側スイッチング素子,駆動用電源,負側スイッチング素子,駆動対象スイッチング素子の電位基準側出力端子となる経路が形成される。これにより、駆動対象スイッチング素子はターンオフ状態に移行し、還流電流は駆動電源側に回生される。この時、正側コンデンサには充電電流が流れるので、その端子電圧は電源電圧VGを超えて上昇する。

【0021】

そして、制御端子の電位Vgsが<(駆動用電源(−)の電位)になると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側スイッチング素子,駆動用電源,負側スイッチング素子,第3スイッチング素子の還流ダイオード,インダクタとなる経路で還流電流が流れる。したがって、制御端子の電位Vgsは、駆動用電源(−)の電位によってクランプされる。この時も、正側コンデンサには充電電流が流れるので端子電圧は上昇を続ける。その状態で(8)第4スイッチング素子をターンオンすると、請求項3の(8)と同じ通電経路が形成される。この時も、正側コンデンサは充電されて端子電圧は上昇を続ける。

すなわち、請求項4によれば、正側及び負側コンデンサが充電される期間が請求項3より長くなるので、それらの端子電圧を電源電圧VGよりも高くすることができ、それにより駆動対象スイッチング素子のターンオン,ターンオフをより高速に行うことができる。

【0022】

請求項5記載の半導体スイッチング素子の駆動回路によれば、請求項3において(1)〜(8)の通電経路を形成するパターンと、それらのうち(3),(4),(7),(8)の通電経路を(3)’,(4)’,(7)’,(8)’の通電経路に置き換えて形成するパターンとを切り替える。ここで、(3)’,(4)’,(7)’,(8)’の通電経路は、それぞれ請求項4における(3),(4),(7),(8)の通電経路に等しい。すなわち、請求項5では、請求項3における(1)〜(8)の通電経路の形成パターンと、請求項4における(1)〜(8)の通電経路の形成パターンとを切り替えて行う。尚、ここでのパターンの切替えは、前者と後者とを1回以上ずつ交互に実行することを言う。また、必ずしも両者の連続実行回数が等しくなくても良い。これにより、請求項3の放電期間がより長いパターンと、請求項4の充電期間がより長いパターンとを適宜組み合わせて実行することで、必要に応じて正側及び負側コンデンサの端子電圧を駆動電源電圧よりも高くしたり、或いは、前記端子電圧が一定となるように調整できる。

【0023】

請求項6記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を切り替えることで(1)〜(8)の通電経路を形成するが、やはり請求項3と異なる部分を説明する。請求項5では、(4)で第1スイッチング素子をターンオフしてから,第3スイッチング素子をターンオンする。また、(8)では、第2スイッチング素子をターンオフしてから、第4スイッチング素子をターンオンする。

これにより、駆動対象スイッチング素子をターンオンさせる場合の第1スイッチング素子のオン期間,並びに駆動対象スイッチング素子をターンオフさせる場合の第2スイッチング素子のオン期間は、請求項3のケースと、請求項4のケースとの中間となる。したがって、正側及び負側コンデンサが充電される期間が両者の中間になる。

【0024】

そして、請求項7記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(3)の通電経路を形成してから(4)の通電経路において第1スイッチング素子をターンオフさせるまでの期間長と、(7)の通電経路を形成してから(8)の通電経路において第2スイッチング素子をターンオフさせるまでの期間長とを調整することで、正側及び負側コンデンサの端子電圧を調整する。したがって、必要に応じて正側及び負側コンデンサの端子電圧を駆動電源電圧よりも高くしたり、或いは、前記端子電圧が一定となるように調整できる。

【0025】

請求項8記載の半導体スイッチング素子の駆動回路によれば、正側コンデンサと負側コンデンサとを直列に接続する構成とし、通電制御回路は、正側及び負側コンデンサと並列に接続される、第1及び第2スイッチング素子の直列回路と、駆動用電源と並列に接続される第3及び第4スイッチング素子の直列回路とで構成して、インダクタを、第1及び第2スイッチング素子の共通接続点と、第3及び第4スイッチング素子の共通接続点との間に接続する。このように構成すれば、正側及び負側スイッチング素子と、インダクタに対してHブリッジ状に接続された第1〜第4スイッチング素子(但し、第1及び第2スイッチング素子は、それぞれ正側及び負側ダイオードを介して駆動用電源に接続される)のオンオフを制御することで、(1)〜(8)の通電経路を形成できる。

【0026】

請求項9記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(2)の通電経路を形成する前にも(5)の通電経路を形成し、(6)の通電経路を形成する前にも(2)の通電経路を形成する。これにより、駆動対象スイッチング素子のターンオン動作を開始させる場合と、駆動対象スイッチング素子のターンオフ動作を開始させる場合とのそれぞれについて、予め正側及び負側コンデンサを充電することができる。

【0027】

請求項10記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(1)〜(8)の通電経路を形成する。(0)初期状態を、第4スイッチング素子がオンである駆動対象スイッチング素子のターンオフ状態とすると、先ず(1)負側スイッチング素子をオンすることで、駆動用電源(+),正側ダイオード,正側コンデンサ,負側スイッチング素子,駆動用電源(−)となる経路が形成され、正側コンデンサが(VG−Vf)に充電される。

【0028】

次に(5)負側スイッチング素子をターンオフしてから、正側スイッチング素子をターンオンすると、今度は駆動用電源(+),正側スイッチング素子,負側コンデンサ,負側ダイオード,駆動用電源(−)となる経路が形成され、負側コンデンサが(VG−Vf)に充電される。(2)で第1スイッチング素子をターンオンすると、駆動用電源(+),正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタ,第4スイッチング素子,駆動用電源(−)となる経路が形成され、これにより、インダクタには(2VG−Vf)の電圧で通電が行われる。

【0029】

この状態から、(3)第4スイッチング素子をターンオフすると、駆動用電源(+),正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタ,駆動対象スイッチング素子の制御端子及び電位基準側出力端子,駆動用電源(−)の経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流によって充電されて制御端子の電位が上昇し、駆動対象スイッチング素子はターンオン状態に移行する。

制御端子の電位Vgsが上昇して(Vgs>VG)になると、インダクタ,第3スイッチング素子の還流ダイオード,正側スイッチング素子,正側コンデンサ,第1スイッチング素子,インダクタの経路で還流電流が流れる。したがって、制御端子の電位Vgsは、電源電圧VGによってクランプされる。

【0030】

その状態で、(4)正側スイッチング素子及び第1スイッチング素子をターンオフ,第3スイッチング素子をターンオンすると、インダクタ,第3スイッチング素子,駆動用電源,負側ダイオード,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタとなる経路が形成される。これにより、還流電流は駆動用電源に回生され、インダクタを介して流れる電流がゼロになると、駆動対象スイッチング素子のターンオン動作が完了する。

【0031】

一方、駆動対象スイッチング素子をターンオフさせる場合は、(5)正側スイッチング素子をターンオンして負側コンデンサを充電し、次に(2)正側スイッチング素子をターンオフしてから、負側スイッチング素子をターンオンして正側コンデンサを充電する。それから、(6)第2スイッチング素子をターンオンすると、駆動用電源(+),第3スイッチング素子,インダクタ,第2スイッチング素子,負側コンデンサ,負側スイッチング素子,駆動用電源(−)の経路が形成される。これにより、インダクタには(2VG−Vf)の電圧で、(2)とは逆方向に通電が行われる。

この状態から、(7)第3スイッチング素子をターンオフすると、駆動対象スイッチング素子の制御端子,インダクタ,第2スイッチング素子,負側コンデンサ,負側スイッチング素子,駆動対象スイッチング素子の電位基準側出力端子となる経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流により放電されて制御端子の電位が低下し、駆動対象スイッチング素子はターンオフ状態に移行する。

【0032】

制御端子の電位Vgsが低下して(Vgs<(駆動用電源(−)の電位)になると、インダクタ,第2スイッチング素子,負側コンデンサ,負側スイッチング素子,第4スイッチング素子の還流ダイオード,インダクタとなる経路で還流電流が流れる。したがって、制御端子の電位Vgsは、駆動用電源(−)の電位によってクランプされる。その状態で、(8)負側スイッチング素子及び第2スイッチング素子をターンオフ,第4スイッチング素子をターンオンすると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側ダイオード,駆動用電源,第4スイッチング素子,インダクタとなる経路が形成される。これにより、還流電流は駆動用電源に回生され、インダクタを介して流れる電流がゼロになると、駆動対象スイッチング素子のターンオフ動作が完了する。

【0033】

請求項11記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を切り替えることで(1)〜(8)の通電経路を形成するが、請求項10と異なる部分を説明する。請求項11では、(3)で第1及び第4スイッチング素子をターンオフさせる。すると、駆動用電源(+),正側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタ,駆動対象スイッチング素子の制御端子及び電位基準側出力端子,駆動用電源(−)の経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流によって充電されて制御端子の電位が上昇し、駆動対象スイッチング素子はターンオン状態に移行する。

【0034】

制御端子の電位Vgsが上昇して(Vgs>VG)になると、インダクタ,第3スイッチング素子の還流ダイオード,正側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路で還流電流が流れる。したがって、制御端子の電位Vgsは、電源電圧VGによってクランプされる。そして、(4)で正側スイッチング素子をターンオフ,第3スイッチング素子をターンオンさせると、請求項9の(4)と同様の経路が形成される。

【0035】

また、(7)では第2及び第3スイッチング素子をターンオフさせる。すると、駆動対象スイッチング素子の制御端子,インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,負側スイッチング素子,駆動対象スイッチング素子の電位基準側出力端子となる経路が形成される。これにより、駆動対象スイッチング素子の制御端子が、インダクタを介して流れる電流により放電されて制御端子の電位が低下し、駆動対象スイッチング素子はターンオフ状態に移行する。

【0036】

制御端子の電位Vgsが低下して(Vgs<(駆動用電源(−)の電位)になると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,負側スイッチング素子,第4スイッチング素子の還流ダイオード,インダクタとなる経路で還流電流が流れる。したがって、制御端子の電位Vgsは、駆動用電源(−)の電位によってクランプされる。その状態で、(8)負側スイッチング素子をターンオフ,第4スイッチング素子をターンオンすると、請求項9の(8)と同様の経路が形成される。

【0037】

請求項12記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(4)の通電経路の形成した後、インダクタを介して流れる電流がゼロになる時間が経過する以前に(5)の通電経路を形成する。これにより、負側コンデンサを充電する時間がより長くなる。また、(8)の通電経路の形成した後、インダクタを介して流れる電流がゼロになる時間が経過する以前に負側スイッチング素子をターンオンする。これにより、正側コンデンサを充電する時間が請求項11よりも長くなる。したがって、正側及び負側コンデンサの端子電圧をより高くすることができる。

【0038】

請求項13記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(4)の通電経路において正側スイッチング素子をターンオフしてから(5)の通電経路において正側スイッチング素子をターンオンするまでの期間長と、(8)の通電経路において負側スイッチング素子をターンオフしてから次回に行う(1)の通電経路において負側スイッチング素子をターンオンするまでの期間長とを調整することで、正側及び負側コンデンサの端子電圧を調整する。したがって、正側及び負側コンデンサの端子電圧をより高くしたり、一定に維持する等の制御が可能となる。

【0039】

請求項14記載の半導体スイッチング素子の駆動回路によれば、請求項10において(1)〜(8)の通電経路を形成するパターンと、それらのうち(3),(4),(7),(8)の通電経路を(3)’,(4)’,(7)’,(8)’の通電経路に置き換えて形成するパターンとを切り替える。ここで、(3)’,(4)’,(7)’,(8)’の通電経路は、それぞれ請求項11における(3),(4),(7),(8)の通電経路に等しい。すなわち、請求項14では、請求項10における(1)〜(8)の通電経路の形成パターンと、請求項11における(1)〜(8)の通電経路の形成パターンとを切り替えて行う。尚、ここでのパターンの切替えは、前者と後者とを1回以上ずつ交互に実行することを言う。また、必ずしも両者の連続実行回数が等しくなくても良い。これにより、請求項10の放電期間がより長いパターンと、請求項11の充電期間がより長いパターンとを適宜組み合わせて実行することで、必要に応じて正側及び負側コンデンサの端子電圧を駆動電源電圧よりも高くしたり、或いは、前記端子電圧が一定となるように調整できる。

【0040】

請求項15記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、正側及び負側スイッチング素子,並びに第1ないし第4スイッチング素子を切り替えることで(1)〜(8)の通電経路を形成するが、請求項9と異なる部分を説明する。請求項13では、(4)で第1スイッチング素子をターンオフ,第3スイッチング素子をターンオンする。すると、インダクタ,第3スイッチング素子の,正側スイッチング素子,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路で還流電流が流れる。したがって、負側コンデンサが充電される。

【0041】

そして、次の(5)では、正側スイッチング素子をターンオフしてから正側スイッチング素子をターンオンする。正側スイッチング素子をターンオフすると、インダクタ,第3スイッチング素子,駆動用電源,負側ダイオード,負側コンデンサ,第2スイッチング素子の還流ダイオード,インダクタの経路で還流電流が流れる。したがって、この時も負側コンデンサが充電される。その後、コンデンサを介して流れる電流がゼロになった後に正側スイッチング素子をターンオンすれば、続く(2)の経路を形成するために備えることができる。

【0042】

また、(8)では、第2スイッチング素子をターンオフ,第4スイッチング素子をターンオンしてから、負側スイッチング素子をターンオフする。第2スイッチング素子をターンオフ,第4スイッチング素子をターンオンすると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,負側スイッチング素子,第4スイッチング素子の経路で還流電流が流れ、正側コンデンサが充電される。その後、負側スイッチング素子をターンオフすると、インダクタ,第1スイッチング素子の還流ダイオード,正側コンデンサ,正側ダイオード,駆動用電源,第4スイッチング素子、インダクタの経路で還流電流が流れ、この時も正側コンデンサが充電される。したがって、正側及び負側コンデンサの端子電圧をより上昇させることができる。

【0043】

請求項16記載の半導体スイッチング素子の駆動回路によれば、通電制御回路は、(5)の通電経路において正側スイッチング素子をターンオフしてから正側スイッチング素子をターンオンするまでの期間長と、(8)の通電経路において負側スイッチング素子をターンオフしてから、次回に行う(1)の通電経路において負側スイッチング素子をターンオンするまでの期間長とを調整することで、正側及び負側コンデンサの端子電圧を調整する。したがって、正側及び負側コンデンサの端子電圧をより上昇させたり一定に維持する等の制御が可能となる。

【図面の簡単な説明】

【0044】

【図1】第1実施例であり、駆動回路の電気的構成を示す図

【図2】タイミングチャート

【図3】NチャネルFETのターンオン時における通電経路の遷移状態を示す図

【図4】同ターンオフ時における図3相当図

【図5】第2実施例を示す図2相当図

【図6】図3の一部相当図

【図7】図4の一部相当図

【図8】インダクタに流れる電流とコンデンサC1,C2の充電電荷.放電電荷との関係を示す図

【図9】第3実施例を示す図2相当図

【図10】図8相当図

【図11】第4実施例を示す図1相当図

【図12】図2相当図

【図13】図3相当図

【図14】図4相当図

【図15】第5実施例を示す図12相当図

【図16】図13の一部相当図

【図17】図14の一部相当図

【図18】第6実施例を示す図12相当図

【図19】図13の一部相当図

【図20】図14の一部相当図

【図21】図8相当図

【図22】第7実施例を示す図12相当図

【図23】図13の一部相当図

【図24】図14の一部相当図

【図25】図8相当図

【発明を実施するための形態】

【0045】

(第1実施例)

以下、第1実施例について図1ないし図4を参照して説明する。図1は、例えばNチャネルFETを駆動するための駆動回路を示す。NチャネルFET1(駆動対象スイッチング素子)は、ドレイン側に図示しない負荷が接続されており、駆動回路2は、NチャネルFET1のゲート−ソース間に接続されている(ローサイド駆動方式)。尚、NチャネルFET1については、FETをMOS構造に限定する意図ではないが、図中では便宜上MOSFETのシンボルで図示している。駆動回路2は、ゲート駆動用電源3により供給される電源VGに基づいて、NチャネルMOSFET2のゲート(制御端子)に対して充放電電流Igを供給する。尚、図1に示すスイッチのシンボルとダイオードとの並列回路は、実体としては例えばNチャネルMOSFET(ダイオードは寄生ダイオード)であるが、説明を簡単にするため上記のシンボルで示している。

【0046】

ゲート駆動用電源3の正側端子は、スイッチSa1(正側スイッチング素子)とダイオードDa1(正側ダイオード)との直列回路の共通接続点(アノード)に接続されており、負側端子は、スイッチSa2(負側スイッチング素子)とダイオードDa2(負側ダイオード)との直列回路の共通接続点(カソード)に接続されている。ダイオードDa1のカソードと、ダイオードDa2のアノードとの間には、スイッチS1及びS2(通電用スイッチング素子)の直列回路と、コンデンサC1(正側コンデンサ),スイッチS3及びS4(通電用スイッチング素子),コンデンサC2(負側コンデンサ)の直列回路とが接続されている。

【0047】

そして、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間には、インダクタL1が接続されている。また、スイッチS3及びS4の共通接続点は、NチャネルFET1のゲートに接続されており、NチャネルFET1のソース(電位基準側出力端子)はゲート駆動用電源3の負側端子に接続されている。スイッチS1〜S4には、それぞれについて並列に、ゲート駆動用電源3の極性に対して逆方向となるダイオード(還流ダイオード)が接続されている。スイッチSa1,Sa2,S1〜S4のオンオフ制御は、図示しない制御回路によって行われる。ここで、スイッチS1〜S4と前記制御回路とが通電制御回路4を構成している。

【0048】

次に、本実施例の作用について図2ないし図4も参照して説明する。図2は、制御回路によって行われるスイッチSa1,Sa2,S1〜S4のオンオフ切替えと、各部の電圧,電流波形を示すタイミングチャートである。また、図3は、NチャネルFET1をターンオンさせる場合のスイッチSa1,Sa2,S1〜S4の切替え順序と、それに伴う電流の流れを示したものである。

【0049】

<NチャネルFET1のターンオン>

図3において、先ず(1)(図2〜図4中の丸数字を、括弧付き数字で示す)初期状態として、スイッチSa1及びSa2,S4がオンしてNチャネルFET1のゲートはゲート駆動用電源3の負側端子の電位(例えば0V,グランド電位)となっており、ターンオフ状態にあるとする。ここから、(2)スイッチSa1をターンオフし、続いて(3)スイッチS3をターンオンすると、ゲート駆動用電源3の正側端子,ダイオードDa1,コンデンサC1,スイッチS3及びS4,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC1が駆動電圧(VG−Vf)に充電される。

【0050】

次に、(4)スイッチS3をターンオフした後、スイッチSa1をターンオンし、(5)更にスイッチS1をターンオンすると、ゲート駆動用電源3の正側端子,スイッチSa1,コンデンサC1,スイッチS1及びS4,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC1がゲート駆動用電源3と直列に接続される。これにより、インダクタL1には電圧(2VG−Vf)が印加され、電流I_L1が増加する。この状態から、(6)スイッチS4をターンオフすると、インダクタンスL1に蓄積された電磁エネルギーも含む電流I_L1がNチャネルFET1のゲートに電流Igとして流れ、当該ゲートを充電する。

【0051】

すると、NチャネルFET1のゲート−ソース間電圧Vgsが上昇し、電圧Vgsが電圧VGよりも上昇すると、(7)電流I_L1はスイッチS3の還流ダイオード,コンデンサC1,スイッチS1を介して流れる。これにより、電圧Vgsは、電圧VGにクランプされる。この状態から、(8)スイッチS1をターンオフし、スイッチS3をターンオンすると、電流I_L1は、スイッチS3及びSa1,ゲート駆動電源3,スイッチSa2,コンデンサC2,スイッチS2の還流ダイオード,インダクタL1の経路で流れ、ゲート駆動電源3側に回生される。そして、(9)電流I_L1がゼロになれば、NチャネルFET1のターンオンが完了する。

【0052】

<NチャネルFET1のターンオフ>

(1)上記のようにNチャネルFET1がターンオンしている状態から、(2)スイッチSa2をターンオフし、(3)更にスイッチS4をターンオンすると、ゲート駆動用電源3の正側端子,スイッチSa1,スイッチS3及びS4,コンデンサC2,ダイオードDa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC2が駆動電圧(VG−Vf)に充電される。

【0053】

次に、(4)スイッチS4をターンオフした後、スイッチSa2をターンオンし、(5)更にスイッチS2をターンオンすると、ゲート駆動用電源3の正側端子,スイッチSa1,スイッチS3及びS2,コンデンサC2,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC2がゲート駆動用電源3と直列に接続される。これにより、インダクタL1には電圧(2VG−Vf)が印加され、NチャネルFET1のターンオン時とは逆の方向に電流I_L1が増加する。この状態から、(6)スイッチS3をターンオフすると、電流I_L1がNチャネルFET1のゲートから電流Igとして流れ、当該ゲートを放電させる。

【0054】

すると、NチャネルFET1のゲート−ソース間電圧Vgsが低下し、電圧Vgs<0Vになると、(7)電流I_L1はスイッチS2,コンデンサC2,スイッチS4の還流ダイオードを介して流れる。これにより、電圧Vgsは0Vにクランプされる。この状態から、(8)スイッチS2をターンオフし、スイッチS4をターンオンすると、電流I_L1は、スイッチS1の還流ダイオード,コンデンサC1,スイッチSa1,ゲート駆動電源3,スイッチSa2,スイッチS4,インダクタL1の経路で流れ、ゲート駆動電源3側に回生される。そして、(9)電流I_L1がゼロになれば、NチャネルFET1のターンオフが完了する。

【0055】

以上のように本実施例によれば、通電制御回路4が4つのスイッチS1〜S4とスイッチSa1及びSa2とを併せて制御することで、インダクタL1に電流を双方向に通電し、インダクタL1を介して流れる電流によりNチャネルFET1のゲートを充電し、また前記ゲートから放電させるようにした。より具体的には、通電制御回路4を、ダイオードDa1のカソードとダイオードDa2のアノードとの間に接続されるスイッチS1及びS2の直列回路と、コンデンサC1とコンデンサC2との間に接続され、共通接続点がNチャネルFET1のゲートに接続されるスイッチS3及びS4の直列回路とで構成し、インダクタL1を、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間に接続する。したがって、スイッチSa1及びSa2と、インダクタL1に対してHブリッジ状に接続されたスイッチS1〜S4のオンオフを制御することで、上述したように請求項1における(1)〜(8)に対応した通電経路を形成できる。

【0056】

(第2実施例)

図5ないし図8は第2実施例を示すものであり、第1実施例と同一部分には同一符号を付して説明を省略し、以下異なる部分について説明する。第2実施例の構成は第1実施例と同様であり、スイッチの一部のオンオフタイミングが異なっている。図5は図2相当図であり、図6,図7は図3,図4の一部相当図である。

【0057】

<NチャネルFET1のターンオン>

図6に示す(6),(8)のスイッチングパターンが第1実施例と相違している。また、(6)のスイッチングパターンが相違することで(7)の通電経路も変化している。(6)では、スイッチS4と共にスイッチS1もターンオフさせている。この時、電流I_L1,NチャネルFET1のゲートを充電する電流Igは、インダクタンスL1,NチャネルFET1のゲート−ソース,コンデンサC2,スイッチS2の還流ダイオードの経路で流れる。これにより、コンデンサC2が充電される。ここで、(1)〜(5)の期間ではコンデンサC2は放電されないため、前記期間のコンデンサC2の端子電圧がVGであれば、(6)において当該端子電圧はVGを超えて上昇する。

【0058】

そして、ゲート−ソース間電圧Vgsが電圧VGよりも上昇すると、(7)電流I_L1はスイッチS3の還流ダイオード,スイッチSa1,ゲート駆動用電源3,スイッチSa2,コンデンサC2,スイッチS2の還流ダイオードを介して流れるので、この時もコンデンサC2が充電される。その結果、図5に示すように、コンデンサC2の電位V_C2は、(7)の期間も上昇を続ける。この状態からスイッチS3をターンオンすれば、図3に示す(8)と同じ状態になる。

【0059】

<NチャネルFET1のターンオフ>

この場合も、図7に示す(6),(8)のスイッチングパターンが第1実施例と相違している。(6)では、スイッチS3と共にスイッチS2もターンオフさせている。この時、電流I_L1,NチャネルFET1のゲートを放電させる電流Igは、インダクタンスL1,スイッチS1の還流ダイオード,コンデンサC1,スイッチSa1,ゲート駆動用電源3,スイッチSa2,NチャネルFET1のソース−ゲートの経路で流れる。これにより、コンデンサC1が充電される。

【0060】

そして、ゲート−ソース間電圧Vgsが0Vよりも低下すると、(7)電流I_L1はスイッチS1の還流ダイオード,コンデンサC1,スイッチSa1,ゲート駆動用電源3,スイッチSa2,スイッチS4の還流ダイオードを介して流れる。したがって、この時もコンデンサC1が充電される。その結果、図5に示すように、コンデンサC1の電位V_C1は電源電圧VGよりも上昇する。この状態からスイッチS4をターンオンすれば、図4に示す(8)と同じ状態になる。

【0061】

ここで、第1実施例と第2実施例との相違について、図8を参照して説明する。図8(a)は図2に示す電流I_L1の波形であり、図8(b)は図5に示す電流I_L1の波形である。第1実施例の場合、ターンオン時における電流I_L1の上昇期間が長く、下降期間が短い。前者(波形で規定される面積,積分量が対応)はコンデンサC1の放電電荷量を規定し、後者はコンデンサC2の充電電荷量を規定する。

一方、ターンオフ時については、負極性の電流I_L1の上昇期間が長く、下降期間が短いが、前者はコンデンサC2の放電電荷量を規定し、後者はコンデンサC1の充電電荷量を規定する。結果として、コンデンサC1,C2の何れについても(放電電荷量)>(充電電荷量)となっており、第1実施例のスイッチングパターンでは、コンデンサC1,C2の端子電圧V_C1,V_C2は低下することになる。

【0062】

第2実施例の場合、ターンオン時における電流I_L1の上昇期間が短く、下降期間が長い。また、ターンオフ時については、負極性の電流I_L1の上昇期間が短く、下降期間が長い。その結果、コンデンサC1,C2の何れについても(放電電荷量)<(充電電荷量)となっており、第2実施例のスイッチングパターンでは、コンデンサC1,C2の端子電圧V_C1,V_C2は上昇することになる。したがって、コンデンサC1,C2の端子電圧V_C1,V_C2を例えば一定に維持する等のように調整するには、第1実施例の制御パターンと第2実施例の制御パターンとを組み合わせる必要がある。それについて、次の第3実施例で説明する。

【0063】

(第3実施例)

図9及び図10は第3実施例を示すものである。図9に示すように、第3実施例では、スイッチS1がターンオフするタイミングが、(6)においてスイッチS4がターンオフするタイミングと、(8)においてスイッチS3がターンオンするタイミングとの間に位置しており、これは、第1実施例よりも長く、第2実施例よりも短くなっている。すなわち、第1実施例では、スイッチS1のターンオフタイミングが(8)に一致しており、第2実施例では同タイミングが(6)に一致している。

これにより、図10に示すように、コンデンサC1、C2の充放電電荷量を調整し、(放電電荷量)≒(充電電荷量)とすることで端子電圧V_C1,V_C2を一定に維持することができる。或いは、例えばある制御周期では、コンデンサC1,C2の充電電荷量をより多くして端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させることも可能となる。

【0064】

また、第3実施例とは異なり、例えば、第1実施例において、NチャネルFET1のターンオン,ターンオフ時に(1)〜(8)の通電経路を形成するパターンと、それらのうちターンオン,ターンオフ時それぞれの(6),(8)の通電経路を、第2実施例の(6),(8)の通電経路に置き換えて形成するパターンとを切り替えて実行しても良い。すなわち、第1実施例における通電経路の形成パターンと、第2実施例における通電経路の形成パターンとを切り替えて行う。尚、ここでのパターンの切替えは、前者と後者とを1回以上ずつ交互に実行することを言う。また、必ずしも両者の連続実行回数が等しくなくても良い。

【0065】

これにより、第1実施例の放電期間がより長いパターンと、第2実施例の充電期間がより長いパターンとを適宜組み合わせて実行することで、必要に応じて端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させたり、或いは端子電圧V_C1,V_C2を一定に維持するように調整することができる。尚、必要であれば、図示しない制御回路に、端子電圧V_C1,V_C2をA/D変換してモニタするような電圧計測手段を設ければ良い。

【0066】

(第4実施例)

図11ないし図14は第4実施例であり、第1実施例と異なる部分について説明する。図11に示す駆動回路11は、駆動回路2と同じ回路素子で構成されているが、それらの接続形態が一部相違している。スイッチS3及びS4の直列回路は、ゲート駆動用電源3の両端に直結されている。また、スイッチSa1及びSa2も直列に接続されており、ダイオードDa1のカソードと、ダイオードDa2のアノードとの間には、コンデンサC1及びC2の直列回路と、スイッチS1及びS2の直列回路とが並列に接続されている。そして、スイッチS1〜S4と図示しない制御回路とが通電制御回路12を構成している。

【0067】

次に、第4実施例の作用について図12ないし図14を参照して説明する。

<NチャネルFET1のターンオン>

図13において、先ず(1)初期状態として、スイッチSa2,S4がオンしてNチャネルFET1のゲートはグランド電位となっており、ターンオフ状態にあるとする。この状態で、コンデンサC1は電圧(VG−Vf)に充電される。ここから、(2)スイッチSa2をターンオフし、スイッチSa1をターンオンすると、コンデンサC2が電圧(VG−Vf)に充電される。

【0068】

次に、(3)スイッチS1をターンオンすると、ゲート駆動用電源3の正側端子,スイッチSa1,コンデンサC1,スイッチS1及びS4,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC1がゲート駆動用電源3と直列に接続される。これにより、インダクタL1には電圧(2VG−Vf)が印加され、電流I_L1が増加する。この状態から、(4)スイッチS4をターンオフすると、インダクタンスL1に蓄積された電磁エネルギーも含む電流I_L1がNチャネルFET1のゲートに電流Igとして流れ、当該ゲートを充電する。

【0069】

すると、NチャネルFET1のゲート−ソース間電圧Vgsが上昇し、電圧Vgsが電圧VGよりも上昇すると、(5)電流I_L1はスイッチS3の還流ダイオード,スイッチSa1,コンデンサC1,スイッチS1を介して流れる。これにより、電圧Vgsは、電圧VGにクランプされる。この状態から、(6)スイッチSa1及びS1をターンオフし、スイッチS3をターンオンすると、電流I_L1は、スイッチS3,ゲート駆動電源3,スイッチSa2の還流ダイオード,コンデンサC2,スイッチS2の還流ダイオード,インダクタL1の経路で流れ、ゲート駆動電源3側に回生される。そして、(7)電流I_L1がゼロになればNチャネルFET1のターンオンが完了し、(8)スイッチSa1をターンオンすれば、コンデンサC2が充電される。

【0070】

<NチャネルFET1のターンオフ>

(1)上記のようにNチャネルFET1がターンオンしてコンデンサC2が充電されている状態から、(2)スイッチSa1をターンオフし、スイッチSa2をターンオフすればコンデンサC1が充電される。それから、(3)更にスイッチS2をターンオンすると、ゲート駆動用電源3の正側端子,スイッチS3及びS2,コンデンサC2,スイッチSa2,ゲート駆動用電源3の負側端子となる通電経路が形成され、コンデンサC2がゲート駆動用電源3と直列に接続される。これにより、インダクタL1には電圧(2VG−Vf)が印加され、NチャネルFET1のターンオン時とは逆の方向に電流I_L1が増加する。この状態から(4)スイッチS3をターンオフすると、電流I_L1がNチャネルFET1のゲートから電流Igとして流れ、当該ゲートを放電させる。

【0071】

NチャネルFET1のゲート−ソース間電圧Vgsが低下し、電圧Vgs<0になると、(5)電流I_L1はスイッチS2,コンデンサC2,スイッチSa2,スイッチS4の還流ダイオードを介して流れる。これにより、電圧Vgsは0Vにクランプされる。この状態から(6)スイッチSa2及びS2をターンオフし、スイッチS4をターンオンすると、電流I_L1は、スイッチS1の還流ダイオード,コンデンサC1,スイッチSa1の還流ダイオード,ゲート駆動電源3,スイッチS4,インダクタL1の経路で流れ、ゲート駆動電源3側に回生される。そして、(7)電流I_L1がゼロになれば、NチャネルFET1のターンオフが完了し、(8)スイッチSa2をターンオンすれば、コンデンサC1が充電状態となる。

【0072】

以上のように第4実施例によれば、コンデンサC1とコンデンサC2とを直列に接続し、通電制御回路12は、コンデンサC1及びC2と並列に接続されるスイッチSa1及びSa2の直列回路と、ゲート駆動用電源3と並列に接続されるスイッチS3及びS4の直列回路とで構成し、インダクタL1を、スイッチS1及びS2の共通接続点と、スイッチS3及びS4の共通接続点との間に接続する。このように構成すれば、スイッチSa1及びSa2,S1〜S4のオンオフを制御することで、上述したように請求項1における(1)〜(8)に対応した通電経路を形成できる。

【0073】

(第5実施例)

図15ないし図17は第5実施例を示すものであり、第4実施例と異なる部分のみ説明する。第5実施例の構成は第4実施例と同様であり、スイッチの一部のオンオフタイミングが異なっている。図15は図12相当図であり、図16,図17は図13,図14の一部相当図である。尚、第4実施例の制御パターンは第1実施例に対応し、第5実施例の制御パターンは第2実施例に対応している。

【0074】

<NチャネルFET1のターンオン>

図16に示す(4),(6)のスイッチングパターンが第4実施例と相違している。(4)では、スイッチS4と共にスイッチS1もターンオフさせている。この時、電流I_L1,すなわちNチャネルFET1のゲートを充電する電流Igは、インダクタンスL1,NチャネルFET1のゲート−ソース,ゲート駆動用電源3,スイッチSa1,コンデンサC2,スイッチS3の還流ダイオードの経路で流れる。これにより、コンデンサC2が充電される。

【0075】

そして、ゲート−ソース間電圧Vgsが電圧VGよりも上昇すると、(5)電流I_L1はスイッチS3の還流ダイオード,スイッチSa1,コンデンサC2,スイッチS2の還流ダイオードを介して流れる。したがって、この時もコンデンサC2が充電される。その結果、図15に示すように、コンデンサC2の電位V_C2は、電源電圧VGよりも上昇する。この状態から、(6)スイッチS3をターンオンし、スイッチSa1をターンオフすると、図13の(6)と同じ状態になる。

【0076】

<NチャネルFET1のターンオフ>

この場合も、図17に示す(4),(6)のスイッチングパターンが第4実施例と相違している。(4)では、スイッチS3と共にスイッチS2もターンオフさせている。この時、電流I_L1,すなわちNチャネルFET1のゲートを放電させる電流Igは、インダクタンスL1,スイッチS1の還流ダイオード,コンデンサC1,スイッチSa2,NチャネルFET1のソース−ゲートの経路で流れる。これにより、コンデンサC1が充電される。

【0077】

そして、ゲート−ソース間電圧Vgsが0Vよりも低下すると、(5)電流I_L1は、スイッチS1の還流ダイオード,コンデンサC1,スイッチSa2,スイッチS4の還流ダイオードを介して流れる。したがって、この時もコンデンサC1が充電される。その結果、図15に示すように、コンデンサC1の電位V_C1は、電源電圧VGよりも上昇する。この状態から、(6)スイッチS4をターンオンし、スイッチSa2をターンオフすると、図14の(6)と同じ状態になる。

すなわち、駆動回路11についても、コンデンサC1,C2の端子電圧V_C1,V_C2を一定に維持するには、第3実施例と同様に、第4実施例の制御パターンと第5実施例の制御パターンとを組み合わせる必要がある。それについて、次の第6実施例で説明する。

【0078】

(第6実施例)

図18ないし図21は第6実施例を示すものである。第4実施例の図12では、NチャネルFET1のターンオン時に(6)の状態を維持したまま(7)で電流I_L1がゼロになった後に、(8)でスイッチSa1をターンオンしている。これに対して第6実施例では、(6)の状態から(8)で電流I_L1がゼロの状態になる前に、(7)でスイッチSa1をターンオンする。

この場合図19に示すように、(7)では、インダクタL1,スイッチS3,スイッチSa1,コンデンサC2,スイッチS2の還流ダイオード,インダクタL1の経路で還流電流が流れ、第4実施例の(6)に引き続いて(7)でもコンデンサC2が充電される。したがって、第4実施例よりもコンデンサC2の端子電圧V_C2を上昇させることができる。

【0079】

また、NチャネルFET1のターンオフ時も、(6)の状態から(8)で逆極性の電流I_L1がゼロの状態になる前に、(7)でスイッチSa2をターンオンする。したがって、図20に示すように、インダクタL1,スイッチS1の還流ダイオード,コンデンサC1,スイッチSa2,スイッチS4,インダクタL1の経路で還流電流が流れ、第4実施例の(6)に引き続いて(7)でもコンデンサC1が充電される。これにより、第4実施例では、コンデンサC1及びC2の充電電荷量と放電電荷量との関係が、(充電電荷量)<(放電電荷量)となっていたが、第6実施例では充電電荷量を増加させて両者をほぼ等しくすることが可能となる。

【0080】

すなわち、図21に示すように、NチャネルFET1のターンオン時はスイッチS1をターンオンしてからターンオフするまでの期間長でコンデンサC1の放電電荷量が規定され、上記ターンオフに続いてスイッチSa1をターンオンするまでの期間でコンデンサC2の充電電荷量が規定される。また、NチャネルFET1のターンオフ時はスイッチS2をターンオンしてからターンオフするまでの期間長でコンデンサC2の放電電荷量が規定され、上記ターンオフに続いてスイッチSa2をターンオンするまでの期間でコンデンサC1の充電電荷量が規定される。

【0081】

したがって、例えばスイッチS1,S2のオン期間を固定して、スイッチSa1,Sa2のターンオンタイミングを調整すれば、例えばある制御周期では、コンデンサC1,C2の充電電荷量をより多くして端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させたり、その状態から放電電荷量をより多くして、端子電圧V_C1,V_C2が電源電圧VGを維持するように調整することができる。

【0082】

また、第6実施例とは異なり、例えば、第4実施例において、NチャネルFET1のターンオン,ターンオフ時に(1)〜(8)の通電経路を形成するパターンと、それらのうちターンオン,ターンオフ時それぞれの(4),(6)の通電経路を、第5実施例の(4),(6)の通電経路に置き換えて形成するパターンとを切り替えて実行しても良い。すなわち、第4実施例における通電経路の形成パターンと、第5実施例における通電経路の形成パターンとを切り替えて行う。尚、ここでのパターンの切替えは、前者と後者とを1回以上ずつ交互に実行することを言う。また、必ずしも両者の連続実行回数が等しくなくても良い。

【0083】

これにより、第4実施例の放電期間がより長いパターンと、第5実施例の充電期間がより長いパターンとを適宜組み合わせて実行することで、必要に応じて端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させたり、或いは端子電圧V_C1,V_C2を一定に維持するように調整することができる。

【0084】

(第7実施例)

図22ないし図25は第7実施例であり、第4実施例と異なる部分について説明する。第4実施例では、NチャネルFET1のターンオン時において、(6)でスイッチS1をターンオフ,スイッチS3をターンオンすると同時にスイッチSa1をターンオフしているが、第7実施例では、スイッチSa1のオン状態を維持するように期間を延長している。その結果、図23に示すように、(6)の経路はインダクタL1,スイッチS3,スイッチSa1,コンデンサC2,スイッチS2の還流ダイオード,インダクタL1の経路となり、同様にコンデンサC2を充電する経路となる。その後、(7)でスイッチSa1をターンオフさせれば、第4実施例の(6)と同じ経路になる。

【0085】

また、第4実施例では、NチャネルFET1のターンオフ時において、(6)でスイッチS2をターンオフ,スイッチS4をターンオンすると同時にスイッチSa2をターンオフしているが、第7実施例では、スイッチSa2のオン状態を維持するように期間を延長している。その結果、図24に示すように、(6)の経路はインダクタL1,スイッチS1の還流ダイオード,コンデンサC1,スイッチSa2,スイッチS4,インダクタL1の経路となり、同様にコンデンサC1を充電する経路となる。その後、(7)でスイッチSa2をターンオフさせれば、第4実施例の(6)と同じ経路になる。

【0086】

すなわち、第7実施例では、図25に示すように、NチャネルFET1のターンオン時はスイッチS1をターンオンしてからターンオフするまでの期間長でコンデンサC1の放電電荷量が規定され、上記ターンオフに続いてスイッチSa1をターンオフするまでの期間でコンデンサC2の充電電荷量が規定される。また、NチャネルFET1のターンオフ時はスイッチS2をターンオンしてからターンオフするまでの期間長でコンデンサC2の放電電荷量が規定され、上記ターンオフに続いてスイッチSa2をターンオフするまでの期間でコンデンサC1の充電電荷量が規定される。

【0087】

したがって、第6実施例と同様に例えばスイッチS1,S2のオン期間を固定して、スイッチSa1,Sa2のターンオフタイミングを調整すれば、例えばある制御周期では、コンデンサC1,C2の充電電荷量をより多くして端子電圧V_C1,V_C2を電源電圧VGよりも上昇させ、NチャネルFET1のターンオン,ターンオフを高速に実行させたり、その状態から放電電荷量をより多くして、端子電圧V_C1,V_C2が電源電圧VGを維持するように調整することができる。

【0088】

本発明は上記し又は図面に記載した実施例にのみ限定されるものではなく、以下のような変型又は拡張が可能である。

ゲート駆動用電源3の負側端子の電位は0Vに限らず、正側端子よりも低い電位であれば良い。

スイッチSa1,Sa2,S1〜S4を構成するスイッチング素子については、MOSFETや、バイポーラトランジスタ、その他どのような半導体スイッチング素子であっても良い。

【0089】

駆動対象スイッチング素子については、電圧駆動型のスイッチング素子であれば良い。また、MOSFETやMISFET,JFETやHEMT(High Electron Mobility Transistor)などであっても良い。

また、駆動回路2を構成する場合、スイッチSa1,Sa2については、還流ダイオードを備える必要はない。

【符号の説明】

【0090】

図面中、1はNチャネルFET1(駆動対象スイッチング素子)、2は駆動回路、3はゲート駆動用電源、4は通電制御回路、11は駆動回路、12は通電制御回路、Sa1はスイッチ(正側スイッチング素子)、Sa2はスイッチ(負側スイッチング素子)、Da1はダイオード(正側ダイオード)、Da2はダイオード(負側ダイオード)、S1〜S4はスイッチ(通電用スイッチング素子)、C1はコンデンサ(正側コンデンサ)、C2はコンデンサ(負側コンデンサ)、L1はインダクタを示す。

【特許請求の範囲】

【請求項1】

駆動対象スイッチング素子の電位基準側出力端子と制御端子との間に印加する駆動電圧を供給する駆動用電源と、

共通接続点となるアノードが前記駆動用電源の正側端子に接続される、正側ダイオード及び正側スイッチング素子からなる正側直列回路と、

共通接続点となるカソードが前記駆動用電源の負側端子に接続される、負側ダイオード及び負側スイッチング素子からなる負側直列回路と、

前記正側直列回路に並列に接続される正側コンデンサと、

前記負側直列回路に並列に接続される負側コンデンサと、

前記駆動対象スイッチング素子の制御端子に接続されるインダクタと、

一端が前記インダクタに接続され、前記駆動用電源の極性に対して逆方向となる還流ダイオードが並列に接続されている4つの通電用スイッチング素子により構成され、前記正側及び負側スイッチング素子と併せて制御することで、以下に示す(1)〜(8)の通電経路を形成可能に構成される通電制御回路とを備えたことを特徴とする半導体スイッチング素子の駆動回路。

(1)前記正側コンデンサを充電する経路。

(2)前記駆動用電源と、前記正側コンデンサとを直列に接続し、前記駆動対象スイッチング素子の制御端子を充電する方向で、前記インダクタに通電する経路。

(3)前記インダクタに蓄積された電磁エネルギーにより、前記駆動対象スイッチング素子の制御端子を充電する経路。

(4)前記制御端子の電位が前記駆動用電源の電圧よりも上昇した場合に、前記駆動用電源側に還流電流を流す経路。

(5)前記負側コンデンサを充電する経路。

(6)前記駆動用電源と、前記負側コンデンサとを直列に接続し、前記駆動対象スイッチング素子の制御端子を放電させる方向で、前記インダクタに通電する経路。

(7)前記インダクタに蓄積された電磁エネルギーにより、前記駆動対象スイッチング素子の制御端子を放電させる経路。

(8)前記制御端子の電位が前記駆動用電源の負側端子の電位よりも低下した場合に、前記駆動用電源側に還流電流を流す経路。

【請求項2】

前記通電制御回路は、

前記正側ダイオードのカソードと、前記負側ダイオードのアノードとの間に接続される、第1及び第2スイッチング素子の直列回路と、

前記正側コンデンサと前記負側コンデンサとの間に接続され、共通接続点が前記駆動対象スイッチング素子の制御端子に接続される前記第3及び第4スイッチング素子の直列回路とで構成され、

前記インダクタは、前記第1及び第2スイッチング素子の共通接続点と、前記第3及び第4スイッチング素子の共通接続点との間に接続されることを特徴とする請求項1記載の半導体スイッチング素子の駆動回路。

【請求項3】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項2記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記正側及び負側スイッチング素子がオン,前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記正側スイッチング素子をターンオフしてから、前記第3スイッチング素子をターンオン。

(2)前記第3スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオンし、更に前記第1スイッチング素子をターンオン。

(3)前記第4スイッチング素子をターンオフ。

(4)前記第1スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(5)前記負側スイッチング素子をターンオフしてから、前記第4スイッチング素子をターンオン。

(6)前記第4スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオンし、更に前記第2スイッチング素子をターンオン。

(7)前記第3スイッチング素子をターンオフ。

(8)前記第2スイッチング素子をターンオフし、前記第4スイッチング素子をターンオン。

【請求項4】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項2記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記正側及び負側スイッチング素子がオン,前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記正側スイッチング素子をターンオフしてから、前記第3スイッチング素子をターンオン。

(2)前記第3スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオンし、更に前記第1スイッチング素子をターンオン。

(3)前記第1及び第4スイッチング素子をターンオフ。

(4)前記第3スイッチング素子をターンオン。

(5)前記負側スイッチング素子をターンオフしてから、前記第4スイッチング素子をターンオン。

(6)前記第4スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオンし、更に前記第2スイッチング素子をターンオン。

(7)前記第2及び第3スイッチング素子をターンオフ。

(8)前記第4スイッチング素子をターンオン。

【請求項5】

前記(1)〜(8)の通電経路を形成するパターンと、それらのうち前記(3),(4),(7),(8)の通電経路を以下の(3)’,(4)’,(7)’,(8)’の通電経路に置き換えて形成するパターンとを切り替えることで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項3記載の半導体スイッチング素子の駆動回路。

(3)’前記第1及び第4スイッチング素子をターンオフ。

(4)’前記第3スイッチング素子をターンオン。

(7)’前記第2及び第3スイッチング素子をターンオフ。

(8)’前記第4スイッチング素子をターンオン。

【請求項6】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項2記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記正側及び負側スイッチング素子がオン,前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記正側スイッチング素子をターンオフしてから、前記第3スイッチング素子をターンオン。

(2)前記第3スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオンし、更に前記第1スイッチング素子をターンオン。

(3)前記第4スイッチング素子をターンオフ。

(4)前記第1スイッチング素子をターンオフしてから,前記第3スイッチング素子をターンオン。

(5)前記負側スイッチング素子をターンオフしてから、前記第4スイッチング素子をターンオン。

(6)前記第4スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオンし、更に前記第2スイッチング素子をターンオン。

(7)前記第3スイッチング素子をターンオフ。

(8)前記第2スイッチング素子をターンオフしてから、前記第4スイッチング素子をターンオン。

【請求項7】

前記通電制御回路は、前記(3)の通電経路を形成してから、前記(4)の通電経路において前記第1スイッチング素子をターンオフさせるまでの期間長と、前記(7)の通電経路を形成してから、前記(8)の通電経路において前記第2スイッチング素子をターンオフさせるまでの期間長とを調整することで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項6記載の半導体スイッチング素子の駆動回路。

【請求項8】

前記正側コンデンサと前記負側コンデンサとが直列に接続されており、

前記通電制御回路は、

前記正側及び負側コンデンサと並列に接続される、第1及び第2スイッチング素子の直列回路と、

前記駆動用電源と並列に接続される、第3及び第4スイッチング素子の直列回路とで構成され、

前記インダクタは、前記第1及び第2スイッチング素子の共通接続点と、前記第3及び第4スイッチング素子の共通接続点との間に接続されることを特徴とする請求項1記載の半導体スイッチング素子の駆動回路。

【請求項9】

前記通電制御回路は、前記(2)の通電経路を形成する前にも前記(5)の通電経路を形成し、前記(6)の通電経路を形成する前にも前記(2)の通電経路を形成することを特徴とする請求項8記載の半導体スイッチング素子の駆動回路。

【請求項10】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項9記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記負側スイッチング素子をオン。

(5)前記負側スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオン。

(2)前記第1スイッチング素子をターンオン。

(3)前記第4スイッチング素子をターンオフ。

(4)前記正側スイッチング素子及び前記第1スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(5)前記正側スイッチング素子をターンオン。

(2)前記正側スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオン。

(6)前記第2スイッチング素子をターンオン。

(7)前記第3スイッチング素子をターンオフ。

(8)前記負側スイッチング素子及び前記第2スイッチング素子をターンオフ,前記第4スイッチング素子をターンオン。

【請求項11】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項9記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記負側スイッチング素子をオン。

(5)前記負側スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオン。

(2)前記第1スイッチング素子をターンオン。

(3)前記第1及び第4スイッチング素子をターンオフ。

(4)前記正側スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(5)前記正側スイッチング素子をターンオン。

(2)前記正側スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオン。

(6)前記第2スイッチング素子をターンオン。

(7)前記第2及び第3スイッチング素子をターンオフ。

(8)前記負側スイッチング素子をターンオフ,前記第4スイッチング素子をターンオン。

【請求項12】

前記通電制御回路は、前記(4)の通電経路の形成した後、前記インダクタを介して流れる電流がゼロになる時間が経過する以前に(5)の通電経路を形成し、

前記(8)の通電経路の形成した後、前記インダクタを介して流れる電流がゼロになる時間が経過する以前に前記負側スイッチング素子をターンオンすることを特徴とする請求項11記載の半導体スイッチング素子の駆動回路。

【請求項13】

前記通電制御回路は、前記(4)の通電経路において前記正側スイッチング素子をターンオフしてから、前記(5)の通電経路において前記正側スイッチング素子をターンオンするまでの期間長と、前記(8)の通電経路において前記負側スイッチング素子をターンオフしてから、次回に行う前記(1)の通電経路において前記負側スイッチング素子をターンオンするまでの期間長とを調整することで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項9ないし12の何れかに記載の半導体スイッチング素子の駆動回路。

【請求項14】

前記(1)〜(8)の通電経路を形成するパターンと、それらのうち前記(3),(4),(7),(8)の通電経路を以下の(3)’,(4)’,(7)’,(8)’の通電経路に置き換えて形成するパターンとを切り替えることで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項10記載の半導体スイッチング素子の駆動回路。

(3)’前記第1及び第4スイッチング素子をターンオフ。

(4)’前記正側スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(7)’前記第2及び第3スイッチング素子をターンオフ。

(8)’前記負側スイッチング素子をターンオフ,前記第4スイッチング素子をターンオン。

【請求項15】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項9記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記負側スイッチング素子をオン。

(5)前記負側スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオン。

(2)前記第1スイッチング素子をターンオン。

(3)前記第4スイッチング素子をターンオフ。

(4)前記第1スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(5)前記正側スイッチング素子をターンオフしてから前記正側スイッチング素子をターンオン。

(2)前記正側スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオン。

(6)前記第2スイッチング素子をターンオン。

(7)前記第3スイッチング素子をターンオフ。

(8)前記第2スイッチング素子をターンオフ,前記第4スイッチング素子をターンオンしてから、前記負側スイッチング素子をターンオフ。

【請求項16】

前記通電制御回路は、前記(5)の通電経路において前記正側スイッチング素子をターンオフしてから前記正側スイッチング素子をターンオンするまでの期間長と、前記(8)の通電経路において前記負側スイッチング素子をターンオフしてから、次回に行う前記(1)の通電経路において前記負側スイッチング素子をターンオンするまでの期間長とを調整することで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項15記載の半導体スイッチング素子の駆動回路。

【請求項1】

駆動対象スイッチング素子の電位基準側出力端子と制御端子との間に印加する駆動電圧を供給する駆動用電源と、

共通接続点となるアノードが前記駆動用電源の正側端子に接続される、正側ダイオード及び正側スイッチング素子からなる正側直列回路と、

共通接続点となるカソードが前記駆動用電源の負側端子に接続される、負側ダイオード及び負側スイッチング素子からなる負側直列回路と、

前記正側直列回路に並列に接続される正側コンデンサと、

前記負側直列回路に並列に接続される負側コンデンサと、

前記駆動対象スイッチング素子の制御端子に接続されるインダクタと、

一端が前記インダクタに接続され、前記駆動用電源の極性に対して逆方向となる還流ダイオードが並列に接続されている4つの通電用スイッチング素子により構成され、前記正側及び負側スイッチング素子と併せて制御することで、以下に示す(1)〜(8)の通電経路を形成可能に構成される通電制御回路とを備えたことを特徴とする半導体スイッチング素子の駆動回路。

(1)前記正側コンデンサを充電する経路。

(2)前記駆動用電源と、前記正側コンデンサとを直列に接続し、前記駆動対象スイッチング素子の制御端子を充電する方向で、前記インダクタに通電する経路。

(3)前記インダクタに蓄積された電磁エネルギーにより、前記駆動対象スイッチング素子の制御端子を充電する経路。

(4)前記制御端子の電位が前記駆動用電源の電圧よりも上昇した場合に、前記駆動用電源側に還流電流を流す経路。

(5)前記負側コンデンサを充電する経路。

(6)前記駆動用電源と、前記負側コンデンサとを直列に接続し、前記駆動対象スイッチング素子の制御端子を放電させる方向で、前記インダクタに通電する経路。

(7)前記インダクタに蓄積された電磁エネルギーにより、前記駆動対象スイッチング素子の制御端子を放電させる経路。

(8)前記制御端子の電位が前記駆動用電源の負側端子の電位よりも低下した場合に、前記駆動用電源側に還流電流を流す経路。

【請求項2】

前記通電制御回路は、

前記正側ダイオードのカソードと、前記負側ダイオードのアノードとの間に接続される、第1及び第2スイッチング素子の直列回路と、

前記正側コンデンサと前記負側コンデンサとの間に接続され、共通接続点が前記駆動対象スイッチング素子の制御端子に接続される前記第3及び第4スイッチング素子の直列回路とで構成され、

前記インダクタは、前記第1及び第2スイッチング素子の共通接続点と、前記第3及び第4スイッチング素子の共通接続点との間に接続されることを特徴とする請求項1記載の半導体スイッチング素子の駆動回路。

【請求項3】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項2記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記正側及び負側スイッチング素子がオン,前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記正側スイッチング素子をターンオフしてから、前記第3スイッチング素子をターンオン。

(2)前記第3スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオンし、更に前記第1スイッチング素子をターンオン。

(3)前記第4スイッチング素子をターンオフ。

(4)前記第1スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(5)前記負側スイッチング素子をターンオフしてから、前記第4スイッチング素子をターンオン。

(6)前記第4スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオンし、更に前記第2スイッチング素子をターンオン。

(7)前記第3スイッチング素子をターンオフ。

(8)前記第2スイッチング素子をターンオフし、前記第4スイッチング素子をターンオン。

【請求項4】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項2記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記正側及び負側スイッチング素子がオン,前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記正側スイッチング素子をターンオフしてから、前記第3スイッチング素子をターンオン。

(2)前記第3スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオンし、更に前記第1スイッチング素子をターンオン。

(3)前記第1及び第4スイッチング素子をターンオフ。

(4)前記第3スイッチング素子をターンオン。

(5)前記負側スイッチング素子をターンオフしてから、前記第4スイッチング素子をターンオン。

(6)前記第4スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオンし、更に前記第2スイッチング素子をターンオン。

(7)前記第2及び第3スイッチング素子をターンオフ。

(8)前記第4スイッチング素子をターンオン。

【請求項5】

前記(1)〜(8)の通電経路を形成するパターンと、それらのうち前記(3),(4),(7),(8)の通電経路を以下の(3)’,(4)’,(7)’,(8)’の通電経路に置き換えて形成するパターンとを切り替えることで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項3記載の半導体スイッチング素子の駆動回路。

(3)’前記第1及び第4スイッチング素子をターンオフ。

(4)’前記第3スイッチング素子をターンオン。

(7)’前記第2及び第3スイッチング素子をターンオフ。

(8)’前記第4スイッチング素子をターンオン。

【請求項6】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項2記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記正側及び負側スイッチング素子がオン,前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記正側スイッチング素子をターンオフしてから、前記第3スイッチング素子をターンオン。

(2)前記第3スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオンし、更に前記第1スイッチング素子をターンオン。

(3)前記第4スイッチング素子をターンオフ。

(4)前記第1スイッチング素子をターンオフしてから,前記第3スイッチング素子をターンオン。

(5)前記負側スイッチング素子をターンオフしてから、前記第4スイッチング素子をターンオン。

(6)前記第4スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオンし、更に前記第2スイッチング素子をターンオン。

(7)前記第3スイッチング素子をターンオフ。

(8)前記第2スイッチング素子をターンオフしてから、前記第4スイッチング素子をターンオン。

【請求項7】

前記通電制御回路は、前記(3)の通電経路を形成してから、前記(4)の通電経路において前記第1スイッチング素子をターンオフさせるまでの期間長と、前記(7)の通電経路を形成してから、前記(8)の通電経路において前記第2スイッチング素子をターンオフさせるまでの期間長とを調整することで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項6記載の半導体スイッチング素子の駆動回路。

【請求項8】

前記正側コンデンサと前記負側コンデンサとが直列に接続されており、

前記通電制御回路は、

前記正側及び負側コンデンサと並列に接続される、第1及び第2スイッチング素子の直列回路と、

前記駆動用電源と並列に接続される、第3及び第4スイッチング素子の直列回路とで構成され、

前記インダクタは、前記第1及び第2スイッチング素子の共通接続点と、前記第3及び第4スイッチング素子の共通接続点との間に接続されることを特徴とする請求項1記載の半導体スイッチング素子の駆動回路。

【請求項9】

前記通電制御回路は、前記(2)の通電経路を形成する前にも前記(5)の通電経路を形成し、前記(6)の通電経路を形成する前にも前記(2)の通電経路を形成することを特徴とする請求項8記載の半導体スイッチング素子の駆動回路。

【請求項10】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項9記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記負側スイッチング素子をオン。

(5)前記負側スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオン。

(2)前記第1スイッチング素子をターンオン。

(3)前記第4スイッチング素子をターンオフ。

(4)前記正側スイッチング素子及び前記第1スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(5)前記正側スイッチング素子をターンオン。

(2)前記正側スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオン。

(6)前記第2スイッチング素子をターンオン。

(7)前記第3スイッチング素子をターンオフ。

(8)前記負側スイッチング素子及び前記第2スイッチング素子をターンオフ,前記第4スイッチング素子をターンオン。

【請求項11】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項9記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記負側スイッチング素子をオン。

(5)前記負側スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオン。

(2)前記第1スイッチング素子をターンオン。

(3)前記第1及び第4スイッチング素子をターンオフ。

(4)前記正側スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(5)前記正側スイッチング素子をターンオン。

(2)前記正側スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオン。

(6)前記第2スイッチング素子をターンオン。

(7)前記第2及び第3スイッチング素子をターンオフ。

(8)前記負側スイッチング素子をターンオフ,前記第4スイッチング素子をターンオン。

【請求項12】

前記通電制御回路は、前記(4)の通電経路の形成した後、前記インダクタを介して流れる電流がゼロになる時間が経過する以前に(5)の通電経路を形成し、

前記(8)の通電経路の形成した後、前記インダクタを介して流れる電流がゼロになる時間が経過する以前に前記負側スイッチング素子をターンオンすることを特徴とする請求項11記載の半導体スイッチング素子の駆動回路。

【請求項13】

前記通電制御回路は、前記(4)の通電経路において前記正側スイッチング素子をターンオフしてから、前記(5)の通電経路において前記正側スイッチング素子をターンオンするまでの期間長と、前記(8)の通電経路において前記負側スイッチング素子をターンオフしてから、次回に行う前記(1)の通電経路において前記負側スイッチング素子をターンオンするまでの期間長とを調整することで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項9ないし12の何れかに記載の半導体スイッチング素子の駆動回路。

【請求項14】

前記(1)〜(8)の通電経路を形成するパターンと、それらのうち前記(3),(4),(7),(8)の通電経路を以下の(3)’,(4)’,(7)’,(8)’の通電経路に置き換えて形成するパターンとを切り替えることで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項10記載の半導体スイッチング素子の駆動回路。

(3)’前記第1及び第4スイッチング素子をターンオフ。

(4)’前記正側スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(7)’前記第2及び第3スイッチング素子をターンオフ。

(8)’前記負側スイッチング素子をターンオフ,前記第4スイッチング素子をターンオン。

【請求項15】

前記通電制御回路は、前記正側及び負側スイッチング素子,並びに前記第1ないし第4スイッチング素子を以下のように切り替えることで(但し、オンと記載したもの以外はオフとし、ターンオフ,ターンオンと記載したもの以外は以前のオンオフ状態を維持するものとする)、前記(1)〜(8)の通電経路を形成することを特徴とする請求項9記載の半導体スイッチング素子の駆動回路。

(0)初期状態を、前記第4スイッチング素子がオンである前記駆動対象スイッチング素子のターンオフ状態とする。

(1)前記負側スイッチング素子をオン。

(5)前記負側スイッチング素子をターンオフしてから、前記正側スイッチング素子をターンオン。

(2)前記第1スイッチング素子をターンオン。

(3)前記第4スイッチング素子をターンオフ。

(4)前記第1スイッチング素子をターンオフ,前記第3スイッチング素子をターンオン。

(5)前記正側スイッチング素子をターンオフしてから前記正側スイッチング素子をターンオン。

(2)前記正側スイッチング素子をターンオフしてから、前記負側スイッチング素子をターンオン。

(6)前記第2スイッチング素子をターンオン。

(7)前記第3スイッチング素子をターンオフ。

(8)前記第2スイッチング素子をターンオフ,前記第4スイッチング素子をターンオンしてから、前記負側スイッチング素子をターンオフ。

【請求項16】

前記通電制御回路は、前記(5)の通電経路において前記正側スイッチング素子をターンオフしてから前記正側スイッチング素子をターンオンするまでの期間長と、前記(8)の通電経路において前記負側スイッチング素子をターンオフしてから、次回に行う前記(1)の通電経路において前記負側スイッチング素子をターンオンするまでの期間長とを調整することで、前記正側及び負側コンデンサの端子電圧を調整することを特徴とする請求項15記載の半導体スイッチング素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【公開番号】特開2012−169904(P2012−169904A)

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願番号】特願2011−29731(P2011−29731)

【出願日】平成23年2月15日(2011.2.15)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願日】平成23年2月15日(2011.2.15)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]