半導体スイッチング素子駆動用電源回路

【課題】従来の自給型ゲート駆動用電源回路では、RCDスナバ回路を充放電動作で使用するため、スナバ抵抗における充放電損失が大きくなり高周波動作では変換効率が低下し、装置が大型になる。さらに駆動用の電源として単一電源しか作れないため、IGBTのゲートに逆バイアスをかけることができずターンオフ損失が大きい。

【解決手段】上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、上アーム側スイッチング素子駆動回路と、下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、バイパスコンデンサの充放電電流を上アーム側スイッチング素子駆動回路と下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、記整流回路の出力を各々のスイッチング素子駆動回路用電源とする。

【解決手段】上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、上アーム側スイッチング素子駆動回路と、下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、バイパスコンデンサの充放電電流を上アーム側スイッチング素子駆動回路と下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、記整流回路の出力を各々のスイッチング素子駆動回路用電源とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体スイッチング素子をオンオフさせるための駆動回路の駆動用電源回路に関するもので、詳しくは自給式の駆動用電源回路における小形、低価格化のための回路構成技術に関する。

【背景技術】

【0002】

図9に、従来の自給式駆動用電源回路を用いたIGBT駆動回路を、図10にゲート駆動回路の詳細を示す。図9の回路構成では、IGBT4の主端子(コレクタ、エミッタ)と並列にダイオード101、抵抗102およびスナバコンデンサ103からなるRCDスナバ回路100が並列に、このRCDスナバ回路100のスナバコンデンサ103と並列にコンデンサ104とコンデンサ105の直列回路が、各々接続されている。さらにコンデンサ105にはダイオード107が並列に接続され、コンデンサ104と105の直列接続点はダイオード106を介しゲート駆動回路3の電源用コンデンサ8に接続されている。図10にゲート駆動回路30の詳細を示す。電源用コンデンサ8と並列にトランジスタ301とトランジスタ302からなるコンプリメンタリ回路が接続され、さらにこのコンプリメンタリ回路の出力は抵抗303を介してIGBT4のゲートに接続される。このような構成において、トランジスタ301がオンすると、IGBT4のゲート容量が充電され、IGBTはオン状態となる。トランジスタ302がオンすると、IGBTのゲート容量は放電され、IGBTはオフ状態となる。

【0003】

図9の回路構成において、IGBT4がオン状態からオフになると、スナバコンデンサ103はダイオード101を介して充電され、これに伴い、コンデンサ104、105も充電される。この充電動作によりコンデンサ105の電圧が電源用コンデンサ8の電圧より高くなるとダイオード106が導通して、電源用コンデンサ8が充電されることになる。次にIGBT4がオンすると、コンデンサ103、104、105に蓄えられていた電荷はスナバ抵抗102、IGBT4を介して放電される。図5の回路の詳細な動作については、特許文献1に開示されている。

【特許文献1】特開8−51770号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上述のように、図9に示した従来の自給型ゲート駆動用電源回路では、RCDスナバ回路100を充放電動作で使用するため、スナバ抵抗102における充放電損失が大きくなり高周波動作では変換効率が低下すると同時に、装置が大型になる。さらに駆動用の電源として正極の単一電源しか作れないため、IGBTのゲートに逆バイアスをかけることができずターンオフ損失が大きいという課題がある。

【課題を解決するための手段】

【0005】

上述の課題を解決するために、第1の発明においては、直流電源と、前記直流電源に並列に接続される直列接続された上下アーム対の半導体スイッチング素子と、これら上下アームをそれぞれ駆動する二つのスイッチング素子駆動回路を含むスイッチング回路において、前記上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、前記上アーム側スイッチング素子駆動回路と、前記下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、前記バイパスコンデンサの充放電電流を前記上アーム側スイッチング素子駆動回路と前記下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、前記整流回路の出力を各々のスイッチング素子駆動回路用電源とする。

第2の発明においては、第1の発明における前記バイパスコンデンサと直列にリアクトルを接続する。

【0006】

第3の発明においては、第1の発明における前記各々の電源部に設けた整流回路は、ダイオード直列回路とコンデンサ直列回路の並列回路で構成する。

第4の発明においては、第1の発明における前記各々の電源部に設けた整流回路は、ダイオード直列回路とコンデンサ直列回路をリアクトルを介して並列接続して構成する。

第5の発明においては、第1〜第4の発明における前記直流電源から直流−直流変換回路を通して前記整流回路のコンデンサ直列回路を充電する。

【発明の効果】

【0007】

本発明では、スイッチング素子の主端子間を整流して正負の駆動用電源を得ているため、ゲート駆動用の順バイアス電源だけでなく逆バイアス電源も作ることができ、動作損失を低損失化できる。結果として、装置の高効率化だけでなく、低価格化、小形化及び逆バイアス電源利用による装置の高信頼性化が可能となる。

【発明を実施するための最良の形態】

【0008】

本発明の第1の要点は、半導体スイッチング素子の両端電圧を直列コンデンサを介し、ダイオード直列回路とコンデンサ直列回路とを並列接続して構成したハーフブリッジ形ダイオード整流器により整流して得られた直流中間点を持つ正負の直流電圧のうち、正側直流電圧を前記半導体スイッチング素子をオン駆動するための駆動回路の順バイアス側電源として供給し、負側直流電圧を前記半導体スイッチング素子をオフ駆動するための駆動回路の逆バイアス側電源として供給することである。

【0009】

また、本発明の第2の要点は、上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、上アーム側スイッチング素子駆動回路と、下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、前記バイパスコンデンサの充放電電流を前記上アーム側スイッチング素子駆動回路と前記下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流して得られた直流中間点を持つ正負の直流電圧のうち、正側直流電圧を前記半導体スイッチング素子をオン駆動するための駆動回路の順バイアス側電源として供給し、負側直流電圧を前記半導体スイッチング素子をオフ駆動するための駆動回路の逆バイアス側電源として供給することである。

【実施例1】

【0010】

図1に、本発明の第1の実施例を示す回路構成図を示す。図1では、IGBT4を駆動するためのゲート駆動回路3の出力がIGBT4のゲートとエミッタに接続されている。また電源用コンデンサ8、9とダイオード6、7によりハーフブリッジ形ダイオード整流回路200が構成され、その電源用コンデンサ8、9は、各々ゲート駆動回路3の順バイアス用電源及び逆バイアス用電源となる。ハーフブリッジ形ダイオード整流回路200のダイオード側交流入力点は直列にコンデンサ5を介してIGBT4のコレクタに、電源用コンデンサ8、9の直列接続点は直接IGBT4のエミッタに、各々接続された構成である。

【0011】

このような回路構成において、IGBT4がオン状態からオフすると、直流電源1→負荷2→コンデンサ5→ダイオード6→電源用コンデンサ8→直流電源1の経路で電流が流れ、コンデンサ5と同時に電源用コンデンサ8を充電する。次にIGBT4がオンすると、コンデンサ5に充電されていたエネルギーにより、コンデンサ5→IGBT4→電源コンデンサ9→ダイオード7→コンデンサ5の経路で電流が流れ、電源コンデンサ9を充電する。

【0012】

このIGBT4のスイッチングによるオンオフの一連の動作により、IGBT4を駆動するための電源となる電源用コンデンサ8、9の充電が低損失で可能となる。

図4にゲート駆動回路3の詳細例を示す。電源用コンデンサ8と9の直列回路と並列にトランジスタ301とトランジスタ302からなるコンプリメンタリ回路が接続され、さらにこのコンプリメンタリ回路の出力は抵抗303を介してIGBT4のゲートに、電源用コンデンサ8と9の直列接続点はIGBTのエミッタに、各々接続される。トランジスタ301がオンすると、電源用コンデンサ8でIGBT4のゲート容量が充電され、IGBTはオン状態となる。トランジスタ302がオンすると、電源用コンデンサ9でIGBTのゲート容量は放電後逆バイアスされ、IGBTはオフ状態となる。

【実施例2】

【0013】

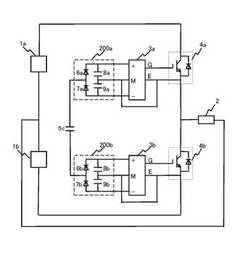

図2に、本発明の第2の実施例を示す。図2は図1に示したIGBT駆動用電源回路を、ブリッジ接続されたIGBT式インバータ回路に適用した場合の構成図である。インバータ回路装置の起動前に、直流電源300により、ダイオード401、402を介して、2つのゲート駆動回路3a、3bの順バイアス側電源用コンデンサ8a、8bを予め充電しておくことで、インバータ回路の起動が可能になる。起動後の動作は図1と同様であるため、詳細は省略する。

【実施例3】

【0014】

図3に、本発明の第3の実施例を示す。本発明による実施例図1の変形例である。図1との相違点は、コンデンサ5とハーフブリッジ形ダイオード整流回路200との間にダイオード202と電流制限用抵抗201の並列回路が挿入されている点である。抵抗201により、IGBT4がオンした時のコンデンサ5の放電電流最大値を制限する。IGBT4の許容最大電流値が問題となる場合には有効な手段となる。

【実施例4】

【0015】

図5に、本発明の第4の実施例を示す。直列接続されたIGBT4a、4bを駆動するためのゲート駆動回路3a、3bが各々IGBT4a、4bのゲート−エミッタに接続される。また電源用コンデンサ8a、9aとダイオード6a、7aによりハーフブリッジ形ダイオード整流回路200aが構成され、その電源用コンデンサ8a、9aは、各々ゲート駆動回路3aの順バイアス用電源及び逆バイアス用電源として接続される。同様に、電源用コンデンサ8b、9bとダイオード6b、7bによりハーフブリッジ形ダイオード整流回路200bが構成され、その電源用コンデンサ8b、9bは、各々ゲート駆動回路3bの順バイアス用電源及び逆バイアス用電源として接続される。

各々のハーフブリッジ形ダイオード整流回路200a、200bのダイオード側交流入力点はコンデンサ5cを介して直列接続され、電源用コンデンサ8a、9aの中間接続点は直接IGBT4aのエミッタに、また電源用コンデンサ8b、9bの中間接続点は直接IGBT4bのエミッタに各々接続された構成である。

【0016】

このような回路構成において、IGBT4aがオフ状態からオンし、IGBT4bがオン状態からオフすると、直流電源1b、1a→IGBT4a→電源用コンデンサ9a→ダイオード7a→コンデンサ5c→ダイオード6b→電源用コンデンサ8b→直流電源1b、1aの経路で電流が流れ、コンデンサ5cと同時に電源用コンデンサ8b、9aを充電する。次にIGBT4aがオフし4bがオンすると、コンデンサ5cに充電されていたエネルギーにより、コンデンサ5c→ダイオード6a→電源用コンデンサ8a→IGBT4b→電源コンデンサ9b→ダイオード7b→コンデンサ5cの経路で電流が流れ、電源コンデンサ9b、8aを充電する。

このIGBT4a、4bのスイッチングによるオンオフの一連の動作により、IGBT4a、4bを駆動するための電源となる電源用コンデンサ8a、8b、9a、9bの充電が低損失で可能となる。

【実施例5】

【0017】

図6に、本発明の第5の実施例を示す。図5に示したハーフブリッジ形ダイオード整流回路200a、200bの各々のダイオード側交流入力点間を直列接続するコンデンサ5cと直列にリアクトル11を挿入した構成である。このリアクトル11を追加することで、IGBT4a、4bのスイッチングにより流れるコンデンサ5cの充放電電流のピーク値を小さくする事が出来るため、ダイオード6a、6b、7a、7b、及び電源用コンデンサ8a、8b、9a、9bの電流定格を下げる効果があり、装置の一層の小形化が可能となる。

【実施例6】

【0018】

図7に、本発明の第6の実施例を示す。図6で挿入したリアクトル11の代わりに、リアクトル11a、11bを各々ハーフブリッジ形ダイオード整流回路200a、200bの直流部分に挿入した構成である。

【0019】

このような回路構成において、IGBT4aがオフ状態からオンし、IGBT4bがオン状態からオフすると、直流電源1b、1a→IGBT4a→電源用コンデンサ9a→ダイオード7a→コンデンサ5c→ダイオード6b→リアクトル11b→電源用コンデンサ8b→直流電源1b、1aの経路で電流が流れ、コンデンサ5cと同時に電源用コンデンサ8b、9aを充電し、さらにリアクトル11bにもエネルギーが蓄積される。コンデンサ5cの電圧が直流電源1a、1bの合計と同じになりその充電が完了したあとも、リアクトル11bに蓄えられたエネルギーにより、リアクトル11b→電源コンデンサ8b→電源コンデンサ9b→ダイオード7b→ダイオード6b→リアクトル11bの経路で電流が還流し、このリアクトル11bのエネルギーにより電源コンデンサ8b、9bのさらなる充電が可能になる。

【0020】

次にIGBT4aがオフし4bがオンすると、コンデンサ5cに充電されていたエネルギーにより、コンデンサ5c→ダイオード6a→リアクトル11a→電源用コンデンサ8a→IGBT4b→電源コンデンサ9b→ダイオード7b→コンデンサ5cの経路で電流が流れ、電源コンデンサ9b、8aを充電し、さらにリアクトル11aにエネルギーが蓄積される。コンデンサ5cの電圧がゼロとなりその放電が完了した後も、リアクトル11aに蓄積されたエネルギーは、リアクトル11a→電源コンデンサ8a→電源コンデンサ9a→ダイオード7a→ダイオード6a→リアクトル11aの経路で還流し、このリアクトル11aのエネルギーで電源コンデンサ8a、9aのさらなる充電が可能となる。このため、リアクトル11a、11bの追加により、図5の回路に対し、コンデンサ5cのピーク電流を下げるだけでなく、電源コンデンサ8a、8b、9a、9bの充電効率を高める効果があり、一層の小形化が可能となる。

【実施例7】

【0021】

図8に、本発明の第7の実施例を示す。図8の回路は図5の回路に対し、動作開始前の初期充電を行うため、直流−直流変換回路の一つであるシリーズレギュレータ回路19を追加し、ダイオード12で整流回路200aの電源コンデンサ8aを、ダイオード13で整流回路200bの電源コンデンサ8bを充電するようにした構成である。IGBT4a、4bの起動前にシリーズレギュレータ回路19より、直流電源1a、1bの電圧を使い、2つのゲート駆動回路3a、3bの順バイアス側電源用コンデンサ8a、8bを予め充電しておくことで、IGBT4a、4bの起動が可能になる。起動後の電源は図5〜図7の説明の通り、コンデンサ5cの充放電により自給している。この結果、シリーズレギュレータ回路19は初期充電用途だけであり、極小さい容量の回路が適用可能である。

【産業上の利用可能性】

【0022】

本発明は、ゲート駆動回路の駆動用電源をスイッチング素子の主端子から得る回路方式であり、インバータ、UPS、スイッチング電源など、スイッチング動作で電力変換を行う装置のほとんどに適用が可能である。

【図面の簡単な説明】

【0023】

【図1】本発明の第1の実施例を示す回路図である。

【図2】本発明の第2の実施例を示す回路図である。

【図3】本発明の第3の実施例を示す回路図である。

【図4】図1〜図3のゲート駆動回路の構成例を示す。

【図5】本発明の第4の実施例を示す回路図である。

【図6】本発明の第5の実施例を示す回路図である。

【図7】本発明の第6の実施例を示す回路図である。

【図8】本発明の第7の実施例を示す回路図である。

【図9】従来のゲート駆動電源回路例を示す。

【図10】図5のゲート駆動回路の詳細を示す。

【符号の説明】

【0024】

1、1a、1b・・・直流電源 2・・・負荷

3、3a、3b、30・・・ゲート駆動回路 4、4a、4b・・・IGBT

5、5a、5b、5c、104、105・・・コンデンサ

103・・・スナバコンデンサ

6、7、6a、7a、6b、7b、101、106、107、202、401、402・・・ダイオード 直流電源・・・300

8、9、8a、9a、8b、9b・・・電源用コンデンサ

11、11a、11b・・・リアクトル

102、201、303・・・抵抗

200、200a、200b・・・ハーフブリッジ形ダイオード整流回路

301、302・・・トランジスタ

【技術分野】

【0001】

本発明は、半導体スイッチング素子をオンオフさせるための駆動回路の駆動用電源回路に関するもので、詳しくは自給式の駆動用電源回路における小形、低価格化のための回路構成技術に関する。

【背景技術】

【0002】

図9に、従来の自給式駆動用電源回路を用いたIGBT駆動回路を、図10にゲート駆動回路の詳細を示す。図9の回路構成では、IGBT4の主端子(コレクタ、エミッタ)と並列にダイオード101、抵抗102およびスナバコンデンサ103からなるRCDスナバ回路100が並列に、このRCDスナバ回路100のスナバコンデンサ103と並列にコンデンサ104とコンデンサ105の直列回路が、各々接続されている。さらにコンデンサ105にはダイオード107が並列に接続され、コンデンサ104と105の直列接続点はダイオード106を介しゲート駆動回路3の電源用コンデンサ8に接続されている。図10にゲート駆動回路30の詳細を示す。電源用コンデンサ8と並列にトランジスタ301とトランジスタ302からなるコンプリメンタリ回路が接続され、さらにこのコンプリメンタリ回路の出力は抵抗303を介してIGBT4のゲートに接続される。このような構成において、トランジスタ301がオンすると、IGBT4のゲート容量が充電され、IGBTはオン状態となる。トランジスタ302がオンすると、IGBTのゲート容量は放電され、IGBTはオフ状態となる。

【0003】

図9の回路構成において、IGBT4がオン状態からオフになると、スナバコンデンサ103はダイオード101を介して充電され、これに伴い、コンデンサ104、105も充電される。この充電動作によりコンデンサ105の電圧が電源用コンデンサ8の電圧より高くなるとダイオード106が導通して、電源用コンデンサ8が充電されることになる。次にIGBT4がオンすると、コンデンサ103、104、105に蓄えられていた電荷はスナバ抵抗102、IGBT4を介して放電される。図5の回路の詳細な動作については、特許文献1に開示されている。

【特許文献1】特開8−51770号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上述のように、図9に示した従来の自給型ゲート駆動用電源回路では、RCDスナバ回路100を充放電動作で使用するため、スナバ抵抗102における充放電損失が大きくなり高周波動作では変換効率が低下すると同時に、装置が大型になる。さらに駆動用の電源として正極の単一電源しか作れないため、IGBTのゲートに逆バイアスをかけることができずターンオフ損失が大きいという課題がある。

【課題を解決するための手段】

【0005】

上述の課題を解決するために、第1の発明においては、直流電源と、前記直流電源に並列に接続される直列接続された上下アーム対の半導体スイッチング素子と、これら上下アームをそれぞれ駆動する二つのスイッチング素子駆動回路を含むスイッチング回路において、前記上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、前記上アーム側スイッチング素子駆動回路と、前記下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、前記バイパスコンデンサの充放電電流を前記上アーム側スイッチング素子駆動回路と前記下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、前記整流回路の出力を各々のスイッチング素子駆動回路用電源とする。

第2の発明においては、第1の発明における前記バイパスコンデンサと直列にリアクトルを接続する。

【0006】

第3の発明においては、第1の発明における前記各々の電源部に設けた整流回路は、ダイオード直列回路とコンデンサ直列回路の並列回路で構成する。

第4の発明においては、第1の発明における前記各々の電源部に設けた整流回路は、ダイオード直列回路とコンデンサ直列回路をリアクトルを介して並列接続して構成する。

第5の発明においては、第1〜第4の発明における前記直流電源から直流−直流変換回路を通して前記整流回路のコンデンサ直列回路を充電する。

【発明の効果】

【0007】

本発明では、スイッチング素子の主端子間を整流して正負の駆動用電源を得ているため、ゲート駆動用の順バイアス電源だけでなく逆バイアス電源も作ることができ、動作損失を低損失化できる。結果として、装置の高効率化だけでなく、低価格化、小形化及び逆バイアス電源利用による装置の高信頼性化が可能となる。

【発明を実施するための最良の形態】

【0008】

本発明の第1の要点は、半導体スイッチング素子の両端電圧を直列コンデンサを介し、ダイオード直列回路とコンデンサ直列回路とを並列接続して構成したハーフブリッジ形ダイオード整流器により整流して得られた直流中間点を持つ正負の直流電圧のうち、正側直流電圧を前記半導体スイッチング素子をオン駆動するための駆動回路の順バイアス側電源として供給し、負側直流電圧を前記半導体スイッチング素子をオフ駆動するための駆動回路の逆バイアス側電源として供給することである。

【0009】

また、本発明の第2の要点は、上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、上アーム側スイッチング素子駆動回路と、下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、前記バイパスコンデンサの充放電電流を前記上アーム側スイッチング素子駆動回路と前記下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流して得られた直流中間点を持つ正負の直流電圧のうち、正側直流電圧を前記半導体スイッチング素子をオン駆動するための駆動回路の順バイアス側電源として供給し、負側直流電圧を前記半導体スイッチング素子をオフ駆動するための駆動回路の逆バイアス側電源として供給することである。

【実施例1】

【0010】

図1に、本発明の第1の実施例を示す回路構成図を示す。図1では、IGBT4を駆動するためのゲート駆動回路3の出力がIGBT4のゲートとエミッタに接続されている。また電源用コンデンサ8、9とダイオード6、7によりハーフブリッジ形ダイオード整流回路200が構成され、その電源用コンデンサ8、9は、各々ゲート駆動回路3の順バイアス用電源及び逆バイアス用電源となる。ハーフブリッジ形ダイオード整流回路200のダイオード側交流入力点は直列にコンデンサ5を介してIGBT4のコレクタに、電源用コンデンサ8、9の直列接続点は直接IGBT4のエミッタに、各々接続された構成である。

【0011】

このような回路構成において、IGBT4がオン状態からオフすると、直流電源1→負荷2→コンデンサ5→ダイオード6→電源用コンデンサ8→直流電源1の経路で電流が流れ、コンデンサ5と同時に電源用コンデンサ8を充電する。次にIGBT4がオンすると、コンデンサ5に充電されていたエネルギーにより、コンデンサ5→IGBT4→電源コンデンサ9→ダイオード7→コンデンサ5の経路で電流が流れ、電源コンデンサ9を充電する。

【0012】

このIGBT4のスイッチングによるオンオフの一連の動作により、IGBT4を駆動するための電源となる電源用コンデンサ8、9の充電が低損失で可能となる。

図4にゲート駆動回路3の詳細例を示す。電源用コンデンサ8と9の直列回路と並列にトランジスタ301とトランジスタ302からなるコンプリメンタリ回路が接続され、さらにこのコンプリメンタリ回路の出力は抵抗303を介してIGBT4のゲートに、電源用コンデンサ8と9の直列接続点はIGBTのエミッタに、各々接続される。トランジスタ301がオンすると、電源用コンデンサ8でIGBT4のゲート容量が充電され、IGBTはオン状態となる。トランジスタ302がオンすると、電源用コンデンサ9でIGBTのゲート容量は放電後逆バイアスされ、IGBTはオフ状態となる。

【実施例2】

【0013】

図2に、本発明の第2の実施例を示す。図2は図1に示したIGBT駆動用電源回路を、ブリッジ接続されたIGBT式インバータ回路に適用した場合の構成図である。インバータ回路装置の起動前に、直流電源300により、ダイオード401、402を介して、2つのゲート駆動回路3a、3bの順バイアス側電源用コンデンサ8a、8bを予め充電しておくことで、インバータ回路の起動が可能になる。起動後の動作は図1と同様であるため、詳細は省略する。

【実施例3】

【0014】

図3に、本発明の第3の実施例を示す。本発明による実施例図1の変形例である。図1との相違点は、コンデンサ5とハーフブリッジ形ダイオード整流回路200との間にダイオード202と電流制限用抵抗201の並列回路が挿入されている点である。抵抗201により、IGBT4がオンした時のコンデンサ5の放電電流最大値を制限する。IGBT4の許容最大電流値が問題となる場合には有効な手段となる。

【実施例4】

【0015】

図5に、本発明の第4の実施例を示す。直列接続されたIGBT4a、4bを駆動するためのゲート駆動回路3a、3bが各々IGBT4a、4bのゲート−エミッタに接続される。また電源用コンデンサ8a、9aとダイオード6a、7aによりハーフブリッジ形ダイオード整流回路200aが構成され、その電源用コンデンサ8a、9aは、各々ゲート駆動回路3aの順バイアス用電源及び逆バイアス用電源として接続される。同様に、電源用コンデンサ8b、9bとダイオード6b、7bによりハーフブリッジ形ダイオード整流回路200bが構成され、その電源用コンデンサ8b、9bは、各々ゲート駆動回路3bの順バイアス用電源及び逆バイアス用電源として接続される。

各々のハーフブリッジ形ダイオード整流回路200a、200bのダイオード側交流入力点はコンデンサ5cを介して直列接続され、電源用コンデンサ8a、9aの中間接続点は直接IGBT4aのエミッタに、また電源用コンデンサ8b、9bの中間接続点は直接IGBT4bのエミッタに各々接続された構成である。

【0016】

このような回路構成において、IGBT4aがオフ状態からオンし、IGBT4bがオン状態からオフすると、直流電源1b、1a→IGBT4a→電源用コンデンサ9a→ダイオード7a→コンデンサ5c→ダイオード6b→電源用コンデンサ8b→直流電源1b、1aの経路で電流が流れ、コンデンサ5cと同時に電源用コンデンサ8b、9aを充電する。次にIGBT4aがオフし4bがオンすると、コンデンサ5cに充電されていたエネルギーにより、コンデンサ5c→ダイオード6a→電源用コンデンサ8a→IGBT4b→電源コンデンサ9b→ダイオード7b→コンデンサ5cの経路で電流が流れ、電源コンデンサ9b、8aを充電する。

このIGBT4a、4bのスイッチングによるオンオフの一連の動作により、IGBT4a、4bを駆動するための電源となる電源用コンデンサ8a、8b、9a、9bの充電が低損失で可能となる。

【実施例5】

【0017】

図6に、本発明の第5の実施例を示す。図5に示したハーフブリッジ形ダイオード整流回路200a、200bの各々のダイオード側交流入力点間を直列接続するコンデンサ5cと直列にリアクトル11を挿入した構成である。このリアクトル11を追加することで、IGBT4a、4bのスイッチングにより流れるコンデンサ5cの充放電電流のピーク値を小さくする事が出来るため、ダイオード6a、6b、7a、7b、及び電源用コンデンサ8a、8b、9a、9bの電流定格を下げる効果があり、装置の一層の小形化が可能となる。

【実施例6】

【0018】

図7に、本発明の第6の実施例を示す。図6で挿入したリアクトル11の代わりに、リアクトル11a、11bを各々ハーフブリッジ形ダイオード整流回路200a、200bの直流部分に挿入した構成である。

【0019】

このような回路構成において、IGBT4aがオフ状態からオンし、IGBT4bがオン状態からオフすると、直流電源1b、1a→IGBT4a→電源用コンデンサ9a→ダイオード7a→コンデンサ5c→ダイオード6b→リアクトル11b→電源用コンデンサ8b→直流電源1b、1aの経路で電流が流れ、コンデンサ5cと同時に電源用コンデンサ8b、9aを充電し、さらにリアクトル11bにもエネルギーが蓄積される。コンデンサ5cの電圧が直流電源1a、1bの合計と同じになりその充電が完了したあとも、リアクトル11bに蓄えられたエネルギーにより、リアクトル11b→電源コンデンサ8b→電源コンデンサ9b→ダイオード7b→ダイオード6b→リアクトル11bの経路で電流が還流し、このリアクトル11bのエネルギーにより電源コンデンサ8b、9bのさらなる充電が可能になる。

【0020】

次にIGBT4aがオフし4bがオンすると、コンデンサ5cに充電されていたエネルギーにより、コンデンサ5c→ダイオード6a→リアクトル11a→電源用コンデンサ8a→IGBT4b→電源コンデンサ9b→ダイオード7b→コンデンサ5cの経路で電流が流れ、電源コンデンサ9b、8aを充電し、さらにリアクトル11aにエネルギーが蓄積される。コンデンサ5cの電圧がゼロとなりその放電が完了した後も、リアクトル11aに蓄積されたエネルギーは、リアクトル11a→電源コンデンサ8a→電源コンデンサ9a→ダイオード7a→ダイオード6a→リアクトル11aの経路で還流し、このリアクトル11aのエネルギーで電源コンデンサ8a、9aのさらなる充電が可能となる。このため、リアクトル11a、11bの追加により、図5の回路に対し、コンデンサ5cのピーク電流を下げるだけでなく、電源コンデンサ8a、8b、9a、9bの充電効率を高める効果があり、一層の小形化が可能となる。

【実施例7】

【0021】

図8に、本発明の第7の実施例を示す。図8の回路は図5の回路に対し、動作開始前の初期充電を行うため、直流−直流変換回路の一つであるシリーズレギュレータ回路19を追加し、ダイオード12で整流回路200aの電源コンデンサ8aを、ダイオード13で整流回路200bの電源コンデンサ8bを充電するようにした構成である。IGBT4a、4bの起動前にシリーズレギュレータ回路19より、直流電源1a、1bの電圧を使い、2つのゲート駆動回路3a、3bの順バイアス側電源用コンデンサ8a、8bを予め充電しておくことで、IGBT4a、4bの起動が可能になる。起動後の電源は図5〜図7の説明の通り、コンデンサ5cの充放電により自給している。この結果、シリーズレギュレータ回路19は初期充電用途だけであり、極小さい容量の回路が適用可能である。

【産業上の利用可能性】

【0022】

本発明は、ゲート駆動回路の駆動用電源をスイッチング素子の主端子から得る回路方式であり、インバータ、UPS、スイッチング電源など、スイッチング動作で電力変換を行う装置のほとんどに適用が可能である。

【図面の簡単な説明】

【0023】

【図1】本発明の第1の実施例を示す回路図である。

【図2】本発明の第2の実施例を示す回路図である。

【図3】本発明の第3の実施例を示す回路図である。

【図4】図1〜図3のゲート駆動回路の構成例を示す。

【図5】本発明の第4の実施例を示す回路図である。

【図6】本発明の第5の実施例を示す回路図である。

【図7】本発明の第6の実施例を示す回路図である。

【図8】本発明の第7の実施例を示す回路図である。

【図9】従来のゲート駆動電源回路例を示す。

【図10】図5のゲート駆動回路の詳細を示す。

【符号の説明】

【0024】

1、1a、1b・・・直流電源 2・・・負荷

3、3a、3b、30・・・ゲート駆動回路 4、4a、4b・・・IGBT

5、5a、5b、5c、104、105・・・コンデンサ

103・・・スナバコンデンサ

6、7、6a、7a、6b、7b、101、106、107、202、401、402・・・ダイオード 直流電源・・・300

8、9、8a、9a、8b、9b・・・電源用コンデンサ

11、11a、11b・・・リアクトル

102、201、303・・・抵抗

200、200a、200b・・・ハーフブリッジ形ダイオード整流回路

301、302・・・トランジスタ

【特許請求の範囲】

【請求項1】

直流電源と、前記直流電源に並列に接続される直列接続された上下アーム対の半導体スイッチング素子と、これら上下アームをそれぞれ駆動する二つのスイッチング素子駆動回路を含むスイッチング回路において、前記上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、前記上アーム側スイッチング素子駆動回路と、前記下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、前記バイパスコンデンサの充放電電流を前記上アーム側スイッチング素子駆動回路と前記下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、前記整流回路の出力を各々のスイッチング素子駆動回路用電源とすることを特徴とする半導体スイッチング素子駆動用電源回路。

【請求項2】

前記バイパスコンデンサと直列にリアクトルを接続することを特徴とする請求項1に記載の半導体スイッチング素子駆動用電源回路。

【請求項3】

前記各々の電源部に設けた整流回路は、ダイオード直列回路とコンデンサ直列回路との並列回路で構成することを特徴とする請求項1に記載の半導体スイッチング素子駆動用電源回路。

【請求項4】

前記各々の電源部に設けた整流回路は、ダイオード直列回路とコンデンサ直列回路とをリアクトルを介して並列接続して構成することを特徴とする請求項1に記載の半導体スイッチング素子駆動用電源回路。

【請求項5】

前記直流電源から直流−直流変換回路を通して前記整流回路のコンデンサ直列回路を充電することを特徴とする請求項1〜4のいずれか1項に記載の半導体スイッチング素子駆動用電源回路。

【請求項1】

直流電源と、前記直流電源に並列に接続される直列接続された上下アーム対の半導体スイッチング素子と、これら上下アームをそれぞれ駆動する二つのスイッチング素子駆動回路を含むスイッチング回路において、前記上下アーム対の半導体スイッチング素子が交互にオンオフ動作することにより、前記上アーム側スイッチング素子駆動回路と、前記下アーム側スイッチング素子駆動回路との間に生じる電位差変動により充放電を繰り返すバイパスコンデンサを備え、前記バイパスコンデンサの充放電電流を前記上アーム側スイッチング素子駆動回路と前記下アーム側スイッチング素子駆動回路の各々の電源部に設けた整流回路で整流し、前記整流回路の出力を各々のスイッチング素子駆動回路用電源とすることを特徴とする半導体スイッチング素子駆動用電源回路。

【請求項2】

前記バイパスコンデンサと直列にリアクトルを接続することを特徴とする請求項1に記載の半導体スイッチング素子駆動用電源回路。

【請求項3】

前記各々の電源部に設けた整流回路は、ダイオード直列回路とコンデンサ直列回路との並列回路で構成することを特徴とする請求項1に記載の半導体スイッチング素子駆動用電源回路。

【請求項4】

前記各々の電源部に設けた整流回路は、ダイオード直列回路とコンデンサ直列回路とをリアクトルを介して並列接続して構成することを特徴とする請求項1に記載の半導体スイッチング素子駆動用電源回路。

【請求項5】

前記直流電源から直流−直流変換回路を通して前記整流回路のコンデンサ直列回路を充電することを特徴とする請求項1〜4のいずれか1項に記載の半導体スイッチング素子駆動用電源回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−80774(P2012−80774A)

【公開日】平成24年4月19日(2012.4.19)

【国際特許分類】

【出願番号】特願2012−13711(P2012−13711)

【出願日】平成24年1月26日(2012.1.26)

【分割の表示】特願2007−182300(P2007−182300)の分割

【原出願日】平成19年7月11日(2007.7.11)

【出願人】(000005234)富士電機株式会社 (3,146)

【Fターム(参考)】

【公開日】平成24年4月19日(2012.4.19)

【国際特許分類】

【出願日】平成24年1月26日(2012.1.26)

【分割の表示】特願2007−182300(P2007−182300)の分割

【原出願日】平成19年7月11日(2007.7.11)

【出願人】(000005234)富士電機株式会社 (3,146)

【Fターム(参考)】

[ Back to top ]