半導体スイッチング装置

【課題】ノーマリオン型の半導体素子を用いて、より安全なノーマリオフ的な動作となる簡単な構成の半導体スイッチング装置を提供する。

【解決手段】市販のゲートドライバ11を用いて、ノーマリオン型のJFET10を駆動する。このとき、NチャネルのJFET10のソースSをゲートドライバ11の高圧側の電源ノード12に接続し、ゲートGをゲートドライバ11の出力ノード15に接続する。入力された制御信号VsigがLレベルの場合、出力ノード15の電位Vgは低圧側の電源ノード13の電位Vnに等しくなる。したがって、Lレベルの制御信号Vsig入力に対して、ゲート・ソース間に負の閾値電圧以下の電圧が印加されてJFET10がターンオフするというノーマリオフ的な動作が実現している。

【解決手段】市販のゲートドライバ11を用いて、ノーマリオン型のJFET10を駆動する。このとき、NチャネルのJFET10のソースSをゲートドライバ11の高圧側の電源ノード12に接続し、ゲートGをゲートドライバ11の出力ノード15に接続する。入力された制御信号VsigがLレベルの場合、出力ノード15の電位Vgは低圧側の電源ノード13の電位Vnに等しくなる。したがって、Lレベルの制御信号Vsig入力に対して、ゲート・ソース間に負の閾値電圧以下の電圧が印加されてJFET10がターンオフするというノーマリオフ的な動作が実現している。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体スイッチング素子とそのゲート制御回路とを含む半導体スイッチング装置に関する。

【背景技術】

【0002】

ワイドバンドギャップ半導体であるSiC(Silicon Carbide)は、高温特性、高周波特性、高耐電圧、低オン抵抗などの面で、Si(Silicon)に比べ優れている。電力変換回路のスイッチング素子として、SiC半導体デバイスを使用することで、スイッチング周波数を上昇させ、インダクタやキャパシタを小型化できる。その結果、高耐電圧、低オン抵抗の性質と相まって、体積が小さく大電力の扱える電力変換回路が実現でき、電源の高電力密度化が可能となる。SiCデバイスは、受動素子としてショットキバリアダイオード素子が商用に供され、能動素子としてはJFET(Junction Field Effect Transistor)が試作されている。

【0003】

ところで、JFETは一般にノーマリオン型の素子である。このため、故障時にJFETの主電流を遮断するための保護回路が必要になるなど、ノーマリオフ型のデバイスに比べてゲートドライバ回路の設計が困難である。そこで、ノーマリオフ型のSiCJFETを使用した回路の開発(たとえば、非特許文献1参照)や、SiCJFETとSiMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)とをカスコード接続したデバイスの開発が行なわれ、回路実装が試みられている(たとえば、非特許文献2参照)。また、ノーマリオン型のSiCJFET用の新たなゲートドライブ回路の設計(たとえば、非特許文献3参照)も試みられている。

【非特許文献1】石川(Katsumi Ishikawa)等、外6名、「Normally-off SiC-JFET inverter with low-voltage control and a high-speed drive circuit」、Pro-ceedings of ISPSD'07、2007年、p.217-220

【非特許文献2】舟木(Tsuyoshi Funaki)等、外7名、「Characterization of Cascode SiCJFET/SiMOSFET Devices」、International Power Electronics Conference(IPEC-Niigata 2005)、2005年4月、p.4-8

【非特許文献3】ケリー(Robin Kelley)等、外1名、「SiC JFET Gate Driver Design for Use in DC/DC Converters」、IEEE APEC 2006、2006年、p.179-182

【発明の開示】

【発明が解決しようとする課題】

【0004】

通常、ノーマリオフ型のJFETはチャネルを微細化し、ゲート電位がソース電位と同じであってもチャネル全体が空乏化する設計とすることによって実現できる。しかしながら、チャネルを微細化することはオン抵抗の増加に直結するので、ノーマリオフ型のJFETではオン抵抗が増大するという問題がある。

【0005】

また、前述の非特許文献2には、SiCJFETとSiMOSFETをカスコード接続した場合には、JFETとMOSFETのボディダイオード素子による負性抵抗の影響で、ターンオフ時に電圧が振動する問題が報告されている。

【0006】

この発明は、上記の問題点を考慮したものである。この発明の目的は、ノーマリオン型の半導体素子を用いて、電力変換装置として、より安全なノーマリオフ的な動作の半導体スイッチング装置を提供することである。

【課題を解決するための手段】

【0007】

この発明は一局面において、ノーマリオン型の半導体スイッチング素子と、ゲートドライブ回路と、駆動電源と、分圧部とを備える半導体スイッチング装置である。半導体スイッチング素子は、第1、第2の主電極および制御電極を有し、第1の主電極および制御電極間の制御電圧が第1の範囲のときに第1、第2の主電極間が導通し、制御電圧が第2の範囲のときに第1、第2の主電極間が非導通になる。ゲートドライブ回路は、第1、第2の電源ノード、制御信号入力ノード、および出力ノードを有し、制御信号入力ノードに制御信号を受け、制御信号の大きさが閾値以下の場合に第1の電源ノードと出力ノードとが導通し、制御信号の大きさが閾値を超える場合に第2の電源ノードと出力ノードとが導通する。ここで、出力ノードは、制御電極に接続される。駆動電源は、第1、第2の電源ノード間に接続される。分圧部は、第1、第2の電源ノード間の電圧を分圧し、分圧された電圧を出力する分圧ノードを有する。ここで、分圧ノードは、第1の主電極に接続される。分圧ノードと第1の電源ノードとの間の電圧が第2の範囲にあり、分圧ノードと第2の電源ノードとの間の電圧が第1の範囲にある。

【0008】

上記構成によれば、制御信号の大きさが閾値以下の場合には、制御電極は出力ノードを介して第1の電源ノードに接続される。また、第1の主電極は分圧ノードに接続される。このとき、分圧ノードと第1の電源ノードとの間の電圧は第2の範囲にあるので、半導体スイッチング素子の制御電圧は第2の範囲になる。この結果、第1、第2の主電極間は非導通になる。

【0009】

一方、制御信号の大きさが閾値を超える場合には、制御電極は出力ノードを介して第2の電源ノードに接続される。また、第1の主電極は分圧ノードに接続される。このとき、分圧ノードと第2の電源ノードとの間の電圧は第1の範囲にあるので、半導体スイッチング素子の制御電圧は第1の範囲になる。この結果、第1、第2の主電極間は導通する。このように閾値以下の大きさの制御信号の入力によって、半導体スイッチング素子がターンオフするという、電力変換装置として、より安全なノーマリオフ的な動作が実現している。

【0010】

また、上記のゲートドライブ回路の動作は、通常のノーマリオフ型の素子用のゲートドライブ回路と同じであるので、市販のゲートドライバを利用することによってスイッチング装置を簡単に構成することができる。

【0011】

また、上記構成によれば、ターンオン時の半導体スイッチング素子の制御電圧が0電圧でない。すなわち、Nチャネルの素子の場合には制御電圧が正になり、Pチャネルの素子の場合には制御電圧が負になる。したがって、0電圧でゲートを駆動する場合に比べてオン抵抗を低減させることができる。

【0012】

好ましい実施の一形態において、分圧部は、少なくとも2個以上のコンデンサ素子で構成され、コンデンサ素子の直列接続を少なくとも1つ以上有する。直列接続された複数のコンデンサ素子を用いて分圧部を構成した場合には、複数のコンデンサ素子の容量に応じて分圧ノードの電位が決まる。この場合、抵抗素子を用いて分圧部を構成する場合に比べて消費電力を低減できるメリットがある。

【0013】

また、好ましい実施の他の形態において、分圧部は、少なくとも1個以上のツェナーダイオード素子またはダイオード素子と、少なくとも1個以上の抵抗素子とから構成され、ツェナーダイオード素子またはダイオード素子と抵抗素子との直列接続を少なくとも1つ以上有する。分圧部にツェナーダイオード素子またはダイオード素子を用いた場合には、半導体スイッチング素子のターンオン時に印加される制御電圧を、ツェナー電圧またはダイオード素子のPN接合ビルトイン電圧で決まる所望の値に設定することができる。

【0014】

また、好ましい実施のさらに他の形態において、分圧部は、少なくとも2個以上の抵抗素子から構成され、抵抗素子の直列接続を少なくとも1つ以上有する。直列接続された複数の抵抗素子を用いて分圧部を構成した場合には、複数の抵抗素子の抵抗値に応じて分圧ノードの電位が決まる。

【0015】

また、好ましい実施のさらに他の形態において、分圧部は、分圧ノードと第1の電源ノードとの間に接続される、または、分圧ノードと第2の電源ノードとの間に接続される、少なくとも1個以上のコンデンサ素子を含む。コンデンサ素子を設けることによって、半導体スイッチング素子のスイッチングに伴なう分圧ノードの電位の変動を抑制することができる。この結果、半導体スイッチング素子をより安定に制御することができる。

【0016】

この発明は他の局面において、ノーマリオン型の半導体スイッチング素子と、ゲートドライブ回路と、駆動電源とを備える半導体スイッチング装置である。半導体スイッチング素子は、第1、第2の主電極および制御電極を有し、第1の主電極および制御電極間の制御電圧が第1の範囲のときに第1、第2の主電極間が導通し、制御電圧が第2の範囲のときに第1、第2の主電極間が非導通になる。ゲートドライブ回路は、第1、第2の電源ノード、制御信号入力ノード、および出力ノードを有し、制御信号入力ノードに制御信号を受け、制御信号の大きさが閾値以下の場合に第1の電源ノードと出力ノードとが導通し、制御信号の大きさが閾値を超える場合に第2の電源ノードと出力ノードとが導通する。ここで、出力ノードは、制御電極に接続され、第2の電源ノードは、第1の主電極に接続される。駆動電源は、第1、第2の電源ノード間に接続される。駆動電源の電圧は、第2の範囲にある。

【0017】

上記構成によれば、制御信号の大きさが閾値以下の場合には、制御電極は出力ノードを介して第1の電源ノードに接続される。また、第1の主電極は第2の電源ノードに接続される。このとき、第1、第2の電源ノード間に接続される駆動電源の電圧は第2の範囲にあるので、半導体スイッチング素子の制御電圧が第2の範囲になる。この結果、第1、第2の主電極間は非導通になる。一方、制御信号の大きさが閾値を超える場合には、制御電極は出力ノードを介して第2の電源ノードに接続される。また、第1の主電極も第2の電源ノードに接続されるので、半導体スイッチング素子の制御電圧は0電圧になって、第1の範囲に含まれる。この結果、第1、第2の主電極間は導通する。このように閾値以下の大きさの制御信号の入力によって、半導体スイッチング素子がターンオフするという、ノーマリオフ的な動作が実現している。

【0018】

また、上記のゲートドライブ回路の動作は、通常のノーマリオフ型の素子用のゲートドライブ回路と同じであるので、市販のゲートドライバを利用することによってスイッチング装置を簡単に構成することができる。

【0019】

好ましくは、上記一局面および他の局面において、半導体スイッチング素子は、シリコンよりバンドギャップの大きい半導体材料を用いて形成される。ワイドバンドギャップの半導体材料を用いることによって、高温特性、高周波特性、高耐電圧、低オン抵抗などの面でシリコンを用いる場合よりも優れた特性の半導体スイッチング装置を実現することができる。

【0020】

また、好ましくは、上記の半導体スイッチング素子は、接合型電界効果トランジスタである。接合型電界効果トランジスタ(JFET)は、ノーマリオンの半導体スイッチング素子として代表的なものであり、本発明を好適に用いることができる。

【発明の効果】

【0021】

以上のとおり、この発明によれば、ノーマリオン型の半導体素子を用いて、電力変換装置として、より安全なノーマリオフ的な動作の簡単な構成の半導体スイッチング装置を提供することができる。

【発明を実施するための最良の形態】

【0022】

以下、この発明の実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰り返さない。また、以下では、SiCを用いたNチャネルのJFETを例に挙げて説明するが、この発明はこれに限るものでなく、PチャネルのJFETなど、ノーマリオン型の半導体スイッチング素子に広く適用できる。

【0023】

[実施の形態1]

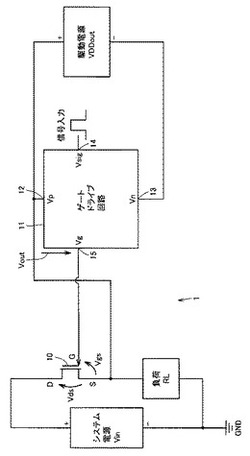

図1は、この発明の実施の形態1による半導体スイッチング装置1の構成を示すブロック図である。図1を参照して、半導体スイッチング装置1は、NチャネルのJFET10と、ゲートドライブ回路11と、駆動電源VDDoutとを含む。また、図1には、JFET10に接続される主回路のシステム電源Vinおよび負荷RLも併せて表示している。システム電源Vinは、JFET10のドレインDと接地GND間に接続される。負荷RLは、JFET10のソースSと接地GND間に接続される。なお、図1において、ゲート・ソース間電圧Vgsおよびドレイン・ソース間電圧Vdsは、それぞれ、ソースSを基準にしたときのゲートGおよびドレインDの電位である。

【0024】

NチャネルのJFET10は、負の閾値電圧Vth1を有する。JFET10は、ゲート・ソース間電圧Vgsが負の閾値電圧Vth1より小さいVgs<Vth1(第2の範囲)の場合にターンオフし、ゲート・ソース間電圧Vgsが負の閾値電圧Vth1以上であるVgs≧Vth1(第1の範囲)の場合にターンオンする。

【0025】

ゲートドライブ回路11は、第1、第2の電源ノード13,12と、制御信号の入力ノード14と、出力ノード15とを含む。電源ノード12には駆動電源VDDoutの正極が接続され、電源ノード13には駆動電源VDDoutの負極が接続される。駆動電源VDDoutは、主回路側とはフローティングの状態にある絶縁電源である。また、出力ノード15はJFET10のゲートGに接続され、高圧側の電源ノード12はJFET10のソースSに接続される。

【0026】

ゲートドライブ回路11は、制御信号に応じて出力ノード15の接続を切替える。具体的には、入力ノード14に入力される制御信号の電圧Vsigが正の閾値電圧Vth2以下のLレベルの場合、出力ノード15と低電圧側の電源ノード13とを導通させる。一方、電圧Vsigが閾値電圧Vth2より大きいHレベルの場合、出力ノード15と高電圧側の電源ノード12とを導通させる。したがって、制御信号の電圧Vsigが閾値電圧Vth2より大きいHレベルの場合に、出力ノード15の電位Vgは高圧側の電源ノード12の電位Vpに等しくなり、制御信号の電圧Vsigが閾値電圧Vth2より大きいHレベルの場合に出力ノード15の電位Vgは低圧側の電源ノード13の電位Vnに等しくなる。

【0027】

ここで、実施の形態1では、JFET10のゲートGが出力ノード15に接続され、ソースSが高圧側の電源ノード12に接続されるので、JFET10のゲート・ソース間電圧Vgsは、出力ノード15と電源ノード12との間の出力電圧Vout=Vg−Vpに等しくなる。したがって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、

Vgs=Vout=Vg−Vp=Vp−Vp=0 …(1)

となって(第1の範囲)、JFET10は導通する。

【0028】

一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、

Vgs=Vout=Vg−Vp=Vn−Vp

=−VDDout …(2)

となる。駆動電源VDDoutの電圧をJFET10の閾値電圧Vth1の絶対値より大きくなるように設定すれば、Vgs=−VDDout<Vth1となって(第2の範囲)、JFET10は非導通になる。したがって、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。

【0029】

上記のような動作のゲートドライブ回路11は、たとえば、駆動電源VDDoutの正極と負極との間に直列接続された2個のNチャネルのトランジスタによって構成することができる。この場合、正極側のトランジスタのゲートには制御信号Vsigが非反転入力され、負極側のトランジスタのゲートには制御信号Vsigが反転入力される。2個のトランジスタの接続点が出力ノード15に相当する。また、上記の動作は通常のノーマリオフ型の素子用のゲートドライブ回路の動作と同じであるので、市販のゲートドライバを利用することによってゲートドライブ回路11を簡単に構成することができる。

【0030】

次に、ゲートドライブ回路11に市販のノーマリオフ型素子用のゲートドライバを使用した場合の半導体スイッチング装置1の動作例について説明する。

【0031】

図2は、市販のゲートドライバを用いたゲートドライブ回路11の構成を示す図である。

【0032】

図3は、JFET10の接続を示す回路図である。

図2、図3を参照して、使用したJFET10のゲート・ソース間の閾値電圧はVth1=−12Vである。また、ゲートドライバ11として、Analog Devices社の製品(型番:ADuM1233)を使用した。このドライバは5MHzまで動作可能である。電源VDDinはゲートドライバ11の入力信号側の回路の電源であり、ゲートドライバ11の入力信号側の電源ノード16,17に接続される。また、JFET10のターンオフに要する時間を短縮するために、JFET10のターンオフ時のゲート・ソース間電圧Vgsの絶対値が、閾値電圧Vth1の絶対値よりも充分大きくなるように駆動電源VDDoutの電圧を17Vとしている。なお、電源VDDinおよびVDDoutに並列に接続されているコンデンサ素子21,22は、バイパスコンデンサ素子である。

【0033】

入力ノード14および電源ノード17間には、制御信号源FGが接続される。これによって、ゲートドライバ11に制御信号Vsigが入力される。制御信号Vsigは、振幅4V、周波数3.1MHzの方形波である。パワー回路側に対して入力信号側の回路を保護するために、入力された制御信号Vsigは絶縁用のパルストランス19を介して出力側に伝達される。パルストランス19の入力側にA/D(Analog to Digital)変換器18が設けられ、出力側にD/A(Digital to Analog)変換器20が設けられる。

【0034】

次に、ドライブ回路の駆動時の制御信号Vsigおよび出力電圧Voutの波形の測定結果について説明する。

【0035】

図4は、図2のゲートドライバ11を用いて図3の回路を駆動しているときの制御信号Vsigおよび出力電圧Voutの波形図である。図4の実線のグラフは制御信号Vsigの波形であり、図4の破線のグラフは出力電圧Voutの波形である。

【0036】

図4を参照して、出力電圧Voutの立ち上がり時間tRを、出力電圧Voutが−0.9VDDout(図4の電圧V3)になった時刻t1から−0.1VDDout(図4の電圧V1)になった時刻t2までの時間と定義する。また、出力電圧Voutの立ち下がり時間tFを、出力電圧Voutが−0.1VDDout(図4の電圧V1)になった時刻t3から−0.9VDDout(図4の電圧V3)になった時刻t4までの時間と定義する。図4の場合、立ち上がり時間tRは18nsであり、立ち下がり時間tFは20nsである。

【0037】

また、制御信号Vsigから出力電圧Voutへの遅延時間tdelayを、制御信号Vsigが振幅の50%に達する時刻t5から、出力電圧Voutが振幅の50%(図4の電圧V2)に達する時刻t6までの時間と定義する。図4の場合、遅延時間tdelayは130nsである。これは、3.1MHzの制御信号Vsigの周期320nsの約40%である。

【0038】

以上より、立ち上がり時間tR、立ち下がり時間tFがともに20ns程度と短く、3MHzを越える周波数のゲート駆動用の出力電圧Voutが生成できることがわかる。一方、遅延時間tdelayは、制御信号Vsigの周期に比べて無視出来ないほど大きいものの、ゲート駆動方式が通常のパルス幅変調による場合には問題とならない。

【0039】

次に、図2のゲートドライバ11で、図3のSiCJFETをスイッチングさせたときのJFET10電圧特性の測定結果について説明する。図3のJFET10の定格は、ドレイン・ソース間耐電圧:400V、順方向電流:1.25Aである。図3に示すように、30Vのシステム電源Vinに33Ωの無誘導抵抗が負荷RLとして接続されている。1A近い電流を高速でスイッチングするため、回路に寄生するインダクタンス成分の影響が大きくなると考えられる。そこで、寄生インダクタンス成分を低減するために、スイッチング回路は、導体幅約5mmのプリント基板で作成し、電源などの各機器との接続ケーブルは、ツイストペア状に撚り合わせ、電流ループが極力小さくなるように注意を払っている。JFETのゲート制御電圧Vgsとして、図2に示すゲートドライブ回路11の出力電圧Voutを入力する。

【0040】

図5は、ゲート・ソース間電圧Vgsおよびドレイン・ソース間電圧Vdsの波形図である。図5の実線のグラフはゲート・ソース間電圧Vgsの波形であり、図5の破線のグラフはドレイン・ソース間電圧Vdsの波形である。

【0041】

図5を参照して、JFET10がターンオフした時刻t7の直後、ドレイン・ソース間電圧Vdsが大きくオーバーシュートし、時刻t9で61Vに達している。これは、電源電圧Vinの約2倍の電圧である。また、オーバーシュートの後も、25V〜40Vの間でリンギングしている。また、時刻t14以降のターンオン時には、約10Vアンダーシュートした後、10Vと−5Vの間でリンギングしている。これらのリンギングは、回路作成時に寄生インダクタンスを完全に排除できなかったために生じたもので、素子や回路に寄生するインダクタンス成分と、JFET10の内部に存在するPN接合のキャパシタンス成分によって引き起こされていると考えられる。

【0042】

ターンオフ時のリンギング周波数について定量的に評価する。ターンオフ時にドレイン・ソース間電圧Vdsが0.1Vinとなる時刻t7、およびその後のリンギングの腹となる時刻t9,t10,t11,t12を図5から読み取ると、順にt7=0.2μs、t9=0.222μs、t10=0.242μs、t11=0.258μs、t12=0.270μsである。時刻t7から時刻t10を1周期とすると、t10−t7=42nsとなる。同様に、t11−t9=36ns、t12−t10=28nsである。JFET10内部のPN接合のキャパシタンス成分は電圧により変化するため、それに伴いリンギング周波数も変化する。ここでは、電圧の変化が最も少ない、時刻t10から時刻t12に注目する。このときの周波数は35.7MHzである。

【0043】

次に、ターンオフや、ターンオンに関わる時間について定量的に評価する。ターンオフに要する時間toffを、ドレイン・ソース間電圧Vdsが電源電圧Vinの10%(図5の電圧V4)を越える時刻t7から、電源電圧Vinの90%(図5の電圧V5)に達する時刻t8までの時間と定義すると、ターンオフ時間toffは8nsとなる。同様に、ターンオンに要する時間tonを、ドレイン・ソース間電圧Vdsが0.9Vinとなる時刻t13から0.1Vinに降下する時刻t14までの時間と定義すると、ターンオン時間tonは10nsである。ゲートドライブ回路11の駆動電源VDDoutの電圧を閾値電圧Vth1に比べて大きく設定し、オーバードライブしているため、ターンオン時間tonが図4の立ち下がり時間tFに比べ60%程度短くなっている。

【0044】

以上のとおり、実施の形態1の半導体スイッチング装置1によれば、市販のノーマリオフ型の素子用のゲートドライバを用いた簡単な構成で、制御信号VsigがLレベルのときにノーマリオンのJFET10がターンオフするというノーマリオフ的な駆動が可能になる。これによって、電力変換装置としての安全性を高めることができる。

【0045】

[実施の形態2]

図6は、この発明の実施の形態2による半導体スイッチング装置2の構成を示すブロック図である。図6の半導体スイッチング装置2は、分圧部30をさらに含む点で、図1の半導体スイッチング装置1と異なる。その他の点については、実施の形態1の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0046】

分圧部30は、高圧側の電源ノード12と分圧ノードNDとの間に逆バイアス方向に接続されたツェナーダイオード素子31と、分圧ノードNDと低圧側の電源ノード13との間に接続された抵抗素子32とを含む。JFET10のソースSは、図1の場合の電源ノード12に代えて、分圧ノードNDに接続される。したがって、図6の場合、JFET10のソースSの電位は、分圧ノードNDの電位Vdに等しい。このとき、分圧ノードNDの電位Vdは、電源ノード12の電位Vpよりツェナーダイオード素子31のツェナー電圧Vz分だけ低く、Vd=Vp−Vzとなる。また、JFET10のゲート・ソース間に供給される出力電圧Voutは、出力ノード15と分圧ノードNDとの電位差Vg−Vdで与えられる。

【0047】

よって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、出力ノードVgの電位Vgは電源ノード12の電位Vpに等しいので、

Vgs=Vout=Vg−Vd=Vp−Vd …(3)

となる。すなわち、この場合のゲート・ソース間の電圧Vgsは、電源ノード13と分圧ノードNDとの間の電圧に等しい。さらに、Vd=Vp−Vzの関係を代入すると、電源ノード13と分圧ノードNDとの間の電圧は、

Vgs=Vp−Vd=Vp−(Vp−Vz)=Vz …(4)

となって(第1の範囲)、JFET10は導通する。

【0048】

一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、出力ノードVgの電位Vgは電源ノード13の電位Vnに等しいので、

Vgs=Vout=Vg−Vd=Vn−Vd …(5)

となる。すなわち、この場合のゲート・ソース間の電圧Vgsは、電源ノード13と分圧ノードNDとの間の電圧に等しい。さらに、Vd=Vp−Vzの関係を代入すると、電源ノード13と分圧ノードNDとの間の電圧は、

Vgs=Vn−Vd=Vn−(Vp−Vz)=Vz−(Vn−Vp)

=Vz−VDDout …(6)

となる。したがって、駆動電源のVDDoutの電圧を閾値電圧Vth1の絶対値よりもさらにツェナー電圧Vz分だけ大きく設定すれば、Vz−VDDout<Vth1<0となって(第2の範囲)、JFET10は非導通になる。

【0049】

以上の結果から、実施の形態1の場合と同様に、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。また、ターンオン時のゲート・ソース間電圧Vgsは、実施の形態1の場合の0Vと異なり、ツェナー電圧Vzに等しい正の電圧になる。したがって、ツェナー電圧VzをJFET10のゲート・ソース間のPN接合のビルトイン電圧に近い値に設定すれば、実施の形態1の場合よりも、高周波特性を維持した上でオン抵抗を低減させることができる。なお、ターンオン時のゲート・ソース間電圧Vgsがゲート・ソース間のPN接合のビルトイン電圧を超える場合にはさらにオン抵抗の低減が期待できるが、ゲートGからホールが注入されることになるのでスイッチング速度が低下するというデメリットがある。

【0050】

また、上記の構成において、ツェナーダイオード素子31および抵抗素子32は複数個設けてもよい。また、ツェナーダイオード素子31を分圧ノードNDと低圧側の電源ノード13との間に設け、抵抗素子32を分圧ノードNDと高圧側の電源ノード12との間に設けることもできる。すなわち、分圧部30は、少なくとも1個以上のツェナーダイオード素子31と、少なくとも1個以上の抵抗素子32とから構成され、少なくとも1つ以上のツェナーダイオード素子31と抵抗素子32との直列接続を有する構成であってもよい。ただし、いずれの場合も、分圧ノードNDと低電圧側の電源ノード13との電位差Vd−Vnが閾値電圧Vth1の絶対値よりも大きくなるように設定する必要がある。

【0051】

[実施の形態3]

図7は、この発明の実施の形態3による半導体スイッチング装置3の構成を示すブロック図である。図7の分圧部30Aは、ツェナーダイオード素子31に代えてダイオード素子33を含む点で図6の分圧部30と異なる。その他の点については、図6の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0052】

分圧部30Aは、高圧側の電源ノード12と分圧ノードNDとの間に順バイアス方向に接続されたダイオード素子33と、分圧ノードNDと低圧側の電源ノード13との間に接続された抵抗素子32とを含む。このとき、分圧ノードNDの電位Vdは、電源ノード12の電位Vpよりダイオード素子33のビルトイン電圧Vb分だけ低く、Vd=Vp−Vbとなる。

【0053】

よって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、

Vgs=Vout=Vg−Vd=Vp−(Vp−Vb)=Vb …(7)

となって(第1の範囲)、JFET10は導通する。一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、

Vgs=Vout=Vg−Vd=Vn−(Vp−Vb)

=Vb−(Vn−Vp)=Vb−VDDout …(8)

となる。したがって、駆動電源のVDDoutの電圧を閾値電圧Vth1の絶対値よりもさらにダイオード素子33のビルトイン電圧Vb分だけ大きく設定すれば、Vb−VDDout<Vth1<0となって(第2の範囲)、JFET10は非導通になる。

【0054】

以上の結果から、実施の形態2の場合と同様に、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。また、ターンオン時のゲート・ソース間電圧Vgsは、ダイオード素子33のビルトイン電圧Vbに等しい正の電圧になるので、実施の形態1の場合に比べてオン抵抗を低減させることができる。

【0055】

上記の構成において、ダイオード素子33および抵抗素子32は複数個設けてもよい。また、直列接続された複数のダイオード素子33を分圧ノードNDと低圧側の電源ノード13との間に設け、抵抗素子32を分圧ノードNDと高圧側の電源ノード12との間に設けることもできる。すなわち、分圧部30Aは、少なくとも1個以上のダイオード素子33と、少なくとも1個以上の抵抗素子32とから構成され、少なくとも1つ以上のダイオード素子33と抵抗素子32との直列接続を有する構成であってもよい。ただし、いずれの場合も、分圧ノードNDと低電圧側の電源ノード13との電位差Vd−Vnが閾値電圧Vth1の絶対値よりも大きくなるように設定する必要がある。

【0056】

[実施の形態4]

図8は、この発明の実施の形態4による半導体スイッチング装置4の構成を示すブロック図である。図8の分圧部30Bは、抵抗素子32と並列にコンデンサ素子34をさらに含む点で、図6の実施の形態2の分圧部30と異なる。コンデンサ素子34を設けることによって、JFET10のスイッチングに伴なう分圧ノードNDの電位の変動を抑制することができるので、図6の実施の形態2の場合に比べて半導体スイッチング装置4をより安定に動作させることができる。その他の点については、図6の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0057】

上記構成において、抵抗素子32と並列でなくツェナーダイオード素子31と並列にコンデンサ素子34を設けてもよい。また、コンデンサ素子34を複数個設けてもよい。すなわち、分圧部30Bは、分圧ノードNDと低圧側の電源ノード13との間に接続される、または、分圧ノードNDと高圧側の電源ノード12との間に接続される、少なくとも1個以上のコンデンサ素子を含む。いずれの場合も、コンデンサ素子によって、JFET10のスイッチングに伴なう分圧ノードNDの電位の変動を抑制するという効果を奏する。

【0058】

[実施の形態5]

図9は、この発明の実施の形態5による半導体スイッチング装置5の構成を示すブロック図である。図9の半導体スイッチング装置5は、分圧部30Cの構成が図6の実施の形態2の分圧部30構成と異なる。その他の点については、実施の形態2の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0059】

分圧部30Cは、高圧側の電源ノード12と分圧ノードNDとの間に接続されたコンデンサ素子C1と、分圧ノードNDと低圧側の電源ノード13との間に接続されたコンデンサ素子C2とを含む。JFET10のソースSは、分圧ノードNDに接続される。したがって、図9の場合、JFET10のゲート・ソース間に供給される出力電圧Voutは、出力ノード15と分圧ノードNDとの電位差Vg−Vdになる。また、分圧部30Cによって、電源ノード12,13間の電圧がコンデンサ素子C1,C2の容量の逆比となるように分割される。

【0060】

よって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、ゲート・ソース間電圧Vgsは、電源ノード12と分圧ノードNDとの間の電圧Vp−Vdに等しく、

Vgs=Vout=Vg−Vd=Vp−Vd

=(Vp−Vn)×C2/(C1+C2)

=VDDout×C2/(C1+C2) …(9)

となって(第1の範囲)、JFET10は導通する。一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、ゲート・ソース間電圧Vgsは、電源ノード13と分圧ノードNDとの間の電圧Vn−Vdに等しく、

Vgs=Vout=Vg−Vd=Vn−Vd

=−(Vp−Vn)×C1/(C1+C2)

=−VDDout×C1/(C1+C2) …(10)

となる。したがって、駆動電源VDDoutの電圧を閾値電圧Vth1の絶対値の(C1+C2)/C1倍より大きく設定すれば、Vgs<Vth1<0となって(第2の範囲)、JFET10は非導通になる。

【0061】

以上の結果から、実施の形態1の場合と同様に、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。このとき、実施の形態9の場合には分圧部30Cがコンデンサ素子のみで構成されており、抵抗素子32が用いられていないので、実施の形態2〜4に比べて消費電力を小さくできるメリットがある。また、ターンオン時のゲート・ソース間電圧Vgsは正の電圧になる。したがって、VDDout×C2/(C1+C2)をJFET10のゲート・ソース間のPN接合のビルトイン電圧に近い値に設定すれば、実施の形態1の場合に比べて、高周波特性を維持した上でオン抵抗を低減させることができる。

【0062】

上記の構成において、第1、第2のコンデンサ素子C1,C2をそれぞれ複数個ずつ設けてもよい。すなわち、分圧部30Cは、少なくとも2個以上のコンデンサ素子で構成され、少なくとも1つ以上のコンデンサ素子の直列接続を有する構成であってもよい。ただし、いずれの場合も、分圧ノードNDと低電圧側の電源ノード13との電位差Vd−Vnが閾値電圧Vth1の絶対値よりも大きくなるように設定する必要がある。

【0063】

[実施の形態6]

図10は、この発明の実施の形態6による半導体スイッチング装置6の構成を示すブロック図である。図10の半導体スイッチング装置6は、分圧部30Dの構成が図6の実施の形態2の分圧部30構成と異なる。その他の点については、実施の形態2の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0064】

分圧部30Dは、高圧側の電源ノード12と分圧ノードNDとの間に接続された抵抗素子R1と、分圧ノードNDと低圧側の電源ノード13との間に接続された抵抗素子R2とを含む。JFET10のソースSは、分圧ノードNDに接続される。したがって、図10の場合、JFET10のゲート・ソース間に供給される出力電圧Voutは、出力ノード15と分圧ノードNDとの電位差Vg−Vdになる。また、分圧部30Dによって、電源ノード12,13間の電圧が抵抗素子R1,R2の抵抗値の比で分割される。

【0065】

よって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、ゲート・ソース間電圧Vgsは、電源ノード12と分圧ノードNDとの間の電圧Vp−Vdに等しく、

Vgs=Vout=Vg−Vd=Vp−Vd

=(Vp−Vn)×R1/(R1+R2)

=VDDout×R1/(R1+R2) …(11)

となって(第1の範囲)、JFET10は導通する。一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、ゲート・ソース間電圧Vgsは、電源ノード13と分圧ノードNDとの間の電圧Vn−Vdに等しく、

Vgs=Vout=Vg−Vd=Vn−Vd

=−(Vp−Vn)×R2/(R1+R2)

=−VDDout×R2/(R1+R2) …(12)

となる。したがって、駆動電源VDDoutの電圧を閾値電圧Vth1の絶対値の(R1+R2)/R2倍より大きく設定すれば、Vgs<Vth1<0となって(第2の範囲)、JFET10は非導通になる。

【0066】

以上の結果から、実施の形態1の場合と同様に、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。また、ターンオン時のゲート・ソース間電圧Vgsは正の電圧になる。したがって、VDDout×R1/(R1+R2)をJFET10のゲート・ソース間のPN接合のビルトイン電圧に近い値に設定すれば、実施の形態1の場合に比べて、高周波特性を維持した上でオン抵抗を低減させることができる。

【0067】

上記の構成において、第1、第2の抵抗素子R1,R2をそれぞれ複数個ずつ設けてもよい。すなわち、分圧部30Dは、少なくとも2個以上の抵抗素子で構成され、少なくとも一つ以上の抵抗素子の直列接続を有する構成であってもよい。ただし、いずれの場合も、分圧ノードNDと低電圧側の電源ノード13との電位差Vd−Vnが閾値電圧Vth1の絶対値よりも大きくなるように設定する必要がある。

【0068】

今回開示された実施の形態はすべての点で例示であって、制限的なものではないと考えられるべきである。この発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味、および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0069】

【図1】この発明の実施の形態1による半導体スイッチング装置1の構成を示すブロック図である。

【図2】市販のゲートドライバを用いたゲートドライブ回路11の構成を示す図である。

【図3】JFET10の接続を示す回路図である。

【図4】図2のゲートドライバ11を用いて図3の回路を駆動しているときの制御信号Vsigおよび出力電圧Voutの波形図である。

【図5】ゲート・ソース間電圧Vgsおよびドレイン・ソース間電圧Vdsの波形図である。

【図6】この発明の実施の形態2による半導体スイッチング装置2の構成を示すブロック図である。

【図7】この発明の実施の形態3による半導体スイッチング装置3の構成を示すブロック図である。

【図8】この発明の実施の形態4による半導体スイッチング装置4の構成を示すブロック図である。

【図9】この発明の実施の形態5による半導体スイッチング装置5の構成を示すブロック図である。

【図10】この発明の実施の形態6による半導体スイッチング装置6の構成を示すブロック図である。

【符号の説明】

【0070】

1〜5 半導体スイッチング装置、10 JFET、11 ゲートドライブ回路、12,13 電源ノード、14 入力ノード、15 出力ノード、30,30A,30B,30C 分圧部、31 ツェナーダイオード素子、32 抵抗素子、33 ダイオード素子、34 コンデンサ素子、C1,C2 コンデンサ素子、D ドレイン、G ゲート、S ソース、R1,R2 抵抗素子、ND 分圧ノード、Vout 出力電圧、Vsig 制御信号、Vth1 閾値電圧(ゲート・ソース間電圧)、Vth2 閾値電圧(制御信号)。

【技術分野】

【0001】

この発明は、半導体スイッチング素子とそのゲート制御回路とを含む半導体スイッチング装置に関する。

【背景技術】

【0002】

ワイドバンドギャップ半導体であるSiC(Silicon Carbide)は、高温特性、高周波特性、高耐電圧、低オン抵抗などの面で、Si(Silicon)に比べ優れている。電力変換回路のスイッチング素子として、SiC半導体デバイスを使用することで、スイッチング周波数を上昇させ、インダクタやキャパシタを小型化できる。その結果、高耐電圧、低オン抵抗の性質と相まって、体積が小さく大電力の扱える電力変換回路が実現でき、電源の高電力密度化が可能となる。SiCデバイスは、受動素子としてショットキバリアダイオード素子が商用に供され、能動素子としてはJFET(Junction Field Effect Transistor)が試作されている。

【0003】

ところで、JFETは一般にノーマリオン型の素子である。このため、故障時にJFETの主電流を遮断するための保護回路が必要になるなど、ノーマリオフ型のデバイスに比べてゲートドライバ回路の設計が困難である。そこで、ノーマリオフ型のSiCJFETを使用した回路の開発(たとえば、非特許文献1参照)や、SiCJFETとSiMOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)とをカスコード接続したデバイスの開発が行なわれ、回路実装が試みられている(たとえば、非特許文献2参照)。また、ノーマリオン型のSiCJFET用の新たなゲートドライブ回路の設計(たとえば、非特許文献3参照)も試みられている。

【非特許文献1】石川(Katsumi Ishikawa)等、外6名、「Normally-off SiC-JFET inverter with low-voltage control and a high-speed drive circuit」、Pro-ceedings of ISPSD'07、2007年、p.217-220

【非特許文献2】舟木(Tsuyoshi Funaki)等、外7名、「Characterization of Cascode SiCJFET/SiMOSFET Devices」、International Power Electronics Conference(IPEC-Niigata 2005)、2005年4月、p.4-8

【非特許文献3】ケリー(Robin Kelley)等、外1名、「SiC JFET Gate Driver Design for Use in DC/DC Converters」、IEEE APEC 2006、2006年、p.179-182

【発明の開示】

【発明が解決しようとする課題】

【0004】

通常、ノーマリオフ型のJFETはチャネルを微細化し、ゲート電位がソース電位と同じであってもチャネル全体が空乏化する設計とすることによって実現できる。しかしながら、チャネルを微細化することはオン抵抗の増加に直結するので、ノーマリオフ型のJFETではオン抵抗が増大するという問題がある。

【0005】

また、前述の非特許文献2には、SiCJFETとSiMOSFETをカスコード接続した場合には、JFETとMOSFETのボディダイオード素子による負性抵抗の影響で、ターンオフ時に電圧が振動する問題が報告されている。

【0006】

この発明は、上記の問題点を考慮したものである。この発明の目的は、ノーマリオン型の半導体素子を用いて、電力変換装置として、より安全なノーマリオフ的な動作の半導体スイッチング装置を提供することである。

【課題を解決するための手段】

【0007】

この発明は一局面において、ノーマリオン型の半導体スイッチング素子と、ゲートドライブ回路と、駆動電源と、分圧部とを備える半導体スイッチング装置である。半導体スイッチング素子は、第1、第2の主電極および制御電極を有し、第1の主電極および制御電極間の制御電圧が第1の範囲のときに第1、第2の主電極間が導通し、制御電圧が第2の範囲のときに第1、第2の主電極間が非導通になる。ゲートドライブ回路は、第1、第2の電源ノード、制御信号入力ノード、および出力ノードを有し、制御信号入力ノードに制御信号を受け、制御信号の大きさが閾値以下の場合に第1の電源ノードと出力ノードとが導通し、制御信号の大きさが閾値を超える場合に第2の電源ノードと出力ノードとが導通する。ここで、出力ノードは、制御電極に接続される。駆動電源は、第1、第2の電源ノード間に接続される。分圧部は、第1、第2の電源ノード間の電圧を分圧し、分圧された電圧を出力する分圧ノードを有する。ここで、分圧ノードは、第1の主電極に接続される。分圧ノードと第1の電源ノードとの間の電圧が第2の範囲にあり、分圧ノードと第2の電源ノードとの間の電圧が第1の範囲にある。

【0008】

上記構成によれば、制御信号の大きさが閾値以下の場合には、制御電極は出力ノードを介して第1の電源ノードに接続される。また、第1の主電極は分圧ノードに接続される。このとき、分圧ノードと第1の電源ノードとの間の電圧は第2の範囲にあるので、半導体スイッチング素子の制御電圧は第2の範囲になる。この結果、第1、第2の主電極間は非導通になる。

【0009】

一方、制御信号の大きさが閾値を超える場合には、制御電極は出力ノードを介して第2の電源ノードに接続される。また、第1の主電極は分圧ノードに接続される。このとき、分圧ノードと第2の電源ノードとの間の電圧は第1の範囲にあるので、半導体スイッチング素子の制御電圧は第1の範囲になる。この結果、第1、第2の主電極間は導通する。このように閾値以下の大きさの制御信号の入力によって、半導体スイッチング素子がターンオフするという、電力変換装置として、より安全なノーマリオフ的な動作が実現している。

【0010】

また、上記のゲートドライブ回路の動作は、通常のノーマリオフ型の素子用のゲートドライブ回路と同じであるので、市販のゲートドライバを利用することによってスイッチング装置を簡単に構成することができる。

【0011】

また、上記構成によれば、ターンオン時の半導体スイッチング素子の制御電圧が0電圧でない。すなわち、Nチャネルの素子の場合には制御電圧が正になり、Pチャネルの素子の場合には制御電圧が負になる。したがって、0電圧でゲートを駆動する場合に比べてオン抵抗を低減させることができる。

【0012】

好ましい実施の一形態において、分圧部は、少なくとも2個以上のコンデンサ素子で構成され、コンデンサ素子の直列接続を少なくとも1つ以上有する。直列接続された複数のコンデンサ素子を用いて分圧部を構成した場合には、複数のコンデンサ素子の容量に応じて分圧ノードの電位が決まる。この場合、抵抗素子を用いて分圧部を構成する場合に比べて消費電力を低減できるメリットがある。

【0013】

また、好ましい実施の他の形態において、分圧部は、少なくとも1個以上のツェナーダイオード素子またはダイオード素子と、少なくとも1個以上の抵抗素子とから構成され、ツェナーダイオード素子またはダイオード素子と抵抗素子との直列接続を少なくとも1つ以上有する。分圧部にツェナーダイオード素子またはダイオード素子を用いた場合には、半導体スイッチング素子のターンオン時に印加される制御電圧を、ツェナー電圧またはダイオード素子のPN接合ビルトイン電圧で決まる所望の値に設定することができる。

【0014】

また、好ましい実施のさらに他の形態において、分圧部は、少なくとも2個以上の抵抗素子から構成され、抵抗素子の直列接続を少なくとも1つ以上有する。直列接続された複数の抵抗素子を用いて分圧部を構成した場合には、複数の抵抗素子の抵抗値に応じて分圧ノードの電位が決まる。

【0015】

また、好ましい実施のさらに他の形態において、分圧部は、分圧ノードと第1の電源ノードとの間に接続される、または、分圧ノードと第2の電源ノードとの間に接続される、少なくとも1個以上のコンデンサ素子を含む。コンデンサ素子を設けることによって、半導体スイッチング素子のスイッチングに伴なう分圧ノードの電位の変動を抑制することができる。この結果、半導体スイッチング素子をより安定に制御することができる。

【0016】

この発明は他の局面において、ノーマリオン型の半導体スイッチング素子と、ゲートドライブ回路と、駆動電源とを備える半導体スイッチング装置である。半導体スイッチング素子は、第1、第2の主電極および制御電極を有し、第1の主電極および制御電極間の制御電圧が第1の範囲のときに第1、第2の主電極間が導通し、制御電圧が第2の範囲のときに第1、第2の主電極間が非導通になる。ゲートドライブ回路は、第1、第2の電源ノード、制御信号入力ノード、および出力ノードを有し、制御信号入力ノードに制御信号を受け、制御信号の大きさが閾値以下の場合に第1の電源ノードと出力ノードとが導通し、制御信号の大きさが閾値を超える場合に第2の電源ノードと出力ノードとが導通する。ここで、出力ノードは、制御電極に接続され、第2の電源ノードは、第1の主電極に接続される。駆動電源は、第1、第2の電源ノード間に接続される。駆動電源の電圧は、第2の範囲にある。

【0017】

上記構成によれば、制御信号の大きさが閾値以下の場合には、制御電極は出力ノードを介して第1の電源ノードに接続される。また、第1の主電極は第2の電源ノードに接続される。このとき、第1、第2の電源ノード間に接続される駆動電源の電圧は第2の範囲にあるので、半導体スイッチング素子の制御電圧が第2の範囲になる。この結果、第1、第2の主電極間は非導通になる。一方、制御信号の大きさが閾値を超える場合には、制御電極は出力ノードを介して第2の電源ノードに接続される。また、第1の主電極も第2の電源ノードに接続されるので、半導体スイッチング素子の制御電圧は0電圧になって、第1の範囲に含まれる。この結果、第1、第2の主電極間は導通する。このように閾値以下の大きさの制御信号の入力によって、半導体スイッチング素子がターンオフするという、ノーマリオフ的な動作が実現している。

【0018】

また、上記のゲートドライブ回路の動作は、通常のノーマリオフ型の素子用のゲートドライブ回路と同じであるので、市販のゲートドライバを利用することによってスイッチング装置を簡単に構成することができる。

【0019】

好ましくは、上記一局面および他の局面において、半導体スイッチング素子は、シリコンよりバンドギャップの大きい半導体材料を用いて形成される。ワイドバンドギャップの半導体材料を用いることによって、高温特性、高周波特性、高耐電圧、低オン抵抗などの面でシリコンを用いる場合よりも優れた特性の半導体スイッチング装置を実現することができる。

【0020】

また、好ましくは、上記の半導体スイッチング素子は、接合型電界効果トランジスタである。接合型電界効果トランジスタ(JFET)は、ノーマリオンの半導体スイッチング素子として代表的なものであり、本発明を好適に用いることができる。

【発明の効果】

【0021】

以上のとおり、この発明によれば、ノーマリオン型の半導体素子を用いて、電力変換装置として、より安全なノーマリオフ的な動作の簡単な構成の半導体スイッチング装置を提供することができる。

【発明を実施するための最良の形態】

【0022】

以下、この発明の実施の形態について図面を参照して詳しく説明する。なお、同一または相当する部分には同一の参照符号を付して、その説明を繰り返さない。また、以下では、SiCを用いたNチャネルのJFETを例に挙げて説明するが、この発明はこれに限るものでなく、PチャネルのJFETなど、ノーマリオン型の半導体スイッチング素子に広く適用できる。

【0023】

[実施の形態1]

図1は、この発明の実施の形態1による半導体スイッチング装置1の構成を示すブロック図である。図1を参照して、半導体スイッチング装置1は、NチャネルのJFET10と、ゲートドライブ回路11と、駆動電源VDDoutとを含む。また、図1には、JFET10に接続される主回路のシステム電源Vinおよび負荷RLも併せて表示している。システム電源Vinは、JFET10のドレインDと接地GND間に接続される。負荷RLは、JFET10のソースSと接地GND間に接続される。なお、図1において、ゲート・ソース間電圧Vgsおよびドレイン・ソース間電圧Vdsは、それぞれ、ソースSを基準にしたときのゲートGおよびドレインDの電位である。

【0024】

NチャネルのJFET10は、負の閾値電圧Vth1を有する。JFET10は、ゲート・ソース間電圧Vgsが負の閾値電圧Vth1より小さいVgs<Vth1(第2の範囲)の場合にターンオフし、ゲート・ソース間電圧Vgsが負の閾値電圧Vth1以上であるVgs≧Vth1(第1の範囲)の場合にターンオンする。

【0025】

ゲートドライブ回路11は、第1、第2の電源ノード13,12と、制御信号の入力ノード14と、出力ノード15とを含む。電源ノード12には駆動電源VDDoutの正極が接続され、電源ノード13には駆動電源VDDoutの負極が接続される。駆動電源VDDoutは、主回路側とはフローティングの状態にある絶縁電源である。また、出力ノード15はJFET10のゲートGに接続され、高圧側の電源ノード12はJFET10のソースSに接続される。

【0026】

ゲートドライブ回路11は、制御信号に応じて出力ノード15の接続を切替える。具体的には、入力ノード14に入力される制御信号の電圧Vsigが正の閾値電圧Vth2以下のLレベルの場合、出力ノード15と低電圧側の電源ノード13とを導通させる。一方、電圧Vsigが閾値電圧Vth2より大きいHレベルの場合、出力ノード15と高電圧側の電源ノード12とを導通させる。したがって、制御信号の電圧Vsigが閾値電圧Vth2より大きいHレベルの場合に、出力ノード15の電位Vgは高圧側の電源ノード12の電位Vpに等しくなり、制御信号の電圧Vsigが閾値電圧Vth2より大きいHレベルの場合に出力ノード15の電位Vgは低圧側の電源ノード13の電位Vnに等しくなる。

【0027】

ここで、実施の形態1では、JFET10のゲートGが出力ノード15に接続され、ソースSが高圧側の電源ノード12に接続されるので、JFET10のゲート・ソース間電圧Vgsは、出力ノード15と電源ノード12との間の出力電圧Vout=Vg−Vpに等しくなる。したがって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、

Vgs=Vout=Vg−Vp=Vp−Vp=0 …(1)

となって(第1の範囲)、JFET10は導通する。

【0028】

一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、

Vgs=Vout=Vg−Vp=Vn−Vp

=−VDDout …(2)

となる。駆動電源VDDoutの電圧をJFET10の閾値電圧Vth1の絶対値より大きくなるように設定すれば、Vgs=−VDDout<Vth1となって(第2の範囲)、JFET10は非導通になる。したがって、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。

【0029】

上記のような動作のゲートドライブ回路11は、たとえば、駆動電源VDDoutの正極と負極との間に直列接続された2個のNチャネルのトランジスタによって構成することができる。この場合、正極側のトランジスタのゲートには制御信号Vsigが非反転入力され、負極側のトランジスタのゲートには制御信号Vsigが反転入力される。2個のトランジスタの接続点が出力ノード15に相当する。また、上記の動作は通常のノーマリオフ型の素子用のゲートドライブ回路の動作と同じであるので、市販のゲートドライバを利用することによってゲートドライブ回路11を簡単に構成することができる。

【0030】

次に、ゲートドライブ回路11に市販のノーマリオフ型素子用のゲートドライバを使用した場合の半導体スイッチング装置1の動作例について説明する。

【0031】

図2は、市販のゲートドライバを用いたゲートドライブ回路11の構成を示す図である。

【0032】

図3は、JFET10の接続を示す回路図である。

図2、図3を参照して、使用したJFET10のゲート・ソース間の閾値電圧はVth1=−12Vである。また、ゲートドライバ11として、Analog Devices社の製品(型番:ADuM1233)を使用した。このドライバは5MHzまで動作可能である。電源VDDinはゲートドライバ11の入力信号側の回路の電源であり、ゲートドライバ11の入力信号側の電源ノード16,17に接続される。また、JFET10のターンオフに要する時間を短縮するために、JFET10のターンオフ時のゲート・ソース間電圧Vgsの絶対値が、閾値電圧Vth1の絶対値よりも充分大きくなるように駆動電源VDDoutの電圧を17Vとしている。なお、電源VDDinおよびVDDoutに並列に接続されているコンデンサ素子21,22は、バイパスコンデンサ素子である。

【0033】

入力ノード14および電源ノード17間には、制御信号源FGが接続される。これによって、ゲートドライバ11に制御信号Vsigが入力される。制御信号Vsigは、振幅4V、周波数3.1MHzの方形波である。パワー回路側に対して入力信号側の回路を保護するために、入力された制御信号Vsigは絶縁用のパルストランス19を介して出力側に伝達される。パルストランス19の入力側にA/D(Analog to Digital)変換器18が設けられ、出力側にD/A(Digital to Analog)変換器20が設けられる。

【0034】

次に、ドライブ回路の駆動時の制御信号Vsigおよび出力電圧Voutの波形の測定結果について説明する。

【0035】

図4は、図2のゲートドライバ11を用いて図3の回路を駆動しているときの制御信号Vsigおよび出力電圧Voutの波形図である。図4の実線のグラフは制御信号Vsigの波形であり、図4の破線のグラフは出力電圧Voutの波形である。

【0036】

図4を参照して、出力電圧Voutの立ち上がり時間tRを、出力電圧Voutが−0.9VDDout(図4の電圧V3)になった時刻t1から−0.1VDDout(図4の電圧V1)になった時刻t2までの時間と定義する。また、出力電圧Voutの立ち下がり時間tFを、出力電圧Voutが−0.1VDDout(図4の電圧V1)になった時刻t3から−0.9VDDout(図4の電圧V3)になった時刻t4までの時間と定義する。図4の場合、立ち上がり時間tRは18nsであり、立ち下がり時間tFは20nsである。

【0037】

また、制御信号Vsigから出力電圧Voutへの遅延時間tdelayを、制御信号Vsigが振幅の50%に達する時刻t5から、出力電圧Voutが振幅の50%(図4の電圧V2)に達する時刻t6までの時間と定義する。図4の場合、遅延時間tdelayは130nsである。これは、3.1MHzの制御信号Vsigの周期320nsの約40%である。

【0038】

以上より、立ち上がり時間tR、立ち下がり時間tFがともに20ns程度と短く、3MHzを越える周波数のゲート駆動用の出力電圧Voutが生成できることがわかる。一方、遅延時間tdelayは、制御信号Vsigの周期に比べて無視出来ないほど大きいものの、ゲート駆動方式が通常のパルス幅変調による場合には問題とならない。

【0039】

次に、図2のゲートドライバ11で、図3のSiCJFETをスイッチングさせたときのJFET10電圧特性の測定結果について説明する。図3のJFET10の定格は、ドレイン・ソース間耐電圧:400V、順方向電流:1.25Aである。図3に示すように、30Vのシステム電源Vinに33Ωの無誘導抵抗が負荷RLとして接続されている。1A近い電流を高速でスイッチングするため、回路に寄生するインダクタンス成分の影響が大きくなると考えられる。そこで、寄生インダクタンス成分を低減するために、スイッチング回路は、導体幅約5mmのプリント基板で作成し、電源などの各機器との接続ケーブルは、ツイストペア状に撚り合わせ、電流ループが極力小さくなるように注意を払っている。JFETのゲート制御電圧Vgsとして、図2に示すゲートドライブ回路11の出力電圧Voutを入力する。

【0040】

図5は、ゲート・ソース間電圧Vgsおよびドレイン・ソース間電圧Vdsの波形図である。図5の実線のグラフはゲート・ソース間電圧Vgsの波形であり、図5の破線のグラフはドレイン・ソース間電圧Vdsの波形である。

【0041】

図5を参照して、JFET10がターンオフした時刻t7の直後、ドレイン・ソース間電圧Vdsが大きくオーバーシュートし、時刻t9で61Vに達している。これは、電源電圧Vinの約2倍の電圧である。また、オーバーシュートの後も、25V〜40Vの間でリンギングしている。また、時刻t14以降のターンオン時には、約10Vアンダーシュートした後、10Vと−5Vの間でリンギングしている。これらのリンギングは、回路作成時に寄生インダクタンスを完全に排除できなかったために生じたもので、素子や回路に寄生するインダクタンス成分と、JFET10の内部に存在するPN接合のキャパシタンス成分によって引き起こされていると考えられる。

【0042】

ターンオフ時のリンギング周波数について定量的に評価する。ターンオフ時にドレイン・ソース間電圧Vdsが0.1Vinとなる時刻t7、およびその後のリンギングの腹となる時刻t9,t10,t11,t12を図5から読み取ると、順にt7=0.2μs、t9=0.222μs、t10=0.242μs、t11=0.258μs、t12=0.270μsである。時刻t7から時刻t10を1周期とすると、t10−t7=42nsとなる。同様に、t11−t9=36ns、t12−t10=28nsである。JFET10内部のPN接合のキャパシタンス成分は電圧により変化するため、それに伴いリンギング周波数も変化する。ここでは、電圧の変化が最も少ない、時刻t10から時刻t12に注目する。このときの周波数は35.7MHzである。

【0043】

次に、ターンオフや、ターンオンに関わる時間について定量的に評価する。ターンオフに要する時間toffを、ドレイン・ソース間電圧Vdsが電源電圧Vinの10%(図5の電圧V4)を越える時刻t7から、電源電圧Vinの90%(図5の電圧V5)に達する時刻t8までの時間と定義すると、ターンオフ時間toffは8nsとなる。同様に、ターンオンに要する時間tonを、ドレイン・ソース間電圧Vdsが0.9Vinとなる時刻t13から0.1Vinに降下する時刻t14までの時間と定義すると、ターンオン時間tonは10nsである。ゲートドライブ回路11の駆動電源VDDoutの電圧を閾値電圧Vth1に比べて大きく設定し、オーバードライブしているため、ターンオン時間tonが図4の立ち下がり時間tFに比べ60%程度短くなっている。

【0044】

以上のとおり、実施の形態1の半導体スイッチング装置1によれば、市販のノーマリオフ型の素子用のゲートドライバを用いた簡単な構成で、制御信号VsigがLレベルのときにノーマリオンのJFET10がターンオフするというノーマリオフ的な駆動が可能になる。これによって、電力変換装置としての安全性を高めることができる。

【0045】

[実施の形態2]

図6は、この発明の実施の形態2による半導体スイッチング装置2の構成を示すブロック図である。図6の半導体スイッチング装置2は、分圧部30をさらに含む点で、図1の半導体スイッチング装置1と異なる。その他の点については、実施の形態1の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0046】

分圧部30は、高圧側の電源ノード12と分圧ノードNDとの間に逆バイアス方向に接続されたツェナーダイオード素子31と、分圧ノードNDと低圧側の電源ノード13との間に接続された抵抗素子32とを含む。JFET10のソースSは、図1の場合の電源ノード12に代えて、分圧ノードNDに接続される。したがって、図6の場合、JFET10のソースSの電位は、分圧ノードNDの電位Vdに等しい。このとき、分圧ノードNDの電位Vdは、電源ノード12の電位Vpよりツェナーダイオード素子31のツェナー電圧Vz分だけ低く、Vd=Vp−Vzとなる。また、JFET10のゲート・ソース間に供給される出力電圧Voutは、出力ノード15と分圧ノードNDとの電位差Vg−Vdで与えられる。

【0047】

よって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、出力ノードVgの電位Vgは電源ノード12の電位Vpに等しいので、

Vgs=Vout=Vg−Vd=Vp−Vd …(3)

となる。すなわち、この場合のゲート・ソース間の電圧Vgsは、電源ノード13と分圧ノードNDとの間の電圧に等しい。さらに、Vd=Vp−Vzの関係を代入すると、電源ノード13と分圧ノードNDとの間の電圧は、

Vgs=Vp−Vd=Vp−(Vp−Vz)=Vz …(4)

となって(第1の範囲)、JFET10は導通する。

【0048】

一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、出力ノードVgの電位Vgは電源ノード13の電位Vnに等しいので、

Vgs=Vout=Vg−Vd=Vn−Vd …(5)

となる。すなわち、この場合のゲート・ソース間の電圧Vgsは、電源ノード13と分圧ノードNDとの間の電圧に等しい。さらに、Vd=Vp−Vzの関係を代入すると、電源ノード13と分圧ノードNDとの間の電圧は、

Vgs=Vn−Vd=Vn−(Vp−Vz)=Vz−(Vn−Vp)

=Vz−VDDout …(6)

となる。したがって、駆動電源のVDDoutの電圧を閾値電圧Vth1の絶対値よりもさらにツェナー電圧Vz分だけ大きく設定すれば、Vz−VDDout<Vth1<0となって(第2の範囲)、JFET10は非導通になる。

【0049】

以上の結果から、実施の形態1の場合と同様に、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。また、ターンオン時のゲート・ソース間電圧Vgsは、実施の形態1の場合の0Vと異なり、ツェナー電圧Vzに等しい正の電圧になる。したがって、ツェナー電圧VzをJFET10のゲート・ソース間のPN接合のビルトイン電圧に近い値に設定すれば、実施の形態1の場合よりも、高周波特性を維持した上でオン抵抗を低減させることができる。なお、ターンオン時のゲート・ソース間電圧Vgsがゲート・ソース間のPN接合のビルトイン電圧を超える場合にはさらにオン抵抗の低減が期待できるが、ゲートGからホールが注入されることになるのでスイッチング速度が低下するというデメリットがある。

【0050】

また、上記の構成において、ツェナーダイオード素子31および抵抗素子32は複数個設けてもよい。また、ツェナーダイオード素子31を分圧ノードNDと低圧側の電源ノード13との間に設け、抵抗素子32を分圧ノードNDと高圧側の電源ノード12との間に設けることもできる。すなわち、分圧部30は、少なくとも1個以上のツェナーダイオード素子31と、少なくとも1個以上の抵抗素子32とから構成され、少なくとも1つ以上のツェナーダイオード素子31と抵抗素子32との直列接続を有する構成であってもよい。ただし、いずれの場合も、分圧ノードNDと低電圧側の電源ノード13との電位差Vd−Vnが閾値電圧Vth1の絶対値よりも大きくなるように設定する必要がある。

【0051】

[実施の形態3]

図7は、この発明の実施の形態3による半導体スイッチング装置3の構成を示すブロック図である。図7の分圧部30Aは、ツェナーダイオード素子31に代えてダイオード素子33を含む点で図6の分圧部30と異なる。その他の点については、図6の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0052】

分圧部30Aは、高圧側の電源ノード12と分圧ノードNDとの間に順バイアス方向に接続されたダイオード素子33と、分圧ノードNDと低圧側の電源ノード13との間に接続された抵抗素子32とを含む。このとき、分圧ノードNDの電位Vdは、電源ノード12の電位Vpよりダイオード素子33のビルトイン電圧Vb分だけ低く、Vd=Vp−Vbとなる。

【0053】

よって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、

Vgs=Vout=Vg−Vd=Vp−(Vp−Vb)=Vb …(7)

となって(第1の範囲)、JFET10は導通する。一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、

Vgs=Vout=Vg−Vd=Vn−(Vp−Vb)

=Vb−(Vn−Vp)=Vb−VDDout …(8)

となる。したがって、駆動電源のVDDoutの電圧を閾値電圧Vth1の絶対値よりもさらにダイオード素子33のビルトイン電圧Vb分だけ大きく設定すれば、Vb−VDDout<Vth1<0となって(第2の範囲)、JFET10は非導通になる。

【0054】

以上の結果から、実施の形態2の場合と同様に、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。また、ターンオン時のゲート・ソース間電圧Vgsは、ダイオード素子33のビルトイン電圧Vbに等しい正の電圧になるので、実施の形態1の場合に比べてオン抵抗を低減させることができる。

【0055】

上記の構成において、ダイオード素子33および抵抗素子32は複数個設けてもよい。また、直列接続された複数のダイオード素子33を分圧ノードNDと低圧側の電源ノード13との間に設け、抵抗素子32を分圧ノードNDと高圧側の電源ノード12との間に設けることもできる。すなわち、分圧部30Aは、少なくとも1個以上のダイオード素子33と、少なくとも1個以上の抵抗素子32とから構成され、少なくとも1つ以上のダイオード素子33と抵抗素子32との直列接続を有する構成であってもよい。ただし、いずれの場合も、分圧ノードNDと低電圧側の電源ノード13との電位差Vd−Vnが閾値電圧Vth1の絶対値よりも大きくなるように設定する必要がある。

【0056】

[実施の形態4]

図8は、この発明の実施の形態4による半導体スイッチング装置4の構成を示すブロック図である。図8の分圧部30Bは、抵抗素子32と並列にコンデンサ素子34をさらに含む点で、図6の実施の形態2の分圧部30と異なる。コンデンサ素子34を設けることによって、JFET10のスイッチングに伴なう分圧ノードNDの電位の変動を抑制することができるので、図6の実施の形態2の場合に比べて半導体スイッチング装置4をより安定に動作させることができる。その他の点については、図6の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0057】

上記構成において、抵抗素子32と並列でなくツェナーダイオード素子31と並列にコンデンサ素子34を設けてもよい。また、コンデンサ素子34を複数個設けてもよい。すなわち、分圧部30Bは、分圧ノードNDと低圧側の電源ノード13との間に接続される、または、分圧ノードNDと高圧側の電源ノード12との間に接続される、少なくとも1個以上のコンデンサ素子を含む。いずれの場合も、コンデンサ素子によって、JFET10のスイッチングに伴なう分圧ノードNDの電位の変動を抑制するという効果を奏する。

【0058】

[実施の形態5]

図9は、この発明の実施の形態5による半導体スイッチング装置5の構成を示すブロック図である。図9の半導体スイッチング装置5は、分圧部30Cの構成が図6の実施の形態2の分圧部30構成と異なる。その他の点については、実施の形態2の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0059】

分圧部30Cは、高圧側の電源ノード12と分圧ノードNDとの間に接続されたコンデンサ素子C1と、分圧ノードNDと低圧側の電源ノード13との間に接続されたコンデンサ素子C2とを含む。JFET10のソースSは、分圧ノードNDに接続される。したがって、図9の場合、JFET10のゲート・ソース間に供給される出力電圧Voutは、出力ノード15と分圧ノードNDとの電位差Vg−Vdになる。また、分圧部30Cによって、電源ノード12,13間の電圧がコンデンサ素子C1,C2の容量の逆比となるように分割される。

【0060】

よって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、ゲート・ソース間電圧Vgsは、電源ノード12と分圧ノードNDとの間の電圧Vp−Vdに等しく、

Vgs=Vout=Vg−Vd=Vp−Vd

=(Vp−Vn)×C2/(C1+C2)

=VDDout×C2/(C1+C2) …(9)

となって(第1の範囲)、JFET10は導通する。一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、ゲート・ソース間電圧Vgsは、電源ノード13と分圧ノードNDとの間の電圧Vn−Vdに等しく、

Vgs=Vout=Vg−Vd=Vn−Vd

=−(Vp−Vn)×C1/(C1+C2)

=−VDDout×C1/(C1+C2) …(10)

となる。したがって、駆動電源VDDoutの電圧を閾値電圧Vth1の絶対値の(C1+C2)/C1倍より大きく設定すれば、Vgs<Vth1<0となって(第2の範囲)、JFET10は非導通になる。

【0061】

以上の結果から、実施の形態1の場合と同様に、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。このとき、実施の形態9の場合には分圧部30Cがコンデンサ素子のみで構成されており、抵抗素子32が用いられていないので、実施の形態2〜4に比べて消費電力を小さくできるメリットがある。また、ターンオン時のゲート・ソース間電圧Vgsは正の電圧になる。したがって、VDDout×C2/(C1+C2)をJFET10のゲート・ソース間のPN接合のビルトイン電圧に近い値に設定すれば、実施の形態1の場合に比べて、高周波特性を維持した上でオン抵抗を低減させることができる。

【0062】

上記の構成において、第1、第2のコンデンサ素子C1,C2をそれぞれ複数個ずつ設けてもよい。すなわち、分圧部30Cは、少なくとも2個以上のコンデンサ素子で構成され、少なくとも1つ以上のコンデンサ素子の直列接続を有する構成であってもよい。ただし、いずれの場合も、分圧ノードNDと低電圧側の電源ノード13との電位差Vd−Vnが閾値電圧Vth1の絶対値よりも大きくなるように設定する必要がある。

【0063】

[実施の形態6]

図10は、この発明の実施の形態6による半導体スイッチング装置6の構成を示すブロック図である。図10の半導体スイッチング装置6は、分圧部30Dの構成が図6の実施の形態2の分圧部30構成と異なる。その他の点については、実施の形態2の場合と共通するので、同一または相当する部分には同一の参照符号を付して説明を繰返さない。

【0064】

分圧部30Dは、高圧側の電源ノード12と分圧ノードNDとの間に接続された抵抗素子R1と、分圧ノードNDと低圧側の電源ノード13との間に接続された抵抗素子R2とを含む。JFET10のソースSは、分圧ノードNDに接続される。したがって、図10の場合、JFET10のゲート・ソース間に供給される出力電圧Voutは、出力ノード15と分圧ノードNDとの電位差Vg−Vdになる。また、分圧部30Dによって、電源ノード12,13間の電圧が抵抗素子R1,R2の抵抗値の比で分割される。

【0065】

よって、制御信号の電圧Vsigが閾値電圧Vth2より大きい場合には、ゲート・ソース間電圧Vgsは、電源ノード12と分圧ノードNDとの間の電圧Vp−Vdに等しく、

Vgs=Vout=Vg−Vd=Vp−Vd

=(Vp−Vn)×R1/(R1+R2)

=VDDout×R1/(R1+R2) …(11)

となって(第1の範囲)、JFET10は導通する。一方、制御信号の電圧Vsigが閾値電圧Vth2以下の場合には、ゲート・ソース間電圧Vgsは、電源ノード13と分圧ノードNDとの間の電圧Vn−Vdに等しく、

Vgs=Vout=Vg−Vd=Vn−Vd

=−(Vp−Vn)×R2/(R1+R2)

=−VDDout×R2/(R1+R2) …(12)

となる。したがって、駆動電源VDDoutの電圧を閾値電圧Vth1の絶対値の(R1+R2)/R2倍より大きく設定すれば、Vgs<Vth1<0となって(第2の範囲)、JFET10は非導通になる。

【0066】

以上の結果から、実施の形態1の場合と同様に、閾値電圧Vth2以下の制御信号の入力によって、JFET10がターンオフするという、ノーマリオフ的な動作が実現している。また、ターンオン時のゲート・ソース間電圧Vgsは正の電圧になる。したがって、VDDout×R1/(R1+R2)をJFET10のゲート・ソース間のPN接合のビルトイン電圧に近い値に設定すれば、実施の形態1の場合に比べて、高周波特性を維持した上でオン抵抗を低減させることができる。

【0067】

上記の構成において、第1、第2の抵抗素子R1,R2をそれぞれ複数個ずつ設けてもよい。すなわち、分圧部30Dは、少なくとも2個以上の抵抗素子で構成され、少なくとも一つ以上の抵抗素子の直列接続を有する構成であってもよい。ただし、いずれの場合も、分圧ノードNDと低電圧側の電源ノード13との電位差Vd−Vnが閾値電圧Vth1の絶対値よりも大きくなるように設定する必要がある。

【0068】

今回開示された実施の形態はすべての点で例示であって、制限的なものではないと考えられるべきである。この発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味、および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0069】

【図1】この発明の実施の形態1による半導体スイッチング装置1の構成を示すブロック図である。

【図2】市販のゲートドライバを用いたゲートドライブ回路11の構成を示す図である。

【図3】JFET10の接続を示す回路図である。

【図4】図2のゲートドライバ11を用いて図3の回路を駆動しているときの制御信号Vsigおよび出力電圧Voutの波形図である。

【図5】ゲート・ソース間電圧Vgsおよびドレイン・ソース間電圧Vdsの波形図である。

【図6】この発明の実施の形態2による半導体スイッチング装置2の構成を示すブロック図である。

【図7】この発明の実施の形態3による半導体スイッチング装置3の構成を示すブロック図である。

【図8】この発明の実施の形態4による半導体スイッチング装置4の構成を示すブロック図である。

【図9】この発明の実施の形態5による半導体スイッチング装置5の構成を示すブロック図である。

【図10】この発明の実施の形態6による半導体スイッチング装置6の構成を示すブロック図である。

【符号の説明】

【0070】

1〜5 半導体スイッチング装置、10 JFET、11 ゲートドライブ回路、12,13 電源ノード、14 入力ノード、15 出力ノード、30,30A,30B,30C 分圧部、31 ツェナーダイオード素子、32 抵抗素子、33 ダイオード素子、34 コンデンサ素子、C1,C2 コンデンサ素子、D ドレイン、G ゲート、S ソース、R1,R2 抵抗素子、ND 分圧ノード、Vout 出力電圧、Vsig 制御信号、Vth1 閾値電圧(ゲート・ソース間電圧)、Vth2 閾値電圧(制御信号)。

【特許請求の範囲】

【請求項1】

第1、第2の主電極および制御電極を有し、前記第1の主電極および前記制御電極間の制御電圧が第1の範囲のときに前記第1、第2の主電極間が導通し、前記制御電圧が第2の範囲のときに前記第1、第2の主電極間が非導通になるノーマリオン型の半導体スイッチング素子と、

第1、第2の電源ノード、制御信号入力ノード、および出力ノードを有し、前記制御信号入力ノードに制御信号を受け、前記制御信号の大きさが閾値以下の場合に前記第1の電源ノードと前記出力ノードとが導通し、前記制御信号の大きさが前記閾値を超える場合に前記第2の電源ノードと前記出力ノードとが導通するゲートドライブ回路とを備え、

前記出力ノードは、前記制御電極に接続され、

さらに、前記第1、第2の電源ノード間に接続される駆動電源と、

前記駆動電源の電圧を分圧し、分圧された電圧を出力する分圧ノードを有する分圧部とを備え、

前記分圧ノードは、前記第1の主電極に接続され、

前記分圧ノードと前記第1の電源ノードとの間の電圧は、前記第2の範囲にあり、

前記分圧ノードと前記第2の電源ノードとの間の電圧は、前記第1の範囲にある、半導体スイッチング装置。

【請求項2】

前記分圧部は、少なくとも2個以上のコンデンサ素子で構成され、コンデンサ素子の直列接続を少なくとも1つ以上有する、請求項1に記載の半導体スイッチング装置。

【請求項3】

前記分圧部は、少なくとも1個以上のツェナーダイオード素子またはダイオード素子と、少なくとも1個以上の抵抗素子とから構成され、ツェナーダイオード素子またはダイオード素子と抵抗素子との直列接続を少なくとも1つ以上有する、請求項1に記載の半導体スイッチング装置。

【請求項4】

前記分圧部は、少なくとも2個以上の抵抗素子から構成され、抵抗素子の直列接続を少なくとも1つ以上有する、請求項1に記載の半導体スイッチング装置。

【請求項5】

前記分圧部は、前記分圧ノードと前記第1の電源ノードとの間に接続される、または、前記分圧ノードと前記第2の電源ノードとの間に接続される、少なくとも1個以上のコンデンサ素子を含む、請求項1に記載の半導体スイッチング装置。

【請求項6】

第1、第2の主電極および制御電極を有し、前記第1の主電極および前記制御電極間の制御電圧が第1の範囲のときに前記第1、第2の主電極間が導通し、前記制御電圧が第2の範囲のときに前記第1、第2の主電極間が非導通になるノーマリオン型の半導体スイッチング素子と、

第1、第2の電源ノード、制御信号入力ノード、および出力ノードを有し、前記制御信号入力ノードに制御信号を受け、前記制御信号の大きさが閾値以下の場合に前記第1の電源ノードと前記出力ノードとが導通し、前記制御信号の大きさが前記閾値を超える場合に前記第2の電源ノードと前記出力ノードとが導通するゲートドライブ回路とを備え、

前記出力ノードは、前記制御電極に接続され、

前記第2の電源ノードは、前記第1の主電極に接続され、

さらに、前記第1、第2の電源ノード間に接続される駆動電源を備え、

前記駆動電源の電圧は前記第2の範囲にある、半導体スイッチング装置。

【請求項7】

前記半導体スイッチング素子は、シリコンよりバンドギャップの大きい半導体材料を用いて形成される、請求項1〜6のいずれか1項に記載の半導体スイッチング装置。

【請求項8】

前記半導体スイッチング素子は、接合型電界効果トランジスタである、請求項1〜7のいずれか1項に記載の半導体スイッチング装置。

【請求項1】

第1、第2の主電極および制御電極を有し、前記第1の主電極および前記制御電極間の制御電圧が第1の範囲のときに前記第1、第2の主電極間が導通し、前記制御電圧が第2の範囲のときに前記第1、第2の主電極間が非導通になるノーマリオン型の半導体スイッチング素子と、

第1、第2の電源ノード、制御信号入力ノード、および出力ノードを有し、前記制御信号入力ノードに制御信号を受け、前記制御信号の大きさが閾値以下の場合に前記第1の電源ノードと前記出力ノードとが導通し、前記制御信号の大きさが前記閾値を超える場合に前記第2の電源ノードと前記出力ノードとが導通するゲートドライブ回路とを備え、

前記出力ノードは、前記制御電極に接続され、

さらに、前記第1、第2の電源ノード間に接続される駆動電源と、

前記駆動電源の電圧を分圧し、分圧された電圧を出力する分圧ノードを有する分圧部とを備え、

前記分圧ノードは、前記第1の主電極に接続され、

前記分圧ノードと前記第1の電源ノードとの間の電圧は、前記第2の範囲にあり、

前記分圧ノードと前記第2の電源ノードとの間の電圧は、前記第1の範囲にある、半導体スイッチング装置。

【請求項2】

前記分圧部は、少なくとも2個以上のコンデンサ素子で構成され、コンデンサ素子の直列接続を少なくとも1つ以上有する、請求項1に記載の半導体スイッチング装置。

【請求項3】

前記分圧部は、少なくとも1個以上のツェナーダイオード素子またはダイオード素子と、少なくとも1個以上の抵抗素子とから構成され、ツェナーダイオード素子またはダイオード素子と抵抗素子との直列接続を少なくとも1つ以上有する、請求項1に記載の半導体スイッチング装置。

【請求項4】

前記分圧部は、少なくとも2個以上の抵抗素子から構成され、抵抗素子の直列接続を少なくとも1つ以上有する、請求項1に記載の半導体スイッチング装置。

【請求項5】

前記分圧部は、前記分圧ノードと前記第1の電源ノードとの間に接続される、または、前記分圧ノードと前記第2の電源ノードとの間に接続される、少なくとも1個以上のコンデンサ素子を含む、請求項1に記載の半導体スイッチング装置。

【請求項6】

第1、第2の主電極および制御電極を有し、前記第1の主電極および前記制御電極間の制御電圧が第1の範囲のときに前記第1、第2の主電極間が導通し、前記制御電圧が第2の範囲のときに前記第1、第2の主電極間が非導通になるノーマリオン型の半導体スイッチング素子と、

第1、第2の電源ノード、制御信号入力ノード、および出力ノードを有し、前記制御信号入力ノードに制御信号を受け、前記制御信号の大きさが閾値以下の場合に前記第1の電源ノードと前記出力ノードとが導通し、前記制御信号の大きさが前記閾値を超える場合に前記第2の電源ノードと前記出力ノードとが導通するゲートドライブ回路とを備え、

前記出力ノードは、前記制御電極に接続され、

前記第2の電源ノードは、前記第1の主電極に接続され、

さらに、前記第1、第2の電源ノード間に接続される駆動電源を備え、

前記駆動電源の電圧は前記第2の範囲にある、半導体スイッチング装置。

【請求項7】

前記半導体スイッチング素子は、シリコンよりバンドギャップの大きい半導体材料を用いて形成される、請求項1〜6のいずれか1項に記載の半導体スイッチング装置。

【請求項8】

前記半導体スイッチング素子は、接合型電界効果トランジスタである、請求項1〜7のいずれか1項に記載の半導体スイッチング装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2010−51093(P2010−51093A)

【公開日】平成22年3月4日(2010.3.4)

【国際特許分類】

【出願番号】特願2008−213101(P2008−213101)

【出願日】平成20年8月21日(2008.8.21)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【出願人】(504132272)国立大学法人京都大学 (1,269)

【Fターム(参考)】

【公開日】平成22年3月4日(2010.3.4)

【国際特許分類】

【出願日】平成20年8月21日(2008.8.21)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【出願人】(504132272)国立大学法人京都大学 (1,269)

【Fターム(参考)】

[ Back to top ]