半導体スイッチ回路の電圧バランス回路

【課題】スイッチング過渡時のスイッチング損失と偏りを低減でき、オン・オフ定常時の電圧アンバランス抑制を容易にし、電圧バランス制御の応答性に優れ、多数のスイッチング素子の直列接続回路に対応できる。

【解決手段】抵抗分圧回路RD1、RD2は、各スイッチング素子S1、S2のエミッタ−コレクタ間に、それぞれ同等抵抗値で同等分圧比の分圧抵抗を並列接続し、スイッチング素子の直列接続点を中点Nとしてスイッチング素子のエミッタ−コレクタ間電圧に比例した電圧を負担電圧としてそれぞれ検出する。電圧バランス制御回路(VD1,VD2,DAMP,VAC)は、各検出電圧の電圧偏差がゼロ(零)になるよう、スレーブ側のスイッチング素子S1のゲート電流を補正して各スイッチング素子の負担電圧をバランスさせる。

【解決手段】抵抗分圧回路RD1、RD2は、各スイッチング素子S1、S2のエミッタ−コレクタ間に、それぞれ同等抵抗値で同等分圧比の分圧抵抗を並列接続し、スイッチング素子の直列接続点を中点Nとしてスイッチング素子のエミッタ−コレクタ間電圧に比例した電圧を負担電圧としてそれぞれ検出する。電圧バランス制御回路(VD1,VD2,DAMP,VAC)は、各検出電圧の電圧偏差がゼロ(零)になるよう、スレーブ側のスイッチング素子S1のゲート電流を補正して各スイッチング素子の負担電圧をバランスさせる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数直列接続の半導体スイッチング素子(IGBT等)をオン・オフ同期制御する半導体スイッチ回路において、各スイッチング素子の負担電圧をアクティブ(能動的に)バランスさせる電圧バランス回路に関する。

【背景技術】

【0002】

(1)半導体スイッチング素子の複数直列接続について

半導体スイッチング素子を複数直列に接続し、それらを1つの素子としてスイッチングをオン・オフ同期することで、低耐電圧のスイッチング素子で高耐電圧特性を得るスイッチング回路を実現するができる。

【0003】

しかも、低耐圧素子は、高耐圧素子に比べて顕著に価格が安いため、低コストで高耐圧の装置が構成できる。例えば、現状、最高で6500V、600Aの耐圧・定格電流をもつIGBTがリリースされているが、それ以上の耐圧を持つ素子が必要な場合にIGBTを直列接続する(例えば、非特許文献4参照)。

【0004】

また、高耐圧素子は大きな電流容量を持つものがないが、低耐圧素子には大容量のものが存在するため、低耐圧素子を複数直列接続することで、高耐圧・大電流のスイッチング素子およびこれを使用した装置を構成できる。この場合、電流容量を高めるために、低耐圧素子を複数並列接続する必要はない。

【0005】

また、低耐圧素子は、高耐圧素子に比べてスイッチング速度が速く、顕著にスイッチング損失が小さい傾向にある。このため、高耐圧素子に比べて、低耐圧素子を複数直列に接続した方が、スイッチング周波数が高い場合の損失(導通損失+スイッチング損失)が小さくなることがある。

【0006】

(2)半導体スイッチング素子の複数直列接続時の問題点

複数の直列接続した半導体スイッチング素子それぞれに均等に電圧が加わらないこと(電圧アンバランスの発生)がある。この電圧アンバランスの発生は、素子耐圧を超える電圧がスイッチング素子に加わって素子が破壊されたり、スイッチング時の発生損失に大きな偏りが発生することで、スイッチング素子の発熱や寿命に大きな影響を与えたりする可能性がある。

【0007】

電圧アンバランスの原因には、(a)スイッチングタイミングのばらつきによる電圧アンバランス、(b)定常的な電流遮断時(スイッチング素子のターンオフ時)における漏れ電流のばらつきによる電圧アンバランス、(c)スイッチング素子のターンオフ動作時のテール電流のばらつきによる電圧アンバランスなどがある。

【0008】

このうち、(a)スイッチングタイミングのばらつきによる電圧アンバランスが発生する原因としては、ゲート制御信号の伝達時間のばらつき、ゲートドライバの特性のばらつき、スイッチング素子の入力容量・閾値電圧などの特性のばらつきなどがある。

【0009】

上記のようなスイッチング動作の過渡時に発生する電圧アンバランスに起因する過電圧を解消する方式の従来技術として、以下の方式がある。

【0010】

(A)アクティブゲートコントロールによる過電圧抑制

(A1)ツェナーダイオードを用いる方式(非特許文献3)

図9は、ツェナーダイオードによるクランプによって電圧バランスさせる回路の例を示し、直列接続回路の1つのスイッチング素子をツェナーダイオードにより電圧クランプする場合である。IGBTのスイッチング素子1のオン・オフをゲートドライブ回路2のゲートドライブ出力で制御する構成において、スイッチング素子1のコレクタ−ゲート間の電圧をクランプするツェナーダイオード3をその電流制限抵抗4との直列接続で設ける。

【0011】

この構成において、ツェナーダイオード3のツェナー電圧はスイッチング素子1の閾値電圧に予め設定しておき、直列接続された複数のスイッチング素子をターンオフさせたとき、スイッチング素子1が速くターンオフした場合にはその負担電圧が大きくなる。この大きい負担電圧が閾値電圧以上になると、ツェナーダイオード3がオンし、スイッチング素子1のコレクタからゲートに電流が注入され、スイッチング素子1のゲート電圧を上昇させ、これによりスイッチング素子1の遮断電流が弱まり、スイッチング素子1のエミッタ−コレクタ間にかかる負担電圧が減少する。このような動作によりスイッチング素子1の負担電圧が閾値電圧付近にクランプされる。

【0012】

(A2)電圧を検出しフィードバックする方式(非特許文献1、非特許文献4)

図10は、電圧フィードバックによる電圧バランス回路の例を示す。同図は、基本的にはツェナーダイオードによる電圧バランス方式と同じもので、スイッチング素子1のエミッタ−コレクタ間電圧(負担電圧)VCEを抵抗分圧回路で分圧し、電圧制御素子により電圧VCEと閾値電圧VREFの差ΔVに応じたゲート電流IGAをゲート電流IGにフィードバックで注入する。

【0013】

以上に説明したアクティブゲートコントロール方式で過電圧抑制を行った結果、電圧アンバランスが小さくなるようにゲート信号を制御できるので、スイッチング素子には耐圧以上の電圧が掛からず、過電圧でのスイッチング素子の破壊を防止できる。

【0014】

また、閾値を分圧値近くに設定すればクランプによって電圧のアンバランスが減少する。例えば、直列回路の両端電圧が1000Vの時に,クランプする電圧閾値を500Vに近くすることで電圧のアンバランスを少なくすることができる。

【0015】

(B)マスタースレーブ方式による過電圧抑制(非特許文献2)

図11は、マスタースレーブ方式の過電圧抑制回路の例を示す。同図は、直列接続の2直列スイッチング素子1A、1Bにかかっている電圧を抵抗分圧回路5A、5Bでそれぞれ検出し、この検出電圧をスレーブ側のスイッチング素子1Bのコントローラ2Bで比較し、スレーブ側のスイッチング素子1Bのゲート信号をマスター側のスイッチング素子1Aにかかる電圧と等しくなるようにコントロールする。このコントロールは、スレーブ側のスイッチング素子1Bの電圧が高ければ、そのゲート電圧を上昇させる制御を行い、低ければそのゲート電圧を下降させる制御を行う。

【0016】

図12に示す電圧検出回路は、(a)ではVce1+Vce2との分圧値とVce1の分圧値を検出してVce1とVce2との電圧偏差を求め、(b)ではVce1と絶縁トランスを介して出力されたVce2の分圧値を検出し,Vce1とVce2との電圧偏差を求めている。

【0017】

以上に説明したマスタースレーブ方式による過電圧抑制方式は、スレーブ側のスイッチング素子のゲート電圧を補正して電圧アンバランスが無くなるように制御することで,過電圧でのスイッチング素子の破壊を防止できる。また、アクティブゲートコントロールと異なり、クランプ回路を備えていないため、クランプ回路での損失発生が生じないことや、クランプが行なわれるスイッチング素子への損失発生に起因する素子損失(発熱)の偏りが抑制できる。

【先行技術文献】

【非特許文献】

【0018】

【非特許文献1】標題「Review of series and parallel connection of IGBTs」、著者 Shammas N.Y.A.,Withanage R.,Chamund D、出典IEE Proceedings Circuits, Devices and Systems,Vol.153,No.1,Feb 2006, Page(s):34−39

【非特許文献2】標題「Control of the switching transients of IGBT series strings by high−performance drive unit、著者 Raciti A.,Belverde G.;Galluzzo,A.;Greco,G.;Melito,M.;Musumeci,S、出典 IEEE Transactions on Industrial Electronics,Vol.48,No.3,June 2001, Page(s): 482−490

【非特許文献3】標題「スナバレスIGBT直列接続に適したアクティブゲートコントロール」、著者 加藤 修治,上田 茂太,酒井 洋満,相澤 英俊、出典 電気学会論文誌DVol.122 No.8 PP816−822

【非特許文献4】標題「Development of a multiple series−connected IGBT converter for large−capacity STATCOM」、著者 H.Kon, M.Tobita, H. Suzuki, J.Kanno, N.Nishizawa, T.Murao, S.Irokawa、出典 The 2010 International Power Electronics Conference, Page(s):2024−2028

【発明の概要】

【発明が解決しようとする課題】

【0019】

(1)スイッチング素子はそのスイッチ状態を変化させる際、能動領域で動作することになるためスイッチング損失が発生する。従来のアクティブゲートコントロールによる電圧バランス方式は、過電圧発生時に電圧をクランプするようにゲートを制御することになり、クランプ中も能動領域で動作して損失が増加する。さらに、クランプ中は、ツェナーダイオード3と抵抗4との直列回路や分圧したクランプ抵抗に高電圧かつ大電流が流れ続けることや、素子の電圧が上がった状態で電流が流れ続けるため、クランプした側のスイッチング素子とそのクランプ回路には大きな損失が発生する。

【0020】

さらに、損失の増加はクランプ動作を行った素子だけになるので、複数の直列接続素子間で損失の偏り(アンバランス)が発生する。

【0021】

一方、 マスタースレーブ方式による過電圧抑制(電圧バランス)方式では、提案されている回路は素子3個以上の直列に対応していない。また、図12の(a)の電圧検出回路では、スイッチング素子1Aと1Bのエミッタ−コレクタ間に並列接続している抵抗が、漏れ電流が流れる程度の抵抗値であった場合に抵抗値が異なることで両素子の遮断時に1Aと1Bに漏れ電流の差が発生し、電圧のアンバランスが発生する原因となるため、その漏れ電流の差で新たに生じる電圧アンバランスに対する対処ができない。また、図12の(b)の回路は検出電圧信号間の絶縁にトランスを用いているため、応答性に問題がある。

【0022】

本発明の目的は、スイッチング過渡時のスイッチング損失と偏りを低減でき、オン・オフ定常時の電圧アンバランス抑制を容易にし、電圧バランス制御の応答性に優れ、多数のスイッチング素子の直列接続回路に対応できる電圧バランス回路を提供することにある。

【課題を解決するための手段】

【0023】

前記の課題を解決するため、本発明は以下の構成を特徴とする。

【0024】

(1)複数直列接続の半導体スイッチング素子をオン・オフ同期制御する半導体スイッチ回路において、各スイッチング素子の負担電圧をアクティブバランスさせる電圧バランス回路であって、

マスター側およびスレーブ側の各スイッチング素子のエミッタ−コレクタ間に、それぞれ同等抵抗値で同等分圧比の分圧抵抗を並列接続し、マスター側のスイッチング素子とスレーブ側のスイッチング素子の直列接続点を中点Nとして両スイッチング素子のエミッタ−コレクタ間電圧に比例した電圧を負担電圧としてそれぞれ検出する抵抗分圧回路と、

前記各検出電圧の電圧偏差がゼロ(零)になるよう、スレーブ側のスイッチング素子のゲート電流を補正して各スイッチング素子の負担電圧をバランスさせる電圧バランス制御回路を備えたことを特徴とする。

【0025】

(2)前記電圧バランス制御回路は、各スイッチング素子が共にターンオフを開始した過渡時に、それらのエミッタ−コレクタ間電圧の偏差電圧の正負に応じて1つのスイッチング素子のターンオフ開始を遅くして各スイッチング素子のターンオフタイミングを同期させることを特徴とする。

【0026】

(3)前記抵抗分圧回路は、前記中点Nから見て高い電位側になる抵抗R11の抵抗値=抵抗R22の抵抗値、低い電位側になる抵抗R12の抵抗値=抵抗R21の抵抗値に設定し、抵抗R11、R22の抵抗値を抵抗R12、R21の抵抗値より大きく設定して抵抗R12、R21のそれぞれ両端に低レベルの検出電圧を得る構成としたことを特徴とする。

【0027】

(4)前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に一対のスイッチング素子間のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を各々補正し、各スイッチング素子の負担電圧をバランスさせることを特徴とする。

【0028】

(5)前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、中間部位のマスター側のスイッチング素子を中心にして両側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を各々補正し、各スイッチング素子の負担電圧をバランスさせることを特徴とする。

【0029】

(6)前記抵抗分圧回路は、2個の直列接続スイッチング素子S1,S2のうち、マスター側とするスイッチング素子S1とこれに直列接続されるスレーブ側のスイッチング素子S2のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とし両スイッチング素子のエミッタ−コレクタ間電圧を比較して接続される該マスター側のゲート電流を補正し、両スイッチング素子の負担電圧をバランスさせることを特徴とする。

【0030】

(7)前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とするスイッチング素子とこれに直列接続されるスイッチング素子をスレーブ側としてそのゲート電流を補正という制御を繰り返し、各スイッチング素子の負担電圧をバランスさせることを特徴とする。

【0031】

(8)前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、マスター側とスレーブ側の検出電圧の和を素子数で割った各スイッチング素子のエミッタ−コレクタ間電圧の平均値から、各スイッチング素子のエミッタ−コレクタ間の電圧を差し引いた電圧偏差を求め、その電圧偏差に基づき各スイッチング素子のゲート電流を補正することで互いのスイッチング素子のエミッタ−コレクタ間の電圧を補正し合い、各スイッチング素子の負担電圧をバランスさせることを特徴とする。

【発明の効果】

【0032】

以上のとおり、本発明によれば、以下の効果がある。

【0033】

(1)スイッチング損失の低減、スイッチング損失の偏りの低減

スイッチング素子はそのスイッチ状態を変化させる際、能動領域で動作することになるためスイッチング損失が発生する。過電圧発生時に電圧をクランプするようにゲートを制御する方式では、クランプ中も能動領域で動作することになるため、損失が増加する。さらに損失の増加はクランプ動作を行った素子だけになるので、複数の直列接続素子間で損失のアンバランスが発生する。

【0034】

本発明で提案する電圧バランス回路では、スイッチング素子のターンオフタイミング自体が同期するため、理想的な状況下(電位差のフィードバックゲインが高く、完全に複数スイッチのスイッチング動作が同期した場合)では通常のスイッチング損失のみとなり、スイッチング損失の増加を抑制でき、また偏りも抑制できる。

【0035】

(2)定常時の電圧アンバランス抑制が容易

非特許文献2の電圧検出回路(図12参照)では、スイッチ1A、1Bが定常的にオフの時、その半導体スイッチの電流遮断時の抵抗値のばらつきにより、電圧のアンバランスが発生するが、それに対する対処ができない。

【0036】

本発明で提案する電圧バランス回路では、複数のスイッチング素子それぞれに並列に同等抵抗値で同等分圧比の分圧抵抗を並列接続する回路構成とすることで、その抵抗値が半導体スイッチのオフ状態時(遮断時)の抵抗値よりもある程度小さければ電圧のアンバランスを抑制できる。

【0037】

(3)2つ以上の直列に対応できる

従来のマスタースレーブ方式では半導体スイッチの直列数は2つまでしか提案されていないが、本発明で提案する電圧バランス回路では、3直列以上の半導体スイッチング素子の電圧バランスができる。

【0038】

(4)スイッチング動作のディレイを減少

従来の電圧検出回路で必要とした絶縁用パルストランスが不要になると共に電圧バランス制御の応答性を高めることができる。

【図面の簡単な説明】

【0039】

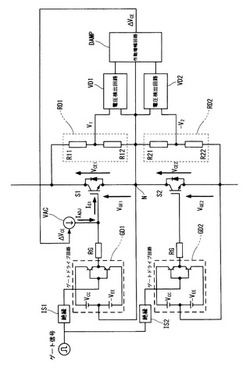

【図1】実施形態1のマスタースレーブ方式の電圧バランス回路図。

【図2】S1のターンオフが早い場合の電圧バランス制御の電圧関係図。

【図3】S1のターンオフが遅い場合の電圧バランス制御の電圧関係図。

【図4】実施形態2の3直列半導体スイッチング素子の抵抗分圧回路図。

【図5】実施形態3の3直列半導体スイッチング素子の抵抗分圧回路図。

【図6】実施形態4の2直列半導体スイッチング素子の抵抗分圧回路図。

【図7】実施形態5の3直列半導体スイッチング素子の抵抗分圧回路図。

【図8】実施形態6の2直列半導体スイッチング素子の抵抗分圧回路図。

【図9】アクティブゲートコントロールによる電圧バランス回路の例。

【図10】電圧フィードバックによる電圧バランス回路の例。

【図11】マスタースレーブ方式の過電圧抑制回路の例。

【図12】抵抗分圧回路による電圧検出回路の例。

【発明を実施するための形態】

【0040】

(実施形態1)

図1は、直列接続した2直列半導体スイッチング素子のスイッチ回路に、マスタースレーブ方式の電圧バランス回路を適用した場合である。

【0041】

図1における半導体スイッチング素子のゲートドライブ回路を説明する。2直列スイッチング素子(IGBT)S1、S2は、ゲートドライブ回路GD1、GD2によってそれぞれのゲート・エミッタ間にゲートドライブ信号が印加される。ゲートドライブ回路GD1、GD2は、それぞれの基準電位がスイッチング素子S1、S2のエミッタとなるよう、互いに独立した直流電圧源VCCおよび−VEEを設け、さらに絶縁回路IS1、IS2を通してゲート信号を取り込む。

【0042】

図1における電圧バランス回路を説明する。抵抗分圧回路RD1は、分圧抵抗R11,R12の直列接続回路をスレーブ側のスイッチング素子S1のエミッタ−コレクタ間に並列接続する。抵抗分圧回路RD2は、分圧抵抗R21,R22の直列接続回路をマスター側のスイッチング素子S2のエミッタ−コレクタ間に並列接続する。これら抵抗分圧回路RD1,RD2は、スイッチング素子S1、S2の直列接続点を中点Nとしてスイッチング素子S1、S2のエミッタ−コレクタ間電圧VCE1、VCE2に比例した電圧を負担電圧V1、−V2としてそれぞれ検出する。

【0043】

電圧バランス制御回路は、検出された両負担電圧の中点Nを基準電位として適当な電圧レベルに調整する電圧検出回路VD1、VD2と、両電圧検出回路VD1、VD2で検出する両負担電圧の電圧偏差ΔVCEを求める差動増幅回路DAMPと、電圧偏差ΔVCEに応じた値でかつ電圧偏差ΔVCEが零になる極性の電流IADJに変換し、この電流IADJをスレーブ側のスイッチング素子S1のゲート電流IG1として注入する電圧/電流変換回路VACを備える。

【0044】

上記の抵抗分圧回路と電圧バランス制御回路で構成する電圧バランス回路は、図2や図3に電圧関係図を示すように、電圧偏差ΔVCEが零になるよう、スレーブ側のスイッチング素子S1の電圧が高ければ、そのゲート電圧を上昇させ、低ければそのゲート電圧を下降させ、スイッチング素子S1、S2の負担電圧VCE1,VCE2をバランスさせることができる。

【0045】

以上の電圧バランス回路の特徴的な構成および作用効果を説明する。

【0046】

(a)抵抗分圧回路RD1、RD2は、スイッチング素子S1、S2のエミッタ−コレクタ間電圧を分圧用抵抗R11、R12、R21、R22を使って検出する。このとき、抵抗R11=R22、R12=R21とし、スイッチング素子S1、S2それぞれに並列に同等抵抗値で同等分圧比の分圧抵抗を接続する回路構成とし、その分圧抵抗値が半導体スイッチのオフ状態時(遮断時)の抵抗値よりもある程度小さければ電圧アンバランスを抑制できる。

【0047】

また、中点Nから見て高い電位側になる抵抗R11の抵抗値=抵抗R22の抵抗値、低い電位側になる抵抗R12の抵抗値=抵抗R21の抵抗値に設定し、抵抗R11、R22の抵抗値を抵抗R12、R21の抵抗値より大きく設定することで、抵抗R12、R21のそれぞれ両端に低レベルの検出電圧を得る。これにより、電圧検出回路VD1、VD2は、スイッチング素子S1のエミッタ(S2のコレクタ)を基準電位(中点N)に対してスイッチング素子S1、S2の電圧(分圧されて絶対値を小さくした電圧)を使って電圧を検出できる。

【0048】

差動増幅回路DAMPは電圧検出回路VD1、VD2それぞれの検出電圧を加算してその電圧偏差ΔVCEを求め、電圧/電流変換回路VACは電圧偏差ΔVCEの大きさに応じた値でかつ電圧偏差ΔVCEが零になる極性の電流に変換してスイッチング素子S1のゲートに電流を注入する。

【0049】

したがって、スイッチング素子S1、S2の直列接続点(中点N)を基準として低レベル電圧でスイッチング素子S1、S2両方の電圧を検出することができ、しかも電圧検出に絶縁手段を介挿することなく、電圧検出回路VD1、VD2、差動増幅回路DAMP、電圧/電流変換回路VACなどの制御電源の実現にはスイッチング素子S1、S2の直列接続点(中点N)を基準電位として構成できる。このため、従来の電圧検出回路で必要とした絶縁用パルストランスが不要になると共に電圧バランス制御の応答性を高めることができる。

【0050】

(b)スイッチング素子S1、S2が共にオンまたはオフ状態の定常時には、抵抗分圧回路RD1、RD2により検出する負担電圧は、スイッチング素子S1、S2のエミッタ−コレクタ間電圧VCE1、VCE2に比例した電圧(=0または電源電圧VDC/2)を負担電圧としてそれぞれ検出するため、両者の電圧偏差ΔVCEはゼロ(零)になる。そのため、スイッチング素子S1のゲートへの電流注入(吸収)が発生することなく、電圧のアンバランスも発生しない。

【0051】

(c)スイッチング過渡時(オン→オフ)には、両スイッチング素子S1、S2のターンオフタイミングのずれなどによって電圧バランス回路の差動増幅回路DAMPには電圧偏差ΔVCEが発生する。

【0052】

このうち、スイッチング素子S1がS2より早くターンオフを開始した場合、差動増幅回路DAMPには正の電圧偏差ΔVCEに基づいて、注入電流IADJに正の電流を発生することで、スイッチング素子S1のターンオフ開始を遅くさせる。これにより、スイッチング素子S1のターンオフはスイッチング素子S2のターンオフに同期させる。すなわちスイッチングオフタイミングのずれを抑制することができる(図2参照)。

【0053】

また、スイッチング素子S2がS1より早くターンオフを開始した場合、負の電圧偏差ΔVCEが発生し、それに伴って負の注入電流IADJが流れることで、スイッチング素子S1のターンオフ開始を早める。これにより、スイッチング素子S2のターンオフはスイッチング素子S1のターンオフに同期させる。すなわちスイッチングオフタイミングのずれを抑制することができる(図3参照)。

【0054】

これら事項により、能動領域になるスイッチングのタイミング自体を同期させることができ、理想的な状況下(電位差のフィードバックゲインが高く、完全に複数スイッチのスイッチング動作が同期した場合)では通常のスイッチング損失のみとなり、スイッチング損失の増加を抑制でき、またスイッチング損失の偏りも抑制できる。

【0055】

(実施形態2)

図4は、本実施形態2による抵抗分圧回路を示す。この抵抗分圧回路による電圧バランス制御は、スイッチング素子の3以上の直列接続の場合で、スイッチング素子S3をマスターにV2とV3との電圧比較から求められる電圧偏差ΔVからスイッチング素子S2のゲート電流を制御し,スイッチング素子S2をマスターにV1とV2との電圧比較から求められる電圧偏差ΔVからスイッチング素子S1のゲート電流を制御し、各スイッチング素子S1、S2、S3の負担電圧をバランスさせる。同様に、4素子以上の場合も順々に一対のスイッチング素子間のエミッタ−コレクタ間電圧を比較し、スレーブ側のゲート電流を各々補正することで、3素子や4素子,…,n素子直列接続の場合にも対応する。なお、補正の順番は、低圧側からでも高圧側からでもどちらでも良い。以下は3素子の例を説明する。

【0056】

図4に示す3直列スイッチング素子の負担電圧を検出するための各抵抗値の設定は、以下の関係とするが、これらはあくまで設定例であり、このほかの抵抗分圧でも良い。

【0057】

R11+R12=R21+R22+R23=R31+R32

R11:R12=(R22+R23):R21

(R21+R22):R23=R31:R32

これら抵抗値の関係とすることで、抵抗R12とR21の電圧を比較してスイッチング素子S1のゲートを制御し、スイッチング素子S1とS2のスイッチングを同期させる。また、抵抗R23とR31の電圧を比較してスイッチング素子S2のゲートを制御し、スイッチング素子S2とS3のスイッチングを同期させる。スイッチング素子S2とS3が同期し、スイッチング素子S1とS2が同期すれば、スイッチング素子S1、S2、S3全てが同期する。

【0058】

(実施形態3)

図5は、本実施形態3による抵抗分圧回路を示す。実施形態2では、直列接続半導体スイッチ素子の下からまたは上から順に電圧偏差を補正する例を示したが、本実施形態3では中間部位のマスター側のスイッチング素子S2を中心にして、検出電圧V1とV2を比較した電圧偏差でスイッチング素子S1を補正し、次いで検出電圧V23とV3を比較し、この電圧偏差でスイッチング素子S3を補正する。スイッチング素子S2を中心に両側にスイッチング素子を増やしていくことで、直列接続する素子数を増やしていくことができる。図5における各抵抗の抵抗値は、以下の関係とする。

【0059】

R11+R12=R21+R22=R31+R32

R11:R12=R22:R21

R31:R32とR1:R2の比率は任意であるが、電圧V3とV23を使った演算によってVce2とVce3の偏差が比較できる抵抗値に設定する。

【0060】

R1+R2<<(R21+R22+R31+R32)ならば、スイッチング素子S1のエミッタ−コレクタ間に設けた抵抗R3は不要とし、そうでなければ(R11+R12):(R21+R22+R31+R32)=R3:(R1+R2)に設定すると良い。

【0061】

これら抵抗値の関係とすることで、抵抗R12とR21の電圧を比較してスイッチング素子S1のゲートを制御し、スイッチング素子S1をS2のスイッチングと同期させる。また、抵抗R32とR2の電圧を比較してスイッチング素子S3のゲートを制御し、スイッチング素子S3をS2のスイッチングと同期させる。

【0062】

実施形態2の抵抗分圧回路では、スイッチング素子S1が基準のスイッチング素子S3と同期するために、スイッチング素子S2とS3の同期を介していたが、本実施形態では同期動作を行う素子がそれぞれ直列基準と比較する形になっている点で異なり、同期の問題はない。

【0063】

(実施形態4)

図6は、(a)に本実施形態4による抵抗分圧回路を示す。本実施形態4では、両素子ともにマスター、スレーブになり、互いにゲート電流を補正しあう。この補正は、図6の(b)に矢印で示すように、お互いが近づくように補正する。

【0064】

図6においては、マスター側とするスイッチング素子S1の抵抗R12の電圧V1と、これに直列接続されるスレーブ側のスイッチング素子S2の抵抗R21の電圧−V2を比較してスイッチング素子S1のゲートを制御し、スイッチング素子S1をS2のスイッチングと同期させる。抵抗R23とR2の電圧V2,V12を比較してスイッチング素子S2のゲートを制御し、スイッチング素子S2をS1のスイッチングと同期させる。

【0065】

本実施形態では、電圧バランス制御による負担電圧がそれぞれ互いに近づく方向へ動作するため、同期する力が強まりスイッチング素子S1とスイッチング素子S2との電圧が等しくなるための制御により応答性が向上する。また、必ずスイッチングタイミングに同期するようになるため、ゲート信号の変化→スイッチング素子が変化する間の遅延がばらつかないようになる。

【0066】

なお、遅い方のスイッチング素子の電流偏差のゲインを高める制御を行っても実施形態4と同様に、スイッチング素子が変化する間の遅延がばらつかないようになる。

【0067】

(実施形態5)

図7は、本実施形態5による抵抗分圧回路を示す。本実施形態5では、実施形態4において、3つの半導体スイッチング素子の多直列とした例を示すもので、スイッチング素子S2とS3は実施形態4と同様に互いに補正しあう制御を行い、スイッチング素子S1はS2をマスターにしてスイッチング素子S2の電圧に合わせるようにスイッチング素子S1のゲート電流を制御する。

【0068】

図7においては、抵抗R12とR21の電圧を比較してスイッチング素子S1のゲートを制御し、スイッチング素子S1をS2のスイッチングと同期させる。抵抗R23とR31の電圧を比較してスイッチング素子S2のゲートを制御し、スイッチング素子S2をS3のスイッチングと同期させる。抵抗R32とR2の電圧を比較してスイッチング素子S3のゲートを制御し、スイッチング素子S3をS2のスイッチングと同期させる。

【0069】

なお、n個の直列接続スイッチング素子S1,S2,S3,…,Snの電圧バランスには、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を比較し、この電圧偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とするスイッチング素子とこれに直列接続されるスイッチング素子をスレーブ側としてそのゲート電流を補正するという制御を繰り返し、各スイッチング素子の負担電圧をバランスさせる

(実施形態6)

図8は、本実施形態6による抵抗分圧回路を示す。本実施形態6では、実施形態4の変形で、実施形態4では互いに電圧を補正し合う方式であったが、本実施形態6ではそれぞれのスイッチング素子の電圧和を素子数で割った各素子のエミッタ−コレクタ間電圧の平均値から、各素子のエミッタ−コレクタ間の電圧を差し引いた電圧偏差を求め、その電圧偏差に基づきゲート電流を補正することで互いのスイッチング素子のエミッタ−コレクタ間の電圧を補正し合う。すなわち、平均値から電圧偏差を求めているところが、実施形態4と相違する。

【0070】

図8においては、抵抗R12とR21の電圧和を直列接続数の2で割って[(V1+V2)/2]、この除算値と抵抗R12の電圧値[V1]を比較して求められた電圧偏差ΔV1でスイッチング素子S1のゲートを制御する。抵抗R23にかかる電圧を直列接続数の2で割って[V23/2]、この除算値と抵抗R22にかかる電圧値[V1]を比較して求められた電圧偏差ΔV2でスイッチング素子S2のゲートを制御する。図8における各抵抗の抵抗値は、以下の関係とする。

【0071】

R11+R12=R21+R22=R1=R2

R11:R12=R22:R21

本実施形態は、互いにエミッタ−コレクタ間電圧VCE1とVCE2の電圧平均値からそれぞれの素子にかかる電圧値を差し引いた電圧偏差を用いることで、互いに補正しあうが平均値に向けて補正し合うために制御上の干渉が起こり辛くなる利点がある。

【符号の説明】

【0072】

1,1A,1B,S1,S2,S3 半導体スイッチング素子

2A,2B コントローラ

IS1、IS2 絶縁回路

GD1,GD2 ゲートドライブ回路

RD1、RD2 抵抗分圧回路

VD1、VD2 電圧検出回路

DAMP 差動増幅回路

VAC 電圧/電流変換回路

【技術分野】

【0001】

本発明は、複数直列接続の半導体スイッチング素子(IGBT等)をオン・オフ同期制御する半導体スイッチ回路において、各スイッチング素子の負担電圧をアクティブ(能動的に)バランスさせる電圧バランス回路に関する。

【背景技術】

【0002】

(1)半導体スイッチング素子の複数直列接続について

半導体スイッチング素子を複数直列に接続し、それらを1つの素子としてスイッチングをオン・オフ同期することで、低耐電圧のスイッチング素子で高耐電圧特性を得るスイッチング回路を実現するができる。

【0003】

しかも、低耐圧素子は、高耐圧素子に比べて顕著に価格が安いため、低コストで高耐圧の装置が構成できる。例えば、現状、最高で6500V、600Aの耐圧・定格電流をもつIGBTがリリースされているが、それ以上の耐圧を持つ素子が必要な場合にIGBTを直列接続する(例えば、非特許文献4参照)。

【0004】

また、高耐圧素子は大きな電流容量を持つものがないが、低耐圧素子には大容量のものが存在するため、低耐圧素子を複数直列接続することで、高耐圧・大電流のスイッチング素子およびこれを使用した装置を構成できる。この場合、電流容量を高めるために、低耐圧素子を複数並列接続する必要はない。

【0005】

また、低耐圧素子は、高耐圧素子に比べてスイッチング速度が速く、顕著にスイッチング損失が小さい傾向にある。このため、高耐圧素子に比べて、低耐圧素子を複数直列に接続した方が、スイッチング周波数が高い場合の損失(導通損失+スイッチング損失)が小さくなることがある。

【0006】

(2)半導体スイッチング素子の複数直列接続時の問題点

複数の直列接続した半導体スイッチング素子それぞれに均等に電圧が加わらないこと(電圧アンバランスの発生)がある。この電圧アンバランスの発生は、素子耐圧を超える電圧がスイッチング素子に加わって素子が破壊されたり、スイッチング時の発生損失に大きな偏りが発生することで、スイッチング素子の発熱や寿命に大きな影響を与えたりする可能性がある。

【0007】

電圧アンバランスの原因には、(a)スイッチングタイミングのばらつきによる電圧アンバランス、(b)定常的な電流遮断時(スイッチング素子のターンオフ時)における漏れ電流のばらつきによる電圧アンバランス、(c)スイッチング素子のターンオフ動作時のテール電流のばらつきによる電圧アンバランスなどがある。

【0008】

このうち、(a)スイッチングタイミングのばらつきによる電圧アンバランスが発生する原因としては、ゲート制御信号の伝達時間のばらつき、ゲートドライバの特性のばらつき、スイッチング素子の入力容量・閾値電圧などの特性のばらつきなどがある。

【0009】

上記のようなスイッチング動作の過渡時に発生する電圧アンバランスに起因する過電圧を解消する方式の従来技術として、以下の方式がある。

【0010】

(A)アクティブゲートコントロールによる過電圧抑制

(A1)ツェナーダイオードを用いる方式(非特許文献3)

図9は、ツェナーダイオードによるクランプによって電圧バランスさせる回路の例を示し、直列接続回路の1つのスイッチング素子をツェナーダイオードにより電圧クランプする場合である。IGBTのスイッチング素子1のオン・オフをゲートドライブ回路2のゲートドライブ出力で制御する構成において、スイッチング素子1のコレクタ−ゲート間の電圧をクランプするツェナーダイオード3をその電流制限抵抗4との直列接続で設ける。

【0011】

この構成において、ツェナーダイオード3のツェナー電圧はスイッチング素子1の閾値電圧に予め設定しておき、直列接続された複数のスイッチング素子をターンオフさせたとき、スイッチング素子1が速くターンオフした場合にはその負担電圧が大きくなる。この大きい負担電圧が閾値電圧以上になると、ツェナーダイオード3がオンし、スイッチング素子1のコレクタからゲートに電流が注入され、スイッチング素子1のゲート電圧を上昇させ、これによりスイッチング素子1の遮断電流が弱まり、スイッチング素子1のエミッタ−コレクタ間にかかる負担電圧が減少する。このような動作によりスイッチング素子1の負担電圧が閾値電圧付近にクランプされる。

【0012】

(A2)電圧を検出しフィードバックする方式(非特許文献1、非特許文献4)

図10は、電圧フィードバックによる電圧バランス回路の例を示す。同図は、基本的にはツェナーダイオードによる電圧バランス方式と同じもので、スイッチング素子1のエミッタ−コレクタ間電圧(負担電圧)VCEを抵抗分圧回路で分圧し、電圧制御素子により電圧VCEと閾値電圧VREFの差ΔVに応じたゲート電流IGAをゲート電流IGにフィードバックで注入する。

【0013】

以上に説明したアクティブゲートコントロール方式で過電圧抑制を行った結果、電圧アンバランスが小さくなるようにゲート信号を制御できるので、スイッチング素子には耐圧以上の電圧が掛からず、過電圧でのスイッチング素子の破壊を防止できる。

【0014】

また、閾値を分圧値近くに設定すればクランプによって電圧のアンバランスが減少する。例えば、直列回路の両端電圧が1000Vの時に,クランプする電圧閾値を500Vに近くすることで電圧のアンバランスを少なくすることができる。

【0015】

(B)マスタースレーブ方式による過電圧抑制(非特許文献2)

図11は、マスタースレーブ方式の過電圧抑制回路の例を示す。同図は、直列接続の2直列スイッチング素子1A、1Bにかかっている電圧を抵抗分圧回路5A、5Bでそれぞれ検出し、この検出電圧をスレーブ側のスイッチング素子1Bのコントローラ2Bで比較し、スレーブ側のスイッチング素子1Bのゲート信号をマスター側のスイッチング素子1Aにかかる電圧と等しくなるようにコントロールする。このコントロールは、スレーブ側のスイッチング素子1Bの電圧が高ければ、そのゲート電圧を上昇させる制御を行い、低ければそのゲート電圧を下降させる制御を行う。

【0016】

図12に示す電圧検出回路は、(a)ではVce1+Vce2との分圧値とVce1の分圧値を検出してVce1とVce2との電圧偏差を求め、(b)ではVce1と絶縁トランスを介して出力されたVce2の分圧値を検出し,Vce1とVce2との電圧偏差を求めている。

【0017】

以上に説明したマスタースレーブ方式による過電圧抑制方式は、スレーブ側のスイッチング素子のゲート電圧を補正して電圧アンバランスが無くなるように制御することで,過電圧でのスイッチング素子の破壊を防止できる。また、アクティブゲートコントロールと異なり、クランプ回路を備えていないため、クランプ回路での損失発生が生じないことや、クランプが行なわれるスイッチング素子への損失発生に起因する素子損失(発熱)の偏りが抑制できる。

【先行技術文献】

【非特許文献】

【0018】

【非特許文献1】標題「Review of series and parallel connection of IGBTs」、著者 Shammas N.Y.A.,Withanage R.,Chamund D、出典IEE Proceedings Circuits, Devices and Systems,Vol.153,No.1,Feb 2006, Page(s):34−39

【非特許文献2】標題「Control of the switching transients of IGBT series strings by high−performance drive unit、著者 Raciti A.,Belverde G.;Galluzzo,A.;Greco,G.;Melito,M.;Musumeci,S、出典 IEEE Transactions on Industrial Electronics,Vol.48,No.3,June 2001, Page(s): 482−490

【非特許文献3】標題「スナバレスIGBT直列接続に適したアクティブゲートコントロール」、著者 加藤 修治,上田 茂太,酒井 洋満,相澤 英俊、出典 電気学会論文誌DVol.122 No.8 PP816−822

【非特許文献4】標題「Development of a multiple series−connected IGBT converter for large−capacity STATCOM」、著者 H.Kon, M.Tobita, H. Suzuki, J.Kanno, N.Nishizawa, T.Murao, S.Irokawa、出典 The 2010 International Power Electronics Conference, Page(s):2024−2028

【発明の概要】

【発明が解決しようとする課題】

【0019】

(1)スイッチング素子はそのスイッチ状態を変化させる際、能動領域で動作することになるためスイッチング損失が発生する。従来のアクティブゲートコントロールによる電圧バランス方式は、過電圧発生時に電圧をクランプするようにゲートを制御することになり、クランプ中も能動領域で動作して損失が増加する。さらに、クランプ中は、ツェナーダイオード3と抵抗4との直列回路や分圧したクランプ抵抗に高電圧かつ大電流が流れ続けることや、素子の電圧が上がった状態で電流が流れ続けるため、クランプした側のスイッチング素子とそのクランプ回路には大きな損失が発生する。

【0020】

さらに、損失の増加はクランプ動作を行った素子だけになるので、複数の直列接続素子間で損失の偏り(アンバランス)が発生する。

【0021】

一方、 マスタースレーブ方式による過電圧抑制(電圧バランス)方式では、提案されている回路は素子3個以上の直列に対応していない。また、図12の(a)の電圧検出回路では、スイッチング素子1Aと1Bのエミッタ−コレクタ間に並列接続している抵抗が、漏れ電流が流れる程度の抵抗値であった場合に抵抗値が異なることで両素子の遮断時に1Aと1Bに漏れ電流の差が発生し、電圧のアンバランスが発生する原因となるため、その漏れ電流の差で新たに生じる電圧アンバランスに対する対処ができない。また、図12の(b)の回路は検出電圧信号間の絶縁にトランスを用いているため、応答性に問題がある。

【0022】

本発明の目的は、スイッチング過渡時のスイッチング損失と偏りを低減でき、オン・オフ定常時の電圧アンバランス抑制を容易にし、電圧バランス制御の応答性に優れ、多数のスイッチング素子の直列接続回路に対応できる電圧バランス回路を提供することにある。

【課題を解決するための手段】

【0023】

前記の課題を解決するため、本発明は以下の構成を特徴とする。

【0024】

(1)複数直列接続の半導体スイッチング素子をオン・オフ同期制御する半導体スイッチ回路において、各スイッチング素子の負担電圧をアクティブバランスさせる電圧バランス回路であって、

マスター側およびスレーブ側の各スイッチング素子のエミッタ−コレクタ間に、それぞれ同等抵抗値で同等分圧比の分圧抵抗を並列接続し、マスター側のスイッチング素子とスレーブ側のスイッチング素子の直列接続点を中点Nとして両スイッチング素子のエミッタ−コレクタ間電圧に比例した電圧を負担電圧としてそれぞれ検出する抵抗分圧回路と、

前記各検出電圧の電圧偏差がゼロ(零)になるよう、スレーブ側のスイッチング素子のゲート電流を補正して各スイッチング素子の負担電圧をバランスさせる電圧バランス制御回路を備えたことを特徴とする。

【0025】

(2)前記電圧バランス制御回路は、各スイッチング素子が共にターンオフを開始した過渡時に、それらのエミッタ−コレクタ間電圧の偏差電圧の正負に応じて1つのスイッチング素子のターンオフ開始を遅くして各スイッチング素子のターンオフタイミングを同期させることを特徴とする。

【0026】

(3)前記抵抗分圧回路は、前記中点Nから見て高い電位側になる抵抗R11の抵抗値=抵抗R22の抵抗値、低い電位側になる抵抗R12の抵抗値=抵抗R21の抵抗値に設定し、抵抗R11、R22の抵抗値を抵抗R12、R21の抵抗値より大きく設定して抵抗R12、R21のそれぞれ両端に低レベルの検出電圧を得る構成としたことを特徴とする。

【0027】

(4)前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に一対のスイッチング素子間のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を各々補正し、各スイッチング素子の負担電圧をバランスさせることを特徴とする。

【0028】

(5)前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、中間部位のマスター側のスイッチング素子を中心にして両側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を各々補正し、各スイッチング素子の負担電圧をバランスさせることを特徴とする。

【0029】

(6)前記抵抗分圧回路は、2個の直列接続スイッチング素子S1,S2のうち、マスター側とするスイッチング素子S1とこれに直列接続されるスレーブ側のスイッチング素子S2のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とし両スイッチング素子のエミッタ−コレクタ間電圧を比較して接続される該マスター側のゲート電流を補正し、両スイッチング素子の負担電圧をバランスさせることを特徴とする。

【0030】

(7)前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とするスイッチング素子とこれに直列接続されるスイッチング素子をスレーブ側としてそのゲート電流を補正という制御を繰り返し、各スイッチング素子の負担電圧をバランスさせることを特徴とする。

【0031】

(8)前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、マスター側とスレーブ側の検出電圧の和を素子数で割った各スイッチング素子のエミッタ−コレクタ間電圧の平均値から、各スイッチング素子のエミッタ−コレクタ間の電圧を差し引いた電圧偏差を求め、その電圧偏差に基づき各スイッチング素子のゲート電流を補正することで互いのスイッチング素子のエミッタ−コレクタ間の電圧を補正し合い、各スイッチング素子の負担電圧をバランスさせることを特徴とする。

【発明の効果】

【0032】

以上のとおり、本発明によれば、以下の効果がある。

【0033】

(1)スイッチング損失の低減、スイッチング損失の偏りの低減

スイッチング素子はそのスイッチ状態を変化させる際、能動領域で動作することになるためスイッチング損失が発生する。過電圧発生時に電圧をクランプするようにゲートを制御する方式では、クランプ中も能動領域で動作することになるため、損失が増加する。さらに損失の増加はクランプ動作を行った素子だけになるので、複数の直列接続素子間で損失のアンバランスが発生する。

【0034】

本発明で提案する電圧バランス回路では、スイッチング素子のターンオフタイミング自体が同期するため、理想的な状況下(電位差のフィードバックゲインが高く、完全に複数スイッチのスイッチング動作が同期した場合)では通常のスイッチング損失のみとなり、スイッチング損失の増加を抑制でき、また偏りも抑制できる。

【0035】

(2)定常時の電圧アンバランス抑制が容易

非特許文献2の電圧検出回路(図12参照)では、スイッチ1A、1Bが定常的にオフの時、その半導体スイッチの電流遮断時の抵抗値のばらつきにより、電圧のアンバランスが発生するが、それに対する対処ができない。

【0036】

本発明で提案する電圧バランス回路では、複数のスイッチング素子それぞれに並列に同等抵抗値で同等分圧比の分圧抵抗を並列接続する回路構成とすることで、その抵抗値が半導体スイッチのオフ状態時(遮断時)の抵抗値よりもある程度小さければ電圧のアンバランスを抑制できる。

【0037】

(3)2つ以上の直列に対応できる

従来のマスタースレーブ方式では半導体スイッチの直列数は2つまでしか提案されていないが、本発明で提案する電圧バランス回路では、3直列以上の半導体スイッチング素子の電圧バランスができる。

【0038】

(4)スイッチング動作のディレイを減少

従来の電圧検出回路で必要とした絶縁用パルストランスが不要になると共に電圧バランス制御の応答性を高めることができる。

【図面の簡単な説明】

【0039】

【図1】実施形態1のマスタースレーブ方式の電圧バランス回路図。

【図2】S1のターンオフが早い場合の電圧バランス制御の電圧関係図。

【図3】S1のターンオフが遅い場合の電圧バランス制御の電圧関係図。

【図4】実施形態2の3直列半導体スイッチング素子の抵抗分圧回路図。

【図5】実施形態3の3直列半導体スイッチング素子の抵抗分圧回路図。

【図6】実施形態4の2直列半導体スイッチング素子の抵抗分圧回路図。

【図7】実施形態5の3直列半導体スイッチング素子の抵抗分圧回路図。

【図8】実施形態6の2直列半導体スイッチング素子の抵抗分圧回路図。

【図9】アクティブゲートコントロールによる電圧バランス回路の例。

【図10】電圧フィードバックによる電圧バランス回路の例。

【図11】マスタースレーブ方式の過電圧抑制回路の例。

【図12】抵抗分圧回路による電圧検出回路の例。

【発明を実施するための形態】

【0040】

(実施形態1)

図1は、直列接続した2直列半導体スイッチング素子のスイッチ回路に、マスタースレーブ方式の電圧バランス回路を適用した場合である。

【0041】

図1における半導体スイッチング素子のゲートドライブ回路を説明する。2直列スイッチング素子(IGBT)S1、S2は、ゲートドライブ回路GD1、GD2によってそれぞれのゲート・エミッタ間にゲートドライブ信号が印加される。ゲートドライブ回路GD1、GD2は、それぞれの基準電位がスイッチング素子S1、S2のエミッタとなるよう、互いに独立した直流電圧源VCCおよび−VEEを設け、さらに絶縁回路IS1、IS2を通してゲート信号を取り込む。

【0042】

図1における電圧バランス回路を説明する。抵抗分圧回路RD1は、分圧抵抗R11,R12の直列接続回路をスレーブ側のスイッチング素子S1のエミッタ−コレクタ間に並列接続する。抵抗分圧回路RD2は、分圧抵抗R21,R22の直列接続回路をマスター側のスイッチング素子S2のエミッタ−コレクタ間に並列接続する。これら抵抗分圧回路RD1,RD2は、スイッチング素子S1、S2の直列接続点を中点Nとしてスイッチング素子S1、S2のエミッタ−コレクタ間電圧VCE1、VCE2に比例した電圧を負担電圧V1、−V2としてそれぞれ検出する。

【0043】

電圧バランス制御回路は、検出された両負担電圧の中点Nを基準電位として適当な電圧レベルに調整する電圧検出回路VD1、VD2と、両電圧検出回路VD1、VD2で検出する両負担電圧の電圧偏差ΔVCEを求める差動増幅回路DAMPと、電圧偏差ΔVCEに応じた値でかつ電圧偏差ΔVCEが零になる極性の電流IADJに変換し、この電流IADJをスレーブ側のスイッチング素子S1のゲート電流IG1として注入する電圧/電流変換回路VACを備える。

【0044】

上記の抵抗分圧回路と電圧バランス制御回路で構成する電圧バランス回路は、図2や図3に電圧関係図を示すように、電圧偏差ΔVCEが零になるよう、スレーブ側のスイッチング素子S1の電圧が高ければ、そのゲート電圧を上昇させ、低ければそのゲート電圧を下降させ、スイッチング素子S1、S2の負担電圧VCE1,VCE2をバランスさせることができる。

【0045】

以上の電圧バランス回路の特徴的な構成および作用効果を説明する。

【0046】

(a)抵抗分圧回路RD1、RD2は、スイッチング素子S1、S2のエミッタ−コレクタ間電圧を分圧用抵抗R11、R12、R21、R22を使って検出する。このとき、抵抗R11=R22、R12=R21とし、スイッチング素子S1、S2それぞれに並列に同等抵抗値で同等分圧比の分圧抵抗を接続する回路構成とし、その分圧抵抗値が半導体スイッチのオフ状態時(遮断時)の抵抗値よりもある程度小さければ電圧アンバランスを抑制できる。

【0047】

また、中点Nから見て高い電位側になる抵抗R11の抵抗値=抵抗R22の抵抗値、低い電位側になる抵抗R12の抵抗値=抵抗R21の抵抗値に設定し、抵抗R11、R22の抵抗値を抵抗R12、R21の抵抗値より大きく設定することで、抵抗R12、R21のそれぞれ両端に低レベルの検出電圧を得る。これにより、電圧検出回路VD1、VD2は、スイッチング素子S1のエミッタ(S2のコレクタ)を基準電位(中点N)に対してスイッチング素子S1、S2の電圧(分圧されて絶対値を小さくした電圧)を使って電圧を検出できる。

【0048】

差動増幅回路DAMPは電圧検出回路VD1、VD2それぞれの検出電圧を加算してその電圧偏差ΔVCEを求め、電圧/電流変換回路VACは電圧偏差ΔVCEの大きさに応じた値でかつ電圧偏差ΔVCEが零になる極性の電流に変換してスイッチング素子S1のゲートに電流を注入する。

【0049】

したがって、スイッチング素子S1、S2の直列接続点(中点N)を基準として低レベル電圧でスイッチング素子S1、S2両方の電圧を検出することができ、しかも電圧検出に絶縁手段を介挿することなく、電圧検出回路VD1、VD2、差動増幅回路DAMP、電圧/電流変換回路VACなどの制御電源の実現にはスイッチング素子S1、S2の直列接続点(中点N)を基準電位として構成できる。このため、従来の電圧検出回路で必要とした絶縁用パルストランスが不要になると共に電圧バランス制御の応答性を高めることができる。

【0050】

(b)スイッチング素子S1、S2が共にオンまたはオフ状態の定常時には、抵抗分圧回路RD1、RD2により検出する負担電圧は、スイッチング素子S1、S2のエミッタ−コレクタ間電圧VCE1、VCE2に比例した電圧(=0または電源電圧VDC/2)を負担電圧としてそれぞれ検出するため、両者の電圧偏差ΔVCEはゼロ(零)になる。そのため、スイッチング素子S1のゲートへの電流注入(吸収)が発生することなく、電圧のアンバランスも発生しない。

【0051】

(c)スイッチング過渡時(オン→オフ)には、両スイッチング素子S1、S2のターンオフタイミングのずれなどによって電圧バランス回路の差動増幅回路DAMPには電圧偏差ΔVCEが発生する。

【0052】

このうち、スイッチング素子S1がS2より早くターンオフを開始した場合、差動増幅回路DAMPには正の電圧偏差ΔVCEに基づいて、注入電流IADJに正の電流を発生することで、スイッチング素子S1のターンオフ開始を遅くさせる。これにより、スイッチング素子S1のターンオフはスイッチング素子S2のターンオフに同期させる。すなわちスイッチングオフタイミングのずれを抑制することができる(図2参照)。

【0053】

また、スイッチング素子S2がS1より早くターンオフを開始した場合、負の電圧偏差ΔVCEが発生し、それに伴って負の注入電流IADJが流れることで、スイッチング素子S1のターンオフ開始を早める。これにより、スイッチング素子S2のターンオフはスイッチング素子S1のターンオフに同期させる。すなわちスイッチングオフタイミングのずれを抑制することができる(図3参照)。

【0054】

これら事項により、能動領域になるスイッチングのタイミング自体を同期させることができ、理想的な状況下(電位差のフィードバックゲインが高く、完全に複数スイッチのスイッチング動作が同期した場合)では通常のスイッチング損失のみとなり、スイッチング損失の増加を抑制でき、またスイッチング損失の偏りも抑制できる。

【0055】

(実施形態2)

図4は、本実施形態2による抵抗分圧回路を示す。この抵抗分圧回路による電圧バランス制御は、スイッチング素子の3以上の直列接続の場合で、スイッチング素子S3をマスターにV2とV3との電圧比較から求められる電圧偏差ΔVからスイッチング素子S2のゲート電流を制御し,スイッチング素子S2をマスターにV1とV2との電圧比較から求められる電圧偏差ΔVからスイッチング素子S1のゲート電流を制御し、各スイッチング素子S1、S2、S3の負担電圧をバランスさせる。同様に、4素子以上の場合も順々に一対のスイッチング素子間のエミッタ−コレクタ間電圧を比較し、スレーブ側のゲート電流を各々補正することで、3素子や4素子,…,n素子直列接続の場合にも対応する。なお、補正の順番は、低圧側からでも高圧側からでもどちらでも良い。以下は3素子の例を説明する。

【0056】

図4に示す3直列スイッチング素子の負担電圧を検出するための各抵抗値の設定は、以下の関係とするが、これらはあくまで設定例であり、このほかの抵抗分圧でも良い。

【0057】

R11+R12=R21+R22+R23=R31+R32

R11:R12=(R22+R23):R21

(R21+R22):R23=R31:R32

これら抵抗値の関係とすることで、抵抗R12とR21の電圧を比較してスイッチング素子S1のゲートを制御し、スイッチング素子S1とS2のスイッチングを同期させる。また、抵抗R23とR31の電圧を比較してスイッチング素子S2のゲートを制御し、スイッチング素子S2とS3のスイッチングを同期させる。スイッチング素子S2とS3が同期し、スイッチング素子S1とS2が同期すれば、スイッチング素子S1、S2、S3全てが同期する。

【0058】

(実施形態3)

図5は、本実施形態3による抵抗分圧回路を示す。実施形態2では、直列接続半導体スイッチ素子の下からまたは上から順に電圧偏差を補正する例を示したが、本実施形態3では中間部位のマスター側のスイッチング素子S2を中心にして、検出電圧V1とV2を比較した電圧偏差でスイッチング素子S1を補正し、次いで検出電圧V23とV3を比較し、この電圧偏差でスイッチング素子S3を補正する。スイッチング素子S2を中心に両側にスイッチング素子を増やしていくことで、直列接続する素子数を増やしていくことができる。図5における各抵抗の抵抗値は、以下の関係とする。

【0059】

R11+R12=R21+R22=R31+R32

R11:R12=R22:R21

R31:R32とR1:R2の比率は任意であるが、電圧V3とV23を使った演算によってVce2とVce3の偏差が比較できる抵抗値に設定する。

【0060】

R1+R2<<(R21+R22+R31+R32)ならば、スイッチング素子S1のエミッタ−コレクタ間に設けた抵抗R3は不要とし、そうでなければ(R11+R12):(R21+R22+R31+R32)=R3:(R1+R2)に設定すると良い。

【0061】

これら抵抗値の関係とすることで、抵抗R12とR21の電圧を比較してスイッチング素子S1のゲートを制御し、スイッチング素子S1をS2のスイッチングと同期させる。また、抵抗R32とR2の電圧を比較してスイッチング素子S3のゲートを制御し、スイッチング素子S3をS2のスイッチングと同期させる。

【0062】

実施形態2の抵抗分圧回路では、スイッチング素子S1が基準のスイッチング素子S3と同期するために、スイッチング素子S2とS3の同期を介していたが、本実施形態では同期動作を行う素子がそれぞれ直列基準と比較する形になっている点で異なり、同期の問題はない。

【0063】

(実施形態4)

図6は、(a)に本実施形態4による抵抗分圧回路を示す。本実施形態4では、両素子ともにマスター、スレーブになり、互いにゲート電流を補正しあう。この補正は、図6の(b)に矢印で示すように、お互いが近づくように補正する。

【0064】

図6においては、マスター側とするスイッチング素子S1の抵抗R12の電圧V1と、これに直列接続されるスレーブ側のスイッチング素子S2の抵抗R21の電圧−V2を比較してスイッチング素子S1のゲートを制御し、スイッチング素子S1をS2のスイッチングと同期させる。抵抗R23とR2の電圧V2,V12を比較してスイッチング素子S2のゲートを制御し、スイッチング素子S2をS1のスイッチングと同期させる。

【0065】

本実施形態では、電圧バランス制御による負担電圧がそれぞれ互いに近づく方向へ動作するため、同期する力が強まりスイッチング素子S1とスイッチング素子S2との電圧が等しくなるための制御により応答性が向上する。また、必ずスイッチングタイミングに同期するようになるため、ゲート信号の変化→スイッチング素子が変化する間の遅延がばらつかないようになる。

【0066】

なお、遅い方のスイッチング素子の電流偏差のゲインを高める制御を行っても実施形態4と同様に、スイッチング素子が変化する間の遅延がばらつかないようになる。

【0067】

(実施形態5)

図7は、本実施形態5による抵抗分圧回路を示す。本実施形態5では、実施形態4において、3つの半導体スイッチング素子の多直列とした例を示すもので、スイッチング素子S2とS3は実施形態4と同様に互いに補正しあう制御を行い、スイッチング素子S1はS2をマスターにしてスイッチング素子S2の電圧に合わせるようにスイッチング素子S1のゲート電流を制御する。

【0068】

図7においては、抵抗R12とR21の電圧を比較してスイッチング素子S1のゲートを制御し、スイッチング素子S1をS2のスイッチングと同期させる。抵抗R23とR31の電圧を比較してスイッチング素子S2のゲートを制御し、スイッチング素子S2をS3のスイッチングと同期させる。抵抗R32とR2の電圧を比較してスイッチング素子S3のゲートを制御し、スイッチング素子S3をS2のスイッチングと同期させる。

【0069】

なお、n個の直列接続スイッチング素子S1,S2,S3,…,Snの電圧バランスには、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を比較し、この電圧偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とするスイッチング素子とこれに直列接続されるスイッチング素子をスレーブ側としてそのゲート電流を補正するという制御を繰り返し、各スイッチング素子の負担電圧をバランスさせる

(実施形態6)

図8は、本実施形態6による抵抗分圧回路を示す。本実施形態6では、実施形態4の変形で、実施形態4では互いに電圧を補正し合う方式であったが、本実施形態6ではそれぞれのスイッチング素子の電圧和を素子数で割った各素子のエミッタ−コレクタ間電圧の平均値から、各素子のエミッタ−コレクタ間の電圧を差し引いた電圧偏差を求め、その電圧偏差に基づきゲート電流を補正することで互いのスイッチング素子のエミッタ−コレクタ間の電圧を補正し合う。すなわち、平均値から電圧偏差を求めているところが、実施形態4と相違する。

【0070】

図8においては、抵抗R12とR21の電圧和を直列接続数の2で割って[(V1+V2)/2]、この除算値と抵抗R12の電圧値[V1]を比較して求められた電圧偏差ΔV1でスイッチング素子S1のゲートを制御する。抵抗R23にかかる電圧を直列接続数の2で割って[V23/2]、この除算値と抵抗R22にかかる電圧値[V1]を比較して求められた電圧偏差ΔV2でスイッチング素子S2のゲートを制御する。図8における各抵抗の抵抗値は、以下の関係とする。

【0071】

R11+R12=R21+R22=R1=R2

R11:R12=R22:R21

本実施形態は、互いにエミッタ−コレクタ間電圧VCE1とVCE2の電圧平均値からそれぞれの素子にかかる電圧値を差し引いた電圧偏差を用いることで、互いに補正しあうが平均値に向けて補正し合うために制御上の干渉が起こり辛くなる利点がある。

【符号の説明】

【0072】

1,1A,1B,S1,S2,S3 半導体スイッチング素子

2A,2B コントローラ

IS1、IS2 絶縁回路

GD1,GD2 ゲートドライブ回路

RD1、RD2 抵抗分圧回路

VD1、VD2 電圧検出回路

DAMP 差動増幅回路

VAC 電圧/電流変換回路

【特許請求の範囲】

【請求項1】

複数直列接続の半導体スイッチング素子をオン・オフ同期制御する半導体スイッチ回路において、各スイッチング素子の負担電圧をアクティブバランスさせる電圧バランス回路であって、

マスター側およびスレーブ側の各スイッチング素子のエミッタ−コレクタ間に、それぞれ同等抵抗値で同等分圧比の分圧抵抗を並列接続し、マスター側のスイッチング素子とスレーブ側のスイッチング素子の直列接続点を中点Nとして両スイッチング素子のエミッタ−コレクタ間電圧に比例した電圧を負担電圧としてそれぞれ検出する抵抗分圧回路と、

前記各検出電圧の電圧偏差がゼロ(零)になるよう、スレーブ側のスイッチング素子のゲート電流を補正して各スイッチング素子の負担電圧をバランスさせる電圧バランス制御回路を備えたことを特徴とする半導体スイッチ回路の電圧バランス回路。

【請求項2】

前記電圧バランス制御回路は、各スイッチング素子が共にターンオフを開始した過渡時に、それらのエミッタ−コレクタ間電圧の偏差電圧の正負に応じて1つのスイッチング素子のターンオフ開始を遅くして各スイッチング素子のターンオフタイミングを同期させることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項3】

前記抵抗分圧回路は、前記中点Nから見て高い電位側になる抵抗R11の抵抗値=抵抗R22の抵抗値、低い電位側になる抵抗R12の抵抗値=抵抗R21の抵抗値に設定し、抵抗R11、R22の抵抗値を抵抗R12、R21の抵抗値より大きく設定して抵抗R12、R21のそれぞれ両端に低レベルの検出電圧を得る構成としたことを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項4】

前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に一対のスイッチング素子間のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を各々補正し、各スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項5】

前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、中間部位のマスター側のスイッチング素子を中心にして両側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を各々補正し、各スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項6】

前記抵抗分圧回路は、2個の直列接続スイッチング素子S1,S2のうち、マスター側とするスイッチング素子S1とこれに直列接続されるスレーブ側のスイッチング素子S2のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とし両スイッチング素子のエミッタ−コレクタ間電圧を比較して接続される該マスター側のゲート電流を補正し、両スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項7】

前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とするスイッチング素子とこれに直列接続されるスイッチング素子をスレーブ側としてそのゲート電流を補正という制御を繰り返し、各スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項8】

前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、マスター側とスレーブ側の検出電圧の和を素子数で割った各スイッチング素子のエミッタ−コレクタ間電圧の平均値から、各スイッチング素子のエミッタ−コレクタ間の電圧を差し引いた電圧偏差を求め、その電圧偏差に基づき各スイッチング素子のゲート電流を補正することで互いのスイッチング素子のエミッタ−コレクタ間の電圧を補正し合い、各スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項1】

複数直列接続の半導体スイッチング素子をオン・オフ同期制御する半導体スイッチ回路において、各スイッチング素子の負担電圧をアクティブバランスさせる電圧バランス回路であって、

マスター側およびスレーブ側の各スイッチング素子のエミッタ−コレクタ間に、それぞれ同等抵抗値で同等分圧比の分圧抵抗を並列接続し、マスター側のスイッチング素子とスレーブ側のスイッチング素子の直列接続点を中点Nとして両スイッチング素子のエミッタ−コレクタ間電圧に比例した電圧を負担電圧としてそれぞれ検出する抵抗分圧回路と、

前記各検出電圧の電圧偏差がゼロ(零)になるよう、スレーブ側のスイッチング素子のゲート電流を補正して各スイッチング素子の負担電圧をバランスさせる電圧バランス制御回路を備えたことを特徴とする半導体スイッチ回路の電圧バランス回路。

【請求項2】

前記電圧バランス制御回路は、各スイッチング素子が共にターンオフを開始した過渡時に、それらのエミッタ−コレクタ間電圧の偏差電圧の正負に応じて1つのスイッチング素子のターンオフ開始を遅くして各スイッチング素子のターンオフタイミングを同期させることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項3】

前記抵抗分圧回路は、前記中点Nから見て高い電位側になる抵抗R11の抵抗値=抵抗R22の抵抗値、低い電位側になる抵抗R12の抵抗値=抵抗R21の抵抗値に設定し、抵抗R11、R22の抵抗値を抵抗R12、R21の抵抗値より大きく設定して抵抗R12、R21のそれぞれ両端に低レベルの検出電圧を得る構成としたことを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項4】

前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に一対のスイッチング素子間のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を各々補正し、各スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項5】

前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、中間部位のマスター側のスイッチング素子を中心にして両側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を各々補正し、各スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項6】

前記抵抗分圧回路は、2個の直列接続スイッチング素子S1,S2のうち、マスター側とするスイッチング素子S1とこれに直列接続されるスレーブ側のスイッチング素子S2のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とし両スイッチング素子のエミッタ−コレクタ間電圧を比較して接続される該マスター側のゲート電流を補正し、両スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項7】

前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、各検出電圧を比較し、その偏差でスレーブ側のゲート電流を補正し、該スレーブ側のスイッチング素子をマスター側とするスイッチング素子とこれに直列接続されるスイッチング素子をスレーブ側としてそのゲート電流を補正という制御を繰り返し、各スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【請求項8】

前記抵抗分圧回路は、n個の直列接続スイッチング素子S1,S2,S3,…,Snのうち、低圧側からまたは高圧側から順々に、マスター側とするスイッチング素子とこれに直列接続されるスレーブ側のスイッチング素子のエミッタ−コレクタ間電圧を検出し、

前記電圧バランス制御回路は、マスター側とスレーブ側の検出電圧の和を素子数で割った各スイッチング素子のエミッタ−コレクタ間電圧の平均値から、各スイッチング素子のエミッタ−コレクタ間の電圧を差し引いた電圧偏差を求め、その電圧偏差に基づき各スイッチング素子のゲート電流を補正することで互いのスイッチング素子のエミッタ−コレクタ間の電圧を補正し合い、各スイッチング素子の負担電圧をバランスさせることを特徴とする請求項1に記載の半導体スイッチ回路の電圧バランス回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2012−213294(P2012−213294A)

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願番号】特願2011−78142(P2011−78142)

【出願日】平成23年3月31日(2011.3.31)

【出願人】(000006105)株式会社明電舎 (1,739)

【Fターム(参考)】

【公開日】平成24年11月1日(2012.11.1)

【国際特許分類】

【出願日】平成23年3月31日(2011.3.31)

【出願人】(000006105)株式会社明電舎 (1,739)

【Fターム(参考)】

[ Back to top ]