半導体チップ、これを含む半導体パッケージ、及びその製造方法

【課題】信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージが提供される。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体チップ、これを含む半導体パッケージ、及びその製造方法に関する。

【背景技術】

【0002】

集積回路に対するパッケージング技術は小型化に対する要求及び実装信頼性を満足させるために持続的に発展されて来た。最近では電気/電子製品の小型化と共に高性能化が要求されることにしたがってスタックに対する多様な技術が開発されている。

【0003】

半導体装置分野で言う‘スタック’というのは少なくとも2つ以上のチップ又はパッケージを垂直に積み上げたことを意味する。このようなスタック技術によれば、メモリ素子の場合は半導体集積工程で具現可能であるメモリ容量より2倍以上のメモリ容量を有する製品を具現することができる。また、スタックパッケージはメモリ容量の増大だけでなく、実装密度及び実装面積使用の効率性の側面で長所を有するので、スタックパッケージに対する研究及び開発が加速化されているのが実情である。

【0004】

スタックパッケージにおいて、信号伝達速度の向上等の長所を有するフリップチップボンディング方式に対する需要が増大されている。また、フリップチップボンディング方式のスタック構造でチップ又はパッケージの間の電気的信号を伝達するために貫通シリコンビア(Through Silicon Via)が提案されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】韓国特許公開第10−2009−0131365号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明が解決しようとする課題は信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージを提供することである。

【0007】

本発明が解決しようとする他の課題は収率を向上させることができる半導体チップの製造方法を提供することである。

【課題を解決するための手段】

【0008】

前記課題を達成するための本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。

【0009】

前記貫通ビアは前記基板の表面から突出され得る。この時、前記貫通ビアの幅は望ましくは前記基板の表面から突出された前記貫通ビアの高さと同一であるか、或いはそれより大きい。

【0010】

前記半導体チップは、前記ウェッティング膜と前記シード膜との間に介在された第1バリア膜と、前記ウェッティング膜と前記基板との間に介在された第2バリア膜とをさらに包含できる。

【0011】

前記ウェッティング膜、前記第1バリア膜及び前記シード膜は延長されて前記貫通ビアの突出部分を覆っており、前記第2バリア膜は前記ウェッティング膜の突出部分の側壁を一部露出させ得る。

【0012】

前記シード膜と前記貫通ビアとは銅を包含でき、前記ウェッティング膜は金、白金及びパラジウムを含むグループから選択される少なくとも1つであり得る。

【0013】

前記課題を達成するための本発明にしたがう半導体パッケージは、パッケージ基板と、前記パッケージ基板上に積層された複数の半導体チップと、前記複数の半導体チップの間に介在されて前記半導体チップを電気的に連結させるソルダボールと、を含み、前記複数の半導体チップの中でいずれか1つの半導体チップは、第1基板、前記第1基板を貫通している第1貫通ビア、前記第1基板と前記第1貫通ビアとの間に介在された第1ウェッティング膜、及び前記第1ウェッティング膜と前記第1貫通ビアとの間に介在された第1シード膜を含み、前記ソルダボールは前記第1ウェッティング膜と接している。

【0014】

前記複数の半導体チップの中で他の1つの半導体チップは導電パッドを含み、前記ソルダボールは前記第1ウェッティング膜と前記導電パッドと同時に接することができる。

【0015】

前記ソルダボールは延長されて前記第1ウェッティング膜の側壁を覆うことができる。

【0016】

前記複数の半導体チップの中で他の1つの半導体チップは、第2基板、前記第2基板を貫通している第2貫通ビア、前記第2基板と前記第2貫通ビアとの間に介在された第2ウェッティング膜、及び前記第2ウェッティング膜と前記貫通ビアとの間に介在された第2シード膜を包含でき、前記ソルダボールは前記第1ウェッティング膜と前記第2ウェッティング膜と同時に接することができる。

【0017】

前記他の課題を達成するための本発明にしたがう半導体チップの製造方法は、基板にホールを形成する段階と、前記ホールの内面にコンフォーマルにウェッティング膜を形成する段階と、前記ウェッティング膜上にコンフォーマルにシード膜を形成する段階と、前記シード膜上に前記ホールを満たす貫通ビアを形成する段階と、前記基板の下部を除去して前記ウェッティング膜を露出させる段階と、を含む。

【0018】

前記ウェッティング膜と前記シード膜を形成する段階は蒸着工程を利用でき、前記貫通ビアを形成する段階は鍍金工程を利用することができる。

【発明の効果】

【0019】

本発明の一実施形態による半導体チップは突出された貫通ビアがウェッティング膜で覆われているので、導電パッドとウェッティング膜とを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

【0020】

また、本発明の一実施形態による半導体パッケージは突出した貫通ビアを覆っているウェッティング膜とソルダボールとが接しているので、ソルダボールとウェッティング膜との間の接着力が向上され、その間に酸化膜が形成されていないので、半導体パッケージの信頼性を向上させ得る。

【0021】

また、本発明の一実施形態による半導体チップの製造方法において、絶縁ライナーは化学的気相蒸着(CVD)のような方法によって、第1バリア膜、ウェッティング膜、第2バリア膜、及びシード膜は物理的気相蒸着(PVD)のような方法によって形成されており、全てが蒸着工程で形成されるので、1つの蒸着工程ラインで処理されて工程時間を短縮させ得る。したがって、生産収率を増大させ得る。

【図面の簡単な説明】

【0022】

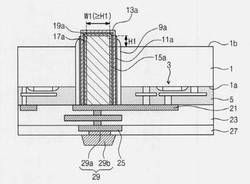

【図1】本発明の一実施形態による半導体チップの断面図である。

【図2】図1のA部分を拡大した断面図である。

【図3】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図4】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図5】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図6】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図7】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図8】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図9】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図10】本発明の一実施形態にしたがって半導体パッケージを製造する過程を示す断面図である。

【図11】本発明の一実施形態にしたがって半導体パッケージを製造する過程を示す断面図である。

【図12】図11のB部分を拡大した断面図である。

【図13】本発明の他の実施形態による半導体チップの拡大断面図である。

【図14】本発明の他の実施形態による半導体パッケージの断面図である。

【図15】本発明の実施形態による半導体素子を具備するメモリカードを示したブロック図である。

【図16】本発明の実施形態による半導体素子を応用した情報処理システムを示したブロック図である。

【発明を実施するための形態】

【0023】

本発明の構成及び効果を十分に理解するために、添付した図面を参照して本発明の望ましい実施形態を説明する。しかし、本発明は以下で開示される実施形態に限定されることではなく、様々な形態に具現されることができ、多様な変更を加えることができる。本実施形態に対する説明は本発明の開示を完全にするものであり、本発明が属する技術分野の通常の知識を有する者に発明の範疇を完全に理解させるために提供されるものである。添付された図面で構成要素は説明を簡単にするためにその大きさが実際より拡大して示されており、各構成要素の比率は誇張されるか、或いは縮小され得る。図面上の同一の構成要素に対しては同一の参照符号又は用語を使用し、同一の構成要素に対して重複された説明は省略され得る。

【0024】

ある構成要素が他の構成要素の“上に”あるか、或いは“連結されている”と記載された場合、他の構成要素の上に直接接しているか、又は連結されていることがあり得るが、中間にその他の構成要素が存在できると理解されなければならない。反面、ある構成要素が他の構成要素の“直ちに上に”あるか、或いは“直接連結されている”と記載された場合には、中間にその他の構成要素が存在しないことと理解できる。構成要素の間の関係を説明する他の表現、例えば、“〜間に”と“直接〜間に”等も同様に解釈できる。

【0025】

第1、第2等の用語は多様な構成要素を説明するために使用されるが、前記構成要素は前記用語によって限定されてはならない。前記用語は1つの構成要素を他の構成要素から区別する目的のみに使用され得る。例えば、本発明の権利範囲を逸脱することなく第1構成要素は第2構成要素と称されることができ、類似に第2構成要素も第1構成要素と称されることができる。

【0026】

単数の表現は文脈で明確に異なって表現されない限り、複数の表現を含む。“含む”又は“有する”等の用語は、明細書に記載された特徴、数字、段階、動作、構成要素部分品又はこれらの組合せが存在することを特定するために、1つ又はそれ以上の他の特徴や数字、段階、動作、構成要素部分品又はこれらの組合せが付加され得るものと解釈できる。

【0027】

本発明の実施形態で使用される用語は異なって定義されない限り、当該技術分野で通常の知識を有する者に通常的に公知された意味に解釈できる。

【0028】

以下、添付した図面を参照して本発明の望ましい実施形態を説明することによって、本発明を詳細に説明する。各図面に提示された同一の参照符号は同一の部材を示す。

【0029】

図1は本発明の一実施形態による半導体チップの断面図である。図2は図1のA部分を拡大した断面図である。図2はビアミドル(via middle)構造を開示する。

【0030】

図1を参照すれば、本発明の一実施形態による半導体チップ100は基板1及び前記基板1を垂直に貫通して電気的信号を伝達する貫通ビア19aを含む。前記基板1は半導体基板であり得る。前記基板1は互いに対向する第1面1a(例えば、前面に該当)と第2面1b(例えば、後面に該当)とを含む。前記第1面1aは回路パターンが形成される活性面に該当され得る。前記第1面1aには複数のトランジスターを含む集積回路3が配置される。前記集積回路3はメモリ回路、ロジック回路、或いはこれらの組合せを包含できる。前記集積回路3は第1層間絶縁膜5で覆われている。前記第1層間絶縁膜5はシリコン酸化膜(例:SiO2)、シリコン窒化膜(例:SiN、Si3N4)、及びシリコン酸窒化物(例:SiON)を含むグループから選択される少なくとも1つであり得る。前記第1層間絶縁膜5は単一層であるか、或いは複数層に構成され得る。前記第1層間絶縁膜5は第2層間絶縁膜23で覆われている。前記第2層間絶縁膜23の内には少なくとも一層の配線21が配置され得る。前記第2層間絶縁膜23は単一層であるか、或いは複数層に構成され得る。前記貫通ビア19aは延長されて前記第1層間絶縁膜5を貫通して前記配線21の一部と接することができる。図示しないが、前記貫通ビア19aと前記配線21との間には銅等の拡散を防止できる拡散防止膜が介在され得る。前記第2層間絶縁膜23はパッシベーション膜27で覆われている。前記第2層間絶縁膜23と前記パッシベーション膜27との間には前記配線21と電気的に連結される最上位配線25が配置され得る。前記最上位配線25は前記パッシベーション膜27を貫通する導電バンプ29と接する。前記導電バンプ29は導電パッド29aとソルダボール29bとを包含できる。前記ソルダボール29bは錫と銀との合金SnAgを包含できる。前記パッシベーション膜27はシリコン窒化膜又は絶縁性高分子膜によって形成され得る。

【0031】

続いて、図1及び図2を参照して、前記貫通ビア19aは前記基板1の第2面1bの外へ突出される。前記貫通ビア19aの幅W1は前記基板1の第2面1bから突出した前記貫通ビア19aの高さH1と同一であるか、或いはそれより大きい。例えば、前記貫通ビア19aの高さは約5μmであり、前記貫通ビア19aの幅W1は約7〜8μmであり得る。前記貫通ビア19aは銅又はタングステンを包含できる。前記貫通ビア19aと前記基板1との間には絶縁ライナー9aが介在されている。前記絶縁ライナー9aはシリコン酸化膜として、例えば200〜300℃で形成される熱酸化膜であり得る。前記絶縁ライナー9aと前記貫通ビア19aとの間にはウェッティング膜パターン(wetting layer、13a)が介在されている。前記ウェッティング膜パターン13aは酸化されない物質として、例えば金Au、パラジウムPd、及び白金Ptを含むグループから選択される少なくとも1つを包含できる。前記ウェッティング膜パターン13aは物理的気相蒸着(PVD)方法で形成され得る。したがって、前記ウェッティング膜パターン13aは約0.2μm以下の薄い厚さを有するように形成され得る。例えば、前記ウェッティング膜パターン13aは約0.01〜0.05μmの厚さを有することができる。また、前記ウェッティング膜パターン13aは原子単一層(atomic monolayer)の厚さ、即ち0.001〜0.005μmの厚さを有するように形成され得る。

【0032】

前記ウェッティング膜パターン13aと前記貫通ビア19aとの間にはシード膜パターン17aが配置される。前記シード膜パターン17aは銅を包含できる。前記ウェッティング膜パターン13aと前記絶縁ライナー9aとの間には第1バリア膜パターン11aが配置され、前記ウェッティング膜パターン13aと前記シード膜パターン17aとの間には第2バリア膜パターン15aが配置され得る。前記バリア膜パターン11a、15aはチタニウム、チタニウム窒化膜、タンタル、及びタンタル窒化膜を含むグループから選択される少なくとも1つを包含できる。前記第2バリア膜パターン15aは前記シード膜パターン17aと前記貫通ビア19aとが包含している銅の拡散を防ぐ。また、前記第1バリア膜パターン11a及び前記第2バリア膜パターン15aは、前記ウェッティング膜パターン13aを構成している金の拡散を防ぐ役割を果たす。前記第1バリア膜パターン11aは前記ウェッティング膜パターン13aと前記絶縁ライナー9aとの間で前記ウェッティング膜パターン13aの接着膜の役割を果たし得る。前記ウェッティング膜パターン13a、前記第2バリア膜パターン15a、及び前記シード膜パターン17aは延長されて、前記貫通ビア19aの突出している面を覆う。前記第1バリア膜パターン11a及び前記絶縁ライナー9aも前記基板1の第2面1bの外へ突出されて、前記ウェッティング膜パターン13aの側壁を露出させ得る。

【0033】

図1及び図2の構造を有する半導体チップ100で、前記基板1の第2面1bから前記貫通ビア19aの端部が突出している。突出した前記貫通ビア19aの端部は導電パッド又は導電バンプの役割を果たし得る。したがって、本発明の構造の半導体チップ100では基板1の第2面1b(後面に該当)に追加的な導電パッドや導電バンプを形成する必要がない。したがって、構造を単純化させながらも、半導体チップの厚さを薄くすることができる。これは半導体チップの高集積化に有利である。また、突出した前記貫通ビア19aの端部が、酸化されないウェッティング膜パターン13aで覆われているので、後にソルダボールと接合させる時、ソルダボールとウェッティング膜パターン13aとの間に自然酸化膜が形成されず、ソルダボールとの濡れ性(wetting property)が良くなる。したがって、前記ソルダボールとウェッティング膜パターン13aとの間の接着性が向上し、自然酸化膜がないので、電気的抵抗が小さくなり、信頼性を向上させ得る。また、本発明で銅を包含できるシード膜パターン17aと貫通ビア19aとの両方が前記ウェッティング膜パターン13aと第2バリア膜パターン15aとによって囲まれるので、銅の拡散を完璧に遮断させ得る。したがって、半導体チップが銅イオンで汚染されることを防ぐことができるので、半導体装置の信頼性を向上させ得る。

【0034】

図3乃至図9は図2の断面を有する半導体チップの製造過程を示す断面図である。

【0035】

図3を参照すれば、第1面1aと第2面1bとを有する基板1を準備する。前記第1面1aに集積回路3を形成する。前記第1面1aの上に第1層間絶縁膜5を積層して前記集積回路3を覆う。

【0036】

図4を参照すれば、前記第1層間絶縁膜5と前記基板1とをパターニングして貫通ホール7を形成する。前記貫通ホール7の底は前記第2面1bと離隔されるように形成される。

【0037】

図5を参照すれば、前記貫通ホール7が形成された前記基板1の前記第1面1aの上に絶縁ライナー膜9、第1バリア膜11、ウェッティング膜13、第2バリア膜15、及びシード膜17を順にコンフォーマルに形成する。前記絶縁ライナー膜9、前記第1バリア膜11、前記ウェッティング膜13、前記第2バリア膜15、及び前記シード膜17は蒸着工程によって形成され得る。前記絶縁ライナー膜9はシリコン酸化膜として、例えば200〜300℃で形成される熱酸化膜で形成され得る。前記ウェッティング膜13は酸化されない物質として、例えば金Au、パラジウムPd及び白金Ptを含むグループから選択される少なくとも1つで形成され得る。特に、前記ウェッティング膜13は物理的気相蒸着(Physical vapor deposition)又は原子薄膜蒸着(Atomic layer deposition)方法を利用して形成され得る。したがって、前記ウェッティング膜13を薄く形成する時、薄い厚さの均一性(uniformitiy)及び接着力(adhesiveness)の向上にも大きく役に立つ。

【0038】

前記バリア膜11、15はチタニウム、チタニウム窒化膜、タンタル、及びタンタル窒化膜を含むグループから選択される少なくとも1つで形成され得る。前記シード膜17は、例えば銅で形成され得る。前記蒸着工程は、例えば、化学的気相蒸着(Chemical vapor deposition)、物理的気相蒸着(Physical vapor deposition)又は原子薄膜蒸着(Atomic layer deposition)であり得る。前記絶縁ライナー膜9、前記第1バリア膜11、前記ウェッティング膜13、前記第2バリア膜15、及び前記シード膜17が全て蒸着工程によって形成されるので、1つの蒸着工程ラインの内で全て形成され得る。したがって、工程時間を短縮させ、生産収率を増大させ得る。前記シード膜17の上に貫通ビア膜19を形成する。前記貫通ビア膜19は鍍金工程を利用して形成され得る。前記鍍金工程は無電解鍍金又は電気鍍金であり得る。前記貫通ビア膜19は前記貫通ホール7を満たすように形成される。

【0039】

図6を参照すれば、平坦化蝕刻工程を実施して前記第1層間絶縁膜5の上の前記絶縁ライナー膜9、前記第1バリア膜11、前記ウェッティング膜13、前記第2バリア膜15、前記シード膜17、及び前記貫通ビア膜19を除去し、前記第1層間絶縁膜5の上部面を露出させる。したがって、前記貫通ホール7の内に絶縁ライナー9a、第1バリア膜パターン11a、ウェッティング膜パターン13a、第2バリア膜パターン15a、シード膜パターン17a、及び貫通ビア19aが残る。

【0040】

図7を参照すれば、前記第1層間絶縁膜5の上に配線21と第2層間絶縁膜23とを形成する。前記第2層間絶縁膜23の上に前記配線21と電気的に連結される最上位配線25を形成する。前記層間絶縁膜5、23はシリコン酸化膜系列の物質で形成され得る。前記配線21、25は不純物がドーピングされたポリシリコンであるか、或いは金属含有膜によって形成され得る。前記第2層間絶縁膜23の上に前記最上位配線25を一部露出させるパッシベーション膜27を形成する。前記パッシベーション膜27はシリコン窒化膜や絶縁性高分子物質で形成され得る。前記パッシベーション膜27の上に前記最上位配線25と接する導電バンプ29を形成する。前記導電バンプ29は導電パッド29aとソルダボール29bとを含み、鍍金工程を2回連続的に進行して形成され得る。前記導電パッド29aは銅のような金属物質で形成され得る。前記ソルダボール29bは錫、鉛、及び銀を含むグループから選択される少なくとも1つの合金を包含できる。前記導電バンプ29を形成した後に、前記基板1の前記第1面1aの上に(前記パッシベーション膜27の上に)支持体31を付着させる。前記支持体31はガラス基板、シリコン基板、金属基板、ポリマー基板等のような硬性材質、或いは伸縮性があるテープ等のような軟性材質で構成され得る。前記支持体31は前記基板1の前記第1面1aを保護する役割を果たす。

【0041】

図8及び図9を参照すれば、前記支持体31が付着された状態で前記基板1を覆して前記第2面1bが上になるようにする。そして、前記基板1に対して全面エッチバック工程を実施して前記第2面1bに隣接する前記基板1を第1厚さT1程度い除去する。この時、前記貫通ビア19aの外側を覆っている前記絶縁ライナー9aと第1バリア膜パターン11aとが一部除去されて前記ウェッティング膜パターン13aが露出される。前記絶縁ライナー9aの前記第2面1bからの高さは前記第1バリア膜パターン11aの前記第2面1bからの高さと同じであるか、或いはそれより低いことがあり得る。この時、前記貫通ビア19aは前記第2面1bから突出されている。

【0042】

図2を再び参照して、前記基板1を覆し、前記支持体31を除去することができる。

【0043】

以下、このように製造された半導体チップ100をパッケージングする過程に対して説明する。

【0044】

図10及び11は本発明の一実施形態にしたがって半導体パッケージを製造する過程を示す断面図である。図12は図11のB部分を拡大した断面図である。

【0045】

図10乃至図12を参照すれば、パッケージ基板200の上に図1の半導体チップと同一である第1半導体チップ100aと第2半導体チップ100bとを積層する。この時、前記第1半導体チップ100aのウェッティング膜パターン13aと前記第2半導体チップ100bのソルダボール29bとが接することができる。前記パッケージ基板200は第1パッド202、第2パッド206、及び前記パッド202と206とを連結するビア204を包含できる。前記パッケージ基板200は印刷回路基板であり得る。このような積層構造で熱を加えれば、前記ソルダボール29bが溶けながら、前記ソルダボール29bと前記ウェッティング膜パターン13aとの間で前記ソルダボール29bの一部と前記ウェッティング膜パターン13aの一部が融合されて金属間化合物(Intermetallic compound、IMC)層129が形成される。前記金属間化合物層129と前記ソルダボール29bとの境界は不明確になり得る。前記金属間化合物層129は前記第2バリア膜パターン15aの側壁を一部覆うように前記ウェッティング膜パターン13aの上端部の中へ一部浸透され得る。前記ソルダボール29bは前記ウェッティング膜パターン13aの側壁を一部覆うことができる。前記ウェッティング膜パターン13aは酸化が行われておらず、自然酸化膜が形成されていないので、前記ソルダボール29bが溶けるとき、前記ウェッティング膜パターン13aの表面によく付着される。したがって、前記ソルダボール29bと前記ウェッティング膜パターン13aとの間の接着力が向上され、界面抵抗が減少されて半導体パッケージの信頼性を向上させ得る。後続的に前記パッケージ基板200の第2パッド206に外部ソルダボール208を付着させ得る。そして、前記半導体チップ100a、100bを覆うモールディング膜210を形成できる。

【0046】

前記第2半導体チップ100bは図1の半導体チップ100と異なり得る。

【0047】

図13は本発明の他の実施形態による半導体チップの拡大断面図であり、ビアラスト(via last)構造を開示する。

【0048】

図13を参照すれば、貫通ビア19aは基板1、第1層間絶縁膜5及び第2層間絶縁膜23を貫通して再配線33と接する。前記再配線33は前記貫通ビア19aと最上位配線25とを電気的に連結させる。図13の半導体チップは、前記第2層間絶縁膜23と前記最上位配線25とを形成した後に、貫通ビア19aを形成し、その後に前記再配線33を形成することによって形成され得る。その以外の構成及び製造過程は図2を参照して説明したことと同一/類似であり得る。

【0049】

図14は本発明の他の実施形態による半導体パッケージの断面図である。

【0050】

図14を参照すれば、パッケージ基板200の上に図1の半導体チップと同一である第1半導体チップ100aと第2半導体チップ100bとを積層し、前記第2半導体チップ100bを図11とは異なって反対に覆して積層する。したがって、前記第1半導体チップ100aのウェッティング膜パターン13aと前記第2半導体チップ100bのウェッティング膜パターン13aとが互いに対向するようにする。そして、これらの間に内部ソルダボール35を配置させた後に加熱して前記内部ソルダボール35が前記ウェッティング膜パターン13aと溶着されるようにする。前記内部ソルダボール35は球形のソルダボールを利用するか、又は自己接合ソルダボンディング(self−assembly solder bonding)工程を利用して形成され得る。前記自己接合ソルダボンディングはソルダ粒子と接着樹脂を含む混合物を前記ウェッティング膜パターン13aの間に塗布した後、熱処理して前記ソルダ粒子の融点以上に加熱すれば、ソルダ粒子が前記接着樹脂の内部で流動して前記ウェッティング膜パターン13a表面まで移動し、溶着されることによって進行し得る。

【0051】

図15は本発明の実施形態による半導体素子を具備するメモリカードを示したブロック図である。

【0052】

図15を参照すれば、メモリカード1200はホスト1230とメモリ1210との諸般データ交換を制御するメモリコントローラ1220を包含できる。SRAM1221は中央処理装置1222の動作メモリとして使用され得る。ホストインターフェイス1223はメモリカード1200と接続されるホストのデータ交換プロトコルを具備することができる。誤謬修正コード1224はメモリ1210から読出されたデータに含まれる誤謬を検出及び訂正できる。メモリインターフェイス1225はメモリ1210とインターフェイシングできる。中央処理装置1222はメモリコントローラ1220のデータを交換するための諸般制御動作を遂行できる。メモリ1210は本発明の実施形態の半導体チップ100及び半導体パッケージの中で少なくともいずれか1つを包含できる。

【0053】

図16は本発明の実施形態による半導体素子を応用した情報処理システムを示したブロック図である。

【0054】

図16を参照すれば、情報処理システム1300は本発明の実施形態による半導体チップ及び半導体パッケージの中で少なくともいずれか1つを具備するメモリシステム1310を包含できる。情報処理システム1300はモバイル機器やコンピューター等を包含できる。一例として、情報処理システム1300はシステムバス1360に電気的に連結されたメモリシステム1310、モデム1320、中央処理装置1330、RAM1340、及びユーザーインターフェイス1350を包含できる。メモリシステム1310はメモリ1311とメモリコントローラ1312を包含でき、図16のメモリカード1200と実質的に同様に構成され得る。このようなメモリシステム1310には中央処理装置1330によって処理されたデータ又は外部から入力されたデータが格納され得る。情報処理システム1300はメモリカード、半導体ディスク装置(Solid State Disk)、カメライメージプロセッサー(Camera Image Sensor)及びその他の応用チップセット(Application Chipset)に提供され得る。

【0055】

以上の発明の詳細な説明は開示された実施状態に本発明を制限しようとする意図ではなく、本発明の要旨を逸脱しない範囲の内で多様な他の組合、変更及び環境で使用することができる。添付された請求の範囲は他の実施状態も含むことと解析しなければならない。

【符号の説明】

【0056】

3 集積回路

5 第1層間絶縁膜

7 貫通ホール

9 絶縁ライナー膜

11 第1バリア膜

13 前記ウェッティング膜

15 第2バリア膜

17 シード膜

19 貫通ビア膜

21 配線

23 第2層間絶縁膜

25 最上位配線

27 パッシベーション膜

29 導電バンプ

29a 導電パッド

29b ソルダボール

100 半導体チップ

【技術分野】

【0001】

本発明は半導体チップ、これを含む半導体パッケージ、及びその製造方法に関する。

【背景技術】

【0002】

集積回路に対するパッケージング技術は小型化に対する要求及び実装信頼性を満足させるために持続的に発展されて来た。最近では電気/電子製品の小型化と共に高性能化が要求されることにしたがってスタックに対する多様な技術が開発されている。

【0003】

半導体装置分野で言う‘スタック’というのは少なくとも2つ以上のチップ又はパッケージを垂直に積み上げたことを意味する。このようなスタック技術によれば、メモリ素子の場合は半導体集積工程で具現可能であるメモリ容量より2倍以上のメモリ容量を有する製品を具現することができる。また、スタックパッケージはメモリ容量の増大だけでなく、実装密度及び実装面積使用の効率性の側面で長所を有するので、スタックパッケージに対する研究及び開発が加速化されているのが実情である。

【0004】

スタックパッケージにおいて、信号伝達速度の向上等の長所を有するフリップチップボンディング方式に対する需要が増大されている。また、フリップチップボンディング方式のスタック構造でチップ又はパッケージの間の電気的信号を伝達するために貫通シリコンビア(Through Silicon Via)が提案されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】韓国特許公開第10−2009−0131365号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明が解決しようとする課題は信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージを提供することである。

【0007】

本発明が解決しようとする他の課題は収率を向上させることができる半導体チップの製造方法を提供することである。

【課題を解決するための手段】

【0008】

前記課題を達成するための本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。

【0009】

前記貫通ビアは前記基板の表面から突出され得る。この時、前記貫通ビアの幅は望ましくは前記基板の表面から突出された前記貫通ビアの高さと同一であるか、或いはそれより大きい。

【0010】

前記半導体チップは、前記ウェッティング膜と前記シード膜との間に介在された第1バリア膜と、前記ウェッティング膜と前記基板との間に介在された第2バリア膜とをさらに包含できる。

【0011】

前記ウェッティング膜、前記第1バリア膜及び前記シード膜は延長されて前記貫通ビアの突出部分を覆っており、前記第2バリア膜は前記ウェッティング膜の突出部分の側壁を一部露出させ得る。

【0012】

前記シード膜と前記貫通ビアとは銅を包含でき、前記ウェッティング膜は金、白金及びパラジウムを含むグループから選択される少なくとも1つであり得る。

【0013】

前記課題を達成するための本発明にしたがう半導体パッケージは、パッケージ基板と、前記パッケージ基板上に積層された複数の半導体チップと、前記複数の半導体チップの間に介在されて前記半導体チップを電気的に連結させるソルダボールと、を含み、前記複数の半導体チップの中でいずれか1つの半導体チップは、第1基板、前記第1基板を貫通している第1貫通ビア、前記第1基板と前記第1貫通ビアとの間に介在された第1ウェッティング膜、及び前記第1ウェッティング膜と前記第1貫通ビアとの間に介在された第1シード膜を含み、前記ソルダボールは前記第1ウェッティング膜と接している。

【0014】

前記複数の半導体チップの中で他の1つの半導体チップは導電パッドを含み、前記ソルダボールは前記第1ウェッティング膜と前記導電パッドと同時に接することができる。

【0015】

前記ソルダボールは延長されて前記第1ウェッティング膜の側壁を覆うことができる。

【0016】

前記複数の半導体チップの中で他の1つの半導体チップは、第2基板、前記第2基板を貫通している第2貫通ビア、前記第2基板と前記第2貫通ビアとの間に介在された第2ウェッティング膜、及び前記第2ウェッティング膜と前記貫通ビアとの間に介在された第2シード膜を包含でき、前記ソルダボールは前記第1ウェッティング膜と前記第2ウェッティング膜と同時に接することができる。

【0017】

前記他の課題を達成するための本発明にしたがう半導体チップの製造方法は、基板にホールを形成する段階と、前記ホールの内面にコンフォーマルにウェッティング膜を形成する段階と、前記ウェッティング膜上にコンフォーマルにシード膜を形成する段階と、前記シード膜上に前記ホールを満たす貫通ビアを形成する段階と、前記基板の下部を除去して前記ウェッティング膜を露出させる段階と、を含む。

【0018】

前記ウェッティング膜と前記シード膜を形成する段階は蒸着工程を利用でき、前記貫通ビアを形成する段階は鍍金工程を利用することができる。

【発明の効果】

【0019】

本発明の一実施形態による半導体チップは突出された貫通ビアがウェッティング膜で覆われているので、導電パッドとウェッティング膜とを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

【0020】

また、本発明の一実施形態による半導体パッケージは突出した貫通ビアを覆っているウェッティング膜とソルダボールとが接しているので、ソルダボールとウェッティング膜との間の接着力が向上され、その間に酸化膜が形成されていないので、半導体パッケージの信頼性を向上させ得る。

【0021】

また、本発明の一実施形態による半導体チップの製造方法において、絶縁ライナーは化学的気相蒸着(CVD)のような方法によって、第1バリア膜、ウェッティング膜、第2バリア膜、及びシード膜は物理的気相蒸着(PVD)のような方法によって形成されており、全てが蒸着工程で形成されるので、1つの蒸着工程ラインで処理されて工程時間を短縮させ得る。したがって、生産収率を増大させ得る。

【図面の簡単な説明】

【0022】

【図1】本発明の一実施形態による半導体チップの断面図である。

【図2】図1のA部分を拡大した断面図である。

【図3】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図4】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図5】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図6】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図7】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図8】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図9】図2の断面を有する半導体チップの製造過程を示す断面図である。

【図10】本発明の一実施形態にしたがって半導体パッケージを製造する過程を示す断面図である。

【図11】本発明の一実施形態にしたがって半導体パッケージを製造する過程を示す断面図である。

【図12】図11のB部分を拡大した断面図である。

【図13】本発明の他の実施形態による半導体チップの拡大断面図である。

【図14】本発明の他の実施形態による半導体パッケージの断面図である。

【図15】本発明の実施形態による半導体素子を具備するメモリカードを示したブロック図である。

【図16】本発明の実施形態による半導体素子を応用した情報処理システムを示したブロック図である。

【発明を実施するための形態】

【0023】

本発明の構成及び効果を十分に理解するために、添付した図面を参照して本発明の望ましい実施形態を説明する。しかし、本発明は以下で開示される実施形態に限定されることではなく、様々な形態に具現されることができ、多様な変更を加えることができる。本実施形態に対する説明は本発明の開示を完全にするものであり、本発明が属する技術分野の通常の知識を有する者に発明の範疇を完全に理解させるために提供されるものである。添付された図面で構成要素は説明を簡単にするためにその大きさが実際より拡大して示されており、各構成要素の比率は誇張されるか、或いは縮小され得る。図面上の同一の構成要素に対しては同一の参照符号又は用語を使用し、同一の構成要素に対して重複された説明は省略され得る。

【0024】

ある構成要素が他の構成要素の“上に”あるか、或いは“連結されている”と記載された場合、他の構成要素の上に直接接しているか、又は連結されていることがあり得るが、中間にその他の構成要素が存在できると理解されなければならない。反面、ある構成要素が他の構成要素の“直ちに上に”あるか、或いは“直接連結されている”と記載された場合には、中間にその他の構成要素が存在しないことと理解できる。構成要素の間の関係を説明する他の表現、例えば、“〜間に”と“直接〜間に”等も同様に解釈できる。

【0025】

第1、第2等の用語は多様な構成要素を説明するために使用されるが、前記構成要素は前記用語によって限定されてはならない。前記用語は1つの構成要素を他の構成要素から区別する目的のみに使用され得る。例えば、本発明の権利範囲を逸脱することなく第1構成要素は第2構成要素と称されることができ、類似に第2構成要素も第1構成要素と称されることができる。

【0026】

単数の表現は文脈で明確に異なって表現されない限り、複数の表現を含む。“含む”又は“有する”等の用語は、明細書に記載された特徴、数字、段階、動作、構成要素部分品又はこれらの組合せが存在することを特定するために、1つ又はそれ以上の他の特徴や数字、段階、動作、構成要素部分品又はこれらの組合せが付加され得るものと解釈できる。

【0027】

本発明の実施形態で使用される用語は異なって定義されない限り、当該技術分野で通常の知識を有する者に通常的に公知された意味に解釈できる。

【0028】

以下、添付した図面を参照して本発明の望ましい実施形態を説明することによって、本発明を詳細に説明する。各図面に提示された同一の参照符号は同一の部材を示す。

【0029】

図1は本発明の一実施形態による半導体チップの断面図である。図2は図1のA部分を拡大した断面図である。図2はビアミドル(via middle)構造を開示する。

【0030】

図1を参照すれば、本発明の一実施形態による半導体チップ100は基板1及び前記基板1を垂直に貫通して電気的信号を伝達する貫通ビア19aを含む。前記基板1は半導体基板であり得る。前記基板1は互いに対向する第1面1a(例えば、前面に該当)と第2面1b(例えば、後面に該当)とを含む。前記第1面1aは回路パターンが形成される活性面に該当され得る。前記第1面1aには複数のトランジスターを含む集積回路3が配置される。前記集積回路3はメモリ回路、ロジック回路、或いはこれらの組合せを包含できる。前記集積回路3は第1層間絶縁膜5で覆われている。前記第1層間絶縁膜5はシリコン酸化膜(例:SiO2)、シリコン窒化膜(例:SiN、Si3N4)、及びシリコン酸窒化物(例:SiON)を含むグループから選択される少なくとも1つであり得る。前記第1層間絶縁膜5は単一層であるか、或いは複数層に構成され得る。前記第1層間絶縁膜5は第2層間絶縁膜23で覆われている。前記第2層間絶縁膜23の内には少なくとも一層の配線21が配置され得る。前記第2層間絶縁膜23は単一層であるか、或いは複数層に構成され得る。前記貫通ビア19aは延長されて前記第1層間絶縁膜5を貫通して前記配線21の一部と接することができる。図示しないが、前記貫通ビア19aと前記配線21との間には銅等の拡散を防止できる拡散防止膜が介在され得る。前記第2層間絶縁膜23はパッシベーション膜27で覆われている。前記第2層間絶縁膜23と前記パッシベーション膜27との間には前記配線21と電気的に連結される最上位配線25が配置され得る。前記最上位配線25は前記パッシベーション膜27を貫通する導電バンプ29と接する。前記導電バンプ29は導電パッド29aとソルダボール29bとを包含できる。前記ソルダボール29bは錫と銀との合金SnAgを包含できる。前記パッシベーション膜27はシリコン窒化膜又は絶縁性高分子膜によって形成され得る。

【0031】

続いて、図1及び図2を参照して、前記貫通ビア19aは前記基板1の第2面1bの外へ突出される。前記貫通ビア19aの幅W1は前記基板1の第2面1bから突出した前記貫通ビア19aの高さH1と同一であるか、或いはそれより大きい。例えば、前記貫通ビア19aの高さは約5μmであり、前記貫通ビア19aの幅W1は約7〜8μmであり得る。前記貫通ビア19aは銅又はタングステンを包含できる。前記貫通ビア19aと前記基板1との間には絶縁ライナー9aが介在されている。前記絶縁ライナー9aはシリコン酸化膜として、例えば200〜300℃で形成される熱酸化膜であり得る。前記絶縁ライナー9aと前記貫通ビア19aとの間にはウェッティング膜パターン(wetting layer、13a)が介在されている。前記ウェッティング膜パターン13aは酸化されない物質として、例えば金Au、パラジウムPd、及び白金Ptを含むグループから選択される少なくとも1つを包含できる。前記ウェッティング膜パターン13aは物理的気相蒸着(PVD)方法で形成され得る。したがって、前記ウェッティング膜パターン13aは約0.2μm以下の薄い厚さを有するように形成され得る。例えば、前記ウェッティング膜パターン13aは約0.01〜0.05μmの厚さを有することができる。また、前記ウェッティング膜パターン13aは原子単一層(atomic monolayer)の厚さ、即ち0.001〜0.005μmの厚さを有するように形成され得る。

【0032】

前記ウェッティング膜パターン13aと前記貫通ビア19aとの間にはシード膜パターン17aが配置される。前記シード膜パターン17aは銅を包含できる。前記ウェッティング膜パターン13aと前記絶縁ライナー9aとの間には第1バリア膜パターン11aが配置され、前記ウェッティング膜パターン13aと前記シード膜パターン17aとの間には第2バリア膜パターン15aが配置され得る。前記バリア膜パターン11a、15aはチタニウム、チタニウム窒化膜、タンタル、及びタンタル窒化膜を含むグループから選択される少なくとも1つを包含できる。前記第2バリア膜パターン15aは前記シード膜パターン17aと前記貫通ビア19aとが包含している銅の拡散を防ぐ。また、前記第1バリア膜パターン11a及び前記第2バリア膜パターン15aは、前記ウェッティング膜パターン13aを構成している金の拡散を防ぐ役割を果たす。前記第1バリア膜パターン11aは前記ウェッティング膜パターン13aと前記絶縁ライナー9aとの間で前記ウェッティング膜パターン13aの接着膜の役割を果たし得る。前記ウェッティング膜パターン13a、前記第2バリア膜パターン15a、及び前記シード膜パターン17aは延長されて、前記貫通ビア19aの突出している面を覆う。前記第1バリア膜パターン11a及び前記絶縁ライナー9aも前記基板1の第2面1bの外へ突出されて、前記ウェッティング膜パターン13aの側壁を露出させ得る。

【0033】

図1及び図2の構造を有する半導体チップ100で、前記基板1の第2面1bから前記貫通ビア19aの端部が突出している。突出した前記貫通ビア19aの端部は導電パッド又は導電バンプの役割を果たし得る。したがって、本発明の構造の半導体チップ100では基板1の第2面1b(後面に該当)に追加的な導電パッドや導電バンプを形成する必要がない。したがって、構造を単純化させながらも、半導体チップの厚さを薄くすることができる。これは半導体チップの高集積化に有利である。また、突出した前記貫通ビア19aの端部が、酸化されないウェッティング膜パターン13aで覆われているので、後にソルダボールと接合させる時、ソルダボールとウェッティング膜パターン13aとの間に自然酸化膜が形成されず、ソルダボールとの濡れ性(wetting property)が良くなる。したがって、前記ソルダボールとウェッティング膜パターン13aとの間の接着性が向上し、自然酸化膜がないので、電気的抵抗が小さくなり、信頼性を向上させ得る。また、本発明で銅を包含できるシード膜パターン17aと貫通ビア19aとの両方が前記ウェッティング膜パターン13aと第2バリア膜パターン15aとによって囲まれるので、銅の拡散を完璧に遮断させ得る。したがって、半導体チップが銅イオンで汚染されることを防ぐことができるので、半導体装置の信頼性を向上させ得る。

【0034】

図3乃至図9は図2の断面を有する半導体チップの製造過程を示す断面図である。

【0035】

図3を参照すれば、第1面1aと第2面1bとを有する基板1を準備する。前記第1面1aに集積回路3を形成する。前記第1面1aの上に第1層間絶縁膜5を積層して前記集積回路3を覆う。

【0036】

図4を参照すれば、前記第1層間絶縁膜5と前記基板1とをパターニングして貫通ホール7を形成する。前記貫通ホール7の底は前記第2面1bと離隔されるように形成される。

【0037】

図5を参照すれば、前記貫通ホール7が形成された前記基板1の前記第1面1aの上に絶縁ライナー膜9、第1バリア膜11、ウェッティング膜13、第2バリア膜15、及びシード膜17を順にコンフォーマルに形成する。前記絶縁ライナー膜9、前記第1バリア膜11、前記ウェッティング膜13、前記第2バリア膜15、及び前記シード膜17は蒸着工程によって形成され得る。前記絶縁ライナー膜9はシリコン酸化膜として、例えば200〜300℃で形成される熱酸化膜で形成され得る。前記ウェッティング膜13は酸化されない物質として、例えば金Au、パラジウムPd及び白金Ptを含むグループから選択される少なくとも1つで形成され得る。特に、前記ウェッティング膜13は物理的気相蒸着(Physical vapor deposition)又は原子薄膜蒸着(Atomic layer deposition)方法を利用して形成され得る。したがって、前記ウェッティング膜13を薄く形成する時、薄い厚さの均一性(uniformitiy)及び接着力(adhesiveness)の向上にも大きく役に立つ。

【0038】

前記バリア膜11、15はチタニウム、チタニウム窒化膜、タンタル、及びタンタル窒化膜を含むグループから選択される少なくとも1つで形成され得る。前記シード膜17は、例えば銅で形成され得る。前記蒸着工程は、例えば、化学的気相蒸着(Chemical vapor deposition)、物理的気相蒸着(Physical vapor deposition)又は原子薄膜蒸着(Atomic layer deposition)であり得る。前記絶縁ライナー膜9、前記第1バリア膜11、前記ウェッティング膜13、前記第2バリア膜15、及び前記シード膜17が全て蒸着工程によって形成されるので、1つの蒸着工程ラインの内で全て形成され得る。したがって、工程時間を短縮させ、生産収率を増大させ得る。前記シード膜17の上に貫通ビア膜19を形成する。前記貫通ビア膜19は鍍金工程を利用して形成され得る。前記鍍金工程は無電解鍍金又は電気鍍金であり得る。前記貫通ビア膜19は前記貫通ホール7を満たすように形成される。

【0039】

図6を参照すれば、平坦化蝕刻工程を実施して前記第1層間絶縁膜5の上の前記絶縁ライナー膜9、前記第1バリア膜11、前記ウェッティング膜13、前記第2バリア膜15、前記シード膜17、及び前記貫通ビア膜19を除去し、前記第1層間絶縁膜5の上部面を露出させる。したがって、前記貫通ホール7の内に絶縁ライナー9a、第1バリア膜パターン11a、ウェッティング膜パターン13a、第2バリア膜パターン15a、シード膜パターン17a、及び貫通ビア19aが残る。

【0040】

図7を参照すれば、前記第1層間絶縁膜5の上に配線21と第2層間絶縁膜23とを形成する。前記第2層間絶縁膜23の上に前記配線21と電気的に連結される最上位配線25を形成する。前記層間絶縁膜5、23はシリコン酸化膜系列の物質で形成され得る。前記配線21、25は不純物がドーピングされたポリシリコンであるか、或いは金属含有膜によって形成され得る。前記第2層間絶縁膜23の上に前記最上位配線25を一部露出させるパッシベーション膜27を形成する。前記パッシベーション膜27はシリコン窒化膜や絶縁性高分子物質で形成され得る。前記パッシベーション膜27の上に前記最上位配線25と接する導電バンプ29を形成する。前記導電バンプ29は導電パッド29aとソルダボール29bとを含み、鍍金工程を2回連続的に進行して形成され得る。前記導電パッド29aは銅のような金属物質で形成され得る。前記ソルダボール29bは錫、鉛、及び銀を含むグループから選択される少なくとも1つの合金を包含できる。前記導電バンプ29を形成した後に、前記基板1の前記第1面1aの上に(前記パッシベーション膜27の上に)支持体31を付着させる。前記支持体31はガラス基板、シリコン基板、金属基板、ポリマー基板等のような硬性材質、或いは伸縮性があるテープ等のような軟性材質で構成され得る。前記支持体31は前記基板1の前記第1面1aを保護する役割を果たす。

【0041】

図8及び図9を参照すれば、前記支持体31が付着された状態で前記基板1を覆して前記第2面1bが上になるようにする。そして、前記基板1に対して全面エッチバック工程を実施して前記第2面1bに隣接する前記基板1を第1厚さT1程度い除去する。この時、前記貫通ビア19aの外側を覆っている前記絶縁ライナー9aと第1バリア膜パターン11aとが一部除去されて前記ウェッティング膜パターン13aが露出される。前記絶縁ライナー9aの前記第2面1bからの高さは前記第1バリア膜パターン11aの前記第2面1bからの高さと同じであるか、或いはそれより低いことがあり得る。この時、前記貫通ビア19aは前記第2面1bから突出されている。

【0042】

図2を再び参照して、前記基板1を覆し、前記支持体31を除去することができる。

【0043】

以下、このように製造された半導体チップ100をパッケージングする過程に対して説明する。

【0044】

図10及び11は本発明の一実施形態にしたがって半導体パッケージを製造する過程を示す断面図である。図12は図11のB部分を拡大した断面図である。

【0045】

図10乃至図12を参照すれば、パッケージ基板200の上に図1の半導体チップと同一である第1半導体チップ100aと第2半導体チップ100bとを積層する。この時、前記第1半導体チップ100aのウェッティング膜パターン13aと前記第2半導体チップ100bのソルダボール29bとが接することができる。前記パッケージ基板200は第1パッド202、第2パッド206、及び前記パッド202と206とを連結するビア204を包含できる。前記パッケージ基板200は印刷回路基板であり得る。このような積層構造で熱を加えれば、前記ソルダボール29bが溶けながら、前記ソルダボール29bと前記ウェッティング膜パターン13aとの間で前記ソルダボール29bの一部と前記ウェッティング膜パターン13aの一部が融合されて金属間化合物(Intermetallic compound、IMC)層129が形成される。前記金属間化合物層129と前記ソルダボール29bとの境界は不明確になり得る。前記金属間化合物層129は前記第2バリア膜パターン15aの側壁を一部覆うように前記ウェッティング膜パターン13aの上端部の中へ一部浸透され得る。前記ソルダボール29bは前記ウェッティング膜パターン13aの側壁を一部覆うことができる。前記ウェッティング膜パターン13aは酸化が行われておらず、自然酸化膜が形成されていないので、前記ソルダボール29bが溶けるとき、前記ウェッティング膜パターン13aの表面によく付着される。したがって、前記ソルダボール29bと前記ウェッティング膜パターン13aとの間の接着力が向上され、界面抵抗が減少されて半導体パッケージの信頼性を向上させ得る。後続的に前記パッケージ基板200の第2パッド206に外部ソルダボール208を付着させ得る。そして、前記半導体チップ100a、100bを覆うモールディング膜210を形成できる。

【0046】

前記第2半導体チップ100bは図1の半導体チップ100と異なり得る。

【0047】

図13は本発明の他の実施形態による半導体チップの拡大断面図であり、ビアラスト(via last)構造を開示する。

【0048】

図13を参照すれば、貫通ビア19aは基板1、第1層間絶縁膜5及び第2層間絶縁膜23を貫通して再配線33と接する。前記再配線33は前記貫通ビア19aと最上位配線25とを電気的に連結させる。図13の半導体チップは、前記第2層間絶縁膜23と前記最上位配線25とを形成した後に、貫通ビア19aを形成し、その後に前記再配線33を形成することによって形成され得る。その以外の構成及び製造過程は図2を参照して説明したことと同一/類似であり得る。

【0049】

図14は本発明の他の実施形態による半導体パッケージの断面図である。

【0050】

図14を参照すれば、パッケージ基板200の上に図1の半導体チップと同一である第1半導体チップ100aと第2半導体チップ100bとを積層し、前記第2半導体チップ100bを図11とは異なって反対に覆して積層する。したがって、前記第1半導体チップ100aのウェッティング膜パターン13aと前記第2半導体チップ100bのウェッティング膜パターン13aとが互いに対向するようにする。そして、これらの間に内部ソルダボール35を配置させた後に加熱して前記内部ソルダボール35が前記ウェッティング膜パターン13aと溶着されるようにする。前記内部ソルダボール35は球形のソルダボールを利用するか、又は自己接合ソルダボンディング(self−assembly solder bonding)工程を利用して形成され得る。前記自己接合ソルダボンディングはソルダ粒子と接着樹脂を含む混合物を前記ウェッティング膜パターン13aの間に塗布した後、熱処理して前記ソルダ粒子の融点以上に加熱すれば、ソルダ粒子が前記接着樹脂の内部で流動して前記ウェッティング膜パターン13a表面まで移動し、溶着されることによって進行し得る。

【0051】

図15は本発明の実施形態による半導体素子を具備するメモリカードを示したブロック図である。

【0052】

図15を参照すれば、メモリカード1200はホスト1230とメモリ1210との諸般データ交換を制御するメモリコントローラ1220を包含できる。SRAM1221は中央処理装置1222の動作メモリとして使用され得る。ホストインターフェイス1223はメモリカード1200と接続されるホストのデータ交換プロトコルを具備することができる。誤謬修正コード1224はメモリ1210から読出されたデータに含まれる誤謬を検出及び訂正できる。メモリインターフェイス1225はメモリ1210とインターフェイシングできる。中央処理装置1222はメモリコントローラ1220のデータを交換するための諸般制御動作を遂行できる。メモリ1210は本発明の実施形態の半導体チップ100及び半導体パッケージの中で少なくともいずれか1つを包含できる。

【0053】

図16は本発明の実施形態による半導体素子を応用した情報処理システムを示したブロック図である。

【0054】

図16を参照すれば、情報処理システム1300は本発明の実施形態による半導体チップ及び半導体パッケージの中で少なくともいずれか1つを具備するメモリシステム1310を包含できる。情報処理システム1300はモバイル機器やコンピューター等を包含できる。一例として、情報処理システム1300はシステムバス1360に電気的に連結されたメモリシステム1310、モデム1320、中央処理装置1330、RAM1340、及びユーザーインターフェイス1350を包含できる。メモリシステム1310はメモリ1311とメモリコントローラ1312を包含でき、図16のメモリカード1200と実質的に同様に構成され得る。このようなメモリシステム1310には中央処理装置1330によって処理されたデータ又は外部から入力されたデータが格納され得る。情報処理システム1300はメモリカード、半導体ディスク装置(Solid State Disk)、カメライメージプロセッサー(Camera Image Sensor)及びその他の応用チップセット(Application Chipset)に提供され得る。

【0055】

以上の発明の詳細な説明は開示された実施状態に本発明を制限しようとする意図ではなく、本発明の要旨を逸脱しない範囲の内で多様な他の組合、変更及び環境で使用することができる。添付された請求の範囲は他の実施状態も含むことと解析しなければならない。

【符号の説明】

【0056】

3 集積回路

5 第1層間絶縁膜

7 貫通ホール

9 絶縁ライナー膜

11 第1バリア膜

13 前記ウェッティング膜

15 第2バリア膜

17 シード膜

19 貫通ビア膜

21 配線

23 第2層間絶縁膜

25 最上位配線

27 パッシベーション膜

29 導電バンプ

29a 導電パッド

29b ソルダボール

100 半導体チップ

【特許請求の範囲】

【請求項1】

基板と、

前記基板を貫通している貫通ビアと、

前記貫通ビアと前記基板との間に介在されたウェッティング膜と、

前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む半導体チップ。

【請求項2】

前記貫通ビアは前記基板の表面から突出していることを特徴とする請求項1に記載の半導体チップ。

【請求項3】

前記貫通ビアの幅は前記基板の表面から突出している前記貫通ビアの高さと同一であるか、或いはそれより大きいことを特徴とする請求項2に記載の半導体チップ。

【請求項4】

前記ウェッティング膜と前記基板との間に介在された第1バリア膜と、

前記ウェッティング膜と前記シード膜との間に介在された第2バリア膜をさらに含むことを特徴とする請求項2に記載の半導体チップ。

【請求項5】

前記ウェッティング膜、前記第2バリア膜、及び前記シード膜は延長されて前記貫通ビアの突出部分を覆っており、

前記第1バリア膜は前記ウェッティング膜の突出部分の側壁を一部露出させていることを特徴とする請求項4に記載の半導体チップ。

【請求項6】

前記シード膜と前記貫通ビアとは銅を含み、

前記ウェッティング膜は金、白金、及びパラジウムを含むグループから選択される少なくとも1つであることを特徴とする請求項1に記載の半導体チップ。

【請求項7】

パッケージ基板と、

前記パッケージ基板の上に積層された複数の半導体チップと、

前記複数の半導体チップの間に介在されて前記半導体チップを電気的に連結させるソルダボールと、を含み、

前記複数の半導体チップの中でいずれか1つの半導体チップは、第1基板、前記第1基板を貫通し、前記第1基板から突出している第1貫通ビア、前記第1基板と前記第1貫通ビアとの間に介在された第1ウェッティング膜、及び前記第1ウェッティング膜と前記第1貫通ビアとの間に介在された第1シード膜を含み、

前記ソルダボールは金属間化合物層を介在して前記第1ウェッティング膜と連結されたことを特徴とする半導体パッケージ。

【請求項8】

前記複数の半導体チップの中で他の1つの半導体チップは導電パッドを含み、前記ソルダボールは前記金属間化合物層と前記導電パッドと同時に接していることを特徴とする請求項7に記載の半導体パッケージ。

【請求項9】

前記金属間化合物層は延長されて前記第1シード膜の側壁の少なくとも一部を覆っていることを特徴とする半導体パッケージ。

【請求項10】

前記複数の半導体チップの中で他の1つの半導体チップは、第2基板、前記第2基板を貫通している第2貫通ビア、前記第2基板と前記第2貫通ビアとの間に介在された第2ウェッティング膜、及び前記第2ウェッティング膜と前記貫通ビアとの間に介在された第2シード膜を含み、

前記ソルダボールは前記第1ウェッティング膜と前記第2ウェッティング膜と同時に接していることを特徴とする請求項7に記載の請求項7に記載の半導体パッケージ。

【請求項11】

基板にホールを形成する段階と、

前記ホールの内面にコンフォーマルにウェッティング膜を形成する段階と、

前記ウェッティング膜の上にコンフォーマルにシード膜を形成する段階と、

前記シード膜の上に前記ホールを満たす貫通ビアを形成する段階と、

前記基板の下部を除去して前記ウェッティング膜を露出させる段階と、を含む半導体チップの製造方法。

【請求項12】

前記ウェッティング膜を形成する段階は、物理的気相蒸着工程又は原子薄膜蒸着工程を利用して形成することを特徴とする請求項11に記載の半導体チップの製造方法。

【請求項13】

第1基板、前記第1基板を貫通し、前記第1基板から突出している貫通ビア、前記第1基板と前記貫通ビアとの間に介在して、突出した前記貫通ビアを覆っているウェッティング膜、及び前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜を含む半導体チップを準備する段階と、

前記半導体チップを第2基板の上にソルダボールを介在して実装する段階と、を含み、

前記ソルダボールは金属間化合物層を介在して前記第1ウェッティング膜に連結されたことを特徴とする半導体パッケージの製造方法。

【請求項1】

基板と、

前記基板を貫通している貫通ビアと、

前記貫通ビアと前記基板との間に介在されたウェッティング膜と、

前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む半導体チップ。

【請求項2】

前記貫通ビアは前記基板の表面から突出していることを特徴とする請求項1に記載の半導体チップ。

【請求項3】

前記貫通ビアの幅は前記基板の表面から突出している前記貫通ビアの高さと同一であるか、或いはそれより大きいことを特徴とする請求項2に記載の半導体チップ。

【請求項4】

前記ウェッティング膜と前記基板との間に介在された第1バリア膜と、

前記ウェッティング膜と前記シード膜との間に介在された第2バリア膜をさらに含むことを特徴とする請求項2に記載の半導体チップ。

【請求項5】

前記ウェッティング膜、前記第2バリア膜、及び前記シード膜は延長されて前記貫通ビアの突出部分を覆っており、

前記第1バリア膜は前記ウェッティング膜の突出部分の側壁を一部露出させていることを特徴とする請求項4に記載の半導体チップ。

【請求項6】

前記シード膜と前記貫通ビアとは銅を含み、

前記ウェッティング膜は金、白金、及びパラジウムを含むグループから選択される少なくとも1つであることを特徴とする請求項1に記載の半導体チップ。

【請求項7】

パッケージ基板と、

前記パッケージ基板の上に積層された複数の半導体チップと、

前記複数の半導体チップの間に介在されて前記半導体チップを電気的に連結させるソルダボールと、を含み、

前記複数の半導体チップの中でいずれか1つの半導体チップは、第1基板、前記第1基板を貫通し、前記第1基板から突出している第1貫通ビア、前記第1基板と前記第1貫通ビアとの間に介在された第1ウェッティング膜、及び前記第1ウェッティング膜と前記第1貫通ビアとの間に介在された第1シード膜を含み、

前記ソルダボールは金属間化合物層を介在して前記第1ウェッティング膜と連結されたことを特徴とする半導体パッケージ。

【請求項8】

前記複数の半導体チップの中で他の1つの半導体チップは導電パッドを含み、前記ソルダボールは前記金属間化合物層と前記導電パッドと同時に接していることを特徴とする請求項7に記載の半導体パッケージ。

【請求項9】

前記金属間化合物層は延長されて前記第1シード膜の側壁の少なくとも一部を覆っていることを特徴とする半導体パッケージ。

【請求項10】

前記複数の半導体チップの中で他の1つの半導体チップは、第2基板、前記第2基板を貫通している第2貫通ビア、前記第2基板と前記第2貫通ビアとの間に介在された第2ウェッティング膜、及び前記第2ウェッティング膜と前記貫通ビアとの間に介在された第2シード膜を含み、

前記ソルダボールは前記第1ウェッティング膜と前記第2ウェッティング膜と同時に接していることを特徴とする請求項7に記載の請求項7に記載の半導体パッケージ。

【請求項11】

基板にホールを形成する段階と、

前記ホールの内面にコンフォーマルにウェッティング膜を形成する段階と、

前記ウェッティング膜の上にコンフォーマルにシード膜を形成する段階と、

前記シード膜の上に前記ホールを満たす貫通ビアを形成する段階と、

前記基板の下部を除去して前記ウェッティング膜を露出させる段階と、を含む半導体チップの製造方法。

【請求項12】

前記ウェッティング膜を形成する段階は、物理的気相蒸着工程又は原子薄膜蒸着工程を利用して形成することを特徴とする請求項11に記載の半導体チップの製造方法。

【請求項13】

第1基板、前記第1基板を貫通し、前記第1基板から突出している貫通ビア、前記第1基板と前記貫通ビアとの間に介在して、突出した前記貫通ビアを覆っているウェッティング膜、及び前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜を含む半導体チップを準備する段階と、

前記半導体チップを第2基板の上にソルダボールを介在して実装する段階と、を含み、

前記ソルダボールは金属間化合物層を介在して前記第1ウェッティング膜に連結されたことを特徴とする半導体パッケージの製造方法。

【図15】

【図16】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−70057(P2013−70057A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2012−207974(P2012−207974)

【出願日】平成24年9月21日(2012.9.21)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成24年9月21日(2012.9.21)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]