半導体チップ、半導体チップの製造方法、および半導体装置

【課題】特性が良好であり、信頼性の高い半導体チップ、半導体チップの製造方法、および半導体装置を提供する。

【解決手段】実施形態の半導体チップは、第1主面と第2主面とを有し、第1主面側に、素子および配線が配置された回路部と回路部を取り囲むガードリング機構部とが設けられた半導体基板と、第1主面側から第2主面側まで通じるビアホール内に設けられたビアと、第1主面側から第2主面側まで通じる第1トレンチ内に設けられた絶縁層と、を備える。第1主面に対して垂直な方向からみて、ビアホールは、回路部が設けられた回路領域に配置されている。第1トレンチは、回路部を取り囲みガードリング機構部が設けられた外周領域に配置されている。第1主面に対して平行な方向における第1トレンチの幅は、この平行な方向におけるビアホールの幅よりも狭い。

【解決手段】実施形態の半導体チップは、第1主面と第2主面とを有し、第1主面側に、素子および配線が配置された回路部と回路部を取り囲むガードリング機構部とが設けられた半導体基板と、第1主面側から第2主面側まで通じるビアホール内に設けられたビアと、第1主面側から第2主面側まで通じる第1トレンチ内に設けられた絶縁層と、を備える。第1主面に対して垂直な方向からみて、ビアホールは、回路部が設けられた回路領域に配置されている。第1トレンチは、回路部を取り囲みガードリング機構部が設けられた外周領域に配置されている。第1主面に対して平行な方向における第1トレンチの幅は、この平行な方向におけるビアホールの幅よりも狭い。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体チップ、半導体チップの製造方法、および半導体装置に関する。

【背景技術】

【0002】

近年の半導体デバイスにおいては、マルチチップパッケージ(Multi Chip Package, MCP)等に代表されるように、複数の半導体チップを積層した半導体装置が高密度化、小型化、または薄型化を達成する上で有効に活用されている。

【0003】

この種の半導体装置において半導体チップを積層する際の1つの技術として、貫通ビア(Through Silicon Via, TSV)が注目されている。この貫通ビアとは、例えば、半導体がシリコン(Si)であるときに、半導体チップの基体である半導体基板の主面間を貫通する電極である。この種の半導体装置を製造するプロセスにおいては、スループットの向上、厚さ方向の集積度を増加させるために半導体チップの薄膜化が求められる。半導体チップの薄型化を図るには、例えば、半導体基板の裏面側を研削する手法が採られている。薄膜化された半導体基板をダイシングする際には、チッピングやクラッキングを抑制するために、レーザダイシングまたはプラズマエッチングといった手法が採られる。

【0004】

しかし、この種のダイシングは、ダイシング刃による機械的な加工ではないため、切断面が比較的滑らかに形成される。このため、切断面の金属ゲッタリング効果が低下し、切断面に付着した金属が半導体チップの内部にまで拡散する場合がある。これにより、半導体装置の特性、信頼性が劣化する場合があった。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011−054637号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明が解決しようとする課題は、特性が良好であり、信頼性の高い半導体チップ、半導体チップの製造方法、および半導体装置を提供することである。

【課題を解決するための手段】

【0007】

実施形態の半導体チップは、第1主面と前記第1主面とは反対側の第2主面とを有し、前記第1主面側に、素子および配線が配置された回路部と前記回路部を取り囲むガードリング機構部とが設けられた半導体基板と、前記半導体基板の前記第1主面側から前記第2主面側まで通じるビアホール内に設けられたビアと、前記半導体基板の前記第1主面側から前記第2主面側まで通じる第1トレンチ内に設けられた絶縁層と、を備える。

【0008】

前記半導体基板の前記第1主面に対して垂直な方向からみて、前記ビアホールは、前記回路部が設けられた回路領域に配置されている。前記第1トレンチは、前記回路部を取り囲み前記ガードリング機構部が設けられた外周領域に配置されている。前記第1主面に対して平行な方向における前記第1トレンチの幅は、前記平行な方向における前記ビアホールの幅よりも狭い。

【図面の簡単な説明】

【0009】

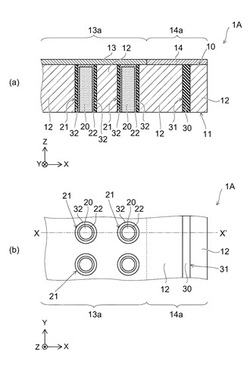

【図1】第1実施形態に係る半導体チップのチップ端領域における模式図であり、(a)は、半導体チップの断面模式図、(b)は、半導体チップの裏面側の平面模式図である。

【図2】第1実施形態に係る半導体チップ全体の表面側の平面模式図である。

【図3】第1実施形態の変形例に係る半導体チップの断面模式図である。

【図4】第1実施形態に係る半導体チップの製造過程を説明するための模式図であり、(a)は、半導体チップの表面側に回路部とガードリング機構部とを形成する製造過程を説明するための断面模式図、(b)は、半導体チップのビアホールおよび第1トレンチを形成する製造過程を説明するための断面模式図、(c)は、裏面側の平面模式図である。

【図5】第1実施形態に係る半導体チップの製造過程を説明するための模式図であり、(a)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の断面模式図、(b)は、ビアホール内の絶縁層を加工する製造過程の断面模式図である。

【図6】第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板の裏面側およびビアホール内に導電層を形成する製造過程の図、(b)は、ビアホール内にビアを形成する製造過程の図である。

【図7】第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板にダイシング加工を施す製造過程の図、(b)は、個片化された半導体チップの図である。

【図8】第1実施形態に係る半導体チップの作用を説明するための断面模式図である。

【図9】第2実施形態に係る半導体チップのチップ端領域における裏面側の平面模式図である。

【図10】第3実施形態に係る半導体チップのチップ端領域における断面模式図であり、(a)は、半導体チップが形成された後の状態の断面模式図、(b)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図、(c)は、ビアホール内および第1トレンチ内にバリアメタル層を形成する製造過程の図である。

【図11】第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板を準備する製造過程の図、(b)は、半導体基板内に、ビアホールおよび第1トレンチを形成する製造過程の図である。

【図12】第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および第1トレンチ内に、絶縁層を形成する製造過程の図、(b)は、ビアホール内に、バリアメタル層を形成する製造過程の図である。

【図13】第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および半導体基板の表面側に導電層を形成する製造過程の図、(b)は、ビアホール内に、ビアを形成する製造過程の図である。

【図14】第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板の表面側に素子部およびガードリング機構部を形成する製造過程の図、(b)は、半導体基板の裏面側を研削する製造過程の図である。

【図15】第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板内にビアホールおよび第1トレンチを形成する製造過程の図、(b)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図である。

【図16】第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および半導体基板の表面側に導電層を形成する製造過程の図、(b)は、ビアホール内に、ビアを形成する製造過程の図である。

【図17】第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、半導体基板の裏面側を研削する製造過程の図である。

【図18】第6実施形態に係る半導体装置の断面模式図である。

【発明を実施するための形態】

【0010】

以下、図面を参照しつつ、実施形態について説明する。以下の説明では、同一の部材には同一の符号を付し、一度説明した部材については適宜その説明を省略する。

【0011】

(第1実施形態)

図1は、第1実施形態に係る半導体チップのチップ端領域における模式図であり、(a)は、半導体チップの断面模式図、(b)は、半導体チップの裏面側の平面模式図である。

図2は、第1実施形態に係る半導体チップ全体の表面側の平面模式図である。

図1(a)には、図1(b)のX−X’断面が示されている。図1(b)には、図2のAで示された部分が拡大されて示されている。

【0012】

第1実施形態に係る半導体チップ1Aは、例えば、マルチチップパッケージ型の半導体装置内に収容される。

図1(a)に示すように、半導体チップ1Aは、表面(第1主面)10と、表面10とは反対側の裏面(第2主面)11と、を有する半導体基板12を備える。半導体基板12は、例えば、シリコン基板を薄膜化したものである。例えば、シリコン基板の裏面側を研削することによって、シリコン基板が薄膜化される。

【0013】

半導体基板12は、半導体基板12の表面10側に、素子および配線が配置された回路部13と、回路部13を取り囲むガードリング機構部14と、を設けている。半導体基板12上に設けられた回路部13には、トランジスタ、ダイオード等の能動素子、抵抗、コンデンサ等の受動素子、これらの素子間を接続する配線、メモリセル等が配置されている。回路部13に形成される能動素子の一部は、半導体基板12内に形成されてもよい。回路部13内の配線は、例えば、層間絶縁膜を介して積層されている。回路部13の大部分は、配線が占めている。

【0014】

半導体基板12上に設けられたガードリング機構部14には、例えば、層間絶縁膜内に形成された導電製のガードリングが配置されている。ガードリング機構部14が回路部13の周りに設けられたことにより、ガードリングによってダイシング時の半導体基板12のクラック発生、ダイシング後の回路部13内への水分の拡散が抑制される。

【0015】

半導体チップ1Aを表面(第1主面)10側もしくは裏面(第2主面)11側からみた場合、回路部13が配置された領域を回路領域13a、ガードリング機構部14が配置され、回路領域13aを取り囲む領域を外周領域14aとする。

【0016】

また、半導体チップ1Aは、半導体基板12の表面10側から裏面11側にまで通じるビアホール21内に、ビア20を備える。ビアホール21は、半導体基板12内に少なくとも1つ設けられている。さらに、半導体チップ1Aは、半導体基板12の表面10側から裏面11側にまで通じる第1トレンチ31内に絶縁層30を備える。第1トレンチ31は、半導体基板12内に少なくとも1つ設けられている。

【0017】

ビア20と半導体基板12との間には、絶縁層32が設けられている。絶縁層32は、ビア20と半導体基板12との絶縁性を維持するためのスペーサ部材である。さらに、絶縁層32とビア20との間には、バリアメタル層22が設けられている。ビア20および絶縁層30は、同じ半導体基板12の中に設けられている。第1実施形態では、絶縁層32を第1絶縁層、絶縁層30を第2絶縁層とする。

【0018】

半導体基板12の表面10(もしくは、裏面11)に対して垂直な方向から半導体チップ1Aをみた場合、ビアホール21は、回路領域13aに配置され、第1トレンチ31は、回路領域13aを取り囲む外周領域14aに配置されている(図1(b)参照)。

【0019】

半導体基板12の表面10に対して平行な方向(図のX方向)における第1トレンチ31の幅は、この平行な方向におけるビアホール21の幅よりも狭くなっている。ここで、「幅」とは、図1(b)のX−X’線に沿ったビアホール21の幅、第1トレンチ31の幅で定義される。第1トレンチ31については、その長手方向に対して略垂直な方向を「幅」と定義することもできる。

【0020】

半導体基板12の表面10(もしくは、裏面11)に対して垂直な方向から半導体チップ1Aをみた場合、第1トレンチ31は、連続であり、ループ状になっている。回路領域13aは、第1トレンチ31によって取り囲まれている。これにより、半導体基板12の回路領域13aは、第1トレンチ31によって、第1トレンチ31から外側の半導体基板12から遮断される。

【0021】

第1トレンチ31は、図示するように、端をもたない閉じたループ状の溝でもよく、一部が不連続となった開かれたループ状の溝でもよい。また、半導体基板12の表面10(もしくは、裏面11)に対して垂直な方向から半導体チップ1Aをみた場合、ループ状の第1トレンチ31は、一重であってもよく、二重以上の多重であってもよい。図2には、一例として、二重の第1トレンチ31が表示されている。すなわち、半導体基板12の表面10に対して垂直な方向から半導体基板12をみた場合、第1トレンチ31に設けられた絶縁層30の外側に、この第1トレンチ31を取り囲む別の第1トレンチ31内に絶縁層30がさらに設けられている。

【0022】

半導体基板12の主成分は、例えば、シリコン(Si)である。ビア20の材質は、例えば、銅(Cu)、タングステン(W)、ニッケル(Ni)、ポリシリコンのいずれかである。絶縁層32、30については、その内部における金属拡散長がシリコン結晶内の金属拡散長よりも短い材質が選択される。例えば、絶縁層32、30の材質の具体例としては、窒化シリコン(Si3N4)、炭化シリコン(SiC)、炭窒化シリコン(SiCN)、酸化シリコン(SiO2)の少なくともいずれかが選択される。バリアメタル層22の材質は、例えば、チタン(Ti)、窒化チタン(TiN)等である。

【0023】

図3は、第1実施形態の変形例に係る半導体チップの断面模式図である。

図3には、半導体チップのチップ端領域における断面模式図が示されている。

【0024】

半導体チップ1Bにおいては、第1トレンチ31内の絶縁層30の中央にシーム状の空間30sが形成されている。但し、半導体チップ1Bでは、第1トレンチ31の側面31wが絶縁層30によって覆われている。このような構造の半導体チップ1Bも第1実施形態に含まれる。

【0025】

半導体チップの製造過程について、半導体チップ1Aの製造過程を例に挙げて説明する。

【0026】

図4は、第1実施形態に係る半導体チップの製造過程を説明するための模式図であり、(a)は、半導体チップの表面側に回路部とガードリング機構部とを形成する製造過程を説明するための断面模式図、(b)は、半導体チップのビアホールおよび第1トレンチを形成する製造過程を説明するための断面模式図、(c)は、裏面側の平面模式図である。図4(b)には、図4(c)のX−X’断面が示されている。

【0027】

まず、図4(a)に示すように、半導体基板12の表面10側に、素子および配線が配置された回路部13と、回路部13を取り囲むガードリング機構部14と、を形成する。この段階での半導体基板12は、ダイシング前のウェーハ状態にある。半導体基板12は、裏面11側が研削され、薄膜化がなされる。薄膜化された半導体基板12については、ガラス板等の支持基板によって支持される。

【0028】

続いて、半導体基板12の表裏を180度反転させた後、図4(b)、(c)に示すように、表面10(もしくは、裏面11)に対して垂直な方向からみて、回路部13が形成された回路領域13aの半導体基板12内に、ビアホール21を少なくとも1つ形成する。さらに、ガードリング機構部14を含み、回路領域13aを取り囲む外周領域14aの半導体基板12内に、第1トレンチ31を少なくとも1つ形成する。

【0029】

この段階で、半導体基板12の裏面11から表面10に向かって、回路部13の一部を裏面11側に開放するビアホール21を少なくとも1つ形成するとともに、半導体基板12の裏面11から表面10に向かって、ガードリング機構部14の一部を裏面11側に開放する第1トレンチ31を少なくとも1つ形成する。

【0030】

ビアホール21および第1トレンチ31は、フォトリソグラフィプロセス、エッチングプロセス等を経て、半導体基板12の裏面11側から形成される。

【0031】

また、半導体基板12の表面10に対して平行な方向(図のX方向)における第1トレンチ31の幅を、X方向におけるビアホール21の幅よりも狭く形成する。さらに、図1に示すように、回路領域13aを取り囲むように第1トレンチ31を形成する。

【0032】

図5は、第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図、(b)は、ビアホール内の絶縁層を加工する製造過程の図である。

【0033】

次に、図5(a)に示すように、半導体基板12の裏面11上、ビアホール21内、および第1トレンチ31内に、絶縁層30、32と同じ材質である絶縁膜33を一括で形成する。絶縁膜33は、例えば、段差被覆率が良好なプラズマCVD(Chemical Vapor Deposition)によって形成される。

【0034】

ここで、ビアホール21の幅は、第1トレンチ31の幅よりも広い。従って、絶縁膜33の厚みを適宜調整することにより、第1トレンチ31内は、絶縁膜33によって埋め込まれ、ビアホール21内は、絶縁膜33によって埋め込まれない状態が得られる。

【0035】

例えば、半導体基板12の裏面11上、ビアホール21内、および第1トレンチ31内に、一括して絶縁膜33を形成し始めてから、第1トレンチ31内が絶縁膜33によって埋め込んだ後に、絶縁膜33の成膜を停止する。これにより、第1トレンチ31内は、絶縁膜33によって埋め込まれるが、ビアホール21内は、絶縁膜33によって埋め込まれない構造が得られる。ビアホール21の側面21w上に形成された絶縁膜33の厚みは、一例として、第1トレンチ31の幅のおよそ半分になる。

【0036】

絶縁膜33を成膜した後、ビアホール21の側面21w上に形成された絶縁膜33は、上述した絶縁層32に相当し、第1トレンチ31内に埋設された絶縁膜33は、上述した絶縁層30に相当する。

【0037】

次に、図5(b)に示すように、RIE(Reactive Ion Etching)等の異方性エッチングによって、ビアホール21の底面21b上に堆積した絶縁膜33を選択的に除去する。また、半導体基板12の裏面11上に形成された絶縁膜33については、必要に応じて除去する。これにより、ビアホール21の側面21w上に、絶縁層32が設けられる。また、第1トレンチ31内には、絶縁層30が設けられる。

【0038】

図6は、第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板の裏面上およびビアホール内に導電層を形成する製造過程の図、(b)は、ビアホール内にビアを形成する製造過程の図である。

【0039】

次に、図6(a)に示すように、半導体基板12の裏面11上およびビアホール21内に、スパッタリング法によって、バリアメタル層22を形成する。

【0040】

続いて、半導体基板12の裏面11上およびビアホール21内に、バリアメタル層22を介して導電層23を形成する。導電層23は、例えば、電解めっき法もしくはプラズマCVDによって形成される。

【0041】

ビアホール21の底面21b上に堆積した絶縁膜33は、既に取り除かれているので、導電層23と回路部13とが接触する。

【0042】

次に、図6(b)に示すように、ビアホール21外に形成された導電層23の余剰部分、および半導体基板12の裏面11上に形成されたバリアメタル層22の余剰部分を、CMP(Chemical Mechanical Polishing)によって除去する。これにより、ビアホール21内に、回路部13に接続されたビア20が形成される。

【0043】

図7は、第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板にダイシング加工を施す製造過程の図、(b)は、個片化された半導体チップの図である。

【0044】

次に、図7(a)に示すように、半導体基板12にダイシング加工を施す。第1実施形態では、ダイシング時の半導体基板12のチッピングやクラックを防止するために、レーザダイシングによって、半導体基板12を分割する。例えば、ダイシングライン90に沿って、レーザ光91を半導体基板12に照射する。レーザダイシングの代わりに、プラズマエッチングによって半導体基板12を分割してもよい。これにより、半導体基板12が個片化されて、半導体チップ1Aが形成される。この状態を、図7(b)に示す。

【0045】

この後、個片化された半導体チップ1Aは、その複数個が積層されて、封止用樹脂によって封止される。これにより、マルチチップパッケージ型の半導体装置が形成される(後述)。封止用樹脂として熱硬化性の樹脂を用いた場合は、半導体チップ1Aが封止される際に半導体チップ1Aが加熱される。

【0046】

また、成膜条件によっては、絶縁層30内に、上述したシーム状の空間30sが生成する場合がある。この場合には、半導体チップ1Aに代わり、半導体チップ1Bが形成される。

【0047】

図8は、第1実施形態に係る半導体チップの作用を説明するための断面模式図である。

図8(a)には、半導体チップ1Aが示されている。図8(b)には、半導体チップ1Bが示されている。

【0048】

半導体チップ1A、1Bによれば、回路部13がリング状の第1トレンチ31によって取り囲まれている。半導体チップ1Aでは、トレンチ31内に絶縁層30が設けられている。半導体チップ1Bでは、第1トレンチ31の側面31wが絶縁層30によって覆われている。

【0049】

ガードリング機構部14は、金属製のガードリングを有する。このため、ダイシングライン90に沿って、半導体基板12を切断すると、切断面85にガードリングの金属成分が付着する場合がある。付着した金属は、汚染金属源になる可能性がある。

【0050】

切断面85は、レーザダイシングもしくはプラズマエッチングによって形成される。この切断は、ダイシング刃による機械的なダイシング加工ではないため、切断面85は、比較的滑らかに形成される。このため、切断面85は、汚染金属のゲッタリング機能を充分に持たない場合がある。そして、この切断面85に、上述したように、ガードリング中の金属成分が付着する場合がある。

【0051】

しかし、半導体チップ1A、1Bでは、ダイシング後において、半導体チップが加熱されたり、半導体チップ自体が温まったとしても、絶縁層30によって、半導体チップ内への汚染金属の熱拡散が抑制される。すなわち、汚染金属が拡散する様子を矢印dで表すと、この矢印dで示すように、絶縁層30がバリア層となって、汚染金属の半導体チップ内への熱拡散が抑制される。これにより、半導体チップ1A、1Bでは、特性劣化、信頼性劣化が起き難くなる。

【0052】

また、絶縁層30の材質は、窒化シリコン(Si3N4)、炭化シリコン(SiC)、炭窒化シリコン(SiCN)、酸化シリコン(SiO2)の少なくともいずれかである。このような材質の線膨張係数は、ビア20を構成する材質(例えば、銅(Cu))の線膨張係数よりも小さい。

【0053】

仮に、第1トレンチ31内に、銅(Cu)等の金属層を埋設してしまうと、金属層の線膨張係数と半導体基板12の線膨張係数との差が大きくなる。このため、半導体チップを積層したり、封止用樹脂によって封止する際に、半導体チップに過剰な応力が印加される。これにより、半導体チップにクラックが生じたり、半導体チップ自体が変形したりする。

【0054】

これに対し、半導体チップ1A、1Bでは、第1トレンチ31内に、絶縁層30を設けている。絶縁層30の線膨張係数と半導体基板12の線膨張係数との差は、金属層の線膨張係数と半導体基板12の線膨張係数との差よりも小さい。このため、半導体チップ1A、1Bを積層する際、もしくは半導体チップ1A、1Bを封止用樹脂によって封止する際には、応力が緩和される。これにより、半導体チップ1A、1Bにはクラックが発生し難く、さらに、半導体チップ1A、1Bは、変形し難くなる。

【0055】

また、半導体チップ1A、1Bでは、ビアホール21内の側面21w上に絶縁層32を形成すると同時に、第1トレンチ31内に絶縁層30を形成している。これは、第1トレンチ31の幅がビアホール21の幅よりも狭いがために達成し得る。

【0056】

換言すれば、半導体チップ1A、1Bでは、チップ全体面積に対する絶縁層30の面積の割合をより小さくすることができる。その結果、半導体チップ1A、1Bでは、回路部13の面積比率を増加させることができる。

【0057】

仮に、第1トレンチ31内を金属層で構成すると、この金属層と第1トレンチ31との間に、バリアメタル層が必要になる。このバリアメタル層は、金属層中の金属成分が半導体基板中へ拡散するのを防止するために必然の部材になる。従って、第1トレンチ31の幅は必然的に広くなり、回路部13の面積比率の増加に限界が生じてしまう。あるいは、第1トレンチ31内の金属層がチップ外部から吸収された水分によって劣化する可能性もある。その結果、第1トレンチ31内の金属層自体が汚染金属源になる可能性がある。

【0058】

これに対し、半導体チップ1A、1Bでは、第1トレンチ31内に絶縁層30を形成している。このため、第1トレンチ31内が汚染金属源になることはない。

【0059】

このように、第1実施形態によれば、特性が良好であり、信頼性の高い半導体チップが形成される。

【0060】

(第2実施形態)

図9は、第2実施形態に係る半導体チップのチップ端領域における裏面側の平面模式図であり、(a)は、半導体チップの裏面側の全体図、(b)は、(a)のA部分の拡大図である。

【0061】

半導体チップ2では、半導体基板12の表面10に対して垂直な方向から半導体基板12をみた場合、外周領域14aの半導体基板12に、第1トレンチ31を挟んで、回路領域13a側の半導体基板12と、回路領域13aとは反対側の半導体基板12と、が連続する部分31sがある。すなわち、半導体チップ2においては、回路領域13aを取り囲む第1トレンチ31のが不連続になっている。この不連続部分を部分31sとしている。

【0062】

半導体チップ2においては、部分31sが第1トレンチ31の第1の端31aと、第1トレンチ31の第2の端31bと、によって挟まれている。また、部分31sにおいて、第1トレンチ31の第1の端31aと、第1トレンチ31の第2の端31bと、が互いに対向している。半導体チップ2では、第1の端31aもしくは第2の端31bからさらに第2トレンチ35が延在している。そして、第1トレンチ31と第2トレンチ35とが半導体基板12を介して互いに対向している。第1トレンチ31の外側には、第1の端31aもしくは第2の端31bから延在された第2トレンチ35がさらに配置されている。第2トレンチ内には、絶縁層30が設けられている。

【0063】

例えば、図9(b)には、第1トレンチ31の回路領域13a側の半導体基板12とは反対側の半導体基板12内に、第2の端31bから延在された第2トレンチ35が設けられた状態が示されている。第1トレンチ31と第2トレンチ35とは、およそ平行に延在している。

【0064】

第2トレンチ35については、第1の端31aから延在してもよい。また、第1トレンチ31の回路領域13a側の半導体基板12内に第2トレンチ35を設けてもよい。

【0065】

このような構造であれば、半導体チップ2を外周領域14aから回路領域13aをみた場合、部分31sが第2トレンチ35によって、遮蔽される。すなわち、第1トレンチ31の一部が不連続になっても、第2トレンチ35の存在によって汚染金属の拡散経路が迷路のように長くなる。従って、半導体チップ2は、汚染金属に対して高いバリア性を有する。なお、Aに示す箇所は1箇所である必要はなく、複数箇所であってもよい。

【0066】

また、半導体チップ2においては、第1トレンチ31の回路領域13a側から部分31sを介して第1トレンチ31の外周にまで半導体基板12が連続する部分がある。従って、半導体チップ2の外周領域14aの強度はより増加する。

【0067】

(第3実施形態)

図10は、第3実施形態に係る半導体チップのチップ端領域における断面模式図であり、(a)は、半導体チップが形成された後の状態の断面模式図、(b)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図、(c)は、ビアホール内および第1トレンチ内にバリアメタル層を形成する製造過程の図である。

【0068】

図10(a)に示す半導体チップ3においては、絶縁層30内に、バリアメタル層25がさらに狭入されている。すなわち、バリアメタル層25が絶縁層30によって挟まれている。半導体チップ3においては、第1トレンチ31の幅が半導体チップ1Aの第1トレンチ31よりも拡げられている。そして、第1トレンチ31内に、絶縁層30とバリアメタル層25とが埋め込まれている。換言すれば、第1トレンチ31内では、X方向において絶縁層30/バリアメタル層25/絶縁層30の積層膜が形成されている。バリアメタル層25の材質は、例えば、チタン(Ti)である。

【0069】

半導体チップ3の製造過程は、以下の手順により行われる。

例えば、図10(b)に示すように、ビアホール21の側面21w上に、絶縁層32を形成し、第1トレンチ31内に、絶縁層30を形成する、ここでは、第1トレンチ31内が第2絶縁層30によって埋め込まれない状態で、絶縁膜33の形成を停止する。

【0070】

次に、図10(c)に示すように、ビアホール21内に、絶縁層32を介してバリアメタル層22を形成し、第1トレンチ31内に、絶縁層30を介してバリアメタル層25を形成する。この後は、図6(a)以降で説明した製造プロセスを実施する。これにより、半導体チップ3が形成される。

【0071】

このような構造によれば、第1トレンチ31内に絶縁層30のほか、バリアメタル層25が設けられたので、汚染金属に対するバリア性がさらに向上する。また、第1トレンチ31の幅を拡げたことにより、絶縁層30の種類の選択の自由度、絶縁層30の膜厚の選択の自由度が増加する。

【0072】

(第4実施形態)

図11は、第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板を準備する製造過程の図、(b)は、半導体基板内に、ビアホールおよび第1トレンチを形成する製造過程の図である。

【0073】

図11(a)に示すように、表面10と表面10とは反対側の裏面11とを有する半導体基板12を準備する。半導体基板12は、ダイシング前のウェーハ状態にある。

【0074】

次に、図11(b)に示すように、半導体基板12の表面10側に形成される回路領域13aに、表面10から裏面11に向かって半導体基板12内にビアホール21を少なくとも1つ形成する。さらに、回路領域13aを取り囲む外周領域14aに、表面10から裏面11に向かって半導体基板12内に第1トレンチ31を少なくとも1つ形成する。ビアホール21および第1トレンチ31は、例えば、フォトリソグラフィプロセス、エッチングプロセスを経て形成される。また、表面10に対して平行な方向(X方向)における第1トレンチ31の幅を、表面10に対して平行な方向におけるビアホール21の幅よりも狭く形成する。また、回路領域13aを取り囲むように第1トレンチ31を形成する。

【0075】

図12は、第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および第1トレンチ内に、絶縁層を形成する製造過程の図、(b)は、ビアホール内に、バリアメタル層を形成する製造過程の図である。

【0076】

次に、図12(a)に示すように、半導体基板12の表面10上、ビアホール21内、および第1トレンチ31内に、絶縁層30、32と同じ材質である絶縁膜33をプラズマCVDによって一括で形成する。

【0077】

ここで、ビアホール21の幅は、第1トレンチ31の幅よりも広い。従って、絶縁膜33の厚みを適宜調整することにより、第1トレンチ31内は、絶縁膜33によって埋め込まれ、ビアホール21内は、絶縁膜33によって埋め込まれない状態が得られる。

【0078】

例えば、半導体基板12の表面10上、ビアホール21内、および第1トレンチ31内に、一括して絶縁膜33を形成し始めてから、第1トレンチ31内が絶縁膜33によって埋め込んだ後に、絶縁膜33の成膜を停止する。これにより、第1トレンチ31内は、絶縁膜33によって埋め込まれるが、ビアホール21内は、絶縁膜33によって埋め込まれない構造が得られる。ビアホール21の側面21w上に形成された絶縁膜33の厚みは、第1トレンチ31の幅のおよそ半分になる。

【0079】

絶縁膜33を成膜した後、ビアホール21の側面21w上に形成された絶縁膜33は、上述した絶縁層32に相当し、第1トレンチ31内に埋設された絶縁膜33は、上述した絶縁層30に相当する。すなわち、ビアホール21の側面21w上に、絶縁層32を形成するとともに、第1トレンチ31内に、絶縁層30を形成する。

【0080】

次に、図12(b)に示すように、半導体基板12の表面10上およびビアホール21内に、スパッタリング法によって、バリアメタル層22を形成する。

【0081】

図13は、第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および半導体基板の表面側に導電層を形成する製造過程の図、(b)は、ビアホール内に、ビアを形成する製造過程の図である。

【0082】

次に、図13(a)に示すように、半導体基板12の表面10上およびビアホール21内に、バリアメタル層22を介して導電層23を形成する。導電層23は、例えば、電解めっき法もしくはプラズマCVDによって形成される。

【0083】

次に、図13(b)に示すように、ビアホール21外に形成された導電層23の余剰部分、および半導体基板12の表面10上に形成されたバリアメタル層22の余剰部分を、CMPによって除去する。これにより、ビアホール21内に、回路部13に接続可能なビア20が形成される。

【0084】

図14は、第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板の表面側に素子部およびガードリング機構部を形成する製造過程の図、(b)は、半導体基板の裏面側を研削する製造過程の図である。

【0085】

次に、図14(a)に示すように、半導体基板12の表面10側の回路領域13aに、素子および配線を含む回路部13を形成し、外周領域14aに、ガードリング機構部を形成する。

【0086】

次に、図14(b)に示すように、裏面11側の半導体基板12を研削し、ビア20および絶縁層30を裏面11から表出させる。

【0087】

この後、ダイシングライン90に沿って、半導体基板12が個片化される。このような製造過程によっても、半導体チップ1Aを形成することができる。

【0088】

(第5実施形態)

図15は、第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板内にビアホールおよび第1トレンチを形成する製造過程の図、(b)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図である。

【0089】

図15(a)に示すように、表面10側において、回路部13と、回路部13を取り囲むガードリング機構部14と、が設けられた半導体基板12を準備した後、半導体基板12の表面10から裏面11に向かって、回路部13の一部にまで通じ、回路部13のその一部の下の半導体基板12の内部にまで延在するビアホール21を少なくとも1つ形成する。さらに、ガードリング機構部14の一部にまで通じ、ガードリング機構部14のその一部の下の半導体基板12の内部にまで延在する第1トレンチ31を少なくとも1つ形成する。

【0090】

ビアホール21および第1トレンチ31は、フォトリソグラフィプロセス、エッチングプロセス等を経て、半導体基板12の表面10側から形成される。また、半導体基板12の表面10に対して平行な方向(図のX方向)における第1トレンチ31の幅を、X方向におけるビアホール21の幅よりも狭く形成する。また、回路領域13aを取り囲むように第1トレンチ31を形成する。

【0091】

次に、図15(b)に示すように、半導体基板12の表面10上、ビアホール21内、および第1トレンチ31内に、絶縁層30、32と同じ材質である絶縁膜33をプラズマCVDによって一括で形成する。

【0092】

ここで、ビアホール21の幅は、第1トレンチ31の幅よりも広い。従って、絶縁膜33の厚みを適宜調整することにより、第1トレンチ31内は、絶縁膜33によって埋め込まれ、ビアホール21内は、絶縁膜33によって埋め込まれない状態が得られる。

【0093】

例えば、半導体基板12の表面10上、ビアホール21内、および第1トレンチ31内に、一括して絶縁膜33を形成し始めてから、第1トレンチ31内が絶縁膜33によって埋め込んだ後に、絶縁膜33の成膜を停止する。これにより、第1トレンチ31内は、絶縁膜33によって埋め込まれるが、ビアホール21内は、絶縁膜33によって埋め込まれない構造が得られる。ビアホール21の側面21w上に形成された絶縁膜33の厚みは、第1トレンチ31の幅のおよそ半分になる。

【0094】

絶縁膜33を成膜した後、ビアホール21の側面21w上に形成された絶縁膜33は、上述した絶縁層32に相当し、第1トレンチ31内に埋設された絶縁膜33は、上述した絶縁層30に相当する。すなわち、ビアホール21の側面21w上に、絶縁層32を形成するとともに、第1トレンチ31内に、絶縁層30を形成する。

【0095】

続いて、半導体基板12の表面10上およびビアホール21内に、スパッタリング法によって、バリアメタル層22を形成する。

【0096】

図16は、第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および半導体基板の表面側に導電層を形成する製造過程の図、(b)は、ビアホール内に、ビアを形成する製造過程の図である。

【0097】

次に、図16(a)に示すように、半導体基板12の表面10上およびビアホール21内に、バリアメタル層22を介して導電層23を形成する。導電層23は、例えば、電解めっき法もしくはプラズマCVDによって形成される。

【0098】

次に、図16(b)に示すように、ビアホール21外に形成された導電層23の余剰部分、および半導体基板12の表面10上に形成されたバリアメタル層22の余剰部分を、CMPによって除去する。これにより、ビアホール21内に、回路部13に接続されるビア20が形成される。回路部13とビア20とは、別途接続用配線によって接続してもよい。

【0099】

図17は、第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、半導体基板の裏面側を研削する製造過程の図である。

【0100】

ビア20を形成した後、図17に示すように、裏面11側の半導体基板12を研削し、ビア20および絶縁層30を裏面11から表出させる。

【0101】

この後、ダイシングライン90に沿って、半導体基板12が個片化される。このような製造過程によっても、半導体チップ1Aを形成することができる。

【0102】

(第6実施形態)

図18は、第6実施形態に係る半導体装置の断面模式図である。

【0103】

図18に示す半導体装置4は、マルチパッケージ型の半導体装置である。図18には、配線基板50上に、一例として半導体チップ1Aが積み重ねられた状態が示されている。配線基板50の下面側には、外部接続端子である半田ボール52が複数個配置されている。

【0104】

半導体装置4には、半導体チップ1Aだけに限らず、半導体チップ1A、1B、2、3のいずれか1つの半導体チップが2つ以上、積み重ねられる。そして、図18に示すように、半導体チップ1Aを積み重ねたとき、それぞれの半導体チップ1Aのビア20どうしは、電極40によって互いに接続される。また、2つ以上の半導体チップ1Aは、封止用樹脂51によって封止されている。

【0105】

以上、具体例を参照しつつ実施形態について説明した。しかし、実施形態はこれらの具体例に限定されるものではない。すなわち、これら具体例に、当業者が適宜設計変更を加えたものも、実施形態の特徴を備えている限り、実施形態の範囲に包含される。前述した各具体例が備える各要素およびその配置、材料、条件、形状、サイズなどは、例示したものに限定されるわけではなく適宜変更することができる。

【0106】

また、前述した各実施形態が備える各要素は、技術的に可能な限りにおいて複合させることができ、これらを組み合わせたものも実施形態の特徴を含む限り実施形態の範囲に包含される。その他、実施形態の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても実施形態の範囲に属するものと了解される。

【0107】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0108】

1A、1B、2、3、100 半導体チップ

4 半導体装置

10 表面

11 裏面

12 半導体基板

21w、31w 側面

13 回路部

13a 回路領域

14 ガードリング機構部

14a 外周領域

20 ビア

21 ビアホール

21b 底面

22、25 バリアメタル層

23 導電層

30、32 絶縁層

30s 空間

31 第1トレンチ

31a 第1の端

31b 第2の端

31s 部分

33 絶縁膜

35 第2トレンチ

40 電極

50 配線基板

51 封止用樹脂

52 半田ボール

85 切断面

90 ダイシングライン

91 レーザ光

【技術分野】

【0001】

本発明の実施形態は、半導体チップ、半導体チップの製造方法、および半導体装置に関する。

【背景技術】

【0002】

近年の半導体デバイスにおいては、マルチチップパッケージ(Multi Chip Package, MCP)等に代表されるように、複数の半導体チップを積層した半導体装置が高密度化、小型化、または薄型化を達成する上で有効に活用されている。

【0003】

この種の半導体装置において半導体チップを積層する際の1つの技術として、貫通ビア(Through Silicon Via, TSV)が注目されている。この貫通ビアとは、例えば、半導体がシリコン(Si)であるときに、半導体チップの基体である半導体基板の主面間を貫通する電極である。この種の半導体装置を製造するプロセスにおいては、スループットの向上、厚さ方向の集積度を増加させるために半導体チップの薄膜化が求められる。半導体チップの薄型化を図るには、例えば、半導体基板の裏面側を研削する手法が採られている。薄膜化された半導体基板をダイシングする際には、チッピングやクラッキングを抑制するために、レーザダイシングまたはプラズマエッチングといった手法が採られる。

【0004】

しかし、この種のダイシングは、ダイシング刃による機械的な加工ではないため、切断面が比較的滑らかに形成される。このため、切断面の金属ゲッタリング効果が低下し、切断面に付着した金属が半導体チップの内部にまで拡散する場合がある。これにより、半導体装置の特性、信頼性が劣化する場合があった。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011−054637号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明が解決しようとする課題は、特性が良好であり、信頼性の高い半導体チップ、半導体チップの製造方法、および半導体装置を提供することである。

【課題を解決するための手段】

【0007】

実施形態の半導体チップは、第1主面と前記第1主面とは反対側の第2主面とを有し、前記第1主面側に、素子および配線が配置された回路部と前記回路部を取り囲むガードリング機構部とが設けられた半導体基板と、前記半導体基板の前記第1主面側から前記第2主面側まで通じるビアホール内に設けられたビアと、前記半導体基板の前記第1主面側から前記第2主面側まで通じる第1トレンチ内に設けられた絶縁層と、を備える。

【0008】

前記半導体基板の前記第1主面に対して垂直な方向からみて、前記ビアホールは、前記回路部が設けられた回路領域に配置されている。前記第1トレンチは、前記回路部を取り囲み前記ガードリング機構部が設けられた外周領域に配置されている。前記第1主面に対して平行な方向における前記第1トレンチの幅は、前記平行な方向における前記ビアホールの幅よりも狭い。

【図面の簡単な説明】

【0009】

【図1】第1実施形態に係る半導体チップのチップ端領域における模式図であり、(a)は、半導体チップの断面模式図、(b)は、半導体チップの裏面側の平面模式図である。

【図2】第1実施形態に係る半導体チップ全体の表面側の平面模式図である。

【図3】第1実施形態の変形例に係る半導体チップの断面模式図である。

【図4】第1実施形態に係る半導体チップの製造過程を説明するための模式図であり、(a)は、半導体チップの表面側に回路部とガードリング機構部とを形成する製造過程を説明するための断面模式図、(b)は、半導体チップのビアホールおよび第1トレンチを形成する製造過程を説明するための断面模式図、(c)は、裏面側の平面模式図である。

【図5】第1実施形態に係る半導体チップの製造過程を説明するための模式図であり、(a)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の断面模式図、(b)は、ビアホール内の絶縁層を加工する製造過程の断面模式図である。

【図6】第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板の裏面側およびビアホール内に導電層を形成する製造過程の図、(b)は、ビアホール内にビアを形成する製造過程の図である。

【図7】第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板にダイシング加工を施す製造過程の図、(b)は、個片化された半導体チップの図である。

【図8】第1実施形態に係る半導体チップの作用を説明するための断面模式図である。

【図9】第2実施形態に係る半導体チップのチップ端領域における裏面側の平面模式図である。

【図10】第3実施形態に係る半導体チップのチップ端領域における断面模式図であり、(a)は、半導体チップが形成された後の状態の断面模式図、(b)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図、(c)は、ビアホール内および第1トレンチ内にバリアメタル層を形成する製造過程の図である。

【図11】第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板を準備する製造過程の図、(b)は、半導体基板内に、ビアホールおよび第1トレンチを形成する製造過程の図である。

【図12】第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および第1トレンチ内に、絶縁層を形成する製造過程の図、(b)は、ビアホール内に、バリアメタル層を形成する製造過程の図である。

【図13】第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および半導体基板の表面側に導電層を形成する製造過程の図、(b)は、ビアホール内に、ビアを形成する製造過程の図である。

【図14】第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板の表面側に素子部およびガードリング機構部を形成する製造過程の図、(b)は、半導体基板の裏面側を研削する製造過程の図である。

【図15】第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板内にビアホールおよび第1トレンチを形成する製造過程の図、(b)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図である。

【図16】第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および半導体基板の表面側に導電層を形成する製造過程の図、(b)は、ビアホール内に、ビアを形成する製造過程の図である。

【図17】第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、半導体基板の裏面側を研削する製造過程の図である。

【図18】第6実施形態に係る半導体装置の断面模式図である。

【発明を実施するための形態】

【0010】

以下、図面を参照しつつ、実施形態について説明する。以下の説明では、同一の部材には同一の符号を付し、一度説明した部材については適宜その説明を省略する。

【0011】

(第1実施形態)

図1は、第1実施形態に係る半導体チップのチップ端領域における模式図であり、(a)は、半導体チップの断面模式図、(b)は、半導体チップの裏面側の平面模式図である。

図2は、第1実施形態に係る半導体チップ全体の表面側の平面模式図である。

図1(a)には、図1(b)のX−X’断面が示されている。図1(b)には、図2のAで示された部分が拡大されて示されている。

【0012】

第1実施形態に係る半導体チップ1Aは、例えば、マルチチップパッケージ型の半導体装置内に収容される。

図1(a)に示すように、半導体チップ1Aは、表面(第1主面)10と、表面10とは反対側の裏面(第2主面)11と、を有する半導体基板12を備える。半導体基板12は、例えば、シリコン基板を薄膜化したものである。例えば、シリコン基板の裏面側を研削することによって、シリコン基板が薄膜化される。

【0013】

半導体基板12は、半導体基板12の表面10側に、素子および配線が配置された回路部13と、回路部13を取り囲むガードリング機構部14と、を設けている。半導体基板12上に設けられた回路部13には、トランジスタ、ダイオード等の能動素子、抵抗、コンデンサ等の受動素子、これらの素子間を接続する配線、メモリセル等が配置されている。回路部13に形成される能動素子の一部は、半導体基板12内に形成されてもよい。回路部13内の配線は、例えば、層間絶縁膜を介して積層されている。回路部13の大部分は、配線が占めている。

【0014】

半導体基板12上に設けられたガードリング機構部14には、例えば、層間絶縁膜内に形成された導電製のガードリングが配置されている。ガードリング機構部14が回路部13の周りに設けられたことにより、ガードリングによってダイシング時の半導体基板12のクラック発生、ダイシング後の回路部13内への水分の拡散が抑制される。

【0015】

半導体チップ1Aを表面(第1主面)10側もしくは裏面(第2主面)11側からみた場合、回路部13が配置された領域を回路領域13a、ガードリング機構部14が配置され、回路領域13aを取り囲む領域を外周領域14aとする。

【0016】

また、半導体チップ1Aは、半導体基板12の表面10側から裏面11側にまで通じるビアホール21内に、ビア20を備える。ビアホール21は、半導体基板12内に少なくとも1つ設けられている。さらに、半導体チップ1Aは、半導体基板12の表面10側から裏面11側にまで通じる第1トレンチ31内に絶縁層30を備える。第1トレンチ31は、半導体基板12内に少なくとも1つ設けられている。

【0017】

ビア20と半導体基板12との間には、絶縁層32が設けられている。絶縁層32は、ビア20と半導体基板12との絶縁性を維持するためのスペーサ部材である。さらに、絶縁層32とビア20との間には、バリアメタル層22が設けられている。ビア20および絶縁層30は、同じ半導体基板12の中に設けられている。第1実施形態では、絶縁層32を第1絶縁層、絶縁層30を第2絶縁層とする。

【0018】

半導体基板12の表面10(もしくは、裏面11)に対して垂直な方向から半導体チップ1Aをみた場合、ビアホール21は、回路領域13aに配置され、第1トレンチ31は、回路領域13aを取り囲む外周領域14aに配置されている(図1(b)参照)。

【0019】

半導体基板12の表面10に対して平行な方向(図のX方向)における第1トレンチ31の幅は、この平行な方向におけるビアホール21の幅よりも狭くなっている。ここで、「幅」とは、図1(b)のX−X’線に沿ったビアホール21の幅、第1トレンチ31の幅で定義される。第1トレンチ31については、その長手方向に対して略垂直な方向を「幅」と定義することもできる。

【0020】

半導体基板12の表面10(もしくは、裏面11)に対して垂直な方向から半導体チップ1Aをみた場合、第1トレンチ31は、連続であり、ループ状になっている。回路領域13aは、第1トレンチ31によって取り囲まれている。これにより、半導体基板12の回路領域13aは、第1トレンチ31によって、第1トレンチ31から外側の半導体基板12から遮断される。

【0021】

第1トレンチ31は、図示するように、端をもたない閉じたループ状の溝でもよく、一部が不連続となった開かれたループ状の溝でもよい。また、半導体基板12の表面10(もしくは、裏面11)に対して垂直な方向から半導体チップ1Aをみた場合、ループ状の第1トレンチ31は、一重であってもよく、二重以上の多重であってもよい。図2には、一例として、二重の第1トレンチ31が表示されている。すなわち、半導体基板12の表面10に対して垂直な方向から半導体基板12をみた場合、第1トレンチ31に設けられた絶縁層30の外側に、この第1トレンチ31を取り囲む別の第1トレンチ31内に絶縁層30がさらに設けられている。

【0022】

半導体基板12の主成分は、例えば、シリコン(Si)である。ビア20の材質は、例えば、銅(Cu)、タングステン(W)、ニッケル(Ni)、ポリシリコンのいずれかである。絶縁層32、30については、その内部における金属拡散長がシリコン結晶内の金属拡散長よりも短い材質が選択される。例えば、絶縁層32、30の材質の具体例としては、窒化シリコン(Si3N4)、炭化シリコン(SiC)、炭窒化シリコン(SiCN)、酸化シリコン(SiO2)の少なくともいずれかが選択される。バリアメタル層22の材質は、例えば、チタン(Ti)、窒化チタン(TiN)等である。

【0023】

図3は、第1実施形態の変形例に係る半導体チップの断面模式図である。

図3には、半導体チップのチップ端領域における断面模式図が示されている。

【0024】

半導体チップ1Bにおいては、第1トレンチ31内の絶縁層30の中央にシーム状の空間30sが形成されている。但し、半導体チップ1Bでは、第1トレンチ31の側面31wが絶縁層30によって覆われている。このような構造の半導体チップ1Bも第1実施形態に含まれる。

【0025】

半導体チップの製造過程について、半導体チップ1Aの製造過程を例に挙げて説明する。

【0026】

図4は、第1実施形態に係る半導体チップの製造過程を説明するための模式図であり、(a)は、半導体チップの表面側に回路部とガードリング機構部とを形成する製造過程を説明するための断面模式図、(b)は、半導体チップのビアホールおよび第1トレンチを形成する製造過程を説明するための断面模式図、(c)は、裏面側の平面模式図である。図4(b)には、図4(c)のX−X’断面が示されている。

【0027】

まず、図4(a)に示すように、半導体基板12の表面10側に、素子および配線が配置された回路部13と、回路部13を取り囲むガードリング機構部14と、を形成する。この段階での半導体基板12は、ダイシング前のウェーハ状態にある。半導体基板12は、裏面11側が研削され、薄膜化がなされる。薄膜化された半導体基板12については、ガラス板等の支持基板によって支持される。

【0028】

続いて、半導体基板12の表裏を180度反転させた後、図4(b)、(c)に示すように、表面10(もしくは、裏面11)に対して垂直な方向からみて、回路部13が形成された回路領域13aの半導体基板12内に、ビアホール21を少なくとも1つ形成する。さらに、ガードリング機構部14を含み、回路領域13aを取り囲む外周領域14aの半導体基板12内に、第1トレンチ31を少なくとも1つ形成する。

【0029】

この段階で、半導体基板12の裏面11から表面10に向かって、回路部13の一部を裏面11側に開放するビアホール21を少なくとも1つ形成するとともに、半導体基板12の裏面11から表面10に向かって、ガードリング機構部14の一部を裏面11側に開放する第1トレンチ31を少なくとも1つ形成する。

【0030】

ビアホール21および第1トレンチ31は、フォトリソグラフィプロセス、エッチングプロセス等を経て、半導体基板12の裏面11側から形成される。

【0031】

また、半導体基板12の表面10に対して平行な方向(図のX方向)における第1トレンチ31の幅を、X方向におけるビアホール21の幅よりも狭く形成する。さらに、図1に示すように、回路領域13aを取り囲むように第1トレンチ31を形成する。

【0032】

図5は、第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図、(b)は、ビアホール内の絶縁層を加工する製造過程の図である。

【0033】

次に、図5(a)に示すように、半導体基板12の裏面11上、ビアホール21内、および第1トレンチ31内に、絶縁層30、32と同じ材質である絶縁膜33を一括で形成する。絶縁膜33は、例えば、段差被覆率が良好なプラズマCVD(Chemical Vapor Deposition)によって形成される。

【0034】

ここで、ビアホール21の幅は、第1トレンチ31の幅よりも広い。従って、絶縁膜33の厚みを適宜調整することにより、第1トレンチ31内は、絶縁膜33によって埋め込まれ、ビアホール21内は、絶縁膜33によって埋め込まれない状態が得られる。

【0035】

例えば、半導体基板12の裏面11上、ビアホール21内、および第1トレンチ31内に、一括して絶縁膜33を形成し始めてから、第1トレンチ31内が絶縁膜33によって埋め込んだ後に、絶縁膜33の成膜を停止する。これにより、第1トレンチ31内は、絶縁膜33によって埋め込まれるが、ビアホール21内は、絶縁膜33によって埋め込まれない構造が得られる。ビアホール21の側面21w上に形成された絶縁膜33の厚みは、一例として、第1トレンチ31の幅のおよそ半分になる。

【0036】

絶縁膜33を成膜した後、ビアホール21の側面21w上に形成された絶縁膜33は、上述した絶縁層32に相当し、第1トレンチ31内に埋設された絶縁膜33は、上述した絶縁層30に相当する。

【0037】

次に、図5(b)に示すように、RIE(Reactive Ion Etching)等の異方性エッチングによって、ビアホール21の底面21b上に堆積した絶縁膜33を選択的に除去する。また、半導体基板12の裏面11上に形成された絶縁膜33については、必要に応じて除去する。これにより、ビアホール21の側面21w上に、絶縁層32が設けられる。また、第1トレンチ31内には、絶縁層30が設けられる。

【0038】

図6は、第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板の裏面上およびビアホール内に導電層を形成する製造過程の図、(b)は、ビアホール内にビアを形成する製造過程の図である。

【0039】

次に、図6(a)に示すように、半導体基板12の裏面11上およびビアホール21内に、スパッタリング法によって、バリアメタル層22を形成する。

【0040】

続いて、半導体基板12の裏面11上およびビアホール21内に、バリアメタル層22を介して導電層23を形成する。導電層23は、例えば、電解めっき法もしくはプラズマCVDによって形成される。

【0041】

ビアホール21の底面21b上に堆積した絶縁膜33は、既に取り除かれているので、導電層23と回路部13とが接触する。

【0042】

次に、図6(b)に示すように、ビアホール21外に形成された導電層23の余剰部分、および半導体基板12の裏面11上に形成されたバリアメタル層22の余剰部分を、CMP(Chemical Mechanical Polishing)によって除去する。これにより、ビアホール21内に、回路部13に接続されたビア20が形成される。

【0043】

図7は、第1実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板にダイシング加工を施す製造過程の図、(b)は、個片化された半導体チップの図である。

【0044】

次に、図7(a)に示すように、半導体基板12にダイシング加工を施す。第1実施形態では、ダイシング時の半導体基板12のチッピングやクラックを防止するために、レーザダイシングによって、半導体基板12を分割する。例えば、ダイシングライン90に沿って、レーザ光91を半導体基板12に照射する。レーザダイシングの代わりに、プラズマエッチングによって半導体基板12を分割してもよい。これにより、半導体基板12が個片化されて、半導体チップ1Aが形成される。この状態を、図7(b)に示す。

【0045】

この後、個片化された半導体チップ1Aは、その複数個が積層されて、封止用樹脂によって封止される。これにより、マルチチップパッケージ型の半導体装置が形成される(後述)。封止用樹脂として熱硬化性の樹脂を用いた場合は、半導体チップ1Aが封止される際に半導体チップ1Aが加熱される。

【0046】

また、成膜条件によっては、絶縁層30内に、上述したシーム状の空間30sが生成する場合がある。この場合には、半導体チップ1Aに代わり、半導体チップ1Bが形成される。

【0047】

図8は、第1実施形態に係る半導体チップの作用を説明するための断面模式図である。

図8(a)には、半導体チップ1Aが示されている。図8(b)には、半導体チップ1Bが示されている。

【0048】

半導体チップ1A、1Bによれば、回路部13がリング状の第1トレンチ31によって取り囲まれている。半導体チップ1Aでは、トレンチ31内に絶縁層30が設けられている。半導体チップ1Bでは、第1トレンチ31の側面31wが絶縁層30によって覆われている。

【0049】

ガードリング機構部14は、金属製のガードリングを有する。このため、ダイシングライン90に沿って、半導体基板12を切断すると、切断面85にガードリングの金属成分が付着する場合がある。付着した金属は、汚染金属源になる可能性がある。

【0050】

切断面85は、レーザダイシングもしくはプラズマエッチングによって形成される。この切断は、ダイシング刃による機械的なダイシング加工ではないため、切断面85は、比較的滑らかに形成される。このため、切断面85は、汚染金属のゲッタリング機能を充分に持たない場合がある。そして、この切断面85に、上述したように、ガードリング中の金属成分が付着する場合がある。

【0051】

しかし、半導体チップ1A、1Bでは、ダイシング後において、半導体チップが加熱されたり、半導体チップ自体が温まったとしても、絶縁層30によって、半導体チップ内への汚染金属の熱拡散が抑制される。すなわち、汚染金属が拡散する様子を矢印dで表すと、この矢印dで示すように、絶縁層30がバリア層となって、汚染金属の半導体チップ内への熱拡散が抑制される。これにより、半導体チップ1A、1Bでは、特性劣化、信頼性劣化が起き難くなる。

【0052】

また、絶縁層30の材質は、窒化シリコン(Si3N4)、炭化シリコン(SiC)、炭窒化シリコン(SiCN)、酸化シリコン(SiO2)の少なくともいずれかである。このような材質の線膨張係数は、ビア20を構成する材質(例えば、銅(Cu))の線膨張係数よりも小さい。

【0053】

仮に、第1トレンチ31内に、銅(Cu)等の金属層を埋設してしまうと、金属層の線膨張係数と半導体基板12の線膨張係数との差が大きくなる。このため、半導体チップを積層したり、封止用樹脂によって封止する際に、半導体チップに過剰な応力が印加される。これにより、半導体チップにクラックが生じたり、半導体チップ自体が変形したりする。

【0054】

これに対し、半導体チップ1A、1Bでは、第1トレンチ31内に、絶縁層30を設けている。絶縁層30の線膨張係数と半導体基板12の線膨張係数との差は、金属層の線膨張係数と半導体基板12の線膨張係数との差よりも小さい。このため、半導体チップ1A、1Bを積層する際、もしくは半導体チップ1A、1Bを封止用樹脂によって封止する際には、応力が緩和される。これにより、半導体チップ1A、1Bにはクラックが発生し難く、さらに、半導体チップ1A、1Bは、変形し難くなる。

【0055】

また、半導体チップ1A、1Bでは、ビアホール21内の側面21w上に絶縁層32を形成すると同時に、第1トレンチ31内に絶縁層30を形成している。これは、第1トレンチ31の幅がビアホール21の幅よりも狭いがために達成し得る。

【0056】

換言すれば、半導体チップ1A、1Bでは、チップ全体面積に対する絶縁層30の面積の割合をより小さくすることができる。その結果、半導体チップ1A、1Bでは、回路部13の面積比率を増加させることができる。

【0057】

仮に、第1トレンチ31内を金属層で構成すると、この金属層と第1トレンチ31との間に、バリアメタル層が必要になる。このバリアメタル層は、金属層中の金属成分が半導体基板中へ拡散するのを防止するために必然の部材になる。従って、第1トレンチ31の幅は必然的に広くなり、回路部13の面積比率の増加に限界が生じてしまう。あるいは、第1トレンチ31内の金属層がチップ外部から吸収された水分によって劣化する可能性もある。その結果、第1トレンチ31内の金属層自体が汚染金属源になる可能性がある。

【0058】

これに対し、半導体チップ1A、1Bでは、第1トレンチ31内に絶縁層30を形成している。このため、第1トレンチ31内が汚染金属源になることはない。

【0059】

このように、第1実施形態によれば、特性が良好であり、信頼性の高い半導体チップが形成される。

【0060】

(第2実施形態)

図9は、第2実施形態に係る半導体チップのチップ端領域における裏面側の平面模式図であり、(a)は、半導体チップの裏面側の全体図、(b)は、(a)のA部分の拡大図である。

【0061】

半導体チップ2では、半導体基板12の表面10に対して垂直な方向から半導体基板12をみた場合、外周領域14aの半導体基板12に、第1トレンチ31を挟んで、回路領域13a側の半導体基板12と、回路領域13aとは反対側の半導体基板12と、が連続する部分31sがある。すなわち、半導体チップ2においては、回路領域13aを取り囲む第1トレンチ31のが不連続になっている。この不連続部分を部分31sとしている。

【0062】

半導体チップ2においては、部分31sが第1トレンチ31の第1の端31aと、第1トレンチ31の第2の端31bと、によって挟まれている。また、部分31sにおいて、第1トレンチ31の第1の端31aと、第1トレンチ31の第2の端31bと、が互いに対向している。半導体チップ2では、第1の端31aもしくは第2の端31bからさらに第2トレンチ35が延在している。そして、第1トレンチ31と第2トレンチ35とが半導体基板12を介して互いに対向している。第1トレンチ31の外側には、第1の端31aもしくは第2の端31bから延在された第2トレンチ35がさらに配置されている。第2トレンチ内には、絶縁層30が設けられている。

【0063】

例えば、図9(b)には、第1トレンチ31の回路領域13a側の半導体基板12とは反対側の半導体基板12内に、第2の端31bから延在された第2トレンチ35が設けられた状態が示されている。第1トレンチ31と第2トレンチ35とは、およそ平行に延在している。

【0064】

第2トレンチ35については、第1の端31aから延在してもよい。また、第1トレンチ31の回路領域13a側の半導体基板12内に第2トレンチ35を設けてもよい。

【0065】

このような構造であれば、半導体チップ2を外周領域14aから回路領域13aをみた場合、部分31sが第2トレンチ35によって、遮蔽される。すなわち、第1トレンチ31の一部が不連続になっても、第2トレンチ35の存在によって汚染金属の拡散経路が迷路のように長くなる。従って、半導体チップ2は、汚染金属に対して高いバリア性を有する。なお、Aに示す箇所は1箇所である必要はなく、複数箇所であってもよい。

【0066】

また、半導体チップ2においては、第1トレンチ31の回路領域13a側から部分31sを介して第1トレンチ31の外周にまで半導体基板12が連続する部分がある。従って、半導体チップ2の外周領域14aの強度はより増加する。

【0067】

(第3実施形態)

図10は、第3実施形態に係る半導体チップのチップ端領域における断面模式図であり、(a)は、半導体チップが形成された後の状態の断面模式図、(b)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図、(c)は、ビアホール内および第1トレンチ内にバリアメタル層を形成する製造過程の図である。

【0068】

図10(a)に示す半導体チップ3においては、絶縁層30内に、バリアメタル層25がさらに狭入されている。すなわち、バリアメタル層25が絶縁層30によって挟まれている。半導体チップ3においては、第1トレンチ31の幅が半導体チップ1Aの第1トレンチ31よりも拡げられている。そして、第1トレンチ31内に、絶縁層30とバリアメタル層25とが埋め込まれている。換言すれば、第1トレンチ31内では、X方向において絶縁層30/バリアメタル層25/絶縁層30の積層膜が形成されている。バリアメタル層25の材質は、例えば、チタン(Ti)である。

【0069】

半導体チップ3の製造過程は、以下の手順により行われる。

例えば、図10(b)に示すように、ビアホール21の側面21w上に、絶縁層32を形成し、第1トレンチ31内に、絶縁層30を形成する、ここでは、第1トレンチ31内が第2絶縁層30によって埋め込まれない状態で、絶縁膜33の形成を停止する。

【0070】

次に、図10(c)に示すように、ビアホール21内に、絶縁層32を介してバリアメタル層22を形成し、第1トレンチ31内に、絶縁層30を介してバリアメタル層25を形成する。この後は、図6(a)以降で説明した製造プロセスを実施する。これにより、半導体チップ3が形成される。

【0071】

このような構造によれば、第1トレンチ31内に絶縁層30のほか、バリアメタル層25が設けられたので、汚染金属に対するバリア性がさらに向上する。また、第1トレンチ31の幅を拡げたことにより、絶縁層30の種類の選択の自由度、絶縁層30の膜厚の選択の自由度が増加する。

【0072】

(第4実施形態)

図11は、第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板を準備する製造過程の図、(b)は、半導体基板内に、ビアホールおよび第1トレンチを形成する製造過程の図である。

【0073】

図11(a)に示すように、表面10と表面10とは反対側の裏面11とを有する半導体基板12を準備する。半導体基板12は、ダイシング前のウェーハ状態にある。

【0074】

次に、図11(b)に示すように、半導体基板12の表面10側に形成される回路領域13aに、表面10から裏面11に向かって半導体基板12内にビアホール21を少なくとも1つ形成する。さらに、回路領域13aを取り囲む外周領域14aに、表面10から裏面11に向かって半導体基板12内に第1トレンチ31を少なくとも1つ形成する。ビアホール21および第1トレンチ31は、例えば、フォトリソグラフィプロセス、エッチングプロセスを経て形成される。また、表面10に対して平行な方向(X方向)における第1トレンチ31の幅を、表面10に対して平行な方向におけるビアホール21の幅よりも狭く形成する。また、回路領域13aを取り囲むように第1トレンチ31を形成する。

【0075】

図12は、第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および第1トレンチ内に、絶縁層を形成する製造過程の図、(b)は、ビアホール内に、バリアメタル層を形成する製造過程の図である。

【0076】

次に、図12(a)に示すように、半導体基板12の表面10上、ビアホール21内、および第1トレンチ31内に、絶縁層30、32と同じ材質である絶縁膜33をプラズマCVDによって一括で形成する。

【0077】

ここで、ビアホール21の幅は、第1トレンチ31の幅よりも広い。従って、絶縁膜33の厚みを適宜調整することにより、第1トレンチ31内は、絶縁膜33によって埋め込まれ、ビアホール21内は、絶縁膜33によって埋め込まれない状態が得られる。

【0078】

例えば、半導体基板12の表面10上、ビアホール21内、および第1トレンチ31内に、一括して絶縁膜33を形成し始めてから、第1トレンチ31内が絶縁膜33によって埋め込んだ後に、絶縁膜33の成膜を停止する。これにより、第1トレンチ31内は、絶縁膜33によって埋め込まれるが、ビアホール21内は、絶縁膜33によって埋め込まれない構造が得られる。ビアホール21の側面21w上に形成された絶縁膜33の厚みは、第1トレンチ31の幅のおよそ半分になる。

【0079】

絶縁膜33を成膜した後、ビアホール21の側面21w上に形成された絶縁膜33は、上述した絶縁層32に相当し、第1トレンチ31内に埋設された絶縁膜33は、上述した絶縁層30に相当する。すなわち、ビアホール21の側面21w上に、絶縁層32を形成するとともに、第1トレンチ31内に、絶縁層30を形成する。

【0080】

次に、図12(b)に示すように、半導体基板12の表面10上およびビアホール21内に、スパッタリング法によって、バリアメタル層22を形成する。

【0081】

図13は、第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および半導体基板の表面側に導電層を形成する製造過程の図、(b)は、ビアホール内に、ビアを形成する製造過程の図である。

【0082】

次に、図13(a)に示すように、半導体基板12の表面10上およびビアホール21内に、バリアメタル層22を介して導電層23を形成する。導電層23は、例えば、電解めっき法もしくはプラズマCVDによって形成される。

【0083】

次に、図13(b)に示すように、ビアホール21外に形成された導電層23の余剰部分、および半導体基板12の表面10上に形成されたバリアメタル層22の余剰部分を、CMPによって除去する。これにより、ビアホール21内に、回路部13に接続可能なビア20が形成される。

【0084】

図14は、第4実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板の表面側に素子部およびガードリング機構部を形成する製造過程の図、(b)は、半導体基板の裏面側を研削する製造過程の図である。

【0085】

次に、図14(a)に示すように、半導体基板12の表面10側の回路領域13aに、素子および配線を含む回路部13を形成し、外周領域14aに、ガードリング機構部を形成する。

【0086】

次に、図14(b)に示すように、裏面11側の半導体基板12を研削し、ビア20および絶縁層30を裏面11から表出させる。

【0087】

この後、ダイシングライン90に沿って、半導体基板12が個片化される。このような製造過程によっても、半導体チップ1Aを形成することができる。

【0088】

(第5実施形態)

図15は、第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、半導体基板内にビアホールおよび第1トレンチを形成する製造過程の図、(b)は、ビアホール内および第1トレンチ内に絶縁層を形成する製造過程の図である。

【0089】

図15(a)に示すように、表面10側において、回路部13と、回路部13を取り囲むガードリング機構部14と、が設けられた半導体基板12を準備した後、半導体基板12の表面10から裏面11に向かって、回路部13の一部にまで通じ、回路部13のその一部の下の半導体基板12の内部にまで延在するビアホール21を少なくとも1つ形成する。さらに、ガードリング機構部14の一部にまで通じ、ガードリング機構部14のその一部の下の半導体基板12の内部にまで延在する第1トレンチ31を少なくとも1つ形成する。

【0090】

ビアホール21および第1トレンチ31は、フォトリソグラフィプロセス、エッチングプロセス等を経て、半導体基板12の表面10側から形成される。また、半導体基板12の表面10に対して平行な方向(図のX方向)における第1トレンチ31の幅を、X方向におけるビアホール21の幅よりも狭く形成する。また、回路領域13aを取り囲むように第1トレンチ31を形成する。

【0091】

次に、図15(b)に示すように、半導体基板12の表面10上、ビアホール21内、および第1トレンチ31内に、絶縁層30、32と同じ材質である絶縁膜33をプラズマCVDによって一括で形成する。

【0092】

ここで、ビアホール21の幅は、第1トレンチ31の幅よりも広い。従って、絶縁膜33の厚みを適宜調整することにより、第1トレンチ31内は、絶縁膜33によって埋め込まれ、ビアホール21内は、絶縁膜33によって埋め込まれない状態が得られる。

【0093】

例えば、半導体基板12の表面10上、ビアホール21内、および第1トレンチ31内に、一括して絶縁膜33を形成し始めてから、第1トレンチ31内が絶縁膜33によって埋め込んだ後に、絶縁膜33の成膜を停止する。これにより、第1トレンチ31内は、絶縁膜33によって埋め込まれるが、ビアホール21内は、絶縁膜33によって埋め込まれない構造が得られる。ビアホール21の側面21w上に形成された絶縁膜33の厚みは、第1トレンチ31の幅のおよそ半分になる。

【0094】

絶縁膜33を成膜した後、ビアホール21の側面21w上に形成された絶縁膜33は、上述した絶縁層32に相当し、第1トレンチ31内に埋設された絶縁膜33は、上述した絶縁層30に相当する。すなわち、ビアホール21の側面21w上に、絶縁層32を形成するとともに、第1トレンチ31内に、絶縁層30を形成する。

【0095】

続いて、半導体基板12の表面10上およびビアホール21内に、スパッタリング法によって、バリアメタル層22を形成する。

【0096】

図16は、第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、(a)は、ビアホール内および半導体基板の表面側に導電層を形成する製造過程の図、(b)は、ビアホール内に、ビアを形成する製造過程の図である。

【0097】

次に、図16(a)に示すように、半導体基板12の表面10上およびビアホール21内に、バリアメタル層22を介して導電層23を形成する。導電層23は、例えば、電解めっき法もしくはプラズマCVDによって形成される。

【0098】

次に、図16(b)に示すように、ビアホール21外に形成された導電層23の余剰部分、および半導体基板12の表面10上に形成されたバリアメタル層22の余剰部分を、CMPによって除去する。これにより、ビアホール21内に、回路部13に接続されるビア20が形成される。回路部13とビア20とは、別途接続用配線によって接続してもよい。

【0099】

図17は、第5実施形態に係る半導体チップの製造過程を説明するための断面模式図であり、半導体基板の裏面側を研削する製造過程の図である。

【0100】

ビア20を形成した後、図17に示すように、裏面11側の半導体基板12を研削し、ビア20および絶縁層30を裏面11から表出させる。

【0101】

この後、ダイシングライン90に沿って、半導体基板12が個片化される。このような製造過程によっても、半導体チップ1Aを形成することができる。

【0102】

(第6実施形態)

図18は、第6実施形態に係る半導体装置の断面模式図である。

【0103】

図18に示す半導体装置4は、マルチパッケージ型の半導体装置である。図18には、配線基板50上に、一例として半導体チップ1Aが積み重ねられた状態が示されている。配線基板50の下面側には、外部接続端子である半田ボール52が複数個配置されている。

【0104】

半導体装置4には、半導体チップ1Aだけに限らず、半導体チップ1A、1B、2、3のいずれか1つの半導体チップが2つ以上、積み重ねられる。そして、図18に示すように、半導体チップ1Aを積み重ねたとき、それぞれの半導体チップ1Aのビア20どうしは、電極40によって互いに接続される。また、2つ以上の半導体チップ1Aは、封止用樹脂51によって封止されている。

【0105】

以上、具体例を参照しつつ実施形態について説明した。しかし、実施形態はこれらの具体例に限定されるものではない。すなわち、これら具体例に、当業者が適宜設計変更を加えたものも、実施形態の特徴を備えている限り、実施形態の範囲に包含される。前述した各具体例が備える各要素およびその配置、材料、条件、形状、サイズなどは、例示したものに限定されるわけではなく適宜変更することができる。

【0106】

また、前述した各実施形態が備える各要素は、技術的に可能な限りにおいて複合させることができ、これらを組み合わせたものも実施形態の特徴を含む限り実施形態の範囲に包含される。その他、実施形態の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても実施形態の範囲に属するものと了解される。

【0107】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0108】

1A、1B、2、3、100 半導体チップ

4 半導体装置

10 表面

11 裏面

12 半導体基板

21w、31w 側面

13 回路部

13a 回路領域

14 ガードリング機構部

14a 外周領域

20 ビア

21 ビアホール

21b 底面

22、25 バリアメタル層

23 導電層

30、32 絶縁層

30s 空間

31 第1トレンチ

31a 第1の端

31b 第2の端

31s 部分

33 絶縁膜

35 第2トレンチ

40 電極

50 配線基板

51 封止用樹脂

52 半田ボール

85 切断面

90 ダイシングライン

91 レーザ光

【特許請求の範囲】

【請求項1】

第1主面と前記第1主面とは反対側の第2主面とを有し、前記第1主面側に、素子および配線が配置された回路部と前記回路部を取り囲むガードリング機構部とが設けられた半導体基板と、

前記半導体基板の前記第1主面側から前記第2主面側にまで通じるビアホール内に設けられたビアと、

前記半導体基板の前記第1主面側から前記第2主面側にまで通じる第1トレンチ内に設けられた絶縁層と、

を備え、

前記半導体基板の前記第1主面に対して垂直な方向からみて、

前記ビアホールは、前記回路部が設けられた回路領域に配置され、

前記第1トレンチは、前記回路部を取り囲み前記ガードリング機構部が設けられた外周領域に配置され、

前記第1主面に対して平行な方向における前記第1トレンチの幅は、前記平行な方向における前記ビアホールの幅よりも狭いことを特徴とする半導体チップ。

【請求項2】

前記半導体基板の前記第1主面に対して垂直な方向からみて、前記回路領域は、前記第1トレンチによって取り囲まれていることを特徴とする請求項1記載の半導体チップ。

【請求項3】

前記半導体基板の前記第1主面に対して垂直な方向からみて、前記第1トレンチに設けられた前記絶縁層の外側に、前記第1トレンチを取り囲む別の第1トレンチ内に設けられた絶縁層をさらに備えたことを特徴とする請求項1または2に記載の半導体チップ。

【請求項4】

前記半導体基板の前記第1主面に対して垂直な方向からみて、前記外周領域の前記半導体基板に、前記第1トレンチを挟んで、前記回路領域側の前記半導体基板と、前記回路領域とは反対側の前記半導体基板と、が連続する部分があり、

前記部分は、前記第1トレンチの第1の端と、前記第1トレンチの第2の端と、によって挟まれ、

前記第1トレンチの外側に、前記第1の端もしくは前記第2の端から延在された第2トレンチ内に設けられた絶縁層をさらに備えたことを特徴とする請求項1〜3のいずれか1つに記載の半導体チップ。

【請求項5】

前記絶縁層内に狭入されたバリアメタル層をさらに備えたことを特徴とする請求項1〜4のいずれか1つに記載の半導体チップ。

【請求項6】

前記絶縁層の材質は、窒化シリコン(Si3N4)、炭化シリコン(SiC)、炭窒化シリコン(SiCN)、酸化シリコン(SiO2)の少なくともいずれかを含むことを特徴とする請求項1〜5のいずれか1つに記載の半導体チップ。

【請求項7】

第1主面と前記第1主面とは反対側の第2主面とを有し、前記第1主面側に、素子および配線が配置された回路部と前記回路部を取り囲むガードリング機構部とが設けられた半導体基板を準備する工程と、

前記第1主面に対して垂直な方向からみて、前記回路部が形成された回路領域の前記半導体基板内に、ビアホールを形成し、前記回路領域を取り囲み、前記ガードリング機構部を有する外周領域の前記半導体基板内に、第1トレンチを形成するとともに、前記第1主面に対して平行な方向における前記第1トレンチの幅を前記平行な方向における前記ビアホールの幅よりも狭く形成する工程と、

前記ビアホールの側面上に、第1絶縁層を形成するとともに、前記第1トレンチ内に、第2絶縁層を形成する工程と、

前記ビアホール内に、前記回路部に接続されるビアを形成する工程と、

を備えたことを特徴とする半導体チップの製造方法。

【請求項8】

前記半導体基板の前記第2主面から前記第1主面に向かって、前記回路部の一部を前記第2主面側に開放する前記ビアホールを形成するとともに、前記半導体基板の前記第2主面から前記第1主面に向かって、前記ガードリング機構部の一部を前記第2主面側に開放する前記第1トレンチを形成することを特徴とする請求項7記載の半導体チップの製造方法。

【請求項9】

前記半導体基板の前記第1主面から前記第2主面に向かって、前記回路部の一部に通じ、前記回路部の前記一部の下の前記半導体基板の内部にまで延在する前記ビアホールを形成するとともに、前記ガードリング機構部の一部に通じ、前記ガードリング機構部の前記一部の下の前記半導体基板の内部にまで延在する前記第1トレンチを形成することを特徴とする請求項7記載の半導体チップの製造方法。

【請求項10】

前記ビアを形成した後、前記第2主面側の前記半導体基板を研削し、前記ビアおよび前記絶縁層を前記第2主面から表出させることを特徴とする請求項9記載の半導体チップの製造方法。

【請求項11】

第1主面と前記第1主面とは反対側の第2主面とを有する半導体基板を準備する工程と、

前記半導体基板の第1主面側に形成される回路領域において、前記第1主面から前記第2主面に向かって前記半導体基板内にビアホールを形成し、前記回路領域を取り囲む外周領域において、前記第1主面から前記第2主面に向かって前記半導体基板内に第1トレンチを形成するとともに、前記第1主面に対して平行な方向における前記第1トレンチの幅を前記平行な方向における前記ビアホールの幅よりも狭く形成する工程と、

前記ビアホールの側面上に、第1絶縁層を形成するとともに、前記第1トレンチ内に、第2絶縁層を形成する工程と、

前記ビアホール内に、前記回路部に接続可能なビアを形成する工程と、

前記半導体基板の前記回路領域に、素子および配線を含む回路部を形成し、前記半導体基板の前記外周領域に、ガードリング機構部を形成する工程と、

前記第2主面側の前記半導体基板を研削し、前記ビアおよび前記絶縁層を前記第2主面から表出させる工程と、

を備えたことを特徴とする半導体チップの製造方法。

【請求項12】

前記ビアホールの側面上に、前記第1絶縁層を形成し、前記第1トレンチ内に、第2絶縁層を形成した後、

前記ビアホール内に、前記第1絶縁層を介して第1バリアメタル層を形成し、前記第1トレンチ内に、前記第2絶縁層を介して第2バリアメタル層を形成することを特徴とする請求項7〜11のいずれか1つに記載の半導体チップの製造方法。

【請求項13】

請求項1〜6のいずれか1つの半導体チップが2つ以上に積み重なり、

2つ以上の前記半導体チップが封止用樹脂によって封止されていることを特徴とする半導体装置。

【請求項1】

第1主面と前記第1主面とは反対側の第2主面とを有し、前記第1主面側に、素子および配線が配置された回路部と前記回路部を取り囲むガードリング機構部とが設けられた半導体基板と、

前記半導体基板の前記第1主面側から前記第2主面側にまで通じるビアホール内に設けられたビアと、

前記半導体基板の前記第1主面側から前記第2主面側にまで通じる第1トレンチ内に設けられた絶縁層と、

を備え、

前記半導体基板の前記第1主面に対して垂直な方向からみて、

前記ビアホールは、前記回路部が設けられた回路領域に配置され、

前記第1トレンチは、前記回路部を取り囲み前記ガードリング機構部が設けられた外周領域に配置され、

前記第1主面に対して平行な方向における前記第1トレンチの幅は、前記平行な方向における前記ビアホールの幅よりも狭いことを特徴とする半導体チップ。

【請求項2】

前記半導体基板の前記第1主面に対して垂直な方向からみて、前記回路領域は、前記第1トレンチによって取り囲まれていることを特徴とする請求項1記載の半導体チップ。

【請求項3】

前記半導体基板の前記第1主面に対して垂直な方向からみて、前記第1トレンチに設けられた前記絶縁層の外側に、前記第1トレンチを取り囲む別の第1トレンチ内に設けられた絶縁層をさらに備えたことを特徴とする請求項1または2に記載の半導体チップ。

【請求項4】

前記半導体基板の前記第1主面に対して垂直な方向からみて、前記外周領域の前記半導体基板に、前記第1トレンチを挟んで、前記回路領域側の前記半導体基板と、前記回路領域とは反対側の前記半導体基板と、が連続する部分があり、

前記部分は、前記第1トレンチの第1の端と、前記第1トレンチの第2の端と、によって挟まれ、

前記第1トレンチの外側に、前記第1の端もしくは前記第2の端から延在された第2トレンチ内に設けられた絶縁層をさらに備えたことを特徴とする請求項1〜3のいずれか1つに記載の半導体チップ。

【請求項5】

前記絶縁層内に狭入されたバリアメタル層をさらに備えたことを特徴とする請求項1〜4のいずれか1つに記載の半導体チップ。

【請求項6】

前記絶縁層の材質は、窒化シリコン(Si3N4)、炭化シリコン(SiC)、炭窒化シリコン(SiCN)、酸化シリコン(SiO2)の少なくともいずれかを含むことを特徴とする請求項1〜5のいずれか1つに記載の半導体チップ。

【請求項7】

第1主面と前記第1主面とは反対側の第2主面とを有し、前記第1主面側に、素子および配線が配置された回路部と前記回路部を取り囲むガードリング機構部とが設けられた半導体基板を準備する工程と、

前記第1主面に対して垂直な方向からみて、前記回路部が形成された回路領域の前記半導体基板内に、ビアホールを形成し、前記回路領域を取り囲み、前記ガードリング機構部を有する外周領域の前記半導体基板内に、第1トレンチを形成するとともに、前記第1主面に対して平行な方向における前記第1トレンチの幅を前記平行な方向における前記ビアホールの幅よりも狭く形成する工程と、

前記ビアホールの側面上に、第1絶縁層を形成するとともに、前記第1トレンチ内に、第2絶縁層を形成する工程と、

前記ビアホール内に、前記回路部に接続されるビアを形成する工程と、

を備えたことを特徴とする半導体チップの製造方法。

【請求項8】

前記半導体基板の前記第2主面から前記第1主面に向かって、前記回路部の一部を前記第2主面側に開放する前記ビアホールを形成するとともに、前記半導体基板の前記第2主面から前記第1主面に向かって、前記ガードリング機構部の一部を前記第2主面側に開放する前記第1トレンチを形成することを特徴とする請求項7記載の半導体チップの製造方法。

【請求項9】

前記半導体基板の前記第1主面から前記第2主面に向かって、前記回路部の一部に通じ、前記回路部の前記一部の下の前記半導体基板の内部にまで延在する前記ビアホールを形成するとともに、前記ガードリング機構部の一部に通じ、前記ガードリング機構部の前記一部の下の前記半導体基板の内部にまで延在する前記第1トレンチを形成することを特徴とする請求項7記載の半導体チップの製造方法。

【請求項10】

前記ビアを形成した後、前記第2主面側の前記半導体基板を研削し、前記ビアおよび前記絶縁層を前記第2主面から表出させることを特徴とする請求項9記載の半導体チップの製造方法。

【請求項11】

第1主面と前記第1主面とは反対側の第2主面とを有する半導体基板を準備する工程と、

前記半導体基板の第1主面側に形成される回路領域において、前記第1主面から前記第2主面に向かって前記半導体基板内にビアホールを形成し、前記回路領域を取り囲む外周領域において、前記第1主面から前記第2主面に向かって前記半導体基板内に第1トレンチを形成するとともに、前記第1主面に対して平行な方向における前記第1トレンチの幅を前記平行な方向における前記ビアホールの幅よりも狭く形成する工程と、

前記ビアホールの側面上に、第1絶縁層を形成するとともに、前記第1トレンチ内に、第2絶縁層を形成する工程と、

前記ビアホール内に、前記回路部に接続可能なビアを形成する工程と、

前記半導体基板の前記回路領域に、素子および配線を含む回路部を形成し、前記半導体基板の前記外周領域に、ガードリング機構部を形成する工程と、

前記第2主面側の前記半導体基板を研削し、前記ビアおよび前記絶縁層を前記第2主面から表出させる工程と、

を備えたことを特徴とする半導体チップの製造方法。

【請求項12】

前記ビアホールの側面上に、前記第1絶縁層を形成し、前記第1トレンチ内に、第2絶縁層を形成した後、

前記ビアホール内に、前記第1絶縁層を介して第1バリアメタル層を形成し、前記第1トレンチ内に、前記第2絶縁層を介して第2バリアメタル層を形成することを特徴とする請求項7〜11のいずれか1つに記載の半導体チップの製造方法。

【請求項13】

請求項1〜6のいずれか1つの半導体チップが2つ以上に積み重なり、

2つ以上の前記半導体チップが封止用樹脂によって封止されていることを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−4863(P2013−4863A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−136449(P2011−136449)

【出願日】平成23年6月20日(2011.6.20)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月20日(2011.6.20)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]