半導体チップおよび半導体パッケージ

【課題】複数の電極パッド間の短絡を確実に防止することができ、従来に比べて信頼性の高い半導体チップおよびそれを備える半導体パッケージを提供すること。

【解決手段】半導体基板11と、半導体基板11上に形成された層間絶縁膜12と、層間絶縁膜12上に形成された複数の電極パッド9と、層間絶縁膜12上に形成されたポリイミドからなる表面保護膜14であって、各電極パッド9を露出させるパッド開口22が形成された表面保護膜14とを含む半導体パッケージ1において、表面保護膜14において隣り合う電極パッド9の間に、当該隣り合う電極パッド9が同一のポリイミドに接しないように、表面保護膜14を選択的に除去したスリット開口23を形成する。

【解決手段】半導体基板11と、半導体基板11上に形成された層間絶縁膜12と、層間絶縁膜12上に形成された複数の電極パッド9と、層間絶縁膜12上に形成されたポリイミドからなる表面保護膜14であって、各電極パッド9を露出させるパッド開口22が形成された表面保護膜14とを含む半導体パッケージ1において、表面保護膜14において隣り合う電極パッド9の間に、当該隣り合う電極パッド9が同一のポリイミドに接しないように、表面保護膜14を選択的に除去したスリット開口23を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ポリイミドからなる表面保護膜を備える半導体チップおよび当該半導体チップを備える半導体パッケージに関する。

【背景技術】

【0002】

従来、耐熱性、機械強度、化学安定性および絶縁性に優れるポリイミド膜が最上層保護膜として形成された半導体チップ、および当該半導体チップを備える半導体装置が知られている。

たとえば、特許文献1の半導体装置は、複数のボンディングパッドが表面に形成された下段側半導体チップと、下段側半導体チップの表面に形成され、ボンディングパッドを露出させる開口部が形成されたポリイミド膜と、下段側半導体チップ上にマイクロバンプを介して積層された上段側半導体チップと、下段側半導体チップと上段側半導体チップのギャップに充填されたアンダーフィル樹脂と、アンダーフィル樹脂の流出を防止するために下段側半導体チップの表面に形成されたAg等からなるダムと、下段側半導体チップが接続された配線基板と、配線基板の接続パッドと下段側半導体チップのボンディングパッドとを接続するボンディングワイヤと、下段側半導体チップ、上段側半導体チップおよびボンディングワイヤを封止するモールド樹脂と、配線基板の裏面に形成された外部接続端子とを含む。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011−71381号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1の半導体装置では、半導体チップをモールド樹脂で封入したときに、モールド樹脂あるいはポリイミド膜自身の応力等により、ポリイミド膜と下段側半導体チップとの間にすき間が発生する場合がある。このすき間に水分が侵入すると、たとえばダム中のAgが、水分と反応してマイグレーションを起こし、ポリイミド膜中の微小な空孔に水分と共に吸い込まれる。すると、ポリイミド膜におけるAgが吸い込まれた部分が導電性を示すため、当該導電性部分により隣り合うボンディングパッド間が短絡され、場合によっては、半導体装置が不動作になるおそれがある。このような問題は、半導体チップのダイボンディング用接合材として用いられるAgペーストによっても引き起こされるおそれがある。

【0005】

対策として従来は、熱等を加えてポリイミド膜とチップ(基板や絶縁膜)との密着性を高めることにより対応していたが、かかる対策では、近年のように、パッケージの小型化・薄型化に伴ってモールド樹脂による応力が増加している半導体装置に対しては、十分な効果を得ることが困難になっている。

そこで、本発明の目的は、複数の電極パッド間の短絡を確実に防止することができ、従来に比べて信頼性の高い半導体チップおよびそれを備える半導体パッケージを提供することである。

【課題を解決するための手段】

【0006】

本発明の半導体チップは、半導体基板と、前記半導体基板上に形成された下層絶縁膜と、前記下層絶縁膜上に形成された複数の電極パッドと、前記下層絶縁膜上に形成されたポリイミドからなる表面保護膜であって、各前記電極パッドを露出させるパッド開口が形成された表面保護膜とを含み、前記表面保護膜において隣り合う前記電極パッドの間には、当該隣り合う前記電極パッドが同一のポリイミドに接しないように、前記表面保護膜を選択的に除去した除去領域が形成されている(請求項1)。

【0007】

この構成によれば、互いに隣り合う電極パッドの一方に接するポリイミドと、他方に接するポリイミドとが除去領域により物理的に切り離されているので、表面保護膜(ポリイミド)中にAgが拡散して、膜の一部が導電性を示しても、電極パッド間の短絡を確実に防ぐことができる。その結果、従来に比べて信頼性の高い半導体チップを実現することができる。

【0008】

また、本発明の半導体チップでは、前記除去領域が、各前記電極パッドを取り囲むように環状に形成され、前記表面保護膜は、当該環状の除去領域および前記パッド開口により区画された環状のパッド保護部を含むことが好ましい(請求項2)。

この構成によれば、パッド保護部の周辺のポリイミドがAgの拡散により導電性を示しても、各パッド保護部が当該周辺のポリイミドから物理的に独立しているので(隔てられているので)、パッド保護部の絶縁性を維持することができる。そのため、各電極パッドの周囲の絶縁性を維持することができる。

【0009】

また、本発明の半導体チップでは、前記除去領域は、前記表面保護膜を一定の幅で溝状に除去したスリット開口を含むことが好ましく(請求項3)、前記スリット開口の幅は、15μm〜50μmであることが好ましい(請求項4)。

この構成によれば、半導体チップを樹脂パッケージで封止する際、モールド樹脂をスリット開口の中に入り込ませて、スリット開口をモールド樹脂で満たすことができる。また、フォトリソグラフィ技術を用いて表面保護膜にスリット開口を形成する場合には、表面保護膜の露光・現像を良好に行うことできる。

【0010】

また、本発明の半導体チップでは、前記表面保護膜は、前記電極パッドの周縁部を被覆するように形成されていることが好ましい(請求項5)。

この構成によれば、表面保護膜と下層絶縁膜との間に電極パッドを挟むことができるので、下層絶縁膜に対する電極パッドの密着性を向上させることができる。そのため、たとえば電極パッドにボンディングワイヤを接合する際に、電極パッドが下層絶縁膜から剥がれることを防止することができる。

【0011】

また、前記下層絶縁膜が、前記半導体基板上に順に積層された複数の層間絶縁膜を含む場合、本発明の半導体チップは、各前記層間絶縁膜上に形成され、前記電極パッドに電気的に接続された配線層を含んでいてもよい(請求項6)。

また、本発明の半導体チップでは、前記下層絶縁膜は、SiO2またはSiNからなっていてもよい(請求項7)。

【0012】

本発明の半導体パッケージは、アイランドと、前記アイランドに、前記電極パッドが上方に向く姿勢でマウントされた本発明の半導体チップと、前記アイランドと前記半導体チップとの間に挟まれた、Agを含む接合材と、前記電極パッドに接続されたボンディングワイヤと、前記半導体チップおよび前記ボンディングワイヤを封止する樹脂パッケージとを含む(請求項8)。

【0013】

この構成によれば、本発明の半導体チップが搭載されているので、表面保護膜(ポリイミド)中に接合材のAgが拡散して、膜の一部が導電性を示しても、電極パッド間の短絡を確実に防ぐことができる。その結果、従来に比べて信頼性の高い半導体パッケージを実現することができる。

また、本発明の半導体パッケージでは、前記樹脂パッケージは、前記表面保護膜の前記除去領域に入り込んでいることが好ましい(請求項9)。

【0014】

この構成によれば、互いに隣り合う電極パッドの一方に接するポリイミドと、他方に接するポリイミドとが除去領域により物理的に切り離されていることに加え、除去領域に樹脂パッケージが入り込んでいるので、ポリイミド間の絶縁性を一層向上させることができる。

また、本発明の半導体チップでは、前記接合材は、Agペーストを含んでいてもよい(請求項10)。

【図面の簡単な説明】

【0015】

【図1】図1は、本発明の一実施形態に係る半導体パッケージの模式的な平面図である。

【図2】図2は、図1の半導体パッケージの模式的な断面図であって、図1のII−II切断面での断面を示している。

【図3】図3は、図1の半導体装置の拡大平面図であって、図1の破線IIIで囲まれた部分を示している。

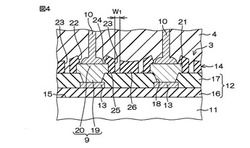

【図4】図4は、図1の半導体装置の拡大断面図であって、図3のIV−IV切断面での断面を示している。

【図5A】図5Aは、図3および図4の半導体装置の製造工程の一部を示す図である。

【図5B】図5Bは、図5Aの次の工程を示す図である。

【図5C】図5Cは、図5Bの次の工程を示す図である。

【図5D】図5Dは、図5Cの次の工程を示す図である。

【図6】図6は、表面保護膜の除去領域の変形例を示す図である。

【発明を実施するための形態】

【0016】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の一実施形態に係る半導体パッケージ1の模式的な平面図である。図2は、図1の半導体パッケージ1の模式的な断面図であって、図1のII−II切断面での断面を示している。なお、図1では、樹脂パッケージ4およびボンディングワイヤ10を省略した状態を表わしている。

【0017】

半導体パッケージ1は、BGA(Ball Grid Array)が採用された半導体装置であり、樹脂製のインタポーザ2と、半導体チップ3と、樹脂パッケージ4とを含む。

インタポーザ2の上面には、アイランド5および複数の内部端子6が設けられている。複数の内部端子6は、インタポーザ2の中央部に配置されたアイランド5を取り囲むように、インタポーザ2の周縁に沿って互いに等間隔で配列されている。半導体チップ3は、アイランド5上に形成されたAgペーストからなる接合材7を用いて、アイランド5に接合されている。

【0018】

一方、インタポーザ2の下面には、実装基板(プリント配線板)上のランド(図示せず)との電気接続のための複数のボール状の外部端子8が整列して配置されている。そして、インタポーザ2の内部端子6と外部端子8とは、インタポーザ2の上下面間を貫通するスルーホール(図示せず)内に設けられた金属を介して電気的に接続されている。

半導体チップ3の上面(アイランド5と対向する面(裏面)とは反対側の面)には、複数の電極パッド9が設けられている。複数の電極パッド9は、半導体チップ3の互いに対向する1対の周縁それぞれに沿って、互いに等間隔で配列されている。なお、この電極パッド9および上記した内部端子6の数は、図1で表した数に限らず、用途に応じて適宜変更することができる。そして、各電極パッド9は、ボンディングワイヤ10を用いてインタポーザ2の内部端子6に電気的に接続されている。

【0019】

樹脂パッケージ4は、インタポーザ2の上面上に設けられた半導体チップ3、ボンディングワイヤ10、アイランド5および内部端子6が露出しないように、これらを一括して被覆(封止)している。

次に、半導体パッケージ1のさらに具体的な構造について説明する。

図3は、図1の半導体パッケージ1の拡大平面図であって、図1の破線IIIで囲まれた部分を示している。図4は、図1の半導体パッケージ1の拡大断面図であって、図3のIV−IV切断面での断面を示している。

【0020】

半導体チップ3は、シリコンからなる半導体基板11と、下層絶縁膜としての複数の層間絶縁膜12と、配線層としての複数のメタル配線13と、電極パッド9と、表面保護膜14とを含む。

半導体基板11には、その表面15に回路を構成するトランジスタ(たとえばCMOSトランジスタ)、ダイオード、抵抗、キャパシタなどの複数の半導体素子が形成されている。つまり、半導体基板11では、この表面15が素子形成面であり、この素子形成面15に層間絶縁膜12が積層されている。

【0021】

層間絶縁膜12は、半導体基板11の表面15から順に積層された第1層間絶縁膜16および第2層間絶縁膜17を含む。第1層間絶縁膜16と第2層間絶縁膜17との界面からなる層に、複数のメタル配線13が配置されている。層間絶縁膜12は、酸化シリコン(SiO2)や窒化シリコン(SiN)等の絶縁物からなり、メタル配線13は、アルミニウム等の導電物からなる。なお、層間絶縁膜12の積層数は、この実施形態では2層となっているが、これに限るものではなく、たとえば、3層、4層およびそれ以上であってもよい。その場合、層間絶縁膜12の各界面にメタル配線13を設けることにより、メタル配線13を複数の配線層としてもよい。

【0022】

最上層の第2層間絶縁膜17には、最上層のメタル配線13と厚さ方向に対向する部分にコンタクトホール18が形成されている。コンタクトホール18は、開口端ほど開口面積が大きくなるようなテーパ形状に形成されている。

電極パッド9は、アルミニウムや金等の導電物からなり、平面視四角形状をしている。電極パッド9は、コンタクトホール18に埋設された下端部19と、第2層間絶縁膜17から上方に突出した上端部20とを含み、下端部19がコンタクトホール18内でメタル配線13に接続されている。また、電極パッド9の上端部20は、コンタクトホール18の開口端から横方向(半導体基板11の表面15に沿う方向)に一様に引き出された周縁部としての引き出し部21をさらに含む。これにより、電極パッド9は、平面視でコンタクトホール18の開口径(たとえば、開口端の径)よりも大きなサイズで形成されている。また、電極パッド9の厚さ(第2層間絶縁膜17からの突出量)は、たとえば、2μm〜4μm程度である。

【0023】

表面保護膜14は、ポリイミドからなり、電極パッド9を覆うように第2層間絶縁膜17上に形成されている。表面保護膜14には、表面保護膜14のポリイミドを選択的に除去したパッド開口22および除去領域としてのスリット開口23が形成されている。

パッド開口22は、複数の電極パッド9が1つずつ露出するように、各電極パッド9と厚さ方向に対向する部分に形成されている。パッド開口22は、開口端ほど開口面積が大きくなるようなテーパ形状に形成されており、その下端(開口端の反対側端部)が、電極パッド9の外周に対して横方向に内側に後退した位置で区画されている。

【0024】

これにより、表面保護膜14は、電極パッド9において、その外周からパッド開口22の下端までの間の部分(この実施形態では、引き出し部21)を上側から被覆するオーバーラップ部24を有している。オーバーラップ部24に重なる引き出し部21は、当該オーバーラップ部24(上側)および第2層間絶縁膜17(下側)によって上下両方向から挟まれることになる。

【0025】

そして、ボンディングワイヤ10は、電極パッド9においてパッド開口22から露出した部分に接合されている。

スリット開口23は、各電極パッド9を取り囲むように環状(この実施形態では、四角環状)に形成されていて、15μm〜50μmの一定幅W1を有している。これにより、表面保護膜14は、環状のスリット開口23およびパッド開口22により区画された環状のパッド保護部25を有している。各パッド保護部25は、スリット開口23により表面保護膜14の他の部分(フィールド部26)および他のパッド保護部25のポリイミドから物理的に完全に隔てられている。

【0026】

さらにこの実施形態では、スリット開口23は、各電極パッド9に接するポリイミド(パッド保護部25)が半導体チップ3のエッジ27に接しないように、半導体チップ3のエッジ27(側面)から間隔を隔てるように形成されている。

また、スリット開口23は、樹脂パッケージ4のモールド樹脂が入り込むことにより、当該モールド樹脂で満たされている。

【0027】

図5A〜図5Dは、図3および図4の半導体パッケージ1の製造工程の一部を工程順に示す図である。

まず、図5Aに示すように、半導体基板11の表面15に半導体素子が作りこまれ、その後、CVD法により第1層間絶縁膜16を形成する。次に、第1層間絶縁膜16上にアルミニウム膜をスパッタし、露光およびエッチングを行うことにより、メタル配線13を形成する。メタル配線13の形成後、CVD法により第2層間絶縁膜17を形成し、露光およびエッチングを行うことにより、コンタクトホール18を形成する。

【0028】

次の工程は、図5Bに示すように、電極パッド9の形成である。電極パッド9の形成は、たとえば、電極パッド9がアルミパッド(Alパッド)である場合には、第2層間絶縁膜17上にアルミニウム膜をスパッタし、露光およびエッチングを行うことにより形成する。

一方、電極パッド9が金パッド(Auパッド)である場合には、コンタクトホール18内および第2層間絶縁膜17上にシード膜を形成し、露光およびエッチングを行う。そして、エッチングによりパターニングされたシード膜から金をめっき成長させることにより形成する。

【0029】

次に、図5Cに示すように、たとえば、スピンコーティング等の塗布方法により、電極パッド9が完全に隠れるように、ポリイミド膜28を半導体基板11の全面に塗布する。

次に、図5Dに示すように、ポリイミド膜28を露光・現像することにより、パッド開口22とスリット開口23を同時に形成する。以上の工程を経て、図3および図4の半導体パッケージ1が得られる。

【0030】

以上のように、この実施形態によれば、スリット開口23により、互いに隣り合う電極パッド9の一方に接するポリイミドと、他方に接するポリイミドとが除去領域により物理的に切り離されているので、表面保護膜14(ポリイミド)中に、たとえば接合材7(Agペースト)の一部が拡散して、表面保護膜14の一部(たとえばフィールド部26)が導電性を示しても、電極パッド9間の短絡を確実に防ぐことができる。その結果、従来に比べて信頼性の高い半導体チップ3を実現することができる。

【0031】

しかも、この実施形態では、電極パッド9に接する各パッド保護部25が完全に独立して形成されているので、パッド保護部25の周辺のポリイミドがAgの拡散により導電性を示しても、パッド保護部25の絶縁性を維持することができる。そのため、各電極パッド9の周囲の絶縁性を維持することができる。

また、電極パッド9の一部(引き出し部21)が、オーバーラップ部24(上側)および第2層間絶縁膜17(下側)によって上下両方向から挟まれて固定されているので、層間絶縁膜12に対する電極パッド9の密着性を向上させることができる。そのため、電極パッド9にボンディングワイヤ10を接合する際に、電極パッド9が層間絶縁膜12から剥がれることを防止することができる。

【0032】

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

たとえば、互いに隣り合う電極パッド9の一方に接するポリイミドと、他方に接するポリイミドとが除去領域により物理的に切り離すための開口(除去領域)は、スリットである必要はなく、このような効果を達成できる形状であれば特に限定されない。

また、表面保護膜14の除去領域は、たとえば、図6のスリット開口29のように、電極パッド9を取り囲むが、それぞれ半導体チップ3のエッジ27に位置する一端および他端を有するライン状に形成されていてもよい。

【0033】

また、たとえば、前述の実施形態では、BGAが採用された半導体パッケージ1を取り上げたが、本発明は、ボール状の外部端子8に代えて、薄板状の外部端子8が整列した、いわゆるLGA(Land Grid Array)が採用された半導体パッケージに適用されてもよい。

また、BGAやLGAなどのように、インタポーザ2を備えるパッケージに限らず、QFN(Quad Flat Non-leaded Package)やSON(Small Outlined Non-leaded Package)など、リードフレームを備えるパッケージが採用された半導体パッケージに適用されてもよい。

【0034】

さらには、それらの表面実装型パッケージに限らず、実装基板に形成されたスルーホールに半導体パッケージのリードを挿入して、半導体パッケージの実装基板への実装が達成されるタイプのパッケージ(リード挿入実装型パッケージ)が採用された半導体パッケージに適用されてもよい。

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0035】

1 半導体パッケージ

2 インタポーザ

3 半導体チップ

4 樹脂パッケージ

5 アイランド

6 内部端子

7 接合材

8 外部端子

9 電極パッド

10 ボンディングワイヤ

11 半導体基板

12 層間絶縁膜

13 メタル配線

14 表面保護膜

15 (半導体基板の)表面

16 第1層間絶縁膜

17 第2層間絶縁膜

18 コンタクトホール

19 (電極パッドの)下端部

20 (電極パッドの)上端部

21 (電極パッドの)引き出し部

22 パッド開口

23 スリット開口

24 (表面保護膜の)オーバーラップ部

25 (表面保護膜の)パッド保護部

26 (表面保護膜の)フィールド部

27 (半導体チップの)エッジ

28 ポリイミド膜

29 スリット開口

【技術分野】

【0001】

本発明は、ポリイミドからなる表面保護膜を備える半導体チップおよび当該半導体チップを備える半導体パッケージに関する。

【背景技術】

【0002】

従来、耐熱性、機械強度、化学安定性および絶縁性に優れるポリイミド膜が最上層保護膜として形成された半導体チップ、および当該半導体チップを備える半導体装置が知られている。

たとえば、特許文献1の半導体装置は、複数のボンディングパッドが表面に形成された下段側半導体チップと、下段側半導体チップの表面に形成され、ボンディングパッドを露出させる開口部が形成されたポリイミド膜と、下段側半導体チップ上にマイクロバンプを介して積層された上段側半導体チップと、下段側半導体チップと上段側半導体チップのギャップに充填されたアンダーフィル樹脂と、アンダーフィル樹脂の流出を防止するために下段側半導体チップの表面に形成されたAg等からなるダムと、下段側半導体チップが接続された配線基板と、配線基板の接続パッドと下段側半導体チップのボンディングパッドとを接続するボンディングワイヤと、下段側半導体チップ、上段側半導体チップおよびボンディングワイヤを封止するモールド樹脂と、配線基板の裏面に形成された外部接続端子とを含む。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011−71381号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1の半導体装置では、半導体チップをモールド樹脂で封入したときに、モールド樹脂あるいはポリイミド膜自身の応力等により、ポリイミド膜と下段側半導体チップとの間にすき間が発生する場合がある。このすき間に水分が侵入すると、たとえばダム中のAgが、水分と反応してマイグレーションを起こし、ポリイミド膜中の微小な空孔に水分と共に吸い込まれる。すると、ポリイミド膜におけるAgが吸い込まれた部分が導電性を示すため、当該導電性部分により隣り合うボンディングパッド間が短絡され、場合によっては、半導体装置が不動作になるおそれがある。このような問題は、半導体チップのダイボンディング用接合材として用いられるAgペーストによっても引き起こされるおそれがある。

【0005】

対策として従来は、熱等を加えてポリイミド膜とチップ(基板や絶縁膜)との密着性を高めることにより対応していたが、かかる対策では、近年のように、パッケージの小型化・薄型化に伴ってモールド樹脂による応力が増加している半導体装置に対しては、十分な効果を得ることが困難になっている。

そこで、本発明の目的は、複数の電極パッド間の短絡を確実に防止することができ、従来に比べて信頼性の高い半導体チップおよびそれを備える半導体パッケージを提供することである。

【課題を解決するための手段】

【0006】

本発明の半導体チップは、半導体基板と、前記半導体基板上に形成された下層絶縁膜と、前記下層絶縁膜上に形成された複数の電極パッドと、前記下層絶縁膜上に形成されたポリイミドからなる表面保護膜であって、各前記電極パッドを露出させるパッド開口が形成された表面保護膜とを含み、前記表面保護膜において隣り合う前記電極パッドの間には、当該隣り合う前記電極パッドが同一のポリイミドに接しないように、前記表面保護膜を選択的に除去した除去領域が形成されている(請求項1)。

【0007】

この構成によれば、互いに隣り合う電極パッドの一方に接するポリイミドと、他方に接するポリイミドとが除去領域により物理的に切り離されているので、表面保護膜(ポリイミド)中にAgが拡散して、膜の一部が導電性を示しても、電極パッド間の短絡を確実に防ぐことができる。その結果、従来に比べて信頼性の高い半導体チップを実現することができる。

【0008】

また、本発明の半導体チップでは、前記除去領域が、各前記電極パッドを取り囲むように環状に形成され、前記表面保護膜は、当該環状の除去領域および前記パッド開口により区画された環状のパッド保護部を含むことが好ましい(請求項2)。

この構成によれば、パッド保護部の周辺のポリイミドがAgの拡散により導電性を示しても、各パッド保護部が当該周辺のポリイミドから物理的に独立しているので(隔てられているので)、パッド保護部の絶縁性を維持することができる。そのため、各電極パッドの周囲の絶縁性を維持することができる。

【0009】

また、本発明の半導体チップでは、前記除去領域は、前記表面保護膜を一定の幅で溝状に除去したスリット開口を含むことが好ましく(請求項3)、前記スリット開口の幅は、15μm〜50μmであることが好ましい(請求項4)。

この構成によれば、半導体チップを樹脂パッケージで封止する際、モールド樹脂をスリット開口の中に入り込ませて、スリット開口をモールド樹脂で満たすことができる。また、フォトリソグラフィ技術を用いて表面保護膜にスリット開口を形成する場合には、表面保護膜の露光・現像を良好に行うことできる。

【0010】

また、本発明の半導体チップでは、前記表面保護膜は、前記電極パッドの周縁部を被覆するように形成されていることが好ましい(請求項5)。

この構成によれば、表面保護膜と下層絶縁膜との間に電極パッドを挟むことができるので、下層絶縁膜に対する電極パッドの密着性を向上させることができる。そのため、たとえば電極パッドにボンディングワイヤを接合する際に、電極パッドが下層絶縁膜から剥がれることを防止することができる。

【0011】

また、前記下層絶縁膜が、前記半導体基板上に順に積層された複数の層間絶縁膜を含む場合、本発明の半導体チップは、各前記層間絶縁膜上に形成され、前記電極パッドに電気的に接続された配線層を含んでいてもよい(請求項6)。

また、本発明の半導体チップでは、前記下層絶縁膜は、SiO2またはSiNからなっていてもよい(請求項7)。

【0012】

本発明の半導体パッケージは、アイランドと、前記アイランドに、前記電極パッドが上方に向く姿勢でマウントされた本発明の半導体チップと、前記アイランドと前記半導体チップとの間に挟まれた、Agを含む接合材と、前記電極パッドに接続されたボンディングワイヤと、前記半導体チップおよび前記ボンディングワイヤを封止する樹脂パッケージとを含む(請求項8)。

【0013】

この構成によれば、本発明の半導体チップが搭載されているので、表面保護膜(ポリイミド)中に接合材のAgが拡散して、膜の一部が導電性を示しても、電極パッド間の短絡を確実に防ぐことができる。その結果、従来に比べて信頼性の高い半導体パッケージを実現することができる。

また、本発明の半導体パッケージでは、前記樹脂パッケージは、前記表面保護膜の前記除去領域に入り込んでいることが好ましい(請求項9)。

【0014】

この構成によれば、互いに隣り合う電極パッドの一方に接するポリイミドと、他方に接するポリイミドとが除去領域により物理的に切り離されていることに加え、除去領域に樹脂パッケージが入り込んでいるので、ポリイミド間の絶縁性を一層向上させることができる。

また、本発明の半導体チップでは、前記接合材は、Agペーストを含んでいてもよい(請求項10)。

【図面の簡単な説明】

【0015】

【図1】図1は、本発明の一実施形態に係る半導体パッケージの模式的な平面図である。

【図2】図2は、図1の半導体パッケージの模式的な断面図であって、図1のII−II切断面での断面を示している。

【図3】図3は、図1の半導体装置の拡大平面図であって、図1の破線IIIで囲まれた部分を示している。

【図4】図4は、図1の半導体装置の拡大断面図であって、図3のIV−IV切断面での断面を示している。

【図5A】図5Aは、図3および図4の半導体装置の製造工程の一部を示す図である。

【図5B】図5Bは、図5Aの次の工程を示す図である。

【図5C】図5Cは、図5Bの次の工程を示す図である。

【図5D】図5Dは、図5Cの次の工程を示す図である。

【図6】図6は、表面保護膜の除去領域の変形例を示す図である。

【発明を実施するための形態】

【0016】

以下では、本発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、本発明の一実施形態に係る半導体パッケージ1の模式的な平面図である。図2は、図1の半導体パッケージ1の模式的な断面図であって、図1のII−II切断面での断面を示している。なお、図1では、樹脂パッケージ4およびボンディングワイヤ10を省略した状態を表わしている。

【0017】

半導体パッケージ1は、BGA(Ball Grid Array)が採用された半導体装置であり、樹脂製のインタポーザ2と、半導体チップ3と、樹脂パッケージ4とを含む。

インタポーザ2の上面には、アイランド5および複数の内部端子6が設けられている。複数の内部端子6は、インタポーザ2の中央部に配置されたアイランド5を取り囲むように、インタポーザ2の周縁に沿って互いに等間隔で配列されている。半導体チップ3は、アイランド5上に形成されたAgペーストからなる接合材7を用いて、アイランド5に接合されている。

【0018】

一方、インタポーザ2の下面には、実装基板(プリント配線板)上のランド(図示せず)との電気接続のための複数のボール状の外部端子8が整列して配置されている。そして、インタポーザ2の内部端子6と外部端子8とは、インタポーザ2の上下面間を貫通するスルーホール(図示せず)内に設けられた金属を介して電気的に接続されている。

半導体チップ3の上面(アイランド5と対向する面(裏面)とは反対側の面)には、複数の電極パッド9が設けられている。複数の電極パッド9は、半導体チップ3の互いに対向する1対の周縁それぞれに沿って、互いに等間隔で配列されている。なお、この電極パッド9および上記した内部端子6の数は、図1で表した数に限らず、用途に応じて適宜変更することができる。そして、各電極パッド9は、ボンディングワイヤ10を用いてインタポーザ2の内部端子6に電気的に接続されている。

【0019】

樹脂パッケージ4は、インタポーザ2の上面上に設けられた半導体チップ3、ボンディングワイヤ10、アイランド5および内部端子6が露出しないように、これらを一括して被覆(封止)している。

次に、半導体パッケージ1のさらに具体的な構造について説明する。

図3は、図1の半導体パッケージ1の拡大平面図であって、図1の破線IIIで囲まれた部分を示している。図4は、図1の半導体パッケージ1の拡大断面図であって、図3のIV−IV切断面での断面を示している。

【0020】

半導体チップ3は、シリコンからなる半導体基板11と、下層絶縁膜としての複数の層間絶縁膜12と、配線層としての複数のメタル配線13と、電極パッド9と、表面保護膜14とを含む。

半導体基板11には、その表面15に回路を構成するトランジスタ(たとえばCMOSトランジスタ)、ダイオード、抵抗、キャパシタなどの複数の半導体素子が形成されている。つまり、半導体基板11では、この表面15が素子形成面であり、この素子形成面15に層間絶縁膜12が積層されている。

【0021】

層間絶縁膜12は、半導体基板11の表面15から順に積層された第1層間絶縁膜16および第2層間絶縁膜17を含む。第1層間絶縁膜16と第2層間絶縁膜17との界面からなる層に、複数のメタル配線13が配置されている。層間絶縁膜12は、酸化シリコン(SiO2)や窒化シリコン(SiN)等の絶縁物からなり、メタル配線13は、アルミニウム等の導電物からなる。なお、層間絶縁膜12の積層数は、この実施形態では2層となっているが、これに限るものではなく、たとえば、3層、4層およびそれ以上であってもよい。その場合、層間絶縁膜12の各界面にメタル配線13を設けることにより、メタル配線13を複数の配線層としてもよい。

【0022】

最上層の第2層間絶縁膜17には、最上層のメタル配線13と厚さ方向に対向する部分にコンタクトホール18が形成されている。コンタクトホール18は、開口端ほど開口面積が大きくなるようなテーパ形状に形成されている。

電極パッド9は、アルミニウムや金等の導電物からなり、平面視四角形状をしている。電極パッド9は、コンタクトホール18に埋設された下端部19と、第2層間絶縁膜17から上方に突出した上端部20とを含み、下端部19がコンタクトホール18内でメタル配線13に接続されている。また、電極パッド9の上端部20は、コンタクトホール18の開口端から横方向(半導体基板11の表面15に沿う方向)に一様に引き出された周縁部としての引き出し部21をさらに含む。これにより、電極パッド9は、平面視でコンタクトホール18の開口径(たとえば、開口端の径)よりも大きなサイズで形成されている。また、電極パッド9の厚さ(第2層間絶縁膜17からの突出量)は、たとえば、2μm〜4μm程度である。

【0023】

表面保護膜14は、ポリイミドからなり、電極パッド9を覆うように第2層間絶縁膜17上に形成されている。表面保護膜14には、表面保護膜14のポリイミドを選択的に除去したパッド開口22および除去領域としてのスリット開口23が形成されている。

パッド開口22は、複数の電極パッド9が1つずつ露出するように、各電極パッド9と厚さ方向に対向する部分に形成されている。パッド開口22は、開口端ほど開口面積が大きくなるようなテーパ形状に形成されており、その下端(開口端の反対側端部)が、電極パッド9の外周に対して横方向に内側に後退した位置で区画されている。

【0024】

これにより、表面保護膜14は、電極パッド9において、その外周からパッド開口22の下端までの間の部分(この実施形態では、引き出し部21)を上側から被覆するオーバーラップ部24を有している。オーバーラップ部24に重なる引き出し部21は、当該オーバーラップ部24(上側)および第2層間絶縁膜17(下側)によって上下両方向から挟まれることになる。

【0025】

そして、ボンディングワイヤ10は、電極パッド9においてパッド開口22から露出した部分に接合されている。

スリット開口23は、各電極パッド9を取り囲むように環状(この実施形態では、四角環状)に形成されていて、15μm〜50μmの一定幅W1を有している。これにより、表面保護膜14は、環状のスリット開口23およびパッド開口22により区画された環状のパッド保護部25を有している。各パッド保護部25は、スリット開口23により表面保護膜14の他の部分(フィールド部26)および他のパッド保護部25のポリイミドから物理的に完全に隔てられている。

【0026】

さらにこの実施形態では、スリット開口23は、各電極パッド9に接するポリイミド(パッド保護部25)が半導体チップ3のエッジ27に接しないように、半導体チップ3のエッジ27(側面)から間隔を隔てるように形成されている。

また、スリット開口23は、樹脂パッケージ4のモールド樹脂が入り込むことにより、当該モールド樹脂で満たされている。

【0027】

図5A〜図5Dは、図3および図4の半導体パッケージ1の製造工程の一部を工程順に示す図である。

まず、図5Aに示すように、半導体基板11の表面15に半導体素子が作りこまれ、その後、CVD法により第1層間絶縁膜16を形成する。次に、第1層間絶縁膜16上にアルミニウム膜をスパッタし、露光およびエッチングを行うことにより、メタル配線13を形成する。メタル配線13の形成後、CVD法により第2層間絶縁膜17を形成し、露光およびエッチングを行うことにより、コンタクトホール18を形成する。

【0028】

次の工程は、図5Bに示すように、電極パッド9の形成である。電極パッド9の形成は、たとえば、電極パッド9がアルミパッド(Alパッド)である場合には、第2層間絶縁膜17上にアルミニウム膜をスパッタし、露光およびエッチングを行うことにより形成する。

一方、電極パッド9が金パッド(Auパッド)である場合には、コンタクトホール18内および第2層間絶縁膜17上にシード膜を形成し、露光およびエッチングを行う。そして、エッチングによりパターニングされたシード膜から金をめっき成長させることにより形成する。

【0029】

次に、図5Cに示すように、たとえば、スピンコーティング等の塗布方法により、電極パッド9が完全に隠れるように、ポリイミド膜28を半導体基板11の全面に塗布する。

次に、図5Dに示すように、ポリイミド膜28を露光・現像することにより、パッド開口22とスリット開口23を同時に形成する。以上の工程を経て、図3および図4の半導体パッケージ1が得られる。

【0030】

以上のように、この実施形態によれば、スリット開口23により、互いに隣り合う電極パッド9の一方に接するポリイミドと、他方に接するポリイミドとが除去領域により物理的に切り離されているので、表面保護膜14(ポリイミド)中に、たとえば接合材7(Agペースト)の一部が拡散して、表面保護膜14の一部(たとえばフィールド部26)が導電性を示しても、電極パッド9間の短絡を確実に防ぐことができる。その結果、従来に比べて信頼性の高い半導体チップ3を実現することができる。

【0031】

しかも、この実施形態では、電極パッド9に接する各パッド保護部25が完全に独立して形成されているので、パッド保護部25の周辺のポリイミドがAgの拡散により導電性を示しても、パッド保護部25の絶縁性を維持することができる。そのため、各電極パッド9の周囲の絶縁性を維持することができる。

また、電極パッド9の一部(引き出し部21)が、オーバーラップ部24(上側)および第2層間絶縁膜17(下側)によって上下両方向から挟まれて固定されているので、層間絶縁膜12に対する電極パッド9の密着性を向上させることができる。そのため、電極パッド9にボンディングワイヤ10を接合する際に、電極パッド9が層間絶縁膜12から剥がれることを防止することができる。

【0032】

以上、本発明の実施形態を説明したが、本発明は、他の形態で実施することもできる。

たとえば、互いに隣り合う電極パッド9の一方に接するポリイミドと、他方に接するポリイミドとが除去領域により物理的に切り離すための開口(除去領域)は、スリットである必要はなく、このような効果を達成できる形状であれば特に限定されない。

また、表面保護膜14の除去領域は、たとえば、図6のスリット開口29のように、電極パッド9を取り囲むが、それぞれ半導体チップ3のエッジ27に位置する一端および他端を有するライン状に形成されていてもよい。

【0033】

また、たとえば、前述の実施形態では、BGAが採用された半導体パッケージ1を取り上げたが、本発明は、ボール状の外部端子8に代えて、薄板状の外部端子8が整列した、いわゆるLGA(Land Grid Array)が採用された半導体パッケージに適用されてもよい。

また、BGAやLGAなどのように、インタポーザ2を備えるパッケージに限らず、QFN(Quad Flat Non-leaded Package)やSON(Small Outlined Non-leaded Package)など、リードフレームを備えるパッケージが採用された半導体パッケージに適用されてもよい。

【0034】

さらには、それらの表面実装型パッケージに限らず、実装基板に形成されたスルーホールに半導体パッケージのリードを挿入して、半導体パッケージの実装基板への実装が達成されるタイプのパッケージ(リード挿入実装型パッケージ)が採用された半導体パッケージに適用されてもよい。

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0035】

1 半導体パッケージ

2 インタポーザ

3 半導体チップ

4 樹脂パッケージ

5 アイランド

6 内部端子

7 接合材

8 外部端子

9 電極パッド

10 ボンディングワイヤ

11 半導体基板

12 層間絶縁膜

13 メタル配線

14 表面保護膜

15 (半導体基板の)表面

16 第1層間絶縁膜

17 第2層間絶縁膜

18 コンタクトホール

19 (電極パッドの)下端部

20 (電極パッドの)上端部

21 (電極パッドの)引き出し部

22 パッド開口

23 スリット開口

24 (表面保護膜の)オーバーラップ部

25 (表面保護膜の)パッド保護部

26 (表面保護膜の)フィールド部

27 (半導体チップの)エッジ

28 ポリイミド膜

29 スリット開口

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上に形成された下層絶縁膜と、

前記下層絶縁膜上に形成された複数の電極パッドと、

前記下層絶縁膜上に形成されたポリイミドからなる表面保護膜であって、各前記電極パッドを露出させるパッド開口が形成された表面保護膜とを含み、

前記表面保護膜において隣り合う前記電極パッドの間には、当該隣り合う前記電極パッドが同一のポリイミドに接しないように、前記表面保護膜を選択的に除去した除去領域が形成されている、半導体チップ。

【請求項2】

前記除去領域が、各前記電極パッドを取り囲むように環状に形成され、

前記表面保護膜は、当該環状の除去領域および前記パッド開口により区画された環状のパッド保護部を含む、請求項1に記載の半導体チップ。

【請求項3】

前記除去領域は、前記表面保護膜を一定の幅で溝状に除去したスリット開口を含む、請求項1または2に記載の半導体チップ。

【請求項4】

前記スリット開口の幅は、15μm〜50μmである、請求項3に記載の半導体チップ。

【請求項5】

前記表面保護膜は、前記電極パッドの周縁部を被覆するように形成されている、請求項1〜4のいずれか一項に記載の半導体チップ。

【請求項6】

前記下層絶縁膜は、前記半導体基板上に順に積層された複数の層間絶縁膜を含み、

前記半導体チップは、各前記層間絶縁膜上に形成され、前記電極パッドに電気的に接続された配線層を含む、請求項1〜5のいずれか一項に記載の半導体チップ。

【請求項7】

前記下層絶縁膜は、SiO2またはSiNからなる、請求項1〜6のいずれか一項に記載の半導体チップ。

【請求項8】

アイランドと、

前記アイランドに、前記電極パッドが上方に向く姿勢でマウントされた請求項1〜7のいずれか一項に記載の半導体チップと、

前記アイランドと前記半導体チップとの間に挟まれた、Agを含む接合材と、

前記電極パッドに接続されたボンディングワイヤと、

前記半導体チップおよび前記ボンディングワイヤを封止する樹脂パッケージとを含む、半導体パッケージ。

【請求項9】

前記樹脂パッケージは、前記表面保護膜の前記除去領域に入り込んでいる、請求項8に記載の半導体パッケージ。

【請求項10】

前記接合材は、Agペーストを含む、請求項8または9に記載の半導体パッケージ。

【請求項1】

半導体基板と、

前記半導体基板上に形成された下層絶縁膜と、

前記下層絶縁膜上に形成された複数の電極パッドと、

前記下層絶縁膜上に形成されたポリイミドからなる表面保護膜であって、各前記電極パッドを露出させるパッド開口が形成された表面保護膜とを含み、

前記表面保護膜において隣り合う前記電極パッドの間には、当該隣り合う前記電極パッドが同一のポリイミドに接しないように、前記表面保護膜を選択的に除去した除去領域が形成されている、半導体チップ。

【請求項2】

前記除去領域が、各前記電極パッドを取り囲むように環状に形成され、

前記表面保護膜は、当該環状の除去領域および前記パッド開口により区画された環状のパッド保護部を含む、請求項1に記載の半導体チップ。

【請求項3】

前記除去領域は、前記表面保護膜を一定の幅で溝状に除去したスリット開口を含む、請求項1または2に記載の半導体チップ。

【請求項4】

前記スリット開口の幅は、15μm〜50μmである、請求項3に記載の半導体チップ。

【請求項5】

前記表面保護膜は、前記電極パッドの周縁部を被覆するように形成されている、請求項1〜4のいずれか一項に記載の半導体チップ。

【請求項6】

前記下層絶縁膜は、前記半導体基板上に順に積層された複数の層間絶縁膜を含み、

前記半導体チップは、各前記層間絶縁膜上に形成され、前記電極パッドに電気的に接続された配線層を含む、請求項1〜5のいずれか一項に記載の半導体チップ。

【請求項7】

前記下層絶縁膜は、SiO2またはSiNからなる、請求項1〜6のいずれか一項に記載の半導体チップ。

【請求項8】

アイランドと、

前記アイランドに、前記電極パッドが上方に向く姿勢でマウントされた請求項1〜7のいずれか一項に記載の半導体チップと、

前記アイランドと前記半導体チップとの間に挟まれた、Agを含む接合材と、

前記電極パッドに接続されたボンディングワイヤと、

前記半導体チップおよび前記ボンディングワイヤを封止する樹脂パッケージとを含む、半導体パッケージ。

【請求項9】

前記樹脂パッケージは、前記表面保護膜の前記除去領域に入り込んでいる、請求項8に記載の半導体パッケージ。

【請求項10】

前記接合材は、Agペーストを含む、請求項8または9に記載の半導体パッケージ。

【図1】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【図6】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図5C】

【図5D】

【図6】

【公開番号】特開2013−115054(P2013−115054A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−256714(P2011−256714)

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月24日(2011.11.24)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]