半導体チップとその製造方法、半導体装置

【課題】立体的な集積に適した、電磁妨害耐性に優れる半導体チップを提供する。また、その半導体チップを用いた、高い電磁妨害耐性と高い処理能力を両立する半導体装置を提供する。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

【解決手段】能動素子もしくは受動素子と、それらの素子を電気的に接続する配線部を備えた半導体チップについて、配線部を被覆するように導電性薄膜を設ける。この導電性薄膜は配線部に対して、不要電磁波を遮蔽するシールドとして働くので、半導体チップの電磁妨害耐性が向上する。また、この半導体チップを三次元集積半導体装置に組み込むことで、隣接するチップをフェイス・トゥ・フェイス接続した場合でも、チップ間のクロストークを遮断できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に係り、詳しくは半導体チップの電磁妨害耐性を向上させる構造とその製法、ならびに電磁妨害耐性に優れる半導体装置の構造に関する。

【背景技術】

【0002】

電子機器に対する、市場からの小型化・高機能化・多機能化への要請はとどまるところを知らない。この要請に応えるため、電子機器に搭載される半導体装置についても、小型化・高機能化が求められている。

【0003】

半導体装置の小型化・高機能化・多機能化を実現する一手法として、複数の半導体チップや受動素子を立体的に集積した三次元集積半導体装置が注目を集めている。単一の半導体チップのみで高機能化を図るのと同等以上の効果を、容易に得ることができるためである。

【0004】

三次元集積半導体装置を実現する手法として、すでにスタックト・ダイ工法やパッケージ・オン・パッケージ工法が実用化されている。スタックト・ダイ工法とは、複数の半導体チップを立体的に積み重ね、個々の半導体チップとインターポーザをボンディングワイヤで接続する工法である。パッケージ・オン・パッケージ工法とは、インターポーザに実装済みの半導体チップを複数用意し、それらを積み重ねた後はんだボールなどで接続する工法である。

【0005】

一方近年では、3D−SiP(3D−System in Package)とも呼ばれる、半導体チップを貫通する電極を用いた三次元集積半導体装置の開発が盛んである(例として、特許文献1)。3D−SiPでは積み重ねた複数の半導体チップを、その半導体チップを貫通する多数の貫通電極で直接に接続する。半導体チップ間の通信がボンディングワイヤよりもはるかに短い配線で、インターポーザを経由せずに行えるため、三次元集積半導体装置全体の処理能力が、スタックト・ダイ工法やパッケージ・オン・パッケージ工法によるものに比べて飛躍的に向上する。

【0006】

図40は、典型的な3D−SiPの構成を示す説明図である。

3D−SiP1は、回路要素12と、回路要素間の電気的接続のための配線を含む配線部13を備えた三種類の半導体チップ10、110、210を、その厚さ方向に積み上げて構成されている。半導体チップ10は、表面上の回路要素12が図中下向きに配置されている。一方、半導体チップ110および210は、回路要素12が図中上向きとなるよう配されている。つまり、半導体チップ10と110は3D−SiP1において、配線部13が形成された表面を相互に対向させた状態で組みつけられている。このような組みつけ方をフェイス・トゥ・フェイス接続と呼ぶ場合がある。

【0007】

各々の半導体チップに形成された回路要素12は、所定の回路機能を実現する電気的部品である。例示するならば、ベース基板を用いて形成されたトランジスタ等の能動素子やベース基板表面などへ形成された受動素子である。

【0008】

半導体チップ110、同210の内部には、一端が半導体チップの裏面(図中下面)に露出する貫通電極18がそれぞれ設けられている。また、配線部13を構成する配線の一部は、回路要素12と貫通電極18、および貫通電極18間の相互接続に用いられる。各貫通電極18は、貫通電極を取り囲むように形成された絶縁膜(図示せず)で、半導体チップから絶縁される。

【0009】

半導体チップ10と同110の間、および半導体チップ110と同210の間はマイクロバンプ120でそれぞれ物理的、電気的に接続される。各マイクロバンプは、図示しない絶縁材によって相互に電気的に絶縁されている。また、半導体チップ210を貫通する貫通電極18のチップ裏面側端面には、パッド214が存在する。3D−SiP1は、このパッドを経由して半導体チップ外部と電気的に接続される。

【0010】

上記の通り、典型的な3D−SiPでは、集積される半導体チップの配線部がマイクロバンプ高さの距離、あるいは半導体チップの厚さの距離を隔てて近接する。その距離は、はなはだしい場合は20μm以下にまで縮小する。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】公開公報 WO06/019156

【特許文献2】特開2006−179806

【特許文献3】特許第3532788号

【発明の概要】

【発明が解決しようとする課題】

【0012】

このように複数の配線部が近接した構造では、一方の配線部に含まれる配線が放射する電磁界が、他方の配線部に含まれる配線に伝播して生じるクロストーク・ノイズが増大する。強力なクロストーク・ノイズは、ノイズが乗った配線に接続される回路要素を誤動作させ、ひいては三次元集積半導体装置の異常動作を引き起こす。

【0013】

三次元集積半導体装置における、半導体チップ間のクロストーク・ノイズを対策する構造の一種として、特許文献2に開示された発明を例示する。この発明においては、立体的に集積する半導体チップの、配線部が形成されている部分以外の表面に対して金属膜を形成する。さらに前記金属膜を接地電位に接続して、前記金属膜を不要電磁波を遮蔽するシールドに用いる。

【0014】

しかし前記発明に基づく半導体装置では、配線部が形成された表面には全く防護手段が施されていない。そのため、図40における半導体チップ10および110のごとく、配線部が形成された表面を相互に対向させた状態で半導体チップを集積した場合、クロストーク・ノイズを回避する手立てはない。

【0015】

三次元集積半導体装置における、半導体チップ間のクロストーク・ノイズを対策する構造の更なる例として、特許文献3に開示された発明を例示する。この発明においては、立体的に集積される個々の半導体チップに対して、配線部の表面全面に金属薄膜を形成する。この金属薄膜は、半導体チップを常温接合技術で集積する際の接合層になるとともに、半導体チップの放射ノイズを抑制するシールド層としても働く。この発明に基づく半導体装置であれば、配線部を不要電磁波から防護することは可能である。

【0016】

しかし、前記発明に基づく半導体装置には、常温接合技術に起因する複数の技術的課題が存在する。

【0017】

第一の課題は、配線層表面の金属層をきわめて平坦に形成しなければならない点である。常温接合技術における接合層には、サブミクロンオーダーでの平坦性が求められる。しかし半導体チップでは、配線部の表面にμmオーダーの凹凸が存在するのが通常である。また、μmオーダーの凹凸がある表面に平坦に金属薄膜を形成できるプロセスは存在しない。よって、前記発明を実用するにあたっては、配線部表面へ金属層を形成する工程に加えて、金属層を平坦化する工程が必須となる。

【0018】

第二の課題は、チップ・トゥ・ウエハ接続プロセスの採用が困難となる点である。

常温接合技術では、接合面の清浄度が接合性に大きく影響する。そのため、接合直前に表面のクリーニングを行う必要がある。

ウエハ・トゥ・ウエハ接続であればこの特徴は問題にならない。一回の処理で多数のチップを一括で接合できるためだ。一方、チップ・トゥ・ウエハ接続に常温接合技術を適用する場合は、プロセスコストの大幅な増大が懸念される。前述の通り、常温接合技術においては接合面に高い清浄度が求められるため、ウエハ側の表面を、チップ接合工程の全ての時間にわたって清浄に保つ必要がある。これはチップ接合工程を全て真空系の中で行うことで可能となるが、それを実現する装置は装置そのもののコストも、ランニングコストも許容できない水準となるだろう。

【0019】

他方、当業者においては半導体チップ間のクロストーク対策として、配線部の中に不要電磁波を遮蔽するような導体構造を設ける手法が考案できるであろう。例としては、配線部のいずれかの導体層に、回路要素を被覆するような大面積の導体パターンを設ける方法などが考えられる。

【0020】

しかし前記の手法では、配線部の配線収容能力が低下する。配線部内に半導体チップの機能には不要な導体構造が形成される以上避けられない問題であり、この問題を解消するには、配線部を構成する導体層を増やすしかない。だが、配線部の導体層を増やすことは、半導体チップの生産コストの上昇に直結する。

【0021】

これに加えて、CMP(化学機械研磨法)や銅配線が適用される高度な半導体チップでは、大面積の導体パターンを形成することそのものにも技術的困難が存在する。大面積の銅パターンをCMPで平坦化すると、銅層表面が凹状に削れるディッシング(段差)が発生し、その後の工程にも支障が生じるためである。

【0022】

本発明は上記課題を鑑みてなされたものであり、立体的な集積に適した、電磁妨害耐性に優れる半導体チップの提供を目的としている。

【課題を解決するための手段】

【0023】

上記の目的を達成するための請求項1に係る発明は、半導体チップのうち、半導体材料の層を少なくとも一つ含むベース基板と、前記ベース基板の表面において能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち、前記ベース基板から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、前記外部接続パッドが形成された導体層を被覆し、かつ前記外部接続パッドをチップ外部に露出させるような開口部を備えた絶縁体からなるパッシベーション層とを備えるものであって、さらに、前記ベース基板に対して前記配線部および前記パッシベーション層を離隔した位置に、少なくとも一種類の金属ないし合金からなる導電性薄膜を具備し、かつ前記導電性薄膜のうち前記外部接続パッドに対応する部分には、第二の開口部が設けられていることを特徴とする半導体チップである。

【0024】

請求項2にかかる発明は、請求項1に記載の半導体チップにおいて、さらに前記ベース基板を厚さ方向に貫通する貫通電極を備えることを特徴とする半導体チップである。

【0025】

請求項3にかかる発明は、下記の1)、2)のうち少なくともいずれか一方を含むことを特徴とする、請求項2に記載の半導体チップである。

1)前記配線部に配置された、前記貫通電極と前記回路要素を電気的に接続するための内部配線。

2)前記配線部を形成する導体層のうち最も前記ベース基板から離れた層に形成され、前記外部配線に接続されていない貫通電極パッド、および前記貫通電極パッドと前記貫通電極を電気的に接続するために前記配線部に配置された貫通配線。

【0026】

請求項4にかかる発明は、前記貫通電極が前記ベース基板に加えて前記配線部を厚さ方向に貫通していることを特徴とする、請求項2および3に記載の半導体チップである。

【0027】

請求項5にかかる発明は、前記貫通電極の内部が導電材料で埋め込まれていることを特徴とする、請求項2から4に記載の半導体チップである。

【0028】

請求項6にかかる発明は、前記導電材料と前記導電性薄膜を形成する材料とが、共通の材料を含むことを特徴とする、請求項5に記載の半導体チップである。

【0029】

請求項7にかかる発明は、半導体チップのうち、半導体材料の層を少なくとも一つ含むベース基板と、前記ベース基板の表面において能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち、前記ベースから最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、前記外部接続パッドが形成された導体層を被覆し、かつパッドをチップ外部に露出させるような開口部を備えた絶縁体からなるパッシベーション層とを備えるものであって、さらに、前記ベース基板に対して前記配線部を離隔した位置に、少なくとも一種類の半導体材料を含む導体からなる導電性薄膜を具備し、かつ前記導電性薄膜のうち前記外部接続パッドに対応する部分には、第二の開口部が設けられていることを特徴とする半導体チップである。

【0030】

請求項8にかかる発明は、前記導電性薄膜に含まれる半導体材料が、1.5Ω・cm以下の比抵抗を示すことを特徴とする、請求項7に記載の半導体チップである。

【0031】

請求項9にかかる発明は、請求項7または8に記載の半導体チップにおいて、さらに前記ベース基板を厚さ方向に貫通する貫通電極を備えることを特徴とする半導体チップである。

【0032】

請求項10にかかる発明は、前記配線部の中に、下記の1)、2)のうち少なくともいずれか一方を含むことを特徴とする、請求項9に記載の半導体チップである。

1)前記配線部に配置された、前記貫通電極と前記回路要素を電気的に接続するための内部配線。

2)前記配線部を形成する導体層のうち最も前記ベース基板から離れた層に形成され、前記外部配線に接続されていない貫通電極パッド、および前記貫通電極パッドと前記貫通電極を電気的に接続するために前記配線部に配置された貫通配線。

【0033】

請求項11にかかる発明は、前記貫通電極が前記配線部を厚さ方向に貫通していることを特徴とする、請求項9および10に記載の半導体チップである。

【0034】

請求項12にかかる発明は、前記貫通電極の内部が導電材料で充填されていることを特徴とする、請求項9から11に記載の半導体チップである。

【0035】

請求項13にかかる発明は、前記導電材料と前記導電性薄膜を形成する材料とが、共通の材料を含むことを特徴とする、請求項12に記載の半導体チップである。

【0036】

請求項14にかかる発明は、前記導電性薄膜が不要電磁波の遮蔽のために設けられていることを特徴とする、請求項1から13に記載の半導体チップである。

【0037】

請求項15にかかる発明は、前記導電性薄膜が、前記配線部のうち電源電位を供給する部分に接続されていることを特徴とする、請求項1から14に記載の半導体チップである。

【0038】

請求項16にかかる発明は、前記導電性薄膜と前記電源電位を供給する配線部との電気的接続を、電源電位を供給するための前記外部接続パッドを前記導電性薄膜で被覆して得ていることを特徴とする、請求項15に記載の半導体チップである。

【0039】

請求項17にかかる発明は、前記導電性薄膜が、前記配線部のうち接地電位を供給する部分に接続されていることを特徴とする請求項1から14に記載の半導体チップである。

【0040】

請求項18にかかる発明は、前記導電性薄膜と前記接地電位を供給する配線部との電気的接続を、接地電位を供給するための前記外部接続パッドを前記導電性薄膜で被覆して得ていることを特徴とする、請求項17に記載の半導体チップである。

【0041】

請求項19にかかる発明は、請求項1から18に記載の半導体チップを少なくとも一つ含んだ、複数の半導体チップを立体的に集積したことを特徴とする三次元集積半導体装置である。

【0042】

請求項20にかかる発明は、請求項19に記載の三次元集積半導体装置において、請求項1から18に記載の半導体チップと電気的に接続される第二の半導体チップが、半導体材料からなり、少なくとも一つの表面を備える第二ベースと、前記第二ベース基板の表面に形成された第二配線部とを備えており、かつ、請求項1から18に記載の半導体チップと前記第二の半導体チップが、前記ベース基板の前記回路要素が形成された表面と、前記第二ベース基板の前記第二配線部が形成された表面が互いに近接するように集積されていることを特徴とする、請求項19に記載の三次元集積半導体装置である。

【0043】

請求項21にかかる発明は、下記(a)から(c)の工程を含むことを特徴とする、半導体チップの製造方法である。

(a)半導体チップのうち、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドとを具備する半導体チップを準備する工程。

(b)前記配線部の表面に導電性薄膜を形成する工程。

(c)導電性薄膜のうち、前記外部接続パッドを被覆している部分に第二の開口部を設ける工程。

【0044】

請求項22にかかる発明は、下記(a)から(f)の工程を含むことを特徴とする、半導体チップの製造方法である。

(a)半導体チップのうち、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドとを具備する半導体チップを準備する工程。

(b)前記半導体チップに、貫通電極となる孔を加工する工程。

(c)前記孔の側面に絶縁皮膜を形成する工程。

(d)前記孔の内部に導電材料の膜を形成し、半導体チップの両面を導通する工程。

(e)前記配線部の表面に導電性薄膜を形成する工程。

(f)前記導電性薄膜のうち、前記外部接続パッドを被覆している部分に第二の開口部を設ける工程。

【0045】

請求項23にかかる発明は、下記(a)から(c)の工程を含むことを特徴とする、半導体チップの製造方法である。

(a)半導体チップのうち、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、導電材料で側面を覆われたトレンチとを具備する半導体チップを準備する工程。

(b)前記配線部の表面に前記導電性薄膜を形成する工程。

(c)前記半導体チップの裏面を研削し、前記トレンチの内部に形成された前記導電材料を一部露出させる工程。

(d)前記導電性薄膜のうち前記外部接続パッドを被覆している部分に、第二の開口部を設ける工程。

【発明の効果】

【0046】

本発明の特徴は、半導体チップのうち、回路要素と配線部が形成された表面に不要電磁波を遮蔽するための導電性薄膜を形成することにある。半導体チップに、配線部の内部では形成が困難あるいは非効率な導電性薄膜を付与し、これをもって不要電磁波を原因とする誤動作に耐性を備えた半導体装置を提供可能とする。

【0047】

導電性薄膜には、半導体チップの外部接続パッドを半導体チップの外部に露出させる、第二の開口部が形成される。これは、半導体チップの内部に形成された回路要素とチップ外の回路を接続するためである。

【0048】

本発明の提示する構造は、貫通電極を備える半導体チップにも適用可能である。貫通電極の構造の違いは本発明の効果に影響しないためだ。また、半導体チップに貫通電極を形成する工程もビアファースト法、ビアミドル法、ビアラスト法のいずれを選択してもよい。さらに、貫通電極の内部に導電材料を充填するか否かも、用途に合わせて選択可能である。

【0049】

前記導電性薄膜の材料は、単体金属、合金、半導体およびこれら複数の組み合わせのいずれでもよい。半導体を用いる場合は、ドーピングなどの手法で比抵抗を低下させるのが望ましい。また、貫通電極内部の導電材料と同じ材料を選択すると、より少ない工程で半導体チップを製造することが可能となる。

【0050】

前記導電性薄膜を、常に一定の電位を供給する電源電位の配線、あるいは接地電位の配線に接続すると、不要電磁波の遮蔽能力が向上する。

【0051】

本発明に基づいて提供される半導体チップは、3D−SiPなど複数の半導体チップを立体的に集積した三次元集積半導体装置の構成要素として好適である。特に複数の半導体チップを、双方の配線部を互いに近接するように対向させる場合は、前記導電性薄膜によるクロストーク・ノイズ抑制機能が最大限に発揮される。

【0052】

本発明に基づいて提供された半導体チップを三次元集積半導体装置の一部として用いるにあたって、半導体チップ間を接合する材料、工法には一切の制限がない。これは半導体チップが元から備えていた外部接続パッドを、導電性薄膜形成後も半導体チップの外部に露出させているためである。そのために、半導体チップの接合工法が常温接合技術に限定されることがなくなり、既知の接合工法をそのまま利用可能となる。これに伴い、導電性薄膜に厳密な平坦性を求める必要もなくなるというメリットも生じる。

【0053】

また同様の理由で、半導体装置の集積にチップ・トゥ・ウエハ接続プロセスを用いた場合でも、必要以上の工程、装置の複雑化を避けることができる。

【図面の簡単な説明】

【0054】

【図1】本発明の一実施形態の半導体チップの一例を模式的に示した断面図である。

【図2】本発明の一実施形態の半導体チップによる三次元集積半導体装置の例を示した断面図である。

【図3】本発明の一実施形態の半導体チップの一例を模式的に示した断面図である。

【図4】本発明の一実施形態の半導体チップと、それを用いた三次元集積半導体装置を模式的に示したものである。

【図5】本発明の一実施形態の半導体チップによる三次元集積半導体装置の例を示した断面図である。

【図6】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図7】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図8】本発明の一実施形態の半導体チップの外部接続パッドの配置を示す図である。

【図9】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図10】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図11】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図12】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図13】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図14】本発明の一実施形態の個々のメモリチップの断面構造を示す図である。

【図15】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図16】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図17】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図18】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図19】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図20】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図21】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図22】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図23】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図24】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図25】本発明の一実施形態による三次元集積化半導体装置のシュム・プロットである。

【図26】本発明を適用しない三次元集積半導体装置のシュム・プロットである。

【図27】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図28】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図29】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図30】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図31】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図32】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図33】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図34】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図35】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図36】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図37】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図38】本発明の一実施形態による三次元集積化半導体装置のシュム・プロットである。

【図39】本発明を適用しない三次元集積半導体装置のシュム・プロットである。

【図40】3D−SiPの構成の一例を示す断面図である。

【発明を実施するための形態】

【0055】

以下、本発明による半導体チップの製造方法を説明する。なお、下記に記載した実施例は、発明の概念を説明するため便宜的に取り上げたものであり、何ら発明の実施形態を限定するものではない。

【0056】

以下の各図表において、同じ構成要素に対しては、とくに断りがない限り複数の図表で同じ番号を付与している。

【0057】

図1は、本発明に基づいて製作した半導体チップの一例を模式的に示したものである。

【0058】

半導体チップ10は、ベース基板11と、ベース基板表面に形成された回路要素12と、ベース基板の回路要素形成面に、絶縁層と導体層を交互に積層してなる配線部13を備える。また、配線部を構成する導体層のうち、もっともベース基板から遠い層には、外部接続パッド14がある。さらに、配線部のうちベース基板に対向する側の表面には、絶縁材料によるパッシベーション膜15が配される。ただしパッシベーション膜15のうち、外部接続パッドに対応する部分には開口部が形成されている。

【0059】

ベース基板11は、半導体材料からなる層を最低一つは備えた部材でなければならない。ただし、半導体材料の材質や構成は任意である。

構成に関しては、全体が単一の材料でできているベース基板を利用可能である。また、SOI(Silicon on Inslator)構造のように、異なる半導体材料の層が直接、もしくは絶縁体を介して積層された構成でもよい。

材料として代表的な物を例示するならば、単体半導体であれば単結晶シリコン、単結晶ゲルマニウムなどがある。炭化ケイ素や、ガリウム砒素、リン化インジウムをはじめとする化合物半導体も、ベース基板11の材料として利用可能である。

【0060】

半導体チップ10が備える回路要素12の種類は、本発明を適用する上での制約にはならない。トランジスタ、ダイオード等の能動素子を備えるチップであっても、抵抗などの受動素子を備えるチップであっても、また双方を備えるチップであっても、本発明を適用することができる。

【0061】

配線部13を構成する絶縁層は絶縁体で形成されていればよく、また導体層は導体で形成されていればよい。同様に、パッシベーション膜15も一種類以上の絶縁体を含む膜であればよい。

【0062】

パッシベーション膜15の上には導電性薄膜16が形成されている。この導電性薄膜が不要電磁波の伝播を遮断するシールドとして働き、半導体チップ10の電磁妨害耐性を向上させる。導電性薄膜の構成材料としては、各種の単体金属、合金、半導体材料およびこれらを組み合わせて積層したものが採用できる。導電性薄膜を形成するプロセスも、採用した材料に応じて任意に選ぶことができる。

【0063】

導電性薄膜16には、外部接続パッド14の全面を半導体チップ10の外部に露出させるための開口部17が設けられる。

【0064】

ここで、必ずしも全ての外部接続パッド14を露出させる必要はない。なぜなら、これによって半導体チップの電磁妨害耐性をより容易に高められるからである。

【0065】

導電性薄膜16の電磁波遮蔽性能を高める方法として、導電性薄膜16の電位を何らかの方法で安定化することが考えられる。これは導電性薄膜16と、配線層12の中の電位が安定した配線、すなわち電源電位を供給する配線もしくは接地電位を供給する配線とを、電気的に接続することで実現される。導電性薄膜16が電源電位を供給する外部接続パッド141ないし接地電位を供給する外部接続パッド142を覆っているならば、配線部12に何ら配線を追加することなく、導電性薄膜を電位の安定した配線に接続できる。

【0066】

図2には、こうして製作した半導体チップによる三次元集積半導体装置の一例を示した。

【0067】

三次元集積半導体装置100は、半導体チップ10と第二の半導体チップ110で構成される。第二の半導体チップにも、回路要素12が形成されたベース基板11と配線部13、パッシベーション膜14、外部接続パッド15が存在する。半導体チップ10と同110は、互いのベース基板の回路要素形成面を対向するように積層されており、互いの外部接続パッドはマイクロバンプ120で接続される。マイクロバンプは両半導体チップの間の電気的接続も担っており、その材料として単体金属、合金を少なくとも一種類含む。公知の技術をかんがみれば、はんだ、金バンプ、金属膜を備える樹脂バンプなどが好適であろう。

【0068】

三次元集積半導体装置100はインターポーザ300に実装されている。三次元集積半導体装置100とインターポーザ300は、半導体チップ110の外部接続パッドを介して電気的に接続される。その方法として、第一には図2に示すようなワイヤボンディング310によるものが挙げられる。また、ベース基板11を公知の方法で薄くした上で、金属バンプ、もしくははんだボールで接続する方法も適用できる。インターポーザ300は、例えばプリント配線板や多層配線基板、リードフレーム等である。ただし、ビルドアップ多層配線基板やシリコン配線基板のような、微細配線の形成に対応した配線基板を利用するのが望ましい。

【0069】

図3は、本発明に基づいて製作した半導体チップの一例を模式的に示したものである。

【0070】

半導体チップ10は、ベース基板11と、ベース基板表面に形成された回路要素12と、ベース基板の回路要素形成面に、絶縁層と導体層を交互に積層してなる配線部13を備える。また、配線部を構成する導体層のうち、もっともベース基板から遠い層には、外部接続パッド14がある。さらに、配線部のうちベース基板に対向する側の表面には、絶縁材料によるパッシベーション膜15が配される。ただしパッシベーション膜15のうち、外部接続パッド14に対応する部分には開口部が形成されている。

【0071】

ベース基板11は、半導体材料からなる層を最低一つは備えた部材でなければならない。ただし、部材の構成や半導体材料の材質は任意である。

構成としては、全体が単一の材料でできているベース基板は当然利用可能である。また、SOI構造など、異なる半導体材料の層が直接、もしくは絶縁体を介して積層された構成でもよい。

材料として代表的な物を例示するならば、単体半導体であれば単結晶シリコン、単結晶ゲルマニウムなどがある。炭化ケイ素や、ガリウム砒素、リン化インジウムをはじめとする化合物半導体も、ベース基板11の材料として利用可能である。

【0072】

半導体チップ10が備える回路要素12の種類は、本発明を適用する上での制約にはならない。トランジスタ、ダイオード等の能動素子を備えるチップであっても、抵抗などの受動素子を備えるチップであっても、また双方を備えるチップであっても、本発明を適用することができる。

【0073】

配線部13を構成する絶縁層は絶縁体で形成されていればよく、また導体層は導体で形成されていればよい。同様に、パッシベーション膜15も一種類以上の絶縁体を含む膜であればよい。

【0074】

半導体チップ10には、半導体チップの表裏を導通させる貫通電極18が備わっている。貫通電極18は側面に絶縁膜181を持ち、ベース基板11やパッシベーション膜14との間、および配線部13の中の接続すべきでない配線と貫通電極を電気的に分離している。貫通電極の形状や加工プロセスは任意である。貫通電極内部が完全に導電材料で充填された構造でもよいし、貫通電極の側面のみに導電材料が形成されたコンフォーマル構造でもよい。

【0075】

貫通電極の導電性を担う導電材料として、導電性を示すあらゆる材料が採用可能である。単体金属でも、合金でも、半導体でも、導電性フィラーを分散した樹脂でもよい。また、これらの中からいくつかを組み合わせた混合物や積層体を用いることもできる。

【0076】

パッシベーション膜15の上には導電性薄膜16が形成されている。導電性薄膜の構成材料には、各種の単体金属、合金、半導体およびこれらを組み合わせて積層したものが利用できる。また、導電性薄膜16は外部接続パッド14の全面を半導体チップ外部に露出させるための開口部17を持つ。

【0077】

ここで、導電性薄膜16の材料と、貫通電極18を構成する導電材料のうち少なくとも一部が同じものであることを許容できれば、工程の簡略が可能である。

貫通電極に導電材料を埋め込むプロセスでは、貫通電極の内部だけでなく、導電材料を埋め込んだ側のウエハ表面にも余分な導電材料の層が形成されることが多い。一般的なプロセスでは、この余分な導電材料はエッチングやCMPなどで完全に除去した上で次工程に供される。しかし、導電性薄膜16と貫通電極18が同じ材料で形成できるのであれば、余分な導電材料の層で導電性薄膜16をかねることができる。これにより、余分な導電材料の除去工程を簡略、あるいは省略できる。

【0078】

また、導電性薄膜16が電源電位供給用の外部接続パッド141ないし接地電位を供給する外部接続パッド142を覆っているならば、配線部12に配線を追加することなく、導電性薄膜16を電位の安定した配線に接続できる。導電性薄膜16の電位の安定は、電磁波遮蔽性能の向上につながる。

【0079】

導電性薄膜16と同様に、パッシベーション膜15の上に貫通電極パッド19が形成されている。貫通電極18はパッシベーション膜14を貫通しているため、貫通電極18と貫通電極パッド19は直接電気的に接続される。

【0080】

図4は、本発明に基づいて製作した半導体チップと、それを用いた三次元集積半導体装置を模式的に示したものである。

【0081】

半導体チップ10は、ベース基板11と、ベース基板表面に形成された回路要素12と、ベース基板の回路要素形成面に、絶縁層と導体層を交互に積層してなる配線部13とを備える。また、配線部を構成する導体層のうち、最もベース基板から遠い層には外部接続パッド14および貫通電極パッド19がある。さらに、配線部のうちベース基板に対向する側の表面には、絶縁材料によるパッシベーション膜15が配される。ただしパッシベーション膜15のうち、外部接続パッドと貫通電極パッドに対応する部分には開口部17が形成されている。

以上に加えて、ベース基板11を貫通する貫通電極18が存在する。貫通電極18とベース基板11は絶縁膜181で分離される。また、貫通電極18の一部については、その一端と貫通電極パッド19が配線部12の中の配線によって電気的に接続されている。

【0082】

ベース基板11は、半導体材料からなる層を最低一つは備えた部材でなければならない。ただし、部材の構成や半導体材料の種類は任意である。

構成としては、全体が単一の材料でできているベース基板は当然利用可能である。また、SOI基板など、異なる半導体材料の層が直接、もしくは絶縁体を介して積層された構成でもよい。

材料として代表的な物を例示するならば、単体半導体であれば単結晶シリコン、単結晶ゲルマニウムなどがある。炭化ケイ素や、ガリウム砒素、リン化インジウムをはじめとする化合物半導体も、ベース基板11の材料として利用可能である。

【0083】

半導体チップ10が備える回路要素12の種類は、本発明を適用する上での制約にはならない。トランジスタ、ダイオード等の能動素子を備えるチップであっても、抵抗などの受動素子を備えるチップであっても、また双方を備えるチップであっても、本発明を適用することができる。

【0084】

配線部13を構成する絶縁層は絶縁体で形成されていればよく、また導体層は導体で形成されていればよい。同様に、パッシベーション膜15も一種類以上の絶縁体を含む膜であればよい。

【0085】

貫通電極18は、ベース基板の回路要素形成面とその裏面を、もしくは回路要素そのものとベース基板の裏面を導通している。貫通電極の構造や加工プロセスは任意である。貫通電極内部が完全に導電材料で充填された構造でもよいし、貫通電極の側面と底面のみに導電材料の皮膜が形成されたコンフォーマル構造でもよい。

【0086】

貫通電極の導電性を担う導電材料として、導電性を示すあらゆる材料が採用可能である。単体金属でも、合金でも、半導体でも、導電性フィラーを分散した樹脂でもよい。また、これらの中からいくつかを組み合わせた混合物や積層体を用いることもできる。

【0087】

パッシベーション膜15の上には導電性薄膜16が形成されている。導電性薄膜の構成材料には、各種の単体金属、合金、半導体およびこれらを組み合わせて積層したものが利用できる。導電性薄膜16は、外部接続パッド14および貫通電極パッド19を露出させる開口部17を持つ。

【0088】

ここで、導電性薄膜16が電源電位を供給する外部接続パッド141ないし接地電位を供給する外部接続パッド142を覆っているならば、配線部12に配線を追加せずに、導電性薄膜16を電位の安定した配線に接続できる。導電性薄膜16の電位が安定することは、電磁波遮蔽性能の向上につながる。

【0089】

図5には、こうして製作した半導体チップによる三次元集積半導体装置の一例を示した。

【0090】

三次元集積半導体装置100は、半導体チップ10と第二の半導体チップ110、第三の半導体チップ210で構成される。第二、第三の半導体チップにも、回路要素12が形成されたベース基板11と、配線部13、パッシベーション膜14、外部接続パッド15が存在する。また、第三の半導体チップ210は貫通電極18と貫通電極パッド19を持つ。半導体チップ10と同110は、互いのベース基板の回路要素形成面を対向するように積層されており、互いの外部接続パッドはマイクロバンプ120で接続される。一方、半導体チップ10と210は、互いのベース基板の回路要素形成面が、ベース基板を介して対向するよう積層されている。半導体チップ10と同210は、互いの貫通電極の端面を結合するマイクロバンプ220で接続されている。マイクロバンプは単体金属、合金のうち少なくとも一種類で構成される。公知の技術をかんがみれば、はんだ、金バンプ、金属膜を備える樹脂バンプなどが好適であろう。

【0091】

三次元集積半導体装置100はインターポーザ300に実装される。三次元集積半導体装置100とインターポーザ300は、半導体チップ210の外部接続パッド14と貫通電極パッド19を介して電気的に接続される。接続にあたっては、図2に示すような金属バンプ320による方法のほか、ボンディングワイヤ、ACFなどが適用できる。インターポーザ300は、例えばプリント配線板や多層配線基板、リードフレーム等である。ただし、ビルドアップ多層配線基板やシリコン配線基板のような、微細配線の形成に対応した配線基板を利用するのが望ましい。

【実施例1】

【0092】

この実施例では、貫通電極を持たない半導体チップをもとに、電磁妨害耐性の高い半導体チップを製作した際の手順を説明する。さらに、その半導体チップを用いて三次元集積半導体装置を製作する手順も説明する。図6から図13は、半導体チップおよび半導体装置の加工手順を説明する図である。

【0093】

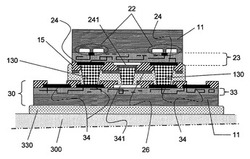

第一の準備工程として、個片化されている第一のテストチップ20を用意した。図6に示すとおり、第一のテストチップ20は、単結晶シリコン製のベース基板11、CMOSトランジスタによるドライバ22、配線部23、アルミニウム製の外部接続パッド24、同じくアルミニウム製の電源供給のための外部接続パッド241、ポリイミド製のパッシベーション膜15を備える。パッシベーション膜には全ての外部接続パッドを半導体チップ外部に露出させるために直径70μmの円形の開口が設けられていた。

【0094】

第二の準備工程として、個片化済みの第二のテストチップ30を用意した。第二のテストチップ30の大まかな構成は図7に示すとおりであり、単結晶シリコン製のベース基板11、配線部33、アルミニウム製の外部接続パッド34、同じくアルミニウム製の電源供給のための外部接続パッド341、ポリイミド製のパッシベーション膜15を備える。パッド34および同341のうち領域301に含まれるものは、第一のテストチップのパッド24や241と対応する配列に配置される。(図8の平面図を参照)

【0095】

第一工程として、第一のテストチップ20のうちパッシベーション膜25が形成された側の表面へ、開口部27が設けられた銅薄膜26を形成した。開口部27は外部接続パッド24を露出するように設けられる一方、電源供給用パッド241は銅薄膜26に覆われるようにした。銅薄膜の厚さは0.7μmであった。

第一工程は、以下に示す第一補工程の一と二の組み合わせで行った。

【0096】

第一補工程の一として、第一のテストチップ20のパッシベーション膜25形成面全体にスパッタリングによる銅薄膜26を形成した。(図示せず)

第一補副工程の二として、フォトレジスト1000を用いたパターニングと選択的ウエットエッチングにより、図9(a)のように銅薄膜26に開口部17を形成した。開口部17は直径75μmの円形とし、その中心はパッシベーション膜15の開口部と一致させた。ウエットエッチングに際しては、銅薄膜を除去し、アルミニウムを侵さない公知のエッチング液を用いた。

その後、フォトレジスト1000は除去してから次の工程へ進んだ。

【0097】

また、以下の第一補工程の三から五を行うことでも、第一工程を完遂できた。

【0098】

第一補工程の三としては、第一のテストチップ20のパッシベーション膜25形成面に対してフォトレジストのパターンを形成した。(図示せず)

続く第一補工程の四として、スパッタリングによる銅薄膜の形成を行った。

その上で、第一補工程の五として、フォトレジストパターンをその表面の銅薄膜ごとリフトオフした。以上の補工程から、図9(b)のように、所望の位置に開口部17を備える銅薄膜26を得た。

【0099】

第二工程として、第一のテストチップ20のパッド24の表面、および無電解銅薄膜26の表面に金でできたスタッドバンプ130を形成した。スタッドバンプ形成後の模式図を図10に示す。スタッドバンプ130の形成は、ワイヤボンダと金ワイヤを用いる公知の方法によって行った。スタッドバンプの高さは30μmとした。

【0100】

第三工程として、三次元集積半導体装置100の組み立てを行った。

まず、インターポーザ300の表面に第二のテストチップ30を、パッド34が露出するように接着剤140で固定した。

続いて第二のテストチップ30に対して第一のテストチップ20をフリップチップ接続した。二つのチップ間の電気的接続は、スタッドバンプ130を利用して実現した。

最後に、チップ間の空隙に熱硬化性のアンダーフィル材330を充填し、大気中で加熱硬化した。(図11)

【0101】

第四工程として、三次元集積半導体装置100とインターポーザ300を電気的に接続した。(図12)この電気的接続は、外部接続パッド34とインターポーザ300をボンディングワイヤ310で接続することで実現した。

【0102】

完成した三次元集積半導体装置について、その電気的特性の評価を行った。

【0103】

図13は、三次元集積半導体装置100を、電気的な構造に注目して抽象化した模式図である。テストチップ20内のドライバ22については、入力信号配線231、出力信号配線232とも、外部接続パッド24、バンプ130を経由してテストチップ30の配線部33へ引き出されている。これらの配線はさらに外部接続パッド34を経て、装置外の評価システムに接続される。またテストチップ30の配線部33には、上記の系とは別に、配線231、232と平行に配されたモニター用の配線331がある。この配線もまた、装置外の測定システムに接続されている。

【0104】

ドライバ22を動作させた場合に、モニター用の配線331に生じるクロストーク・ノイズの測定結果を表1に示す。表1における対象例とは、三次元集積半導体装置100と同様の装置を、銅薄膜16を設けないテストチップで組み立てたものの測定結果である。

【表1】

【実施例2】

【0105】

この実施例では、貫通電極を備えるとともに、高い電磁妨害耐性を示す半導体チップを製作した際の工程を説明する。また、製作した半導体チップを含む三次元集積半導体装置を製作した際の工程もあわせて説明する。図15から図24は、半導体チップおよび半導体装置の加工手順を説明する図である。

【0106】

第一の準備工程として、メモリチップ40が一面に形成されたメモリウエハ400を用意した。ウエハの直径は200mm、ウエハの厚さは405μmであった。

個々のメモリチップの断面構造を図14に示す。個片で見た場合のメモリチップ40は、SOI基板からなるベース基板11(詳細な構造は図示せず)、CMOSトランジスタと受動素子からなるメモリ回路42、配線部13、金で被覆されたアルミニウム製の外部接続パッド14、同じく金被覆アルミニウム製の接地電位供給のための外部接続パッド142、窒化シリコン製のパッシベーション膜15を備える。パッシベーション膜には全ての外部接続パッドを半導体チップ外部に露出させるため、直径50μmの円形の開口が設けられていた。

【0107】

配線部13の中には、貫通電極と配線部の導通を得るため外部接続パッド14と同じ層に配置されたランド構造143、ランド構造143とメモリ回路を接続する内部配線、メモリ回路と外部接続パッドを結ぶ外部接続配線が配置されていた。(いずれも図示せず)

【0108】

第二の準備工程として、マイコンチップ50を用意した。マイコンチップ50の大まかな構成は図15に示すとおりであり、単結晶シリコン製のベース基板11、マイコン回路52、配線部13、金で被覆されたアルミニウム製の外部接続パッド14、同じく金被覆アルミニウム製の接地電位供給のための外部接続パッド142、ポリイミド製のパッシベーション膜15を備える。パッシベーション膜には全ての外部接続パッドを半導体チップ外部に露出させるため、直径50μmの円形の開口が設けられていた。

【0109】

第一工程として、メモリウエハ400の所定の位置に、貫通電極のもととなる貫通孔182を形成した。(図16)ここでいう所定の位置とは、前記ランド構造が配置された部分を含む。貫通孔182の加工には、公知の方法であるボッシュプロセスを用いた。孔の断面は直径35μmの円とした。また孔のピッチは最も狭い部分で150μmであった。

【0110】

第二工程として、ベース基板11や配線部13中の配線と、貫通電極を絶縁するための絶縁膜181を形成した。図17に示すように、テトラエトキシシランを材料とするプラズマCVD(化学気相成長法)で、二酸化ケイ素の薄膜181をメモリウエハ400の表面全体に形成した。薄膜481の厚さは貫通孔182の側面で平均0.17μmであった。

【0111】

第三工程として、絶縁膜181のうち、外部接続パッド14と142、およびランド構造143を被覆する部分を除去した。感光性エッチングレジストとドライエッチングを用いた公知の選択的エッチングプロセスで、絶縁膜181の不要部分を除去できた。エッチングレジスト除去後のメモリウエハの模式図を図18に示す。

【0112】

第四工程として、導電性薄膜46と貫通電極パッド49の形成と、貫通孔482側面への導体材料部形成を行った。これは、以下の第四補工程の一から五に示すプロセスで行った。

【0113】

第四補工程の一として、バリアメタルとなる窒化チタン薄膜183を、スパッタリングでメモリウエハ400表裏の露出面全体に形成した。工程終了時の模式図を図19に示す。貫通孔182側面のバリアメタル厚は平均0.08μmであった。

【0114】

第四補工程の二として、めっきシード層となる銅薄膜を、スパッタリングでメモリウエハ400の表裏全面に形成した。(図示せず)貫通孔182側面の銅薄膜の厚さは平均で0.54μmであった。

【0115】

第四補工程の三として、所望の形状の導電性薄膜46、貫通電極パッド49および491を作るためのめっきレジストパターン(図示せず)を形成した。

【0116】

第四補工程の四として、外部接続パッド14に対して開口部17を備える導電性薄膜46、貫通電極パッド49と491、ならびに貫通孔182側面の導体材料部を形成した。この補工程は窒化チタン薄膜をシード層とする電解銅めっきで行った。電解銅の厚さはメモリウエハ表面で平均5μm、貫通電極側面で平均3.4μmであった。めっき完了後、めっきレジストパターンは除去した。

【0117】

第四補工程の五として、銅薄膜、ならびに窒化チタン薄膜183の不要部分をウエットエッチングで除去した。(図20)

【0118】

第五工程として、上記の第四工程までを実施した第二のメモリウエハ401を用意し、このウエハの外部接続パッド14、142と貫通電極パッド49、491の表面に金スタッドバンプ130、1301を形成した。(図21)スタッドバンプ130の形成は、ワイヤボンダと金ワイヤを用いる公知の方法によって行った。スタッドバンプ130の高さは40μm、スタッドバンプ1301の高さは20μmとした。

【0119】

第六工程として、メモリウエハ400と第二のメモリウエハ401を接合した。

予めメモリウエハ400の裏面に未硬化の熱硬化性アンダーフィル材料330を塗布した上で、スタッドバンプ130を用いた公知の圧着プロセスによって両メモリウエハの貫通電極パッド491を接合した。その後、アンダーフィル材料330を硬化させた。(図22)

【0120】

第七工程として、接合した二枚のメモリウエハを分割し、個々の積層メモリチップ101を得た。(図示せず)ウエハの分割には公知のウエハダイシング技術を用いた。

【0121】

第八工程として、積層メモリチップ101をインターポーザ300に実装した。図23の通り、金スタッドバンプ1301による圧着をもって、積層メモリチップ101とインターポーザ300を電気的に接続した。その後、熱硬化性アンダーフィル材330を注入、熱硬化させた。

【0122】

第九工程として、マイコンチップ50と積層メモリチップ101を接合して、三次元集積半導体装置100を完成させた。(図24)マイコンチップ50の外部接続パッド14に対して高さ20μmの金スタッドバンプ130を形成し、これをもって両チップの外部接続パッドを物理的、電気的に接続した。

【0123】

完成した三次元集積半導体装置100について、その特性を評価した。図25に本実施例で製作した三次元集積化半導体装置100のシュム・プロットを示した。一方、対象例として本発明を適用しないマイコンチップとメモリチップで試作した三次元集積半導体装置のシュム・プロットを、図26に示した。図25で背景に色の付いた部分が、本発明の効果によってメモリ特性が改善した部分である。

【実施例3】

【0124】

この実施例では、貫通電極を備えた半導体チップを使って、高い電磁妨害耐性を示す半導体チップを製作した際の工程を説明する。また、製作した半導体チップを含む三次元集積半導体装置を組み立てた際の工程もあわせて説明する。図27から図37は、半導体チップおよび半導体装置の加工手順を説明する図である。

【0125】

第一の準備工程として、メモリチップ60が一面に形成されたメモリウエハ600を用意した。ウエハの直径は150mm、ウエハの厚さは625μmであった。

個々のメモリチップの断面構造を図27に示す。個片で見た場合のメモリチップ60は、SOI基板からなるベース基板61(詳細な構造は図示せず)、CMOSトランジスタと受動素子からなるメモリ回路42、配線部13、金で被覆されたアルミニウム製の外部接続パッド14、同じく金被覆アルミニウム製の接地電位供給のための外部接続パッド142、窒化シリコン製のパッシベーション膜15を備える。パッシベーション膜には全ての外部接続パッドを半導体チップ外部に露出させるため、直径50μmの円形の開口が設けられていた。

【0126】

ベース基板61には、導電性シリコンが充填されたビアホール682が形成されている。ビアホール682は直径10μm、深さ110μmの円柱状で、その側壁には二酸化ケイ素による絶縁膜681が設けられている。ビアホール間のピッチは最も狭いところで25μmであった。またビアホール681は、配線部13を経由して貫通電極パッド19と電気的に接続されていた。

【0127】

第二の準備工程として、マイコンチップ50を準備した。これは実施例2で用いたマイコンチップと全く同一のものである。(図15参照)マイコンチップ50に対しては、外部接続パッド14、142上に金でできた高さ30μmのスタッドバンプ130を公知の方法で形成しておいた。

【0128】

第三の準備工程として、ガリウム砒素薄膜66、ならびにガリウムインジウム砒素薄膜661が積層された、ガリウム砒素製のブランクウエハ1010を準備した。(図28)支持ウエハは直径150mmの円形で、その表面には厚さ1.2μmの円形のアルミニウム砒素薄膜661が形成されていた。さらにその上に、直径145mm、厚さ10μmの円形のガリウム砒素薄膜66が形成されていた。ガリウム砒素薄膜は炭素でドープされており、その抵抗率は1.47Ω・cmであった。

【0129】

第一工程として、ガリウム砒素薄膜66に対して開口部17を形成した。開口部の形成は、ガリウム砒素薄膜66のうち所定の部分を、公知のエッチャントを用いたウエットエッチングで除去することで行った。開口部17形成後のブランクウエハ1010を図29に示す。開口部17の径は58.5μmであった。

【0130】

ガリウム砒素薄膜66は後の工程でメモリウエハ600に転写される。そこで、開口部67の配置は、ガリウム砒素薄膜66を転写した際に外部接続パッド64、貫通電極パッド69を全て露出させるように定めた。

【0131】

第二工程として、メモリウエハ600とブランクウエハ1010を貼り合わせた。

まず、ポリイミドを主成分とする感光性接着剤1401をメモリウエハ600の配線層側表面に貼り付けたあと、全ての外部接続パッド14、142および貫通電極パッド69を露出させるパターンを形成した。

次いで、感光性接着剤1401を用いて、メモリウエハ600とブランクウエハ1020を接着した。このとき、ブランクウエハ1010はガリウム砒素薄膜66が形成された面を接着面とした。

第二工程の最後に、感光性接着剤1401を熱硬化させ、二枚のウエハを完全に固着させた。第二工程完了時のウエハの模式図を図30に示す。

【0132】

第三工程として、ベース基板61に埋設されたビアホール682を裏面に露出させて貫通電極68とした。メモリウエハ600をベース基板側から、BG(Back Grinding)とCMPを用いて厚みが100μmになるまで研削した。その後、図31に示す通り、メモリウエハ600の研削面全面に対し、低温CVDによる二酸化ケイ素のパッシベーション膜651を形成した。ただし貫通電極68の端部のみはパッシベーション膜651で被覆することなく、露出させた。

【0133】

第四工程として、貫通電極68のベース基板61側端部に、半導体チップ積層用のメタルポスト150を設けた。メタルポスト150は銅で形成し、ベース基板表面からの高さは5μmとした。また、メタルポスト150の頂面には、厚さ2μmのスズ薄膜1501を形成した。(図32)

メタルポスト150とスズ薄膜1501の形成は、スパッタ銅をめっきシード層とする公知の電解めっきアディティブプロセスで実施した。

【0134】

第五工程として、ブランクウエハ1010をメモリウエハ600から剥離した。まず、メモリウエハ600のベース基板側にガラス製のサポートウエハ1020を耐酸性接着フィルム1030で貼り付けた。このとき、メタルポスト150全体を接着フィルムに埋設した。次いでメモリウエハ600を塩酸に浸漬し、ガリウムインジウム砒素薄膜681を除去した。第五工程完了時のウエハ600の模式図を図33に示す。

【0135】

第六工程として、上記第四工程までを適用した第二のメモリウエハ601を用意し、メモリウエハ600と電気的、物理的に接合した。(図34)ウエハ間で対応する外部接続パッド64とメタルポスト150、および貫通電極パッド69とメタルポスト150をアライメントした上で、リフローによって一括で接合した。その後、ウエハ間にアンダーフィル材料(図示せず)を充填・硬化した。

【0136】

第七工程として、第五工程と同様に、第二のメモリウエハに接合したブランクウエハ1010を除去した。

【0137】

第八工程として、ガラス製の第二のサポートウエハ1021を、外部接続パッド14の露出する面へ新たに貼り付けるとともに、サポートウエハ1020の剥離を行った。(図35)

【0138】

第九工程として、メモリウエハ600、601およびサポートウエハ1021を一括でダイシングし、個々の積層メモリ102へと分離した。(図示せず)

【0139】

第十工程として、積層メモリ102をビルドアップ多層基板によるインターポーザ330に実装した。実装にはメタルポスト150を用いた。この後、個片化したサポートウエハ1021を剥離した。(図36)

【0140】

第十一工程として、マイコンチップ50と積層メモリチップ101を接合して、三次元集積半導体装置100を完成させた。(図37)

【0141】

完成した三次元集積半導体装置100について、その特性を評価した。図38に本実施例で製作した三次元集積化半導体装置100のシュム・プロットを示した。一方、対象例として本発明を適用しないマイコンチップとメモリチップで試作した三次元集積半導体装置のシュム・プロットを、図39に示した。図38で背景に色の付いた部分が、本発明の効果によってメモリ特性が改善した部分である。

【符号の説明】

【0142】

1…3D−SiP

10、110、210…半導体チップ

11、61…ベース基板

12…回路要素

13、23、33…配線部

14、24、34…外部接続パッド

15…パッシベーション膜

16…導電性薄膜

17…導電性薄膜の開口部

18、68…貫通電極

19、49…貫通電極パッド

20、30…テストチップ

22…CMOSによるドライバ

26…銅薄膜

40、60…メモリチップ

42、62…メモリ回路

50…マイコンチップ

52…マイコン回路

66…ガリウム砒素薄膜

100…三次元集積半導体装置

101…積層メモリチップ

120…マイクロバンプ

130、1301…スタッドバンプ

140、1401…接着剤

141、241、341…電源供給のための外部接続パッド

142…接地電位供給のための外部接続パッド

143…ランド構造

150…メタルポスト

181…貫通電極側面の絶縁皮膜

182…貫通孔

183…バリアメタル

231…入力信号配線

232…出力信号配線

300…インターポーザ

310…ボンディングワイヤ

320…はんだバンプ

330…アンダーフィル材料

331…モニター配線

400、401、600、601…メモリチップウエハ

491…半導体チップ裏面の貫通電極パッド

651…裏面側のパッシベーション膜

681…ビアホール側面の絶縁皮膜

682…ビアホール

1000…フォトレジスト

1010…ブランクウエハ

1020、1021…サポートウエハ

1030…接着フィルム

1501…スズ薄膜

【技術分野】

【0001】

本発明は半導体装置に係り、詳しくは半導体チップの電磁妨害耐性を向上させる構造とその製法、ならびに電磁妨害耐性に優れる半導体装置の構造に関する。

【背景技術】

【0002】

電子機器に対する、市場からの小型化・高機能化・多機能化への要請はとどまるところを知らない。この要請に応えるため、電子機器に搭載される半導体装置についても、小型化・高機能化が求められている。

【0003】

半導体装置の小型化・高機能化・多機能化を実現する一手法として、複数の半導体チップや受動素子を立体的に集積した三次元集積半導体装置が注目を集めている。単一の半導体チップのみで高機能化を図るのと同等以上の効果を、容易に得ることができるためである。

【0004】

三次元集積半導体装置を実現する手法として、すでにスタックト・ダイ工法やパッケージ・オン・パッケージ工法が実用化されている。スタックト・ダイ工法とは、複数の半導体チップを立体的に積み重ね、個々の半導体チップとインターポーザをボンディングワイヤで接続する工法である。パッケージ・オン・パッケージ工法とは、インターポーザに実装済みの半導体チップを複数用意し、それらを積み重ねた後はんだボールなどで接続する工法である。

【0005】

一方近年では、3D−SiP(3D−System in Package)とも呼ばれる、半導体チップを貫通する電極を用いた三次元集積半導体装置の開発が盛んである(例として、特許文献1)。3D−SiPでは積み重ねた複数の半導体チップを、その半導体チップを貫通する多数の貫通電極で直接に接続する。半導体チップ間の通信がボンディングワイヤよりもはるかに短い配線で、インターポーザを経由せずに行えるため、三次元集積半導体装置全体の処理能力が、スタックト・ダイ工法やパッケージ・オン・パッケージ工法によるものに比べて飛躍的に向上する。

【0006】

図40は、典型的な3D−SiPの構成を示す説明図である。

3D−SiP1は、回路要素12と、回路要素間の電気的接続のための配線を含む配線部13を備えた三種類の半導体チップ10、110、210を、その厚さ方向に積み上げて構成されている。半導体チップ10は、表面上の回路要素12が図中下向きに配置されている。一方、半導体チップ110および210は、回路要素12が図中上向きとなるよう配されている。つまり、半導体チップ10と110は3D−SiP1において、配線部13が形成された表面を相互に対向させた状態で組みつけられている。このような組みつけ方をフェイス・トゥ・フェイス接続と呼ぶ場合がある。

【0007】

各々の半導体チップに形成された回路要素12は、所定の回路機能を実現する電気的部品である。例示するならば、ベース基板を用いて形成されたトランジスタ等の能動素子やベース基板表面などへ形成された受動素子である。

【0008】

半導体チップ110、同210の内部には、一端が半導体チップの裏面(図中下面)に露出する貫通電極18がそれぞれ設けられている。また、配線部13を構成する配線の一部は、回路要素12と貫通電極18、および貫通電極18間の相互接続に用いられる。各貫通電極18は、貫通電極を取り囲むように形成された絶縁膜(図示せず)で、半導体チップから絶縁される。

【0009】

半導体チップ10と同110の間、および半導体チップ110と同210の間はマイクロバンプ120でそれぞれ物理的、電気的に接続される。各マイクロバンプは、図示しない絶縁材によって相互に電気的に絶縁されている。また、半導体チップ210を貫通する貫通電極18のチップ裏面側端面には、パッド214が存在する。3D−SiP1は、このパッドを経由して半導体チップ外部と電気的に接続される。

【0010】

上記の通り、典型的な3D−SiPでは、集積される半導体チップの配線部がマイクロバンプ高さの距離、あるいは半導体チップの厚さの距離を隔てて近接する。その距離は、はなはだしい場合は20μm以下にまで縮小する。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】公開公報 WO06/019156

【特許文献2】特開2006−179806

【特許文献3】特許第3532788号

【発明の概要】

【発明が解決しようとする課題】

【0012】

このように複数の配線部が近接した構造では、一方の配線部に含まれる配線が放射する電磁界が、他方の配線部に含まれる配線に伝播して生じるクロストーク・ノイズが増大する。強力なクロストーク・ノイズは、ノイズが乗った配線に接続される回路要素を誤動作させ、ひいては三次元集積半導体装置の異常動作を引き起こす。

【0013】

三次元集積半導体装置における、半導体チップ間のクロストーク・ノイズを対策する構造の一種として、特許文献2に開示された発明を例示する。この発明においては、立体的に集積する半導体チップの、配線部が形成されている部分以外の表面に対して金属膜を形成する。さらに前記金属膜を接地電位に接続して、前記金属膜を不要電磁波を遮蔽するシールドに用いる。

【0014】

しかし前記発明に基づく半導体装置では、配線部が形成された表面には全く防護手段が施されていない。そのため、図40における半導体チップ10および110のごとく、配線部が形成された表面を相互に対向させた状態で半導体チップを集積した場合、クロストーク・ノイズを回避する手立てはない。

【0015】

三次元集積半導体装置における、半導体チップ間のクロストーク・ノイズを対策する構造の更なる例として、特許文献3に開示された発明を例示する。この発明においては、立体的に集積される個々の半導体チップに対して、配線部の表面全面に金属薄膜を形成する。この金属薄膜は、半導体チップを常温接合技術で集積する際の接合層になるとともに、半導体チップの放射ノイズを抑制するシールド層としても働く。この発明に基づく半導体装置であれば、配線部を不要電磁波から防護することは可能である。

【0016】

しかし、前記発明に基づく半導体装置には、常温接合技術に起因する複数の技術的課題が存在する。

【0017】

第一の課題は、配線層表面の金属層をきわめて平坦に形成しなければならない点である。常温接合技術における接合層には、サブミクロンオーダーでの平坦性が求められる。しかし半導体チップでは、配線部の表面にμmオーダーの凹凸が存在するのが通常である。また、μmオーダーの凹凸がある表面に平坦に金属薄膜を形成できるプロセスは存在しない。よって、前記発明を実用するにあたっては、配線部表面へ金属層を形成する工程に加えて、金属層を平坦化する工程が必須となる。

【0018】

第二の課題は、チップ・トゥ・ウエハ接続プロセスの採用が困難となる点である。

常温接合技術では、接合面の清浄度が接合性に大きく影響する。そのため、接合直前に表面のクリーニングを行う必要がある。

ウエハ・トゥ・ウエハ接続であればこの特徴は問題にならない。一回の処理で多数のチップを一括で接合できるためだ。一方、チップ・トゥ・ウエハ接続に常温接合技術を適用する場合は、プロセスコストの大幅な増大が懸念される。前述の通り、常温接合技術においては接合面に高い清浄度が求められるため、ウエハ側の表面を、チップ接合工程の全ての時間にわたって清浄に保つ必要がある。これはチップ接合工程を全て真空系の中で行うことで可能となるが、それを実現する装置は装置そのもののコストも、ランニングコストも許容できない水準となるだろう。

【0019】

他方、当業者においては半導体チップ間のクロストーク対策として、配線部の中に不要電磁波を遮蔽するような導体構造を設ける手法が考案できるであろう。例としては、配線部のいずれかの導体層に、回路要素を被覆するような大面積の導体パターンを設ける方法などが考えられる。

【0020】

しかし前記の手法では、配線部の配線収容能力が低下する。配線部内に半導体チップの機能には不要な導体構造が形成される以上避けられない問題であり、この問題を解消するには、配線部を構成する導体層を増やすしかない。だが、配線部の導体層を増やすことは、半導体チップの生産コストの上昇に直結する。

【0021】

これに加えて、CMP(化学機械研磨法)や銅配線が適用される高度な半導体チップでは、大面積の導体パターンを形成することそのものにも技術的困難が存在する。大面積の銅パターンをCMPで平坦化すると、銅層表面が凹状に削れるディッシング(段差)が発生し、その後の工程にも支障が生じるためである。

【0022】

本発明は上記課題を鑑みてなされたものであり、立体的な集積に適した、電磁妨害耐性に優れる半導体チップの提供を目的としている。

【課題を解決するための手段】

【0023】

上記の目的を達成するための請求項1に係る発明は、半導体チップのうち、半導体材料の層を少なくとも一つ含むベース基板と、前記ベース基板の表面において能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち、前記ベース基板から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、前記外部接続パッドが形成された導体層を被覆し、かつ前記外部接続パッドをチップ外部に露出させるような開口部を備えた絶縁体からなるパッシベーション層とを備えるものであって、さらに、前記ベース基板に対して前記配線部および前記パッシベーション層を離隔した位置に、少なくとも一種類の金属ないし合金からなる導電性薄膜を具備し、かつ前記導電性薄膜のうち前記外部接続パッドに対応する部分には、第二の開口部が設けられていることを特徴とする半導体チップである。

【0024】

請求項2にかかる発明は、請求項1に記載の半導体チップにおいて、さらに前記ベース基板を厚さ方向に貫通する貫通電極を備えることを特徴とする半導体チップである。

【0025】

請求項3にかかる発明は、下記の1)、2)のうち少なくともいずれか一方を含むことを特徴とする、請求項2に記載の半導体チップである。

1)前記配線部に配置された、前記貫通電極と前記回路要素を電気的に接続するための内部配線。

2)前記配線部を形成する導体層のうち最も前記ベース基板から離れた層に形成され、前記外部配線に接続されていない貫通電極パッド、および前記貫通電極パッドと前記貫通電極を電気的に接続するために前記配線部に配置された貫通配線。

【0026】

請求項4にかかる発明は、前記貫通電極が前記ベース基板に加えて前記配線部を厚さ方向に貫通していることを特徴とする、請求項2および3に記載の半導体チップである。

【0027】

請求項5にかかる発明は、前記貫通電極の内部が導電材料で埋め込まれていることを特徴とする、請求項2から4に記載の半導体チップである。

【0028】

請求項6にかかる発明は、前記導電材料と前記導電性薄膜を形成する材料とが、共通の材料を含むことを特徴とする、請求項5に記載の半導体チップである。

【0029】

請求項7にかかる発明は、半導体チップのうち、半導体材料の層を少なくとも一つ含むベース基板と、前記ベース基板の表面において能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち、前記ベースから最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、前記外部接続パッドが形成された導体層を被覆し、かつパッドをチップ外部に露出させるような開口部を備えた絶縁体からなるパッシベーション層とを備えるものであって、さらに、前記ベース基板に対して前記配線部を離隔した位置に、少なくとも一種類の半導体材料を含む導体からなる導電性薄膜を具備し、かつ前記導電性薄膜のうち前記外部接続パッドに対応する部分には、第二の開口部が設けられていることを特徴とする半導体チップである。

【0030】

請求項8にかかる発明は、前記導電性薄膜に含まれる半導体材料が、1.5Ω・cm以下の比抵抗を示すことを特徴とする、請求項7に記載の半導体チップである。

【0031】

請求項9にかかる発明は、請求項7または8に記載の半導体チップにおいて、さらに前記ベース基板を厚さ方向に貫通する貫通電極を備えることを特徴とする半導体チップである。

【0032】

請求項10にかかる発明は、前記配線部の中に、下記の1)、2)のうち少なくともいずれか一方を含むことを特徴とする、請求項9に記載の半導体チップである。

1)前記配線部に配置された、前記貫通電極と前記回路要素を電気的に接続するための内部配線。

2)前記配線部を形成する導体層のうち最も前記ベース基板から離れた層に形成され、前記外部配線に接続されていない貫通電極パッド、および前記貫通電極パッドと前記貫通電極を電気的に接続するために前記配線部に配置された貫通配線。

【0033】

請求項11にかかる発明は、前記貫通電極が前記配線部を厚さ方向に貫通していることを特徴とする、請求項9および10に記載の半導体チップである。

【0034】

請求項12にかかる発明は、前記貫通電極の内部が導電材料で充填されていることを特徴とする、請求項9から11に記載の半導体チップである。

【0035】

請求項13にかかる発明は、前記導電材料と前記導電性薄膜を形成する材料とが、共通の材料を含むことを特徴とする、請求項12に記載の半導体チップである。

【0036】

請求項14にかかる発明は、前記導電性薄膜が不要電磁波の遮蔽のために設けられていることを特徴とする、請求項1から13に記載の半導体チップである。

【0037】

請求項15にかかる発明は、前記導電性薄膜が、前記配線部のうち電源電位を供給する部分に接続されていることを特徴とする、請求項1から14に記載の半導体チップである。

【0038】

請求項16にかかる発明は、前記導電性薄膜と前記電源電位を供給する配線部との電気的接続を、電源電位を供給するための前記外部接続パッドを前記導電性薄膜で被覆して得ていることを特徴とする、請求項15に記載の半導体チップである。

【0039】

請求項17にかかる発明は、前記導電性薄膜が、前記配線部のうち接地電位を供給する部分に接続されていることを特徴とする請求項1から14に記載の半導体チップである。

【0040】

請求項18にかかる発明は、前記導電性薄膜と前記接地電位を供給する配線部との電気的接続を、接地電位を供給するための前記外部接続パッドを前記導電性薄膜で被覆して得ていることを特徴とする、請求項17に記載の半導体チップである。

【0041】

請求項19にかかる発明は、請求項1から18に記載の半導体チップを少なくとも一つ含んだ、複数の半導体チップを立体的に集積したことを特徴とする三次元集積半導体装置である。

【0042】

請求項20にかかる発明は、請求項19に記載の三次元集積半導体装置において、請求項1から18に記載の半導体チップと電気的に接続される第二の半導体チップが、半導体材料からなり、少なくとも一つの表面を備える第二ベースと、前記第二ベース基板の表面に形成された第二配線部とを備えており、かつ、請求項1から18に記載の半導体チップと前記第二の半導体チップが、前記ベース基板の前記回路要素が形成された表面と、前記第二ベース基板の前記第二配線部が形成された表面が互いに近接するように集積されていることを特徴とする、請求項19に記載の三次元集積半導体装置である。

【0043】

請求項21にかかる発明は、下記(a)から(c)の工程を含むことを特徴とする、半導体チップの製造方法である。

(a)半導体チップのうち、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドとを具備する半導体チップを準備する工程。

(b)前記配線部の表面に導電性薄膜を形成する工程。

(c)導電性薄膜のうち、前記外部接続パッドを被覆している部分に第二の開口部を設ける工程。

【0044】

請求項22にかかる発明は、下記(a)から(f)の工程を含むことを特徴とする、半導体チップの製造方法である。

(a)半導体チップのうち、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドとを具備する半導体チップを準備する工程。

(b)前記半導体チップに、貫通電極となる孔を加工する工程。

(c)前記孔の側面に絶縁皮膜を形成する工程。

(d)前記孔の内部に導電材料の膜を形成し、半導体チップの両面を導通する工程。

(e)前記配線部の表面に導電性薄膜を形成する工程。

(f)前記導電性薄膜のうち、前記外部接続パッドを被覆している部分に第二の開口部を設ける工程。

【0045】

請求項23にかかる発明は、下記(a)から(c)の工程を含むことを特徴とする、半導体チップの製造方法である。

(a)半導体チップのうち、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、導電材料で側面を覆われたトレンチとを具備する半導体チップを準備する工程。

(b)前記配線部の表面に前記導電性薄膜を形成する工程。

(c)前記半導体チップの裏面を研削し、前記トレンチの内部に形成された前記導電材料を一部露出させる工程。

(d)前記導電性薄膜のうち前記外部接続パッドを被覆している部分に、第二の開口部を設ける工程。

【発明の効果】

【0046】

本発明の特徴は、半導体チップのうち、回路要素と配線部が形成された表面に不要電磁波を遮蔽するための導電性薄膜を形成することにある。半導体チップに、配線部の内部では形成が困難あるいは非効率な導電性薄膜を付与し、これをもって不要電磁波を原因とする誤動作に耐性を備えた半導体装置を提供可能とする。

【0047】

導電性薄膜には、半導体チップの外部接続パッドを半導体チップの外部に露出させる、第二の開口部が形成される。これは、半導体チップの内部に形成された回路要素とチップ外の回路を接続するためである。

【0048】

本発明の提示する構造は、貫通電極を備える半導体チップにも適用可能である。貫通電極の構造の違いは本発明の効果に影響しないためだ。また、半導体チップに貫通電極を形成する工程もビアファースト法、ビアミドル法、ビアラスト法のいずれを選択してもよい。さらに、貫通電極の内部に導電材料を充填するか否かも、用途に合わせて選択可能である。

【0049】

前記導電性薄膜の材料は、単体金属、合金、半導体およびこれら複数の組み合わせのいずれでもよい。半導体を用いる場合は、ドーピングなどの手法で比抵抗を低下させるのが望ましい。また、貫通電極内部の導電材料と同じ材料を選択すると、より少ない工程で半導体チップを製造することが可能となる。

【0050】

前記導電性薄膜を、常に一定の電位を供給する電源電位の配線、あるいは接地電位の配線に接続すると、不要電磁波の遮蔽能力が向上する。

【0051】

本発明に基づいて提供される半導体チップは、3D−SiPなど複数の半導体チップを立体的に集積した三次元集積半導体装置の構成要素として好適である。特に複数の半導体チップを、双方の配線部を互いに近接するように対向させる場合は、前記導電性薄膜によるクロストーク・ノイズ抑制機能が最大限に発揮される。

【0052】

本発明に基づいて提供された半導体チップを三次元集積半導体装置の一部として用いるにあたって、半導体チップ間を接合する材料、工法には一切の制限がない。これは半導体チップが元から備えていた外部接続パッドを、導電性薄膜形成後も半導体チップの外部に露出させているためである。そのために、半導体チップの接合工法が常温接合技術に限定されることがなくなり、既知の接合工法をそのまま利用可能となる。これに伴い、導電性薄膜に厳密な平坦性を求める必要もなくなるというメリットも生じる。

【0053】

また同様の理由で、半導体装置の集積にチップ・トゥ・ウエハ接続プロセスを用いた場合でも、必要以上の工程、装置の複雑化を避けることができる。

【図面の簡単な説明】

【0054】

【図1】本発明の一実施形態の半導体チップの一例を模式的に示した断面図である。

【図2】本発明の一実施形態の半導体チップによる三次元集積半導体装置の例を示した断面図である。

【図3】本発明の一実施形態の半導体チップの一例を模式的に示した断面図である。

【図4】本発明の一実施形態の半導体チップと、それを用いた三次元集積半導体装置を模式的に示したものである。

【図5】本発明の一実施形態の半導体チップによる三次元集積半導体装置の例を示した断面図である。

【図6】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図7】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図8】本発明の一実施形態の半導体チップの外部接続パッドの配置を示す図である。

【図9】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図10】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図11】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図12】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図13】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図14】本発明の一実施形態の個々のメモリチップの断面構造を示す図である。

【図15】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図16】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図17】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図18】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図19】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図20】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図21】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図22】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図23】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図24】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図25】本発明の一実施形態による三次元集積化半導体装置のシュム・プロットである。

【図26】本発明を適用しない三次元集積半導体装置のシュム・プロットである。

【図27】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図28】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図29】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図30】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図31】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図32】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図33】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図34】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図35】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図36】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図37】本発明の一実施形態の半導体チップおよび半導体装置の加工手順を説明する断面図である。

【図38】本発明の一実施形態による三次元集積化半導体装置のシュム・プロットである。

【図39】本発明を適用しない三次元集積半導体装置のシュム・プロットである。

【図40】3D−SiPの構成の一例を示す断面図である。

【発明を実施するための形態】

【0055】

以下、本発明による半導体チップの製造方法を説明する。なお、下記に記載した実施例は、発明の概念を説明するため便宜的に取り上げたものであり、何ら発明の実施形態を限定するものではない。

【0056】

以下の各図表において、同じ構成要素に対しては、とくに断りがない限り複数の図表で同じ番号を付与している。

【0057】

図1は、本発明に基づいて製作した半導体チップの一例を模式的に示したものである。

【0058】

半導体チップ10は、ベース基板11と、ベース基板表面に形成された回路要素12と、ベース基板の回路要素形成面に、絶縁層と導体層を交互に積層してなる配線部13を備える。また、配線部を構成する導体層のうち、もっともベース基板から遠い層には、外部接続パッド14がある。さらに、配線部のうちベース基板に対向する側の表面には、絶縁材料によるパッシベーション膜15が配される。ただしパッシベーション膜15のうち、外部接続パッドに対応する部分には開口部が形成されている。

【0059】

ベース基板11は、半導体材料からなる層を最低一つは備えた部材でなければならない。ただし、半導体材料の材質や構成は任意である。

構成に関しては、全体が単一の材料でできているベース基板を利用可能である。また、SOI(Silicon on Inslator)構造のように、異なる半導体材料の層が直接、もしくは絶縁体を介して積層された構成でもよい。

材料として代表的な物を例示するならば、単体半導体であれば単結晶シリコン、単結晶ゲルマニウムなどがある。炭化ケイ素や、ガリウム砒素、リン化インジウムをはじめとする化合物半導体も、ベース基板11の材料として利用可能である。

【0060】

半導体チップ10が備える回路要素12の種類は、本発明を適用する上での制約にはならない。トランジスタ、ダイオード等の能動素子を備えるチップであっても、抵抗などの受動素子を備えるチップであっても、また双方を備えるチップであっても、本発明を適用することができる。

【0061】

配線部13を構成する絶縁層は絶縁体で形成されていればよく、また導体層は導体で形成されていればよい。同様に、パッシベーション膜15も一種類以上の絶縁体を含む膜であればよい。

【0062】

パッシベーション膜15の上には導電性薄膜16が形成されている。この導電性薄膜が不要電磁波の伝播を遮断するシールドとして働き、半導体チップ10の電磁妨害耐性を向上させる。導電性薄膜の構成材料としては、各種の単体金属、合金、半導体材料およびこれらを組み合わせて積層したものが採用できる。導電性薄膜を形成するプロセスも、採用した材料に応じて任意に選ぶことができる。

【0063】

導電性薄膜16には、外部接続パッド14の全面を半導体チップ10の外部に露出させるための開口部17が設けられる。

【0064】

ここで、必ずしも全ての外部接続パッド14を露出させる必要はない。なぜなら、これによって半導体チップの電磁妨害耐性をより容易に高められるからである。

【0065】

導電性薄膜16の電磁波遮蔽性能を高める方法として、導電性薄膜16の電位を何らかの方法で安定化することが考えられる。これは導電性薄膜16と、配線層12の中の電位が安定した配線、すなわち電源電位を供給する配線もしくは接地電位を供給する配線とを、電気的に接続することで実現される。導電性薄膜16が電源電位を供給する外部接続パッド141ないし接地電位を供給する外部接続パッド142を覆っているならば、配線部12に何ら配線を追加することなく、導電性薄膜を電位の安定した配線に接続できる。

【0066】

図2には、こうして製作した半導体チップによる三次元集積半導体装置の一例を示した。

【0067】

三次元集積半導体装置100は、半導体チップ10と第二の半導体チップ110で構成される。第二の半導体チップにも、回路要素12が形成されたベース基板11と配線部13、パッシベーション膜14、外部接続パッド15が存在する。半導体チップ10と同110は、互いのベース基板の回路要素形成面を対向するように積層されており、互いの外部接続パッドはマイクロバンプ120で接続される。マイクロバンプは両半導体チップの間の電気的接続も担っており、その材料として単体金属、合金を少なくとも一種類含む。公知の技術をかんがみれば、はんだ、金バンプ、金属膜を備える樹脂バンプなどが好適であろう。

【0068】

三次元集積半導体装置100はインターポーザ300に実装されている。三次元集積半導体装置100とインターポーザ300は、半導体チップ110の外部接続パッドを介して電気的に接続される。その方法として、第一には図2に示すようなワイヤボンディング310によるものが挙げられる。また、ベース基板11を公知の方法で薄くした上で、金属バンプ、もしくははんだボールで接続する方法も適用できる。インターポーザ300は、例えばプリント配線板や多層配線基板、リードフレーム等である。ただし、ビルドアップ多層配線基板やシリコン配線基板のような、微細配線の形成に対応した配線基板を利用するのが望ましい。

【0069】

図3は、本発明に基づいて製作した半導体チップの一例を模式的に示したものである。

【0070】

半導体チップ10は、ベース基板11と、ベース基板表面に形成された回路要素12と、ベース基板の回路要素形成面に、絶縁層と導体層を交互に積層してなる配線部13を備える。また、配線部を構成する導体層のうち、もっともベース基板から遠い層には、外部接続パッド14がある。さらに、配線部のうちベース基板に対向する側の表面には、絶縁材料によるパッシベーション膜15が配される。ただしパッシベーション膜15のうち、外部接続パッド14に対応する部分には開口部が形成されている。

【0071】

ベース基板11は、半導体材料からなる層を最低一つは備えた部材でなければならない。ただし、部材の構成や半導体材料の材質は任意である。

構成としては、全体が単一の材料でできているベース基板は当然利用可能である。また、SOI構造など、異なる半導体材料の層が直接、もしくは絶縁体を介して積層された構成でもよい。

材料として代表的な物を例示するならば、単体半導体であれば単結晶シリコン、単結晶ゲルマニウムなどがある。炭化ケイ素や、ガリウム砒素、リン化インジウムをはじめとする化合物半導体も、ベース基板11の材料として利用可能である。

【0072】

半導体チップ10が備える回路要素12の種類は、本発明を適用する上での制約にはならない。トランジスタ、ダイオード等の能動素子を備えるチップであっても、抵抗などの受動素子を備えるチップであっても、また双方を備えるチップであっても、本発明を適用することができる。

【0073】

配線部13を構成する絶縁層は絶縁体で形成されていればよく、また導体層は導体で形成されていればよい。同様に、パッシベーション膜15も一種類以上の絶縁体を含む膜であればよい。

【0074】

半導体チップ10には、半導体チップの表裏を導通させる貫通電極18が備わっている。貫通電極18は側面に絶縁膜181を持ち、ベース基板11やパッシベーション膜14との間、および配線部13の中の接続すべきでない配線と貫通電極を電気的に分離している。貫通電極の形状や加工プロセスは任意である。貫通電極内部が完全に導電材料で充填された構造でもよいし、貫通電極の側面のみに導電材料が形成されたコンフォーマル構造でもよい。

【0075】

貫通電極の導電性を担う導電材料として、導電性を示すあらゆる材料が採用可能である。単体金属でも、合金でも、半導体でも、導電性フィラーを分散した樹脂でもよい。また、これらの中からいくつかを組み合わせた混合物や積層体を用いることもできる。

【0076】

パッシベーション膜15の上には導電性薄膜16が形成されている。導電性薄膜の構成材料には、各種の単体金属、合金、半導体およびこれらを組み合わせて積層したものが利用できる。また、導電性薄膜16は外部接続パッド14の全面を半導体チップ外部に露出させるための開口部17を持つ。

【0077】

ここで、導電性薄膜16の材料と、貫通電極18を構成する導電材料のうち少なくとも一部が同じものであることを許容できれば、工程の簡略が可能である。

貫通電極に導電材料を埋め込むプロセスでは、貫通電極の内部だけでなく、導電材料を埋め込んだ側のウエハ表面にも余分な導電材料の層が形成されることが多い。一般的なプロセスでは、この余分な導電材料はエッチングやCMPなどで完全に除去した上で次工程に供される。しかし、導電性薄膜16と貫通電極18が同じ材料で形成できるのであれば、余分な導電材料の層で導電性薄膜16をかねることができる。これにより、余分な導電材料の除去工程を簡略、あるいは省略できる。

【0078】

また、導電性薄膜16が電源電位供給用の外部接続パッド141ないし接地電位を供給する外部接続パッド142を覆っているならば、配線部12に配線を追加することなく、導電性薄膜16を電位の安定した配線に接続できる。導電性薄膜16の電位の安定は、電磁波遮蔽性能の向上につながる。

【0079】

導電性薄膜16と同様に、パッシベーション膜15の上に貫通電極パッド19が形成されている。貫通電極18はパッシベーション膜14を貫通しているため、貫通電極18と貫通電極パッド19は直接電気的に接続される。

【0080】

図4は、本発明に基づいて製作した半導体チップと、それを用いた三次元集積半導体装置を模式的に示したものである。

【0081】

半導体チップ10は、ベース基板11と、ベース基板表面に形成された回路要素12と、ベース基板の回路要素形成面に、絶縁層と導体層を交互に積層してなる配線部13とを備える。また、配線部を構成する導体層のうち、最もベース基板から遠い層には外部接続パッド14および貫通電極パッド19がある。さらに、配線部のうちベース基板に対向する側の表面には、絶縁材料によるパッシベーション膜15が配される。ただしパッシベーション膜15のうち、外部接続パッドと貫通電極パッドに対応する部分には開口部17が形成されている。

以上に加えて、ベース基板11を貫通する貫通電極18が存在する。貫通電極18とベース基板11は絶縁膜181で分離される。また、貫通電極18の一部については、その一端と貫通電極パッド19が配線部12の中の配線によって電気的に接続されている。

【0082】

ベース基板11は、半導体材料からなる層を最低一つは備えた部材でなければならない。ただし、部材の構成や半導体材料の種類は任意である。

構成としては、全体が単一の材料でできているベース基板は当然利用可能である。また、SOI基板など、異なる半導体材料の層が直接、もしくは絶縁体を介して積層された構成でもよい。

材料として代表的な物を例示するならば、単体半導体であれば単結晶シリコン、単結晶ゲルマニウムなどがある。炭化ケイ素や、ガリウム砒素、リン化インジウムをはじめとする化合物半導体も、ベース基板11の材料として利用可能である。

【0083】

半導体チップ10が備える回路要素12の種類は、本発明を適用する上での制約にはならない。トランジスタ、ダイオード等の能動素子を備えるチップであっても、抵抗などの受動素子を備えるチップであっても、また双方を備えるチップであっても、本発明を適用することができる。

【0084】

配線部13を構成する絶縁層は絶縁体で形成されていればよく、また導体層は導体で形成されていればよい。同様に、パッシベーション膜15も一種類以上の絶縁体を含む膜であればよい。

【0085】

貫通電極18は、ベース基板の回路要素形成面とその裏面を、もしくは回路要素そのものとベース基板の裏面を導通している。貫通電極の構造や加工プロセスは任意である。貫通電極内部が完全に導電材料で充填された構造でもよいし、貫通電極の側面と底面のみに導電材料の皮膜が形成されたコンフォーマル構造でもよい。

【0086】

貫通電極の導電性を担う導電材料として、導電性を示すあらゆる材料が採用可能である。単体金属でも、合金でも、半導体でも、導電性フィラーを分散した樹脂でもよい。また、これらの中からいくつかを組み合わせた混合物や積層体を用いることもできる。

【0087】

パッシベーション膜15の上には導電性薄膜16が形成されている。導電性薄膜の構成材料には、各種の単体金属、合金、半導体およびこれらを組み合わせて積層したものが利用できる。導電性薄膜16は、外部接続パッド14および貫通電極パッド19を露出させる開口部17を持つ。

【0088】

ここで、導電性薄膜16が電源電位を供給する外部接続パッド141ないし接地電位を供給する外部接続パッド142を覆っているならば、配線部12に配線を追加せずに、導電性薄膜16を電位の安定した配線に接続できる。導電性薄膜16の電位が安定することは、電磁波遮蔽性能の向上につながる。

【0089】

図5には、こうして製作した半導体チップによる三次元集積半導体装置の一例を示した。

【0090】

三次元集積半導体装置100は、半導体チップ10と第二の半導体チップ110、第三の半導体チップ210で構成される。第二、第三の半導体チップにも、回路要素12が形成されたベース基板11と、配線部13、パッシベーション膜14、外部接続パッド15が存在する。また、第三の半導体チップ210は貫通電極18と貫通電極パッド19を持つ。半導体チップ10と同110は、互いのベース基板の回路要素形成面を対向するように積層されており、互いの外部接続パッドはマイクロバンプ120で接続される。一方、半導体チップ10と210は、互いのベース基板の回路要素形成面が、ベース基板を介して対向するよう積層されている。半導体チップ10と同210は、互いの貫通電極の端面を結合するマイクロバンプ220で接続されている。マイクロバンプは単体金属、合金のうち少なくとも一種類で構成される。公知の技術をかんがみれば、はんだ、金バンプ、金属膜を備える樹脂バンプなどが好適であろう。

【0091】

三次元集積半導体装置100はインターポーザ300に実装される。三次元集積半導体装置100とインターポーザ300は、半導体チップ210の外部接続パッド14と貫通電極パッド19を介して電気的に接続される。接続にあたっては、図2に示すような金属バンプ320による方法のほか、ボンディングワイヤ、ACFなどが適用できる。インターポーザ300は、例えばプリント配線板や多層配線基板、リードフレーム等である。ただし、ビルドアップ多層配線基板やシリコン配線基板のような、微細配線の形成に対応した配線基板を利用するのが望ましい。

【実施例1】

【0092】

この実施例では、貫通電極を持たない半導体チップをもとに、電磁妨害耐性の高い半導体チップを製作した際の手順を説明する。さらに、その半導体チップを用いて三次元集積半導体装置を製作する手順も説明する。図6から図13は、半導体チップおよび半導体装置の加工手順を説明する図である。

【0093】

第一の準備工程として、個片化されている第一のテストチップ20を用意した。図6に示すとおり、第一のテストチップ20は、単結晶シリコン製のベース基板11、CMOSトランジスタによるドライバ22、配線部23、アルミニウム製の外部接続パッド24、同じくアルミニウム製の電源供給のための外部接続パッド241、ポリイミド製のパッシベーション膜15を備える。パッシベーション膜には全ての外部接続パッドを半導体チップ外部に露出させるために直径70μmの円形の開口が設けられていた。

【0094】

第二の準備工程として、個片化済みの第二のテストチップ30を用意した。第二のテストチップ30の大まかな構成は図7に示すとおりであり、単結晶シリコン製のベース基板11、配線部33、アルミニウム製の外部接続パッド34、同じくアルミニウム製の電源供給のための外部接続パッド341、ポリイミド製のパッシベーション膜15を備える。パッド34および同341のうち領域301に含まれるものは、第一のテストチップのパッド24や241と対応する配列に配置される。(図8の平面図を参照)

【0095】

第一工程として、第一のテストチップ20のうちパッシベーション膜25が形成された側の表面へ、開口部27が設けられた銅薄膜26を形成した。開口部27は外部接続パッド24を露出するように設けられる一方、電源供給用パッド241は銅薄膜26に覆われるようにした。銅薄膜の厚さは0.7μmであった。

第一工程は、以下に示す第一補工程の一と二の組み合わせで行った。

【0096】

第一補工程の一として、第一のテストチップ20のパッシベーション膜25形成面全体にスパッタリングによる銅薄膜26を形成した。(図示せず)

第一補副工程の二として、フォトレジスト1000を用いたパターニングと選択的ウエットエッチングにより、図9(a)のように銅薄膜26に開口部17を形成した。開口部17は直径75μmの円形とし、その中心はパッシベーション膜15の開口部と一致させた。ウエットエッチングに際しては、銅薄膜を除去し、アルミニウムを侵さない公知のエッチング液を用いた。

その後、フォトレジスト1000は除去してから次の工程へ進んだ。

【0097】

また、以下の第一補工程の三から五を行うことでも、第一工程を完遂できた。

【0098】

第一補工程の三としては、第一のテストチップ20のパッシベーション膜25形成面に対してフォトレジストのパターンを形成した。(図示せず)

続く第一補工程の四として、スパッタリングによる銅薄膜の形成を行った。

その上で、第一補工程の五として、フォトレジストパターンをその表面の銅薄膜ごとリフトオフした。以上の補工程から、図9(b)のように、所望の位置に開口部17を備える銅薄膜26を得た。

【0099】

第二工程として、第一のテストチップ20のパッド24の表面、および無電解銅薄膜26の表面に金でできたスタッドバンプ130を形成した。スタッドバンプ形成後の模式図を図10に示す。スタッドバンプ130の形成は、ワイヤボンダと金ワイヤを用いる公知の方法によって行った。スタッドバンプの高さは30μmとした。

【0100】

第三工程として、三次元集積半導体装置100の組み立てを行った。

まず、インターポーザ300の表面に第二のテストチップ30を、パッド34が露出するように接着剤140で固定した。

続いて第二のテストチップ30に対して第一のテストチップ20をフリップチップ接続した。二つのチップ間の電気的接続は、スタッドバンプ130を利用して実現した。

最後に、チップ間の空隙に熱硬化性のアンダーフィル材330を充填し、大気中で加熱硬化した。(図11)

【0101】

第四工程として、三次元集積半導体装置100とインターポーザ300を電気的に接続した。(図12)この電気的接続は、外部接続パッド34とインターポーザ300をボンディングワイヤ310で接続することで実現した。

【0102】

完成した三次元集積半導体装置について、その電気的特性の評価を行った。

【0103】

図13は、三次元集積半導体装置100を、電気的な構造に注目して抽象化した模式図である。テストチップ20内のドライバ22については、入力信号配線231、出力信号配線232とも、外部接続パッド24、バンプ130を経由してテストチップ30の配線部33へ引き出されている。これらの配線はさらに外部接続パッド34を経て、装置外の評価システムに接続される。またテストチップ30の配線部33には、上記の系とは別に、配線231、232と平行に配されたモニター用の配線331がある。この配線もまた、装置外の測定システムに接続されている。

【0104】

ドライバ22を動作させた場合に、モニター用の配線331に生じるクロストーク・ノイズの測定結果を表1に示す。表1における対象例とは、三次元集積半導体装置100と同様の装置を、銅薄膜16を設けないテストチップで組み立てたものの測定結果である。

【表1】

【実施例2】

【0105】

この実施例では、貫通電極を備えるとともに、高い電磁妨害耐性を示す半導体チップを製作した際の工程を説明する。また、製作した半導体チップを含む三次元集積半導体装置を製作した際の工程もあわせて説明する。図15から図24は、半導体チップおよび半導体装置の加工手順を説明する図である。

【0106】

第一の準備工程として、メモリチップ40が一面に形成されたメモリウエハ400を用意した。ウエハの直径は200mm、ウエハの厚さは405μmであった。

個々のメモリチップの断面構造を図14に示す。個片で見た場合のメモリチップ40は、SOI基板からなるベース基板11(詳細な構造は図示せず)、CMOSトランジスタと受動素子からなるメモリ回路42、配線部13、金で被覆されたアルミニウム製の外部接続パッド14、同じく金被覆アルミニウム製の接地電位供給のための外部接続パッド142、窒化シリコン製のパッシベーション膜15を備える。パッシベーション膜には全ての外部接続パッドを半導体チップ外部に露出させるため、直径50μmの円形の開口が設けられていた。

【0107】

配線部13の中には、貫通電極と配線部の導通を得るため外部接続パッド14と同じ層に配置されたランド構造143、ランド構造143とメモリ回路を接続する内部配線、メモリ回路と外部接続パッドを結ぶ外部接続配線が配置されていた。(いずれも図示せず)

【0108】

第二の準備工程として、マイコンチップ50を用意した。マイコンチップ50の大まかな構成は図15に示すとおりであり、単結晶シリコン製のベース基板11、マイコン回路52、配線部13、金で被覆されたアルミニウム製の外部接続パッド14、同じく金被覆アルミニウム製の接地電位供給のための外部接続パッド142、ポリイミド製のパッシベーション膜15を備える。パッシベーション膜には全ての外部接続パッドを半導体チップ外部に露出させるため、直径50μmの円形の開口が設けられていた。

【0109】

第一工程として、メモリウエハ400の所定の位置に、貫通電極のもととなる貫通孔182を形成した。(図16)ここでいう所定の位置とは、前記ランド構造が配置された部分を含む。貫通孔182の加工には、公知の方法であるボッシュプロセスを用いた。孔の断面は直径35μmの円とした。また孔のピッチは最も狭い部分で150μmであった。

【0110】

第二工程として、ベース基板11や配線部13中の配線と、貫通電極を絶縁するための絶縁膜181を形成した。図17に示すように、テトラエトキシシランを材料とするプラズマCVD(化学気相成長法)で、二酸化ケイ素の薄膜181をメモリウエハ400の表面全体に形成した。薄膜481の厚さは貫通孔182の側面で平均0.17μmであった。

【0111】

第三工程として、絶縁膜181のうち、外部接続パッド14と142、およびランド構造143を被覆する部分を除去した。感光性エッチングレジストとドライエッチングを用いた公知の選択的エッチングプロセスで、絶縁膜181の不要部分を除去できた。エッチングレジスト除去後のメモリウエハの模式図を図18に示す。

【0112】

第四工程として、導電性薄膜46と貫通電極パッド49の形成と、貫通孔482側面への導体材料部形成を行った。これは、以下の第四補工程の一から五に示すプロセスで行った。

【0113】

第四補工程の一として、バリアメタルとなる窒化チタン薄膜183を、スパッタリングでメモリウエハ400表裏の露出面全体に形成した。工程終了時の模式図を図19に示す。貫通孔182側面のバリアメタル厚は平均0.08μmであった。

【0114】

第四補工程の二として、めっきシード層となる銅薄膜を、スパッタリングでメモリウエハ400の表裏全面に形成した。(図示せず)貫通孔182側面の銅薄膜の厚さは平均で0.54μmであった。

【0115】

第四補工程の三として、所望の形状の導電性薄膜46、貫通電極パッド49および491を作るためのめっきレジストパターン(図示せず)を形成した。

【0116】

第四補工程の四として、外部接続パッド14に対して開口部17を備える導電性薄膜46、貫通電極パッド49と491、ならびに貫通孔182側面の導体材料部を形成した。この補工程は窒化チタン薄膜をシード層とする電解銅めっきで行った。電解銅の厚さはメモリウエハ表面で平均5μm、貫通電極側面で平均3.4μmであった。めっき完了後、めっきレジストパターンは除去した。

【0117】

第四補工程の五として、銅薄膜、ならびに窒化チタン薄膜183の不要部分をウエットエッチングで除去した。(図20)

【0118】

第五工程として、上記の第四工程までを実施した第二のメモリウエハ401を用意し、このウエハの外部接続パッド14、142と貫通電極パッド49、491の表面に金スタッドバンプ130、1301を形成した。(図21)スタッドバンプ130の形成は、ワイヤボンダと金ワイヤを用いる公知の方法によって行った。スタッドバンプ130の高さは40μm、スタッドバンプ1301の高さは20μmとした。

【0119】

第六工程として、メモリウエハ400と第二のメモリウエハ401を接合した。

予めメモリウエハ400の裏面に未硬化の熱硬化性アンダーフィル材料330を塗布した上で、スタッドバンプ130を用いた公知の圧着プロセスによって両メモリウエハの貫通電極パッド491を接合した。その後、アンダーフィル材料330を硬化させた。(図22)

【0120】

第七工程として、接合した二枚のメモリウエハを分割し、個々の積層メモリチップ101を得た。(図示せず)ウエハの分割には公知のウエハダイシング技術を用いた。

【0121】

第八工程として、積層メモリチップ101をインターポーザ300に実装した。図23の通り、金スタッドバンプ1301による圧着をもって、積層メモリチップ101とインターポーザ300を電気的に接続した。その後、熱硬化性アンダーフィル材330を注入、熱硬化させた。

【0122】

第九工程として、マイコンチップ50と積層メモリチップ101を接合して、三次元集積半導体装置100を完成させた。(図24)マイコンチップ50の外部接続パッド14に対して高さ20μmの金スタッドバンプ130を形成し、これをもって両チップの外部接続パッドを物理的、電気的に接続した。

【0123】

完成した三次元集積半導体装置100について、その特性を評価した。図25に本実施例で製作した三次元集積化半導体装置100のシュム・プロットを示した。一方、対象例として本発明を適用しないマイコンチップとメモリチップで試作した三次元集積半導体装置のシュム・プロットを、図26に示した。図25で背景に色の付いた部分が、本発明の効果によってメモリ特性が改善した部分である。

【実施例3】

【0124】

この実施例では、貫通電極を備えた半導体チップを使って、高い電磁妨害耐性を示す半導体チップを製作した際の工程を説明する。また、製作した半導体チップを含む三次元集積半導体装置を組み立てた際の工程もあわせて説明する。図27から図37は、半導体チップおよび半導体装置の加工手順を説明する図である。

【0125】

第一の準備工程として、メモリチップ60が一面に形成されたメモリウエハ600を用意した。ウエハの直径は150mm、ウエハの厚さは625μmであった。

個々のメモリチップの断面構造を図27に示す。個片で見た場合のメモリチップ60は、SOI基板からなるベース基板61(詳細な構造は図示せず)、CMOSトランジスタと受動素子からなるメモリ回路42、配線部13、金で被覆されたアルミニウム製の外部接続パッド14、同じく金被覆アルミニウム製の接地電位供給のための外部接続パッド142、窒化シリコン製のパッシベーション膜15を備える。パッシベーション膜には全ての外部接続パッドを半導体チップ外部に露出させるため、直径50μmの円形の開口が設けられていた。

【0126】

ベース基板61には、導電性シリコンが充填されたビアホール682が形成されている。ビアホール682は直径10μm、深さ110μmの円柱状で、その側壁には二酸化ケイ素による絶縁膜681が設けられている。ビアホール間のピッチは最も狭いところで25μmであった。またビアホール681は、配線部13を経由して貫通電極パッド19と電気的に接続されていた。

【0127】

第二の準備工程として、マイコンチップ50を準備した。これは実施例2で用いたマイコンチップと全く同一のものである。(図15参照)マイコンチップ50に対しては、外部接続パッド14、142上に金でできた高さ30μmのスタッドバンプ130を公知の方法で形成しておいた。

【0128】

第三の準備工程として、ガリウム砒素薄膜66、ならびにガリウムインジウム砒素薄膜661が積層された、ガリウム砒素製のブランクウエハ1010を準備した。(図28)支持ウエハは直径150mmの円形で、その表面には厚さ1.2μmの円形のアルミニウム砒素薄膜661が形成されていた。さらにその上に、直径145mm、厚さ10μmの円形のガリウム砒素薄膜66が形成されていた。ガリウム砒素薄膜は炭素でドープされており、その抵抗率は1.47Ω・cmであった。

【0129】

第一工程として、ガリウム砒素薄膜66に対して開口部17を形成した。開口部の形成は、ガリウム砒素薄膜66のうち所定の部分を、公知のエッチャントを用いたウエットエッチングで除去することで行った。開口部17形成後のブランクウエハ1010を図29に示す。開口部17の径は58.5μmであった。

【0130】

ガリウム砒素薄膜66は後の工程でメモリウエハ600に転写される。そこで、開口部67の配置は、ガリウム砒素薄膜66を転写した際に外部接続パッド64、貫通電極パッド69を全て露出させるように定めた。

【0131】

第二工程として、メモリウエハ600とブランクウエハ1010を貼り合わせた。

まず、ポリイミドを主成分とする感光性接着剤1401をメモリウエハ600の配線層側表面に貼り付けたあと、全ての外部接続パッド14、142および貫通電極パッド69を露出させるパターンを形成した。

次いで、感光性接着剤1401を用いて、メモリウエハ600とブランクウエハ1020を接着した。このとき、ブランクウエハ1010はガリウム砒素薄膜66が形成された面を接着面とした。

第二工程の最後に、感光性接着剤1401を熱硬化させ、二枚のウエハを完全に固着させた。第二工程完了時のウエハの模式図を図30に示す。

【0132】

第三工程として、ベース基板61に埋設されたビアホール682を裏面に露出させて貫通電極68とした。メモリウエハ600をベース基板側から、BG(Back Grinding)とCMPを用いて厚みが100μmになるまで研削した。その後、図31に示す通り、メモリウエハ600の研削面全面に対し、低温CVDによる二酸化ケイ素のパッシベーション膜651を形成した。ただし貫通電極68の端部のみはパッシベーション膜651で被覆することなく、露出させた。

【0133】

第四工程として、貫通電極68のベース基板61側端部に、半導体チップ積層用のメタルポスト150を設けた。メタルポスト150は銅で形成し、ベース基板表面からの高さは5μmとした。また、メタルポスト150の頂面には、厚さ2μmのスズ薄膜1501を形成した。(図32)

メタルポスト150とスズ薄膜1501の形成は、スパッタ銅をめっきシード層とする公知の電解めっきアディティブプロセスで実施した。

【0134】

第五工程として、ブランクウエハ1010をメモリウエハ600から剥離した。まず、メモリウエハ600のベース基板側にガラス製のサポートウエハ1020を耐酸性接着フィルム1030で貼り付けた。このとき、メタルポスト150全体を接着フィルムに埋設した。次いでメモリウエハ600を塩酸に浸漬し、ガリウムインジウム砒素薄膜681を除去した。第五工程完了時のウエハ600の模式図を図33に示す。

【0135】

第六工程として、上記第四工程までを適用した第二のメモリウエハ601を用意し、メモリウエハ600と電気的、物理的に接合した。(図34)ウエハ間で対応する外部接続パッド64とメタルポスト150、および貫通電極パッド69とメタルポスト150をアライメントした上で、リフローによって一括で接合した。その後、ウエハ間にアンダーフィル材料(図示せず)を充填・硬化した。

【0136】

第七工程として、第五工程と同様に、第二のメモリウエハに接合したブランクウエハ1010を除去した。

【0137】

第八工程として、ガラス製の第二のサポートウエハ1021を、外部接続パッド14の露出する面へ新たに貼り付けるとともに、サポートウエハ1020の剥離を行った。(図35)

【0138】

第九工程として、メモリウエハ600、601およびサポートウエハ1021を一括でダイシングし、個々の積層メモリ102へと分離した。(図示せず)

【0139】

第十工程として、積層メモリ102をビルドアップ多層基板によるインターポーザ330に実装した。実装にはメタルポスト150を用いた。この後、個片化したサポートウエハ1021を剥離した。(図36)

【0140】

第十一工程として、マイコンチップ50と積層メモリチップ101を接合して、三次元集積半導体装置100を完成させた。(図37)

【0141】

完成した三次元集積半導体装置100について、その特性を評価した。図38に本実施例で製作した三次元集積化半導体装置100のシュム・プロットを示した。一方、対象例として本発明を適用しないマイコンチップとメモリチップで試作した三次元集積半導体装置のシュム・プロットを、図39に示した。図38で背景に色の付いた部分が、本発明の効果によってメモリ特性が改善した部分である。

【符号の説明】

【0142】

1…3D−SiP

10、110、210…半導体チップ

11、61…ベース基板

12…回路要素

13、23、33…配線部

14、24、34…外部接続パッド

15…パッシベーション膜

16…導電性薄膜

17…導電性薄膜の開口部

18、68…貫通電極

19、49…貫通電極パッド

20、30…テストチップ

22…CMOSによるドライバ

26…銅薄膜

40、60…メモリチップ

42、62…メモリ回路

50…マイコンチップ

52…マイコン回路

66…ガリウム砒素薄膜

100…三次元集積半導体装置

101…積層メモリチップ

120…マイクロバンプ

130、1301…スタッドバンプ

140、1401…接着剤

141、241、341…電源供給のための外部接続パッド

142…接地電位供給のための外部接続パッド

143…ランド構造

150…メタルポスト

181…貫通電極側面の絶縁皮膜

182…貫通孔

183…バリアメタル

231…入力信号配線

232…出力信号配線

300…インターポーザ

310…ボンディングワイヤ

320…はんだバンプ

330…アンダーフィル材料

331…モニター配線

400、401、600、601…メモリチップウエハ

491…半導体チップ裏面の貫通電極パッド

651…裏面側のパッシベーション膜

681…ビアホール側面の絶縁皮膜

682…ビアホール

1000…フォトレジスト

1010…ブランクウエハ

1020、1021…サポートウエハ

1030…接着フィルム

1501…スズ薄膜

【特許請求の範囲】

【請求項1】

半導体チップのうち、

半導体材料の層を少なくとも一つ含むベース基板と、

前記ベース基板の表面において、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記ベース基板から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、

前記外部接続パッドが形成された導体層を被覆し、かつ前記外部接続パッドをチップ外部に露出させるような開口部を備えた絶縁体からなるパッシベーション層と、

を備えるものであって、

さらに、前記ベース基板に対して前記配線部および前記パッシベーション層を離隔した位置に、少なくとも一種類の金属ないし合金からなる導電性薄膜を具備し、

かつ、前記導電性薄膜のうち前記外部接続パッドに対応する部分には第二の開口部が設けられていることを特徴とする半導体チップ。

【請求項2】

請求項1に記載の半導体チップにおいて、さらに前記ベース基板を厚さ方向に貫通する貫通電極を備えることを特徴とする半導体チップ。

【請求項3】

前記配線部の中に、下記の1)、2)のうち少なくともいずれか一方を含むことを特徴とする、請求項2に記載の半導体チップ。

1)前記配線部に配置された、前記貫通電極と前記回路要素を電気的に接続するための内部配線。

2)前記配線部を形成する導体層のうち最も前記ベース基板から離れた層に形成され、前記外部配線に接続されていない貫通電極パッド、および前記貫通電極パッドと前記貫通電極を電気的に接続するために前記配線部に配置された貫通配線。

【請求項4】

前記貫通電極が前記ベース基板に加えて前記配線部を厚さ方向に貫通していることを特徴とする、請求項2および3に記載の半導体チップ。

【請求項5】

前記貫通電極の内部が導電材料で埋め込まれていることを特徴とする、請求項2から4に記載の半導体チップ。

【請求項6】

前記導電材料と前記導電性薄膜を形成する材料とが、共通の材料を含むことを特徴とする、請求項5に記載の半導体チップ。

【請求項7】

半導体チップのうち、

半導体材料の層を少なくとも一つ含むベース基板と、

前記ベース基板の表面において、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記ベースから最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、

前記外部接続パッドが形成された導体層を被覆し、かつ前記外部接続をチップ外部に露出させるような開口部を備えた絶縁体からなるパッシベーション層と、

を備えるものであって、

さらに、

前記ベース基板に対して前記配線部を離隔した位置に、少なくとも一種類の半導体材料を含む導体からなる導電性薄膜を具備し、

かつ前記導電性薄膜のうち前記外部接続パッドに対応する部分には第二の開口部が設けられていることを特徴とする半導体チップ。

【請求項8】

前記導電性薄膜に含まれる半導体材料が、1.5Ω・cm以下の比抵抗を示すことを特徴とする、請求項7に記載の半導体チップ。

【請求項9】

請求項7または8に記載の半導体チップにおいて、さらに前記ベース基板を厚さ方向に貫通する貫通電極を備えることを特徴とする半導体チップ。

【請求項10】

前記配線部の中に、下記の1)、2)のうち少なくともいずれか一方を含むことを特徴とする、請求項9に記載の半導体チップ。

1)前記配線部に配置された、前記貫通電極と前記回路要素を電気的に接続するための内部配線。

2)前記配線部を形成する導体層のうち最も前記ベース基板から離れた層に形成され、前記外部配線に接続されていない貫通電極パッド、および前記貫通電極パッドと前記貫通電極を電気的に接続するために前記配線部に配置された貫通配線。

【請求項11】

前記貫通電極が前記配線部を厚さ方向に貫通していることを特徴とする、請求項9および10に記載の半導体チップ。

【請求項12】

前記貫通電極の内部が導電材料で充填されていることを特徴とする、請求項9から11に記載の半導体チップ。

【請求項13】

前記導電材料が前記導電性薄膜を形成する材料と同じであることを特徴とする、請求項12に記載の半導体チップ。

【請求項14】

前記導電性薄膜が不要電磁波の遮蔽のために設けられていることを特徴とする、請求項1から13に記載の半導体チップ。

【請求項15】

前記導電性薄膜が、前記配線部のうち電源電位を供給する部分に接続されていることを特徴とする、請求項1から14に記載の半導体チップ。

【請求項16】

前記導電性薄膜と前記電源電位を供給する配線部との電気的接続を、電源電位を供給するための前記外部接続パッドを前記導電性薄膜で被覆して得ていることを特徴とする、請求項15に記載の半導体チップ。

【請求項17】

前記導電性薄膜が、前記配線部のうち接地電位を供給する部分に接続されていることを特徴とする請求項1から14に記載の半導体チップ。

【請求項18】

前記導電性薄膜と前記接地電位を供給する配線部との電気的接続を、接地電位を供給するための前記外部接続パッドを前記導電性薄膜で被覆して得ていることを特徴とする、請求項17に記載の半導体チップ。

【請求項19】

請求項1から18に記載の半導体チップを少なくとも一つ含んだ、複数の半導体チップを立体的に集積したことを特徴とする三次元集積半導体装置。

【請求項20】

請求項19に記載の三次元集積半導体装置において、請求項1から18に記載の半導体チップと電気的に接続される第二の半導体チップが、

半導体材料からなり、少なくとも一つの表面を備える第二ベースと、

前記第二ベース基板の表面に形成された第二配線部と、

を備えており、

かつ、請求項1から18に記載の半導体チップと前記第二の半導体チップが、前記ベース基板の前記回路要素が形成された表面と、前記第二ベース基板の前記第二配線部が形成された表面が互いに近接するように集積されていることを特徴とする、請求項19に記載の三次元集積半導体装置。

【請求項21】

下記(a)から(c)の工程を含むことを特徴とする、半導体チップの製造方法。

(a)半導体チップのうち、

能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、を具備する半導体チップを準備する工程。

(b)前記配線部の表面に導電性薄膜を形成する工程。

(c)導電性薄膜のうち、前記外部接続パッドを被覆している部分に第二の開口部を設ける工程。

【請求項22】

下記(a)から(f)の工程を含むことを特徴とする、半導体チップの製造方法。

(a)半導体チップのうち、

能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、を具備する半導体チップを準備する工程。

(b)前記半導体チップに、貫通電極となる孔を加工する工程。

(c)前記孔の側面に絶縁皮膜を形成する工程。

(d)前記孔の内部に導電材料の膜を形成し、半導体チップの両面を導通する工程。

(e)前記配線部の表面に導電性薄膜を形成する工程。

(f)前記導電性薄膜のうち、前記外部接続パッドを被覆している部分に第二の開口部を設ける工程。

【請求項23】

下記(a)から(d)の工程を含むことを特徴とする、半導体チップの製造方法。

(a)半導体チップのうち、

能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、

導電材料で側面を覆われたトレンチと、を具備する半導体チップを準備する工程。

(b)前記配線部の表面に前記導電性薄膜を形成する工程。

(c)前記半導体チップの裏面を研削し、前記トレンチの内部に形成された前記導電材料を一部露出させる工程。

(d)前記導電性薄膜のうち前記外部接続パッドを被覆している部分に、第二の開口部を設ける工程。

【請求項1】

半導体チップのうち、

半導体材料の層を少なくとも一つ含むベース基板と、

前記ベース基板の表面において、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記ベース基板から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、

前記外部接続パッドが形成された導体層を被覆し、かつ前記外部接続パッドをチップ外部に露出させるような開口部を備えた絶縁体からなるパッシベーション層と、

を備えるものであって、

さらに、前記ベース基板に対して前記配線部および前記パッシベーション層を離隔した位置に、少なくとも一種類の金属ないし合金からなる導電性薄膜を具備し、

かつ、前記導電性薄膜のうち前記外部接続パッドに対応する部分には第二の開口部が設けられていることを特徴とする半導体チップ。

【請求項2】

請求項1に記載の半導体チップにおいて、さらに前記ベース基板を厚さ方向に貫通する貫通電極を備えることを特徴とする半導体チップ。

【請求項3】

前記配線部の中に、下記の1)、2)のうち少なくともいずれか一方を含むことを特徴とする、請求項2に記載の半導体チップ。

1)前記配線部に配置された、前記貫通電極と前記回路要素を電気的に接続するための内部配線。

2)前記配線部を形成する導体層のうち最も前記ベース基板から離れた層に形成され、前記外部配線に接続されていない貫通電極パッド、および前記貫通電極パッドと前記貫通電極を電気的に接続するために前記配線部に配置された貫通配線。

【請求項4】

前記貫通電極が前記ベース基板に加えて前記配線部を厚さ方向に貫通していることを特徴とする、請求項2および3に記載の半導体チップ。

【請求項5】

前記貫通電極の内部が導電材料で埋め込まれていることを特徴とする、請求項2から4に記載の半導体チップ。

【請求項6】

前記導電材料と前記導電性薄膜を形成する材料とが、共通の材料を含むことを特徴とする、請求項5に記載の半導体チップ。

【請求項7】

半導体チップのうち、

半導体材料の層を少なくとも一つ含むベース基板と、

前記ベース基板の表面において、能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記ベースから最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、

前記外部接続パッドが形成された導体層を被覆し、かつ前記外部接続をチップ外部に露出させるような開口部を備えた絶縁体からなるパッシベーション層と、

を備えるものであって、

さらに、

前記ベース基板に対して前記配線部を離隔した位置に、少なくとも一種類の半導体材料を含む導体からなる導電性薄膜を具備し、

かつ前記導電性薄膜のうち前記外部接続パッドに対応する部分には第二の開口部が設けられていることを特徴とする半導体チップ。

【請求項8】

前記導電性薄膜に含まれる半導体材料が、1.5Ω・cm以下の比抵抗を示すことを特徴とする、請求項7に記載の半導体チップ。

【請求項9】

請求項7または8に記載の半導体チップにおいて、さらに前記ベース基板を厚さ方向に貫通する貫通電極を備えることを特徴とする半導体チップ。

【請求項10】

前記配線部の中に、下記の1)、2)のうち少なくともいずれか一方を含むことを特徴とする、請求項9に記載の半導体チップ。

1)前記配線部に配置された、前記貫通電極と前記回路要素を電気的に接続するための内部配線。

2)前記配線部を形成する導体層のうち最も前記ベース基板から離れた層に形成され、前記外部配線に接続されていない貫通電極パッド、および前記貫通電極パッドと前記貫通電極を電気的に接続するために前記配線部に配置された貫通配線。

【請求項11】

前記貫通電極が前記配線部を厚さ方向に貫通していることを特徴とする、請求項9および10に記載の半導体チップ。

【請求項12】

前記貫通電極の内部が導電材料で充填されていることを特徴とする、請求項9から11に記載の半導体チップ。

【請求項13】

前記導電材料が前記導電性薄膜を形成する材料と同じであることを特徴とする、請求項12に記載の半導体チップ。

【請求項14】

前記導電性薄膜が不要電磁波の遮蔽のために設けられていることを特徴とする、請求項1から13に記載の半導体チップ。

【請求項15】

前記導電性薄膜が、前記配線部のうち電源電位を供給する部分に接続されていることを特徴とする、請求項1から14に記載の半導体チップ。

【請求項16】

前記導電性薄膜と前記電源電位を供給する配線部との電気的接続を、電源電位を供給するための前記外部接続パッドを前記導電性薄膜で被覆して得ていることを特徴とする、請求項15に記載の半導体チップ。

【請求項17】

前記導電性薄膜が、前記配線部のうち接地電位を供給する部分に接続されていることを特徴とする請求項1から14に記載の半導体チップ。

【請求項18】

前記導電性薄膜と前記接地電位を供給する配線部との電気的接続を、接地電位を供給するための前記外部接続パッドを前記導電性薄膜で被覆して得ていることを特徴とする、請求項17に記載の半導体チップ。

【請求項19】

請求項1から18に記載の半導体チップを少なくとも一つ含んだ、複数の半導体チップを立体的に集積したことを特徴とする三次元集積半導体装置。

【請求項20】

請求項19に記載の三次元集積半導体装置において、請求項1から18に記載の半導体チップと電気的に接続される第二の半導体チップが、

半導体材料からなり、少なくとも一つの表面を備える第二ベースと、

前記第二ベース基板の表面に形成された第二配線部と、

を備えており、

かつ、請求項1から18に記載の半導体チップと前記第二の半導体チップが、前記ベース基板の前記回路要素が形成された表面と、前記第二ベース基板の前記第二配線部が形成された表面が互いに近接するように集積されていることを特徴とする、請求項19に記載の三次元集積半導体装置。

【請求項21】

下記(a)から(c)の工程を含むことを特徴とする、半導体チップの製造方法。

(a)半導体チップのうち、

能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、を具備する半導体チップを準備する工程。

(b)前記配線部の表面に導電性薄膜を形成する工程。

(c)導電性薄膜のうち、前記外部接続パッドを被覆している部分に第二の開口部を設ける工程。

【請求項22】

下記(a)から(f)の工程を含むことを特徴とする、半導体チップの製造方法。

(a)半導体チップのうち、

能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、を具備する半導体チップを準備する工程。

(b)前記半導体チップに、貫通電極となる孔を加工する工程。

(c)前記孔の側面に絶縁皮膜を形成する工程。

(d)前記孔の内部に導電材料の膜を形成し、半導体チップの両面を導通する工程。

(e)前記配線部の表面に導電性薄膜を形成する工程。

(f)前記導電性薄膜のうち、前記外部接続パッドを被覆している部分に第二の開口部を設ける工程。

【請求項23】

下記(a)から(d)の工程を含むことを特徴とする、半導体チップの製造方法。

(a)半導体チップのうち、

能動素子と受動素子のいずれか一つ以上で構成される回路要素と、

前記回路要素が存在する表面上に交互に配された絶縁層と導体層で形成され、回路要素と半導体チップの外部を電気的に接続するための外部配線を含む配線部と、

前記配線部をなす導体層のうち、前記回路要素から最も離れた層に形成され、前記外部配線に接続された外部接続パッドと、

導電材料で側面を覆われたトレンチと、を具備する半導体チップを準備する工程。

(b)前記配線部の表面に前記導電性薄膜を形成する工程。

(c)前記半導体チップの裏面を研削し、前記トレンチの内部に形成された前記導電材料を一部露出させる工程。

(d)前記導電性薄膜のうち前記外部接続パッドを被覆している部分に、第二の開口部を設ける工程。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【公開番号】特開2012−216572(P2012−216572A)

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願番号】特願2011−79096(P2011−79096)

【出願日】平成23年3月31日(2011.3.31)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願日】平成23年3月31日(2011.3.31)

【出願人】(000003193)凸版印刷株式会社 (10,630)

【Fターム(参考)】

[ Back to top ]