半導体チップを3次元積層アセンブリへと多段に形成していく、はんだ接合プロセス

【課題】 エレクトロマイグレーション(EM)の耐性があり、ハイエンドの半導体チップにも採用できるようなプロセスとして、半導体チップを3次元積層アセンブリへと多段に形成していく、はんだ接合プロセスの提供。

【解決手段】

電気接合部に異なる融点をもつ2種のはんだを積層させて構成しておき、3次元積層アセンブリを作成するにあたって、チップ積層時(一次)は低温はんだのみを溶融して積層接合して、アンダーフィルによって封止する。マザーボードへの積層時(二次)は高温はんだを溶融させる。マザーボードへの二次実装時においてもそのギャップとバンプ形状を保持することができる。

【解決手段】

電気接合部に異なる融点をもつ2種のはんだを積層させて構成しておき、3次元積層アセンブリを作成するにあたって、チップ積層時(一次)は低温はんだのみを溶融して積層接合して、アンダーフィルによって封止する。マザーボードへの積層時(二次)は高温はんだを溶融させる。マザーボードへの二次実装時においてもそのギャップとバンプ形状を保持することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体チップのはんだ接合プロセスに関する。より詳しくは、半導体チップを、一次的に有機インターポーザへとはんだ接合し、二次的にマザーボードへとはんだ接合していく、3次元積層アセンブリまたは3次元積層デバイスの形成技術に関する。

【0002】

図1は、半導体チップを、一次的に有機インターポーザへとはんだ接合し、二次的にマザーボードへとはんだ接合していく、3次元積層アセンブリ(3次元積層デバイス)の形成プロセスを示す模式図である。

【0003】

半導体チップ、有機インターポーザ、マザーボード、の3つは、これらの各々が、積層されてはんだ接合されていく「基板」である。

【背景技術】

【0004】

図2は、従来技術のはんだバンプ適応例であるところの、従来はんだバンプ例1と従来はんだバンプ例2とを紹介して、解決すべき課題を説明する図である。

【0005】

3次元積層アセンブリにおいて電気的な接続をとるはんだバンプ接合部の金属には、電気的接続を容易にとることができ、積層される複数の基板の間に必要とされる機械強度の観点から適切な強度を有しながら、接合部保護のための封止樹脂の充填を可能にするために一定のギャップを保持できるような役割が求められる。

【0006】

図1や図2では、はんだバンプは大きく誇張して描いてあるが、実際には微細なものであり、はんだバンプによって形成される基板間のクリアランス(ギャップ)はかなり狭いものである。

【0007】

また、はんだバンプには、デバイス動作時の電流によるエレクトロマイグレーション(EM)に対する耐性も要求される。半導体チップとはんだバンプとの間には半導体チップの配線層(BEOL)の絶縁層としてLow−K層という比較的脆い性質の材料が配されている場合には、接合部において破壊が生じないように、柔軟性を要求される。

【0008】

従来はんだバンプ例1のように、貫通電極(TSV:Through Silicone Via)をもつ3次元積層アセンブリのはんだバンプ材料に対して、1種類のはんだ材料のみを用いると、1つ目の基板を接合する際には溶融したバンプに加熱と同時に高さ制御を行うことによりチップ間に所望のギャップを維持することができる。しかしさらに次の基板を積層する際にも同じ熱と荷重が加えられるため、最初の接合部のバンプが再溶融しそのチップ間のギャップを維持することができない。結果的に溶融したはんだがつぶれてしまい、電極間のショートが発生してしまう。

【0009】

そこで、従来はんだバンプ例2のように、ギャップを保持する目的で、所定の高さの銅ポストとはんだ材料を積層させた構成を適用することが考えられる。この手法に従えば、銅ポストの高さに応じたギャップは保持できるが、金属間化合物ではないはんだ層は、やはり積層時にバンプの周辺に押し出されてしまい、接合部に残らず、金属間化合物層のみが残る。

【0010】

残った金属間化合物層は機械的に硬く脆い性質を持つ。従って、積層されたチップが搭載される有機基板との熱膨張率(CTE)の違いに起因して反りなどの機械的ストレスが生じたり、機械的ストレスが外部から加わったときに、この銅ポストと金属間化合物のみからなる接合部にはそれらのストレスを受けとめられるだけの柔軟な領域がないため、相対的に脆い金属間化合物層において容易に破壊されてしまう。そこで、金属間化合物にはならない柔軟な鉛フリーはんだを残した状態で、接合とアンダーフィル(UF)による封止とを完了させてしまうことが好ましい。

【0011】

また、極めて薄い貫通電極付きのチップでは、積層接合する際に、熱加圧接合中の荷重や熱、あるいはバンプの高さばらつきなどに起因する機械的ストレスがチップに加わる。しかし、荷重をかけない加熱リフローでは、チップのわずかな反りによって接合が取れなくなってしまうことがあるため、採用することができない。したがって、いったん熱加圧接合した接合部のストレスを、その後の実装過程においてリリースするという必要が生じてくる。

【0012】

図3は、半導体チップの有機インターポーザへの通常の実装プロセスにおける温度プロファイルと、その温度プロファイルに沿った場合に有機インターポーザが受けるストレスを模式的に示す図である。

【0013】

通常は、このような温度プロファイルに沿ってバンプ金属の接合が行われる。しかし、現在多く用いられているSnAg系の鉛フリーバンプは、融点が約220度であり、かつ共晶はんだに比べて硬いため、接合完了後、220度から25度の常温までの温度変化によって、有機基板が大きく熱収縮し、これにより電極接合部の根元にあたる半導体チップの脆弱なLow−K層が破壊されてしまうことが大きな問題になっている。

【0014】

電極部の金属全体に低融点で柔軟な低温はんだを用いることによってこの問題は解決できるが、エレクトロマイグレーション(EM)の耐性がなく、ハイエンドの半導体チップには採用できなかった。

【0015】

特許文献1は、高融点鉛フリーはんだと、共晶はんだ(鉛はんだ)とを用いて、鉛はんだのみを溶融させて接合する技術を開示している。しかし、本発明が提案していくような、1次実装の接合部において2次実装で溶融する融点をもつ高融点鉛フリーはんだを採用し、接合完了後アンダーフィルで封止し、2次実装において2種のはんだ層を共融させるプロセスを適用するものではない。

【0016】

この他の従来例においても、一次実装時のLow−K層の破壊(White bump)対策と二次実装後の接合部の信頼性を両立できるようなプロセスは見あたらない。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】日本国 特許第3975569号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

背景技術の課題を解決するべく、エレクトロマイグレーション(EM)の耐性があり、ハイエンドの半導体チップにも採用できるようなプロセスとして、また半導体チップを3次元積層アセンブリへと多段に形成していく、はんだ接合プロセスが求められる。

【課題を解決するための手段】

【0019】

電気接合部に異なる融点をもつ2種のはんだを用い、3次元積層アセンブリを作成するにあたって、チップ積層時(一次)は低温はんだのみを溶融して積層接合して、アンダーフィルによって封止する。

【発明の効果】

【0020】

マザーボードへの二次実装時においてもそのギャップとバンプ形状を保持し、すなわち、多段積層時(二次)に加熱・加圧接合によって加えられる荷重と熱によって接合部が潰れることなく、高融点はんだの高さに準じた任意の高さを保つことができる。

【0021】

このバンプはすでにアンダーフィルで封止されているため、高融点はんだ部分が溶融してもチップが大きくずれたり、溶融した高融点はんだ層がつぶれてしまうことがない。

【0022】

低融点はんだの融点より低温でアンダーフィルを塗布・硬化させることによってチップ間のギャップおよびバンプ形状を固定し、基板への実装時に3次元積層構造の適切な基板間および電極間のクリアランスを保持したまま実装が可能となる。

【0023】

低コストでストレスの集中が少なく信頼性の高い3次元積層半導体アセンブリが実現できる。

【0024】

また、電気接合部のはんだは接合後もその全体が金属間化合物になることなく残存するため、適度な柔軟性を有し、相対的に少ない量の低融点はんだが高融点はんだに拡散し、高融点はんだ成分が主体となるため、EM耐性の観点からも優れたバンプとなる。

【0025】

さらには、二次実装では荷重をかけず加熱と自重のみによるリフロー接合が適用できるため、多段チップ積層時に加えられた貫通電極付き極薄チップに残留する大きな応力が高融点はんだが溶融することにより開放できる。

【図面の簡単な説明】

【0026】

【図1】図1は、半導体チップを、一次的に有機インターポーザへとはんだ接合し、二次的にマザーボードへとはんだ接合していく、3次元積層アセンブリ(3次元積層デバイス)の形成プロセスを示す模式図である。

【図2】図2は、従来技術のはんだバンプ適応例であるところの、従来はんだバンプ例1と従来はんだバンプ例2とを紹介して、解決すべき課題を説明する図である。

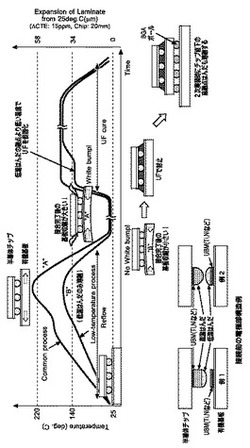

【図3】図3は、半導体チップの有機インターポーザへの通常の実装プロセスにおける温度プロファイルと、その温度プロファイルに沿った場合に有機インターポーザが受けるストレスを模式的に示す図である。

【図4】図4は、通常のプロセスAと本発明のプロセスBとを比較して説明する図である。

【図5】図5は、本発明のプロセスBに用いるところの、低融点はんだと高融点はんだとを積層させた構成を説明する図である。

【図6】図6は、本発明を実際に適用したはんだバンプの断面図である。

【発明を実施するための形態】

【0027】

図4は、通常のプロセスAと本発明のプロセスBとを比較して説明する図である。

【0028】

通常のプロセスAにおいては、はんだバンプの溶融のために220℃付近まで加熱される。ここで、チップの熱膨張係数(CTE)に比較して、有機インターポーザの熱膨張係数(CTE)の方が大きいため、これらの間の差(ΔCTE)約15ppmの分だけ、有機インターポーザが膨張する(基板膨張)。

【0029】

次に、溶融されたはんだを冷却してはんだ接合を完了するために温度を下げるが、この温度変化のプロセスにおいて、有機インターポーザが収縮する(基板収縮)。

【0030】

通常のプロセスAに比較して、本発明のプロセスBでは低温はんだのみを溶融させれば済むため、プロセスAに比較して温度が変化する落差が小さい分、接合完了後の基板収縮が小さくて済む。

【0031】

プロセスBでは、電気接合部に異なる融点をもつ2種のはんだを積層させて構成しておき、3次元積層アセンブリの基板積層時は、低温はんだのみを溶融して積層接合する。このことで、多段積層時に加熱・加圧接合によって加えられる荷重と熱によって接合部が潰れることなく、高融点はんだの高さに準じた任意の高さを保つ。

【0032】

すなわち、3次元チップのチップ積層接合時には低融点のバンプのみで積層接合し、その際、高融点のはんだは溶融せず、チップ間のギャップを保持するスペーサーの役割をする。

【0033】

続いて、アンダーフィルを塗布および硬化(あるいは半硬化)する。アンダーフィルによる封止である。ただし、その塗布・硬化(cure)の温度は低融点はんだの融点よりも低い温度を採用することが好ましい。

【0034】

もっとも、2段ステップの本硬化プロセスの場合、アンダーフィルの流動性が十分に低くなった時点以降であれば、硬化温度が低融点はんだの融点を超えてもよい。あるいは、流動性が十分に低くなれば、半硬化の状態で2次実装を行ってもよい。

【0035】

アンダーフィルの適用方法は、接合完了後のキャピラリー工法等に限定されるものではなく、接合と同時に樹脂硬化を行う、事前塗布工法などの手法であってもよい。

【0036】

その後、積層チップの2次実装時にアンダーフィルに封止されたバンプのうち高融点はんだ部分も溶融し、接合部全体が概ね高融点半田成分で均質化される。

【0037】

また、高融点はんだの溶融を通じて、チップの多段積層の接合時の荷重および熱履歴、あるいはバンプの高さばらつきに起因する積層チップ内の残留応力を開放することが可能となり、3次元半導体デバイス固有の貫通電極を持つ極薄チップに残留する機械ストレスを緩和し、3次元積層アセンブリの信頼性を向上する。

【0038】

2次実装時に積層チップ間の高融点はんだが溶融することにより、電極部の大部分を占める高融点はんだが残存する少量の低融点はんだと共融し、高融点はんだの物性に近い高信頼性のはんだ接続が形成される。

【0039】

図5は、本発明のプロセスBに用いるところの、低融点はんだと高融点はんだとを積層させた構成を説明する図である。

【0040】

(第1の)はんだバンプとしては、相対的に融点の低いはんだ材料(低融点はんだ)の上に相対的に融点の高いはんだ材料(高融点はんだ)が積層されて構成されている。有機インターポーザの上に低融点はんだが提供されていればよく、低融点はんだが例1のように高融点はんだに付随して提供されてもよく、低融点はんだが(高融点はんだから分離されて)例2のように有機インターポーザの側から提供されてもよい。

【0041】

3次元多段積層基板間に用いる2種のはんだ材料の成分として、高融点はんだとしてはSnAg、SnAgCu、あるいは少なくともSnを含み、2次実装時に溶融するために、2次実装において接合を行う電極材料と同等あるいはそれ以下の融点を有するものを用いる。これにより、有機基板に搭載した際に、基板の熱膨張などにより積層チップに加えられるストレスを緩和できる。

【0042】

また、低融点はんだとしてはSn、Bi、Inのうち少なくとも1種を含み、前記高融点はんだより20度以上融点が低いように設定する。

【実施例】

【0043】

図6は、本発明を実際に適用したはんだバンプの断面図である。

【0044】

第1のはんだバンプを構成している相対的に融点の低いはんだ材料の融点が、140℃であり、第1のはんだバンプを構成している相対的に融点の高いはんだ材料の融点が、220℃であり、アンダーフィル材料による封止が、110℃で塗布して、120℃で予備硬化、150℃で本硬化させることによって実行され、第2のはんだバンプの融点が第1のはんだバンプの高融点成分と同じ220℃であり、2次実装を想定したリフロー温度である250℃を経たという条件において実験されたものである。

【0045】

この実施例により、高温リフロー後も、はんだバンプの高さ/ギャップが良好に維持されていることを確認している。

【0046】

本発明は、特定の狭い(絶対的な)温度条件でしか適用できないものではなく、融点、塗布温度、硬化温度、接合温度、を相対的な関係において工夫して設定すれば、本発明の技術的思想を具現化させることができる。

【0047】

本発明は、半導体チップ、有機インターポーザ、マザーボードという3種類の「基板」に対するはんだ接合として説明してきたが、本発明の技術的思想は、解決すべき課題の共通性があれば、これら3種類の「基板」に限られることなく、広く適用することができる。「半導体」「有機」「マザー」という表現に限定的な意味はなく、相対的に異なる性質の基板であることを示し、別個の役割を担うべき基板として、説明の便宜上に採用しているにすぎない。

【技術分野】

【0001】

本発明は、半導体チップのはんだ接合プロセスに関する。より詳しくは、半導体チップを、一次的に有機インターポーザへとはんだ接合し、二次的にマザーボードへとはんだ接合していく、3次元積層アセンブリまたは3次元積層デバイスの形成技術に関する。

【0002】

図1は、半導体チップを、一次的に有機インターポーザへとはんだ接合し、二次的にマザーボードへとはんだ接合していく、3次元積層アセンブリ(3次元積層デバイス)の形成プロセスを示す模式図である。

【0003】

半導体チップ、有機インターポーザ、マザーボード、の3つは、これらの各々が、積層されてはんだ接合されていく「基板」である。

【背景技術】

【0004】

図2は、従来技術のはんだバンプ適応例であるところの、従来はんだバンプ例1と従来はんだバンプ例2とを紹介して、解決すべき課題を説明する図である。

【0005】

3次元積層アセンブリにおいて電気的な接続をとるはんだバンプ接合部の金属には、電気的接続を容易にとることができ、積層される複数の基板の間に必要とされる機械強度の観点から適切な強度を有しながら、接合部保護のための封止樹脂の充填を可能にするために一定のギャップを保持できるような役割が求められる。

【0006】

図1や図2では、はんだバンプは大きく誇張して描いてあるが、実際には微細なものであり、はんだバンプによって形成される基板間のクリアランス(ギャップ)はかなり狭いものである。

【0007】

また、はんだバンプには、デバイス動作時の電流によるエレクトロマイグレーション(EM)に対する耐性も要求される。半導体チップとはんだバンプとの間には半導体チップの配線層(BEOL)の絶縁層としてLow−K層という比較的脆い性質の材料が配されている場合には、接合部において破壊が生じないように、柔軟性を要求される。

【0008】

従来はんだバンプ例1のように、貫通電極(TSV:Through Silicone Via)をもつ3次元積層アセンブリのはんだバンプ材料に対して、1種類のはんだ材料のみを用いると、1つ目の基板を接合する際には溶融したバンプに加熱と同時に高さ制御を行うことによりチップ間に所望のギャップを維持することができる。しかしさらに次の基板を積層する際にも同じ熱と荷重が加えられるため、最初の接合部のバンプが再溶融しそのチップ間のギャップを維持することができない。結果的に溶融したはんだがつぶれてしまい、電極間のショートが発生してしまう。

【0009】

そこで、従来はんだバンプ例2のように、ギャップを保持する目的で、所定の高さの銅ポストとはんだ材料を積層させた構成を適用することが考えられる。この手法に従えば、銅ポストの高さに応じたギャップは保持できるが、金属間化合物ではないはんだ層は、やはり積層時にバンプの周辺に押し出されてしまい、接合部に残らず、金属間化合物層のみが残る。

【0010】

残った金属間化合物層は機械的に硬く脆い性質を持つ。従って、積層されたチップが搭載される有機基板との熱膨張率(CTE)の違いに起因して反りなどの機械的ストレスが生じたり、機械的ストレスが外部から加わったときに、この銅ポストと金属間化合物のみからなる接合部にはそれらのストレスを受けとめられるだけの柔軟な領域がないため、相対的に脆い金属間化合物層において容易に破壊されてしまう。そこで、金属間化合物にはならない柔軟な鉛フリーはんだを残した状態で、接合とアンダーフィル(UF)による封止とを完了させてしまうことが好ましい。

【0011】

また、極めて薄い貫通電極付きのチップでは、積層接合する際に、熱加圧接合中の荷重や熱、あるいはバンプの高さばらつきなどに起因する機械的ストレスがチップに加わる。しかし、荷重をかけない加熱リフローでは、チップのわずかな反りによって接合が取れなくなってしまうことがあるため、採用することができない。したがって、いったん熱加圧接合した接合部のストレスを、その後の実装過程においてリリースするという必要が生じてくる。

【0012】

図3は、半導体チップの有機インターポーザへの通常の実装プロセスにおける温度プロファイルと、その温度プロファイルに沿った場合に有機インターポーザが受けるストレスを模式的に示す図である。

【0013】

通常は、このような温度プロファイルに沿ってバンプ金属の接合が行われる。しかし、現在多く用いられているSnAg系の鉛フリーバンプは、融点が約220度であり、かつ共晶はんだに比べて硬いため、接合完了後、220度から25度の常温までの温度変化によって、有機基板が大きく熱収縮し、これにより電極接合部の根元にあたる半導体チップの脆弱なLow−K層が破壊されてしまうことが大きな問題になっている。

【0014】

電極部の金属全体に低融点で柔軟な低温はんだを用いることによってこの問題は解決できるが、エレクトロマイグレーション(EM)の耐性がなく、ハイエンドの半導体チップには採用できなかった。

【0015】

特許文献1は、高融点鉛フリーはんだと、共晶はんだ(鉛はんだ)とを用いて、鉛はんだのみを溶融させて接合する技術を開示している。しかし、本発明が提案していくような、1次実装の接合部において2次実装で溶融する融点をもつ高融点鉛フリーはんだを採用し、接合完了後アンダーフィルで封止し、2次実装において2種のはんだ層を共融させるプロセスを適用するものではない。

【0016】

この他の従来例においても、一次実装時のLow−K層の破壊(White bump)対策と二次実装後の接合部の信頼性を両立できるようなプロセスは見あたらない。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】日本国 特許第3975569号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

背景技術の課題を解決するべく、エレクトロマイグレーション(EM)の耐性があり、ハイエンドの半導体チップにも採用できるようなプロセスとして、また半導体チップを3次元積層アセンブリへと多段に形成していく、はんだ接合プロセスが求められる。

【課題を解決するための手段】

【0019】

電気接合部に異なる融点をもつ2種のはんだを用い、3次元積層アセンブリを作成するにあたって、チップ積層時(一次)は低温はんだのみを溶融して積層接合して、アンダーフィルによって封止する。

【発明の効果】

【0020】

マザーボードへの二次実装時においてもそのギャップとバンプ形状を保持し、すなわち、多段積層時(二次)に加熱・加圧接合によって加えられる荷重と熱によって接合部が潰れることなく、高融点はんだの高さに準じた任意の高さを保つことができる。

【0021】

このバンプはすでにアンダーフィルで封止されているため、高融点はんだ部分が溶融してもチップが大きくずれたり、溶融した高融点はんだ層がつぶれてしまうことがない。

【0022】

低融点はんだの融点より低温でアンダーフィルを塗布・硬化させることによってチップ間のギャップおよびバンプ形状を固定し、基板への実装時に3次元積層構造の適切な基板間および電極間のクリアランスを保持したまま実装が可能となる。

【0023】

低コストでストレスの集中が少なく信頼性の高い3次元積層半導体アセンブリが実現できる。

【0024】

また、電気接合部のはんだは接合後もその全体が金属間化合物になることなく残存するため、適度な柔軟性を有し、相対的に少ない量の低融点はんだが高融点はんだに拡散し、高融点はんだ成分が主体となるため、EM耐性の観点からも優れたバンプとなる。

【0025】

さらには、二次実装では荷重をかけず加熱と自重のみによるリフロー接合が適用できるため、多段チップ積層時に加えられた貫通電極付き極薄チップに残留する大きな応力が高融点はんだが溶融することにより開放できる。

【図面の簡単な説明】

【0026】

【図1】図1は、半導体チップを、一次的に有機インターポーザへとはんだ接合し、二次的にマザーボードへとはんだ接合していく、3次元積層アセンブリ(3次元積層デバイス)の形成プロセスを示す模式図である。

【図2】図2は、従来技術のはんだバンプ適応例であるところの、従来はんだバンプ例1と従来はんだバンプ例2とを紹介して、解決すべき課題を説明する図である。

【図3】図3は、半導体チップの有機インターポーザへの通常の実装プロセスにおける温度プロファイルと、その温度プロファイルに沿った場合に有機インターポーザが受けるストレスを模式的に示す図である。

【図4】図4は、通常のプロセスAと本発明のプロセスBとを比較して説明する図である。

【図5】図5は、本発明のプロセスBに用いるところの、低融点はんだと高融点はんだとを積層させた構成を説明する図である。

【図6】図6は、本発明を実際に適用したはんだバンプの断面図である。

【発明を実施するための形態】

【0027】

図4は、通常のプロセスAと本発明のプロセスBとを比較して説明する図である。

【0028】

通常のプロセスAにおいては、はんだバンプの溶融のために220℃付近まで加熱される。ここで、チップの熱膨張係数(CTE)に比較して、有機インターポーザの熱膨張係数(CTE)の方が大きいため、これらの間の差(ΔCTE)約15ppmの分だけ、有機インターポーザが膨張する(基板膨張)。

【0029】

次に、溶融されたはんだを冷却してはんだ接合を完了するために温度を下げるが、この温度変化のプロセスにおいて、有機インターポーザが収縮する(基板収縮)。

【0030】

通常のプロセスAに比較して、本発明のプロセスBでは低温はんだのみを溶融させれば済むため、プロセスAに比較して温度が変化する落差が小さい分、接合完了後の基板収縮が小さくて済む。

【0031】

プロセスBでは、電気接合部に異なる融点をもつ2種のはんだを積層させて構成しておき、3次元積層アセンブリの基板積層時は、低温はんだのみを溶融して積層接合する。このことで、多段積層時に加熱・加圧接合によって加えられる荷重と熱によって接合部が潰れることなく、高融点はんだの高さに準じた任意の高さを保つ。

【0032】

すなわち、3次元チップのチップ積層接合時には低融点のバンプのみで積層接合し、その際、高融点のはんだは溶融せず、チップ間のギャップを保持するスペーサーの役割をする。

【0033】

続いて、アンダーフィルを塗布および硬化(あるいは半硬化)する。アンダーフィルによる封止である。ただし、その塗布・硬化(cure)の温度は低融点はんだの融点よりも低い温度を採用することが好ましい。

【0034】

もっとも、2段ステップの本硬化プロセスの場合、アンダーフィルの流動性が十分に低くなった時点以降であれば、硬化温度が低融点はんだの融点を超えてもよい。あるいは、流動性が十分に低くなれば、半硬化の状態で2次実装を行ってもよい。

【0035】

アンダーフィルの適用方法は、接合完了後のキャピラリー工法等に限定されるものではなく、接合と同時に樹脂硬化を行う、事前塗布工法などの手法であってもよい。

【0036】

その後、積層チップの2次実装時にアンダーフィルに封止されたバンプのうち高融点はんだ部分も溶融し、接合部全体が概ね高融点半田成分で均質化される。

【0037】

また、高融点はんだの溶融を通じて、チップの多段積層の接合時の荷重および熱履歴、あるいはバンプの高さばらつきに起因する積層チップ内の残留応力を開放することが可能となり、3次元半導体デバイス固有の貫通電極を持つ極薄チップに残留する機械ストレスを緩和し、3次元積層アセンブリの信頼性を向上する。

【0038】

2次実装時に積層チップ間の高融点はんだが溶融することにより、電極部の大部分を占める高融点はんだが残存する少量の低融点はんだと共融し、高融点はんだの物性に近い高信頼性のはんだ接続が形成される。

【0039】

図5は、本発明のプロセスBに用いるところの、低融点はんだと高融点はんだとを積層させた構成を説明する図である。

【0040】

(第1の)はんだバンプとしては、相対的に融点の低いはんだ材料(低融点はんだ)の上に相対的に融点の高いはんだ材料(高融点はんだ)が積層されて構成されている。有機インターポーザの上に低融点はんだが提供されていればよく、低融点はんだが例1のように高融点はんだに付随して提供されてもよく、低融点はんだが(高融点はんだから分離されて)例2のように有機インターポーザの側から提供されてもよい。

【0041】

3次元多段積層基板間に用いる2種のはんだ材料の成分として、高融点はんだとしてはSnAg、SnAgCu、あるいは少なくともSnを含み、2次実装時に溶融するために、2次実装において接合を行う電極材料と同等あるいはそれ以下の融点を有するものを用いる。これにより、有機基板に搭載した際に、基板の熱膨張などにより積層チップに加えられるストレスを緩和できる。

【0042】

また、低融点はんだとしてはSn、Bi、Inのうち少なくとも1種を含み、前記高融点はんだより20度以上融点が低いように設定する。

【実施例】

【0043】

図6は、本発明を実際に適用したはんだバンプの断面図である。

【0044】

第1のはんだバンプを構成している相対的に融点の低いはんだ材料の融点が、140℃であり、第1のはんだバンプを構成している相対的に融点の高いはんだ材料の融点が、220℃であり、アンダーフィル材料による封止が、110℃で塗布して、120℃で予備硬化、150℃で本硬化させることによって実行され、第2のはんだバンプの融点が第1のはんだバンプの高融点成分と同じ220℃であり、2次実装を想定したリフロー温度である250℃を経たという条件において実験されたものである。

【0045】

この実施例により、高温リフロー後も、はんだバンプの高さ/ギャップが良好に維持されていることを確認している。

【0046】

本発明は、特定の狭い(絶対的な)温度条件でしか適用できないものではなく、融点、塗布温度、硬化温度、接合温度、を相対的な関係において工夫して設定すれば、本発明の技術的思想を具現化させることができる。

【0047】

本発明は、半導体チップ、有機インターポーザ、マザーボードという3種類の「基板」に対するはんだ接合として説明してきたが、本発明の技術的思想は、解決すべき課題の共通性があれば、これら3種類の「基板」に限られることなく、広く適用することができる。「半導体」「有機」「マザー」という表現に限定的な意味はなく、相対的に異なる性質の基板であることを示し、別個の役割を担うべき基板として、説明の便宜上に採用しているにすぎない。

【特許請求の範囲】

【請求項1】

一次的に半導体チップを有機インターポーザにはんだ接合し、二次的にその有機インターポーザをマザーボードにはんだ接合する方法であって、

第1のはんだバンプであって、相対的に融点の低いはんだ材料の上に相対的に融点の高いはんだ材料が積層されて構成されている第1のはんだバンプを、有機インターポーザの上に提供するステップと、

相対的に融点の低いはんだ材料は溶融するものの、相対的に融点の高いはんだ材料は溶融しない第1の温度において、第1のはんだバンプを加熱するステップと、

半導体チップと有機インターポーザとの間のギャップ空間をアンダーフィル材料によって封止するステップと、

その有機インターポーザをマザーボードにはんだ接合するにあたって、相対的に融点の高いはんだ材料が溶融する第2の温度において、第1のはんだバンプを加熱するステップとを有する、

方法。

【請求項2】

相対的に融点の高いはんだ材料が溶融する第2の温度において、第1のはんだバンプを加熱するステップの前に、さらなるステップとして、

第2の温度において溶融する第2のはんだバンプ(BGA)を、マザーボードの上に提供するステップとを有する、

請求項1に記載の方法。

【請求項3】

相対的に融点の低いはんだ材料が、Sn、Bi、Inのうちの少なくとも1の元素を含む材料であり、

相対的に融点の高いはんだ材料が、SnAg、SnCu、SnAgCu、または少なくともSnを含む合金から選択される材料である、

請求項1に記載の方法。

【請求項4】

半導体チップと、提供される第1のはんだバンプとの間に、Low−K層が配されている、

請求項1に記載の方法。

【請求項5】

第1のはんだバンプを構成している相対的に融点の低いはんだ材料の融点が、140℃であり、

第1のはんだバンプを構成している相対的に融点の高いはんだ材料の融点が、220℃であり、

アンダーフィル材料による封止が、110℃で塗布して、120℃ですくなくとも予備硬化させることによって実行され、

第2のはんだバンプの融点が、220℃である、

請求項2に記載の方法。

【請求項6】

請求項1〜5の何れかの方法によって形成される、

半導体チップ、有機インターポーザ、および、マザーボード、がはんだ接合された、

3次元積層アセンブリ。

【請求項1】

一次的に半導体チップを有機インターポーザにはんだ接合し、二次的にその有機インターポーザをマザーボードにはんだ接合する方法であって、

第1のはんだバンプであって、相対的に融点の低いはんだ材料の上に相対的に融点の高いはんだ材料が積層されて構成されている第1のはんだバンプを、有機インターポーザの上に提供するステップと、

相対的に融点の低いはんだ材料は溶融するものの、相対的に融点の高いはんだ材料は溶融しない第1の温度において、第1のはんだバンプを加熱するステップと、

半導体チップと有機インターポーザとの間のギャップ空間をアンダーフィル材料によって封止するステップと、

その有機インターポーザをマザーボードにはんだ接合するにあたって、相対的に融点の高いはんだ材料が溶融する第2の温度において、第1のはんだバンプを加熱するステップとを有する、

方法。

【請求項2】

相対的に融点の高いはんだ材料が溶融する第2の温度において、第1のはんだバンプを加熱するステップの前に、さらなるステップとして、

第2の温度において溶融する第2のはんだバンプ(BGA)を、マザーボードの上に提供するステップとを有する、

請求項1に記載の方法。

【請求項3】

相対的に融点の低いはんだ材料が、Sn、Bi、Inのうちの少なくとも1の元素を含む材料であり、

相対的に融点の高いはんだ材料が、SnAg、SnCu、SnAgCu、または少なくともSnを含む合金から選択される材料である、

請求項1に記載の方法。

【請求項4】

半導体チップと、提供される第1のはんだバンプとの間に、Low−K層が配されている、

請求項1に記載の方法。

【請求項5】

第1のはんだバンプを構成している相対的に融点の低いはんだ材料の融点が、140℃であり、

第1のはんだバンプを構成している相対的に融点の高いはんだ材料の融点が、220℃であり、

アンダーフィル材料による封止が、110℃で塗布して、120℃ですくなくとも予備硬化させることによって実行され、

第2のはんだバンプの融点が、220℃である、

請求項2に記載の方法。

【請求項6】

請求項1〜5の何れかの方法によって形成される、

半導体チップ、有機インターポーザ、および、マザーボード、がはんだ接合された、

3次元積層アセンブリ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−93507(P2013−93507A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−235876(P2011−235876)

【出願日】平成23年10月27日(2011.10.27)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構、立体構造新機能集積回路(ドリームチップ)技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月27日(2011.10.27)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成20年度、独立行政法人新エネルギー・産業技術総合開発機構、立体構造新機能集積回路(ドリームチップ)技術開発 委託事業、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MACHINES CORPORATION

【Fターム(参考)】

[ Back to top ]