半導体チップパッケージ

【課題】集積回路チップ内の電圧発生回路で発生されるパワーノイズを除去又は最小化できる半導体チップパッケージを提供する。

【解決手段】半導体チップパッケージは、外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記電圧発生回路の前記供給電圧の出力ノードに接続された接続ターミナルとを含む集積回路チップと、前記供給電圧に対するパワーノイズを減少させるために前記接続ターミナルに電気的に接続されたノイズ除去器と、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有する。

【解決手段】半導体チップパッケージは、外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記電圧発生回路の前記供給電圧の出力ノードに接続された接続ターミナルとを含む集積回路チップと、前記供給電圧に対するパワーノイズを減少させるために前記接続ターミナルに電気的に接続されたノイズ除去器と、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積回路チップのパワーノイズ除去に関し、より詳細には、外部電源電圧を受信して内部回路に必要とされる電圧を提供する回路でのパワーノイズを減少させるための半導体チップパッケージに関する。

【背景技術】

【0002】

ダイナミックランダムアクセスメモリ(以下、DRAM)等のような半導体メモリを含む集積回路チップは、パッケージング(packaging)された後に外部から電源を受信して動作する。

外部電源電圧供給ターミナルを通じて印加される外部電源電圧(External Voltage)は、外部環境や集積回路チップの動作の時に発生するノイズ等によって電圧レベルが変動され得る。

しかし、外部電源電圧のレベルは必要によって、自由に変更することは難しい。

【0003】

多数の集積回路チップには、外部電源電圧をチップ内部で必要とされる電源電圧のレベルに変換するためのIVC(Internal Voltage Converter)等のような電圧発生回路が具備されている。

IVCは、半導体素子の動作に適合する電圧を比較的自由に生成できる。IVCは、ネガティブフィードバック(Negative Feedback)を通じて外部電源電圧が変化してもこれに関わらず、内部電圧を安定的に維持することができる。IVCを活用すれば、半導体素子の動作パラメーター(Parameter)が便利に制御され得る。

【0004】

従って、IVCのような電圧発生回路は、多様な電源電圧を有する製品に対応が可能であり、消費電力の減少にも役に立つ。

しかしながら、電圧発生回路に接続された内部回路の高速化にしたがって発生するパワーノイズに対して脆弱な面があるという問題がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】韓国特許出願公開第10−2004−0120174号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は上記従来の集積回路チップにおける問題点に鑑みてなされたものであって、本発明の目的は、集積回路チップ内の電圧発生回路で発生されるパワーノイズを除去又は最小化できる半導体チップパッケージを提供することにある。

また、本発明の他の目的は、半導体メモリ装置の内部電圧発生回路で発生されるパワーノイズを除去又は最小化できる半導体チップパッケージを提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するためになされた本発明による半導体チップパッケージは、外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記電圧発生回路の前記供給電圧の出力ノードに接続された接続ターミナルとを含む集積回路チップと、前記供給電圧に対するパワーノイズを減少させるために前記接続ターミナルに電気的に接続されたノイズ除去器と、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有することを特徴とする。

【0008】

前記電圧発生回路は、周辺回路やセルアレイに必要とされる前記供給電圧を発生する内部電圧コンバーターであることが好ましい。

前記電圧発生回路は、前記外部電源電圧以上の高電圧を発生する高電圧発生回路であることが好ましい。

前記電圧発生回路は、バックバイアス電圧を発生するバックバイアス電圧発生回路であることが好ましい。

前記ノイズ除去器は、前記パワーノイズを除去するためのデカップリング素子であることが好ましい。

前記デカップリング素子は、前記搭載基板の上部に形成されるデカップリングキャパシターであることが好ましい。

前記デカップリング素子は、前記搭載基板の内部に形成されるデカップリングキャパシターであることが好ましい。

前記デカップリングキャパシターは、ワイヤボンディングを使用して前記接続ターミナルと接続されることが好ましい。

【0009】

また、上記目的を達成するためになされた本発明による半導体チップパッケージは、外部電源電圧を受信して分配する外部電圧供給回路と、前記外部電圧供給回路から分配された外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記外部電圧供給回路の入力ノードに接続された第1接続ターミナルと前記電圧発生回路の前記供給電圧の出力ノードに接続された第2接続ターミナルとを具備する集積回路チップと、前記外部電源電圧に対するパワーノイズ及び前記供給電圧に対するパワーノイズを減少させるために前記第1及び第2接続ターミナルに各々独立的に接続された第1及び第2ノイズ除去器を具備し、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有することを特徴とする。

【0010】

前記電圧発生回路は、半導体メモリの周辺回路やメモリセルアレイに必要とされる内部電圧を発生する内部電圧コンバーターであることが好ましい。

【発明の効果】

【0011】

本発明に係る半導体チップパッケージによれば、集積回路チップ内の電圧発生回路で発生するパワーノイズが搭載基板に形成されるノイズ除去器によって効率的に除去又は最小化されるという効果がある。

したがって、DRAM等のような半導体メモリ装置の内部電圧コンバーターに本発明が適用される場合に内部回路はより安定的な内部電圧を受信できる。したがって、半導体メモリ装置のデータアクセス動作に対する信頼性が改善されるという効果がある。

【図面の簡単な説明】

【0012】

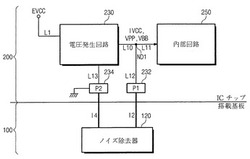

【図1】本発明の実施形態による半導体チップパッケージの回路接続ブロック図である。

【図2】図1の変形実施形態による回路接続ブロック図である。

【図3】図1の半導体チップパッケージの例示断面構造を示す断面図である。

【図4】図3の半導体チップパッケージの例示的な機能回路を示すブロック図である。

【図5】図3の半導体チップパッケージでデカップリングキャパシターと集積回路チップ内の回路との間の電気的接続を示す例示回路図である。

【図6】図5のデカップリングキャパシターの等価回路図である。

【図7】図5の中のIVCを具体的に例示する回路図である。

【図8】図7での電圧の波形を示すグラフである。

【図9】本発明が例示的に適用される揮発性メモリチップのパッケージ構造を示した概略的な断面図である。

【図10】本発明が例示的に適用される不揮発性メモリチップのパッケージ構造を示した概略的な断面図である。

【発明を実施するための形態】

【0013】

次に、本発明に係る半導体チップパッケージを実施するための形態の具体例を図面を参照しながら説明する。

【0014】

上述したような本発明の目的、他の目的、特徴、及び長所は添付した図面と関連した以下の望ましい実施形態を通じて容易に理解できる。しかし、本発明はここで説明される実施形態に限定されなく、他の形態に具体化できる。むしろ、ここで紹介される実施形態は、理解を容易に提供する意図以外には他の意図が無く、開示された内容がより徹底であり、完全になるように、そして当業者に本発明の思想が十分に伝達されるようにするために提供するものである。

【0015】

本明細書で、いずれかの素子又はラインが対象素子ブロックに接続されると言及された場合にそれは直接的な接続されるのみでなく、いずれかの他の素子を通じて対象素子ブロックに間接的に接続された意味までも含む。

また、できるだけ、各図面で提示された同一又は類似な参照符号は同一又は類似な構成要素を示す。一部図面において、素子及びラインの連結関係は技術的内容の効果的な説明をために示したのみであり、他の素子や回路ブロックがさらに具備され得る。

ここに説明され、例示される各実施形態はそれの相補的な実施形態も包含でき、IVC回路及び半導体パッケージに基本的動作と構造とに関する詳細は本発明の要旨を曖昧にしないようにするために詳細に説明されなかったことを留意しなければならない。

【0016】

図1は、本発明の実施形態による半導体チップパッケージの回路接続ブロック図である。

図1を参照すると、半導体チップパッケージは、集積回路チップ200と搭載基板100と含む。

【0017】

集積回路チップ200は、外部電源電圧を受信して内部回路250に使用される供給電圧を発生する電圧発生回路230と、電圧発生回路230の供給電圧の出力ノードND1に接続された接続ターミナル232を具備する。

【0018】

搭載基板100は、供給電圧に対するパワーノイズを減少させるために接続ターミナル232に電気的に接続されたノイズ除去器120を具備し、半導体チップパッケージとして集積回路チップをパッケージングするために集積回路チップ200を搭載する。

集積回路チップ200がDRAM等の半導体メモリ装置である場合にメモリセルアレイ、コア回路、及び周辺回路を包含し得る。

【0019】

電圧発生回路230は、周辺回路やメモリセルアレイに必要とされる内部電圧IVCCを発生する内部電圧コンバーターIVC(Internal Voltage Converter)、外部電源電圧以上の高電圧VPPを発生する高電圧発生回路、又はバック(back)バイアス電圧を発生するバックバイアス電圧発生回路であり得る。

【0020】

搭載基板100に配置されたノイズ除去器120は、パワーノイズを除去するためのデカップリング素子としてデカップリングキャパシターであり得る。

デカップリング素子は、搭載基板100の上部、内部、下部、又は側部に形成され得る。

デカップリングキャパシターは、接続ターミナル232にワイヤボンディングを通じて接続されるか、或いはフリップチップボンディングを通じて接続され得る。

【0021】

デカップリングキャパシターは、SMT実装又は埋め込み型(Embedded)実装方式によって搭載基板100搭載され得る。

ここで、デカップリング素子はフィルムタイプキャパシター(Film Type Capacitor)やシリコンキャパシター(Silicon Capacitor)であり得る。

【0022】

図1で、電圧発生回路230がラインL1を通じて外部電源電圧EVCCを受信して内部回路250で使用される供給電圧(例:IVCC)を出力ラインL10を通じて出力すれば、内部回路250は出力ノードND1に接続されたラインL11を通じて内部電源電圧を受信する。

電圧発生回路230の動作や内部回路250の高速動作によって負荷が変動されれば、パワーノイズが発生し、出力ノードND1は発生したパワーノイズに影響を受ける。

【0023】

パワーノイズは、出力ノードND1にラインL12を通じて接続されたパッド等の接続ターミナル232にも現れる。

本発明の実施形態では相互接続ラインI2を通じて接続ターミナル232とノイズ除去器120とを電気的に接続することによって電圧発生回路230のパワーノイズを除去又は最小化する。

一方、ラインL13を通じて電圧発生回路230に接続された接続ターミナル234は接地パッドとして機能し、ノイズ除去器120とは接地用相互接続ラインI4を通じて接続される。

【0024】

ノイズ除去器120は、集積回路チップ200の外部に位置する搭載基板100に形成される。

したがって、集積回路チップ200の内部に配置されるノイズ除去器に比べて容量を相対的にさらに大きくすることができるので、ノイズ除去性能が著しく優れる。

【0025】

具体的に、ノイズ除去器としてデカップリングキャパシター(Decoupling Capacitor)は、システム基板、半導体パッケージの搭載基板、又は集積回路チップの内部に設置され得る。デカップリングキャパシターが集積回路チップの内部に位置される場合に効率は相対的に良いが、チップの制限された面積でよってキャパシターの容量は比較的低い。したがって、チップパッケージの搭載基板100にデカップリングキャパシターを形成する方式が利用される。

【0026】

このように、集積回路チップ内の電圧発生回路230で発生するパワーノイズが搭載基板100に形成されるノイズ除去器120によって効率的に除去又は最小化される。

したがって、DRAM等のような半導体メモリ装置の内部電圧コンバーターIVCに図1のスキームが適用される場合に電圧発生回路230の電源及びグラウンドの変動(Fluctuation)が抑制されて内部回路250はノイズ除去された、さらに安定的な内部電圧を受信できる。したがって、DRAM等のような半導体メモリ装置のパワーノイズの免疫性(Immunity)が向上されてデータアクセス動作に対する信頼性が改善される。

【0027】

図2は、図1の変形実施形態による回路接続ブロック図である。

図2を参照すると、図1のノイズ除去器に対応するデカップリング素子121が絶縁領域300に形成される。

絶縁領域300は、集積回路チップ200の上部に形成される領域であり得る。

しかし、異なる場合には絶縁領域300は図1の搭載基板100に形成された領域であり得る。

【0028】

IVC231がラインL1を通じて外部電源電圧EVCCを受信して内部回路250に使用される供給電圧(例:IVCC)を出力ラインL10を通じて出力すれば、内部回路250は出力ノードND1に接続されたラインL11を通じて内部電源電圧を受信する。

IVC231や内部回路250によってパワーノイズが発生すれば、出力ノードND1は発生したパワーノイズの影響を受ける。

【0029】

図1と類似して、パワーノイズは、出力ノードND1にラインL12を通じて接続されたパッド等の接続ターミナル232にも現れる。

本発明の実施形態では相互接続ラインI2を通じて接続ターミナル232とデカップリング素子121とを電気的に接続することによって、IVC231のパワーノイズを除去又は最小化する。一方、IVC231に接続された接続ターミナル234は接地パッドとして機能し、デカップリング素子121とは接地用相互接続ラインI4を通じて接続される。

【0030】

図2の半導体チップパッケージの構造でも集積回路チップ内のIVC231又は高電圧発生器で発生するパワーノイズが、絶縁領域250に形成されるデカップリング素子121によって効率的に除去又は最小化される。

【0031】

図3は、図1の半導体チップパッケージの例示断面構造を示す断面図である。

図3を参照すると、集積回路チップ200は搭載基板100の上部に搭載される。

ノイズ除去をためのデカップリング素子C1、C2は搭載基板100の上部に形成されて集積回路チップ200内の電圧発生回路230に接続され得る。

デカップリング素子C3、C4は搭載基板100の下部に形成されて集積回路チップ200内の電圧発生回路230に接続され得る。

デカップリング素子C5、C6は搭載基板100の内部に形成されて集積回路チップ200内の電圧発生回路230に接続され得る。

デカップリング素子C7、C8は搭載基板100の側部に形成されて集積回路チップ200内の電圧発生回路230に接続され得る。

【0032】

半導体チップパッケージは、ボードの上でコントローラやマイクロプロセッサー等のような外部装置と電気的に接続するために搭載基板100に形成された接触バンパー(B1〜B6)を有することができる。

図3で、集積回路チップ200の内部で発生するパワーノイズは、搭載基板100に形成されるデカップリング素子(C1〜C8)の中で少なくとも1つによって効率的に除去又は最小化される。

【0033】

図4は、図3の半導体チップパッケージの例示的な機能回路を示すブロック図である。

図4を参照すると、ノイズ除去器としての第1デカップリングキャパシター123と第2デカップリングキャパシター121とは搭載基板100に形成される。

外部電圧供給回路(EVSC)210、IVC231、データ出力バッファ241、周辺回路252、及びセルアレイ回路254は集積回路チップ200に形成される。

【0034】

外部電圧供給回路210は、外部電源電圧EVCCを受信して分配する。

IVC231は、外部電圧供給回路210から分配された外部電源電圧を受信して内部回路に使用される供給電圧を発生する。

【0035】

周辺回路252とセルアレイ回路254とは、内部回路250に属する回路である。

周辺回路252は、IVC231から周辺内部電源電圧VINTPを受信する。

セルアレイ回路254は、IVC231からアレイ内部電源電圧VINTAを受信する。

【0036】

データ出力バッファ241は、メモリセルに格納されたデータを外部へ出力するためのバッファとして外部電圧供給回路210から外部電源電圧EVCCを受信できる。

外部電圧供給回路210で発生したパワーノイズは、第1デカップリングキャパシター123によって除去又は最小化される。また、IVC231で発生したパワーノイズは第2デカップリングキャパシター121によって除去又は最小化される。

【0037】

図5は、図3の半導体チップパッケージで、デカップリングキャパシターと集積回路チップ内の回路との間の電気的接続を示す例示回路図である。

図5を参照すると、外部電圧供給回路210は、外部電源から外部電源電圧EVCCを受信する。したがって、外部電圧供給回路210の入力に接続されたパッド236、238の間には外部電源電圧EVCCが現れる。

【0038】

内部電圧発生器(IVC)231は、外部電圧供給回路210の外部電源電圧をラインL1から受けて内部回路250で使用される供給電圧を発生する。

内部電圧発生器231の出力に接続されたパッド232、234の間には内部電源電圧IVCCが現れる。内部電源電圧IVCCは、周辺内部電源電圧VINTPやアレイ内部電源電圧VINTAであり得る。

【0039】

外部電圧供給回路210で発生するパワーノイズは、パッド236、238と電気的に接続され搭載基板100に形成された第1デカップリングキャパシター123によって除去又は最小化される。

また、内部電圧発生器231で発生するパワーノイズは、パッド232、234と電気的に接続され搭載基板100に形成された第2デカップリングキャパシター121によって除去又は最小化される。

第1、第2デカップリングキャパシター123、121は、集積回路チップ200の内部に形成されること無く、搭載基板100に形成されるので、ノイズ除去性能が相対的に優れる。

【0040】

図6は、図5のデカップリングキャパシターの等価回路図である。

図6を参照すると、負荷端P1、P2の間に並列に接続されたデカップリングキャパシターDCは、第2デカップリングキャパシター121に対応する。

外部電源と負荷端P1との間に接続された抵抗R1、R2は各々寄生抵抗又は必要時に挿入される抵抗であり得る。

図6のような構造に形成されるRCフィルターはパワーノイズを除去する。

【0041】

図7は、図5の中のIVCを具体的に例示する回路図である。

図7を参照すると、電流ミラータイプで構成された典型的なIVCの例が示す。

IVC231は、図7のようなバックゲート−ソース接続形態を有するP型MOSトランジスタMP1、MP2、MP3、N型MOSトランジスタMN1、MN2、及び抵抗R1で具現され得る。

【0042】

図7で、ターゲット電圧になる基準電圧VrefがN型MOSトランジスタMN1のゲートへ印加され、外部電源電圧EVCCがP型MOSトランジスタMP1、MP2、MP3のソースへ印加されれば、P型MOSトランジスタMP3のドレインには内部電源電圧IVCCが図8のグラフ波形のように発生する。

ここで、内部電源電圧IVCCは外部電源電圧EVCCの電圧レベルより小さいか、或いは同一であり得る。図7のIVCは、例示的具現に過ぎず、他の種々のタイプの内部電圧発生回路が本発明の実施形態で使用され得る。

【0043】

図8は、図7での電圧の波形を示すグラフであって、横軸は時間を、縦軸は電圧を示す。

IVC231で発生する内部電源電圧VINTのパワーノイズは、搭載基板100に形成されたデカップリングキャパシター121によって除去又は最小化される。

したがって、IVC231で発生する内部電源電圧VINTは、安定化された状態で内部回路250へ供給される。

【0044】

図9は、本発明が例示的に適用される揮発性メモリチップのパッケージ構造を示した概略的な断面図であり、図10は本発明が例示的に適用される不揮発性メモリチップのパッケージ構造を示した概略的な断面図である。

【0045】

先ず、図9を参照すると、半導体チップパッケージに属することで、揮発性メモリチップパッケージ500は、搭載基板100、DRAM等のような揮発性メモリ(Volatile Memory)チップ200、及び保護層300を含む。

搭載基板100に形成されたデカップリングキャパシター121は、揮発性メモリチップ200の内部に配置された電圧発生回路のパワーノイズを効果的に除去又は減少させる。

これによって、揮発性メモリチップ200の動作信頼性が改善され得る。

【0046】

揮発性メモリチップパッケージ500は、PoP(Package on Package)、Ball grid arrays(BGAs)、Chip scale packages(CSPs)、Plastic Leaded Chip Carrier(PLCC)、Plastic Dual In−Line Package(PDIP)、Die in Waffle Pack、Die in Wafer Form、Chip On Board(COB)、Ceramic Dual In−Line Package(CERDIP)、Plastic Metric Quad Flat Pack(MQFP)、Thin Quad Flatpack(TQFP)、Small Outline(SOIC)、Shrink Small Outline Package(SSOP)、Thin Small Outline(TSOP)、Thin Quad Flatpack(TQFP)、System In Package(SIP)、Multi Chip Package(MCP)、Wafer−level Fabricated Package(WFP)、Wafer−Level Processed Stack Package(WSP)等のパッケージであり得る。

【0047】

図10を参照すると、半導体チップパッケージに属することで、不揮発性メモリチップパッケージ510は、搭載基板100、不揮発性メモリ(Non−Volatile Memory)チップ220、及び保護層300を含む。

【0048】

搭載基板100に形成されたデカップリングキャパシター121、123は不揮発性メモリチップ220の内部に配置された電圧発生回路のパワーノイズを効果的に除去又は減少させる。

これによって、不揮発性メモリチップ220の動作信頼性が改善され得る。

【0049】

不揮発性メモリは、例えば、EEPROM(Electrically Erasable Programmable Read−Only Memory)、フラッシュメモリ(flash memory)、MRAM(Magnetoresistive RAM)、スピン伝達トルクMRAM(Spin−Transfer Torque MRAM)、Conductive bridging RAM(CBRAM)、FeRAM(Ferroelectric RAM)、OUM(Ovonic Unified Memory)と称されるPRAM(Phase change RAM)、抵抗メモリ(Resistive RAM:RRAM(登録商標)又はReRAM)、ナノチューブRRAM(登録商標)(Nanotube RRAM(登録商標))、ポリマーRAM(Polymer RAM:PoRAM)、ナノ浮遊ゲートメモリ(Nano Floating Gate Memory:NFGM)、ホログラフィックメモリ(holographic memory)、分子電子メモリ素子(Molecular Electronics Memory Device)、又は絶縁抵抗変化メモリ(Insulator Resistance Change Memory)であり得る。

【0050】

このように、集積回路チップの外部にデカップリングキャパシター(Decoupling Capacitor)を接続する場合、パワーノイズと電圧降下により効率的な対処が可能になる。

【0051】

以上、図面と明細書とを通じて最良の実施形態が開示したが、本技術分野の通常の知識を有する者であれば、これから多様な変形及び均等な他の実施形態が可能である点を理解できる。例えば、事案が異なる場合に本発明の技術的思想を逸脱しなくて集積回路チップのパッケージ構成、デカップリングキャパシターと電圧発生回路との間の電気的連結等を多様な形態に変更及び変形できる。

【符号の説明】

【0052】

100 搭載基板

120 ノイズ除去器

121 デカップリング素子(キャパシター)(第2デカップリングキャパシター)

123 第1デカップリングキャパシター

200 集積回路チップ(揮発性メモリチップ)

210 外部電圧供給回路

220 不揮発性メモリチップ

230 電圧発生回路

231 IVC、内部電圧発生器

232、234、236、238 接続ターミナル(パッド)

241 データ出力バッファ

250 内部回路

252 周辺回路

254 セルアレイ回路

300 絶縁領域(保護層)

500 揮発性メモリチップパッケージ

510 不揮発性メモリチップパッケージ

【技術分野】

【0001】

本発明は、集積回路チップのパワーノイズ除去に関し、より詳細には、外部電源電圧を受信して内部回路に必要とされる電圧を提供する回路でのパワーノイズを減少させるための半導体チップパッケージに関する。

【背景技術】

【0002】

ダイナミックランダムアクセスメモリ(以下、DRAM)等のような半導体メモリを含む集積回路チップは、パッケージング(packaging)された後に外部から電源を受信して動作する。

外部電源電圧供給ターミナルを通じて印加される外部電源電圧(External Voltage)は、外部環境や集積回路チップの動作の時に発生するノイズ等によって電圧レベルが変動され得る。

しかし、外部電源電圧のレベルは必要によって、自由に変更することは難しい。

【0003】

多数の集積回路チップには、外部電源電圧をチップ内部で必要とされる電源電圧のレベルに変換するためのIVC(Internal Voltage Converter)等のような電圧発生回路が具備されている。

IVCは、半導体素子の動作に適合する電圧を比較的自由に生成できる。IVCは、ネガティブフィードバック(Negative Feedback)を通じて外部電源電圧が変化してもこれに関わらず、内部電圧を安定的に維持することができる。IVCを活用すれば、半導体素子の動作パラメーター(Parameter)が便利に制御され得る。

【0004】

従って、IVCのような電圧発生回路は、多様な電源電圧を有する製品に対応が可能であり、消費電力の減少にも役に立つ。

しかしながら、電圧発生回路に接続された内部回路の高速化にしたがって発生するパワーノイズに対して脆弱な面があるという問題がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】韓国特許出願公開第10−2004−0120174号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は上記従来の集積回路チップにおける問題点に鑑みてなされたものであって、本発明の目的は、集積回路チップ内の電圧発生回路で発生されるパワーノイズを除去又は最小化できる半導体チップパッケージを提供することにある。

また、本発明の他の目的は、半導体メモリ装置の内部電圧発生回路で発生されるパワーノイズを除去又は最小化できる半導体チップパッケージを提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するためになされた本発明による半導体チップパッケージは、外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記電圧発生回路の前記供給電圧の出力ノードに接続された接続ターミナルとを含む集積回路チップと、前記供給電圧に対するパワーノイズを減少させるために前記接続ターミナルに電気的に接続されたノイズ除去器と、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有することを特徴とする。

【0008】

前記電圧発生回路は、周辺回路やセルアレイに必要とされる前記供給電圧を発生する内部電圧コンバーターであることが好ましい。

前記電圧発生回路は、前記外部電源電圧以上の高電圧を発生する高電圧発生回路であることが好ましい。

前記電圧発生回路は、バックバイアス電圧を発生するバックバイアス電圧発生回路であることが好ましい。

前記ノイズ除去器は、前記パワーノイズを除去するためのデカップリング素子であることが好ましい。

前記デカップリング素子は、前記搭載基板の上部に形成されるデカップリングキャパシターであることが好ましい。

前記デカップリング素子は、前記搭載基板の内部に形成されるデカップリングキャパシターであることが好ましい。

前記デカップリングキャパシターは、ワイヤボンディングを使用して前記接続ターミナルと接続されることが好ましい。

【0009】

また、上記目的を達成するためになされた本発明による半導体チップパッケージは、外部電源電圧を受信して分配する外部電圧供給回路と、前記外部電圧供給回路から分配された外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記外部電圧供給回路の入力ノードに接続された第1接続ターミナルと前記電圧発生回路の前記供給電圧の出力ノードに接続された第2接続ターミナルとを具備する集積回路チップと、前記外部電源電圧に対するパワーノイズ及び前記供給電圧に対するパワーノイズを減少させるために前記第1及び第2接続ターミナルに各々独立的に接続された第1及び第2ノイズ除去器を具備し、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有することを特徴とする。

【0010】

前記電圧発生回路は、半導体メモリの周辺回路やメモリセルアレイに必要とされる内部電圧を発生する内部電圧コンバーターであることが好ましい。

【発明の効果】

【0011】

本発明に係る半導体チップパッケージによれば、集積回路チップ内の電圧発生回路で発生するパワーノイズが搭載基板に形成されるノイズ除去器によって効率的に除去又は最小化されるという効果がある。

したがって、DRAM等のような半導体メモリ装置の内部電圧コンバーターに本発明が適用される場合に内部回路はより安定的な内部電圧を受信できる。したがって、半導体メモリ装置のデータアクセス動作に対する信頼性が改善されるという効果がある。

【図面の簡単な説明】

【0012】

【図1】本発明の実施形態による半導体チップパッケージの回路接続ブロック図である。

【図2】図1の変形実施形態による回路接続ブロック図である。

【図3】図1の半導体チップパッケージの例示断面構造を示す断面図である。

【図4】図3の半導体チップパッケージの例示的な機能回路を示すブロック図である。

【図5】図3の半導体チップパッケージでデカップリングキャパシターと集積回路チップ内の回路との間の電気的接続を示す例示回路図である。

【図6】図5のデカップリングキャパシターの等価回路図である。

【図7】図5の中のIVCを具体的に例示する回路図である。

【図8】図7での電圧の波形を示すグラフである。

【図9】本発明が例示的に適用される揮発性メモリチップのパッケージ構造を示した概略的な断面図である。

【図10】本発明が例示的に適用される不揮発性メモリチップのパッケージ構造を示した概略的な断面図である。

【発明を実施するための形態】

【0013】

次に、本発明に係る半導体チップパッケージを実施するための形態の具体例を図面を参照しながら説明する。

【0014】

上述したような本発明の目的、他の目的、特徴、及び長所は添付した図面と関連した以下の望ましい実施形態を通じて容易に理解できる。しかし、本発明はここで説明される実施形態に限定されなく、他の形態に具体化できる。むしろ、ここで紹介される実施形態は、理解を容易に提供する意図以外には他の意図が無く、開示された内容がより徹底であり、完全になるように、そして当業者に本発明の思想が十分に伝達されるようにするために提供するものである。

【0015】

本明細書で、いずれかの素子又はラインが対象素子ブロックに接続されると言及された場合にそれは直接的な接続されるのみでなく、いずれかの他の素子を通じて対象素子ブロックに間接的に接続された意味までも含む。

また、できるだけ、各図面で提示された同一又は類似な参照符号は同一又は類似な構成要素を示す。一部図面において、素子及びラインの連結関係は技術的内容の効果的な説明をために示したのみであり、他の素子や回路ブロックがさらに具備され得る。

ここに説明され、例示される各実施形態はそれの相補的な実施形態も包含でき、IVC回路及び半導体パッケージに基本的動作と構造とに関する詳細は本発明の要旨を曖昧にしないようにするために詳細に説明されなかったことを留意しなければならない。

【0016】

図1は、本発明の実施形態による半導体チップパッケージの回路接続ブロック図である。

図1を参照すると、半導体チップパッケージは、集積回路チップ200と搭載基板100と含む。

【0017】

集積回路チップ200は、外部電源電圧を受信して内部回路250に使用される供給電圧を発生する電圧発生回路230と、電圧発生回路230の供給電圧の出力ノードND1に接続された接続ターミナル232を具備する。

【0018】

搭載基板100は、供給電圧に対するパワーノイズを減少させるために接続ターミナル232に電気的に接続されたノイズ除去器120を具備し、半導体チップパッケージとして集積回路チップをパッケージングするために集積回路チップ200を搭載する。

集積回路チップ200がDRAM等の半導体メモリ装置である場合にメモリセルアレイ、コア回路、及び周辺回路を包含し得る。

【0019】

電圧発生回路230は、周辺回路やメモリセルアレイに必要とされる内部電圧IVCCを発生する内部電圧コンバーターIVC(Internal Voltage Converter)、外部電源電圧以上の高電圧VPPを発生する高電圧発生回路、又はバック(back)バイアス電圧を発生するバックバイアス電圧発生回路であり得る。

【0020】

搭載基板100に配置されたノイズ除去器120は、パワーノイズを除去するためのデカップリング素子としてデカップリングキャパシターであり得る。

デカップリング素子は、搭載基板100の上部、内部、下部、又は側部に形成され得る。

デカップリングキャパシターは、接続ターミナル232にワイヤボンディングを通じて接続されるか、或いはフリップチップボンディングを通じて接続され得る。

【0021】

デカップリングキャパシターは、SMT実装又は埋め込み型(Embedded)実装方式によって搭載基板100搭載され得る。

ここで、デカップリング素子はフィルムタイプキャパシター(Film Type Capacitor)やシリコンキャパシター(Silicon Capacitor)であり得る。

【0022】

図1で、電圧発生回路230がラインL1を通じて外部電源電圧EVCCを受信して内部回路250で使用される供給電圧(例:IVCC)を出力ラインL10を通じて出力すれば、内部回路250は出力ノードND1に接続されたラインL11を通じて内部電源電圧を受信する。

電圧発生回路230の動作や内部回路250の高速動作によって負荷が変動されれば、パワーノイズが発生し、出力ノードND1は発生したパワーノイズに影響を受ける。

【0023】

パワーノイズは、出力ノードND1にラインL12を通じて接続されたパッド等の接続ターミナル232にも現れる。

本発明の実施形態では相互接続ラインI2を通じて接続ターミナル232とノイズ除去器120とを電気的に接続することによって電圧発生回路230のパワーノイズを除去又は最小化する。

一方、ラインL13を通じて電圧発生回路230に接続された接続ターミナル234は接地パッドとして機能し、ノイズ除去器120とは接地用相互接続ラインI4を通じて接続される。

【0024】

ノイズ除去器120は、集積回路チップ200の外部に位置する搭載基板100に形成される。

したがって、集積回路チップ200の内部に配置されるノイズ除去器に比べて容量を相対的にさらに大きくすることができるので、ノイズ除去性能が著しく優れる。

【0025】

具体的に、ノイズ除去器としてデカップリングキャパシター(Decoupling Capacitor)は、システム基板、半導体パッケージの搭載基板、又は集積回路チップの内部に設置され得る。デカップリングキャパシターが集積回路チップの内部に位置される場合に効率は相対的に良いが、チップの制限された面積でよってキャパシターの容量は比較的低い。したがって、チップパッケージの搭載基板100にデカップリングキャパシターを形成する方式が利用される。

【0026】

このように、集積回路チップ内の電圧発生回路230で発生するパワーノイズが搭載基板100に形成されるノイズ除去器120によって効率的に除去又は最小化される。

したがって、DRAM等のような半導体メモリ装置の内部電圧コンバーターIVCに図1のスキームが適用される場合に電圧発生回路230の電源及びグラウンドの変動(Fluctuation)が抑制されて内部回路250はノイズ除去された、さらに安定的な内部電圧を受信できる。したがって、DRAM等のような半導体メモリ装置のパワーノイズの免疫性(Immunity)が向上されてデータアクセス動作に対する信頼性が改善される。

【0027】

図2は、図1の変形実施形態による回路接続ブロック図である。

図2を参照すると、図1のノイズ除去器に対応するデカップリング素子121が絶縁領域300に形成される。

絶縁領域300は、集積回路チップ200の上部に形成される領域であり得る。

しかし、異なる場合には絶縁領域300は図1の搭載基板100に形成された領域であり得る。

【0028】

IVC231がラインL1を通じて外部電源電圧EVCCを受信して内部回路250に使用される供給電圧(例:IVCC)を出力ラインL10を通じて出力すれば、内部回路250は出力ノードND1に接続されたラインL11を通じて内部電源電圧を受信する。

IVC231や内部回路250によってパワーノイズが発生すれば、出力ノードND1は発生したパワーノイズの影響を受ける。

【0029】

図1と類似して、パワーノイズは、出力ノードND1にラインL12を通じて接続されたパッド等の接続ターミナル232にも現れる。

本発明の実施形態では相互接続ラインI2を通じて接続ターミナル232とデカップリング素子121とを電気的に接続することによって、IVC231のパワーノイズを除去又は最小化する。一方、IVC231に接続された接続ターミナル234は接地パッドとして機能し、デカップリング素子121とは接地用相互接続ラインI4を通じて接続される。

【0030】

図2の半導体チップパッケージの構造でも集積回路チップ内のIVC231又は高電圧発生器で発生するパワーノイズが、絶縁領域250に形成されるデカップリング素子121によって効率的に除去又は最小化される。

【0031】

図3は、図1の半導体チップパッケージの例示断面構造を示す断面図である。

図3を参照すると、集積回路チップ200は搭載基板100の上部に搭載される。

ノイズ除去をためのデカップリング素子C1、C2は搭載基板100の上部に形成されて集積回路チップ200内の電圧発生回路230に接続され得る。

デカップリング素子C3、C4は搭載基板100の下部に形成されて集積回路チップ200内の電圧発生回路230に接続され得る。

デカップリング素子C5、C6は搭載基板100の内部に形成されて集積回路チップ200内の電圧発生回路230に接続され得る。

デカップリング素子C7、C8は搭載基板100の側部に形成されて集積回路チップ200内の電圧発生回路230に接続され得る。

【0032】

半導体チップパッケージは、ボードの上でコントローラやマイクロプロセッサー等のような外部装置と電気的に接続するために搭載基板100に形成された接触バンパー(B1〜B6)を有することができる。

図3で、集積回路チップ200の内部で発生するパワーノイズは、搭載基板100に形成されるデカップリング素子(C1〜C8)の中で少なくとも1つによって効率的に除去又は最小化される。

【0033】

図4は、図3の半導体チップパッケージの例示的な機能回路を示すブロック図である。

図4を参照すると、ノイズ除去器としての第1デカップリングキャパシター123と第2デカップリングキャパシター121とは搭載基板100に形成される。

外部電圧供給回路(EVSC)210、IVC231、データ出力バッファ241、周辺回路252、及びセルアレイ回路254は集積回路チップ200に形成される。

【0034】

外部電圧供給回路210は、外部電源電圧EVCCを受信して分配する。

IVC231は、外部電圧供給回路210から分配された外部電源電圧を受信して内部回路に使用される供給電圧を発生する。

【0035】

周辺回路252とセルアレイ回路254とは、内部回路250に属する回路である。

周辺回路252は、IVC231から周辺内部電源電圧VINTPを受信する。

セルアレイ回路254は、IVC231からアレイ内部電源電圧VINTAを受信する。

【0036】

データ出力バッファ241は、メモリセルに格納されたデータを外部へ出力するためのバッファとして外部電圧供給回路210から外部電源電圧EVCCを受信できる。

外部電圧供給回路210で発生したパワーノイズは、第1デカップリングキャパシター123によって除去又は最小化される。また、IVC231で発生したパワーノイズは第2デカップリングキャパシター121によって除去又は最小化される。

【0037】

図5は、図3の半導体チップパッケージで、デカップリングキャパシターと集積回路チップ内の回路との間の電気的接続を示す例示回路図である。

図5を参照すると、外部電圧供給回路210は、外部電源から外部電源電圧EVCCを受信する。したがって、外部電圧供給回路210の入力に接続されたパッド236、238の間には外部電源電圧EVCCが現れる。

【0038】

内部電圧発生器(IVC)231は、外部電圧供給回路210の外部電源電圧をラインL1から受けて内部回路250で使用される供給電圧を発生する。

内部電圧発生器231の出力に接続されたパッド232、234の間には内部電源電圧IVCCが現れる。内部電源電圧IVCCは、周辺内部電源電圧VINTPやアレイ内部電源電圧VINTAであり得る。

【0039】

外部電圧供給回路210で発生するパワーノイズは、パッド236、238と電気的に接続され搭載基板100に形成された第1デカップリングキャパシター123によって除去又は最小化される。

また、内部電圧発生器231で発生するパワーノイズは、パッド232、234と電気的に接続され搭載基板100に形成された第2デカップリングキャパシター121によって除去又は最小化される。

第1、第2デカップリングキャパシター123、121は、集積回路チップ200の内部に形成されること無く、搭載基板100に形成されるので、ノイズ除去性能が相対的に優れる。

【0040】

図6は、図5のデカップリングキャパシターの等価回路図である。

図6を参照すると、負荷端P1、P2の間に並列に接続されたデカップリングキャパシターDCは、第2デカップリングキャパシター121に対応する。

外部電源と負荷端P1との間に接続された抵抗R1、R2は各々寄生抵抗又は必要時に挿入される抵抗であり得る。

図6のような構造に形成されるRCフィルターはパワーノイズを除去する。

【0041】

図7は、図5の中のIVCを具体的に例示する回路図である。

図7を参照すると、電流ミラータイプで構成された典型的なIVCの例が示す。

IVC231は、図7のようなバックゲート−ソース接続形態を有するP型MOSトランジスタMP1、MP2、MP3、N型MOSトランジスタMN1、MN2、及び抵抗R1で具現され得る。

【0042】

図7で、ターゲット電圧になる基準電圧VrefがN型MOSトランジスタMN1のゲートへ印加され、外部電源電圧EVCCがP型MOSトランジスタMP1、MP2、MP3のソースへ印加されれば、P型MOSトランジスタMP3のドレインには内部電源電圧IVCCが図8のグラフ波形のように発生する。

ここで、内部電源電圧IVCCは外部電源電圧EVCCの電圧レベルより小さいか、或いは同一であり得る。図7のIVCは、例示的具現に過ぎず、他の種々のタイプの内部電圧発生回路が本発明の実施形態で使用され得る。

【0043】

図8は、図7での電圧の波形を示すグラフであって、横軸は時間を、縦軸は電圧を示す。

IVC231で発生する内部電源電圧VINTのパワーノイズは、搭載基板100に形成されたデカップリングキャパシター121によって除去又は最小化される。

したがって、IVC231で発生する内部電源電圧VINTは、安定化された状態で内部回路250へ供給される。

【0044】

図9は、本発明が例示的に適用される揮発性メモリチップのパッケージ構造を示した概略的な断面図であり、図10は本発明が例示的に適用される不揮発性メモリチップのパッケージ構造を示した概略的な断面図である。

【0045】

先ず、図9を参照すると、半導体チップパッケージに属することで、揮発性メモリチップパッケージ500は、搭載基板100、DRAM等のような揮発性メモリ(Volatile Memory)チップ200、及び保護層300を含む。

搭載基板100に形成されたデカップリングキャパシター121は、揮発性メモリチップ200の内部に配置された電圧発生回路のパワーノイズを効果的に除去又は減少させる。

これによって、揮発性メモリチップ200の動作信頼性が改善され得る。

【0046】

揮発性メモリチップパッケージ500は、PoP(Package on Package)、Ball grid arrays(BGAs)、Chip scale packages(CSPs)、Plastic Leaded Chip Carrier(PLCC)、Plastic Dual In−Line Package(PDIP)、Die in Waffle Pack、Die in Wafer Form、Chip On Board(COB)、Ceramic Dual In−Line Package(CERDIP)、Plastic Metric Quad Flat Pack(MQFP)、Thin Quad Flatpack(TQFP)、Small Outline(SOIC)、Shrink Small Outline Package(SSOP)、Thin Small Outline(TSOP)、Thin Quad Flatpack(TQFP)、System In Package(SIP)、Multi Chip Package(MCP)、Wafer−level Fabricated Package(WFP)、Wafer−Level Processed Stack Package(WSP)等のパッケージであり得る。

【0047】

図10を参照すると、半導体チップパッケージに属することで、不揮発性メモリチップパッケージ510は、搭載基板100、不揮発性メモリ(Non−Volatile Memory)チップ220、及び保護層300を含む。

【0048】

搭載基板100に形成されたデカップリングキャパシター121、123は不揮発性メモリチップ220の内部に配置された電圧発生回路のパワーノイズを効果的に除去又は減少させる。

これによって、不揮発性メモリチップ220の動作信頼性が改善され得る。

【0049】

不揮発性メモリは、例えば、EEPROM(Electrically Erasable Programmable Read−Only Memory)、フラッシュメモリ(flash memory)、MRAM(Magnetoresistive RAM)、スピン伝達トルクMRAM(Spin−Transfer Torque MRAM)、Conductive bridging RAM(CBRAM)、FeRAM(Ferroelectric RAM)、OUM(Ovonic Unified Memory)と称されるPRAM(Phase change RAM)、抵抗メモリ(Resistive RAM:RRAM(登録商標)又はReRAM)、ナノチューブRRAM(登録商標)(Nanotube RRAM(登録商標))、ポリマーRAM(Polymer RAM:PoRAM)、ナノ浮遊ゲートメモリ(Nano Floating Gate Memory:NFGM)、ホログラフィックメモリ(holographic memory)、分子電子メモリ素子(Molecular Electronics Memory Device)、又は絶縁抵抗変化メモリ(Insulator Resistance Change Memory)であり得る。

【0050】

このように、集積回路チップの外部にデカップリングキャパシター(Decoupling Capacitor)を接続する場合、パワーノイズと電圧降下により効率的な対処が可能になる。

【0051】

以上、図面と明細書とを通じて最良の実施形態が開示したが、本技術分野の通常の知識を有する者であれば、これから多様な変形及び均等な他の実施形態が可能である点を理解できる。例えば、事案が異なる場合に本発明の技術的思想を逸脱しなくて集積回路チップのパッケージ構成、デカップリングキャパシターと電圧発生回路との間の電気的連結等を多様な形態に変更及び変形できる。

【符号の説明】

【0052】

100 搭載基板

120 ノイズ除去器

121 デカップリング素子(キャパシター)(第2デカップリングキャパシター)

123 第1デカップリングキャパシター

200 集積回路チップ(揮発性メモリチップ)

210 外部電圧供給回路

220 不揮発性メモリチップ

230 電圧発生回路

231 IVC、内部電圧発生器

232、234、236、238 接続ターミナル(パッド)

241 データ出力バッファ

250 内部回路

252 周辺回路

254 セルアレイ回路

300 絶縁領域(保護層)

500 揮発性メモリチップパッケージ

510 不揮発性メモリチップパッケージ

【特許請求の範囲】

【請求項1】

外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記電圧発生回路の前記供給電圧の出力ノードに接続された接続ターミナルとを含む集積回路チップと、

前記供給電圧に対するパワーノイズを減少させるために前記接続ターミナルに電気的に接続されたノイズ除去器と、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有することを特徴とする半導体チップパッケージ。

【請求項2】

前記電圧発生回路は、周辺回路やセルアレイに必要とされる前記供給電圧を発生する内部電圧コンバーターであることを特徴とする請求項1に記載の半導体チップパッケージ。

【請求項3】

前記電圧発生回路は、前記外部電源電圧以上の高電圧を発生する高電圧発生回路であることを特徴とする請求項1に記載の半導体チップパッケージ。

【請求項4】

前記電圧発生回路は、バックバイアス電圧を発生するバックバイアス電圧発生回路であることを特徴とする請求項1に記載の半導体チップパッケージ。

【請求項5】

前記ノイズ除去器は、前記パワーノイズを除去するためのデカップリング素子であることを特徴とする請求項1に記載の半導体チップパッケージ。

【請求項6】

前記デカップリング素子は、前記搭載基板の上部に形成されるデカップリングキャパシターであることを特徴とする請求項5に記載の半導体チップパッケージ。

【請求項7】

前記デカップリング素子は、前記搭載基板の内部に形成されるデカップリングキャパシターであることを特徴とする請求項5に記載の半導体チップパッケージ。

【請求項8】

前記デカップリングキャパシターは、ワイヤボンディングを使用して前記接続ターミナルと接続されることを特徴とする請求項6に記載の半導体チップパッケージ。

【請求項9】

外部電源電圧を受信して分配する外部電圧供給回路と、前記外部電圧供給回路から分配された外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記外部電圧供給回路の入力ノードに接続された第1接続ターミナルと前記電圧発生回路の前記供給電圧の出力ノードに接続された第2接続ターミナルとを具備する集積回路チップと、

前記外部電源電圧に対するパワーノイズ及び前記供給電圧に対するパワーノイズを減少させるために前記第1及び第2接続ターミナルに各々独立的に接続された第1及び第2ノイズ除去器を具備し、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有することを特徴とする半導体チップパッケージ。

【請求項10】

前記電圧発生回路は、半導体メモリの周辺回路やメモリセルアレイに必要とされる内部電圧を発生する内部電圧コンバーターであることを特徴とする請求項9に記載の半導体チップパッケージ。

【請求項1】

外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記電圧発生回路の前記供給電圧の出力ノードに接続された接続ターミナルとを含む集積回路チップと、

前記供給電圧に対するパワーノイズを減少させるために前記接続ターミナルに電気的に接続されたノイズ除去器と、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有することを特徴とする半導体チップパッケージ。

【請求項2】

前記電圧発生回路は、周辺回路やセルアレイに必要とされる前記供給電圧を発生する内部電圧コンバーターであることを特徴とする請求項1に記載の半導体チップパッケージ。

【請求項3】

前記電圧発生回路は、前記外部電源電圧以上の高電圧を発生する高電圧発生回路であることを特徴とする請求項1に記載の半導体チップパッケージ。

【請求項4】

前記電圧発生回路は、バックバイアス電圧を発生するバックバイアス電圧発生回路であることを特徴とする請求項1に記載の半導体チップパッケージ。

【請求項5】

前記ノイズ除去器は、前記パワーノイズを除去するためのデカップリング素子であることを特徴とする請求項1に記載の半導体チップパッケージ。

【請求項6】

前記デカップリング素子は、前記搭載基板の上部に形成されるデカップリングキャパシターであることを特徴とする請求項5に記載の半導体チップパッケージ。

【請求項7】

前記デカップリング素子は、前記搭載基板の内部に形成されるデカップリングキャパシターであることを特徴とする請求項5に記載の半導体チップパッケージ。

【請求項8】

前記デカップリングキャパシターは、ワイヤボンディングを使用して前記接続ターミナルと接続されることを特徴とする請求項6に記載の半導体チップパッケージ。

【請求項9】

外部電源電圧を受信して分配する外部電圧供給回路と、前記外部電圧供給回路から分配された外部電源電圧を受信して内部回路に使用される供給電圧を発生する電圧発生回路と、前記外部電圧供給回路の入力ノードに接続された第1接続ターミナルと前記電圧発生回路の前記供給電圧の出力ノードに接続された第2接続ターミナルとを具備する集積回路チップと、

前記外部電源電圧に対するパワーノイズ及び前記供給電圧に対するパワーノイズを減少させるために前記第1及び第2接続ターミナルに各々独立的に接続された第1及び第2ノイズ除去器を具備し、半導体チップパッケージとして前記集積回路チップをパッケージングするために前記集積回路チップを搭載する搭載基板とを有することを特徴とする半導体チップパッケージ。

【請求項10】

前記電圧発生回路は、半導体メモリの周辺回路やメモリセルアレイに必要とされる内部電圧を発生する内部電圧コンバーターであることを特徴とする請求項9に記載の半導体チップパッケージ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−84339(P2013−84339A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2012−225051(P2012−225051)

【出願日】平成24年10月10日(2012.10.10)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成24年10月10日(2012.10.10)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

[ Back to top ]