半導体デバイス、画像処理装置

【課題】複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供すること。

【解決手段】送信側から受信側にデータをシリアル送信する半導体デバイス100であって、データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段301,302と、送信側と受信側に共通のクロック信号を提供するクロック信号提供手段103と、クロック信号に同期して同じデータを送信する複数の伝送路117と、受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段110と、遅延クロック信号に同期して伝送路を介して送信されたデータを取り込む複数の受信バッファ111と、コードを予め定められた規則に基づき検証して複数の受信バッファから1つの受信バッファを、複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段113、115と、を有する。

【解決手段】送信側から受信側にデータをシリアル送信する半導体デバイス100であって、データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段301,302と、送信側と受信側に共通のクロック信号を提供するクロック信号提供手段103と、クロック信号に同期して同じデータを送信する複数の伝送路117と、受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段110と、遅延クロック信号に同期して伝送路を介して送信されたデータを取り込む複数の受信バッファ111と、コードを予め定められた規則に基づき検証して複数の受信バッファから1つの受信バッファを、複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段113、115と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、シリアルデータを伝送する半導体デバイスに関する。

【背景技術】

【0002】

ASIC等のLSIデバイス間のデータ転送において、複数のシリアル伝送路上を伝達されるデータの同期をLSYNC信号を用いて取る方式が知られている。画像データのデータ転送にはよくLVDS(Low voltage differential signaling)が用いられ、LSYNC信号を用いて同期を取る技術が提案されている(例えば、特許文献1参照。)。

【0003】

特許文献1には、デバイス間I/Fの同期をとる目的で、シリアル伝送路上に流されるLSYNC信号を用いてタイミング同期を取る画像転送装置が開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に開示された画像転送装置は、比較的高価なLVDS I/Fを複数個、使用するためASICの実装上のコスト増となるという問題がある。また、LVDS I/Fによる信号レベルの同期にはトレーニング等の手順が必要となるため、こちらもコスト増をもたらす。

【0005】

本発明は、上記課題に鑑み、複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題に鑑み、本発明は、送信側と受信側がクロック信号により同期して送信側から受信側にデータをシリアル送信する半導体デバイスであって、データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段と、送信側と受信側に共通のクロック信号を提供するクロック信号提供手段と、クロック信号に同期して同じデータを送信する複数の伝送路と、受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段と、前記複数の遅延クロック信号に同期して、前記複数の伝送路を介して送信されたデータを取り込む複数の受信バッファと、前記コードを予め定められた規則に基づき検証して前記複数の受信バッファから1つの受信バッファを、前記複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段と、を有する。

【発明の効果】

【0007】

複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供することができる。

【図面の簡単な説明】

【0008】

【図1】画像処理装置のハードウェア構成図の一例である。

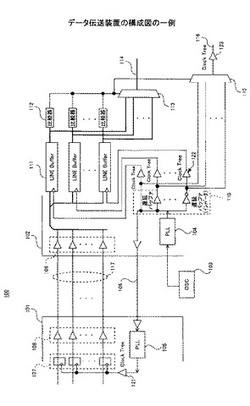

【図2】データ伝送装置の構成図の一例である。

【図3】データ伝送装置の動作を示すタイミングチャート図の一例である。

【図4】ラインバッファが正常に取り込めるものと、そうでないものの違いを説明する図の一例である。

【図5】画像データの転送時の同期信号等の一例を示す図である。

【図6】ライン同期信号、ラインゲート信号及び画像データ信号を1ライン転送分に着目して拡大した図の一例である。

【図7】ラインゲート信号を省略した信号のタイミングチャート図の1例である。

【図8】同期判定データが含まれた画像データの無効域を説明する図の一例である。

【図9】画像データ送信側デバイスにおいて無効域にインクリメントデータを伝送する構成例を示す図である。

【図10】各比較器がインクリメントパターンが正常か否かを判定する手順を示すフローチャート図の一例である。

【図11】画像データ送信側デバイスにおいて無効域にインクリメントデータを伝送する構成例を示す図の一例である。

【図12】画像データ送信側デバイスにおいて無効域にライン同期信号を埋め込む構成例を示す図の一例である。

【図13】ラインバッファが正常に画像データ信号を取り込んだか否かを判定する手順を示すフローチャート図の一例である。

【発明を実施するための形態】

【0009】

以下、本発明を実施するための形態について図面を参照しながら説明する。

図1は、画像処理装置200のハードウェア構成図の一例を示す。本実施形態のデータ伝送装置は、ASIC216と印刷部228や、撮像部227とASIC216の間の画像データの伝送を行う。ASIC216と印刷部228に着目した場合はASIC216が送信側で印刷部228が受信側になり、撮像部227とASIC216に着目した場合は撮像部227が送信側でASIC216が受信側になる。

【0010】

画像処理装置200の構成は公知なので簡単に説明する。画像処理装置200は、コントローラ230と、オペレーションパネル225と、ファクシミリコントロールユニット(FCU)226と、撮像部227及び印刷部228が有する。

【0011】

コントローラ230は、CPU214と、ASIC216と、NB(ノースブリッジ)215と、SB(サウスブリッジ)217と、MEM−P(システムメモリ)211と、MEM−C(ローカルメモリ)212と、HDD(ハードディスクドライブ)213と、メモリカードスロット223と、NIC(ネットワークインタフェースコントローラ)218と、USBデバイス219と、IEEE1394デバイス221と、セントロニクスデバイス222とを有する。

【0012】

CPU214は、種々の情報処理を実行するためのICであり、アプリケーションやプラットフォーム等をUNIX(登録商標)等のOSによりプロセス単位で並列的に実行する。ASIC216は、画像処理用のICである。ASIC216は、端末から受信した印刷データをレンダリングして文字、図形、背景などオブジェクト毎に適切なディザ処理を行うなどして印刷部228に送信する。また、ASIC216は、撮像部227が撮影した画像データに対し、写真や文字などに像域分離して、文字のエッジ強調、写真の階調補完等を行う。

【0013】

NB215は、CPU214とASIC216を接続するためのブリッジである。SB217は、NB215と周辺機器等を接続するためのブリッジである。ASIC216とNB215は、AGP(Accelerated Graphics Port)を介して接続されている。

【0014】

MEM−P211は、NB215に接続されたメモリである。MEM−C212は、ASIC216に接続されたメモリである。HDD213は、ASIC216に接続されたストレージであり、画像データ蓄積・文書データ蓄積・プログラム蓄積・フォントデータ蓄積・フォームデータ蓄積等を行うために使用される。

【0015】

メモリカードスロット223は、SB217に接続され、メモリカード224をセット(挿入)するために使用される。NIC218は、ネットワーク500等を介してMACアドレス等を使用したデータ通信を行うためのコントローラである。USBデバイス219は、USB規格に準拠したシリアルポートを提供するためのデバイスである。IEEE1394デバイス221は、IEEE1394規格に準拠したシリアルポートを提供するためのデバイスである。セントロニクスデバイス222は、セントロニクス仕様に準拠したパラレルポートを提供するためのデバイスである。NIC1218と、USBデバイス219と、IEEE1394デバイス221と、セントロニクスデバイス222と、PCI(Peripheral Component Interconect)バスを介してNB215とSB217に接続されている。

【0016】

オペレーションパネル225は、ユーザが機器100に入力を行うためのハードウェア(操作部)であると共に、画像処理装置200がオペレータに可視情報を提供するためのハードウェア(表示部)である。オペレーションパネル225は、ASIC216に接続されている。FCU226と、撮像部227と、印刷部228は、PCIバスを介してASIC216に接続されており、本実施形態のデータ伝送装置は、例えば、PCIバスの代わりに適用されることが想定される。

【0017】

図2は、データ伝送装置100の構成図の一例を示す。データ伝送装置100は、画像データ送信側デバイス101及び画像データ受信側デバイス102を有する。画像データ送信側デバイス101は、画像データ出力用FF(フリップフロップ)107、画像データ送信用出力バッファ108、PLL105及びクロックツリー121を有する。

【0018】

画像データ送信側デバイス101及び画像データ受信側デバイス102は、上記のASIC216の他、FPGAのようなLSIデバイス、MPUやDSPなどであり、データを送信又は受信するICであればよい。画像データ送信側デバイス101は画像データの送信元デバイスで、画像データ受信側デバイス102は画像データの受信先デバイスである。

【0019】

画像データ受信側デバイス102は、画像データ受信用入力バッファ109、複数のラインバッファ111、それぞれのラインバッファ111に接続された複数の比較器112、セレクタ114、PLL104、遅延バッファ110、クロックツリー122、及び、セレクタ115を有する。なお、PLL104にはOSC103が接続されている。

【0020】

画像データ送信側デバイス101のPLL105の出力側はクロックツリー121と接続され、クロックツリー121は複数の画像データ出力用FF107とそれぞれ接続されている。また、各画像データ出力用FF107はそれぞれ各画像データ送信用出力バッファ108と接続されている。

【0021】

画像データ受信用入力バッファ109は、データ伝送路117毎に画像データ送信用出力バッファ108と接続され、複数のラインバッファ111はデータ伝送路117毎に設けられている。セレクタ113の入力側には、1対のラインバッファ111と比較器112の間からそれぞれデータ線が接続され、出力側は受信画像データ出力線114が接続されている。また、各比較器112から2つのセレクタ113、115にセレクタ信号線がそれぞれ接続されている。

【0022】

PLL104は、データ伝送路117と同じ数の遅延バッファ110に接続され、各遅延バッファ110はそれぞれ対応するクロックツリー122と接続されると共に、セレクタ115の入力側に接続される。クロックツリー122はそれぞれラインバッファ111に接続される。セレクタ115の出力側にはクロックツリー123と配信信号線116が接続されている。

【0023】

画像データ出力用FF107は、PLL105からのクロックに同期して画像データを画像データ送信用出力バッファ108に出力する。画像データ送信用出力バッファ108は、画像データを一時的に記憶するバッファである。

【0024】

画像データ受信用入力バッファ109は画像データを一時的に記憶するバッファである。ラインバッファ111はデータ伝送経路117毎に受信した画像データを取り込む。ラインバッファ111が取り込む画像データは、1ライン分の場合も、1ライン分よりも少ない又は大きい場合もある。比較器112は、ラインバッファ111が受信した画像データに含まれる特定のコード(以下、同期判定コードという)を抽出して、正常に画像データを受信するラインバッファ111を選択する。

【0025】

セレクタ113は、比較器112の選択結果を用いて、複数のラインバッファ111の出力から1つの画像データを選択する。遅延バッファ110は、PLL104から供給されるクロック信号のクロック位相をずらす(遅延させる)。セレクタ115は、各遅延バッファ110が出力するクロック信号から、比較器112の選択結果を用いて1つのクロック信号を選択する。

【0026】

本実施形態の画像データ送信側デバイス101及び画像データ受信側デバイス102は、OSC103が発振するクロックで同期通信を行う。OSC103が発信するクロックは、いったん画像データ受信側デバイス102内を通過して、クロック配信用信号線106を介して画像データ送信側デバイス101に入力される。

【0027】

OSC103が発信するクロックは画像データ送信側デバイス101及び画像データ受信側デバイス102に共通だが、配線長や経路の関係で2つのデバイス間で位相差が生じてると考えらえる。したがって、ある程度の位相差という意味では、OSC103が発信するクロックの配信経路は図示以外の構成でもよい。

【0028】

クロック配信用信号線106を介して画像データ送信側デバイス101に入力されたクロックは、PLL105を経由して、各画像データ出力用FF107に配信される。各画像データ出力用FF107にはクロックツリー121から共通にクロックが供給されるので、各画像データ出力用FF107は画像データ送信側デバイス101の同期回路となる。画像データ出力用FF107は画像データ送信側デバイス101から画像データを出力する最終段FF(フリップフロップ)で、配信されたクロックに同期して画像データを出力する。

【0029】

画像データ出力用FF107から出力された画像データは画像データ送信用出力バッファ108から、各データ伝送路117を介して画像データ受信側デバイス102に入力される。

【0030】

画像データ受信側デバイス102は、画像データ受信用入力バッファ109に画像データを一時的に記憶した後、ラインバッファ111に取り込む。ラインバッファ111はFFとして構成されており、各ラインバッファ111にはPLL104からクロックが供給されているので、各ラインバッファ111はクロックに同期して重複した画像データを同期受信する。

【0031】

本実施形態では、各ラインバッファ111に供給されるクロックの位相が、遅延バッファ110にて明示的にずらされている。すなわち、各遅延バッファ110は、位相が互いに異なるクロックを複数生成するよう、ラインバッファ111と同じ数だけ用意されている。このため、各ラインバッファ111が取り込む画像データは、同じものとそうでないものが生じる。遅延バッファ110が供給するクロックのうち、画像データ送信側デバイス101のクロックと同じ位相のクロックが供給されるラインバッファ111が、画像データ送信側デバイス101と"同期"したと称される。

【0032】

このラインバッファ111のバッファ段数(容量)は、同期したラインバッファ111を判定するのに必要なクロックサイクル数と、同期したラインバッファ111の画像データを処理する後段ブロックとのI/Fを確立するまでのサイクル数分を最低バッファ段数とする。例えば、比較器112でラインバッファ111の同期判定コードを検証するまでのクロック数と、そのクロック数で受信された画像データをセレクタ113,115が選択するためのクロック数とで計5クロック必要で、さらに、セレクタ115が出力するクロックに後段のブロック(不図示)の同期クロックが切り替わるまでに3クロック必要な場合は、ラインバッファ111のバッファ段数はそれぞれ5+3=8段分となる。また、仮に、後段のブロックの同期クロックの切り替えにクロックの消費が不要なら、ラインバッファ111のバッファ段数はそれぞれ5段分となる。このようにバッファ段数を設計することで、ラインバッファ111のバッファ段数を最小限にすることができる。

【0033】

1つのクロックで画像データの1段がラインバッファ111に取り込まれるが、図4で後述する、各クロックのタイミング(位相)による画像データの取りこぼしを考慮すると、最大でラインバッファ111のバッファ段数と同じ数のラインバッファ111があることが好ましい。したがって、ラインバッファ111の数は、最大ではラインバッファ111のバッファ段数と同じになる。

【0034】

画像データ受信側デバイス102は、セレクタ114が出力する同期化された画像データと、セレクタ115が出力する同期クロックを用いて、受信した画像データを処理する(例えば、後段に出力する)。

【0035】

図3は、データ伝送装置100の動作を示すタイミングチャート図の一例である。各信号の意味が以下のとおりである。

Send Clock :画像データ送信側デバイス内のクロック信号

Send Data :画像データ出力信号

Receive Clock:画像データ受信側デバイス内のクロック信号

Receive Data :画像データ入力信号

ClockA :画像データ受信側デバイス内で、遅延バッファにて一定量位相をずらしたクロック信号A

ClockB :画像データ受信側デバイス内で、遅延バッファにて一定量位相をずらしたクロック信号B

ClockC :画像データ受信側デバイス内で、遅延バッファにて一定量位相をずらしたクロック信号C

ClockX :画像データ受信側デバイス内で、遅延バッファにて一定量位相をずらしたクロック信号X

Receive DataA:ClockAでReceive Dataを取り込んだ画像データ

Receive DataB:ClockBでReceive Dataを取り込んだ画像データ

Receive DataC:ClockCでReceive Dataを取り込んだ画像データ

Receive DataX:ClockXでReceive Dataを取り込んだ画像データ

Send Dataは、画像データ送信側デバイス101が送信する画像データである。Send Clockは、例えばクロックツリー121の出力するクロックである。

【0036】

Send Dataは画像データ出力用FF107から画像データ受信側デバイス102に向けて出力され、ラインバッファ111によって受信される。このとき、画像データ受信側デバイス102のPLL104から出力される動作クロックがReceive Clockであり、配線遅延や信号間スキューによる遅延を受けた画像データがReceive Dataである。

【0037】

配線遅延や信号間スキューによる遅延がない理想的なデータ転送であれば、複数のReceive Dataは時間的にずれることなく画像データの変化点がクロックの立ち上がりエッジと一致する。しかしながら、図3に示すように、クロックの立ち上がりエッジは、複数のReceive Dataの画像データの変化点と前後したり重なっており、Receive Clockの立ち上がりエッジをトリガーにしてラインバッファ111がReceive Dataを取り込むと正常に受信することができない場合がある。

【0038】

そこで、各遅延バッファ110は、Receive Clockの位相を一定時間づつずらしたクロックClockA、ClockB、ClockC、・・・ClockXを生成する。それぞれのクロックClockA、ClockB、ClockC、・・・ClockXがラインバッファ111に供給され、ラインバッファ111がクロックClockA、ClockB、ClockC、・・・ClockXの立ち上がりエッジをトリガーにReceiveDataを取り込むことで、画像データReceive DataA〜Xがそれぞれ生成される。

【0039】

このため、ラインバッファ111が受信する画像データReceive DataA〜Xのうち、ClockA〜XとReceive Dataとのタイミングの関係で、ラインバッファ111が正常に取り込めたものと、そうでないものが生じる。

【0040】

図4は、ラインバッファ111が正常に取り込めるものと、そうでないものの違いを説明する図の一例である。図4は、Receive Dataの一部を表示したものであり、複数の「○」「×」で示す各タイミングは、各クロックの画像データ取り込みのタイミングを示す。ラインバッファ111がクロックにより正常に取り込めるタイミングを「○」で、正常に取り込めないタイミングを「×」でそれぞれ示している。図4に示すように、正常に取り込めるか否かは、Receive Dataと各クロックの立ち上がりエッジ(画像データ取り込みタイミング)の相対的な関係で決まる。

【0041】

複数のReceive DataA〜Xは最大でも1クロックの1周期分までは遅延しないという前提では、遅延バッファ110は、ClockA〜Xを1周期の範囲で分散させれば、ClockA〜Xのいずれかでラインバッファ111の1つは必ずReceive Dataを取り込めると考えられる。したがって、遅延バッファ110が位相をずらす量は、画像データを取り込む1クロックサイクルの周期を1/Xにした時間とする必要があることがわかる。

【0042】

例えばX(ラインバッファのバッファ段数)= 4で1クロックサイクルの周期が20nsの場合、遅延バッファ110がClockA〜Xの1つをずらすべき時間は「20÷4≒5ns」である。したがって、遅延バッファ110は、位相差0ns(源振クロック)、5ns、10ns、15nsの4つのクロックを生成する。4つのラインバッファ111は、それぞれのクロックで受信動作する。

【0043】

Xの値は、源振クロックの周波数や受信時のタイミング特性(正常に取り込めるタイミング幅)等を考慮して決定することで、ラインバッファ111のバッファ段数よりも小さくできる。Xを適切に決定すれば、複数のClockA〜Xに適切な分解能が得られ、複数個用意したClockA〜Xのどれかが必ず正しく画像データを取り込むことができる。

【0044】

このようにラインバッファ111には、正常に画像データを取り込んだものと正常でない画像データを取り込んだものが存在する。このため、ラインバッファ111のどれが正しく受信したかを判別するのが比較器112である。なお、比較器112が正常に受信された画像データを見極める方法については後述する。

【0045】

比較器112が正常に受信された画像データを特定すると、比較器112は一致信号をセレクタ113、115に出力するので、セレクタ113は正常に受信したラインバッファ111の画像データを選択して受信画像データ出力線114に出力し、セレクタ115は正常に受信したラインバッファ111に供給されていたクロックを選択して配信信号線116に出力する。このようにして、画像データ受信側デバイス102は同期化された画像データを受信することができる。

【0046】

〔比較器による抽出方法〕

各ラインバッファ111がそれぞれ異なるクロックで画像データを取り込んだ場合、比較器112が、どのクロックで取り込んだ画像データが正常受信されたものかを判別する手順について説明する。

【0047】

図5は、画像データの転送時の同期信号等の一例を示す。図6,7は図5の一部を拡大した図である。

【0048】

画像データは1枚の原稿を撮像部227で読み込んだものや、画像処理装置200において印刷部228に送出されるものである。すなわち、この画像データはラスタライズされたビットマップデータである。

【0049】

1ページの画像データが転送される際に、画像データの有効域を示す信号として、例えばフレームゲート信号がある。この信号が有効(Highアクティブ信号の場合は"1"、Lowアクティブ信号の場合は"0")を示している間に転送される画像データは、1ページ分の画像データとして有効なデータである。撮像部227と接続されたASIC216、ASIC216と接続された印刷部228は、フレームゲート信号を監視して受信すべき画像データがあることを検出する。

【0050】

同様に、画像データのライン転送の開始を示す同期タイミング信号として、ライン同期信号がある。撮像部227と接続されたASIC216、ASIC216と接続された印刷部228は、ライン同期信号の有効パルスを起点に1ラインのデータ転送開始を検出する。

【0051】

ラインゲート信号は、画像データの1ライン分の転送において、有効画像域を示す信号である。この信号が有効を示している間に転送される画像データは、1ライン分の画像データとして有効なデータである。なお、図ではHighアクティブとしている。

【0052】

したがって、フレームゲート信号が有効("1")の間に、画像データのライン数分だけライン同期信号の有効を示し、各ライン同期信号の後のラインゲート信号が1ライン毎に有効データを示す。

【0053】

画像データの受信側はこれらの制御信号を検出して画像データを取り込むことで、画像データを受信することができる。

【0054】

図6は、ライン同期信号、ラインゲート信号及び画像データ信号を1ライン転送分に着目して拡大した図の一例である。図6で示している画像データ信号は、ラインゲート信号が有効な領域以外は無効データであることになるので、画像データの有効域以外で送信元は無効データを転送している。

【0055】

画像データの無効データは、一律"0"固定であったり"1"固定であったり、又は、全くのランダムデータ(不定値)である場合もある。この無効データが存在する無効域は、スキャナやプロッタ装置のメカ制御制約上生ずるもので、現在のスキャナ装置やプロッタ装置の制御手法では必ず存在する。本実施形態では、この無効域に、比較器112がラインバッファ111の選択に使用する同期判定コードを含めて転送する。

【0056】

なお、図6のライン同期信号とラインゲート信号はどちらか一方を省略することも可能である。図7(a)は、ラインゲート信号を省略した信号のタイミングチャート図の1例であり、図7(b)は、ライン同期信号を省略した信号のタイミングチャート図の1例である。

【0057】

ラインゲート信号がない図7(a)の例では、ライン同期信号から何クロック目から有効画像データが開始するかを予め固定しておくことで、画像データ受信側デバイス102は、ライン同期信号から固定のクロック数をカウントすることで画像データを受信することができる。換言すれば、ライン同期信号から固定長の領域が無効域である。

【0058】

ライン同期信号がない図7(b)の例では、画像データ受信側デバイス102はラインゲート信号が有効を示す間に、画像データを受信する。換言すれば、ラインゲート信号が有効を示さない領域が無効域である。

【0059】

図8は、同期判定コードが含まれた画像データの無効域を説明する図の一例である。図8のハッチングされた画像データの信号は画像データとしては無効であるが、本実施形態では、同期化判定のための同期判定コードを転送する領域として利用されている。ライン同期信号(フレームゲート信号、ラインゲート信号も)は画像データ信号やクロック信号と共に、画像データ送信側デバイス101から画像データ受信側デバイス102に送信されるので、比較器112はライン同期信号を検出してから画像データが開始されるまでの間の無効域の同期判定コードを利用して、ラインバッファ111に画像データが正しく取り込まれたか否かを判定できる。

【0060】

図9(a)は、画像データ送信側デバイス101において無効域に同期判定コードを埋め込む構成例を、図9(b)はセレクタ301が出力する画像データ信号を説明する図の一例をそれぞれ示す。図9(a)ではインクリメントパターンが同期判定コードである。セレクタ301の入力側に送信画像とパターンジェネレータ302が接続されている。セレクタ301の出力側は画像データ出力用FF107に分岐して接続される。パターンジェネレータ302にはフレームゲート信号とラインゲート信号が入力され、ラインゲート信号はセレクタ線を介してセレクタ301に供給されている。

【0061】

パターンジェネレータ302はフレームゲート信号がアサートされると(図ではHighアクティブになると)起動して、インクリメントパターンを生成する。図では1クロック毎に1つカウントアップされたインクリメントパターンを生成するが、規則的なパターンであれば2つずつインクリメントしてもよい。また、パターンジェネレータ302は、フレームゲート信号がネゲートされると、出力値を初期値(図では1)に戻す。

【0062】

また、パターンジェネレータ302は、ラインゲート信号がアサートされるとインクリメントを停止する。したがって、パターンジェネレータ302は、

・フレームゲート信号がアサートされてからラインゲート信号がアサートされるまでの間、カウントパターンをインクリメントし、

・ラインゲート信号がアサートされている間は一定値を出力し、

・ラインゲート信号がネゲートされてからフレームゲート信号がネゲートされるまでの間は、カウントパターンをインクリメントし、

・フレームゲート信号がネゲートされると、初期値を出力する。

【0063】

セレクタ301は、ラインゲート信号が有効を示す場合は送信画像を出力し、ラインゲート信号が有効を示さない場合はインクリメントパターンを出力する。

【0064】

図9(b)に示すように、フレームゲート信号がアサートされるとインクリメントパターンがクロック毎に1つずつ増大する。そして、ラインゲート信号がアサートされるとインクリメントパターンは一定値(図では8)になり、ラインゲート信号がネゲートされるとインクリメントパターンはクロック毎に1つずつ増大する。これにより図では、インクリメントパターンが1〜13までカウントアップされている。

【0065】

セレクタ301は、ラインゲート信号がアサートされている間、送信画像を出力するので、セレクタが出力する画像データ信号は、インクリメントパターンが8の部分が送信画像に置き換わった信号になる。

【0066】

したがって、ラインバッファ111は、数値の1〜8、送信画像、及び、数値の9〜13を受信する。フレームゲート信号の開始からラインゲート信号の開始までのクロック数、及び、ラインゲート信号の終了からフレームゲート信号の終了までのクロック数は固定であるので、ラインバッファ111は、正常に画像データ信号を受信できた場合、数値の1〜8と数値の9〜13を受信できるはずである。このことは、ライン同期信号からラインゲート信号の開始までにインクリメントパターンを埋め込んだ場合も同様である。したがって、比較器112は、数値の1〜8と数値の9〜13を受信できたか否かにより、正常に画像データ信号を取り込むことができるラインバッファ111を特定することができる。なお、数値によってビット数が異なるので、最大の数値のビット数が格納可能なビット数単位でインクリメントパターンを格納すればよい。

【0067】

図10は、各比較器112がインクリメントパターンが正常か否かを判定する手順を示すフローチャート図の一例である。この手順は、ページ転送の最初にだけ実施して、以降は、ページの全体の転送が終了するまで、比較器112が一致すると判定したラインバッファ111の画像データ信号を受信画像データ出力線114に出力すればよい。また、セレクタ113,115がより確実に正常なラインバッファ111を選択するため、ライン毎にこの手順を実行してもよい。

【0068】

比較器112は、フレームゲート信号がアサートされると(S10)、インクリメントパターンの検出を開始して、予め定められたインクリメントパターンと一致するか否かを判定する(S20)。図では1〜8の数値が順番に(所定のクロック数ずつ)検出されるか否かを判定する。

【0069】

ラインバッファ111から1〜8の数値が1つでも検出されない場合(S20のNo)、比較器112は不一致信号をセレクタに出力する(S60)。

【0070】

ラインバッファ111から1〜8の数値が全て検出された場合(S20のYes)、比較器112はラインゲート信号がネゲートされるまで待機する(S30)。

【0071】

ラインゲート信号がネゲートされると、比較器112はインクリメントパターンの検出を再開して、予め定められたインクリメントパターンと一致するか否かを判定する(S40)。図では9〜13の数値が順番に(所定のクロック数ずつ)検出されるか否かを判定する。

【0072】

ラインバッファ111から9〜13の数値が1つでも検出されない場合(S40のNo)、比較器112は不一致信号をセレクタに出力する(S60)。

【0073】

ラインバッファ111から9〜13の数値が全て検出された場合(S40のYes)、比較器112は一致信号をセレクタに出力する(S50)。

【0074】

こうすることで、比較器112は、複数のラインバッファ111のうち正常に画像データ信号を取り込めるラインバッファ111、及び、複数のクロックClockA〜Xのうち正常に画像データ信号を取り込めるクロックを特定することができる。なお、ステップS30、S40の判定を省略してもよいし、ステップ10、S20の判定を省略してもよい。

【0075】

なお、ラインバッファ111は複数あるので、2つ以上のラインバッファ111が正常に画像データ信号を取り込むことができる場合もある。この場合、セレクタ113,115は、一番初めに一致信号を出力した比較器112に接続されたラインバッファ111とクロックを選択することもできるし、一番最後に一致信号を出力した比較器112に接続されたラインバッファ111とクロックを選択することもできる。また、クロック信号の位相が乱れた際により安定したラインバッファ111を選ぶため、正常に画像データを取り込んだ2つ以上のラインバッファ111のうち、供給されるクロック信号の位相差が中央のラインバッファ111(図4の真ん中の「○」のラインバッファ)を選択することが好適となる。

【0076】

上述したように、無効域に埋め込まれるインクリメントパターンは、規則的に変化する値や知られた一定値であればどのようなものでもよい。

図11(a)は画像データ送信側デバイス101において無効域にインクリメントデータを伝送する別の構成例を示す。図11(a)において図9(a)と同一部の説明は省略する。図11(a)ではラインゲート信号がパターンジェネレータ302に供給されていない。このような構成では、パターンジェネレータ302は、ラインゲート信号がアサートされている間は一定値を出力するのでなく、フレームゲート信号がアサートされている間、クロックに同期してカウントアップを継続する。

【0077】

図11(b)はセレクタ301が出力する画像データ信号を説明する図の一例である。フレームゲート信号がアサートされるとインクリメントパターンがクロック毎に1つずつ増大するので、図では一例として1〜60までカウントアップされている。セレクタ301は、ラインゲート信号がアサートされている間、インクリメントパターンでなく送信画像を送信するので、画像データ信号は、数値の1〜8、送信画像、及び、数値の56〜60となる。

【0078】

したがって、比較器112は、数値の1〜8と数値の56〜60を受信できたか否かにより、正常に画像データ信号を取り込むことができるラインバッファ111を特定することができる。この場合の比較器112の動作手順は、図10のステップS40で検出する数値が変わるだけである。このように、画像データ受信側デバイス102は、画像データ送信側デバイス101が無効域に埋め込む同期判定コードがどのようなものか分かっていれば、画像データを取り出すべきラインバッファ111を決定できる。例えば、インクリメントパターンでなく、デクリメントパターンでもよいし、一定値(例えば、0〜9の同じの数値の繰り返し)でもよい。デクリメントパターンの場合、比較器112は例えば1つずつ小さくなる数値を順番に検出できるか否かにより、ラインバッファ111を決定する。一定値が埋め込まれる場合、比較器112は、予め定められた回数だけ、同じ数値が検出できるか否かによりラインバッファ111を決定する。

【0079】

また、画像データ送信側デバイス101がパターンジェネレータ302のような、無効域に数値を埋め込む構成を有していない場合でも、無効域が常に"0"又は常に"1"となる送信画像であれば、比較器112はほぼ同様にラインバッファ111を選択することが可能である。

【0080】

図12(a)は、画像データ送信側デバイス101において無効域にライン同期信号を埋め込む構成例を示す。セレクタ301の入力側には送信画像とライン同期信号が入力され、ライン同期信号はセレクタ301のセレクタ線になっている。セレクタ301は、ライン同期信号が有効を示さない状態では送信画像を出力し、ライン同期信号が有効を示す状態になった時だけライン同期信号を出力する。このような構成により、ライン同期信号を画像データ信号に含めることができる。

【0081】

図12(b)は、ライン同期信号が無効域に埋め込まれた画像データ信号の一例を示す図である。上記のように、ライン同期信号から送信画像の有効域までのクロック数は固定である。そして、図12(b)では無効域の値は"0"になっている。このような送信画像とライン同期信号がセレクタ301に入力されると、ライン同期信号に同期して無効域に"1"が埋め込まれた画像データ信号が出力される。ラインバッファ111にはそれぞれ画像データ信号が取り込まれるが、固定のクロック数だけ"0"が取り込まれるものとそうでないものが生じる。よって、比較器112は、ライン同期信号を基準に、1つの"1"が検出されるかどうかと、"0"の数が固定長の数だけ検出されるかどうかにより、ラインバッファ111が正常に画像データ信号を取り込んでいるか否かを判定できる。無効域に"0"でなく"1"が埋め込まれる送信画像の場合、画像データ送信側デバイス101はライン同期信号に同期して"0"を送信画像に埋め込めばよい。

【0082】

図13は、ラインバッファ111が正常に画像データ信号を取り込んだか否かを判定する手順を示すフローチャート図の一例である。

【0083】

比較器112は、ライン同期信号が有効を示すと比較を開始する(S110)。

ライン同期信号が検出された際、比較器112は"1"が検出されたか否かを判定する(S120)。

【0084】

ラインバッファ111から"1"が検出されない場合(S120のNo)、比較器112は不一致信号をセレクタに出力する(S150)。

【0085】

ラインバッファ111から"1"が検出された場合(S120のYes)、比較器112は決まった数の"0"が検出されたか否かを判定する(S130)。

【0086】

ラインバッファ111から決まった数の"0"が検出されない場合(S130のNo)、比較器112は不一致信号をセレクタ113,115に出力する(S150)。

【0087】

ラインバッファ111から決まった数の"0"が検出された場合(S130のYes)、比較器112は一致信号をセレクタ113,115に出力する(S140)。

【0088】

以上のような処理により、画像データ送信側デバイス101がパターンジェネレータ302を有していなくても、画像データ受信側デバイス102は無効域を利用して正常に画像データ信号を取り込むラインバッファ111を選択できる。

【0089】

したがって、以上説明したように、本実施形態のデータ伝送装置100は、温度条件や経年劣化その他の外的要因でデバイス間のI/F状況が変動しても、位相の異なるクロックで取り込んだ複数のラインバッファ111から、正常に画像データ信号を取り込んだラインバッファ111を選択するので、外的要因による変動に追従して同期を確立することができる。開発者がASIC上で実装面積やアナログ的な調整をしたり、LVDS用の専用IPを配置することなく、比較的小規模で安価なコストで、タイミング設計も容易なASICを提供することができる

【符号の説明】

【0090】

100 データ伝送装置

101 画像データ送信側デバイス

102 画像データ受信側デバイス

103 OSC(クロック発振源)

104、105 PLL

106 クロック配信用信号線

107 画像データ出力用FF(フリップフロップ)

108 画像データ送信用出力バッファ

109 画像データ受信用入力バッファ

110 遅延バッファ

111 ラインバッファ

112 比較器

113、115 セレクタ

114 受信画像データ出力線

116 配信信号線

【先行技術文献】

【特許文献】

【0091】

【特許文献1】特開2006−080877号公報

【技術分野】

【0001】

本発明は、シリアルデータを伝送する半導体デバイスに関する。

【背景技術】

【0002】

ASIC等のLSIデバイス間のデータ転送において、複数のシリアル伝送路上を伝達されるデータの同期をLSYNC信号を用いて取る方式が知られている。画像データのデータ転送にはよくLVDS(Low voltage differential signaling)が用いられ、LSYNC信号を用いて同期を取る技術が提案されている(例えば、特許文献1参照。)。

【0003】

特許文献1には、デバイス間I/Fの同期をとる目的で、シリアル伝送路上に流されるLSYNC信号を用いてタイミング同期を取る画像転送装置が開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に開示された画像転送装置は、比較的高価なLVDS I/Fを複数個、使用するためASICの実装上のコスト増となるという問題がある。また、LVDS I/Fによる信号レベルの同期にはトレーニング等の手順が必要となるため、こちらもコスト増をもたらす。

【0005】

本発明は、上記課題に鑑み、複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題に鑑み、本発明は、送信側と受信側がクロック信号により同期して送信側から受信側にデータをシリアル送信する半導体デバイスであって、データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段と、送信側と受信側に共通のクロック信号を提供するクロック信号提供手段と、クロック信号に同期して同じデータを送信する複数の伝送路と、受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段と、前記複数の遅延クロック信号に同期して、前記複数の伝送路を介して送信されたデータを取り込む複数の受信バッファと、前記コードを予め定められた規則に基づき検証して前記複数の受信バッファから1つの受信バッファを、前記複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段と、を有する。

【発明の効果】

【0007】

複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供することができる。

【図面の簡単な説明】

【0008】

【図1】画像処理装置のハードウェア構成図の一例である。

【図2】データ伝送装置の構成図の一例である。

【図3】データ伝送装置の動作を示すタイミングチャート図の一例である。

【図4】ラインバッファが正常に取り込めるものと、そうでないものの違いを説明する図の一例である。

【図5】画像データの転送時の同期信号等の一例を示す図である。

【図6】ライン同期信号、ラインゲート信号及び画像データ信号を1ライン転送分に着目して拡大した図の一例である。

【図7】ラインゲート信号を省略した信号のタイミングチャート図の1例である。

【図8】同期判定データが含まれた画像データの無効域を説明する図の一例である。

【図9】画像データ送信側デバイスにおいて無効域にインクリメントデータを伝送する構成例を示す図である。

【図10】各比較器がインクリメントパターンが正常か否かを判定する手順を示すフローチャート図の一例である。

【図11】画像データ送信側デバイスにおいて無効域にインクリメントデータを伝送する構成例を示す図の一例である。

【図12】画像データ送信側デバイスにおいて無効域にライン同期信号を埋め込む構成例を示す図の一例である。

【図13】ラインバッファが正常に画像データ信号を取り込んだか否かを判定する手順を示すフローチャート図の一例である。

【発明を実施するための形態】

【0009】

以下、本発明を実施するための形態について図面を参照しながら説明する。

図1は、画像処理装置200のハードウェア構成図の一例を示す。本実施形態のデータ伝送装置は、ASIC216と印刷部228や、撮像部227とASIC216の間の画像データの伝送を行う。ASIC216と印刷部228に着目した場合はASIC216が送信側で印刷部228が受信側になり、撮像部227とASIC216に着目した場合は撮像部227が送信側でASIC216が受信側になる。

【0010】

画像処理装置200の構成は公知なので簡単に説明する。画像処理装置200は、コントローラ230と、オペレーションパネル225と、ファクシミリコントロールユニット(FCU)226と、撮像部227及び印刷部228が有する。

【0011】

コントローラ230は、CPU214と、ASIC216と、NB(ノースブリッジ)215と、SB(サウスブリッジ)217と、MEM−P(システムメモリ)211と、MEM−C(ローカルメモリ)212と、HDD(ハードディスクドライブ)213と、メモリカードスロット223と、NIC(ネットワークインタフェースコントローラ)218と、USBデバイス219と、IEEE1394デバイス221と、セントロニクスデバイス222とを有する。

【0012】

CPU214は、種々の情報処理を実行するためのICであり、アプリケーションやプラットフォーム等をUNIX(登録商標)等のOSによりプロセス単位で並列的に実行する。ASIC216は、画像処理用のICである。ASIC216は、端末から受信した印刷データをレンダリングして文字、図形、背景などオブジェクト毎に適切なディザ処理を行うなどして印刷部228に送信する。また、ASIC216は、撮像部227が撮影した画像データに対し、写真や文字などに像域分離して、文字のエッジ強調、写真の階調補完等を行う。

【0013】

NB215は、CPU214とASIC216を接続するためのブリッジである。SB217は、NB215と周辺機器等を接続するためのブリッジである。ASIC216とNB215は、AGP(Accelerated Graphics Port)を介して接続されている。

【0014】

MEM−P211は、NB215に接続されたメモリである。MEM−C212は、ASIC216に接続されたメモリである。HDD213は、ASIC216に接続されたストレージであり、画像データ蓄積・文書データ蓄積・プログラム蓄積・フォントデータ蓄積・フォームデータ蓄積等を行うために使用される。

【0015】

メモリカードスロット223は、SB217に接続され、メモリカード224をセット(挿入)するために使用される。NIC218は、ネットワーク500等を介してMACアドレス等を使用したデータ通信を行うためのコントローラである。USBデバイス219は、USB規格に準拠したシリアルポートを提供するためのデバイスである。IEEE1394デバイス221は、IEEE1394規格に準拠したシリアルポートを提供するためのデバイスである。セントロニクスデバイス222は、セントロニクス仕様に準拠したパラレルポートを提供するためのデバイスである。NIC1218と、USBデバイス219と、IEEE1394デバイス221と、セントロニクスデバイス222と、PCI(Peripheral Component Interconect)バスを介してNB215とSB217に接続されている。

【0016】

オペレーションパネル225は、ユーザが機器100に入力を行うためのハードウェア(操作部)であると共に、画像処理装置200がオペレータに可視情報を提供するためのハードウェア(表示部)である。オペレーションパネル225は、ASIC216に接続されている。FCU226と、撮像部227と、印刷部228は、PCIバスを介してASIC216に接続されており、本実施形態のデータ伝送装置は、例えば、PCIバスの代わりに適用されることが想定される。

【0017】

図2は、データ伝送装置100の構成図の一例を示す。データ伝送装置100は、画像データ送信側デバイス101及び画像データ受信側デバイス102を有する。画像データ送信側デバイス101は、画像データ出力用FF(フリップフロップ)107、画像データ送信用出力バッファ108、PLL105及びクロックツリー121を有する。

【0018】

画像データ送信側デバイス101及び画像データ受信側デバイス102は、上記のASIC216の他、FPGAのようなLSIデバイス、MPUやDSPなどであり、データを送信又は受信するICであればよい。画像データ送信側デバイス101は画像データの送信元デバイスで、画像データ受信側デバイス102は画像データの受信先デバイスである。

【0019】

画像データ受信側デバイス102は、画像データ受信用入力バッファ109、複数のラインバッファ111、それぞれのラインバッファ111に接続された複数の比較器112、セレクタ114、PLL104、遅延バッファ110、クロックツリー122、及び、セレクタ115を有する。なお、PLL104にはOSC103が接続されている。

【0020】

画像データ送信側デバイス101のPLL105の出力側はクロックツリー121と接続され、クロックツリー121は複数の画像データ出力用FF107とそれぞれ接続されている。また、各画像データ出力用FF107はそれぞれ各画像データ送信用出力バッファ108と接続されている。

【0021】

画像データ受信用入力バッファ109は、データ伝送路117毎に画像データ送信用出力バッファ108と接続され、複数のラインバッファ111はデータ伝送路117毎に設けられている。セレクタ113の入力側には、1対のラインバッファ111と比較器112の間からそれぞれデータ線が接続され、出力側は受信画像データ出力線114が接続されている。また、各比較器112から2つのセレクタ113、115にセレクタ信号線がそれぞれ接続されている。

【0022】

PLL104は、データ伝送路117と同じ数の遅延バッファ110に接続され、各遅延バッファ110はそれぞれ対応するクロックツリー122と接続されると共に、セレクタ115の入力側に接続される。クロックツリー122はそれぞれラインバッファ111に接続される。セレクタ115の出力側にはクロックツリー123と配信信号線116が接続されている。

【0023】

画像データ出力用FF107は、PLL105からのクロックに同期して画像データを画像データ送信用出力バッファ108に出力する。画像データ送信用出力バッファ108は、画像データを一時的に記憶するバッファである。

【0024】

画像データ受信用入力バッファ109は画像データを一時的に記憶するバッファである。ラインバッファ111はデータ伝送経路117毎に受信した画像データを取り込む。ラインバッファ111が取り込む画像データは、1ライン分の場合も、1ライン分よりも少ない又は大きい場合もある。比較器112は、ラインバッファ111が受信した画像データに含まれる特定のコード(以下、同期判定コードという)を抽出して、正常に画像データを受信するラインバッファ111を選択する。

【0025】

セレクタ113は、比較器112の選択結果を用いて、複数のラインバッファ111の出力から1つの画像データを選択する。遅延バッファ110は、PLL104から供給されるクロック信号のクロック位相をずらす(遅延させる)。セレクタ115は、各遅延バッファ110が出力するクロック信号から、比較器112の選択結果を用いて1つのクロック信号を選択する。

【0026】

本実施形態の画像データ送信側デバイス101及び画像データ受信側デバイス102は、OSC103が発振するクロックで同期通信を行う。OSC103が発信するクロックは、いったん画像データ受信側デバイス102内を通過して、クロック配信用信号線106を介して画像データ送信側デバイス101に入力される。

【0027】

OSC103が発信するクロックは画像データ送信側デバイス101及び画像データ受信側デバイス102に共通だが、配線長や経路の関係で2つのデバイス間で位相差が生じてると考えらえる。したがって、ある程度の位相差という意味では、OSC103が発信するクロックの配信経路は図示以外の構成でもよい。

【0028】

クロック配信用信号線106を介して画像データ送信側デバイス101に入力されたクロックは、PLL105を経由して、各画像データ出力用FF107に配信される。各画像データ出力用FF107にはクロックツリー121から共通にクロックが供給されるので、各画像データ出力用FF107は画像データ送信側デバイス101の同期回路となる。画像データ出力用FF107は画像データ送信側デバイス101から画像データを出力する最終段FF(フリップフロップ)で、配信されたクロックに同期して画像データを出力する。

【0029】

画像データ出力用FF107から出力された画像データは画像データ送信用出力バッファ108から、各データ伝送路117を介して画像データ受信側デバイス102に入力される。

【0030】

画像データ受信側デバイス102は、画像データ受信用入力バッファ109に画像データを一時的に記憶した後、ラインバッファ111に取り込む。ラインバッファ111はFFとして構成されており、各ラインバッファ111にはPLL104からクロックが供給されているので、各ラインバッファ111はクロックに同期して重複した画像データを同期受信する。

【0031】

本実施形態では、各ラインバッファ111に供給されるクロックの位相が、遅延バッファ110にて明示的にずらされている。すなわち、各遅延バッファ110は、位相が互いに異なるクロックを複数生成するよう、ラインバッファ111と同じ数だけ用意されている。このため、各ラインバッファ111が取り込む画像データは、同じものとそうでないものが生じる。遅延バッファ110が供給するクロックのうち、画像データ送信側デバイス101のクロックと同じ位相のクロックが供給されるラインバッファ111が、画像データ送信側デバイス101と"同期"したと称される。

【0032】

このラインバッファ111のバッファ段数(容量)は、同期したラインバッファ111を判定するのに必要なクロックサイクル数と、同期したラインバッファ111の画像データを処理する後段ブロックとのI/Fを確立するまでのサイクル数分を最低バッファ段数とする。例えば、比較器112でラインバッファ111の同期判定コードを検証するまでのクロック数と、そのクロック数で受信された画像データをセレクタ113,115が選択するためのクロック数とで計5クロック必要で、さらに、セレクタ115が出力するクロックに後段のブロック(不図示)の同期クロックが切り替わるまでに3クロック必要な場合は、ラインバッファ111のバッファ段数はそれぞれ5+3=8段分となる。また、仮に、後段のブロックの同期クロックの切り替えにクロックの消費が不要なら、ラインバッファ111のバッファ段数はそれぞれ5段分となる。このようにバッファ段数を設計することで、ラインバッファ111のバッファ段数を最小限にすることができる。

【0033】

1つのクロックで画像データの1段がラインバッファ111に取り込まれるが、図4で後述する、各クロックのタイミング(位相)による画像データの取りこぼしを考慮すると、最大でラインバッファ111のバッファ段数と同じ数のラインバッファ111があることが好ましい。したがって、ラインバッファ111の数は、最大ではラインバッファ111のバッファ段数と同じになる。

【0034】

画像データ受信側デバイス102は、セレクタ114が出力する同期化された画像データと、セレクタ115が出力する同期クロックを用いて、受信した画像データを処理する(例えば、後段に出力する)。

【0035】

図3は、データ伝送装置100の動作を示すタイミングチャート図の一例である。各信号の意味が以下のとおりである。

Send Clock :画像データ送信側デバイス内のクロック信号

Send Data :画像データ出力信号

Receive Clock:画像データ受信側デバイス内のクロック信号

Receive Data :画像データ入力信号

ClockA :画像データ受信側デバイス内で、遅延バッファにて一定量位相をずらしたクロック信号A

ClockB :画像データ受信側デバイス内で、遅延バッファにて一定量位相をずらしたクロック信号B

ClockC :画像データ受信側デバイス内で、遅延バッファにて一定量位相をずらしたクロック信号C

ClockX :画像データ受信側デバイス内で、遅延バッファにて一定量位相をずらしたクロック信号X

Receive DataA:ClockAでReceive Dataを取り込んだ画像データ

Receive DataB:ClockBでReceive Dataを取り込んだ画像データ

Receive DataC:ClockCでReceive Dataを取り込んだ画像データ

Receive DataX:ClockXでReceive Dataを取り込んだ画像データ

Send Dataは、画像データ送信側デバイス101が送信する画像データである。Send Clockは、例えばクロックツリー121の出力するクロックである。

【0036】

Send Dataは画像データ出力用FF107から画像データ受信側デバイス102に向けて出力され、ラインバッファ111によって受信される。このとき、画像データ受信側デバイス102のPLL104から出力される動作クロックがReceive Clockであり、配線遅延や信号間スキューによる遅延を受けた画像データがReceive Dataである。

【0037】

配線遅延や信号間スキューによる遅延がない理想的なデータ転送であれば、複数のReceive Dataは時間的にずれることなく画像データの変化点がクロックの立ち上がりエッジと一致する。しかしながら、図3に示すように、クロックの立ち上がりエッジは、複数のReceive Dataの画像データの変化点と前後したり重なっており、Receive Clockの立ち上がりエッジをトリガーにしてラインバッファ111がReceive Dataを取り込むと正常に受信することができない場合がある。

【0038】

そこで、各遅延バッファ110は、Receive Clockの位相を一定時間づつずらしたクロックClockA、ClockB、ClockC、・・・ClockXを生成する。それぞれのクロックClockA、ClockB、ClockC、・・・ClockXがラインバッファ111に供給され、ラインバッファ111がクロックClockA、ClockB、ClockC、・・・ClockXの立ち上がりエッジをトリガーにReceiveDataを取り込むことで、画像データReceive DataA〜Xがそれぞれ生成される。

【0039】

このため、ラインバッファ111が受信する画像データReceive DataA〜Xのうち、ClockA〜XとReceive Dataとのタイミングの関係で、ラインバッファ111が正常に取り込めたものと、そうでないものが生じる。

【0040】

図4は、ラインバッファ111が正常に取り込めるものと、そうでないものの違いを説明する図の一例である。図4は、Receive Dataの一部を表示したものであり、複数の「○」「×」で示す各タイミングは、各クロックの画像データ取り込みのタイミングを示す。ラインバッファ111がクロックにより正常に取り込めるタイミングを「○」で、正常に取り込めないタイミングを「×」でそれぞれ示している。図4に示すように、正常に取り込めるか否かは、Receive Dataと各クロックの立ち上がりエッジ(画像データ取り込みタイミング)の相対的な関係で決まる。

【0041】

複数のReceive DataA〜Xは最大でも1クロックの1周期分までは遅延しないという前提では、遅延バッファ110は、ClockA〜Xを1周期の範囲で分散させれば、ClockA〜Xのいずれかでラインバッファ111の1つは必ずReceive Dataを取り込めると考えられる。したがって、遅延バッファ110が位相をずらす量は、画像データを取り込む1クロックサイクルの周期を1/Xにした時間とする必要があることがわかる。

【0042】

例えばX(ラインバッファのバッファ段数)= 4で1クロックサイクルの周期が20nsの場合、遅延バッファ110がClockA〜Xの1つをずらすべき時間は「20÷4≒5ns」である。したがって、遅延バッファ110は、位相差0ns(源振クロック)、5ns、10ns、15nsの4つのクロックを生成する。4つのラインバッファ111は、それぞれのクロックで受信動作する。

【0043】

Xの値は、源振クロックの周波数や受信時のタイミング特性(正常に取り込めるタイミング幅)等を考慮して決定することで、ラインバッファ111のバッファ段数よりも小さくできる。Xを適切に決定すれば、複数のClockA〜Xに適切な分解能が得られ、複数個用意したClockA〜Xのどれかが必ず正しく画像データを取り込むことができる。

【0044】

このようにラインバッファ111には、正常に画像データを取り込んだものと正常でない画像データを取り込んだものが存在する。このため、ラインバッファ111のどれが正しく受信したかを判別するのが比較器112である。なお、比較器112が正常に受信された画像データを見極める方法については後述する。

【0045】

比較器112が正常に受信された画像データを特定すると、比較器112は一致信号をセレクタ113、115に出力するので、セレクタ113は正常に受信したラインバッファ111の画像データを選択して受信画像データ出力線114に出力し、セレクタ115は正常に受信したラインバッファ111に供給されていたクロックを選択して配信信号線116に出力する。このようにして、画像データ受信側デバイス102は同期化された画像データを受信することができる。

【0046】

〔比較器による抽出方法〕

各ラインバッファ111がそれぞれ異なるクロックで画像データを取り込んだ場合、比較器112が、どのクロックで取り込んだ画像データが正常受信されたものかを判別する手順について説明する。

【0047】

図5は、画像データの転送時の同期信号等の一例を示す。図6,7は図5の一部を拡大した図である。

【0048】

画像データは1枚の原稿を撮像部227で読み込んだものや、画像処理装置200において印刷部228に送出されるものである。すなわち、この画像データはラスタライズされたビットマップデータである。

【0049】

1ページの画像データが転送される際に、画像データの有効域を示す信号として、例えばフレームゲート信号がある。この信号が有効(Highアクティブ信号の場合は"1"、Lowアクティブ信号の場合は"0")を示している間に転送される画像データは、1ページ分の画像データとして有効なデータである。撮像部227と接続されたASIC216、ASIC216と接続された印刷部228は、フレームゲート信号を監視して受信すべき画像データがあることを検出する。

【0050】

同様に、画像データのライン転送の開始を示す同期タイミング信号として、ライン同期信号がある。撮像部227と接続されたASIC216、ASIC216と接続された印刷部228は、ライン同期信号の有効パルスを起点に1ラインのデータ転送開始を検出する。

【0051】

ラインゲート信号は、画像データの1ライン分の転送において、有効画像域を示す信号である。この信号が有効を示している間に転送される画像データは、1ライン分の画像データとして有効なデータである。なお、図ではHighアクティブとしている。

【0052】

したがって、フレームゲート信号が有効("1")の間に、画像データのライン数分だけライン同期信号の有効を示し、各ライン同期信号の後のラインゲート信号が1ライン毎に有効データを示す。

【0053】

画像データの受信側はこれらの制御信号を検出して画像データを取り込むことで、画像データを受信することができる。

【0054】

図6は、ライン同期信号、ラインゲート信号及び画像データ信号を1ライン転送分に着目して拡大した図の一例である。図6で示している画像データ信号は、ラインゲート信号が有効な領域以外は無効データであることになるので、画像データの有効域以外で送信元は無効データを転送している。

【0055】

画像データの無効データは、一律"0"固定であったり"1"固定であったり、又は、全くのランダムデータ(不定値)である場合もある。この無効データが存在する無効域は、スキャナやプロッタ装置のメカ制御制約上生ずるもので、現在のスキャナ装置やプロッタ装置の制御手法では必ず存在する。本実施形態では、この無効域に、比較器112がラインバッファ111の選択に使用する同期判定コードを含めて転送する。

【0056】

なお、図6のライン同期信号とラインゲート信号はどちらか一方を省略することも可能である。図7(a)は、ラインゲート信号を省略した信号のタイミングチャート図の1例であり、図7(b)は、ライン同期信号を省略した信号のタイミングチャート図の1例である。

【0057】

ラインゲート信号がない図7(a)の例では、ライン同期信号から何クロック目から有効画像データが開始するかを予め固定しておくことで、画像データ受信側デバイス102は、ライン同期信号から固定のクロック数をカウントすることで画像データを受信することができる。換言すれば、ライン同期信号から固定長の領域が無効域である。

【0058】

ライン同期信号がない図7(b)の例では、画像データ受信側デバイス102はラインゲート信号が有効を示す間に、画像データを受信する。換言すれば、ラインゲート信号が有効を示さない領域が無効域である。

【0059】

図8は、同期判定コードが含まれた画像データの無効域を説明する図の一例である。図8のハッチングされた画像データの信号は画像データとしては無効であるが、本実施形態では、同期化判定のための同期判定コードを転送する領域として利用されている。ライン同期信号(フレームゲート信号、ラインゲート信号も)は画像データ信号やクロック信号と共に、画像データ送信側デバイス101から画像データ受信側デバイス102に送信されるので、比較器112はライン同期信号を検出してから画像データが開始されるまでの間の無効域の同期判定コードを利用して、ラインバッファ111に画像データが正しく取り込まれたか否かを判定できる。

【0060】

図9(a)は、画像データ送信側デバイス101において無効域に同期判定コードを埋め込む構成例を、図9(b)はセレクタ301が出力する画像データ信号を説明する図の一例をそれぞれ示す。図9(a)ではインクリメントパターンが同期判定コードである。セレクタ301の入力側に送信画像とパターンジェネレータ302が接続されている。セレクタ301の出力側は画像データ出力用FF107に分岐して接続される。パターンジェネレータ302にはフレームゲート信号とラインゲート信号が入力され、ラインゲート信号はセレクタ線を介してセレクタ301に供給されている。

【0061】

パターンジェネレータ302はフレームゲート信号がアサートされると(図ではHighアクティブになると)起動して、インクリメントパターンを生成する。図では1クロック毎に1つカウントアップされたインクリメントパターンを生成するが、規則的なパターンであれば2つずつインクリメントしてもよい。また、パターンジェネレータ302は、フレームゲート信号がネゲートされると、出力値を初期値(図では1)に戻す。

【0062】

また、パターンジェネレータ302は、ラインゲート信号がアサートされるとインクリメントを停止する。したがって、パターンジェネレータ302は、

・フレームゲート信号がアサートされてからラインゲート信号がアサートされるまでの間、カウントパターンをインクリメントし、

・ラインゲート信号がアサートされている間は一定値を出力し、

・ラインゲート信号がネゲートされてからフレームゲート信号がネゲートされるまでの間は、カウントパターンをインクリメントし、

・フレームゲート信号がネゲートされると、初期値を出力する。

【0063】

セレクタ301は、ラインゲート信号が有効を示す場合は送信画像を出力し、ラインゲート信号が有効を示さない場合はインクリメントパターンを出力する。

【0064】

図9(b)に示すように、フレームゲート信号がアサートされるとインクリメントパターンがクロック毎に1つずつ増大する。そして、ラインゲート信号がアサートされるとインクリメントパターンは一定値(図では8)になり、ラインゲート信号がネゲートされるとインクリメントパターンはクロック毎に1つずつ増大する。これにより図では、インクリメントパターンが1〜13までカウントアップされている。

【0065】

セレクタ301は、ラインゲート信号がアサートされている間、送信画像を出力するので、セレクタが出力する画像データ信号は、インクリメントパターンが8の部分が送信画像に置き換わった信号になる。

【0066】

したがって、ラインバッファ111は、数値の1〜8、送信画像、及び、数値の9〜13を受信する。フレームゲート信号の開始からラインゲート信号の開始までのクロック数、及び、ラインゲート信号の終了からフレームゲート信号の終了までのクロック数は固定であるので、ラインバッファ111は、正常に画像データ信号を受信できた場合、数値の1〜8と数値の9〜13を受信できるはずである。このことは、ライン同期信号からラインゲート信号の開始までにインクリメントパターンを埋め込んだ場合も同様である。したがって、比較器112は、数値の1〜8と数値の9〜13を受信できたか否かにより、正常に画像データ信号を取り込むことができるラインバッファ111を特定することができる。なお、数値によってビット数が異なるので、最大の数値のビット数が格納可能なビット数単位でインクリメントパターンを格納すればよい。

【0067】

図10は、各比較器112がインクリメントパターンが正常か否かを判定する手順を示すフローチャート図の一例である。この手順は、ページ転送の最初にだけ実施して、以降は、ページの全体の転送が終了するまで、比較器112が一致すると判定したラインバッファ111の画像データ信号を受信画像データ出力線114に出力すればよい。また、セレクタ113,115がより確実に正常なラインバッファ111を選択するため、ライン毎にこの手順を実行してもよい。

【0068】

比較器112は、フレームゲート信号がアサートされると(S10)、インクリメントパターンの検出を開始して、予め定められたインクリメントパターンと一致するか否かを判定する(S20)。図では1〜8の数値が順番に(所定のクロック数ずつ)検出されるか否かを判定する。

【0069】

ラインバッファ111から1〜8の数値が1つでも検出されない場合(S20のNo)、比較器112は不一致信号をセレクタに出力する(S60)。

【0070】

ラインバッファ111から1〜8の数値が全て検出された場合(S20のYes)、比較器112はラインゲート信号がネゲートされるまで待機する(S30)。

【0071】

ラインゲート信号がネゲートされると、比較器112はインクリメントパターンの検出を再開して、予め定められたインクリメントパターンと一致するか否かを判定する(S40)。図では9〜13の数値が順番に(所定のクロック数ずつ)検出されるか否かを判定する。

【0072】

ラインバッファ111から9〜13の数値が1つでも検出されない場合(S40のNo)、比較器112は不一致信号をセレクタに出力する(S60)。

【0073】

ラインバッファ111から9〜13の数値が全て検出された場合(S40のYes)、比較器112は一致信号をセレクタに出力する(S50)。

【0074】

こうすることで、比較器112は、複数のラインバッファ111のうち正常に画像データ信号を取り込めるラインバッファ111、及び、複数のクロックClockA〜Xのうち正常に画像データ信号を取り込めるクロックを特定することができる。なお、ステップS30、S40の判定を省略してもよいし、ステップ10、S20の判定を省略してもよい。

【0075】

なお、ラインバッファ111は複数あるので、2つ以上のラインバッファ111が正常に画像データ信号を取り込むことができる場合もある。この場合、セレクタ113,115は、一番初めに一致信号を出力した比較器112に接続されたラインバッファ111とクロックを選択することもできるし、一番最後に一致信号を出力した比較器112に接続されたラインバッファ111とクロックを選択することもできる。また、クロック信号の位相が乱れた際により安定したラインバッファ111を選ぶため、正常に画像データを取り込んだ2つ以上のラインバッファ111のうち、供給されるクロック信号の位相差が中央のラインバッファ111(図4の真ん中の「○」のラインバッファ)を選択することが好適となる。

【0076】

上述したように、無効域に埋め込まれるインクリメントパターンは、規則的に変化する値や知られた一定値であればどのようなものでもよい。

図11(a)は画像データ送信側デバイス101において無効域にインクリメントデータを伝送する別の構成例を示す。図11(a)において図9(a)と同一部の説明は省略する。図11(a)ではラインゲート信号がパターンジェネレータ302に供給されていない。このような構成では、パターンジェネレータ302は、ラインゲート信号がアサートされている間は一定値を出力するのでなく、フレームゲート信号がアサートされている間、クロックに同期してカウントアップを継続する。

【0077】

図11(b)はセレクタ301が出力する画像データ信号を説明する図の一例である。フレームゲート信号がアサートされるとインクリメントパターンがクロック毎に1つずつ増大するので、図では一例として1〜60までカウントアップされている。セレクタ301は、ラインゲート信号がアサートされている間、インクリメントパターンでなく送信画像を送信するので、画像データ信号は、数値の1〜8、送信画像、及び、数値の56〜60となる。

【0078】

したがって、比較器112は、数値の1〜8と数値の56〜60を受信できたか否かにより、正常に画像データ信号を取り込むことができるラインバッファ111を特定することができる。この場合の比較器112の動作手順は、図10のステップS40で検出する数値が変わるだけである。このように、画像データ受信側デバイス102は、画像データ送信側デバイス101が無効域に埋め込む同期判定コードがどのようなものか分かっていれば、画像データを取り出すべきラインバッファ111を決定できる。例えば、インクリメントパターンでなく、デクリメントパターンでもよいし、一定値(例えば、0〜9の同じの数値の繰り返し)でもよい。デクリメントパターンの場合、比較器112は例えば1つずつ小さくなる数値を順番に検出できるか否かにより、ラインバッファ111を決定する。一定値が埋め込まれる場合、比較器112は、予め定められた回数だけ、同じ数値が検出できるか否かによりラインバッファ111を決定する。

【0079】

また、画像データ送信側デバイス101がパターンジェネレータ302のような、無効域に数値を埋め込む構成を有していない場合でも、無効域が常に"0"又は常に"1"となる送信画像であれば、比較器112はほぼ同様にラインバッファ111を選択することが可能である。

【0080】

図12(a)は、画像データ送信側デバイス101において無効域にライン同期信号を埋め込む構成例を示す。セレクタ301の入力側には送信画像とライン同期信号が入力され、ライン同期信号はセレクタ301のセレクタ線になっている。セレクタ301は、ライン同期信号が有効を示さない状態では送信画像を出力し、ライン同期信号が有効を示す状態になった時だけライン同期信号を出力する。このような構成により、ライン同期信号を画像データ信号に含めることができる。

【0081】

図12(b)は、ライン同期信号が無効域に埋め込まれた画像データ信号の一例を示す図である。上記のように、ライン同期信号から送信画像の有効域までのクロック数は固定である。そして、図12(b)では無効域の値は"0"になっている。このような送信画像とライン同期信号がセレクタ301に入力されると、ライン同期信号に同期して無効域に"1"が埋め込まれた画像データ信号が出力される。ラインバッファ111にはそれぞれ画像データ信号が取り込まれるが、固定のクロック数だけ"0"が取り込まれるものとそうでないものが生じる。よって、比較器112は、ライン同期信号を基準に、1つの"1"が検出されるかどうかと、"0"の数が固定長の数だけ検出されるかどうかにより、ラインバッファ111が正常に画像データ信号を取り込んでいるか否かを判定できる。無効域に"0"でなく"1"が埋め込まれる送信画像の場合、画像データ送信側デバイス101はライン同期信号に同期して"0"を送信画像に埋め込めばよい。

【0082】

図13は、ラインバッファ111が正常に画像データ信号を取り込んだか否かを判定する手順を示すフローチャート図の一例である。

【0083】

比較器112は、ライン同期信号が有効を示すと比較を開始する(S110)。

ライン同期信号が検出された際、比較器112は"1"が検出されたか否かを判定する(S120)。

【0084】

ラインバッファ111から"1"が検出されない場合(S120のNo)、比較器112は不一致信号をセレクタに出力する(S150)。

【0085】

ラインバッファ111から"1"が検出された場合(S120のYes)、比較器112は決まった数の"0"が検出されたか否かを判定する(S130)。

【0086】

ラインバッファ111から決まった数の"0"が検出されない場合(S130のNo)、比較器112は不一致信号をセレクタ113,115に出力する(S150)。

【0087】

ラインバッファ111から決まった数の"0"が検出された場合(S130のYes)、比較器112は一致信号をセレクタ113,115に出力する(S140)。

【0088】

以上のような処理により、画像データ送信側デバイス101がパターンジェネレータ302を有していなくても、画像データ受信側デバイス102は無効域を利用して正常に画像データ信号を取り込むラインバッファ111を選択できる。

【0089】

したがって、以上説明したように、本実施形態のデータ伝送装置100は、温度条件や経年劣化その他の外的要因でデバイス間のI/F状況が変動しても、位相の異なるクロックで取り込んだ複数のラインバッファ111から、正常に画像データ信号を取り込んだラインバッファ111を選択するので、外的要因による変動に追従して同期を確立することができる。開発者がASIC上で実装面積やアナログ的な調整をしたり、LVDS用の専用IPを配置することなく、比較的小規模で安価なコストで、タイミング設計も容易なASICを提供することができる

【符号の説明】

【0090】

100 データ伝送装置

101 画像データ送信側デバイス

102 画像データ受信側デバイス

103 OSC(クロック発振源)

104、105 PLL

106 クロック配信用信号線

107 画像データ出力用FF(フリップフロップ)

108 画像データ送信用出力バッファ

109 画像データ受信用入力バッファ

110 遅延バッファ

111 ラインバッファ

112 比較器

113、115 セレクタ

114 受信画像データ出力線

116 配信信号線

【先行技術文献】

【特許文献】

【0091】

【特許文献1】特開2006−080877号公報

【特許請求の範囲】

【請求項1】

送信側と受信側がクロック信号により同期して送信側から受信側にデータをシリアル送信する半導体デバイスであって、

データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段と、

送信側と受信側に共通のクロック信号を提供するクロック信号提供手段と、

クロック信号に同期して同じデータを送信する複数の伝送路と、

受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段と、

前記複数の遅延クロック信号に同期して、前記複数の伝送路を介して送信されたデータをそれぞれ取り込む複数の受信バッファと、

前記コードを予め定められた規則に基づき検証して前記複数の受信バッファから1つの受信バッファを、前記複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段と、

を有する半導体デバイス。

【請求項2】

前記クロック生成手段の数をX、クロック信号の1クロックサイクルの周期をTとした場合、各クロック生成手段は、T/Xの位相に相当する時間、クロック信号の位相を遅延させる、

ことを特徴とする請求項1記載の半導体デバイス。

【請求項3】

前記複数のラインバッファのバッファ段数は、前記受信バッファがデータの受信を開始してから、前記選択手段が前記複数の受信バッファから1つの受信バッファを選択するまでのクロック数又は前記複数の遅延クロック信号から1つの遅延クロック信号を選択するまでのクロック数以上である、

ことを特徴とする請求項1又は2記載の半導体デバイス。

【請求項4】

前記複数のラインバッファのバッファ段数は、前記選択手段が前記複数の受信バッファから1つの受信バッファを選択した後、又は、前記複数の遅延クロック信号から1つの遅延クロック信号を選択した後、後段のブロックの動作クロックの切り替えに必要なクロック数をさらに加えたクロック数以上である、

ことを特徴とする請求項3記載の半導体デバイス。

【請求項5】

前記コードは、クロック信号に同期して規則的に増大する数値である、ことを特徴とする請求項1〜4いずれか1項記載の半導体デバイス。

【請求項6】

前記コードは、ライン同期信号が埋め込まれた後に続く一定の数値である、ことを特徴とする請求項1〜4いずれか1項記載の半導体デバイス。

【請求項7】

前記選択手段は、検証が成立した前記コードを記憶した前記複数の受信バッファのうち、タイミング的に中央の前記遅延クロック信号が供給されている前記受信バッファを選択する、

ことを特徴とする請求項1〜6いずれか1項記載の半導体デバイス。

【請求項8】

前記選択手段は、フレームゲート信号の有効開始時からラインゲート信号の有効開始時まで、又は、ラインゲート信号の有効終了時からフレームゲート信号の有効終了時までをデータ転送の前記合間として、前記受信バッファに記憶されたデータから前記コードを抽出する、

ことを特徴とする請求項1〜7いずれか1項記載の半導体デバイス。

【請求項9】

前記選択手段は、ライン同期信号が有効を示した時から予め固定の時間をデータ転送の前記合間として、前記受信バッファに記憶されたデータから前記コードを抽出する、

ことを特徴とする請求項1〜7いずれか1項記載の半導体デバイス。

【請求項10】

請求項1〜9いずれか1項記載の半導体デバイスを搭載した画像処理装置。

【請求項1】

送信側と受信側がクロック信号により同期して送信側から受信側にデータをシリアル送信する半導体デバイスであって、

データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段と、

送信側と受信側に共通のクロック信号を提供するクロック信号提供手段と、

クロック信号に同期して同じデータを送信する複数の伝送路と、

受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段と、

前記複数の遅延クロック信号に同期して、前記複数の伝送路を介して送信されたデータをそれぞれ取り込む複数の受信バッファと、

前記コードを予め定められた規則に基づき検証して前記複数の受信バッファから1つの受信バッファを、前記複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段と、

を有する半導体デバイス。

【請求項2】

前記クロック生成手段の数をX、クロック信号の1クロックサイクルの周期をTとした場合、各クロック生成手段は、T/Xの位相に相当する時間、クロック信号の位相を遅延させる、

ことを特徴とする請求項1記載の半導体デバイス。

【請求項3】

前記複数のラインバッファのバッファ段数は、前記受信バッファがデータの受信を開始してから、前記選択手段が前記複数の受信バッファから1つの受信バッファを選択するまでのクロック数又は前記複数の遅延クロック信号から1つの遅延クロック信号を選択するまでのクロック数以上である、

ことを特徴とする請求項1又は2記載の半導体デバイス。

【請求項4】

前記複数のラインバッファのバッファ段数は、前記選択手段が前記複数の受信バッファから1つの受信バッファを選択した後、又は、前記複数の遅延クロック信号から1つの遅延クロック信号を選択した後、後段のブロックの動作クロックの切り替えに必要なクロック数をさらに加えたクロック数以上である、

ことを特徴とする請求項3記載の半導体デバイス。

【請求項5】

前記コードは、クロック信号に同期して規則的に増大する数値である、ことを特徴とする請求項1〜4いずれか1項記載の半導体デバイス。

【請求項6】

前記コードは、ライン同期信号が埋め込まれた後に続く一定の数値である、ことを特徴とする請求項1〜4いずれか1項記載の半導体デバイス。

【請求項7】

前記選択手段は、検証が成立した前記コードを記憶した前記複数の受信バッファのうち、タイミング的に中央の前記遅延クロック信号が供給されている前記受信バッファを選択する、

ことを特徴とする請求項1〜6いずれか1項記載の半導体デバイス。

【請求項8】

前記選択手段は、フレームゲート信号の有効開始時からラインゲート信号の有効開始時まで、又は、ラインゲート信号の有効終了時からフレームゲート信号の有効終了時までをデータ転送の前記合間として、前記受信バッファに記憶されたデータから前記コードを抽出する、

ことを特徴とする請求項1〜7いずれか1項記載の半導体デバイス。

【請求項9】

前記選択手段は、ライン同期信号が有効を示した時から予め固定の時間をデータ転送の前記合間として、前記受信バッファに記憶されたデータから前記コードを抽出する、

ことを特徴とする請求項1〜7いずれか1項記載の半導体デバイス。

【請求項10】

請求項1〜9いずれか1項記載の半導体デバイスを搭載した画像処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−120071(P2012−120071A)

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願番号】特願2010−269985(P2010−269985)

【出願日】平成22年12月3日(2010.12.3)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願日】平成22年12月3日(2010.12.3)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]