半導体デバイスの製造方法

【課題】III族窒化物半導体の複数の半導体部材を成長させる際の結晶性を向上できる半導体デバイスの製造方法を提供する。

【解決手段】下地基板10の上に第1バッファー層30を形成する第1バッファー層形成工程と、前記第1バッファー層30の上に、複数の開口を有するマスク40を形成するマスク形成工程と、前記第1バッファー層30の表面において前記複数の開口により露出された複数の領域に、III族窒化物半導体の複数の第2バッファー層60a、60bを形成する第2バッファー層形成工程と、前記複数の第2バッファー層60a、60bの上に、III族窒化物半導体の複数の半導体部材を成長させる成長工程とを備える。

【解決手段】下地基板10の上に第1バッファー層30を形成する第1バッファー層形成工程と、前記第1バッファー層30の上に、複数の開口を有するマスク40を形成するマスク形成工程と、前記第1バッファー層30の表面において前記複数の開口により露出された複数の領域に、III族窒化物半導体の複数の第2バッファー層60a、60bを形成する第2バッファー層形成工程と、前記複数の第2バッファー層60a、60bの上に、III族窒化物半導体の複数の半導体部材を成長させる成長工程とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイスの製造方法に関する。

【背景技術】

【0002】

従来から、窒化ガリウム系化合物半導体を選択的に成長させる技術が提案されている(特許文献1参照)。すなわち、下地基板の上に、複数の開口を有するマスクを形成し、下地基板において複数の開口により露出された複数の領域から、複数の窒化ガリウム系化合物半導体を成長させている。これにより、複数の窒化ガリウム系化合物半導体が互いに分離された状態で成長するので、下地基板と窒化ガリウム系化合物半導体との熱膨張係数の差に基づく応力が低減され、複数の窒化ガリウム系化合物半導体のそれぞれにクラックが発生することが低減される。

【0003】

また、下地基板の表面を加工した後に、GaN系半導体結晶を成長させる技術が提案されている(特許文献2参照)。すなわち、下地基板の表面を凹凸状に加工した後に、凸部の上方部からGaN系半導体結晶を横方向に成長させる。これにより、GaN系半導体結晶が凹凸面を覆うようになる。

【0004】

一方、下地基板の上にMBE法によりクロム層を成膜し、そのクロム層を窒化する技術が提案されている(非特許文献1参照)。

【特許文献1】特開平11−186178号公報

【特許文献2】特開2000−331947号公報

【非特許文献1】李旭鉉、外7名、「MBE法による低温CrxNバッファ層を用いたGaNの成長」、応用物理学会予稿集、364ペ−ジ

【発明の開示】

【発明が解決しようとする課題】

【0005】

仮に、特許文献1の技術において、下地基板の上にバッファー層を形成した後に、複数の開口を有するマスクを形成し、下地基板において複数の開口により露出された複数の領域から、複数の窒化ガリウム系化合物半導体を成長させたとする。この場合、下地基板と複数の窒化ガリウム系化合物半導体との熱膨張係数の差に基づく内部応力や原子間距離の差に基づく格子不整合を、バッファー層で緩和させることができる。

【0006】

しかし、バッファー層が下地基板の表面全体に渡って形成されるので、バッファー層の特定箇所に存在する転位がバッファー層内を表面全体に渡って伝播する可能性がある。これにより、バッファー層自体の結晶性が悪化するので、その上に成長させる複数の窒化ガリウム系化合物半導体の結晶性も悪化する。

【0007】

一方、特許文献2の技術では、GaN系半導体結晶が横方向成長して凹凸面を覆うので、GaN系半導体結晶の上面が平坦になる。

【0008】

ここで、仮に、GaN系半導体結晶を切削刃を用いてスクライビングすることにより、GaN系半導体結晶を複数の半導体部材に分離させたとする。この場合、スクライビングの刃の切削面に対する被切削面(GaN系半導体結晶の上面)の成す角度が大きいので、スクライビングの刃とGaN系半導体結晶との接触面積が小さくなりやすく、スクライビングの刃からの応力が限られた部分に集中しやすい。このため、GaN系半導体結晶が大きなダメージを受けやすくなるという問題が生じる。また、レーザを用いてスクライビングを行うこと(レーザスクライビング)により、GaN系半導体結晶を複数の半導体部材に分離させたとする。この場合、スクライビングで形成する溝を深くするために、レーザの出力を高くする必要がある。このため、GaN系半導体結晶が大きなダメージを受けやるという問題が生じる。したがって、スクライビングにより分離されて得られる複数の半導体部材の側面近傍において、結晶が受けるダメージや結晶性の乱れが大きくなるので、複数の半導体部材を用いて製造される半導体デバイスの特性も悪化するという問題が発生する。

【0009】

本発明の第1の目的は、III族窒化物半導体の複数の半導体部材を成長させる際の結晶性を向上できる半導体デバイスの製造方法を提供することにある。

【0010】

本発明の第2の目的は、III族窒化物半導体の複数の半導体部材を分離させた際の側面近傍において、結晶が受けるダメージや結晶性の乱れを低減できる半導体デバイスの製造方法を提供することにある。

【課題を解決するための手段】

【0011】

本発明の第1側面に係る半導体デバイスの製造方法は、下地基板の上に第1バッファー層を形成する第1バッファー層形成工程と、前記第1バッファー層の上に、複数の開口を有するマスクを形成するマスク形成工程と、前記第1バッファー層の表面において前記複数の開口により露出された複数の領域に、III族窒化物半導体の複数の第2バッファー層を形成する第2バッファー層形成工程と、前記複数の第2バッファー層の上に、III族窒化物半導体の複数の半導体部材を成長させる成長工程とを備えたことを特徴とする。

【0012】

本発明の第2側面に係る半導体デバイスの製造方法は、下地基板の上に金属層を形成する金属層形成工程と、前記金属層の上に、複数の開口を有するマスクを形成するマスク形成工程と、前記金属層において前記複数の開口により露出された複数の領域を窒化することにより、金属窒化物の複数の第1バッファー層を形成する窒化工程と、前記複数の第1バッファー層の上に、III族窒化物半導体の複数の第2バッファー層を形成する第2バッファー層形成工程と、前記複数の第2バッファー層の上に、III族窒化物半導体の複数の半導体部材を成長させる成長工程とを備えたことを特徴とする。

【0013】

本発明の第3側面に係る半導体デバイスの製造方法は、下地基板に、断面においてV字の形状を有する溝を形成する溝形成工程と、前記下地基板の上に、前記溝に沿ってくぼんだ第1凹部を上面に有する中間層を形成する中間層形成工程と、前記中間層の上に、III族窒化物半導体の半導体層を成長させる成長工程とを備え、前記半導体層は、前記第1凹部に沿ってくぼんだ第2凹部を上面に有することを特徴とする。

【0014】

本発明の第4側面に係る半導体デバイスの製造方法は、下地基板に、中間層を形成する中間層形成工程と、前記下地基板及び前記中間層に、断面においてV字の形状を有する溝を形成するとともに、前記中間層を複数の中間部材にする溝形成工程と、前記複数の中間部材の上に、III族窒化物半導体の半導体層を成長させる成長工程とを備え、前記半導体層は、前記溝に沿ってくぼんだ凹部を上面に有することを特徴とする。

【発明の効果】

【0015】

本発明によれば、III族窒化物半導体の複数の半導体部材を成長させる際の結晶性を向上できる。

【0016】

また、本発明によれば、III族窒化物半導体の複数の半導体部材を分離させた際の側面近傍において、結晶が受けるダメージや結晶性の乱れを低減できる。

【発明を実施するための最良の形態】

【0017】

本明細書において、「膜」は、連続した膜でもよいし、不連続な膜でもよいものとする。「膜」は、厚さを持って形成されている状態を表す。

【0018】

本発明は、LED(Light Emitting Diode)などの半導体デバイスに適用可能な複数の半導体部材を選択的に成長させるための方法に関する。

【0019】

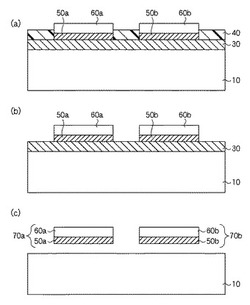

本発明の第1実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を、図1〜図4を用いて説明する。図1、図2及び図4は、半導体デバイスの製造方法を示す工程断面図である。図3は、図2(b)に示す工程により得られた構造体の平面図である。以下では、III族窒化物半導体の一例として、窒化ガリウムを中心に説明するが、他のIII族窒化物半導体に関しても同様である。

【0020】

図1(a)に示す工程では、下地基板10を準備する。下地基板10の材料は、例えば、Al2O3(サファイア)である。

【0021】

図1(b)に示す工程では、スパッタ法などにより、下地基板10の上にクロム層(金属層)20を成膜する。成膜されるクロム層20の厚さは、例えば、20nmである。

【0022】

ここで、クロム層20を成膜するのは、その後に窒化して形成するクロム窒化物の原子間距離が窒化ガリウムに近く、窒化ガリウムとの格子不整合が小さいためである。

【0023】

図1(c)に示す工程では、クロム層20を1000℃以上1300℃以下(1273K以上1573K以下)の温度で窒化することにより、クロム窒化物(金属窒化物)の第1バッファー層30を形成する。すなわち、下地基板10を1000℃以上1300℃の温度に加熱するとともに、クロム層20の表面をアンモニアガス雰囲気にする。これにより、クロム層20が窒化して第1バッファー層30になる。

【0024】

ここで、クロムの結晶構造が立方晶系であるのに対して、クロム窒化物の結晶構造が六方晶系である。クロム層20を窒化した際に、クロムの結晶格子がクロム窒化物の結晶格子へと再配列するためには、一定以上のエネルギーが必要であると考えられる。

【0025】

仮に、クロム層20の窒化温度が1000℃未満であると、クロムの結晶格子がクロム窒化物の結晶格子へと再配列するために十分なエネルギーがクロム層20に与えられないので、窒化されて形成される第1バッファー層30の結晶性が悪くなる。

【0026】

それに対して、本実施形態では、クロム層20の窒化温度が1000℃以上であるので、クロムの結晶格子がクロム窒化物の結晶格子へと再配列するために十分なエネルギーがクロム層20に与えられる。これにより、クロム層20が窒化されて形成されるクロム窒化物の第1バッファー層30の結晶性が向上する。

【0027】

だだし、過度な高温で窒化することは、熱負荷増大による装置の部材劣化の問題が生じるとともに、形成された第1バッファー層と下地基板との相互熱拡散などの問題が生じる。このため、窒化温度は1300℃以下が好ましい。

【0028】

また、第1バッファー層30の材料であるクロム窒化物は、下地基板(サファイア)と窒化ガリウムとの間の原子間距離を有するので、下地基板との格子不整合が小さい。この点からも、第1バッファー層30の結晶性が向上する。

【0029】

図2(a)に示す工程では、第1バッファー層30の上にマスク層40iを成膜する。成膜されるマスク層40iの厚さは、例えば、100nmである。マスク層40iの材料は、例えば、酸化シリコン及び窒化シリコンのいずれかである。

【0030】

ここで、図1(a)〜図2(a)の工程は、同じチャンバ内で連続的に行うことが好ましい。この場合、各層の界面に自然酸化膜が形成されることを低減できる。

【0031】

図2(b)に示す工程では、リソグラフィ法などにより、マスク層40iに複数の開口40a,40b,・・・を形成して、マスク40を形成する。例えば、図3に示すように、第1バッファー層30の上に、複数の開口40a,40b,・・・を有するマスク40が形成される。

【0032】

ここで、複数の開口40a,40b,・・・の寸法は、LEDなどの半導体デバイスに適した大きさに対応したものとなっている。また、複数の開口40a,40b,・・・の形状は、LEDなどの半導体デバイスに適した形状に対応したものとなっている。なお、複数の開口40a,40b,・・・のそれぞれの形状は、下地基板10の上面に垂直な方向から見た場合に、矩形状以外の形状であっても良く、例えば、三角形、円等であっても良い。

【0033】

図2(c)に示す工程では、HVPE法やMOCVD法などにより、第1バッファー層30の表面において複数の開口40a,40b,・・・により露出された複数の領域30a,30b,・・・から、窒化ガリウムの複数の第2バッファー層50a,50b,・・・を成長させる。

【0034】

ここで、複数の第2バッファー層50a,50b,・・・は、それぞれ、例えば、GaNの単結晶体、多結晶体又はアモルファス体で構成されうる。複数の第2バッファー層50a,50b,・・・の厚さは、それぞれ、数十Å〜数十μmであることが好ましい。複数の第2バッファー層50a,50b,・・・の成長温度は、それぞれ、900℃付近であることが好ましい。複数の第2バッファー層50a,50b,・・・は、それぞれ、いわゆる低温バッファー層である。

【0035】

図4(a)に示す工程では、HVPE法やMOCVD法などにより、複数の第2バッファー層50a,50b,・・・の上に、窒化ガリウムの複数の半導体部材60a,60b,・・・を成長させる。

【0036】

ここで、複数の半導体部材60a,60b,・・・は、それぞれ、例えば、GaNの単結晶体で構成されうる。複数の半導体部材60a,60b,・・・の厚さは、それぞれ、数十Å〜数十μmであることが好ましい。複数の半導体部材50a,50b,・・・の成長温度は、それぞれ、複数の第2バッファー層50a,50b,・・・の成長温度(900℃付近)よりも高い温度である約1100℃になる。

【0037】

また、複数の第2バッファー層50a,50b,・・・は、第1バッファー層30の表面においてマスク40の複数の開口40a,40b,・・・により露出された複数の領域30a,30b,・・・に形成されている。マスク40の結晶方位が複数の第2バッファー層50a,50b,・・・の結晶方位と異なるので、複数の第2バッファー層50a,50b,・・・のいずれかの特定箇所に存在する転位は、他の第2バッファー層50a,50b,・・・に伝播しにくい。これにより、複数の第2バッファー層50a,50b,・・・は、全体として、その結晶性が向上する。この結果、複数の第2バッファー層50a,50b,・・・の上に成長させる複数の半導体部材60a,60b,・・・の結晶性も向上する。すなわち、III族窒化物半導体の複数の半導体部材を成長させる際の結晶性を向上できる。

【0038】

さらに、第1バッファー層30の材料であるクロム窒化物は、下地基板(サファイア)と窒化ガリウムとの間の原子間距離を有するので、窒化ガリウムとの格子不整合が小さい。例えば、サファイアの30°回転した(0001)面方向の原子間距離は、2.747Åである。窒化ガリウムの(0001)面方向の原子間距離は、3.188Åである。クロム窒化物の(111)面方向の原子間距離は、2.927Åであり、サファイアの原子間距離と窒化ガリウムの原子間距離との間の値である。これにより、第1バッファー層30の上に成長する複数の第2バッファー層50a,50b,・・・及び複数の半導体部材60a,60b,・・・は、結晶性が向上する。

【0039】

また、第1バッファー層30の材料であるクロム窒化物は、下地基板(サファイア)と窒化ガリウムとの間の熱膨張係数を有する。例えば、サファイアの(0001)面方向の熱膨張係数は、7.50である。窒化ガリウムの(0001)面方向の熱膨張係数は、5.45である。クロム窒化物の(111)面方向の熱膨張係数は、6.00であり、サファイアの熱膨張係数と窒化ガリウムの熱膨張係数との間の値である。これにより、下地基板10と、複数の第2バッファー層50a,50b,・・・及び複数の半導体部材60a,60b,・・・との間の熱膨張係数の差に基づいて発生する内部応力を第1バッファー層30で緩和することができる。このため、複数の第2バッファー層50a,50b,・・・及び複数の半導体部材60a,60b,・・・のそれぞれの内部応力が低減されるので、この点からも、複数の第2バッファー層50a,50b,・・・及び複数の半導体部材60a,60b,・・・の結晶性が向上する。

【0040】

図4(b)に示す工程では、マスク40を除去する。例えば、マスク40を、選択的にエッチングして除去する。例えば、マスク40の材料が酸化シリコンである場合、HF溶液あるいはBOE(バッファードHF)溶液を用いることにより、マスク40を選択的にエッチングすることができる。

【0041】

なお、マスク40を切削刃あるいはレーザを用いてスクライビングすることにより、マスク40を機械的あるいは物理的に除去してもよい。

【0042】

図4(c)に示す工程では、第1バッファー層30を選択的にエッチングして、複数の半導体部材60a,60b,・・・を下地基板10から分離するとともに互いに分離する。これにより、複数の半導体デバイス70a,70b,・・・を得ることができる。

【0043】

ここで、複数の半導体デイバス70a,70b,・・・は、それぞれ、第2バッファー層50a,50b,・・・と半導体部材60a,60b,・・・とを含む。複数の半導体デバイス70a,70b,・・・の形状は、それぞれ、複数の開口40a,40b,・・・の形状に対応して、LEDなどの半導体デバイスに適した大きさになっている。複数の半導体デバイス70a,70b,・・・の寸法は、複数の開口40a,40b,・・・の寸法に対応して、LEDなどの半導体デバイスに適した大きさになっている。

【0044】

このように、図1(a)〜図4(a)の工程を行った結果、例えば、図5のSEM写真に示されるような試料が得られた。図5のSEM写真では、下地基板10の上面に垂直な方向から見た場合に、複数の半導体部材60a,60b,・・・の寸法が、それぞれ、縦約1mm、横約1mmになっている。また、複数の半導体部材60a,60b,・・・の間に、マスク40が格子状に形成されている。複数の半導体部材60a,60b,・・・の間の部分を断面観察した結果、図6及び図7に示すように、傾斜した側面を有している。そこで、図2(b)の工程で形成するマスク40の複数の開口40a,40b,・・・の寸法は、半導体部材60a,60b,・・・の側面の傾斜角を考慮して決められている。

【0045】

図5〜図7に示す試料に対してさらに図4(b)、(c)の工程を行った結果得られた複数の半導体部材の1つに対してX線回折(XRD)分析を行った結果を、図8に示す。すなわち、半導体部材のXRDプロファイルにおける(0002)面のピークの半値幅を求めたところ、383[arcsec]であった。図8には、この結果を、「本実施形態」として棒グラフで示してある。

【0046】

また、図8には、比較のために、特許文献1に示される第1実施例の方法により複数の半導体部材を得た場合について、予想される値を「特許文献1」として棒グラフで示してある。特許文献1に示される第1実施例の方法によれば、下地基板の上に複数の開口を有するマスクを形成した後に、下地基板において複数の開口により露出された複数の領域から、複数の半導体部材を成長させることになる。

【0047】

この場合、下地基板(サファイア)と複数の半導体部材(窒化ガリウム)との間で熱膨張係数の差や原子間距離の差が大きいので、成長させた複数の半導体部材(窒化ガリウム)の結晶性が「本実施形態」に比べて悪くなることが予想される。よって、図8では、「特許文献1」のXRD半値幅が「本実施形態」のXRD半値幅よりも大きいものとしている。

【0048】

さらに、図8には、比較のために、特許文献1に示された方法に対して非特許文献1で示された低温CrxNバッファ層を適用した場合について、予想される値を「非特許文献1」として棒グラフで示してある。すなわち、この組み合わせによれば、下地基板の上に低温CrxNバッファ層を形成し、低温CrxNバッファ層の上に複数の開口を有するマスクを形成した後に、下地基板において複数の開口により露出された複数の領域から、複数の半導体部材を成長させることになる。

【0049】

この場合、下地基板と複数の窒化ガリウム系化合物半導体との熱膨張係数の差に基づく内部応力や原子間距離の差に基づく格子不整合を、バッファー層で緩和させることができる。これにより、成長させた複数の半導体部材(窒化ガリウム)の結晶性が「特許文献1」に比べて良くなることが予想される。よって、図8では、「非特許文献1」のXRD半値幅が「特許文献1」のXRD半値幅よりも小さいものとしている。

【0050】

しかし、バッファー層が下地基板の表面全体に渡って形成されることになるので、バッファー層の特定箇所に存在する転位がバッファー層内を表面全体に渡って伝播する可能性がある。これにより、バッファー層自体の結晶性が悪化するので、その上に成長させた複数の半導体部材(窒化ガリウム)の結晶性が「本実施形態」に比べて悪くなることが予想される。よって、図8では、「非特許文献1」のXRD半値幅が「本実施形態」のXRD半値幅よりも大きいものとしている。

【0051】

次に、「非特許文献1」と「本実施形態」との予測される関係を、窒化温度に対応付けて比較したものを図9に示す。図9に示す関係は、本発明者が発明者となっている特願2006−272324の図13に基づいて予測されたものである。

【0052】

図9に示すように、窒化温度が1000℃から低くなるにしたがって、XRD半値幅がW1から急激に大きくなり結晶性が悪くなることが予測される。

【0053】

ここで、非特許文献1では、窒化温度が低温T2(500℃〜600℃)であり、1000℃未満である。図9によれば、窒化温度T2に対するXRD半値幅は、W1より大きいW2であると予測される。

【0054】

それに対して、本実施形態では、窒化温度が1000℃以上1300℃以下の温度T1である。窒化温度T1に対するXRD半値幅は、W1より小さい383[arcsec]である。

【0055】

次に、本発明の第2実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を、図10〜図13を用いて説明する。図10、図12及び図13は、半導体デバイスの製造方法を示す工程断面図である。図11は、図10(c)に示す工程により得られた構造体の平面図である。以下では、III族窒化物半導体の一例として、窒化ガリウムを中心に説明するが、他のIII族窒化物半導体に関しても同様である。なお、以下では、第1実施形態と異なる部分を中心に説明し、同様の部分の説明を省略する。

【0056】

図10(a)に示す工程では、クロム層120の上にマスク層40iを成膜する。

【0057】

図10(b)に示す工程では、リソグラフィ法などにより、マスク層40iに複数の開口40a,40b,・・・を形成して、マスク40を形成する。

【0058】

図10(c)に示す工程では、クロム層120において複数の開口40a,40b,・・・により露出された複数の領域120a,120b,・・・を、1000℃以上1300℃以下の温度で窒化することにより、複数の第1バッファー層130a,130b,・・・を形成する。例えば、図11に示すように、クロム層120の上に、複数の開口40a,40b,・・・を有するマスク40が形成される。

【0059】

図12(a)に示す工程では、複数の開口40a,40b,・・・により露出された複数の第1バッファー層130a,130b,・・・から、窒化ガリウムの複数の第2バッファー層50a,50b,・・・を成長させる。

【0060】

図12(b)に示す工程では、HVPE法やMOCVD法などにより、複数の第2バッファー層150a,150b,・・・の上に、窒化ガリウムの複数の半導体部材160a,160b,・・・を成長させる。

【0061】

図13(a)に示す工程では、マスク40を除去する。例えば、マスク40を、選択的にエッチングして除去する。

【0062】

図13(b)に示す工程では、クロム層120及び複数の第1バッファー層130a,130b,・・・を選択的にエッチングして、複数の半導体部材160a,160b,・・・を下地基板10から分離するとともに互いに分離する。これにより、複数の半導体デバイス170a,170b,・・・を得ることができる。

【0063】

このように、クロム層を窒化する前にマスクを形成して、クロム層の表面において複数の開口により露出された複数の領域を、選択的に窒化している。このクロム層の結晶方位は、第1バッファー層の結晶方位と異なる。これにより、第1バッファー層を介して内部応力が隣接する半導体部材に伝播することを低減できる。

【0064】

次に、本発明の第3実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を、図14〜図17を用いて説明する。図14、図16及び図17は、半導体デバイスの製造方法を示す工程断面図である。図15は、図14(b)に示す工程により得られた構造体の平面図である。以下では、III族窒化物半導体の一例として、窒化ガリウムを中心に説明するが、他のIII族窒化物半導体に関しても同様である。なお、以下では、第1実施形態と異なる部分を中心に説明し、同様の部分の説明を省略する。

【0065】

図14(a)に示す工程では、下地基板210に、断面においてV字の形状を有する溝を形成する。例えば、下地基板210をスクライビングすることにより、溝210a,210b,210c,・・・を形成する。このとき、レーザあるいは切削刃を用いてスクライビングすることができる。

【0066】

ここで、溝210a,210b,210c,・・・において対向する第1の面210a1,210b1,210c1,・・・と第2の面210a2,210b2,210c2,・・・とは、いずれも、スクライビングの刃の切削面に沿った方向に延びている。

【0067】

図14(b)に示す工程では、溝210a,210b,210c,・・・が形成された下地基板210の上に、クロム層220を成膜する。ここで、クロム層220は、複数の第1クロム層220a,220b,・・・と、複数の第2クロム層221a,221b,221c,・・・とを含む。すなわち、溝210a,210b,210c,・・・が形成されていない領域に、複数の第1クロム層220a,220b,・・・が成膜され、溝210a,210b,210c,・・・が形成されている領域に、複数の第2クロム層221a,221b,221c,・・・が成膜される。

【0068】

ここで、溝210a,210b,210c,・・・が形成される領域に成膜される第2クロム層221a,221b,221c,・・・は、第1クロム層220a,220b,・・・と結晶方位が異なっている。

【0069】

図14(c)に示す工程では、クロム層220を1000℃以上1300℃以下の温度で窒化することにより、下地基板210の上に、溝210a,210b,210c,・・・に沿ってくぼんだ第1凹部231a1,231b1,231c1,・・・を上面に有するクロム窒化物の中間層230を形成する。ここで、中間層230は、複数の第1中間層230a,230b,・・・と、複数の第2中間層231a,231b,231c,・・・とを含む。すなわち、溝210a,210b,210c,・・・が形成されていない複数の領域に、複数の第1中間層230a,230b,・・・が形成され、溝210a,210b,210c,・・・が形成されている領域に、複数の第2中間層231a,231b,231c,・・・が形成される(図15参照)。

【0070】

ここで、複数の第2中間層231a,231b,231c,・・・のそれぞれの結晶方位は、複数の第1中間層230a,230b,・・・のそれぞれの結晶方位と異なる。これにより、基板から受ける応力の向きは第1中間層と第2中間層とで異なるため、複数の第2中間層231a,231b,231c,・・・のそれぞれは、複数の第1中間層230a,230b,・・・の間に働く内部応力を緩和することができる。

【0071】

図16(a)に示す工程では、中間層230の上に、低温バッファー層250を形成する。ここで、低温バッファー層250は、複数の第1低温バッファー層250a,250b,・・・と、複数の第2低温バッファー層251a,251b,251c,・・・とを含む。すなわち、溝210a,210b,210c,・・・が形成されていない複数の領域に、複数の第1低温バッファー層250a,250b,・・・が形成され、溝210a,210b,210c,・・・が形成されている領域に、複数の第2低温バッファー層251a,251b,251c,・・・が形成される。

【0072】

ここで、複数の第2低温バッファー層251a,251b,251c,・・・のそれぞれの結晶方位は、複数の第1低温バッファー層250a,250b,・・・のそれぞれの結晶方位と異なる。これにより、基板から受ける応力の向きは第1低温バッファー層と第2低温バッファー層とで異なるため、複数の第2低温バッファー層251a,251b,251c,・・・のそれぞれは、複数の第1低温バッファー層250a,250b,・・・の間に働く内部応力を緩和することができる。

【0073】

そして、低温バッファー層250の上に、窒化ガリウムの半導体層260を成長させる。ここで、半導体層260は、溝210a,210b,210c,・・・に沿ってくぼんだ第2凹部261a1,261b1,261c1,・・・を上面に有する。

【0074】

ここで、第2凹部261a1,261b1,261c1,・・・において対向する第1の面261a11,261b11,261c11,・・・と第2の面261a12,261b12,261c12,・・・とは、いずれも、スクライビングの刃の切削面に沿った方向に延びている。この結果、半導体層260を切削刃を用いてスクライビングすることにより、半導体層260を複数の半導体部材に分離させる際に、スクライビングの刃の切削面に対する被切削面(半導体層260の上面)の成す角度を小さくできるので、スクライビングの刃と半導体層260との接触面積を大きくでき、スクライビングの刃からの応力が限られた部分に集中することを避けることができる。また、レーザを用いてスクライビングを行うこと(レーザスクライビング)により、GaN系半導体結晶を複数の半導体部材に分離させる際に、スクライビングで形成する溝を浅くすることができるので、レーザの出力を低くすることが可能となる。したがって、スクライビングより分離されて得られる複数の半導体部材の側面近傍において、結晶が受けるダメージを小さくすることができ、かつ結晶性の乱れを低減できるので、複数の半導体部材を用いて製造される半導体デバイスの特性を向上できる。すなわち、III族窒化物半導体の複数の半導体部材を分離させた際の側面近傍において、結晶が受けるダメージや結晶性の乱れを低減できる。

【0075】

半導体層260は、複数の第1半導体層260a,260b,・・・と、複数の第2半導体層261a,261b,261c,・・・とを含む。すなわち、溝210a,210b,210c,・・・が形成されていない複数の領域に、複数の第1半導体層260a,260b,・・・が形成され、溝210a,210b,210c,・・・が形成されている領域に、複数の第2半導体層261a,261b,261c,・・・が形成される。

【0076】

ここで、複数の第2半導体層261a,261b,261c,・・・のそれぞれの結晶方位は、複数の第1半導体層260a,260b,・・・のそれぞれの結晶方位と異なる。これにより、基板から受ける応力の向きは第1半導体層と第2半導体層とで異なるため、複数の第2半導体層261a,261b,261c,・・・のそれぞれは、複数の第1半導体層260a,260b,・・・の間に働く内部応力を緩和することができる。

【0077】

このようにして、例えば、図18及び図19のSEM写真で示される試料が得られた。図18は、溝が形成されている領域の近傍を、下地基板の表面に垂直な方向から観察したSEM写真である。図19は、溝が形成されている領域の近傍を、下地基板の表面に沿った方向から観察したSEM写真である。図18及び図19に示されるように、第2凹部において対向する第1の面と第2の面とは、いずれも、スクライビングの刃の切削面に沿った方向に延びている。

【0078】

図16(b)に示す工程では、複数の第2半導体層261a,261b,261c,・・・、複数の第2低温バッファー層251a,251b,251c,・・・、及び複数の第2中間層231a,231b,231c,・・・をスクライビングすることにより、複数の第2半導体層261a,261b,261c,・・・、複数の第2低温バッファー層251a,251b,251c,・・・、及び複数の第2中間層231a,231b,231c,・・・を除去する。

【0079】

ここで、上述のように、スクライビングの刃の切削面に対する被切削面(半導体層260の上面)の成す角度が小さい状態でスクライビングするので、スクライビングの刃と半導体層260との接触面積が大きくなっている。

【0080】

図17に示す工程では、複数の第1中間層230a,230b,・・・を選択的にエッチングすることにより、複数の半導体部材260a,260b,・・・を下地基板210から分離するとともに互いに分離する。これにより、複数の半導体デバイス270a,270b,・・・を得ることができる。

【0081】

次に、本発明の第4実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を、図20及び図21を用いて説明する。図20及び図21は、半導体デバイスの製造方法を示す工程断面図である。以下では、III族窒化物半導体の一例として、窒化ガリウムを中心に説明するが、他のIII族窒化物半導体に関しても同様である。なお、以下では、第3実施形態と異なる部分を中心に説明し、同様の部分の説明を省略する。

【0082】

図20(a)に示す工程では、下地基板310の上に、中間層330を形成する。なお、中間層330は、図1(a)〜(c)と同様の工程により形成されても良い。

【0083】

図20(b)に示す工程では、下地基板310及び中間層330をスクライビングすることにより、下地基板310及び中間層330に、断面においてV字の形状を有する溝310a,310b,310c,・・・を形成するとともに、中間層330を複数の中間部材330a,330b,・・・にする。ここで、溝310a,310b,310c,・・・が形成されている領域に第2中間層が形成されていない。このとき、レーザあるいは切削刃を用いてスクライビングすることができる。

【0084】

ここで、溝310a,310b,310c,・・・は、下地基板310の強度を十分に確保した状態で深さを大きくしやすい点で、第3実施形態と異なる。

【0085】

図20(c)に示す工程では、複数の中間部材330a,330b,・・・の上に、低温バッファー層350を形成する。ここで、低温バッファー層350は、複数の第1低温バッファー層350a,350b,・・・と、複数の第2低温バッファー層351a,351b,351c,・・・とを含む。

【0086】

ここで、複数の第1低温バッファー層350a,350b,・・・が複数の中間部材(バッファー層)330a,330b,・・・を間にして下地基板310の上に配されているのに対して、複数の第2低温バッファー層351a,351b,351c,・・・は、下地基板310に直接的に接している。これにより、複数の第2低温バッファー層351a,351b,351c,・・・のそれぞれの結晶性は、複数の第1低温バッファー層350a,350b,・・・のそれぞれの結晶性と異なる。複数の第2低温バッファー層351a,351b,351c,・・・は、例えば、多結晶又はアモルファスとして形成することができる。したがって、複数の第2低温バッファー層351a,351b,351c,・・・のそれぞれは、複数の第1低温バッファー層350a,350b,・・・の間に働く内部応力を緩和することができる。

【0087】

そして、低温バッファー層350の上に、窒化ガリウムの半導体層360を成長させる。ここで、半導体層360は、溝310a,310b,310c,・・・に沿ってくぼんだ凹部361a1,361b1,361c1,・・・を上面に有する。半導体層360は、複数の第1半導体層360a,360b,・・・と、複数の第2半導体層361a,361b,361c,・・・とを含む。

【0088】

ここで、複数の第2低温バッファー層351a,351b,351c,・・・のそれぞれの結晶性が複数の第1低温バッファー層350a,350b,・・・のそれぞれの結晶性と異なることに対応して、複数の第2半導体層361a,361b,361c,・・・のそれぞれの結晶性は、複数の第1半導体層360a,360b,・・・のそれぞれの結晶性と異なる。複数の第2半導体層361a,361b,361c,・・・は、例えば、多結晶又はアモルファスとして形成することができる。したがって、複数の第2半導体層361a,361b,361c,・・・のそれぞれは、複数の第1半導体層360a,360b,・・・の間に働く内部応力を緩和することができる。

【0089】

このようにして、例えば、図22及び図23のSEM写真で示される試料が得られた。図22は、溝が形成されている領域の近傍を、下地基板の表面に垂直な方向から観察したSEM写真である。図23は、溝が形成されている領域の近傍を、下地基板の表面に沿った方向から観察したSEM写真である。図22及び図23に示されるように、凹部において対向する第1の面と第2の面とは、いずれも、スクライビングの刃の切削面に沿った方向に延びている。

【0090】

図21(a)に示す工程では、複数の第2半導体層361a,361b,361c,・・・及び複数の第2低温バッファー層351a,351b,351c,・・・をスクライビングすることにより、複数の第2半導体層361a,361b,361c,・・・及び複数の第2低温バッファー層351a,351b,351c,・・・を除去する。ここで、複数の中間部材330a,330b,・・・の傾斜した側面が露出されている。

【0091】

図21(b)に示す工程では、複数の中間部材330a,330b,・・・を選択的にエッチングすることにより、複数の第1半導体層360a,360b,・・・を下地基板310から分離するとともに互いに分離する。これにより、複数の半導体デバイス370a,370b,・・・を得ることができる。

【0092】

ここで、複数の中間部材330a,330b,・・・は、その傾斜した側面が露出されているので、エッチング溶液との接触面積が大きい。これにより、第3実施形態に比べて、複数の中間部材330a,330b,・・・を短時間にエッチングすることができる。

【0093】

なお、下地基板は、Si、SiC、GaAsなどの単結晶又は多結晶半導体基板、Nb、V、Ta、Zr、Hf、Ti、Al、Cr、Mo、W、Cu、Fe、Cなどの単結晶、多結晶、あるいは非晶質基板を用いることもできる。

【0094】

第1実施形態及び第2実施形態における第1バッファー層、又は、第3実施形態及び第4実施形態における低温バッファー層の材料は、窒化ガリウムの代わりに、AlxGa1−xN(0≦x<1)でもよい。

【0095】

III族窒化物半導体は、AlxGayIn1−x−yNpV1−p(ここで、V=As、P、Sb、Biであり、0≦x≦1、0≦y≦1、0≦x+y≦1、0.9≦p≦1)であってもよい。

【図面の簡単な説明】

【0096】

【図1】本発明の第1実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図2】本発明の第1実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図3】図2(b)に示す工程により得られた構造体の平面図。

【図4】本発明の第1実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図5】図1(a)〜図4(a)の工程を行って得られた試料のSEM写真。

【図6】図1(a)〜図4(a)の工程を行って得られた試料のSEM写真。

【図7】図1(a)〜図4(a)の工程を行って得られた試料のSEM写真。

【図8】図1〜図4の工程を行って得られた試料をXRD分析結果を示す図。

【図9】XRD分析結果と窒化温度との関係を示す図。

【図10】本発明の第2実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図11】図10(c)に示す工程により得られた構造体の平面図。

【図12】本発明の第2実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図13】本発明の第2実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図14】本発明の第3実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図15】図14(b)に示す工程により得られた構造体の平面図。

【図16】本発明の第3実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図17】本発明の第3実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図18】図14(a)〜図16(a)の工程を行って得られた試料のSEM写真。

【図19】図14(a)〜図16(a)の工程を行って得られた試料のSEM写真。

【図20】本発明の第4実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図21】本発明の第4実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図22】図20(a)〜図20(b)の工程を行って得られた試料のSEM写真。

【図23】図20(a)〜図20(b)の工程を行って得られた試料のSEM写真。

【符号の説明】

【0097】

10,210,310 下地基板

20,120,220 クロム層(金属層)

30,130a等,230,330 第1バッファー層

40 マスク

50a等、150a等 第1バッファー層

60a等、160a等 第2バッファー層

70a等、170a等、270a等、370a等 半導体部材

210a等、310a等 溝

【技術分野】

【0001】

本発明は、半導体デバイスの製造方法に関する。

【背景技術】

【0002】

従来から、窒化ガリウム系化合物半導体を選択的に成長させる技術が提案されている(特許文献1参照)。すなわち、下地基板の上に、複数の開口を有するマスクを形成し、下地基板において複数の開口により露出された複数の領域から、複数の窒化ガリウム系化合物半導体を成長させている。これにより、複数の窒化ガリウム系化合物半導体が互いに分離された状態で成長するので、下地基板と窒化ガリウム系化合物半導体との熱膨張係数の差に基づく応力が低減され、複数の窒化ガリウム系化合物半導体のそれぞれにクラックが発生することが低減される。

【0003】

また、下地基板の表面を加工した後に、GaN系半導体結晶を成長させる技術が提案されている(特許文献2参照)。すなわち、下地基板の表面を凹凸状に加工した後に、凸部の上方部からGaN系半導体結晶を横方向に成長させる。これにより、GaN系半導体結晶が凹凸面を覆うようになる。

【0004】

一方、下地基板の上にMBE法によりクロム層を成膜し、そのクロム層を窒化する技術が提案されている(非特許文献1参照)。

【特許文献1】特開平11−186178号公報

【特許文献2】特開2000−331947号公報

【非特許文献1】李旭鉉、外7名、「MBE法による低温CrxNバッファ層を用いたGaNの成長」、応用物理学会予稿集、364ペ−ジ

【発明の開示】

【発明が解決しようとする課題】

【0005】

仮に、特許文献1の技術において、下地基板の上にバッファー層を形成した後に、複数の開口を有するマスクを形成し、下地基板において複数の開口により露出された複数の領域から、複数の窒化ガリウム系化合物半導体を成長させたとする。この場合、下地基板と複数の窒化ガリウム系化合物半導体との熱膨張係数の差に基づく内部応力や原子間距離の差に基づく格子不整合を、バッファー層で緩和させることができる。

【0006】

しかし、バッファー層が下地基板の表面全体に渡って形成されるので、バッファー層の特定箇所に存在する転位がバッファー層内を表面全体に渡って伝播する可能性がある。これにより、バッファー層自体の結晶性が悪化するので、その上に成長させる複数の窒化ガリウム系化合物半導体の結晶性も悪化する。

【0007】

一方、特許文献2の技術では、GaN系半導体結晶が横方向成長して凹凸面を覆うので、GaN系半導体結晶の上面が平坦になる。

【0008】

ここで、仮に、GaN系半導体結晶を切削刃を用いてスクライビングすることにより、GaN系半導体結晶を複数の半導体部材に分離させたとする。この場合、スクライビングの刃の切削面に対する被切削面(GaN系半導体結晶の上面)の成す角度が大きいので、スクライビングの刃とGaN系半導体結晶との接触面積が小さくなりやすく、スクライビングの刃からの応力が限られた部分に集中しやすい。このため、GaN系半導体結晶が大きなダメージを受けやすくなるという問題が生じる。また、レーザを用いてスクライビングを行うこと(レーザスクライビング)により、GaN系半導体結晶を複数の半導体部材に分離させたとする。この場合、スクライビングで形成する溝を深くするために、レーザの出力を高くする必要がある。このため、GaN系半導体結晶が大きなダメージを受けやるという問題が生じる。したがって、スクライビングにより分離されて得られる複数の半導体部材の側面近傍において、結晶が受けるダメージや結晶性の乱れが大きくなるので、複数の半導体部材を用いて製造される半導体デバイスの特性も悪化するという問題が発生する。

【0009】

本発明の第1の目的は、III族窒化物半導体の複数の半導体部材を成長させる際の結晶性を向上できる半導体デバイスの製造方法を提供することにある。

【0010】

本発明の第2の目的は、III族窒化物半導体の複数の半導体部材を分離させた際の側面近傍において、結晶が受けるダメージや結晶性の乱れを低減できる半導体デバイスの製造方法を提供することにある。

【課題を解決するための手段】

【0011】

本発明の第1側面に係る半導体デバイスの製造方法は、下地基板の上に第1バッファー層を形成する第1バッファー層形成工程と、前記第1バッファー層の上に、複数の開口を有するマスクを形成するマスク形成工程と、前記第1バッファー層の表面において前記複数の開口により露出された複数の領域に、III族窒化物半導体の複数の第2バッファー層を形成する第2バッファー層形成工程と、前記複数の第2バッファー層の上に、III族窒化物半導体の複数の半導体部材を成長させる成長工程とを備えたことを特徴とする。

【0012】

本発明の第2側面に係る半導体デバイスの製造方法は、下地基板の上に金属層を形成する金属層形成工程と、前記金属層の上に、複数の開口を有するマスクを形成するマスク形成工程と、前記金属層において前記複数の開口により露出された複数の領域を窒化することにより、金属窒化物の複数の第1バッファー層を形成する窒化工程と、前記複数の第1バッファー層の上に、III族窒化物半導体の複数の第2バッファー層を形成する第2バッファー層形成工程と、前記複数の第2バッファー層の上に、III族窒化物半導体の複数の半導体部材を成長させる成長工程とを備えたことを特徴とする。

【0013】

本発明の第3側面に係る半導体デバイスの製造方法は、下地基板に、断面においてV字の形状を有する溝を形成する溝形成工程と、前記下地基板の上に、前記溝に沿ってくぼんだ第1凹部を上面に有する中間層を形成する中間層形成工程と、前記中間層の上に、III族窒化物半導体の半導体層を成長させる成長工程とを備え、前記半導体層は、前記第1凹部に沿ってくぼんだ第2凹部を上面に有することを特徴とする。

【0014】

本発明の第4側面に係る半導体デバイスの製造方法は、下地基板に、中間層を形成する中間層形成工程と、前記下地基板及び前記中間層に、断面においてV字の形状を有する溝を形成するとともに、前記中間層を複数の中間部材にする溝形成工程と、前記複数の中間部材の上に、III族窒化物半導体の半導体層を成長させる成長工程とを備え、前記半導体層は、前記溝に沿ってくぼんだ凹部を上面に有することを特徴とする。

【発明の効果】

【0015】

本発明によれば、III族窒化物半導体の複数の半導体部材を成長させる際の結晶性を向上できる。

【0016】

また、本発明によれば、III族窒化物半導体の複数の半導体部材を分離させた際の側面近傍において、結晶が受けるダメージや結晶性の乱れを低減できる。

【発明を実施するための最良の形態】

【0017】

本明細書において、「膜」は、連続した膜でもよいし、不連続な膜でもよいものとする。「膜」は、厚さを持って形成されている状態を表す。

【0018】

本発明は、LED(Light Emitting Diode)などの半導体デバイスに適用可能な複数の半導体部材を選択的に成長させるための方法に関する。

【0019】

本発明の第1実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を、図1〜図4を用いて説明する。図1、図2及び図4は、半導体デバイスの製造方法を示す工程断面図である。図3は、図2(b)に示す工程により得られた構造体の平面図である。以下では、III族窒化物半導体の一例として、窒化ガリウムを中心に説明するが、他のIII族窒化物半導体に関しても同様である。

【0020】

図1(a)に示す工程では、下地基板10を準備する。下地基板10の材料は、例えば、Al2O3(サファイア)である。

【0021】

図1(b)に示す工程では、スパッタ法などにより、下地基板10の上にクロム層(金属層)20を成膜する。成膜されるクロム層20の厚さは、例えば、20nmである。

【0022】

ここで、クロム層20を成膜するのは、その後に窒化して形成するクロム窒化物の原子間距離が窒化ガリウムに近く、窒化ガリウムとの格子不整合が小さいためである。

【0023】

図1(c)に示す工程では、クロム層20を1000℃以上1300℃以下(1273K以上1573K以下)の温度で窒化することにより、クロム窒化物(金属窒化物)の第1バッファー層30を形成する。すなわち、下地基板10を1000℃以上1300℃の温度に加熱するとともに、クロム層20の表面をアンモニアガス雰囲気にする。これにより、クロム層20が窒化して第1バッファー層30になる。

【0024】

ここで、クロムの結晶構造が立方晶系であるのに対して、クロム窒化物の結晶構造が六方晶系である。クロム層20を窒化した際に、クロムの結晶格子がクロム窒化物の結晶格子へと再配列するためには、一定以上のエネルギーが必要であると考えられる。

【0025】

仮に、クロム層20の窒化温度が1000℃未満であると、クロムの結晶格子がクロム窒化物の結晶格子へと再配列するために十分なエネルギーがクロム層20に与えられないので、窒化されて形成される第1バッファー層30の結晶性が悪くなる。

【0026】

それに対して、本実施形態では、クロム層20の窒化温度が1000℃以上であるので、クロムの結晶格子がクロム窒化物の結晶格子へと再配列するために十分なエネルギーがクロム層20に与えられる。これにより、クロム層20が窒化されて形成されるクロム窒化物の第1バッファー層30の結晶性が向上する。

【0027】

だだし、過度な高温で窒化することは、熱負荷増大による装置の部材劣化の問題が生じるとともに、形成された第1バッファー層と下地基板との相互熱拡散などの問題が生じる。このため、窒化温度は1300℃以下が好ましい。

【0028】

また、第1バッファー層30の材料であるクロム窒化物は、下地基板(サファイア)と窒化ガリウムとの間の原子間距離を有するので、下地基板との格子不整合が小さい。この点からも、第1バッファー層30の結晶性が向上する。

【0029】

図2(a)に示す工程では、第1バッファー層30の上にマスク層40iを成膜する。成膜されるマスク層40iの厚さは、例えば、100nmである。マスク層40iの材料は、例えば、酸化シリコン及び窒化シリコンのいずれかである。

【0030】

ここで、図1(a)〜図2(a)の工程は、同じチャンバ内で連続的に行うことが好ましい。この場合、各層の界面に自然酸化膜が形成されることを低減できる。

【0031】

図2(b)に示す工程では、リソグラフィ法などにより、マスク層40iに複数の開口40a,40b,・・・を形成して、マスク40を形成する。例えば、図3に示すように、第1バッファー層30の上に、複数の開口40a,40b,・・・を有するマスク40が形成される。

【0032】

ここで、複数の開口40a,40b,・・・の寸法は、LEDなどの半導体デバイスに適した大きさに対応したものとなっている。また、複数の開口40a,40b,・・・の形状は、LEDなどの半導体デバイスに適した形状に対応したものとなっている。なお、複数の開口40a,40b,・・・のそれぞれの形状は、下地基板10の上面に垂直な方向から見た場合に、矩形状以外の形状であっても良く、例えば、三角形、円等であっても良い。

【0033】

図2(c)に示す工程では、HVPE法やMOCVD法などにより、第1バッファー層30の表面において複数の開口40a,40b,・・・により露出された複数の領域30a,30b,・・・から、窒化ガリウムの複数の第2バッファー層50a,50b,・・・を成長させる。

【0034】

ここで、複数の第2バッファー層50a,50b,・・・は、それぞれ、例えば、GaNの単結晶体、多結晶体又はアモルファス体で構成されうる。複数の第2バッファー層50a,50b,・・・の厚さは、それぞれ、数十Å〜数十μmであることが好ましい。複数の第2バッファー層50a,50b,・・・の成長温度は、それぞれ、900℃付近であることが好ましい。複数の第2バッファー層50a,50b,・・・は、それぞれ、いわゆる低温バッファー層である。

【0035】

図4(a)に示す工程では、HVPE法やMOCVD法などにより、複数の第2バッファー層50a,50b,・・・の上に、窒化ガリウムの複数の半導体部材60a,60b,・・・を成長させる。

【0036】

ここで、複数の半導体部材60a,60b,・・・は、それぞれ、例えば、GaNの単結晶体で構成されうる。複数の半導体部材60a,60b,・・・の厚さは、それぞれ、数十Å〜数十μmであることが好ましい。複数の半導体部材50a,50b,・・・の成長温度は、それぞれ、複数の第2バッファー層50a,50b,・・・の成長温度(900℃付近)よりも高い温度である約1100℃になる。

【0037】

また、複数の第2バッファー層50a,50b,・・・は、第1バッファー層30の表面においてマスク40の複数の開口40a,40b,・・・により露出された複数の領域30a,30b,・・・に形成されている。マスク40の結晶方位が複数の第2バッファー層50a,50b,・・・の結晶方位と異なるので、複数の第2バッファー層50a,50b,・・・のいずれかの特定箇所に存在する転位は、他の第2バッファー層50a,50b,・・・に伝播しにくい。これにより、複数の第2バッファー層50a,50b,・・・は、全体として、その結晶性が向上する。この結果、複数の第2バッファー層50a,50b,・・・の上に成長させる複数の半導体部材60a,60b,・・・の結晶性も向上する。すなわち、III族窒化物半導体の複数の半導体部材を成長させる際の結晶性を向上できる。

【0038】

さらに、第1バッファー層30の材料であるクロム窒化物は、下地基板(サファイア)と窒化ガリウムとの間の原子間距離を有するので、窒化ガリウムとの格子不整合が小さい。例えば、サファイアの30°回転した(0001)面方向の原子間距離は、2.747Åである。窒化ガリウムの(0001)面方向の原子間距離は、3.188Åである。クロム窒化物の(111)面方向の原子間距離は、2.927Åであり、サファイアの原子間距離と窒化ガリウムの原子間距離との間の値である。これにより、第1バッファー層30の上に成長する複数の第2バッファー層50a,50b,・・・及び複数の半導体部材60a,60b,・・・は、結晶性が向上する。

【0039】

また、第1バッファー層30の材料であるクロム窒化物は、下地基板(サファイア)と窒化ガリウムとの間の熱膨張係数を有する。例えば、サファイアの(0001)面方向の熱膨張係数は、7.50である。窒化ガリウムの(0001)面方向の熱膨張係数は、5.45である。クロム窒化物の(111)面方向の熱膨張係数は、6.00であり、サファイアの熱膨張係数と窒化ガリウムの熱膨張係数との間の値である。これにより、下地基板10と、複数の第2バッファー層50a,50b,・・・及び複数の半導体部材60a,60b,・・・との間の熱膨張係数の差に基づいて発生する内部応力を第1バッファー層30で緩和することができる。このため、複数の第2バッファー層50a,50b,・・・及び複数の半導体部材60a,60b,・・・のそれぞれの内部応力が低減されるので、この点からも、複数の第2バッファー層50a,50b,・・・及び複数の半導体部材60a,60b,・・・の結晶性が向上する。

【0040】

図4(b)に示す工程では、マスク40を除去する。例えば、マスク40を、選択的にエッチングして除去する。例えば、マスク40の材料が酸化シリコンである場合、HF溶液あるいはBOE(バッファードHF)溶液を用いることにより、マスク40を選択的にエッチングすることができる。

【0041】

なお、マスク40を切削刃あるいはレーザを用いてスクライビングすることにより、マスク40を機械的あるいは物理的に除去してもよい。

【0042】

図4(c)に示す工程では、第1バッファー層30を選択的にエッチングして、複数の半導体部材60a,60b,・・・を下地基板10から分離するとともに互いに分離する。これにより、複数の半導体デバイス70a,70b,・・・を得ることができる。

【0043】

ここで、複数の半導体デイバス70a,70b,・・・は、それぞれ、第2バッファー層50a,50b,・・・と半導体部材60a,60b,・・・とを含む。複数の半導体デバイス70a,70b,・・・の形状は、それぞれ、複数の開口40a,40b,・・・の形状に対応して、LEDなどの半導体デバイスに適した大きさになっている。複数の半導体デバイス70a,70b,・・・の寸法は、複数の開口40a,40b,・・・の寸法に対応して、LEDなどの半導体デバイスに適した大きさになっている。

【0044】

このように、図1(a)〜図4(a)の工程を行った結果、例えば、図5のSEM写真に示されるような試料が得られた。図5のSEM写真では、下地基板10の上面に垂直な方向から見た場合に、複数の半導体部材60a,60b,・・・の寸法が、それぞれ、縦約1mm、横約1mmになっている。また、複数の半導体部材60a,60b,・・・の間に、マスク40が格子状に形成されている。複数の半導体部材60a,60b,・・・の間の部分を断面観察した結果、図6及び図7に示すように、傾斜した側面を有している。そこで、図2(b)の工程で形成するマスク40の複数の開口40a,40b,・・・の寸法は、半導体部材60a,60b,・・・の側面の傾斜角を考慮して決められている。

【0045】

図5〜図7に示す試料に対してさらに図4(b)、(c)の工程を行った結果得られた複数の半導体部材の1つに対してX線回折(XRD)分析を行った結果を、図8に示す。すなわち、半導体部材のXRDプロファイルにおける(0002)面のピークの半値幅を求めたところ、383[arcsec]であった。図8には、この結果を、「本実施形態」として棒グラフで示してある。

【0046】

また、図8には、比較のために、特許文献1に示される第1実施例の方法により複数の半導体部材を得た場合について、予想される値を「特許文献1」として棒グラフで示してある。特許文献1に示される第1実施例の方法によれば、下地基板の上に複数の開口を有するマスクを形成した後に、下地基板において複数の開口により露出された複数の領域から、複数の半導体部材を成長させることになる。

【0047】

この場合、下地基板(サファイア)と複数の半導体部材(窒化ガリウム)との間で熱膨張係数の差や原子間距離の差が大きいので、成長させた複数の半導体部材(窒化ガリウム)の結晶性が「本実施形態」に比べて悪くなることが予想される。よって、図8では、「特許文献1」のXRD半値幅が「本実施形態」のXRD半値幅よりも大きいものとしている。

【0048】

さらに、図8には、比較のために、特許文献1に示された方法に対して非特許文献1で示された低温CrxNバッファ層を適用した場合について、予想される値を「非特許文献1」として棒グラフで示してある。すなわち、この組み合わせによれば、下地基板の上に低温CrxNバッファ層を形成し、低温CrxNバッファ層の上に複数の開口を有するマスクを形成した後に、下地基板において複数の開口により露出された複数の領域から、複数の半導体部材を成長させることになる。

【0049】

この場合、下地基板と複数の窒化ガリウム系化合物半導体との熱膨張係数の差に基づく内部応力や原子間距離の差に基づく格子不整合を、バッファー層で緩和させることができる。これにより、成長させた複数の半導体部材(窒化ガリウム)の結晶性が「特許文献1」に比べて良くなることが予想される。よって、図8では、「非特許文献1」のXRD半値幅が「特許文献1」のXRD半値幅よりも小さいものとしている。

【0050】

しかし、バッファー層が下地基板の表面全体に渡って形成されることになるので、バッファー層の特定箇所に存在する転位がバッファー層内を表面全体に渡って伝播する可能性がある。これにより、バッファー層自体の結晶性が悪化するので、その上に成長させた複数の半導体部材(窒化ガリウム)の結晶性が「本実施形態」に比べて悪くなることが予想される。よって、図8では、「非特許文献1」のXRD半値幅が「本実施形態」のXRD半値幅よりも大きいものとしている。

【0051】

次に、「非特許文献1」と「本実施形態」との予測される関係を、窒化温度に対応付けて比較したものを図9に示す。図9に示す関係は、本発明者が発明者となっている特願2006−272324の図13に基づいて予測されたものである。

【0052】

図9に示すように、窒化温度が1000℃から低くなるにしたがって、XRD半値幅がW1から急激に大きくなり結晶性が悪くなることが予測される。

【0053】

ここで、非特許文献1では、窒化温度が低温T2(500℃〜600℃)であり、1000℃未満である。図9によれば、窒化温度T2に対するXRD半値幅は、W1より大きいW2であると予測される。

【0054】

それに対して、本実施形態では、窒化温度が1000℃以上1300℃以下の温度T1である。窒化温度T1に対するXRD半値幅は、W1より小さい383[arcsec]である。

【0055】

次に、本発明の第2実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を、図10〜図13を用いて説明する。図10、図12及び図13は、半導体デバイスの製造方法を示す工程断面図である。図11は、図10(c)に示す工程により得られた構造体の平面図である。以下では、III族窒化物半導体の一例として、窒化ガリウムを中心に説明するが、他のIII族窒化物半導体に関しても同様である。なお、以下では、第1実施形態と異なる部分を中心に説明し、同様の部分の説明を省略する。

【0056】

図10(a)に示す工程では、クロム層120の上にマスク層40iを成膜する。

【0057】

図10(b)に示す工程では、リソグラフィ法などにより、マスク層40iに複数の開口40a,40b,・・・を形成して、マスク40を形成する。

【0058】

図10(c)に示す工程では、クロム層120において複数の開口40a,40b,・・・により露出された複数の領域120a,120b,・・・を、1000℃以上1300℃以下の温度で窒化することにより、複数の第1バッファー層130a,130b,・・・を形成する。例えば、図11に示すように、クロム層120の上に、複数の開口40a,40b,・・・を有するマスク40が形成される。

【0059】

図12(a)に示す工程では、複数の開口40a,40b,・・・により露出された複数の第1バッファー層130a,130b,・・・から、窒化ガリウムの複数の第2バッファー層50a,50b,・・・を成長させる。

【0060】

図12(b)に示す工程では、HVPE法やMOCVD法などにより、複数の第2バッファー層150a,150b,・・・の上に、窒化ガリウムの複数の半導体部材160a,160b,・・・を成長させる。

【0061】

図13(a)に示す工程では、マスク40を除去する。例えば、マスク40を、選択的にエッチングして除去する。

【0062】

図13(b)に示す工程では、クロム層120及び複数の第1バッファー層130a,130b,・・・を選択的にエッチングして、複数の半導体部材160a,160b,・・・を下地基板10から分離するとともに互いに分離する。これにより、複数の半導体デバイス170a,170b,・・・を得ることができる。

【0063】

このように、クロム層を窒化する前にマスクを形成して、クロム層の表面において複数の開口により露出された複数の領域を、選択的に窒化している。このクロム層の結晶方位は、第1バッファー層の結晶方位と異なる。これにより、第1バッファー層を介して内部応力が隣接する半導体部材に伝播することを低減できる。

【0064】

次に、本発明の第3実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を、図14〜図17を用いて説明する。図14、図16及び図17は、半導体デバイスの製造方法を示す工程断面図である。図15は、図14(b)に示す工程により得られた構造体の平面図である。以下では、III族窒化物半導体の一例として、窒化ガリウムを中心に説明するが、他のIII族窒化物半導体に関しても同様である。なお、以下では、第1実施形態と異なる部分を中心に説明し、同様の部分の説明を省略する。

【0065】

図14(a)に示す工程では、下地基板210に、断面においてV字の形状を有する溝を形成する。例えば、下地基板210をスクライビングすることにより、溝210a,210b,210c,・・・を形成する。このとき、レーザあるいは切削刃を用いてスクライビングすることができる。

【0066】

ここで、溝210a,210b,210c,・・・において対向する第1の面210a1,210b1,210c1,・・・と第2の面210a2,210b2,210c2,・・・とは、いずれも、スクライビングの刃の切削面に沿った方向に延びている。

【0067】

図14(b)に示す工程では、溝210a,210b,210c,・・・が形成された下地基板210の上に、クロム層220を成膜する。ここで、クロム層220は、複数の第1クロム層220a,220b,・・・と、複数の第2クロム層221a,221b,221c,・・・とを含む。すなわち、溝210a,210b,210c,・・・が形成されていない領域に、複数の第1クロム層220a,220b,・・・が成膜され、溝210a,210b,210c,・・・が形成されている領域に、複数の第2クロム層221a,221b,221c,・・・が成膜される。

【0068】

ここで、溝210a,210b,210c,・・・が形成される領域に成膜される第2クロム層221a,221b,221c,・・・は、第1クロム層220a,220b,・・・と結晶方位が異なっている。

【0069】

図14(c)に示す工程では、クロム層220を1000℃以上1300℃以下の温度で窒化することにより、下地基板210の上に、溝210a,210b,210c,・・・に沿ってくぼんだ第1凹部231a1,231b1,231c1,・・・を上面に有するクロム窒化物の中間層230を形成する。ここで、中間層230は、複数の第1中間層230a,230b,・・・と、複数の第2中間層231a,231b,231c,・・・とを含む。すなわち、溝210a,210b,210c,・・・が形成されていない複数の領域に、複数の第1中間層230a,230b,・・・が形成され、溝210a,210b,210c,・・・が形成されている領域に、複数の第2中間層231a,231b,231c,・・・が形成される(図15参照)。

【0070】

ここで、複数の第2中間層231a,231b,231c,・・・のそれぞれの結晶方位は、複数の第1中間層230a,230b,・・・のそれぞれの結晶方位と異なる。これにより、基板から受ける応力の向きは第1中間層と第2中間層とで異なるため、複数の第2中間層231a,231b,231c,・・・のそれぞれは、複数の第1中間層230a,230b,・・・の間に働く内部応力を緩和することができる。

【0071】

図16(a)に示す工程では、中間層230の上に、低温バッファー層250を形成する。ここで、低温バッファー層250は、複数の第1低温バッファー層250a,250b,・・・と、複数の第2低温バッファー層251a,251b,251c,・・・とを含む。すなわち、溝210a,210b,210c,・・・が形成されていない複数の領域に、複数の第1低温バッファー層250a,250b,・・・が形成され、溝210a,210b,210c,・・・が形成されている領域に、複数の第2低温バッファー層251a,251b,251c,・・・が形成される。

【0072】

ここで、複数の第2低温バッファー層251a,251b,251c,・・・のそれぞれの結晶方位は、複数の第1低温バッファー層250a,250b,・・・のそれぞれの結晶方位と異なる。これにより、基板から受ける応力の向きは第1低温バッファー層と第2低温バッファー層とで異なるため、複数の第2低温バッファー層251a,251b,251c,・・・のそれぞれは、複数の第1低温バッファー層250a,250b,・・・の間に働く内部応力を緩和することができる。

【0073】

そして、低温バッファー層250の上に、窒化ガリウムの半導体層260を成長させる。ここで、半導体層260は、溝210a,210b,210c,・・・に沿ってくぼんだ第2凹部261a1,261b1,261c1,・・・を上面に有する。

【0074】

ここで、第2凹部261a1,261b1,261c1,・・・において対向する第1の面261a11,261b11,261c11,・・・と第2の面261a12,261b12,261c12,・・・とは、いずれも、スクライビングの刃の切削面に沿った方向に延びている。この結果、半導体層260を切削刃を用いてスクライビングすることにより、半導体層260を複数の半導体部材に分離させる際に、スクライビングの刃の切削面に対する被切削面(半導体層260の上面)の成す角度を小さくできるので、スクライビングの刃と半導体層260との接触面積を大きくでき、スクライビングの刃からの応力が限られた部分に集中することを避けることができる。また、レーザを用いてスクライビングを行うこと(レーザスクライビング)により、GaN系半導体結晶を複数の半導体部材に分離させる際に、スクライビングで形成する溝を浅くすることができるので、レーザの出力を低くすることが可能となる。したがって、スクライビングより分離されて得られる複数の半導体部材の側面近傍において、結晶が受けるダメージを小さくすることができ、かつ結晶性の乱れを低減できるので、複数の半導体部材を用いて製造される半導体デバイスの特性を向上できる。すなわち、III族窒化物半導体の複数の半導体部材を分離させた際の側面近傍において、結晶が受けるダメージや結晶性の乱れを低減できる。

【0075】

半導体層260は、複数の第1半導体層260a,260b,・・・と、複数の第2半導体層261a,261b,261c,・・・とを含む。すなわち、溝210a,210b,210c,・・・が形成されていない複数の領域に、複数の第1半導体層260a,260b,・・・が形成され、溝210a,210b,210c,・・・が形成されている領域に、複数の第2半導体層261a,261b,261c,・・・が形成される。

【0076】

ここで、複数の第2半導体層261a,261b,261c,・・・のそれぞれの結晶方位は、複数の第1半導体層260a,260b,・・・のそれぞれの結晶方位と異なる。これにより、基板から受ける応力の向きは第1半導体層と第2半導体層とで異なるため、複数の第2半導体層261a,261b,261c,・・・のそれぞれは、複数の第1半導体層260a,260b,・・・の間に働く内部応力を緩和することができる。

【0077】

このようにして、例えば、図18及び図19のSEM写真で示される試料が得られた。図18は、溝が形成されている領域の近傍を、下地基板の表面に垂直な方向から観察したSEM写真である。図19は、溝が形成されている領域の近傍を、下地基板の表面に沿った方向から観察したSEM写真である。図18及び図19に示されるように、第2凹部において対向する第1の面と第2の面とは、いずれも、スクライビングの刃の切削面に沿った方向に延びている。

【0078】

図16(b)に示す工程では、複数の第2半導体層261a,261b,261c,・・・、複数の第2低温バッファー層251a,251b,251c,・・・、及び複数の第2中間層231a,231b,231c,・・・をスクライビングすることにより、複数の第2半導体層261a,261b,261c,・・・、複数の第2低温バッファー層251a,251b,251c,・・・、及び複数の第2中間層231a,231b,231c,・・・を除去する。

【0079】

ここで、上述のように、スクライビングの刃の切削面に対する被切削面(半導体層260の上面)の成す角度が小さい状態でスクライビングするので、スクライビングの刃と半導体層260との接触面積が大きくなっている。

【0080】

図17に示す工程では、複数の第1中間層230a,230b,・・・を選択的にエッチングすることにより、複数の半導体部材260a,260b,・・・を下地基板210から分離するとともに互いに分離する。これにより、複数の半導体デバイス270a,270b,・・・を得ることができる。

【0081】

次に、本発明の第4実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を、図20及び図21を用いて説明する。図20及び図21は、半導体デバイスの製造方法を示す工程断面図である。以下では、III族窒化物半導体の一例として、窒化ガリウムを中心に説明するが、他のIII族窒化物半導体に関しても同様である。なお、以下では、第3実施形態と異なる部分を中心に説明し、同様の部分の説明を省略する。

【0082】

図20(a)に示す工程では、下地基板310の上に、中間層330を形成する。なお、中間層330は、図1(a)〜(c)と同様の工程により形成されても良い。

【0083】

図20(b)に示す工程では、下地基板310及び中間層330をスクライビングすることにより、下地基板310及び中間層330に、断面においてV字の形状を有する溝310a,310b,310c,・・・を形成するとともに、中間層330を複数の中間部材330a,330b,・・・にする。ここで、溝310a,310b,310c,・・・が形成されている領域に第2中間層が形成されていない。このとき、レーザあるいは切削刃を用いてスクライビングすることができる。

【0084】

ここで、溝310a,310b,310c,・・・は、下地基板310の強度を十分に確保した状態で深さを大きくしやすい点で、第3実施形態と異なる。

【0085】

図20(c)に示す工程では、複数の中間部材330a,330b,・・・の上に、低温バッファー層350を形成する。ここで、低温バッファー層350は、複数の第1低温バッファー層350a,350b,・・・と、複数の第2低温バッファー層351a,351b,351c,・・・とを含む。

【0086】

ここで、複数の第1低温バッファー層350a,350b,・・・が複数の中間部材(バッファー層)330a,330b,・・・を間にして下地基板310の上に配されているのに対して、複数の第2低温バッファー層351a,351b,351c,・・・は、下地基板310に直接的に接している。これにより、複数の第2低温バッファー層351a,351b,351c,・・・のそれぞれの結晶性は、複数の第1低温バッファー層350a,350b,・・・のそれぞれの結晶性と異なる。複数の第2低温バッファー層351a,351b,351c,・・・は、例えば、多結晶又はアモルファスとして形成することができる。したがって、複数の第2低温バッファー層351a,351b,351c,・・・のそれぞれは、複数の第1低温バッファー層350a,350b,・・・の間に働く内部応力を緩和することができる。

【0087】

そして、低温バッファー層350の上に、窒化ガリウムの半導体層360を成長させる。ここで、半導体層360は、溝310a,310b,310c,・・・に沿ってくぼんだ凹部361a1,361b1,361c1,・・・を上面に有する。半導体層360は、複数の第1半導体層360a,360b,・・・と、複数の第2半導体層361a,361b,361c,・・・とを含む。

【0088】

ここで、複数の第2低温バッファー層351a,351b,351c,・・・のそれぞれの結晶性が複数の第1低温バッファー層350a,350b,・・・のそれぞれの結晶性と異なることに対応して、複数の第2半導体層361a,361b,361c,・・・のそれぞれの結晶性は、複数の第1半導体層360a,360b,・・・のそれぞれの結晶性と異なる。複数の第2半導体層361a,361b,361c,・・・は、例えば、多結晶又はアモルファスとして形成することができる。したがって、複数の第2半導体層361a,361b,361c,・・・のそれぞれは、複数の第1半導体層360a,360b,・・・の間に働く内部応力を緩和することができる。

【0089】

このようにして、例えば、図22及び図23のSEM写真で示される試料が得られた。図22は、溝が形成されている領域の近傍を、下地基板の表面に垂直な方向から観察したSEM写真である。図23は、溝が形成されている領域の近傍を、下地基板の表面に沿った方向から観察したSEM写真である。図22及び図23に示されるように、凹部において対向する第1の面と第2の面とは、いずれも、スクライビングの刃の切削面に沿った方向に延びている。

【0090】

図21(a)に示す工程では、複数の第2半導体層361a,361b,361c,・・・及び複数の第2低温バッファー層351a,351b,351c,・・・をスクライビングすることにより、複数の第2半導体層361a,361b,361c,・・・及び複数の第2低温バッファー層351a,351b,351c,・・・を除去する。ここで、複数の中間部材330a,330b,・・・の傾斜した側面が露出されている。

【0091】

図21(b)に示す工程では、複数の中間部材330a,330b,・・・を選択的にエッチングすることにより、複数の第1半導体層360a,360b,・・・を下地基板310から分離するとともに互いに分離する。これにより、複数の半導体デバイス370a,370b,・・・を得ることができる。

【0092】

ここで、複数の中間部材330a,330b,・・・は、その傾斜した側面が露出されているので、エッチング溶液との接触面積が大きい。これにより、第3実施形態に比べて、複数の中間部材330a,330b,・・・を短時間にエッチングすることができる。

【0093】

なお、下地基板は、Si、SiC、GaAsなどの単結晶又は多結晶半導体基板、Nb、V、Ta、Zr、Hf、Ti、Al、Cr、Mo、W、Cu、Fe、Cなどの単結晶、多結晶、あるいは非晶質基板を用いることもできる。

【0094】

第1実施形態及び第2実施形態における第1バッファー層、又は、第3実施形態及び第4実施形態における低温バッファー層の材料は、窒化ガリウムの代わりに、AlxGa1−xN(0≦x<1)でもよい。

【0095】

III族窒化物半導体は、AlxGayIn1−x−yNpV1−p(ここで、V=As、P、Sb、Biであり、0≦x≦1、0≦y≦1、0≦x+y≦1、0.9≦p≦1)であってもよい。

【図面の簡単な説明】

【0096】

【図1】本発明の第1実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図2】本発明の第1実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図3】図2(b)に示す工程により得られた構造体の平面図。

【図4】本発明の第1実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図5】図1(a)〜図4(a)の工程を行って得られた試料のSEM写真。

【図6】図1(a)〜図4(a)の工程を行って得られた試料のSEM写真。

【図7】図1(a)〜図4(a)の工程を行って得られた試料のSEM写真。

【図8】図1〜図4の工程を行って得られた試料をXRD分析結果を示す図。

【図9】XRD分析結果と窒化温度との関係を示す図。

【図10】本発明の第2実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図11】図10(c)に示す工程により得られた構造体の平面図。

【図12】本発明の第2実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図13】本発明の第2実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図14】本発明の第3実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図15】図14(b)に示す工程により得られた構造体の平面図。

【図16】本発明の第3実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図17】本発明の第3実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図18】図14(a)〜図16(a)の工程を行って得られた試料のSEM写真。

【図19】図14(a)〜図16(a)の工程を行って得られた試料のSEM写真。

【図20】本発明の第4実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図21】本発明の第4実施形態に係るIII族窒化物半導体の半導体デバイスの製造方法を示す工程断面図。

【図22】図20(a)〜図20(b)の工程を行って得られた試料のSEM写真。

【図23】図20(a)〜図20(b)の工程を行って得られた試料のSEM写真。

【符号の説明】

【0097】

10,210,310 下地基板

20,120,220 クロム層(金属層)

30,130a等,230,330 第1バッファー層

40 マスク

50a等、150a等 第1バッファー層

60a等、160a等 第2バッファー層

70a等、170a等、270a等、370a等 半導体部材

210a等、310a等 溝

【特許請求の範囲】

【請求項1】

下地基板に、断面においてV字の形状を有する溝を形成する溝形成工程と、

前記下地基板の上に、前記溝に沿ってくぼんだ第1凹部を上面に有する中間層を形成する中間層形成工程と、

前記中間層の上に、III族窒化物半導体の半導体層を成長させる成長工程と、

を備え、

前記半導体層は、前記第1凹部に沿ってくぼんだ第2凹部を上面に有する

ことを特徴とする半導体デバイスの製造方法。

【請求項2】

前記中間層形成工程では、前記溝が形成されていない領域に複数の第1中間層が形成され、前記溝が形成されている領域に複数の第2中間層が形成され、

前記成長工程では、前記溝が形成されていない領域に複数の第1半導体層が形成され、前記溝が形成されている領域に複数の第2半導体層が形成され、

前記複数の第2中間層は、それぞれ、前記第1凹部を上面に有し、

前記複数の第2半導体層は、それぞれ、前記第2凹部を上面に有する

ことを特徴とする請求項1に記載の半導体デバイスの製造方法。

【請求項3】

前記複数の第2半導体層及び前記複数の第2中間層を除去する除去工程と、

前記複数の第1中間層を選択的にエッチングすることにより、前記複数の第1半導体層を複数の半導体部材として前記下地基板から分離するとともに互いに分離する分離工程と、

をさらに備えた

ことを特徴とする請求項2に記載の半導体デバイスの製造方法。

【請求項4】

前記溝形成工程では、前記下地基板をスクライビングすることにより、前記溝を形成する

ことを特徴とする請求項1から3のいずれか1項に記載の半導体デバイスの製造方法。

【請求項5】

前記除去工程では、前記複数の第2半導体層及び前記複数の第2中間層をスクライビングすることにより、前記複数の第2半導体層及び前記複数の第2中間層を除去する

ことを特徴とする請求項3に記載の半導体デバイスの製造方法。

【請求項6】

下地基板の上に、中間層を形成する中間層形成工程と、

前記下地基板及び前記中間層に、断面においてV字の形状を有する溝を形成するとともに、前記中間層を複数の中間部材にする溝形成工程と、

前記複数の中間部材の上に、III族窒化物半導体の半導体層を成長させる成長工程と、

を備え、

前記半導体層は、前記溝に沿ってくぼんだ凹部を上面に有する

ことを特徴とする半導体デバイスの製造方法。

【請求項7】

前記成長工程では、前記溝が形成されていない領域に複数の第1半導体層が形成され、前記溝が形成されている領域に複数の第2半導体層が形成され、

前記複数の第2半導体層は、それぞれ、前記凹部を上面に有する

ことを特徴とする請求項6に記載の半導体デバイスの製造方法。

【請求項8】

前記複数の第2半導体層を除去する除去工程と、

前記複数の中間部材を選択的にエッチングすることにより、前記複数の第1半導体層を複数の半導体部材として前記下地基板から分離するとともに互いに分離する分離工程と、

をさらに備えた

ことを特徴とする請求項7に記載の半導体デバイスの製造方法。

【請求項9】

前記溝形成工程では、前記下地基板及び前記中間層をスクライビングすることにより、前記下地基板の表面の一部が露出した前記溝を形成する

ことを特徴とする請求項6から8のいずれか1項に記載の半導体デバイスの製造方法。

【請求項10】

前記除去工程では、前記複数の第2半導体層をスクライビングすることにより、前記複数の第2半導体層を除去する

ことを特徴とする請求項8に記載の半導体デバイスの製造方法。

【請求項1】

下地基板に、断面においてV字の形状を有する溝を形成する溝形成工程と、

前記下地基板の上に、前記溝に沿ってくぼんだ第1凹部を上面に有する中間層を形成する中間層形成工程と、

前記中間層の上に、III族窒化物半導体の半導体層を成長させる成長工程と、

を備え、

前記半導体層は、前記第1凹部に沿ってくぼんだ第2凹部を上面に有する

ことを特徴とする半導体デバイスの製造方法。

【請求項2】

前記中間層形成工程では、前記溝が形成されていない領域に複数の第1中間層が形成され、前記溝が形成されている領域に複数の第2中間層が形成され、

前記成長工程では、前記溝が形成されていない領域に複数の第1半導体層が形成され、前記溝が形成されている領域に複数の第2半導体層が形成され、

前記複数の第2中間層は、それぞれ、前記第1凹部を上面に有し、

前記複数の第2半導体層は、それぞれ、前記第2凹部を上面に有する

ことを特徴とする請求項1に記載の半導体デバイスの製造方法。

【請求項3】

前記複数の第2半導体層及び前記複数の第2中間層を除去する除去工程と、

前記複数の第1中間層を選択的にエッチングすることにより、前記複数の第1半導体層を複数の半導体部材として前記下地基板から分離するとともに互いに分離する分離工程と、

をさらに備えた

ことを特徴とする請求項2に記載の半導体デバイスの製造方法。

【請求項4】

前記溝形成工程では、前記下地基板をスクライビングすることにより、前記溝を形成する

ことを特徴とする請求項1から3のいずれか1項に記載の半導体デバイスの製造方法。

【請求項5】

前記除去工程では、前記複数の第2半導体層及び前記複数の第2中間層をスクライビングすることにより、前記複数の第2半導体層及び前記複数の第2中間層を除去する

ことを特徴とする請求項3に記載の半導体デバイスの製造方法。

【請求項6】

下地基板の上に、中間層を形成する中間層形成工程と、

前記下地基板及び前記中間層に、断面においてV字の形状を有する溝を形成するとともに、前記中間層を複数の中間部材にする溝形成工程と、

前記複数の中間部材の上に、III族窒化物半導体の半導体層を成長させる成長工程と、

を備え、

前記半導体層は、前記溝に沿ってくぼんだ凹部を上面に有する

ことを特徴とする半導体デバイスの製造方法。

【請求項7】

前記成長工程では、前記溝が形成されていない領域に複数の第1半導体層が形成され、前記溝が形成されている領域に複数の第2半導体層が形成され、

前記複数の第2半導体層は、それぞれ、前記凹部を上面に有する

ことを特徴とする請求項6に記載の半導体デバイスの製造方法。

【請求項8】

前記複数の第2半導体層を除去する除去工程と、

前記複数の中間部材を選択的にエッチングすることにより、前記複数の第1半導体層を複数の半導体部材として前記下地基板から分離するとともに互いに分離する分離工程と、

をさらに備えた

ことを特徴とする請求項7に記載の半導体デバイスの製造方法。

【請求項9】

前記溝形成工程では、前記下地基板及び前記中間層をスクライビングすることにより、前記下地基板の表面の一部が露出した前記溝を形成する

ことを特徴とする請求項6から8のいずれか1項に記載の半導体デバイスの製造方法。

【請求項10】

前記除去工程では、前記複数の第2半導体層をスクライビングすることにより、前記複数の第2半導体層を除去する

ことを特徴とする請求項8に記載の半導体デバイスの製造方法。

【図1】

【図2】

【図3】

【図4】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図20】

【図21】

【図5】

【図6】

【図7】

【図18】

【図19】

【図22】

【図23】

【図2】

【図3】

【図4】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図20】

【図21】

【図5】

【図6】

【図7】

【図18】

【図19】

【図22】

【図23】

【公開番号】特開2009−164611(P2009−164611A)

【公開日】平成21年7月23日(2009.7.23)

【国際特許分類】

【出願番号】特願2008−335166(P2008−335166)

【出願日】平成20年12月26日(2008.12.26)

【分割の表示】特願2007−240190(P2007−240190)の分割

【原出願日】平成19年9月14日(2007.9.14)

【出願人】(899000035)株式会社 東北テクノアーチ (68)

【出願人】(000165974)古河機械金属株式会社 (211)

【出願人】(000005968)三菱化学株式会社 (4,356)

【出願人】(000224798)DOWAホールディングス株式会社 (550)

【出願人】(506334160)エピバレー株式会社 (8)

【氏名又は名称原語表記】Epivalley Company Limited

【出願人】(308041646)ウェーブスクエア, インコーポレイテッド (3)

【Fターム(参考)】

【公開日】平成21年7月23日(2009.7.23)

【国際特許分類】

【出願日】平成20年12月26日(2008.12.26)

【分割の表示】特願2007−240190(P2007−240190)の分割

【原出願日】平成19年9月14日(2007.9.14)

【出願人】(899000035)株式会社 東北テクノアーチ (68)

【出願人】(000165974)古河機械金属株式会社 (211)

【出願人】(000005968)三菱化学株式会社 (4,356)

【出願人】(000224798)DOWAホールディングス株式会社 (550)

【出願人】(506334160)エピバレー株式会社 (8)

【氏名又は名称原語表記】Epivalley Company Limited

【出願人】(308041646)ウェーブスクエア, インコーポレイテッド (3)

【Fターム(参考)】

[ Back to top ]