半導体デバイス及びその製造方法

【課題】衛星放送用の送受信用増幅素子や高速データ転送用素子としての高電子移動度トランジスタや磁気センサなどの半導体デバイス及びその製造方法を提供すること。

【解決手段】基板1と、この基板1上に設けられた第1のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)2と、この第1のAlyGa1-yAszSb1-z層2の上に設けられた電子走行層としてのInxGa1-xAs層(0≦x≦1)3と、このInxGa1-xAs層3の上に設けられた第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)4とを備えている。第1のAlyGa1-yAszSb1-z層2、第2のAlyGa1-yAszSb1-z層4のいずれか一方、若しくは両方にはSnがドープされており、InxGa1-xAs電子走行層3への電子供給層となっている。

【解決手段】基板1と、この基板1上に設けられた第1のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)2と、この第1のAlyGa1-yAszSb1-z層2の上に設けられた電子走行層としてのInxGa1-xAs層(0≦x≦1)3と、このInxGa1-xAs層3の上に設けられた第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)4とを備えている。第1のAlyGa1-yAszSb1-z層2、第2のAlyGa1-yAszSb1-z層4のいずれか一方、若しくは両方にはSnがドープされており、InxGa1-xAs電子走行層3への電子供給層となっている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイス及びその製造方法に関し、より詳細には、衛星放送用の送受信用増幅素子や高速データ転送用素子として好適な高電子移動度トランジスタ(High Electron Mobility Transistor;以下、HEMTと略記する)や高感度な磁気センサなどの半導体デバイス及びその製造方法に関する。

【背景技術】

【0002】

衛星放送の送受信用増幅素子等に代表されるGHz帯の高周波素子として、HEMTが知られている。代表的なものには、GaAs基板上のGaAs層やInP基板上のIn0.53Ga0.47As層を電子走行層として用いたものなどがあり、これらはいずれも、GaAsとAlGaAs、InGaAsとInAlAsのヘテロ構造界面に蓄積する2次元電子ガス層を利用したものである。

【0003】

しかし、これらの素子によって、十数GHz帯の電波の送受信が可能な素子を得るためには、0.2μm以下の極めて短いゲート長を有するHEMTが必要になる。このような長さのゲート電極を形成するには、光リソグラフイーが用いられることもあるが、高度の技術が必要になり、安定的に生産するのは容易ではない。しかもゲート長を短くすると、ゲート抵抗の増大によるノイズの増大、さらにはゲインの低下などの原因にもなるなどトランジスタの特性としても問題が生じてくる。

【0004】

このため、微細化技術が容易で、量産性があり、かつ、従来以上に高い周波数帯に対応できる新しい構造の高周波素子が求められている。つまり、電子走行層の電子の走行速度が速く、比較的長いゲート長でも高い周波数帯に対応できる高周波素子が好ましい。さらに、このような高周波素子において、ゲート長の0.2μm以下、あるいは0.1μm以下までの一層の微細化を行なえば、更に高周波帯であるミリ波帯などへの応用も期待できるため、幅広い分野への応用が可能になる。

【0005】

これらの要求に応えるため、GaAsやIn0.53Ga0.47Asに対して、電子移動度と飽和速度が圧倒的に大きいInAsや高In濃度のInxGa1-xAsの良質な薄膜を、HEMTの電子走行層に用いる研究が行なわれている。電子移動度が高いという特徴は、ホール素子、磁気抵抗素子といった磁気センサにおいては高感度のセンサを実現するために重要な特性であり、磁気センサへの応用の点でも同様である。InAsや高In濃度のInxGa1-xAsの高い電子移動度と飽和速度は、GaAsやIn0.53Ga0.47Asを電子走行層として用いたHEMTに比べて長いゲート長を有するHEMTでも、十数GHz帯あるいは、さらに高い周波数帯に対応する高周波素子を実現できる可能性を有している。

【0006】

しかし、InAsや高In濃度のInxGa1-xAs系HEMTを実現する上では、電子供給層が如何なる材料であるかが重要な問題である。すなわち、電子供給層の伝導帯とチャネルの伝導帯との不連続の値が電子走行層へ電子を閉じ込めるために十分な大きさを持ち、電子濃度の値も適切で、かつ電子走行層であるInAsや高In濃度のInxGa1-xAsと結晶的にうまく整合がとれる材料である必要がある。

【0007】

例えば、特許文献1によると、InAsと異なる格子定数をもつ汎用性のGaAs基板上に、InAsと実質的に格子整合するAlGaAsSb層、電子走行層としてのInAs層、さらにInAsと実質的に格子整合するAlGaAsSb層を順次積層する構造をとることで、優れた高周波特性を有する電界効果トランジスタ(Field effect transistor;以下、FETと略記する)を実現している。

【0008】

ここでは、層中で発生した電子のみをキャリアとするInAs層が電子走行層として用いられており、意図的なドーピングによる電子供給は行われていない。これらのキャリアは意図せずにドープされたAlGaAsSb中のドナー不純物や、AlGaAsSbとInAsとの界面から供給されているものである。更に低いオン抵抗(大きい相互コンダクタンス)のHEMTを得るためには、InAs層のシート抵抗を下げなければならず、更に電子濃度を大きくする必要がある。つまり、InAs電子走行層の電子移動度を低下させずに、電子濃度を大きくする技術が必須となっている。このような技術の確立は、高感度で温度特性が良好な磁気センサを作成する上でも極めて重要な課題となっている。

【0009】

まず、InAsや高In濃度のInxGa1-xAs電子走行層の電子濃度を大きくする方法として、InAsや高In濃度のInxGa1-xAs電子走行層に直接ドナー不純物をドープする方法がある。ドナー不純物は、ドナー原子として作用するものなら何でも良く、例えば、Te、Se、S、Si、Snなどが挙げられる。しかし、この場合、ドナー不純物は、InAsや高In濃度のInxGa1-xAs層中で不純物散乱源となり、電子移動度は低下してしまう。

【0010】

InAsや高In濃度のInxGa1-xAs電子走行層の電子濃度を大きくするもう一つの方法として、変調ドープを用いる方法がある。この構造ではInAsや高In濃度のInxGa1-xAs電子走行層にはドナー不純物はドープされておらず、AlGaAsSb層のみにドナー不純物がドープされている。このときInAsや高In濃度のInxGa1-xAsとAlGaAsSbとの伝導帯の不連続性のためにヘテロ界面のInAsや高In濃度のInxGa1-xAs側に電子の蓄積が起こる。

【0011】

すなわち、InAsや高In濃度のInxGa1-xAsの電子親和度が大きいためAlGaAsSb層内のドナー不純物により供給された電子がInAsや高In濃度のInxGa1-xAs側に引きつけられて2次元電子ガス層を形成する。InAsや高In濃度のInxGa1-xAs層にはドナー不純物はドープされていないため、不純物散乱の影響もなく高い電子移動度を得ることができる。ここでドナー不純物がドープされる位置は、AlGaAsSb層の厚さ方向に均一でも良く、分布があっても良い。例えば、AlGaAsSb層にドナー不純物がデルタドープされていても良い。

【0012】

III−V族化合物半導体のn型ドーパントとしては、一般にTe、Se、S、Sn、Siなどが知られているが、なかでもIV族元素Siが最も広く使われている。Siは蒸気圧が低いので、標準の分子線エピタキシー(以下、MBEと略記する)プロセスにおいて使用されるフラックスソースの温度範囲において、その制御が容易なためである。

【0013】

しかしながら、AlSbやGaSbなどのアンチモン化合物中においては、Siはアクセプタ不純物として働く(例えば、非特許文献1参照)ことが明らかになってきている。更に、AlSbとGaSbとの混晶であるAlGaSbや、InAsあるいは高In濃度のInxGa1-xAsと格子定数の近いAlGaAsSbにおいても、Siはアクセプタ不純物であり、AlGaAsSbの電子供給層を形成することができない。

【0014】

そのため、AlGaAsSb層へのドナー不純物としては、AlSbやGaSbなどのアンチモン化合物中においても、ドナー不純物として十分に働くVI族元素であるTeなどが用いられる(例えば、非特許文献1参照)。しかしながら、Teは蒸気圧が非常に高いため、標準のMBEプロセスにおいて使用されるフラックスソースの温度範囲が非常に低く、ドーピング量を急激に変えることが難しく、その制御が容易ではない。更に、Teは蒸気圧が非常に高いため、MBE装置内に非常に残留しやすくなる。この残留物はMBE装置を汚染し、そして、同装置を用いた後プロセスのp型プロセスの妨げにもなり、工業上好ましくない。

【0015】

従って、AlGaAsSb層へのドナー不純物としては、取り扱いが容易なIV族元素を用いることが好ましい。Siと同じくIV族元素であるSnも比較的蒸気圧が低く、取り扱いやすいドーパント材料である。非特許文献1によると、SnもAlSbやGaSbなどのアンチモン化合物中においてアクセプタ不純物として働く旨の記述がある。しかし、実際にAlGaAsSb層にSnをドープした場合、InAs電子走行層への電子供給層として働くかは明らかではなかった。このため、InAsや高In濃度のInxGa1-xAs電子走行層に対し、電子供給層として機能するAlGaAsSb層を用いたHEMT、もしくは磁気センサは実現できなかった。

【0016】

【特許文献1】特開平5−90301号公報(特許3200142号公報)

【非特許文献1】Physica E20 (2004) 196−203, Herbert Kroemer, UCSB

【発明の開示】

【発明が解決しようとする課題】

【0017】

上述したように、蒸気圧が低いIV族元素をドナー不純物として用いることで、InAsや高In濃度のInxGa1-xAs電子走行層の電子濃度を、MBE装置を汚染することなく精度良く容易に制御し、かつInAsや高In濃度のInxGa1-xAs電子走行層の電子移動度を低下させずに、電子濃度を大きくする技術は確立されていなかった。

【0018】

本発明は、このような状況に鑑みてなされたもので、その目的とするところは、蒸気圧が低いIV族元素Snをドナー不純物として用いることで、InAsや高In濃度のInxGa1-xAsチャネル層の電子濃度を、MBE装置を汚染することなく精度良く容易に制御し、かつInAsや高In濃度のInxGa1-xAs電子走行層の電子移動度を低下させずに、電子濃度を大きくする技術を確立することで、優れた高周波特性を有するHEMTや高感度な磁気センサなどの半導体デバイス及びその製造方法を提供することにある。

【課題を解決するための手段】

【0019】

本発明は、このような目的を達成するために、請求項1に記載の発明は、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスであって、少なくとも1層以上の前記AlyGa1-yAszSb1-z層にはSnがドープされており、電子走行層である前記InxGa1-xAs層への電子供給層となっていることを特徴とする。

【0020】

また、請求項2に記載の発明は、請求項1に記載の発明において、前記AlyGa1-yAszSb1-z層中には、SnがドープされたAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)が設けられていることを特徴とする。

【0021】

また、請求項3に記載の発明は、請求項1に記載の発明において、前記AlyGa1-yAszSb1-z層中には、Snのデルタドープ層が設けられていることを特徴とする。

【0022】

また、請求項4に記載の発明は、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスであって、基板と、該基板上に設けられた第1のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)と、該第1のAlyGa1-yAszSb1-z層の上に設けられた電子走行層としてのInxGa1-xAs層(0≦x≦1)と、該InxGa1-xAs層の上に設けられた第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とを備え、前記第1又は第2のAlyGa1-yAszSb1-z層のうち、少なくとも一方のAlyGa1-yAszSb1-z層にはSnがドープされており、前記InxGa1-xAs層への電子供給層となっていることを特徴とする。

【0023】

また、請求項5に記載の発明は、請求項4に記載の発明において、前記AlyGa1-yAszSb1-z層中には、SnがドープされたAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)が設けられていることを特徴とする。

【0024】

また、請求項6に記載の発明は、請求項4に記載の発明において、前記AlyGa1-yAszSb1-z層中には、Snのデルタドープ層が設けられていることを特徴とする。

【0025】

また、請求項7に記載の発明は、請求項2又は5に記載の発明において、前記InxGa1-xAsと前記SnがドープされたAlyGa1-yAszSb1-z層との間にある、Snがドープされていない前記AlyGa1-yAszSb1-z層の膜厚は、2.5nm以上20nm以下であることを特徴とする。

【0026】

また、請求項8に記載の発明は、請求項3又は6に記載の発明において、前記InxGa1-xAsと前記デルタドープ層との間にある、Snがドープされていない前記AlyGa1-yAszSb1-z層の膜厚は、2.5nm以上20nm以下であることを特徴とする。

【0027】

また、請求項9に記載の発明は、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスの製造方法であって、基板上に、アンドープの第1のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層を形成する工程と、該第1のAlyGa1-yAszSb1-z層の上に、電子走行層としてのInxGa1-xAs層(0≦x≦1)を形成する工程と、該InxGa1-xAs層の上に、アンドープの第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する工程と、該AlyGa1-yAszSb1-z層の上にSnのデルタドープ層を形成する工程と、該Snのデルタドープ層の上にアンドープの第3のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する工程とを有することを特徴とする。

【0028】

また、請求項10に記載の発明は、請求項9に記載の発明において、前記デルタドープ層を形成する工程は、分子線エピタキシー法によりSnとSbとを同時に、若しくはSnとAsとSbとを同時に照射することを特徴とする。

【0029】

また、請求項11に記載の発明は、請求項1乃至8のいずれかに記載の半導体デバイスと、前記半導体デバイス上にオーミック接合されたソース電極及びドレイン電極と、前記半導体デバイス上に設けられたゲート電極とを備えることを特徴とする高電子移動度トランジスタである。

【0030】

また、請求項12に記載の発明は、請求項1乃至8のいずれかに記載の半導体デバイスと、前記半導体デバイス上に形成されたオーミック電極とを備えることを特徴とする磁気センサである。

【発明の効果】

【0031】

本発明によれば、AlGaAsSb電子供給層のドナー不純物として、蒸気圧が低く、取り扱いが容易なIV族元素Snを用いることにより、MBE装置を汚染することなく、容易にInxGa1-xAsチャネル層の電子濃度を制御することができる。従って、高い電子濃度と高い電子移動度をもつInxGa1-xAsチャネル層を工業的に安定して製造することができるため、衛星放送の送受信用増幅素子や高速データ転送用素子として、優れた高周波特性を有するHEMTや高感度な磁気センサなどの半導体デバイス及びその製造方法を提供することができる。

【発明を実施するための最良の形態】

【0032】

以下、図面を参照して本発明の実施形態について説明する。

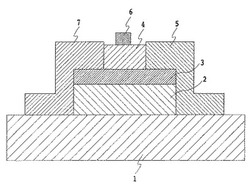

図1は、本発明による高電子移動度トランジスタ(HEMT)の一実施形態を説明するための断面図で、符号1は基板、2は第1のAlyGa1-yAszSb1-z層、3はInxGa1-xAs電子走行層、4は第2のAlyGa1-yAszSb1-z層を示している。5と7は1対のオーミック電極であり、5はソース電極、7はドレイン電極である。6はソース電極5とドレイン電極7の間に設けられたゲート電極である。

【0033】

本発明の高電子移動度トランジスタ(HEMT)は、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスである。具体的には、基板1と、この基板1上に設けられた第1のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)2と、この第1のAlyGa1-yAszSb1-z層2の上に設けられた電子走行層としてのInxGa1-xAs層(0≦x≦1)3と、このInxGa1-xAs層3の上に設けられた第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)4とを備えている。

【0034】

ここで、第1のAlyGa1-yAszSb1-z層2、第2のAlyGa1-yAszSb1-z層4のいずれか一方、若しくは両方にはSnがドープされており、InxGa1-xAs電子走行層3への電子供給層となっている。また、第1のAlyGa1-yAszSb1-z層2、第2のAlyGa1-yAszSb1-z層4のいずれか一方が存在しないか、若しくは他の半導体材料となっている場合でも、SnがドープされたAlyGa1-yAszSb1-z層とInxGa1-xAs電子走行層3とのヘテロ接合を、少なくとも一つ有している薄膜構造となっていれば、本発明の技術的範囲内である。以下、各構成要素について説明する。

【0035】

本発明に用いられる基板1は、基板であれば何でも良いが、GaAs基板、もしくはGaP基板、表面に単結晶のGaAsを成長させたSi基板、サファイア基板などが好適である。なかでも半絶縁性で良質の単結晶基板が得られるGaAs基板は、特に好ましい。ここで言う半絶縁性とは、抵抗率が107Ω・cm以上のものを指す。単結晶基板を用いる場合、基板の面方位は(100)、(111)、(110)等が好ましい。これらの面方位から1°から5°ずらした面方位を用いることもある。中でも(100)は良質の薄膜を成長させる上で最適である。通常行われるように、基板表面を平坦化させ、清浄化させる目的で、基板と同じ材質の半導体を成長させたものを本発明の基板として使用しても良い。GaAs基板上にGaAsを成長させるのは、この最も代表的な1例である。

【0036】

本発明に用いられる第1のAlyGa1-yAszSb1-z層2は、(a)InxGa1-xAs電子走行層3との格子定数が近く、(b)InxGa1-xAs電子走行層3と比べて抵抗率が十分高く、(c)InxGa1-xAs電子走行層3と大きく格子定数の異なるGaAs等の基板上に直接積層した場合でも、欠陥の少ない平坦な表面を有していることが好ましい。第1のAlyGa1-yAszSb1-z層2とInxGa1‐xAs電子走行層3の格子定数は、InxGa1‐xAs電子走行層3の膜厚が臨界膜厚を超えない程度に近ければ良い。例えば、InxGa1-xAs電子走行層3の膜厚が15nmの場合、第1のAlyGa1-yAszSb1-z層2とInxGa1-xAs電子走行層3の格子定数は1.3%以内で一致していることが好ましい。

【0037】

InxGa1-xAs(0≦x≦1)電子走行層3のIn組成xが0.53以上1以下の場合、第1のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層2のAs組成zは0以上0.7以下であることが好ましい。第1のAlyGa1-yAszSb1-z層2の抵抗率は、Al組成yが大きいほど高くなる一方、素子化プロセス中に酸化しやすいという懸念があり、Al組成yは0.5以上0.8以下の範囲であることが好ましい。

【0038】

第1のAlyGa1-yAszSb1-z層2の表面の平坦性は、膜厚が厚いほど良好であるが、工業上はなるべく薄くすることが望ましい。すなわち、膜厚は5nm以上3000nm以下の範囲が好ましく、より好ましくは10nm以上1000nmである。第1のAlyGa1-yAszSb1-z層2をInxGa1‐xAs電子走行層3への電子供給層として用いる場合、Snは厚さ方向に均一にドープされていても、分布があっても良く、デルタドープされていても良い。特にInxGa1-xAs電子走行層3との界面近傍の第1のAlyGa1-yAszSb1-z層2にはSnをドープしない構造にすることによって、不純物散乱の影響を低減でき、高い電子移動度を得ることができるため好ましい。

【0039】

ここでデルタドープとは、分子線エピタキシー法を用いたIII−V族化合物半導体の薄膜成長において、ドーパントとV族元素を同時に照射して行なうドーピングの手法である。III族元素を照射しないため、薄膜の成長は進行しない状態でのドーピングとなる。その結果、デルタドープ層の膜厚は限りなくゼロに近く、厳密には数原子層程度の膜厚である。デルタドープは所望の場所に、所望の量のドーピングが可能であり好ましい。

【0040】

本発明に用いられるInxGa1-xAs(0≦x≦1)電子走行層3は、制御電極にかかる電圧によって電気伝導を制御する都合上、膜厚は2000nm以下が好ましい。より好ましくは、5nm以上100nm以下である。また、InxGa1-xAs電子走行層3の電子濃度は、3×1017cm-3以上2×1018cm-3以下のとき、高い電子移動度を有し、好ましい。InxGa1-xAs(0≦x≦1)電子走行層3は、In組成xが大きいほど高い電子移動度が得られるので好ましく、特にIn組成xは0.53以上1以下であることが好ましい。

【0041】

本発明に用いられる第2のAlyGa1-yAszSb1-z層4は、(a)InxGa1-xAs電子走行層3との格子定数が近く、(b)InxGa1-xAs電子走行層3と比べて抵抗率が十分高いことが好ましい。第2のAlyGa1-yAszSb1-z層4とInxGa1‐xAs電子走行層3の格子定数は、InxGa1‐xAs電子走行層3の膜厚が臨界膜厚を超えない程度に近ければ良い。例えば、InxGa1-xAs電子走行層3の膜厚が15nmの場合、第2のAlyGa1-yAszSb1-z層4とInxGa1-xAs電子走行層3の格子定数は1.3%以内で一致していることが好ましい。InxGa1-xAs(0≦x≦1)電子走行層3のIn組成xが0.53以上1以下の場合、第2のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層4のAs組成zは0以上0.7以下であることが好ましい。

【0042】

第2のAlyGa1-yAszSb1-z層4の抵抗率は、Al組成yが大きいほど高くなる一方、素子化プロセス中に酸化しやすいという懸念があり、Al組成yは0.5以上0.8以下の範囲であることが好ましい。第2のAlyGa1-yAszSb1-z層4の膜厚は、5nm以上100nmの範囲が好ましい。第2のAlyGa1-yAszSb1-z層4をInxGa1‐xAsチャネル層3への電子供給層として用いる場合、Snは厚さ方向に均一にドープされていても、分布があっても良く、デルタドープされていても良い。特に、ゲート電極6が形成される側の界面近傍のみ、Snをドープしない構造にすると、ゲート耐圧が低下せず良好である。

【0043】

また、InxGa1-xAs電子走行層3との界面近傍の第2のAlyGa1-yAszSb1-z層4には、Snをドープしない構造にすることによって、不純物散乱の影響を低減でき、高い電子移動度を得ることができるため好ましい。第1のAlyGa1-yAszSb1-z層2と第2のAlyGa1-yAszSb1-z層4は、同じ組成である方が製造工程を簡略化できるため好ましいが、異なる組成であっても良く、必要に応じて適宜実施される。

【0044】

本発明に用いられるソース電極5、及びドレイン電極7は、その下部のInxGa1-xAs電子走行層3とオーミック接合をとる必要がある。オーミック接合には、各種の構造があるが、図1では、InxGa1-xAs電子走行層3に直接接合する構造をとっている。InxGa1-xAs電子走行層3はバンドギャップが狭く、電極をコンタクトしただけで、接触抵抗の低いオーミック接合が得られる。このためオーミック電極5、7の下部のみ、第2のAlyGa1-yAszSb1-z層4をエッチングして、InxGa1-xAsチャネル層3に直接電極を形成することができる。この場合、電極5、7とInxGa1-xAsチャネル層3の間の接触抵抗を低減するために、合金化過程を行っても良いが、蒸着しただけでも良好なオーミック接合が得られる。このため、電極金属はAuGe/Ni/Auの3層構造をはじめとする公知の積層電極構造でも良いが、Al、Ti、Au、Wなどの単層の金属でも良く、極めて多くの組み合わせが可能である。

【0045】

本発明に用いられるゲート電極6は、その下部に空乏層を形成できるものであれば良く、ショットキー接合を用いる方法のほか、ゲート電極とInxGa1-xAs電子走行層3の間に、絶縁物を挟んだMIS(METAL−INSULATOR−SEMICONDUCTOR)構造や、PN接合を利用することもできる。特に、第2のAlyGa1-yAszSb1-z層4とショットキー接合を形成する材料としては、Al、Ti、W、Pt、WSi、Auなどが好ましく、これらを積層構造にしたものも良い。

【0046】

図10は、本発明による高電子移動度トランジスタの製造方法を説明するためのフローチャートを示す図である。

本発明の高電子移動度トランジスタは、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスの製造方法である。

【0047】

まず、ステップ1(S1)において、基板上に、アンドープの第1のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層を形成する。次に、ステップ2(S2)において、第1のAlyGa1-yAszSb1-z層の上に、電子走行層としてのInxGa1-xAs層(0≦x≦1)を形成する。次に、ステップ3(S3)において、InxGa1-xAs層の上に、アンドープの第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する。次に、ステップ4(S4)において、AlyGa1-yAszSb1-z層の上にSnのデルタドープ層を形成する。最後に、ステップ5(S5)において、Snのデルタドープ層の上にアンドープの第3のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する。また、デルタドープ層を設けるステップ4は、分子線エピタキシー法によりSnとSbとを同時に、若しくはSnとAsとSbとを同時に照射する。

【0048】

以下に本発明の具体的な実施例について述べるが、本発明はこれらの実施例のみに限定されるものではない。

[実施例1]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.53Ga0.47Sb層を成長した。また、本実施例では、Al0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47Sb層上に成長した。

【0049】

この薄膜積層体の電気的特性をファンデルポー法、ホール測定により評価した結果、電子移動度は30300cm2/Vs、シート電子濃度1.60×1012cm-2であった。ここで、電子移動度は単位電界あたりの電子の動く速度、シート電子濃度は、1cm2当たりの電子の数である。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。この結果から、従来アクセプタとして働くといわれていたIV族元素Snは、ドナーとして働くことが明らかとなった。TeなどのVI族元素に比べて、蒸気圧が低く、取り扱いが容易で、チャンバの汚染の恐れがないIV族元素Snで、電子走行層の電子濃度を制御できることは、工業上極めて好ましい。

【0050】

これらの薄膜積層体において、メサエッチ工程を経た後、ソース電極、ドレイン電極を形成する箇所をエッチングすることでInAs表面を露出させ、InAs上に直接ソース電極、ドレイン電極を形成し、さらにGaAsキャップ層上にゲート電極を形成することで、高電子移動度トランジスタHEMTを作製した。

【0051】

本実施例においては、Snデルタドープ層をInAsとAl0.53Ga0.47Sb層との界面から5nm離れた部位に、Snセル温度を950℃に加熱した状態で、56秒間照射することで形成している。

【0052】

ここで、Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)、Snを照射する時間をそれぞれ変化させたときの、薄膜積層体のシート電子濃度の値を図2及び図3に示す。

【0053】

図2は、Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)と薄膜積層体のシート電子濃度の関係をグラフに示した図で、図3は、Snを照射した時間と薄膜積層体のシート電子濃度の関係をグラフに示した図である。

【0054】

このときのSnセル温度は950℃である。図2からドープ位置が近いとシート電子濃度が高く、ドープ位置が遠いとシート電子濃度が低いことがわかった。AlGaAsSb電子供給層中の電子が、InAs電子走行層に落ち込む電子の確率が、ドープ位置が遠くなるに従って減少するためと考えられる。図3からは、Snの照射する時間を長くするほど、シート電子濃度は単調に増加することがわかった。これらの結果から、Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)、Snを照射する時間を制御するだけで、薄膜積層体のシート電子濃度を容易に制御することができることを見出した。

【0055】

図4は、薄膜積層体のシート電子濃度と電子移動度の関係をグラフに示した図である。ここにはSnのドープ位置を2.5nmから20nm、Snセル温度を930℃から970℃、Sn照射時間を0秒から94秒まで変化させた、全データをプロットした。この図4からシート電子濃度が5×1011cm-2以上3×1012cm-3以下、すなわち、電子濃度3×1017cm-3以上2×1018cm-3以下で高い電子移動度を有していることがわかる。特に1.2×1012cm-2以上1.6×1012cm-2以下、すなわち、電子濃度8×1017cm-3以上1.1×1018cm-3以下では電子移動度は30000cm2/Vs以上であり好ましい。

【0056】

図5は、薄膜積層体のSnデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)と電子移動度の関係をグラフに示した図である。このときのSnセル温度は950℃、Snの照射時間は56秒としている。ドープする位置を近づけすぎると、InAsがSnの不純物散乱の影響を受けてしまうので電子移動度は低下してしまう。逆にドープする位置が遠いと、シート電子濃度は低くなってしまうため、電子移動度は低下する。電子移動度は27000(cm2/Vs)以上であることが好ましく、図5の結果から、Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)は、2.5nm以上20nm以下であることが好ましい。

【0057】

[実施例2]

上述した薄膜積層体をメサエッチ工程により、十字型に成形した後、電極を形成する箇所のみエッチングすることでInAs表面を露出させ、InAs上に電極を形成することで、磁気センサであるホール素子を作製した。

【0058】

図6は、作製したホール素子の構造を示す断面図で、図7は、作製したホール素子の構造を示す上面図である。なお、符号9はオーミック電極を示している。

【0059】

このとき用いた薄膜積層体の電気的特性は、電子移動度30300cm2/Vs、シート抵抗158Ω、シート電子濃度1.30×1012cm-2である。本例のホール素子で得られた特性は、入力抵抗値が300Ω、定電圧1Vで駆動したとき、50mTの磁束密度の印加でホール電圧が75mVであった。すなわち、磁界での感度は、75mV/V・50mTの高感度を示した。

【0060】

[実施例3]

上述した実施例1の薄膜積層体を用いて、磁気センサである磁気抵抗素子を作製した。このとき用いた薄膜積層体の電気的特性は、電子移動度30700cm2/Vs、シート抵抗144Ω、シート電子濃度1.42×1012cm-2である。

【0061】

図8は、作製した磁気抵抗素子の構造を示す断面図で、図9は、作製した磁気抵抗素子の構造を示す上面図である。

メサエッチ工程により、短冊状に成形した後、電極を形成する箇所のみエッチングすることでInAs表面を露出させ、InAs上にオーミック電極9、短絡電極10を形成することで磁気抵抗素子を作製した。端子電極部を除いてInAsの薄膜からなる磁気抵抗素子部の長さが1450μm、InAs薄膜の幅が120μm、幅120μmのInAs磁気抵抗素子部を跨いで形成されたCu/Ni/Au/Niの4層からなる短絡電極は長さ120μmでその幅は9μmであり、等間隔でInAs薄膜に直接接触して形成した。電極間の抵抗値は磁界の印加がない場合は1200Ωであった。

【0062】

磁気抵抗素子を磁気センサとして使うときに加えられる磁束密度領域、すなわち、磁気抵抗変化が磁束密度に直線的に変化する磁束密度の領域でもあり、かつ、高感度で微弱な磁界変化を検出するためのバイアス磁束密度の領域でもある0.45Tの磁束密度のときの絶対的な抵抗変化率は160%であり、極めて大きな磁気抵抗変化示した。

【0063】

[実施例4]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に75秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nm のアンドープAl0.53Ga0.47Sb層を成長した。また、今回の実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47Sb層上に成長した。

【0064】

この薄膜積層体の電子移動度は28000cm2/Vs、シート電子濃度2.16×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。実施例1と比較して、電子移動度はやや低下するものの、Snの照射時間を長くすることで、より高いシート電子濃度の特性を得ることができる。

【0065】

[実施例5]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚35nmのSnをドープしたAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をSnドープAl0.53Ga0.47Sb層上に成長した。

【0066】

この薄膜積層体の電子移動度は24300cm2/Vs、シート電子濃度2.11×1012cm-2であった。Snのドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snドープ層の効果は非常に大きいことがわかった。

【0067】

[実施例6]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚20nmのSnをドープしたAl0.53Ga0.47Sb層を成長した後、膜厚15nmのアンドープのAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をSnドープAl0.53Ga0.47Sb層上に成長した。

【0068】

この薄膜積層体の電子移動度は25100cm2/Vs、シート電子濃度1.88×1012cm-2であった。Snのドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snドープ層の効果は非常に大きいことがわかった。

【0069】

[実施例7]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープのAl0.53Ga0.47Sb層を成長した後、膜厚30nmのSnをドープしたAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をSnドープAl0.53Ga0.47Sb層上に成長した。

【0070】

この薄膜積層体の電子移動度は29500cm2/Vs、シート電子濃度1.36×1012cm-2であった。Snのドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snドープ層の効果は非常に大きいことがわかった。

【0071】

[実施例8]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更にその上に膜厚5nmのアンドープのAl0.53Ga0.47Sb層、膜厚15nmのSnをドープしたAl0.53Ga0.47Sb層、膜厚15nmのアンドープのAl0.53Ga0.47Sb層を順次成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をSnドープAl0.53Ga0.47Sb層上に成長した。

【0072】

この薄膜積層体の電子移動度は30100cm2/Vs、シート電子濃度1.31×1012cm-2であった。Snのドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snドープ層の効果は非常に大きいことがわかった。

【0073】

[実施例9]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚595nmのアンドープAl0.53Ga0.47Sb層を成長した後、Snのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚5nmのアンドープAl0.53Ga0.47Sb層を成長した。更に、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長した後、膜厚35nmのアンドープAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47Sb層上に成長した。

【0074】

この薄膜積層体の電子移動度は30500cm2/Vs、シート電子濃度1.49×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較しても、同等の特性が得られており、InAs電子走行層の下層のAlGaAsSb層も、Snをドープすることで電子供給層として働くことが明らかとなった。

【0075】

[実施例10]

薄膜形成方法の一例として分子線エピタキシー法(MBE法)を用いた場合について詳細に述べる。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱し表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてInAsキャップ層をアンドープAl0.53Ga0.47Sb層上に成長した。

【0076】

この薄膜積層体の電子移動度は29500cm2/Vs、シート電子濃度1.26×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は23300cm2/Vs、シート電子濃度5.4×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して同等の特性が得られており、キャップ層をInAsにした場合でも、Snデルタドープ層の効果は非常に大きい。

【0077】

[実施例11]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.65Ga0.35Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.65Ga0.35Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.65Ga0.35Sb層を成長した。また、本実施例ではAl0.65Ga0.35Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.65Ga0.35Sb層上に成長した。

【0078】

この薄膜積層体の電子移動度は28700cm2/Vs、シート電子濃度1.39×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は21500cm2/Vs、シート電子濃度5.1×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度はやや低下するものの、Snデルタドープ層の効果は非常に大きい。

【0079】

[実施例12]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.8Ga0.2Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.8Ga0.2Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.8Ga0.2Sb層を成長した。また、本実施例ではAl0.8Ga0.2Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.8Ga0.2Sb層上に成長した。

【0080】

この薄膜積層体の電子移動度は25700cm2/Vs、シート電子濃度1.41×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は17100cm2/Vs、シート電子濃度4.1×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度はやや低下するものの、Snデルタドープ層の効果は非常に大きい。

【0081】

[実施例13]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を成長した。また、本実施例ではAl0.53Ga0.47As0.13Sb0.87層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47As0.13Sb0.87層上に成長した。

【0082】

この薄膜積層体の電子移動度は23000cm2/Vs、シート電子濃度1.67×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は15800cm2/Vs、シート電子濃度3.2×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度はやや低下するものの、Snデルタドープ層の効果は非常に大きい。

【0083】

[実施例14]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を成長した後、基板温度を460℃に保持しながら膜厚30nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nm のアンドープAl0.53Ga0.47As0.13Sb0.87層を成長した。また、本実施例ではAl0.53Ga0.47As0.13Sb0.87層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47As0.13Sb0.87層上に成長した。

【0084】

この薄膜積層体の電子移動度は24700cm2/Vs、シート電子濃度1.86×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は21300cm2/Vs、シート電子濃度5.6×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例13と比較して、より高い電子移動度、シート電子濃度を得ることができる。

【0085】

[実施例15]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47As0.3Sb0.7層を成長した後、基板温度を460℃に保持しながら膜厚15nmのIn0.8Ga0.2As層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47As0.3Sb0.7層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.53Ga0.47As0.3Sb0.7層を成長した。また、本実施例ではAl0.53Ga0.47As0.3Sb0.7層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47As0.3Sb0.7層上に成長した。

【0086】

この薄膜積層体の電子移動度は11300cm2/Vs、シート電子濃度1.42×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は5600cm2/Vs、シート電子濃度5×1010cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度は低下するものの、Snデルタドープ層の効果は非常に大きい。

【0087】

[実施例16]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47As0.2Sb0.8層を成長した後、基板温度を460℃に保持しながら膜厚15nmのIn0.8Ga0.2As層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47As0.2Sb0.8層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nm のアンドープAl0.53Ga0.47As0.2Sb0.8層を成長した。また、本実施例ではAl0.53Ga0.47As0.2Sb0.8層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47As0.2Sb0.8層上に成長した。

【0088】

この薄膜積層体の電子移動度は11700cm2/Vs、シート電子濃度1.29×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は8100cm2/Vs、シート電子濃度2.4×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度はやや低下するものの、Snデルタドープ層の効果は非常に大きい。

【図面の簡単な説明】

【0089】

【図1】本発明による高電子移動度トランジスタ(HEMT)の一実施形態を説明するための断面図である。

【図2】Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)と薄膜積層体のシート電子濃度の関係をグラフに示した図である。

【図3】Snを照射した時間と薄膜積層体のシート電子濃度の関係をグラフに示した図である。

【図4】薄膜積層体のシート電子濃度と電子移動度の関係をグラフに示した図である。

【図5】薄膜積層体のSnデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)と電子移動度の関係をグラフに示した図である。

【図6】作製したホール素子の構造を示す断面図である。

【図7】作製したホール素子の構造を示す上面図である。

【図8】作製した磁気抵抗素子の構造を示す断面図である。

【図9】作製した磁気抵抗素子の構造を示す上面図である。

【図10】本発明による高電子移動度トランジスタ(HEMT)の製造方法を説明するためのフローチャートを示す図である。

【符号の説明】

【0090】

1 基板

2 第1のAlyGa1-yAszSb1-z層

3 InxGa1-xAs電子走行層

4 第2のAlyGa1-yAszSb1-z層

5 ソース電極、

6 ソース電極5とドレイン電極7の間に設けられたゲート電極

7 ドレイン電極

8 薄膜積層体

9 オーミック電極

10 短絡電極

【技術分野】

【0001】

本発明は、半導体デバイス及びその製造方法に関し、より詳細には、衛星放送用の送受信用増幅素子や高速データ転送用素子として好適な高電子移動度トランジスタ(High Electron Mobility Transistor;以下、HEMTと略記する)や高感度な磁気センサなどの半導体デバイス及びその製造方法に関する。

【背景技術】

【0002】

衛星放送の送受信用増幅素子等に代表されるGHz帯の高周波素子として、HEMTが知られている。代表的なものには、GaAs基板上のGaAs層やInP基板上のIn0.53Ga0.47As層を電子走行層として用いたものなどがあり、これらはいずれも、GaAsとAlGaAs、InGaAsとInAlAsのヘテロ構造界面に蓄積する2次元電子ガス層を利用したものである。

【0003】

しかし、これらの素子によって、十数GHz帯の電波の送受信が可能な素子を得るためには、0.2μm以下の極めて短いゲート長を有するHEMTが必要になる。このような長さのゲート電極を形成するには、光リソグラフイーが用いられることもあるが、高度の技術が必要になり、安定的に生産するのは容易ではない。しかもゲート長を短くすると、ゲート抵抗の増大によるノイズの増大、さらにはゲインの低下などの原因にもなるなどトランジスタの特性としても問題が生じてくる。

【0004】

このため、微細化技術が容易で、量産性があり、かつ、従来以上に高い周波数帯に対応できる新しい構造の高周波素子が求められている。つまり、電子走行層の電子の走行速度が速く、比較的長いゲート長でも高い周波数帯に対応できる高周波素子が好ましい。さらに、このような高周波素子において、ゲート長の0.2μm以下、あるいは0.1μm以下までの一層の微細化を行なえば、更に高周波帯であるミリ波帯などへの応用も期待できるため、幅広い分野への応用が可能になる。

【0005】

これらの要求に応えるため、GaAsやIn0.53Ga0.47Asに対して、電子移動度と飽和速度が圧倒的に大きいInAsや高In濃度のInxGa1-xAsの良質な薄膜を、HEMTの電子走行層に用いる研究が行なわれている。電子移動度が高いという特徴は、ホール素子、磁気抵抗素子といった磁気センサにおいては高感度のセンサを実現するために重要な特性であり、磁気センサへの応用の点でも同様である。InAsや高In濃度のInxGa1-xAsの高い電子移動度と飽和速度は、GaAsやIn0.53Ga0.47Asを電子走行層として用いたHEMTに比べて長いゲート長を有するHEMTでも、十数GHz帯あるいは、さらに高い周波数帯に対応する高周波素子を実現できる可能性を有している。

【0006】

しかし、InAsや高In濃度のInxGa1-xAs系HEMTを実現する上では、電子供給層が如何なる材料であるかが重要な問題である。すなわち、電子供給層の伝導帯とチャネルの伝導帯との不連続の値が電子走行層へ電子を閉じ込めるために十分な大きさを持ち、電子濃度の値も適切で、かつ電子走行層であるInAsや高In濃度のInxGa1-xAsと結晶的にうまく整合がとれる材料である必要がある。

【0007】

例えば、特許文献1によると、InAsと異なる格子定数をもつ汎用性のGaAs基板上に、InAsと実質的に格子整合するAlGaAsSb層、電子走行層としてのInAs層、さらにInAsと実質的に格子整合するAlGaAsSb層を順次積層する構造をとることで、優れた高周波特性を有する電界効果トランジスタ(Field effect transistor;以下、FETと略記する)を実現している。

【0008】

ここでは、層中で発生した電子のみをキャリアとするInAs層が電子走行層として用いられており、意図的なドーピングによる電子供給は行われていない。これらのキャリアは意図せずにドープされたAlGaAsSb中のドナー不純物や、AlGaAsSbとInAsとの界面から供給されているものである。更に低いオン抵抗(大きい相互コンダクタンス)のHEMTを得るためには、InAs層のシート抵抗を下げなければならず、更に電子濃度を大きくする必要がある。つまり、InAs電子走行層の電子移動度を低下させずに、電子濃度を大きくする技術が必須となっている。このような技術の確立は、高感度で温度特性が良好な磁気センサを作成する上でも極めて重要な課題となっている。

【0009】

まず、InAsや高In濃度のInxGa1-xAs電子走行層の電子濃度を大きくする方法として、InAsや高In濃度のInxGa1-xAs電子走行層に直接ドナー不純物をドープする方法がある。ドナー不純物は、ドナー原子として作用するものなら何でも良く、例えば、Te、Se、S、Si、Snなどが挙げられる。しかし、この場合、ドナー不純物は、InAsや高In濃度のInxGa1-xAs層中で不純物散乱源となり、電子移動度は低下してしまう。

【0010】

InAsや高In濃度のInxGa1-xAs電子走行層の電子濃度を大きくするもう一つの方法として、変調ドープを用いる方法がある。この構造ではInAsや高In濃度のInxGa1-xAs電子走行層にはドナー不純物はドープされておらず、AlGaAsSb層のみにドナー不純物がドープされている。このときInAsや高In濃度のInxGa1-xAsとAlGaAsSbとの伝導帯の不連続性のためにヘテロ界面のInAsや高In濃度のInxGa1-xAs側に電子の蓄積が起こる。

【0011】

すなわち、InAsや高In濃度のInxGa1-xAsの電子親和度が大きいためAlGaAsSb層内のドナー不純物により供給された電子がInAsや高In濃度のInxGa1-xAs側に引きつけられて2次元電子ガス層を形成する。InAsや高In濃度のInxGa1-xAs層にはドナー不純物はドープされていないため、不純物散乱の影響もなく高い電子移動度を得ることができる。ここでドナー不純物がドープされる位置は、AlGaAsSb層の厚さ方向に均一でも良く、分布があっても良い。例えば、AlGaAsSb層にドナー不純物がデルタドープされていても良い。

【0012】

III−V族化合物半導体のn型ドーパントとしては、一般にTe、Se、S、Sn、Siなどが知られているが、なかでもIV族元素Siが最も広く使われている。Siは蒸気圧が低いので、標準の分子線エピタキシー(以下、MBEと略記する)プロセスにおいて使用されるフラックスソースの温度範囲において、その制御が容易なためである。

【0013】

しかしながら、AlSbやGaSbなどのアンチモン化合物中においては、Siはアクセプタ不純物として働く(例えば、非特許文献1参照)ことが明らかになってきている。更に、AlSbとGaSbとの混晶であるAlGaSbや、InAsあるいは高In濃度のInxGa1-xAsと格子定数の近いAlGaAsSbにおいても、Siはアクセプタ不純物であり、AlGaAsSbの電子供給層を形成することができない。

【0014】

そのため、AlGaAsSb層へのドナー不純物としては、AlSbやGaSbなどのアンチモン化合物中においても、ドナー不純物として十分に働くVI族元素であるTeなどが用いられる(例えば、非特許文献1参照)。しかしながら、Teは蒸気圧が非常に高いため、標準のMBEプロセスにおいて使用されるフラックスソースの温度範囲が非常に低く、ドーピング量を急激に変えることが難しく、その制御が容易ではない。更に、Teは蒸気圧が非常に高いため、MBE装置内に非常に残留しやすくなる。この残留物はMBE装置を汚染し、そして、同装置を用いた後プロセスのp型プロセスの妨げにもなり、工業上好ましくない。

【0015】

従って、AlGaAsSb層へのドナー不純物としては、取り扱いが容易なIV族元素を用いることが好ましい。Siと同じくIV族元素であるSnも比較的蒸気圧が低く、取り扱いやすいドーパント材料である。非特許文献1によると、SnもAlSbやGaSbなどのアンチモン化合物中においてアクセプタ不純物として働く旨の記述がある。しかし、実際にAlGaAsSb層にSnをドープした場合、InAs電子走行層への電子供給層として働くかは明らかではなかった。このため、InAsや高In濃度のInxGa1-xAs電子走行層に対し、電子供給層として機能するAlGaAsSb層を用いたHEMT、もしくは磁気センサは実現できなかった。

【0016】

【特許文献1】特開平5−90301号公報(特許3200142号公報)

【非特許文献1】Physica E20 (2004) 196−203, Herbert Kroemer, UCSB

【発明の開示】

【発明が解決しようとする課題】

【0017】

上述したように、蒸気圧が低いIV族元素をドナー不純物として用いることで、InAsや高In濃度のInxGa1-xAs電子走行層の電子濃度を、MBE装置を汚染することなく精度良く容易に制御し、かつInAsや高In濃度のInxGa1-xAs電子走行層の電子移動度を低下させずに、電子濃度を大きくする技術は確立されていなかった。

【0018】

本発明は、このような状況に鑑みてなされたもので、その目的とするところは、蒸気圧が低いIV族元素Snをドナー不純物として用いることで、InAsや高In濃度のInxGa1-xAsチャネル層の電子濃度を、MBE装置を汚染することなく精度良く容易に制御し、かつInAsや高In濃度のInxGa1-xAs電子走行層の電子移動度を低下させずに、電子濃度を大きくする技術を確立することで、優れた高周波特性を有するHEMTや高感度な磁気センサなどの半導体デバイス及びその製造方法を提供することにある。

【課題を解決するための手段】

【0019】

本発明は、このような目的を達成するために、請求項1に記載の発明は、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスであって、少なくとも1層以上の前記AlyGa1-yAszSb1-z層にはSnがドープされており、電子走行層である前記InxGa1-xAs層への電子供給層となっていることを特徴とする。

【0020】

また、請求項2に記載の発明は、請求項1に記載の発明において、前記AlyGa1-yAszSb1-z層中には、SnがドープされたAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)が設けられていることを特徴とする。

【0021】

また、請求項3に記載の発明は、請求項1に記載の発明において、前記AlyGa1-yAszSb1-z層中には、Snのデルタドープ層が設けられていることを特徴とする。

【0022】

また、請求項4に記載の発明は、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスであって、基板と、該基板上に設けられた第1のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)と、該第1のAlyGa1-yAszSb1-z層の上に設けられた電子走行層としてのInxGa1-xAs層(0≦x≦1)と、該InxGa1-xAs層の上に設けられた第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とを備え、前記第1又は第2のAlyGa1-yAszSb1-z層のうち、少なくとも一方のAlyGa1-yAszSb1-z層にはSnがドープされており、前記InxGa1-xAs層への電子供給層となっていることを特徴とする。

【0023】

また、請求項5に記載の発明は、請求項4に記載の発明において、前記AlyGa1-yAszSb1-z層中には、SnがドープされたAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)が設けられていることを特徴とする。

【0024】

また、請求項6に記載の発明は、請求項4に記載の発明において、前記AlyGa1-yAszSb1-z層中には、Snのデルタドープ層が設けられていることを特徴とする。

【0025】

また、請求項7に記載の発明は、請求項2又は5に記載の発明において、前記InxGa1-xAsと前記SnがドープされたAlyGa1-yAszSb1-z層との間にある、Snがドープされていない前記AlyGa1-yAszSb1-z層の膜厚は、2.5nm以上20nm以下であることを特徴とする。

【0026】

また、請求項8に記載の発明は、請求項3又は6に記載の発明において、前記InxGa1-xAsと前記デルタドープ層との間にある、Snがドープされていない前記AlyGa1-yAszSb1-z層の膜厚は、2.5nm以上20nm以下であることを特徴とする。

【0027】

また、請求項9に記載の発明は、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスの製造方法であって、基板上に、アンドープの第1のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層を形成する工程と、該第1のAlyGa1-yAszSb1-z層の上に、電子走行層としてのInxGa1-xAs層(0≦x≦1)を形成する工程と、該InxGa1-xAs層の上に、アンドープの第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する工程と、該AlyGa1-yAszSb1-z層の上にSnのデルタドープ層を形成する工程と、該Snのデルタドープ層の上にアンドープの第3のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する工程とを有することを特徴とする。

【0028】

また、請求項10に記載の発明は、請求項9に記載の発明において、前記デルタドープ層を形成する工程は、分子線エピタキシー法によりSnとSbとを同時に、若しくはSnとAsとSbとを同時に照射することを特徴とする。

【0029】

また、請求項11に記載の発明は、請求項1乃至8のいずれかに記載の半導体デバイスと、前記半導体デバイス上にオーミック接合されたソース電極及びドレイン電極と、前記半導体デバイス上に設けられたゲート電極とを備えることを特徴とする高電子移動度トランジスタである。

【0030】

また、請求項12に記載の発明は、請求項1乃至8のいずれかに記載の半導体デバイスと、前記半導体デバイス上に形成されたオーミック電極とを備えることを特徴とする磁気センサである。

【発明の効果】

【0031】

本発明によれば、AlGaAsSb電子供給層のドナー不純物として、蒸気圧が低く、取り扱いが容易なIV族元素Snを用いることにより、MBE装置を汚染することなく、容易にInxGa1-xAsチャネル層の電子濃度を制御することができる。従って、高い電子濃度と高い電子移動度をもつInxGa1-xAsチャネル層を工業的に安定して製造することができるため、衛星放送の送受信用増幅素子や高速データ転送用素子として、優れた高周波特性を有するHEMTや高感度な磁気センサなどの半導体デバイス及びその製造方法を提供することができる。

【発明を実施するための最良の形態】

【0032】

以下、図面を参照して本発明の実施形態について説明する。

図1は、本発明による高電子移動度トランジスタ(HEMT)の一実施形態を説明するための断面図で、符号1は基板、2は第1のAlyGa1-yAszSb1-z層、3はInxGa1-xAs電子走行層、4は第2のAlyGa1-yAszSb1-z層を示している。5と7は1対のオーミック電極であり、5はソース電極、7はドレイン電極である。6はソース電極5とドレイン電極7の間に設けられたゲート電極である。

【0033】

本発明の高電子移動度トランジスタ(HEMT)は、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスである。具体的には、基板1と、この基板1上に設けられた第1のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)2と、この第1のAlyGa1-yAszSb1-z層2の上に設けられた電子走行層としてのInxGa1-xAs層(0≦x≦1)3と、このInxGa1-xAs層3の上に設けられた第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)4とを備えている。

【0034】

ここで、第1のAlyGa1-yAszSb1-z層2、第2のAlyGa1-yAszSb1-z層4のいずれか一方、若しくは両方にはSnがドープされており、InxGa1-xAs電子走行層3への電子供給層となっている。また、第1のAlyGa1-yAszSb1-z層2、第2のAlyGa1-yAszSb1-z層4のいずれか一方が存在しないか、若しくは他の半導体材料となっている場合でも、SnがドープされたAlyGa1-yAszSb1-z層とInxGa1-xAs電子走行層3とのヘテロ接合を、少なくとも一つ有している薄膜構造となっていれば、本発明の技術的範囲内である。以下、各構成要素について説明する。

【0035】

本発明に用いられる基板1は、基板であれば何でも良いが、GaAs基板、もしくはGaP基板、表面に単結晶のGaAsを成長させたSi基板、サファイア基板などが好適である。なかでも半絶縁性で良質の単結晶基板が得られるGaAs基板は、特に好ましい。ここで言う半絶縁性とは、抵抗率が107Ω・cm以上のものを指す。単結晶基板を用いる場合、基板の面方位は(100)、(111)、(110)等が好ましい。これらの面方位から1°から5°ずらした面方位を用いることもある。中でも(100)は良質の薄膜を成長させる上で最適である。通常行われるように、基板表面を平坦化させ、清浄化させる目的で、基板と同じ材質の半導体を成長させたものを本発明の基板として使用しても良い。GaAs基板上にGaAsを成長させるのは、この最も代表的な1例である。

【0036】

本発明に用いられる第1のAlyGa1-yAszSb1-z層2は、(a)InxGa1-xAs電子走行層3との格子定数が近く、(b)InxGa1-xAs電子走行層3と比べて抵抗率が十分高く、(c)InxGa1-xAs電子走行層3と大きく格子定数の異なるGaAs等の基板上に直接積層した場合でも、欠陥の少ない平坦な表面を有していることが好ましい。第1のAlyGa1-yAszSb1-z層2とInxGa1‐xAs電子走行層3の格子定数は、InxGa1‐xAs電子走行層3の膜厚が臨界膜厚を超えない程度に近ければ良い。例えば、InxGa1-xAs電子走行層3の膜厚が15nmの場合、第1のAlyGa1-yAszSb1-z層2とInxGa1-xAs電子走行層3の格子定数は1.3%以内で一致していることが好ましい。

【0037】

InxGa1-xAs(0≦x≦1)電子走行層3のIn組成xが0.53以上1以下の場合、第1のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層2のAs組成zは0以上0.7以下であることが好ましい。第1のAlyGa1-yAszSb1-z層2の抵抗率は、Al組成yが大きいほど高くなる一方、素子化プロセス中に酸化しやすいという懸念があり、Al組成yは0.5以上0.8以下の範囲であることが好ましい。

【0038】

第1のAlyGa1-yAszSb1-z層2の表面の平坦性は、膜厚が厚いほど良好であるが、工業上はなるべく薄くすることが望ましい。すなわち、膜厚は5nm以上3000nm以下の範囲が好ましく、より好ましくは10nm以上1000nmである。第1のAlyGa1-yAszSb1-z層2をInxGa1‐xAs電子走行層3への電子供給層として用いる場合、Snは厚さ方向に均一にドープされていても、分布があっても良く、デルタドープされていても良い。特にInxGa1-xAs電子走行層3との界面近傍の第1のAlyGa1-yAszSb1-z層2にはSnをドープしない構造にすることによって、不純物散乱の影響を低減でき、高い電子移動度を得ることができるため好ましい。

【0039】

ここでデルタドープとは、分子線エピタキシー法を用いたIII−V族化合物半導体の薄膜成長において、ドーパントとV族元素を同時に照射して行なうドーピングの手法である。III族元素を照射しないため、薄膜の成長は進行しない状態でのドーピングとなる。その結果、デルタドープ層の膜厚は限りなくゼロに近く、厳密には数原子層程度の膜厚である。デルタドープは所望の場所に、所望の量のドーピングが可能であり好ましい。

【0040】

本発明に用いられるInxGa1-xAs(0≦x≦1)電子走行層3は、制御電極にかかる電圧によって電気伝導を制御する都合上、膜厚は2000nm以下が好ましい。より好ましくは、5nm以上100nm以下である。また、InxGa1-xAs電子走行層3の電子濃度は、3×1017cm-3以上2×1018cm-3以下のとき、高い電子移動度を有し、好ましい。InxGa1-xAs(0≦x≦1)電子走行層3は、In組成xが大きいほど高い電子移動度が得られるので好ましく、特にIn組成xは0.53以上1以下であることが好ましい。

【0041】

本発明に用いられる第2のAlyGa1-yAszSb1-z層4は、(a)InxGa1-xAs電子走行層3との格子定数が近く、(b)InxGa1-xAs電子走行層3と比べて抵抗率が十分高いことが好ましい。第2のAlyGa1-yAszSb1-z層4とInxGa1‐xAs電子走行層3の格子定数は、InxGa1‐xAs電子走行層3の膜厚が臨界膜厚を超えない程度に近ければ良い。例えば、InxGa1-xAs電子走行層3の膜厚が15nmの場合、第2のAlyGa1-yAszSb1-z層4とInxGa1-xAs電子走行層3の格子定数は1.3%以内で一致していることが好ましい。InxGa1-xAs(0≦x≦1)電子走行層3のIn組成xが0.53以上1以下の場合、第2のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層4のAs組成zは0以上0.7以下であることが好ましい。

【0042】

第2のAlyGa1-yAszSb1-z層4の抵抗率は、Al組成yが大きいほど高くなる一方、素子化プロセス中に酸化しやすいという懸念があり、Al組成yは0.5以上0.8以下の範囲であることが好ましい。第2のAlyGa1-yAszSb1-z層4の膜厚は、5nm以上100nmの範囲が好ましい。第2のAlyGa1-yAszSb1-z層4をInxGa1‐xAsチャネル層3への電子供給層として用いる場合、Snは厚さ方向に均一にドープされていても、分布があっても良く、デルタドープされていても良い。特に、ゲート電極6が形成される側の界面近傍のみ、Snをドープしない構造にすると、ゲート耐圧が低下せず良好である。

【0043】

また、InxGa1-xAs電子走行層3との界面近傍の第2のAlyGa1-yAszSb1-z層4には、Snをドープしない構造にすることによって、不純物散乱の影響を低減でき、高い電子移動度を得ることができるため好ましい。第1のAlyGa1-yAszSb1-z層2と第2のAlyGa1-yAszSb1-z層4は、同じ組成である方が製造工程を簡略化できるため好ましいが、異なる組成であっても良く、必要に応じて適宜実施される。

【0044】

本発明に用いられるソース電極5、及びドレイン電極7は、その下部のInxGa1-xAs電子走行層3とオーミック接合をとる必要がある。オーミック接合には、各種の構造があるが、図1では、InxGa1-xAs電子走行層3に直接接合する構造をとっている。InxGa1-xAs電子走行層3はバンドギャップが狭く、電極をコンタクトしただけで、接触抵抗の低いオーミック接合が得られる。このためオーミック電極5、7の下部のみ、第2のAlyGa1-yAszSb1-z層4をエッチングして、InxGa1-xAsチャネル層3に直接電極を形成することができる。この場合、電極5、7とInxGa1-xAsチャネル層3の間の接触抵抗を低減するために、合金化過程を行っても良いが、蒸着しただけでも良好なオーミック接合が得られる。このため、電極金属はAuGe/Ni/Auの3層構造をはじめとする公知の積層電極構造でも良いが、Al、Ti、Au、Wなどの単層の金属でも良く、極めて多くの組み合わせが可能である。

【0045】

本発明に用いられるゲート電極6は、その下部に空乏層を形成できるものであれば良く、ショットキー接合を用いる方法のほか、ゲート電極とInxGa1-xAs電子走行層3の間に、絶縁物を挟んだMIS(METAL−INSULATOR−SEMICONDUCTOR)構造や、PN接合を利用することもできる。特に、第2のAlyGa1-yAszSb1-z層4とショットキー接合を形成する材料としては、Al、Ti、W、Pt、WSi、Auなどが好ましく、これらを積層構造にしたものも良い。

【0046】

図10は、本発明による高電子移動度トランジスタの製造方法を説明するためのフローチャートを示す図である。

本発明の高電子移動度トランジスタは、InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスの製造方法である。

【0047】

まず、ステップ1(S1)において、基板上に、アンドープの第1のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層を形成する。次に、ステップ2(S2)において、第1のAlyGa1-yAszSb1-z層の上に、電子走行層としてのInxGa1-xAs層(0≦x≦1)を形成する。次に、ステップ3(S3)において、InxGa1-xAs層の上に、アンドープの第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する。次に、ステップ4(S4)において、AlyGa1-yAszSb1-z層の上にSnのデルタドープ層を形成する。最後に、ステップ5(S5)において、Snのデルタドープ層の上にアンドープの第3のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する。また、デルタドープ層を設けるステップ4は、分子線エピタキシー法によりSnとSbとを同時に、若しくはSnとAsとSbとを同時に照射する。

【0048】

以下に本発明の具体的な実施例について述べるが、本発明はこれらの実施例のみに限定されるものではない。

[実施例1]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.53Ga0.47Sb層を成長した。また、本実施例では、Al0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47Sb層上に成長した。

【0049】

この薄膜積層体の電気的特性をファンデルポー法、ホール測定により評価した結果、電子移動度は30300cm2/Vs、シート電子濃度1.60×1012cm-2であった。ここで、電子移動度は単位電界あたりの電子の動く速度、シート電子濃度は、1cm2当たりの電子の数である。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。この結果から、従来アクセプタとして働くといわれていたIV族元素Snは、ドナーとして働くことが明らかとなった。TeなどのVI族元素に比べて、蒸気圧が低く、取り扱いが容易で、チャンバの汚染の恐れがないIV族元素Snで、電子走行層の電子濃度を制御できることは、工業上極めて好ましい。

【0050】

これらの薄膜積層体において、メサエッチ工程を経た後、ソース電極、ドレイン電極を形成する箇所をエッチングすることでInAs表面を露出させ、InAs上に直接ソース電極、ドレイン電極を形成し、さらにGaAsキャップ層上にゲート電極を形成することで、高電子移動度トランジスタHEMTを作製した。

【0051】

本実施例においては、Snデルタドープ層をInAsとAl0.53Ga0.47Sb層との界面から5nm離れた部位に、Snセル温度を950℃に加熱した状態で、56秒間照射することで形成している。

【0052】

ここで、Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)、Snを照射する時間をそれぞれ変化させたときの、薄膜積層体のシート電子濃度の値を図2及び図3に示す。

【0053】

図2は、Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)と薄膜積層体のシート電子濃度の関係をグラフに示した図で、図3は、Snを照射した時間と薄膜積層体のシート電子濃度の関係をグラフに示した図である。

【0054】

このときのSnセル温度は950℃である。図2からドープ位置が近いとシート電子濃度が高く、ドープ位置が遠いとシート電子濃度が低いことがわかった。AlGaAsSb電子供給層中の電子が、InAs電子走行層に落ち込む電子の確率が、ドープ位置が遠くなるに従って減少するためと考えられる。図3からは、Snの照射する時間を長くするほど、シート電子濃度は単調に増加することがわかった。これらの結果から、Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)、Snを照射する時間を制御するだけで、薄膜積層体のシート電子濃度を容易に制御することができることを見出した。

【0055】

図4は、薄膜積層体のシート電子濃度と電子移動度の関係をグラフに示した図である。ここにはSnのドープ位置を2.5nmから20nm、Snセル温度を930℃から970℃、Sn照射時間を0秒から94秒まで変化させた、全データをプロットした。この図4からシート電子濃度が5×1011cm-2以上3×1012cm-3以下、すなわち、電子濃度3×1017cm-3以上2×1018cm-3以下で高い電子移動度を有していることがわかる。特に1.2×1012cm-2以上1.6×1012cm-2以下、すなわち、電子濃度8×1017cm-3以上1.1×1018cm-3以下では電子移動度は30000cm2/Vs以上であり好ましい。

【0056】

図5は、薄膜積層体のSnデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)と電子移動度の関係をグラフに示した図である。このときのSnセル温度は950℃、Snの照射時間は56秒としている。ドープする位置を近づけすぎると、InAsがSnの不純物散乱の影響を受けてしまうので電子移動度は低下してしまう。逆にドープする位置が遠いと、シート電子濃度は低くなってしまうため、電子移動度は低下する。電子移動度は27000(cm2/Vs)以上であることが好ましく、図5の結果から、Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)は、2.5nm以上20nm以下であることが好ましい。

【0057】

[実施例2]

上述した薄膜積層体をメサエッチ工程により、十字型に成形した後、電極を形成する箇所のみエッチングすることでInAs表面を露出させ、InAs上に電極を形成することで、磁気センサであるホール素子を作製した。

【0058】

図6は、作製したホール素子の構造を示す断面図で、図7は、作製したホール素子の構造を示す上面図である。なお、符号9はオーミック電極を示している。

【0059】

このとき用いた薄膜積層体の電気的特性は、電子移動度30300cm2/Vs、シート抵抗158Ω、シート電子濃度1.30×1012cm-2である。本例のホール素子で得られた特性は、入力抵抗値が300Ω、定電圧1Vで駆動したとき、50mTの磁束密度の印加でホール電圧が75mVであった。すなわち、磁界での感度は、75mV/V・50mTの高感度を示した。

【0060】

[実施例3]

上述した実施例1の薄膜積層体を用いて、磁気センサである磁気抵抗素子を作製した。このとき用いた薄膜積層体の電気的特性は、電子移動度30700cm2/Vs、シート抵抗144Ω、シート電子濃度1.42×1012cm-2である。

【0061】

図8は、作製した磁気抵抗素子の構造を示す断面図で、図9は、作製した磁気抵抗素子の構造を示す上面図である。

メサエッチ工程により、短冊状に成形した後、電極を形成する箇所のみエッチングすることでInAs表面を露出させ、InAs上にオーミック電極9、短絡電極10を形成することで磁気抵抗素子を作製した。端子電極部を除いてInAsの薄膜からなる磁気抵抗素子部の長さが1450μm、InAs薄膜の幅が120μm、幅120μmのInAs磁気抵抗素子部を跨いで形成されたCu/Ni/Au/Niの4層からなる短絡電極は長さ120μmでその幅は9μmであり、等間隔でInAs薄膜に直接接触して形成した。電極間の抵抗値は磁界の印加がない場合は1200Ωであった。

【0062】

磁気抵抗素子を磁気センサとして使うときに加えられる磁束密度領域、すなわち、磁気抵抗変化が磁束密度に直線的に変化する磁束密度の領域でもあり、かつ、高感度で微弱な磁界変化を検出するためのバイアス磁束密度の領域でもある0.45Tの磁束密度のときの絶対的な抵抗変化率は160%であり、極めて大きな磁気抵抗変化示した。

【0063】

[実施例4]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に75秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nm のアンドープAl0.53Ga0.47Sb層を成長した。また、今回の実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47Sb層上に成長した。

【0064】

この薄膜積層体の電子移動度は28000cm2/Vs、シート電子濃度2.16×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。実施例1と比較して、電子移動度はやや低下するものの、Snの照射時間を長くすることで、より高いシート電子濃度の特性を得ることができる。

【0065】

[実施例5]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚35nmのSnをドープしたAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をSnドープAl0.53Ga0.47Sb層上に成長した。

【0066】

この薄膜積層体の電子移動度は24300cm2/Vs、シート電子濃度2.11×1012cm-2であった。Snのドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snドープ層の効果は非常に大きいことがわかった。

【0067】

[実施例6]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚20nmのSnをドープしたAl0.53Ga0.47Sb層を成長した後、膜厚15nmのアンドープのAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をSnドープAl0.53Ga0.47Sb層上に成長した。

【0068】

この薄膜積層体の電子移動度は25100cm2/Vs、シート電子濃度1.88×1012cm-2であった。Snのドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snドープ層の効果は非常に大きいことがわかった。

【0069】

[実施例7]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープのAl0.53Ga0.47Sb層を成長した後、膜厚30nmのSnをドープしたAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をSnドープAl0.53Ga0.47Sb層上に成長した。

【0070】

この薄膜積層体の電子移動度は29500cm2/Vs、シート電子濃度1.36×1012cm-2であった。Snのドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snドープ層の効果は非常に大きいことがわかった。

【0071】

[実施例8]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更にその上に膜厚5nmのアンドープのAl0.53Ga0.47Sb層、膜厚15nmのSnをドープしたAl0.53Ga0.47Sb層、膜厚15nmのアンドープのAl0.53Ga0.47Sb層を順次成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をSnドープAl0.53Ga0.47Sb層上に成長した。

【0072】

この薄膜積層体の電子移動度は30100cm2/Vs、シート電子濃度1.31×1012cm-2であった。Snのドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snドープ層の効果は非常に大きいことがわかった。

【0073】

[実施例9]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚595nmのアンドープAl0.53Ga0.47Sb層を成長した後、Snのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚5nmのアンドープAl0.53Ga0.47Sb層を成長した。更に、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長した後、膜厚35nmのアンドープAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47Sb層上に成長した。

【0074】

この薄膜積層体の電子移動度は30500cm2/Vs、シート電子濃度1.49×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は25300cm2/Vs、シート電子濃度5.9×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較しても、同等の特性が得られており、InAs電子走行層の下層のAlGaAsSb層も、Snをドープすることで電子供給層として働くことが明らかとなった。

【0075】

[実施例10]

薄膜形成方法の一例として分子線エピタキシー法(MBE法)を用いた場合について詳細に述べる。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱し表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.53Ga0.47Sb層を成長した。また、本実施例ではAl0.53Ga0.47Sb層の最表面の酸化等を防止する目的で、半導体保護層としてInAsキャップ層をアンドープAl0.53Ga0.47Sb層上に成長した。

【0076】

この薄膜積層体の電子移動度は29500cm2/Vs、シート電子濃度1.26×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は23300cm2/Vs、シート電子濃度5.4×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して同等の特性が得られており、キャップ層をInAsにした場合でも、Snデルタドープ層の効果は非常に大きい。

【0077】

[実施例11]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.65Ga0.35Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.65Ga0.35Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.65Ga0.35Sb層を成長した。また、本実施例ではAl0.65Ga0.35Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.65Ga0.35Sb層上に成長した。

【0078】

この薄膜積層体の電子移動度は28700cm2/Vs、シート電子濃度1.39×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は21500cm2/Vs、シート電子濃度5.1×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度はやや低下するものの、Snデルタドープ層の効果は非常に大きい。

【0079】

[実施例12]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.8Ga0.2Sb層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.8Ga0.2Sb層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.8Ga0.2Sb層を成長した。また、本実施例ではAl0.8Ga0.2Sb層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.8Ga0.2Sb層上に成長した。

【0080】

この薄膜積層体の電子移動度は25700cm2/Vs、シート電子濃度1.41×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は17100cm2/Vs、シート電子濃度4.1×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度はやや低下するものの、Snデルタドープ層の効果は非常に大きい。

【0081】

[実施例13]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を成長した後、基板温度を460℃に保持しながら膜厚15nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を成長した。また、本実施例ではAl0.53Ga0.47As0.13Sb0.87層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47As0.13Sb0.87層上に成長した。

【0082】

この薄膜積層体の電子移動度は23000cm2/Vs、シート電子濃度1.67×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は15800cm2/Vs、シート電子濃度3.2×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度はやや低下するものの、Snデルタドープ層の効果は非常に大きい。

【0083】

[実施例14]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を成長した後、基板温度を460℃に保持しながら膜厚30nmのInAs層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47As0.13Sb0.87層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nm のアンドープAl0.53Ga0.47As0.13Sb0.87層を成長した。また、本実施例ではAl0.53Ga0.47As0.13Sb0.87層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47As0.13Sb0.87層上に成長した。

【0084】

この薄膜積層体の電子移動度は24700cm2/Vs、シート電子濃度1.86×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は21300cm2/Vs、シート電子濃度5.6×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例13と比較して、より高い電子移動度、シート電子濃度を得ることができる。

【0085】

[実施例15]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47As0.3Sb0.7層を成長した後、基板温度を460℃に保持しながら膜厚15nmのIn0.8Ga0.2As層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47As0.3Sb0.7層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nmのアンドープAl0.53Ga0.47As0.3Sb0.7層を成長した。また、本実施例ではAl0.53Ga0.47As0.3Sb0.7層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47As0.3Sb0.7層上に成長した。

【0086】

この薄膜積層体の電子移動度は11300cm2/Vs、シート電子濃度1.42×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は5600cm2/Vs、シート電子濃度5×1010cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度は低下するものの、Snデルタドープ層の効果は非常に大きい。

【0087】

[実施例16]

薄膜形成方法の一例として、分子線エピタキシー法(MBE法)を用いた場合について以下に説明する。まず、半絶縁性のGaAs(100)基板にAsを照射しながら630℃で加熱して表面酸素を脱離させる。そのまま基板温度を580℃まで下げた後、膜厚70nmのGaAsバッファ層を成長し、更に基板温度を530℃に下げながら膜厚35nmのGaAsバッファ層を成長する。次に、基板温度を460℃に下げながら膜厚600nmのアンドープAl0.53Ga0.47As0.2Sb0.8層を成長した後、基板温度を460℃に保持しながら膜厚15nmのIn0.8Ga0.2As層を成長し、更に膜厚5nmのアンドープAl0.53Ga0.47As0.2Sb0.8層を、その上にはSnのセル温度を950℃に加熱した状態で、SnとSbを同時に56秒間照射することでSnのデルタドープ層を形成し、その上には膜厚30nm のアンドープAl0.53Ga0.47As0.2Sb0.8層を成長した。また、本実施例ではAl0.53Ga0.47As0.2Sb0.8層の最表面の酸化等を防止する目的で、半導体保護層としてGaAsキャップ層をアンドープAl0.53Ga0.47As0.2Sb0.8層上に成長した。

【0088】

この薄膜積層体の電子移動度は11700cm2/Vs、シート電子濃度1.29×1012cm-2であった。Snのデルタドープ層がない場合の薄膜積層体では、電子移動度は8100cm2/Vs、シート電子濃度2.4×1011cm-2であるので、本実施例では、電子移動度、電子濃度ともに高い値を有し、Snデルタドープ層の効果は非常に大きいことがわかった。また、実施例1と比較して、電子移動度はやや低下するものの、Snデルタドープ層の効果は非常に大きい。

【図面の簡単な説明】

【0089】

【図1】本発明による高電子移動度トランジスタ(HEMT)の一実施形態を説明するための断面図である。

【図2】Snデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)と薄膜積層体のシート電子濃度の関係をグラフに示した図である。

【図3】Snを照射した時間と薄膜積層体のシート電子濃度の関係をグラフに示した図である。

【図4】薄膜積層体のシート電子濃度と電子移動度の関係をグラフに示した図である。

【図5】薄膜積層体のSnデルタドープ層の位置(InAsとAl0.53Ga0.47Sb層との界面からの距離)と電子移動度の関係をグラフに示した図である。

【図6】作製したホール素子の構造を示す断面図である。

【図7】作製したホール素子の構造を示す上面図である。

【図8】作製した磁気抵抗素子の構造を示す断面図である。

【図9】作製した磁気抵抗素子の構造を示す上面図である。

【図10】本発明による高電子移動度トランジスタ(HEMT)の製造方法を説明するためのフローチャートを示す図である。

【符号の説明】

【0090】

1 基板

2 第1のAlyGa1-yAszSb1-z層

3 InxGa1-xAs電子走行層

4 第2のAlyGa1-yAszSb1-z層

5 ソース電極、

6 ソース電極5とドレイン電極7の間に設けられたゲート電極

7 ドレイン電極

8 薄膜積層体

9 オーミック電極

10 短絡電極

【特許請求の範囲】

【請求項1】

InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスであって、

少なくとも1層以上の前記AlyGa1-yAszSb1-z層にはSnがドープされており、電子走行層である前記InxGa1-xAs層への電子供給層となっていることを特徴とする半導体デバイス。

【請求項2】

前記AlyGa1-yAszSb1-z層中には、SnがドープされたAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)が設けられていることを特徴とする請求項1に記載の半導体デバイス。

【請求項3】

前記AlyGa1-yAszSb1-z層中には、Snのデルタドープ層が設けられていることを特徴とする請求項1に記載の半導体デバイス。

【請求項4】

InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスであって、

基板と、該基板上に設けられた第1のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)と、該第1のAlyGa1-yAszSb1-z層の上に設けられた電子走行層としてのInxGa1-xAs層(0≦x≦1)と、該InxGa1-xAs層の上に設けられた第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とを備え、

前記第1又は第2のAlyGa1-yAszSb1-z層のうち、少なくとも一方のAlyGa1-yAszSb1-z層にはSnがドープされており、前記InxGa1-xAs層への電子供給層となっていることを特徴とする半導体デバイス。

【請求項5】

前記AlyGa1-yAszSb1-z層中には、SnがドープされたAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)が設けられていることを特徴とする請求項4に記載の半導体デバイス。

【請求項6】

前記AlyGa1-yAszSb1-z層中には、Snのデルタドープ層が設けられていることを特徴とする請求項4に記載の半導体デバイス。

【請求項7】

前記InxGa1-xAsと前記SnがドープされたAlyGa1-yAszSb1-z層との間にある、Snがドープされていない前記AlyGa1-yAszSb1-z層の膜厚は、2.5nm以上20nm以下であることを特徴とする請求項2又は5に記載の半導体デバイス。

【請求項8】

前記InxGa1-xAsと前記デルタドープ層との間にある、Snがドープされていない前記AlyGa1-yAszSb1-z層の膜厚は、2.5nm以上20nm以下であることを特徴とする請求項3又は6に記載の半導体デバイス。

【請求項9】

InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスの製造方法であって、

基板上に、アンドープの第1のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層を形成する工程と、該第1のAlyGa1-yAszSb1-z層の上に、電子走行層としてのInxGa1-xAs層(0≦x≦1)を形成する工程と、該InxGa1-xAs層の上に、アンドープの第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する工程と、該AlyGa1-yAszSb1-z層の上にSnのデルタドープ層を形成する工程と、該Snのデルタドープ層の上にアンドープの第3のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する工程とを有することを特徴とする半導体デバイスの製造方法。

【請求項10】

前記デルタドープ層を形成する工程は、分子線エピタキシー法によりSnとSbとを同時に、若しくはSnとAsとSbとを同時に照射することを特徴とする請求項9に記載の半導体デバイスの製造方法。

【請求項11】

請求項1乃至8のいずれかに記載の半導体デバイスと、前記半導体デバイス上にオーミック接合されたソース電極及びドレイン電極と、前記半導体デバイス上に設けられたゲート電極とを備えることを特徴とする高電子移動度トランジスタ。

【請求項12】

請求項1乃至8のいずれかに記載の半導体デバイスと、前記半導体デバイス上に形成されたオーミック電極とを備えることを特徴とする磁気センサ。

【請求項1】

InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスであって、

少なくとも1層以上の前記AlyGa1-yAszSb1-z層にはSnがドープされており、電子走行層である前記InxGa1-xAs層への電子供給層となっていることを特徴とする半導体デバイス。

【請求項2】

前記AlyGa1-yAszSb1-z層中には、SnがドープされたAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)が設けられていることを特徴とする請求項1に記載の半導体デバイス。

【請求項3】

前記AlyGa1-yAszSb1-z層中には、Snのデルタドープ層が設けられていることを特徴とする請求項1に記載の半導体デバイス。

【請求項4】

InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスであって、

基板と、該基板上に設けられた第1のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)と、該第1のAlyGa1-yAszSb1-z層の上に設けられた電子走行層としてのInxGa1-xAs層(0≦x≦1)と、該InxGa1-xAs層の上に設けられた第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とを備え、

前記第1又は第2のAlyGa1-yAszSb1-z層のうち、少なくとも一方のAlyGa1-yAszSb1-z層にはSnがドープされており、前記InxGa1-xAs層への電子供給層となっていることを特徴とする半導体デバイス。

【請求項5】

前記AlyGa1-yAszSb1-z層中には、SnがドープされたAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)が設けられていることを特徴とする請求項4に記載の半導体デバイス。

【請求項6】

前記AlyGa1-yAszSb1-z層中には、Snのデルタドープ層が設けられていることを特徴とする請求項4に記載の半導体デバイス。

【請求項7】

前記InxGa1-xAsと前記SnがドープされたAlyGa1-yAszSb1-z層との間にある、Snがドープされていない前記AlyGa1-yAszSb1-z層の膜厚は、2.5nm以上20nm以下であることを特徴とする請求項2又は5に記載の半導体デバイス。

【請求項8】

前記InxGa1-xAsと前記デルタドープ層との間にある、Snがドープされていない前記AlyGa1-yAszSb1-z層の膜厚は、2.5nm以上20nm以下であることを特徴とする請求項3又は6に記載の半導体デバイス。

【請求項9】

InxGa1-xAs層(0≦x≦1)とAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)とのヘテロ接合を少なくとも一つ有する半導体デバイスの製造方法であって、

基板上に、アンドープの第1のAlyGa1-yAszSb1-z(0≦y≦1、0≦z<1)層を形成する工程と、該第1のAlyGa1-yAszSb1-z層の上に、電子走行層としてのInxGa1-xAs層(0≦x≦1)を形成する工程と、該InxGa1-xAs層の上に、アンドープの第2のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する工程と、該AlyGa1-yAszSb1-z層の上にSnのデルタドープ層を形成する工程と、該Snのデルタドープ層の上にアンドープの第3のAlyGa1-yAszSb1-z層(0≦y≦1、0≦z<1)を形成する工程とを有することを特徴とする半導体デバイスの製造方法。

【請求項10】

前記デルタドープ層を形成する工程は、分子線エピタキシー法によりSnとSbとを同時に、若しくはSnとAsとSbとを同時に照射することを特徴とする請求項9に記載の半導体デバイスの製造方法。

【請求項11】

請求項1乃至8のいずれかに記載の半導体デバイスと、前記半導体デバイス上にオーミック接合されたソース電極及びドレイン電極と、前記半導体デバイス上に設けられたゲート電極とを備えることを特徴とする高電子移動度トランジスタ。

【請求項12】

請求項1乃至8のいずれかに記載の半導体デバイスと、前記半導体デバイス上に形成されたオーミック電極とを備えることを特徴とする磁気センサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2009−38307(P2009−38307A)

【公開日】平成21年2月19日(2009.2.19)

【国際特許分類】

【出願番号】特願2007−203369(P2007−203369)

【出願日】平成19年8月3日(2007.8.3)

【出願人】(303046277)旭化成エレクトロニクス株式会社 (840)

【Fターム(参考)】

【公開日】平成21年2月19日(2009.2.19)

【国際特許分類】

【出願日】平成19年8月3日(2007.8.3)

【出願人】(303046277)旭化成エレクトロニクス株式会社 (840)

【Fターム(参考)】

[ Back to top ]