半導体デバイス

【課題】2以上の半導体集積回路を搭載した半導体デバイスにおいて、各半導体集積回路に接続するそれぞれのプログラム格納デバイス(記憶デバイス)のうちの一部の記憶デバイスのみを高セキュリティにするだけで、これらの全ての記憶デバイスについて、記憶デバイスの入れ替え脅威を高いセキュリティレベルで排除することを可能にする。

【解決手段】少なくとも1つの半導体集積回路(Main SoC11で例示)は、他の半導体集積回路(Sub SoC12で例示)の起動プログラムより信頼性が確保された起動プログラムで起動し、起動した起動プログラムにより上記他の半導体集積回路(Sub SoC12で例示)の起動プログラムの認証を行う。

【解決手段】少なくとも1つの半導体集積回路(Main SoC11で例示)は、他の半導体集積回路(Sub SoC12で例示)の起動プログラムより信頼性が確保された起動プログラムで起動し、起動した起動プログラムにより上記他の半導体集積回路(Sub SoC12で例示)の起動プログラムの認証を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイスに関し、より詳細には、2以上の半導体集積回路を搭載した半導体デバイスに関する。

【背景技術】

【0002】

近年のLSI(Large Scale Integration)のプロセス微細化により、LSIに搭載可能な回路規模はどんどん増加し、LSIが処理する機能や性能は加速度的に向上している。なお、回路規模によっては、その半導体集積回路をVLSI(Very LSI)、ULSI(Ultra-LSI)などと呼ぶこともある。

【0003】

機能向上の1つとして、プロセッサ機能をLSIの中に取り込むと、LSI内部のプロセッサがLSI全体を内部から制御することが可能となり、LSI内部にあたかも一つのシステムを構築できる。このように、半導体集積回路であって、その内部にプロセッサを内蔵してシステムを構築するデバイスは、SoC(System on a Chip)と呼ばれている。

【0004】

SoCと呼ばれる半導体集積回路には、様々なデバイスがある。非常に高性能なプロセッサを搭載し、SoCの外部に接続される全てのデバイスを統合的に管理できるものや、複数のプロセッサを内蔵し、さらに処理能力や演算能力を高めたもの、また、外部デバイスの制御は他のプロセッサに任せて、自身はSoC内部の制御のみを行うものなど様々である。

【0005】

ところで、SoCにおいて、CPU(Central Processing Unit)等のプロセッサを安全に立ち上げることは非常に重要であり、特にセキュリティを重視した製品では確実に信頼できるプログラムデータからプロセッサ(以下、CPUで例示)を起動する必要がある。プログラムが悪意ある者によって差し替えられた状態で起動を許してしまうと、SoC内外の記憶装置に暗号化して保存したデータが読み出される危険性や、暗号化データの復号化ができなかったとして消去されてしまう恐れもある。また、ユーザがプログラムを差し替えられたことに気付かずに利用すると、差し替えられた後に生成したデータは、悪意ある者によって搾取されてしまう。

【0006】

このような危険性を排除するために、CPUを安全且つ確実に立ち上げることは重要である。実現方法として、例えばプログラムデータを暗号化した上で記憶デバイスに保存しておき、起動時に復号化してからRAM(Random Access Memory)上に展開して起動する方法や、TPM(Trusted Platform Module)などのSoCとは別に外部にセキュリティデバイスを利用する方法などがある。

【0007】

さらに、HDD(Hard Disk Drive)やSDカード、USB(Universal Serial Bus)メモリなど一般的に広く利用され汎用性の高い記憶デバイスにプログラムデータを保存するのではなく、基板にオンボードで直接実装するタイプの記憶デバイスに保存することもセキュリティ性を高める方法の一つである。独自のI/F(Interface)プロトコルで動作するデバイスの採用や、Flash DIMM(Dual Inline Memory Module)など一般的にはユーザが入手しにくいデバイスを採用する方法もある。オンボードタイプデバイスやユーザが入手しにくいデバイスなどの場合、第三者によってデバイスの入れ替えを行うのは難しいばかりではなく、基板に実装したまま外部から書き換えることは非常に専門的な知識が必要となるため、セキュリティ性が高くなる。

【0008】

複合機(MFP)を例に挙げ具体的に説明すると、次のようになる。一般的なモデル(製品)とセキュリティを重視したモデルの2種類ある場合、セキュリティを重視したモデルではデータの暗号化や、動作時に一次的に保存したメモリデータ、HDDデータの消去などといったセキュリティ機能が付加される。ここで脅威となる一例は、一般的なモデルのプログラムデータ格納デバイスをセキュリティを重視したモデルのデバイスと置き換えることが挙げられる。置き換え後にCPUの起動が可能であると、それまでに蓄積されたデータの消去がなされず、また今後利用する際に生成されるデータは暗号化されていないため、非常に危険な状態となってしまう。従って、CPUを安全に起動することは、セキュリティ上、非常に重要な要素となる。

【0009】

一方、近年、MFPに限らず様々なシステムは、大規模化・複雑化に伴って複数のCPUによってシステム全体を制御することが多くなってきた。例えば、特許文献1には、上述したようなSoCで代表される半導体集積回路を、同じ回路基板などに2以上搭載した半導体デバイスが開示されている。この半導体デバイスも複数のCPUをもつことになる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2001−13215号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

そして、このように複数のCPUを搭載する半導体デバイスの場合、全てのCPUに対して安全に起動することが求められる。プログラム格納デバイスの入れ替え脅威を排除するためには、全ての記憶デバイスを交換リスクがなく安全性の高いデバイスにする必要が生じる。従って、図6で示す半導体デバイスのように、Main SoC11とSub SoC12に対してプログラム格納デバイスとしてそれぞれ接続する外部記憶装置50a,50bは、いずれも高セキュリティの装置を採用する必要が生じる。

【0012】

しかしながら、一般的にHDDなど先に挙げた汎用性の高い記憶デバイスに比べ、セキュリティ性の高い記憶デバイスは技術的に高度であったり、販売数量が少ないなどといった理由によりコストが高くなる傾向にある。

【0013】

本発明は、上述のような実状に鑑みてなされたものであり、その目的は、2以上の半導体集積回路を搭載した半導体デバイスにおいて、各半導体集積回路に接続するそれぞれのプログラム格納デバイス(記憶デバイス)のうちの一部の記憶デバイスのみを高セキュリティにするだけで、これらの全ての記憶デバイスについて、記憶デバイスの入れ替え脅威を高いセキュリティレベルで排除することを可能にすることにある。

【課題を解決するための手段】

【0014】

上記課題を解決するために、本発明の第1の技術手段は、2以上の半導体集積回路を搭載した半導体デバイスであって、少なくとも1つの半導体集積回路は、他の半導体集積回路の起動プログラムより信頼性が確保された起動プログラムで起動し、該起動した起動プログラムにより前記他の半導体集積回路の起動プログラムの認証を行うことを特徴としたものである。

【0015】

第2の技術手段は、第1の技術手段において、前記少なくとも1つの半導体集積回路は、前記他の半導体集積回路の起動プログラムの認証が不可であった場合、不可であった前記他の半導体集積回路の起動プログラムに、リセットの命令を行うことを特徴としたものである。

【0016】

第3の技術手段は、第2の技術手段において、前記少なくとも1つの半導体集積回路は、前記他の半導体集積回路の起動プログラムの認証が不可であった場合、少なくとも不可であった前記他の半導体集積回路に電源を供給するための電源管理デバイスに、電源オフの命令を行うことを特徴としたものである。

【0017】

第4の技術手段は、第1〜第3のいずれか1の技術手段において、前記少なくとも1つの半導体集積回路は、オンボードタイプのメモリにアクセスするためのインターフェースを有し、前記他の半導体集積回路は、前記メモリより低セキュリティで且つ非オンボードタイプの外部記憶装置にアクセスするためのインターフェースを有することを特徴としたものである。

【発明の効果】

【0018】

本発明に係る半導体デバイスによれば、各半導体集積回路に接続するそれぞれのプログラム格納デバイス(記憶デバイス)のうちの一部の記憶デバイスのみを高セキュリティにするだけで、これらの全ての記憶デバイスについて、記憶デバイスの入れ替え脅威を高いセキュリティレベルで排除することを可能にする。

【図面の簡単な説明】

【0019】

【図1】SoC及びそれに接続されたデバイスでなるシステムの構成例を示す図である。

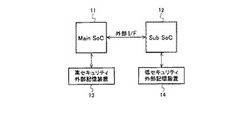

【図2】本発明に係る、複数のSoCが接続されてなる半導体デバイスの一構成例を示す図である。

【図3】図2の半導体デバイスにおけるMain SoCの起動処理例を説明するためのフロー図である。

【図4】図2の半導体デバイスにおけるSub SoCの起動処理例を説明するためのフロー図である。

【図5】本発明に係る、複数のSoCが接続されてなる半導体デバイスの他の構成例を示す図である。

【図6】従来技術による、複数のSoCが接続されてなる半導体デバイスの構成例を示す図である。

【発明を実施するための形態】

【0020】

本発明に係る半導体デバイスは、2以上の半導体集積回路が搭載されており、複合半導体集積回路装置やハイブリッド集積回路などとも呼ぶこともある。これら半導体集積回路は一般的には基板上に搭載されている。個々の半導体集積回路は、プロセッサ(内部プロセッサ)をはじめ、メインメモリ用のメモリI/F、プロセッサを有する他の半導体集積回路用の外部I/F、及びレジスタを備えたLSI等の回路であり、以下、プロセッサを有することからSoCとして説明する。

【0021】

図1は、SoC及びそれに接続されたデバイスでなるシステムの構成例を示す図で、図2は、本発明に係る、複数のSoCが接続されてなる半導体デバイスの一構成例を示す図である。図2では、半導体デバイスに搭載されるSoCの数が2つである場合を例示するが、2以上であれば適用できる。

【0022】

図1で例示するSoC1はプロセッサ(以下、CPU10bで例示)を備えると共に、タイマ10a、外部I/F10c、メモリコントロール10d、及び外部記憶装置I/F10eを備え、これらがシステムバスに接続されている。そして、SoC1には、メモリコントロール10dにメインメモリとしてのメモリ2が、外部記憶装置I/F10eに外部記憶装置3がそれぞれ接続できるようになっている。

【0023】

CPU10bは、SoC1の全体を制御するモジュールである。起動時、外部記憶装置3に保存しているプログラムデータを読み出し、内部のRAM上に展開することで動作を開始する。なお、このプロセッサとしては、CPUの他に、例えばDSP(Digital Signal Processor)、GPU(Graphics Processor Unit)など、様々なプロセッサが適用できる。また、タイマ10aは、CPU10bから指示された時間を計測し、計測完了後、CPU10bに対してインターラプトを発行するモジュールである。

【0024】

メモリコントロール(メモリコントローラ)10dは、メインメモリであるメモリ2を接続するためのメモリI/Fの一例であって、SDRAM(Synchronous Dynamic RAM)やDDR SDRAM(Double-Data-Rate SDRAM)など、基板上で接続されたメモリ2とのデータ送受信を行うモジュールである。メモリコントロール10dは、CPU10bなどからのデータ送受信要求をバス経由で受け付け、指示に従ってメインメモリであるメモリ2に対してデータ送受信要求を行う。また、その結果を、指示元であるCPU10bなどに対して戻す。

【0025】

外部記憶装置I/F10eは、外部記憶装置3内に保存されたデータの読み出し、書き込みを行うモジュールである。外部記憶装置I/F10eは、CPU10bの指示に従って外部記憶装置3内のデータにアクセスし、主にメモリコントロール10dとの間でデータ送受信を行う。

【0026】

外部I/F10cは、SoC1に接続される外部デバイスとデータ転送やメッセージ転送を行うためのI/Fモジュールである。外部デバイスとは、例えば基板上で接続された他のSoCやASIC(Application Specific Integrated Circuit)などである。また、このインターフェース規格としては、PCI(Peripheral Component Interconnect)やPCI Expressなどがある。

【0027】

このように、SoC1では、外部I/F10cにより他のSoCを接続することが可能となっており、本発明に係る半導体デバイスは、上記外部デバイスとして他のSoCが接続したようなシステム構成をもつ。ここで、SoC1に外部I/F10cを介して接続したSoCは、SoC1と同様に、CPU等のプロセッサ、外部I/F、メモリコントロール、外部記憶装置I/Fなどを備える。

【0028】

また、SoC1内のプロセッサと他のSoC内のプロセッサの両方が、システムを制御するためのレジスタ群やメインメモリにアクセス可能となっている。つまり、半導体デバイスでは、双方のプロセッサがいずれのSoCを制御することも可能になっている。

【0029】

そして、本発明に係る半導体デバイスは、このようなSoC1及び他のSoCといった2以上のSoCを搭載し、その主たる特徴として次の特徴を有する。

すなわち、その少なくとも1つのSoCの起動プログラムは、高セキュリティデバイスに保存されるなどによって、他のSoCの起動プログラムより信頼性が確保されているものとする。つまり、その少なくとも1つのSoCの起動プログラムが格納された外部記憶装置3は、他のSoCの起動プログラムが格納された外部記憶装置3に比べて、高セキュリティとする。

【0030】

そして、その少なくとも1つのSoCは、その信頼性が確保された起動プログラムで起動すると共に、その起動した起動プログラムにより上記他のSoCの起動プログラムの認証を行う。換言すれば、上記少なくとも1つのSoCは、上記他のSoCが単独で起動した場合よりも起動プログラムの信頼性を確保可能な方法で起動され、起動後(なお、起動開始後であれば起動途中であってもよい)にSoC間の通信をすることによって、上記他のSoCの起動プログラムを認証する。これにより、起動プログラムの信頼性を確保するSoCは1つのみで済むため、システムのセキュリティ性を維持しつつ、低コスト化が実現可能となる。

【0031】

以下、図2を併せて参照しながら、上記少なくとも1つのSoCがMain SoC11で例示し、上記他のSoCがSub SoC12で例示して、本発明に係る半導体デバイスについて説明するが、これに限ったものではない。この例では、図1のSoC1、それに外部I/F10cを介して接続したSoCが、それぞれ図2のMain SoC11、Sub SoC12であることを前提にしている。しかし、上述したようにMain SoC11とSub SoC12とは同様であり、特に基本的なハードウェア構成は同様であり、主に起動プログラムが相違している。但し、上記少なくとも1つのSoCの例であるMain SoCは高セキュリティであることを前提とするため、ハードウェア構成にて、Sub SoC12に比べMain SoC11の方に耐タンパー性をもたせるように構成してもよい。以下、区別のために、Main SoC11の起動プログラムを起動プログラムMとし、Sub SoC12の起動プログラムを起動プログラムSとして説明する。

【0032】

Main SoC11とSub SoC12は、図1で説明するとお互いの外部I/F10cによって接続する。従来技術では、起動するプログラムの信頼性を確保するために、図6で説明したように、各々のSoC11,12が高セキュリティ性の外部記憶装置を利用してCPUを起動させる必要があった。

【0033】

これに対して本発明に係る半導体デバイスにおいては、Sub SoC12の起動プログラムSは低セキュリティで済むため、Sub SoC12に接続する外部記憶装置14は低セキュリティの装置で済む。従って、起動に関して、Main SoC11とSub SoC12における違いは、基本的に図1で説明すると外部記憶装置I/F10eのみとなる。より具体的には、Main SoC11は外部記憶装置I/Fとして、セキュリティ性が高い外部記憶装置13にアクセスするI/Fを有し、Sub SoC12は外部記憶装置I/Fとして外部記憶装置13より低セキュリティの外部記憶装置14にアクセスするためのI/Fを有する。

【0034】

つまり、Main SoC11の起動プログラムMは、Main SoC11のプログラム格納デバイスの例である高セキュリティ外部記憶装置13に記憶され、Sub SoC12の起動プログラムSは、Sub SoC12のプログラム格納デバイスの例である低セキュリティ外部記憶装置14に記憶されていることになる。

【0035】

特に、Main SoC11は外部記憶装置I/Fとして、セキュリティ性が高く且つオンボードタイプのメモリにアクセスするI/Fを有することが好ましい。そして、Sub SoC12は外部記憶装置I/Fとして上記メモリより低セキュリティで且つ非オンボードタイプの外部記憶装置(HDDやSDカードなどの汎用的な外部記憶装置)にアクセスするためのI/Fを有することが好ましい。図1で説明すると、図1における外部記憶装置3としては、Main SoC11に接続する外部記憶装置13としては高セキュリティでオンボードタイプのメモリなどが採用でき、Sub SoC12に接続する外部記憶装置14としては低セキュリティのHDDやSDカードなどの汎用的な外部記憶装置が採用できる。但し、外部記憶装置14は、非オンボードタイプで無くても外部記憶装置13より低セキュリティであれば、コストを減らす効果が得られる。

【0036】

また、Main SoC11の起動プログラムMは、乱数やハッシュなどで起動プログラムSの認証処理が可能な構成、つまりMain SoC11内部のCPUによって処理可能な構成とすることが好ましい。これにより、TPM等の専用のセキュリティデバイスを利用せずに構成可能になり、専用デバイスが無いため低コストで済み、また乱数利用によりハッシュ値そのものがSub SoC12が搭載された基板上に電送されずに済む。

【0037】

次に、図2で例示した半導体デバイスにおける起動処理の一例を、図3及び図4を参照しながら説明する。図3は、図2の半導体デバイスにおけるMain SoCの起動処理例を説明するためのフロー図で、図4は、図2の半導体デバイスにおけるSub SoCの起動処理例を説明するためのフロー図である。

【0038】

まず、図3を参照しながらMain SoC11の起動処理例を説明する。Main SoC11のCPUは、高セキュリティ外部記憶装置13から起動プログラムMのデータを読み出し、RAM上に展開した後、この起動プログラムMにより起動する(ステップS1)。ステップS1では、高セキュリティデバイスからの起動であるため、起動プログラムMは改竄などされていない。

【0039】

次に、上記CPUは乱数データを生成し(ステップS2)、Sub SoC12と外部I/Fで接続を行う(ステップS3)。接続後、Main SoC11はSub SoC12とデータ転送や通信などを行うことが可能となる。

【0040】

Main SoC11のCPUは、Sub SoC12に対して外部I/Fを介して乱数データ送信を行う(ステップS4)。乱数のデータ長は256bitや512bitなど、製品のセキュリティ要件やハッシュアルゴリズムに応じて決定すればよい。そして、上記CPUは、乱数データ送信と同時若しくは送信前にタイマを起動する(ステップS5)。このタイマは、乱数データ送信からSub SoC12からのハッシュ値が返信されるまでの時間とタイムアウト時間を計測するためのものである。

【0041】

次に、予めMain SoC11側(高セキュリティ外部記憶装置13でもよい)に保持しているSub SoC12の起動プログラムデータハッシュ値(起動プログラムSのデータを元に計算されたハッシュ値)と、自身がステップS2で生成した乱数データを使って、再度ハッシュ演算を行う(ステップS6)。このハッシュ計算の結果を期待値として利用することになる。

【0042】

ステップS6の処理後、又は処理中に、上記CPUはSub SoC12からの返信データを受信したか否かを判定し(ステップS7)、受信していなければタイマで設定されている乱数データ送信時からの指定時間(例えば60秒など)が経過したか否かを判定して(ステップS10)、その指定期間だけ待つ。

【0043】

上記CPUは、Sub SoC12から返信データを受信した場合(ステップS7でYESの場合)、その返信データをステップS6で計算した期待値のデータと比較し、一致したか否かを判定する(ステップS8)。一致した場合(ステップS8でYESの場合)には、Sub SoC12に対してその結果を通知し(ステップS9)、Main SoC11の正常起動を完了する。

【0044】

一方で、不一致の場合(ステップS8でNOの場合)には、結果を通知せずに、まずSub SoC12に対してソフトウェアリセット通知を発行する(ステップS11)。これにより、Sub SoC12はそのCPUがリセット状態となるため全ての機能が停止することになる。次に、上記CPUは、Sub SoC12との接続に用いている外部I/Fでの接続を遮断する(ステップS12)。PCI Expressであればリンク接続を停止、リンクのないI/Fであれば、Sub SoC12からの要求には一切応じないように動作する。

【0045】

また、Sub SoC12から指定時間が経過しても返信データが送信されない場合、つまりMain SoC11で指定時間が経過しても返信データが受信できない場合(ステップS10でNOの場合)には、Sub SoC12は信頼できる起動プログラムからの起動ではない可能性があるため、指定時間経過の時点で、期待値が不一致であった場合と同様にステップS11へ進みソフトウェアリセットを通知する。

【0046】

次に、図4を参照しながらSub SoC12の起動処理例を説明する。この起動プログラムは、Sub SoC12のプログラム格納デバイスの例である低セキュリティ外部記憶装置14に記憶されているものとする。

【0047】

Sub SoC12のCPUは、低セキュリティデバイスである外部記憶装置14から起動プログラムSのデータを読み出し、RAM上に展開した後、この起動プログラムSにより起動する(ステップS21)。上記CPUは、起動後、若しくは起動時に読み出した起動プログラムSのデータのハッシュ値を計算する(ステップS22)。

【0048】

次に、上記CPUは、Main SoC11と外部I/Fで接続を行う(ステップS23)。この処理は、図3のステップS3からの接続要求をトリガとして実行すればよい。接続後、Sub SoC12はMain SoC11とデータ転送や通信などを行うことが可能となる。

【0049】

そして、上記CPUは、起動プログラムSの認証(換言すると起動プログラムSが格納された低セキュリティ外部記憶装置14がその格納部分で書き換えられていないかの認証)を行うために、Main SoC11から乱数データを受信する(ステップS24)。次に、上記CPUは、既にステップS22で算出している起動プログラムSのデータのハッシュ値と、Main SoC11から受信した乱数データからさらにハッシュ演算を行い、認証用のハッシュデータを生成する(ステップS25)。そして、上記CPUは、生成したハッシュデータをMain SoC11へ外部I/Fを介して送信する(ステップS26)。

【0050】

その後、Main SoC11から認証完了通知を受信したとき(ステップS27でYESの場合)、Sub SoC12の起動は完了する。一方、認証完了通知が受信されない場合(ステップS27でNOの場合)、認証完了通知待ちのまま待機状態を継続する。

【0051】

また、ステップS11で説明したように、Main SoC11は、Sub SoC12の起動プログラムSの認証が不可であった場合、不可であったSub SoC12の起動プログラムSに、リセットの命令を行う。これにより、Sub SoC12のCPUを停止状態にすることができる。

【0052】

このように、もし、低セキュリティ外部記憶装置14内の起動プログラムが不正に書き換えられて、その不正プログラムなどによって動作しようとしても、Main SoC11がソフトウェアリセットによってSub SoC12を強制的に停止することで、システム全体のセキュリティ性を高めることができる。

【0053】

以上のように、Main SoC11は従来同様に高セキュリティ性の外部記憶装置13を利用してCPUを起動するが、Sub SoC12は低セキュリティの外部記憶装置14を利用して起動することが可能であり、セキュリティ性を維持しつつ、外部記憶装置にかかるコストを低減することが可能である。Sub SoC12は起動後にMain SoC11から起動プログラムSの認証を受けることによって起動プログラムSの信頼性を確認する。また、Sub SoC12の起動プログラムSが認証不可の場合にはソフトウェアリセットによりSub SoC12を停止させることで、さらにセキュリティ向上が図れる。

【0054】

すなわち、本発明に係る半導体デバイスによれば、各SoCに接続するそれぞれのプログラム格納デバイス(記憶デバイス)のうちの一部(少なくとも1つ)の記憶デバイスのみを高セキュリティにするだけで、これらの全ての記憶デバイスについて、記憶デバイスの入れ替え脅威を高いセキュリティレベルで排除することが可能になる。なお、図3及び図4では、起動プログラムSの認証を行う方法としてハッシュ計算を用いた例を挙げたが、これに限らず、例えば公開鍵暗号方式を利用して認証を行ってもよい。

【0055】

図5は、本発明に係る、複数のSoCが接続されてなる半導体デバイスの他の構成例を示す図である。図5で例示する構成例は、図2の構成例において、Main SoC11に電源管理デバイス15が接続されてなる。Main SoC11と電源管理デバイス15は低速通信ライン、例えばUART(Universal Asynchronous Receiver Transmitter)、USART(Universal Synchronous Asynchronous Receiver Transmitter)やI2C(Inter-Integrated Circuit)やSMBus(System Management Bus)などのシリアル通信で接続されることが多い。

【0056】

図3及び図4で説明した流れでは、異常終了の場合にMain SoC11がSub SoC12に対してソフトウェアリセットを実施することでSub SoC12を停止させている。しかし、さらに確実にSub SoC12及びMain SoC11を備えたシステム全体を停止するために、次のような制御を付加することが好ましい。

【0057】

つまり、Main SoC11は、Sub SoC12の起動プログラムSの認証が不可であった場合、電源管理デバイス15に電源オフの命令を行う。より具体的には、Main SoC11はソフトウェアリセット発行後、図3のステップS12の前後で、電源管理デバイス15に対して電源停止を促す停止通知信号を発行する。電源管理デバイス15は、上記通信ラインを利用してMain SoC11からの電源停止命令を受信すると、システム全体への電源供給を停止する(シャットダウン状態に移行する)。

【0058】

ここで、半導体デバイスに設けられた電源管理デバイス15が、一度にMain SoC11とSub SoC12を含むシステムの電源をオン/オフするような制御を行うデバイスであることを前提に説明したが、Sub SoC12とMain SoC11との電源を個別に制御できるデバイスであるか、Sub SoC12用の電源管理デバイスとMain SoC11用の電源管理デバイスなどといった具合に個別の電源管理デバイスであってもよい。その場合、Main SoC11からの電源オフ命令は、少なくとも不可であったSub SoC12に電源をオフする命令であってもよく、この命令により少なくともこのSub SoC12の電源がオフできる。

【0059】

図5を参照して説明した構成例によれば、ソフトウェアリセットに加え電源を停止させるため、さらに確実な高セキュリティ性を得ることが可能となる。

【符号の説明】

【0060】

1…SoC、2…メモリ、3…外部記憶装置、10a…タイマ、10b…CPU、10c…外部I/F、10d…メモリコントロール、10e…外部記憶装置I/F、11…Main SoC、12…Sub SoC、13…高セキュリティ外部記憶装置、14…低セキュリティ外部記憶装置、15…電源管理デバイス。

【技術分野】

【0001】

本発明は、半導体デバイスに関し、より詳細には、2以上の半導体集積回路を搭載した半導体デバイスに関する。

【背景技術】

【0002】

近年のLSI(Large Scale Integration)のプロセス微細化により、LSIに搭載可能な回路規模はどんどん増加し、LSIが処理する機能や性能は加速度的に向上している。なお、回路規模によっては、その半導体集積回路をVLSI(Very LSI)、ULSI(Ultra-LSI)などと呼ぶこともある。

【0003】

機能向上の1つとして、プロセッサ機能をLSIの中に取り込むと、LSI内部のプロセッサがLSI全体を内部から制御することが可能となり、LSI内部にあたかも一つのシステムを構築できる。このように、半導体集積回路であって、その内部にプロセッサを内蔵してシステムを構築するデバイスは、SoC(System on a Chip)と呼ばれている。

【0004】

SoCと呼ばれる半導体集積回路には、様々なデバイスがある。非常に高性能なプロセッサを搭載し、SoCの外部に接続される全てのデバイスを統合的に管理できるものや、複数のプロセッサを内蔵し、さらに処理能力や演算能力を高めたもの、また、外部デバイスの制御は他のプロセッサに任せて、自身はSoC内部の制御のみを行うものなど様々である。

【0005】

ところで、SoCにおいて、CPU(Central Processing Unit)等のプロセッサを安全に立ち上げることは非常に重要であり、特にセキュリティを重視した製品では確実に信頼できるプログラムデータからプロセッサ(以下、CPUで例示)を起動する必要がある。プログラムが悪意ある者によって差し替えられた状態で起動を許してしまうと、SoC内外の記憶装置に暗号化して保存したデータが読み出される危険性や、暗号化データの復号化ができなかったとして消去されてしまう恐れもある。また、ユーザがプログラムを差し替えられたことに気付かずに利用すると、差し替えられた後に生成したデータは、悪意ある者によって搾取されてしまう。

【0006】

このような危険性を排除するために、CPUを安全且つ確実に立ち上げることは重要である。実現方法として、例えばプログラムデータを暗号化した上で記憶デバイスに保存しておき、起動時に復号化してからRAM(Random Access Memory)上に展開して起動する方法や、TPM(Trusted Platform Module)などのSoCとは別に外部にセキュリティデバイスを利用する方法などがある。

【0007】

さらに、HDD(Hard Disk Drive)やSDカード、USB(Universal Serial Bus)メモリなど一般的に広く利用され汎用性の高い記憶デバイスにプログラムデータを保存するのではなく、基板にオンボードで直接実装するタイプの記憶デバイスに保存することもセキュリティ性を高める方法の一つである。独自のI/F(Interface)プロトコルで動作するデバイスの採用や、Flash DIMM(Dual Inline Memory Module)など一般的にはユーザが入手しにくいデバイスを採用する方法もある。オンボードタイプデバイスやユーザが入手しにくいデバイスなどの場合、第三者によってデバイスの入れ替えを行うのは難しいばかりではなく、基板に実装したまま外部から書き換えることは非常に専門的な知識が必要となるため、セキュリティ性が高くなる。

【0008】

複合機(MFP)を例に挙げ具体的に説明すると、次のようになる。一般的なモデル(製品)とセキュリティを重視したモデルの2種類ある場合、セキュリティを重視したモデルではデータの暗号化や、動作時に一次的に保存したメモリデータ、HDDデータの消去などといったセキュリティ機能が付加される。ここで脅威となる一例は、一般的なモデルのプログラムデータ格納デバイスをセキュリティを重視したモデルのデバイスと置き換えることが挙げられる。置き換え後にCPUの起動が可能であると、それまでに蓄積されたデータの消去がなされず、また今後利用する際に生成されるデータは暗号化されていないため、非常に危険な状態となってしまう。従って、CPUを安全に起動することは、セキュリティ上、非常に重要な要素となる。

【0009】

一方、近年、MFPに限らず様々なシステムは、大規模化・複雑化に伴って複数のCPUによってシステム全体を制御することが多くなってきた。例えば、特許文献1には、上述したようなSoCで代表される半導体集積回路を、同じ回路基板などに2以上搭載した半導体デバイスが開示されている。この半導体デバイスも複数のCPUをもつことになる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2001−13215号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

そして、このように複数のCPUを搭載する半導体デバイスの場合、全てのCPUに対して安全に起動することが求められる。プログラム格納デバイスの入れ替え脅威を排除するためには、全ての記憶デバイスを交換リスクがなく安全性の高いデバイスにする必要が生じる。従って、図6で示す半導体デバイスのように、Main SoC11とSub SoC12に対してプログラム格納デバイスとしてそれぞれ接続する外部記憶装置50a,50bは、いずれも高セキュリティの装置を採用する必要が生じる。

【0012】

しかしながら、一般的にHDDなど先に挙げた汎用性の高い記憶デバイスに比べ、セキュリティ性の高い記憶デバイスは技術的に高度であったり、販売数量が少ないなどといった理由によりコストが高くなる傾向にある。

【0013】

本発明は、上述のような実状に鑑みてなされたものであり、その目的は、2以上の半導体集積回路を搭載した半導体デバイスにおいて、各半導体集積回路に接続するそれぞれのプログラム格納デバイス(記憶デバイス)のうちの一部の記憶デバイスのみを高セキュリティにするだけで、これらの全ての記憶デバイスについて、記憶デバイスの入れ替え脅威を高いセキュリティレベルで排除することを可能にすることにある。

【課題を解決するための手段】

【0014】

上記課題を解決するために、本発明の第1の技術手段は、2以上の半導体集積回路を搭載した半導体デバイスであって、少なくとも1つの半導体集積回路は、他の半導体集積回路の起動プログラムより信頼性が確保された起動プログラムで起動し、該起動した起動プログラムにより前記他の半導体集積回路の起動プログラムの認証を行うことを特徴としたものである。

【0015】

第2の技術手段は、第1の技術手段において、前記少なくとも1つの半導体集積回路は、前記他の半導体集積回路の起動プログラムの認証が不可であった場合、不可であった前記他の半導体集積回路の起動プログラムに、リセットの命令を行うことを特徴としたものである。

【0016】

第3の技術手段は、第2の技術手段において、前記少なくとも1つの半導体集積回路は、前記他の半導体集積回路の起動プログラムの認証が不可であった場合、少なくとも不可であった前記他の半導体集積回路に電源を供給するための電源管理デバイスに、電源オフの命令を行うことを特徴としたものである。

【0017】

第4の技術手段は、第1〜第3のいずれか1の技術手段において、前記少なくとも1つの半導体集積回路は、オンボードタイプのメモリにアクセスするためのインターフェースを有し、前記他の半導体集積回路は、前記メモリより低セキュリティで且つ非オンボードタイプの外部記憶装置にアクセスするためのインターフェースを有することを特徴としたものである。

【発明の効果】

【0018】

本発明に係る半導体デバイスによれば、各半導体集積回路に接続するそれぞれのプログラム格納デバイス(記憶デバイス)のうちの一部の記憶デバイスのみを高セキュリティにするだけで、これらの全ての記憶デバイスについて、記憶デバイスの入れ替え脅威を高いセキュリティレベルで排除することを可能にする。

【図面の簡単な説明】

【0019】

【図1】SoC及びそれに接続されたデバイスでなるシステムの構成例を示す図である。

【図2】本発明に係る、複数のSoCが接続されてなる半導体デバイスの一構成例を示す図である。

【図3】図2の半導体デバイスにおけるMain SoCの起動処理例を説明するためのフロー図である。

【図4】図2の半導体デバイスにおけるSub SoCの起動処理例を説明するためのフロー図である。

【図5】本発明に係る、複数のSoCが接続されてなる半導体デバイスの他の構成例を示す図である。

【図6】従来技術による、複数のSoCが接続されてなる半導体デバイスの構成例を示す図である。

【発明を実施するための形態】

【0020】

本発明に係る半導体デバイスは、2以上の半導体集積回路が搭載されており、複合半導体集積回路装置やハイブリッド集積回路などとも呼ぶこともある。これら半導体集積回路は一般的には基板上に搭載されている。個々の半導体集積回路は、プロセッサ(内部プロセッサ)をはじめ、メインメモリ用のメモリI/F、プロセッサを有する他の半導体集積回路用の外部I/F、及びレジスタを備えたLSI等の回路であり、以下、プロセッサを有することからSoCとして説明する。

【0021】

図1は、SoC及びそれに接続されたデバイスでなるシステムの構成例を示す図で、図2は、本発明に係る、複数のSoCが接続されてなる半導体デバイスの一構成例を示す図である。図2では、半導体デバイスに搭載されるSoCの数が2つである場合を例示するが、2以上であれば適用できる。

【0022】

図1で例示するSoC1はプロセッサ(以下、CPU10bで例示)を備えると共に、タイマ10a、外部I/F10c、メモリコントロール10d、及び外部記憶装置I/F10eを備え、これらがシステムバスに接続されている。そして、SoC1には、メモリコントロール10dにメインメモリとしてのメモリ2が、外部記憶装置I/F10eに外部記憶装置3がそれぞれ接続できるようになっている。

【0023】

CPU10bは、SoC1の全体を制御するモジュールである。起動時、外部記憶装置3に保存しているプログラムデータを読み出し、内部のRAM上に展開することで動作を開始する。なお、このプロセッサとしては、CPUの他に、例えばDSP(Digital Signal Processor)、GPU(Graphics Processor Unit)など、様々なプロセッサが適用できる。また、タイマ10aは、CPU10bから指示された時間を計測し、計測完了後、CPU10bに対してインターラプトを発行するモジュールである。

【0024】

メモリコントロール(メモリコントローラ)10dは、メインメモリであるメモリ2を接続するためのメモリI/Fの一例であって、SDRAM(Synchronous Dynamic RAM)やDDR SDRAM(Double-Data-Rate SDRAM)など、基板上で接続されたメモリ2とのデータ送受信を行うモジュールである。メモリコントロール10dは、CPU10bなどからのデータ送受信要求をバス経由で受け付け、指示に従ってメインメモリであるメモリ2に対してデータ送受信要求を行う。また、その結果を、指示元であるCPU10bなどに対して戻す。

【0025】

外部記憶装置I/F10eは、外部記憶装置3内に保存されたデータの読み出し、書き込みを行うモジュールである。外部記憶装置I/F10eは、CPU10bの指示に従って外部記憶装置3内のデータにアクセスし、主にメモリコントロール10dとの間でデータ送受信を行う。

【0026】

外部I/F10cは、SoC1に接続される外部デバイスとデータ転送やメッセージ転送を行うためのI/Fモジュールである。外部デバイスとは、例えば基板上で接続された他のSoCやASIC(Application Specific Integrated Circuit)などである。また、このインターフェース規格としては、PCI(Peripheral Component Interconnect)やPCI Expressなどがある。

【0027】

このように、SoC1では、外部I/F10cにより他のSoCを接続することが可能となっており、本発明に係る半導体デバイスは、上記外部デバイスとして他のSoCが接続したようなシステム構成をもつ。ここで、SoC1に外部I/F10cを介して接続したSoCは、SoC1と同様に、CPU等のプロセッサ、外部I/F、メモリコントロール、外部記憶装置I/Fなどを備える。

【0028】

また、SoC1内のプロセッサと他のSoC内のプロセッサの両方が、システムを制御するためのレジスタ群やメインメモリにアクセス可能となっている。つまり、半導体デバイスでは、双方のプロセッサがいずれのSoCを制御することも可能になっている。

【0029】

そして、本発明に係る半導体デバイスは、このようなSoC1及び他のSoCといった2以上のSoCを搭載し、その主たる特徴として次の特徴を有する。

すなわち、その少なくとも1つのSoCの起動プログラムは、高セキュリティデバイスに保存されるなどによって、他のSoCの起動プログラムより信頼性が確保されているものとする。つまり、その少なくとも1つのSoCの起動プログラムが格納された外部記憶装置3は、他のSoCの起動プログラムが格納された外部記憶装置3に比べて、高セキュリティとする。

【0030】

そして、その少なくとも1つのSoCは、その信頼性が確保された起動プログラムで起動すると共に、その起動した起動プログラムにより上記他のSoCの起動プログラムの認証を行う。換言すれば、上記少なくとも1つのSoCは、上記他のSoCが単独で起動した場合よりも起動プログラムの信頼性を確保可能な方法で起動され、起動後(なお、起動開始後であれば起動途中であってもよい)にSoC間の通信をすることによって、上記他のSoCの起動プログラムを認証する。これにより、起動プログラムの信頼性を確保するSoCは1つのみで済むため、システムのセキュリティ性を維持しつつ、低コスト化が実現可能となる。

【0031】

以下、図2を併せて参照しながら、上記少なくとも1つのSoCがMain SoC11で例示し、上記他のSoCがSub SoC12で例示して、本発明に係る半導体デバイスについて説明するが、これに限ったものではない。この例では、図1のSoC1、それに外部I/F10cを介して接続したSoCが、それぞれ図2のMain SoC11、Sub SoC12であることを前提にしている。しかし、上述したようにMain SoC11とSub SoC12とは同様であり、特に基本的なハードウェア構成は同様であり、主に起動プログラムが相違している。但し、上記少なくとも1つのSoCの例であるMain SoCは高セキュリティであることを前提とするため、ハードウェア構成にて、Sub SoC12に比べMain SoC11の方に耐タンパー性をもたせるように構成してもよい。以下、区別のために、Main SoC11の起動プログラムを起動プログラムMとし、Sub SoC12の起動プログラムを起動プログラムSとして説明する。

【0032】

Main SoC11とSub SoC12は、図1で説明するとお互いの外部I/F10cによって接続する。従来技術では、起動するプログラムの信頼性を確保するために、図6で説明したように、各々のSoC11,12が高セキュリティ性の外部記憶装置を利用してCPUを起動させる必要があった。

【0033】

これに対して本発明に係る半導体デバイスにおいては、Sub SoC12の起動プログラムSは低セキュリティで済むため、Sub SoC12に接続する外部記憶装置14は低セキュリティの装置で済む。従って、起動に関して、Main SoC11とSub SoC12における違いは、基本的に図1で説明すると外部記憶装置I/F10eのみとなる。より具体的には、Main SoC11は外部記憶装置I/Fとして、セキュリティ性が高い外部記憶装置13にアクセスするI/Fを有し、Sub SoC12は外部記憶装置I/Fとして外部記憶装置13より低セキュリティの外部記憶装置14にアクセスするためのI/Fを有する。

【0034】

つまり、Main SoC11の起動プログラムMは、Main SoC11のプログラム格納デバイスの例である高セキュリティ外部記憶装置13に記憶され、Sub SoC12の起動プログラムSは、Sub SoC12のプログラム格納デバイスの例である低セキュリティ外部記憶装置14に記憶されていることになる。

【0035】

特に、Main SoC11は外部記憶装置I/Fとして、セキュリティ性が高く且つオンボードタイプのメモリにアクセスするI/Fを有することが好ましい。そして、Sub SoC12は外部記憶装置I/Fとして上記メモリより低セキュリティで且つ非オンボードタイプの外部記憶装置(HDDやSDカードなどの汎用的な外部記憶装置)にアクセスするためのI/Fを有することが好ましい。図1で説明すると、図1における外部記憶装置3としては、Main SoC11に接続する外部記憶装置13としては高セキュリティでオンボードタイプのメモリなどが採用でき、Sub SoC12に接続する外部記憶装置14としては低セキュリティのHDDやSDカードなどの汎用的な外部記憶装置が採用できる。但し、外部記憶装置14は、非オンボードタイプで無くても外部記憶装置13より低セキュリティであれば、コストを減らす効果が得られる。

【0036】

また、Main SoC11の起動プログラムMは、乱数やハッシュなどで起動プログラムSの認証処理が可能な構成、つまりMain SoC11内部のCPUによって処理可能な構成とすることが好ましい。これにより、TPM等の専用のセキュリティデバイスを利用せずに構成可能になり、専用デバイスが無いため低コストで済み、また乱数利用によりハッシュ値そのものがSub SoC12が搭載された基板上に電送されずに済む。

【0037】

次に、図2で例示した半導体デバイスにおける起動処理の一例を、図3及び図4を参照しながら説明する。図3は、図2の半導体デバイスにおけるMain SoCの起動処理例を説明するためのフロー図で、図4は、図2の半導体デバイスにおけるSub SoCの起動処理例を説明するためのフロー図である。

【0038】

まず、図3を参照しながらMain SoC11の起動処理例を説明する。Main SoC11のCPUは、高セキュリティ外部記憶装置13から起動プログラムMのデータを読み出し、RAM上に展開した後、この起動プログラムMにより起動する(ステップS1)。ステップS1では、高セキュリティデバイスからの起動であるため、起動プログラムMは改竄などされていない。

【0039】

次に、上記CPUは乱数データを生成し(ステップS2)、Sub SoC12と外部I/Fで接続を行う(ステップS3)。接続後、Main SoC11はSub SoC12とデータ転送や通信などを行うことが可能となる。

【0040】

Main SoC11のCPUは、Sub SoC12に対して外部I/Fを介して乱数データ送信を行う(ステップS4)。乱数のデータ長は256bitや512bitなど、製品のセキュリティ要件やハッシュアルゴリズムに応じて決定すればよい。そして、上記CPUは、乱数データ送信と同時若しくは送信前にタイマを起動する(ステップS5)。このタイマは、乱数データ送信からSub SoC12からのハッシュ値が返信されるまでの時間とタイムアウト時間を計測するためのものである。

【0041】

次に、予めMain SoC11側(高セキュリティ外部記憶装置13でもよい)に保持しているSub SoC12の起動プログラムデータハッシュ値(起動プログラムSのデータを元に計算されたハッシュ値)と、自身がステップS2で生成した乱数データを使って、再度ハッシュ演算を行う(ステップS6)。このハッシュ計算の結果を期待値として利用することになる。

【0042】

ステップS6の処理後、又は処理中に、上記CPUはSub SoC12からの返信データを受信したか否かを判定し(ステップS7)、受信していなければタイマで設定されている乱数データ送信時からの指定時間(例えば60秒など)が経過したか否かを判定して(ステップS10)、その指定期間だけ待つ。

【0043】

上記CPUは、Sub SoC12から返信データを受信した場合(ステップS7でYESの場合)、その返信データをステップS6で計算した期待値のデータと比較し、一致したか否かを判定する(ステップS8)。一致した場合(ステップS8でYESの場合)には、Sub SoC12に対してその結果を通知し(ステップS9)、Main SoC11の正常起動を完了する。

【0044】

一方で、不一致の場合(ステップS8でNOの場合)には、結果を通知せずに、まずSub SoC12に対してソフトウェアリセット通知を発行する(ステップS11)。これにより、Sub SoC12はそのCPUがリセット状態となるため全ての機能が停止することになる。次に、上記CPUは、Sub SoC12との接続に用いている外部I/Fでの接続を遮断する(ステップS12)。PCI Expressであればリンク接続を停止、リンクのないI/Fであれば、Sub SoC12からの要求には一切応じないように動作する。

【0045】

また、Sub SoC12から指定時間が経過しても返信データが送信されない場合、つまりMain SoC11で指定時間が経過しても返信データが受信できない場合(ステップS10でNOの場合)には、Sub SoC12は信頼できる起動プログラムからの起動ではない可能性があるため、指定時間経過の時点で、期待値が不一致であった場合と同様にステップS11へ進みソフトウェアリセットを通知する。

【0046】

次に、図4を参照しながらSub SoC12の起動処理例を説明する。この起動プログラムは、Sub SoC12のプログラム格納デバイスの例である低セキュリティ外部記憶装置14に記憶されているものとする。

【0047】

Sub SoC12のCPUは、低セキュリティデバイスである外部記憶装置14から起動プログラムSのデータを読み出し、RAM上に展開した後、この起動プログラムSにより起動する(ステップS21)。上記CPUは、起動後、若しくは起動時に読み出した起動プログラムSのデータのハッシュ値を計算する(ステップS22)。

【0048】

次に、上記CPUは、Main SoC11と外部I/Fで接続を行う(ステップS23)。この処理は、図3のステップS3からの接続要求をトリガとして実行すればよい。接続後、Sub SoC12はMain SoC11とデータ転送や通信などを行うことが可能となる。

【0049】

そして、上記CPUは、起動プログラムSの認証(換言すると起動プログラムSが格納された低セキュリティ外部記憶装置14がその格納部分で書き換えられていないかの認証)を行うために、Main SoC11から乱数データを受信する(ステップS24)。次に、上記CPUは、既にステップS22で算出している起動プログラムSのデータのハッシュ値と、Main SoC11から受信した乱数データからさらにハッシュ演算を行い、認証用のハッシュデータを生成する(ステップS25)。そして、上記CPUは、生成したハッシュデータをMain SoC11へ外部I/Fを介して送信する(ステップS26)。

【0050】

その後、Main SoC11から認証完了通知を受信したとき(ステップS27でYESの場合)、Sub SoC12の起動は完了する。一方、認証完了通知が受信されない場合(ステップS27でNOの場合)、認証完了通知待ちのまま待機状態を継続する。

【0051】

また、ステップS11で説明したように、Main SoC11は、Sub SoC12の起動プログラムSの認証が不可であった場合、不可であったSub SoC12の起動プログラムSに、リセットの命令を行う。これにより、Sub SoC12のCPUを停止状態にすることができる。

【0052】

このように、もし、低セキュリティ外部記憶装置14内の起動プログラムが不正に書き換えられて、その不正プログラムなどによって動作しようとしても、Main SoC11がソフトウェアリセットによってSub SoC12を強制的に停止することで、システム全体のセキュリティ性を高めることができる。

【0053】

以上のように、Main SoC11は従来同様に高セキュリティ性の外部記憶装置13を利用してCPUを起動するが、Sub SoC12は低セキュリティの外部記憶装置14を利用して起動することが可能であり、セキュリティ性を維持しつつ、外部記憶装置にかかるコストを低減することが可能である。Sub SoC12は起動後にMain SoC11から起動プログラムSの認証を受けることによって起動プログラムSの信頼性を確認する。また、Sub SoC12の起動プログラムSが認証不可の場合にはソフトウェアリセットによりSub SoC12を停止させることで、さらにセキュリティ向上が図れる。

【0054】

すなわち、本発明に係る半導体デバイスによれば、各SoCに接続するそれぞれのプログラム格納デバイス(記憶デバイス)のうちの一部(少なくとも1つ)の記憶デバイスのみを高セキュリティにするだけで、これらの全ての記憶デバイスについて、記憶デバイスの入れ替え脅威を高いセキュリティレベルで排除することが可能になる。なお、図3及び図4では、起動プログラムSの認証を行う方法としてハッシュ計算を用いた例を挙げたが、これに限らず、例えば公開鍵暗号方式を利用して認証を行ってもよい。

【0055】

図5は、本発明に係る、複数のSoCが接続されてなる半導体デバイスの他の構成例を示す図である。図5で例示する構成例は、図2の構成例において、Main SoC11に電源管理デバイス15が接続されてなる。Main SoC11と電源管理デバイス15は低速通信ライン、例えばUART(Universal Asynchronous Receiver Transmitter)、USART(Universal Synchronous Asynchronous Receiver Transmitter)やI2C(Inter-Integrated Circuit)やSMBus(System Management Bus)などのシリアル通信で接続されることが多い。

【0056】

図3及び図4で説明した流れでは、異常終了の場合にMain SoC11がSub SoC12に対してソフトウェアリセットを実施することでSub SoC12を停止させている。しかし、さらに確実にSub SoC12及びMain SoC11を備えたシステム全体を停止するために、次のような制御を付加することが好ましい。

【0057】

つまり、Main SoC11は、Sub SoC12の起動プログラムSの認証が不可であった場合、電源管理デバイス15に電源オフの命令を行う。より具体的には、Main SoC11はソフトウェアリセット発行後、図3のステップS12の前後で、電源管理デバイス15に対して電源停止を促す停止通知信号を発行する。電源管理デバイス15は、上記通信ラインを利用してMain SoC11からの電源停止命令を受信すると、システム全体への電源供給を停止する(シャットダウン状態に移行する)。

【0058】

ここで、半導体デバイスに設けられた電源管理デバイス15が、一度にMain SoC11とSub SoC12を含むシステムの電源をオン/オフするような制御を行うデバイスであることを前提に説明したが、Sub SoC12とMain SoC11との電源を個別に制御できるデバイスであるか、Sub SoC12用の電源管理デバイスとMain SoC11用の電源管理デバイスなどといった具合に個別の電源管理デバイスであってもよい。その場合、Main SoC11からの電源オフ命令は、少なくとも不可であったSub SoC12に電源をオフする命令であってもよく、この命令により少なくともこのSub SoC12の電源がオフできる。

【0059】

図5を参照して説明した構成例によれば、ソフトウェアリセットに加え電源を停止させるため、さらに確実な高セキュリティ性を得ることが可能となる。

【符号の説明】

【0060】

1…SoC、2…メモリ、3…外部記憶装置、10a…タイマ、10b…CPU、10c…外部I/F、10d…メモリコントロール、10e…外部記憶装置I/F、11…Main SoC、12…Sub SoC、13…高セキュリティ外部記憶装置、14…低セキュリティ外部記憶装置、15…電源管理デバイス。

【特許請求の範囲】

【請求項1】

2以上の半導体集積回路を搭載した半導体デバイスであって、少なくとも1つの半導体集積回路は、他の半導体集積回路の起動プログラムより信頼性が確保された起動プログラムで起動し、該起動した起動プログラムにより前記他の半導体集積回路の起動プログラムの認証を行うことを特徴とする半導体デバイス。

【請求項2】

前記少なくとも1つの半導体集積回路は、前記他の半導体集積回路の起動プログラムの認証が不可であった場合、不可であった前記他の半導体集積回路の起動プログラムに、リセットの命令を行うことを特徴とする請求項1に記載の半導体デバイス。

【請求項3】

前記少なくとも1つの半導体集積回路は、前記他の半導体集積回路の起動プログラムの認証が不可であった場合、少なくとも不可であった前記他の半導体集積回路に電源を供給するための電源管理デバイスに、電源オフの命令を行うことを特徴とする請求項2に記載の半導体デバイス。

【請求項4】

前記少なくとも1つの半導体集積回路は、オンボードタイプのメモリにアクセスするためのインターフェースを有し、前記他の半導体集積回路は、前記メモリより低セキュリティで且つ非オンボードタイプの外部記憶装置にアクセスするためのインターフェースを有することを特徴とする請求項1〜3のいずれか1項に記載の半導体デバイス。

【請求項1】

2以上の半導体集積回路を搭載した半導体デバイスであって、少なくとも1つの半導体集積回路は、他の半導体集積回路の起動プログラムより信頼性が確保された起動プログラムで起動し、該起動した起動プログラムにより前記他の半導体集積回路の起動プログラムの認証を行うことを特徴とする半導体デバイス。

【請求項2】

前記少なくとも1つの半導体集積回路は、前記他の半導体集積回路の起動プログラムの認証が不可であった場合、不可であった前記他の半導体集積回路の起動プログラムに、リセットの命令を行うことを特徴とする請求項1に記載の半導体デバイス。

【請求項3】

前記少なくとも1つの半導体集積回路は、前記他の半導体集積回路の起動プログラムの認証が不可であった場合、少なくとも不可であった前記他の半導体集積回路に電源を供給するための電源管理デバイスに、電源オフの命令を行うことを特徴とする請求項2に記載の半導体デバイス。

【請求項4】

前記少なくとも1つの半導体集積回路は、オンボードタイプのメモリにアクセスするためのインターフェースを有し、前記他の半導体集積回路は、前記メモリより低セキュリティで且つ非オンボードタイプの外部記憶装置にアクセスするためのインターフェースを有することを特徴とする請求項1〜3のいずれか1項に記載の半導体デバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−252667(P2012−252667A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2011−126920(P2011−126920)

【出願日】平成23年6月7日(2011.6.7)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成23年6月7日(2011.6.7)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]