半導体データ処理デバイス

【課題】システムに実装された状態で内部回路に対して自由度の高いセルフテストを実行でき半導体データ処理デバイスを提供する。

【解決手段】CPU及び内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路(7,8)と、テスト回路を起動するテスト制御回路(6)と共に、テスト起動レジスタ(9)、テスト状態レジスタ(10)、及びテスト汎用レジスタ(11)を備える。テスト起動レジスタにスタートビットがセットされて、テスト制御回路は、テスト回路によるCPUなどのテスト動作を起動しテスト結果を蓄積し、テスト動作の終了に応答してCPUと内部回路をリセットする。この後、CPUは、テスト状態レジスタの値によりテストが行われたことを確認すると、テスト回路よりテスト結果を読み出して判定を行い、テスト汎用レジスタの設定に従って、続けてテストを行うかどうかなどを判定しテストを続けることが可能とされる。

【解決手段】CPU及び内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路(7,8)と、テスト回路を起動するテスト制御回路(6)と共に、テスト起動レジスタ(9)、テスト状態レジスタ(10)、及びテスト汎用レジスタ(11)を備える。テスト起動レジスタにスタートビットがセットされて、テスト制御回路は、テスト回路によるCPUなどのテスト動作を起動しテスト結果を蓄積し、テスト動作の終了に応答してCPUと内部回路をリセットする。この後、CPUは、テスト状態レジスタの値によりテストが行われたことを確認すると、テスト回路よりテスト結果を読み出して判定を行い、テスト汎用レジスタの設定に従って、続けてテストを行うかどうかなどを判定しテストを続けることが可能とされる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、自己診断機能を備えた半導体データ処理デバイスに係り、例えば自動車の制御システムに適用して有効な技術に関する。

【背景技術】

【0002】

半導体データ処理デバイスたとえばマイクロコンピュータは、家電製品、AV機器、携帯電話、自動車、産業機械等の機器に組み込まれ、メモリに記憶されているプログラムにしたがって処理を行うことで、それぞれの機器の制御を行う半導体集積回路である。

【0003】

自動車では、制御装置の故障が事故につながる可能性があるため、マイクロコンピュータを含む部品に高い信頼性が求められるとともに、故障が発生した場合にはこれを検出して自動車が危険な状態にならないように安全機能を働かせるように設計されている。マイクロコンピュータはセンサやアクチュエータの診断を行ってこれらの故障を検出するだけでなく、マイクロコンピュータ自身の故障も検出する必要がある。

【0004】

マイクロコンピュータの故障検出には様々な方法があるが、マイクロコンピュータの内部でテストパターンを発生させてメモリや論理回路をテストするBIST(Built In Self Test)という手法が用いられるようになってきた。CPUのプログラム処理による方法に比べて短時間でテストを実行することが可能である。

【0005】

特許文献1には、メモリとCPUと論理回路を含むマイクロコンピュータにおいて、メモリとCPUと論理回路のBISTを行う方法が示されている。同文献においては、CPU及び当該CPUが制御する周辺回路などの論理回路にテスト回路がテストパターンを与えて動作させ、動作結果をテスト回路が圧縮し、圧縮結果をCPUが比較するテスト動作と、テスト回路がRAMにテストパターンを与えて動作させ、動作結果をテスト回路が圧縮し、圧縮結果をCPUが比較するテスト動作とを行う、自己診断機能を備える。この自己診断機能を用いるために、パワーオンリセット後にCPUが操作するテスト起動レジスタを備える。テスト起動レジスタにスタートビットをセットすることにより、テスト制御回路はテスト回路を動作させてテストを実行させる。テスト回路によるテスト動作が終了すると、テスト制御回路はCPU等を再度初期化し、そのとき、テスト起動レジスタは初期化対象とはされず、そこにセット状態のテストスタートビットが残されていれば、CPUはテスト回路にテスト動作の結果があることを認識し、これを期待値と比較してテスト結果の正否を判別する。

【0006】

【特許文献1】特開2001−27958号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

上記特許文献1に記載の技術は、パワーオンリセット後にCPUのプログラム処理によってメモリ、CPU、及び論理回路のBISTを実行し、結果をCPUで判定することが可能である。しかしながら、テスト結果が不一致であった場合にテストをリトライしたり、複数のテストを1つずつCPUが結果を確認しながら実行すること、には対応できない。また、テストの結果の判定をCPUのプログラム処理で行うため、CPUがテスト結果の判定のための演算処理機能の一部に故障を有している場合を想定したときには正しく判定が行われていない可能性もある。

【0008】

本発明の目的は、システムに実装された状態で、パワーオンリセット後に内部回路のセルフテストを実行することができ、そのテストが1回限りではなく必要に応じて何回でも実行できるなどの、テストの自由度が高い半導体データ処理デバイスを提供することにある。

【0009】

本発明の別の目的は、上述したテストの自由度が高く、その上、CPUによるテスト結果の判定機能に故障が発生した場合にもテスト結果の判定を行うことができる半導体データ処理デバイスを提供することにある。

【0010】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0012】

すなわち、CPUと内部回路を備えた半導体データ処理デバイスはセルフテスト機能を実現するために、前記CPU及び内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路と、テスト回路に起動をかけるテスト制御回路とともに、テスト起動レジスタ、テスト状態レジスタ、およびテスト汎用レジスタを備える。パワーオンリセット解除後のCPUのプログラム制御によってテスト起動レジスタにスタートビットがセットされることにより、テスト制御回路は、前記テスト回路によるCPUなどのテスト動作を起動してテスト結果を内部に蓄積し、前記テスト回路によるテスト動作の終了に応答して前記CPUと前記内部回路をリセットする。この後、CPUは、リセット解除後のプログラム実行においてテスト状態レジスタの値によりテストが行われたことを確認すると、前記テスト回路よりテスト結果を読み出して判定を行い、テスト汎用レジスタの設定に従って、続けてテストを行うかどうかを判定し、前記テスト起動レジスタに書き込むことによってテストを続けることが可能とされる。

【0013】

上記より、パワーオンリセット後のCPUのプログラム処理によってセルフテストを開始することができ、テスト動作の終了によるリセット解除後には、先にテストが行われたか否か、どの回路部分のテストが行われたか否かをテスト状態レジスタで判別でき、それによってテスト結果の判定を行ったり、また、テスト汎用レジスタの設定に従ってリトライを行ったり、リトライを繰り返したりする動作を、その設定に従って自由に行うことができる。

【0014】

テスト結果の判定はCPUが行ってもよいし、また、それ専用の比較器を配置してもよい。

【発明の効果】

【0015】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0016】

すなわち、システムに実装された状態で、パワーオンリセット後に内部回路のセルフテストを実行することができ、そのテストが1回限りではなく必要に応じて何回でも実行できるなどの自由度が高いセルフテストが可能である。

【0017】

また、テスト結果の判定に専用化された比較器をそなえることにより、CPUによるテスト結果の判定機能に故障が発生した場合にもテスト結果の判定を行うことができる。

【発明を実施するための最良の形態】

【0018】

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0019】

〔1〕本発明に係る半導体データ処理デバイス(100)は、命令をフェッチして実行するCPU(1)と、前記CPUの制御に基づいて動作する内部回路(2,3)とを含み、更に、前記CPUと内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路(7,8)と、前記テスト回路に起動をかけるテスト制御回路(6)と、前記CPUが前記テスト回路に起動をかけるためのテスト起動レジスタ(9)と、前記テスト回路によるテストが完了したことを示すフラグを含むテスト状態レジスタ(10)と、前記CPUが読み出しまたは書き込み可能なテスト汎用レジスタ(11)と、前記CPU、前記内部回路、前記テスト回路、前記テスト制御回路、前記テスト起動レジスタ、及び前記テスト状態レジスタをリセットするリセット制御回路(5)と、を含む。前記テスト制御回路は、前記CPUの前記テスト起動レジスタへの書き込みによって前記テスト回路によるテスト動作を起動し、前記テスト回路によるテスト動作の終了に応答して前記CPUと前記内部回路をリセットする。前記CPUは、リセット解除後のプログラム実行において前記テスト状態レジスタの値によりテストが行われたことを確認して前記テスト回路より結果を読み出して判定を行い、前記テスト汎用レジスタの設定状態に基づいて続けてテストを行うかどうかを判定し、前記テスト起動レジスタを操作することによってテストを続けることが可能である。

【0020】

〔2〕項1の半導体データ処理デバイスにおいて、前記内部回路は、前記CPUによって制御される論理回路(2)と、前記CPUによってアクセス可能にされるメモリ(3)である。前記テスト回路は、前記CPU及び論理回路をテスト対象とする第1のテスト回路(7)と、前記メモリをテスト対象とする第2のテスト回路(8)である。前記テスト起動レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々のスタートフラグビット(STA,STB)を有する。前記テスト状態レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々の状態フラグビット(ENA,ENB)を有する。

【0021】

〔3〕項1の半導体データ処理デバイスにおいて、前記テスト汎用レジスタは、テスト動作のリトライ上限回数データとテスト動作の現在のリトライ回数データを保持するレジスタである。

【0022】

〔4〕本発明の別の観点による半導体データ処理デバイスは、項1の半導体データ処理デバイスの構成に加えて、前記CPUが前記テスト回路のテスト結果の期待値を設定し、前記テスト回路がテストを終了したとき、前記CPUが設定したテスト結果の期待値とテスト回路の出力を比較して結果を出力する比較器(40)を有する。

【0023】

〔5〕項4の半導体データ処理デバイスにおいて、前記比較器による比較結果を前記半導体データ処理デバイスの外部に出力する出力端子を有する。

【0024】

〔6〕項4の半導体データ処理デバイスにおいて、前記内部回路は、前記CPUによって制御される論理回路と、前記CPUによってアクセス可能にされるメモリである。前記テスト回路は、前記CPU及び論理回路をテスト対象とする第1のテスト回路と、前記メモリをテスト対象とする第2のテスト回路である。前記テスト起動レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々のスタートフラグビットを有する。前記テスト状態レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々の状態フラグビットを有する。

【0025】

〔7〕項4の半導体データ処理デバイスにおいて、前記テスト汎用レジスタは、テスト動作のリトライ上限回数データとテスト動作の現在のリトライ回数データを保持するレジスタである。

【0026】

2.実施の形態の詳細

実施の形態について更に詳述する。

【0027】

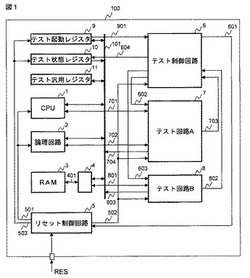

図1は本発明に係る半導体データ処理デバイスの一実施の形態であるマイクロコンピュータのブロック図である。マイクロコンピュータ100は、中央処理装置(CPU)1、論理回路2、RAM3及びリセット制御回路5と共に、BIST(Built In Self Test)回路として、テスト制御回路6、テスト回路A7、テスト回路B8、テスト起動レジスタ9、テスト状態レジスタ10、及びテスト汎用レジスタ11を有する。

【0028】

CPU1は命令を実行して演算やデータ転送などの処理を行う回路である。論理回路2はCPU1の設定に従って特定の機能を実行する回路モジュールであり、例えばダイレクトメモリアクセスコントローラ、A/Dコンバータ、タイマ、通信モジュール、外部入出力回路などである。RAM3はCPU1が実行する命令および処理するデータを記憶する記憶回路である。CPU1、論理回路2、RAM3、テスト制御回路6,7はバス101に接続されている。リセット制御回路5はCPU1及び論理回路2を初期化するためのリセット信号501と、テスト起動レジスタ9及びテスト状態レジスタ10を初期化するためのリセット信号503と、テスト制御回路6、テスト回路A7及びテスト回路B8を初期化するためのリセット信号502を生成する。外部からのリセット要求信号RESによる初期化が指定されたときリセット制御回路5はリセット信号501、502及び503を活性化し、テスト制御回路6からのリセット要求信号601により初期化が指定されたときリセット制御回路5はリセット信号503を活性化する。

【0029】

テスト制御回路6はCPU1、論理回路2、RAM3のテストの起動などの制御を行う。テスト回路A7はCPU1と論理回路2をテストする回路である。テスト制御回路6からのテスト起動信号602により、インタフェース配線701を用いてCPU1にテストパターンを注入し、インタフェース信号配線702を用いて論理回路2にテストパターンを注入する。テストパターンの注入が完了するとCPU1と論理回路2にクロックを与えて動作させ、動作結果をインタフェース配線701、702から取り込み、圧縮して保持する。この動作をテストの数だけ繰り返す。テストが終了するとテスト回路A7はテスト制御回路6に完了信号703を通知する。テスト回路B8はRAM3をテストする回路である。テスト制御回路6からの起動信号603により、インタフェース配線801を用いてRAM3にテストパターンを注入してテストを行い、その結果をインタフェース配線801から取り込む。セレクタ4はRAM3のインタフェース配線401を、通常動作時にはバス101と接続し、テスト時にはテスト回路B8とのインタフェース配線801と接続する。テストが終了するとテスト回路B8はテスト制御回路6に完了信号802を通知する。

【0030】

テスト制御回路6は、特に制限されないが、ステートマシン又はプログラム制御回路で構成される。テスト回路A7及びテスト回路B8は、テストパターンを記憶し若しくは発生するテストパターン回路と、テスト動作結果の圧縮回路を有し、テスト制御回路6の制御に従って動作される。

【0031】

テスト起動レジスタ9はCPU1がバス101を介して書き込み可能なレジスタで、起動を意味する値が設定されるとテスト制御回路6に起動信号901を出力する。パワーオンリセットを行うと、リセット信号503によりテスト起動レジスタは起動しないを意味する値に初期設定される。また、リセット信号502によりテスト制御回路6、テスト回路A7、テスト回路B8が初期化される。CPU1がテスト起動レジスタ9に起動を意味する値を設定するとテストが開始され、完了するとテスト制御回路6はリセット制御回路5にリセット要求601を出力して、リセット信号501により再びCPU1と論理回路2を初期化する。テスト状態レジスタ10はテストが完了したか否かを示すレジスタであり、その値は最初テスト未完を意味する値に初期化され、テストが完了するとテスト制御回路6が信号604によりテスト完了を意味する値に設定変更する。

【0032】

テスト汎用レジスタ11はCPU1が読み出しおよび書き込み可能なレジスタで、リセット制御回路5による初期化は行われない。テスト結果が不一致だった場合にリトライするかどうかを決定したり、複数のテストを実行する場合にテストの総数や完了したテストの番号を記憶するために使用する。CPU1や論理回路2の内部レジスタ(図示せず)はリセット信号501によってテスト終了後に初期化され、RAM3はテストによってデータが書き換えられてしまうため上記目的に使用することはできない。テストを実行しても値を保持することのできるテスト汎用レジスタ11によって上記目的を達成する。

【0033】

リセット要求が解除されるとCPU1はプログラムの実行を開始するが、テスト状態レジスタがテスト完了を意味する値に設定されていることを確認したときは、テストの結果判定を行う。テストの結果判定はCPU1がテスト回路A7から結果データを読み出し、期待値と比較することによって行う。RAMのテスト結果はCPU1がテスト回路B8から合否判定データを読み出すことによって行う。

【0034】

図2は図1におけるテスト起動レジスタ(CR:Control Register)9の一例を示す。テスト起動レジスタ9はCPU1がバス101を介して読み出しおよび書き込み可能な8ビットのレジスタである。ビット7から2は予約でありレジスタの実体は無くても良い。読み出す場合には不定値あるいは“0”などの固定値を読み出すようにする。ビット1はテスト回路B8の起動許可ビット(STB)である。初期値は“0”であり起動しないを意味する。“1”はテスト回路B8によるテストの起動を意味する。起動許可ビットSTBが“1”に設定されると、信号901によって、テスト回路B8にテスト動作が指示され、これによってテスト回路B8がRAM3のテストを開始する。ビット0はテスト回路A7の起動許可ビット(STA)である。初期値は“0”であり起動しないを意味し、“1”はテスト回路A7によるテスト動作の起動を意味する。起動許可ビットSTAが“1”に設定されると、信号901によって、テスト回路A7にテスト動作が指示され、これによってテスト回路A7がCPU1と論理回路2のテストを開始する。信号901はテスト起動レジスタ9の起動許可ビットのビット数に応ずる数複数ビットを有する信号である。

【0035】

図3は図1におけるテスト状態レジスタ(SR:Status Register)10を示す。テスト状態レジスタ10はCPU1がバス101を介して読み出し可能な8ビットのレジスタである。ビット7から2は予約でありレジスタの実体は無くても良い。読み出す場合には不定値あるいは“0”などの固定値を読み出すようにする。ビット1はテスト回路B8の終了フラグ(ENB)である。初期値は“0”であり、テスト回路B8によるテスト動作が終了していないを意味する。“1”はテスト回路B8によるテストの終了を意味し、テスト回路B8のテスト実行が完了するとテスト制御回路6が終了フラグENBを“1”に設定する。ビット0はテスト回路A7の終了フラグ(ENA)である。初期値は“0”であり、テスト回路A7によるテスト動作が終了していないを意味する。“1”はテスト回路A7によるテストの完了を意味し、テスト回路A7のテスト実行が完了するとテスト制御回路6がENAを“1”に設定する。

【0036】

例えば,テスト回路A7及びテスト回路B8のテスト実行が完了すると、STAとENAおよびSTBとENBはそれぞれ値が“1”“1”に設定されることになる。テストを再実行させる場合には、CPU1がSTAとSTBを一旦“0”に戻した後、テスト制御回路6がENAとENBを“0”に設定し、その後に、CPU1がSTAまたはSTBに“1”を設定する手順を採用することができる。上記CPU1がSTAとSTBを一旦“0”に戻す処理は、テストが完了する毎にテスト制御回路6がSTA,STBを順次“0”にクリアする手順に代えてもよい。また、STAとSTBは同時に“1”に設定する必要性は無く、必要な方だけを“1”に設定してもよい。例えば、テスト回路A7の結果が不一致だった場合にCPU1と論理回路2のテストのみリトライする方法が考えられる。STAとSTBが同時に“1”に設定されたとき、テスト制御回路6は、テスト回路A7の動作を先に行ってから、テスト回路B8の動作を開始し、双方のつと実行が完了したときリセット要求601を出力する。

【0037】

特に制限されないが、図2及び図3の例は、テスト回路A7、テスト回路B8に対するテスト対象回路部分をテスト起動レジスタ9によって指定する構成にはなっていない。

【0038】

図7にはテスト回路A7、テスト回路B8に対するテスト対象回路部分(例えば第1回路ブロック、第2回路ブロック、及び第3回路ブロック)をテスト起動レジスタ9によって指定可能にする場合のレジスタ構成が例示される。テスト回路A7、テスト回路B8は夫々3ブロックに分けてテスト可能とする場合について説明する。

【0039】

テスト起動レジスタ(CR)9は、テスト回路A7の起動許可ビットとしてSTA0,STA1,STA2の3ビットを有し、テスト回路B8の起動許可ビットとしてSTB0,STB1,STB2の3ビットを有する。起動許可ビットSTA0,STA1,STA2はテスト回路A7の第1回路ブロック、第2回路ブロック、第3回路ブロックの起動許可/不許可を指示する。起動許可ビットSTB0,STB1,STB2はテスト回路B8の第1回路ブロック、第2回路ブロック、第3回路ブロックの起動許可/不許可を指示する。夫々のビットの論理値の意味は前記と同じである。この場合、前記信号901は6ビットになる。

【0040】

テスト状態レジスタ(SR)10は、テスト回路A7の終了フラグとしてENA0,ENA1,ENA2の3ビットを有し、テスト回路B8の終了フラグとしてENB0,ENB1,ENB2の3ビットを有する。終了フラグENA0,ENA1,ENA2はテスト回路A7の第1回路ブロック、第2回路ブロック、第3回路ブロックのテスト実行完了/未完を意味する。終了フラグENB0,ENB1,ENB2はテスト回路B8の第1回路ブロック、第2回路ブロック、第3回路ブロックのテスト実行完了/未完を意味する。夫々のビットの論理値の意味は前記と同じである。

【0041】

テスト汎用レジスタ(GR)11は、テスト回路A7の現リトライ回数データRTYAを保持するレジスタ(GR1)、テスト回路B8の現リトライ回数データRTYBを保持するレジスタ(GR2)、テスト回路A7のテスト実行に関するリトライ上限回数データLIMAを保持するレジスタGR3、及びテスト回路B8のテスト実行に関するリトライ上限回数データLIMBを保持するレジスタ(GR4)から構成される。

【0042】

図4は図1におけるCPUとテスト回路A7の処理フローを例示する。ここでは、例えばテスト起動レジスタ9として図2の構成、テスト状態レジスタ10として図3の構成を採用し、テスト回路A7のテストを実行する場合について説明する。

【0043】

まずパワーオンリセットによってCPU1とテスト回路A7は共にリセットされる(S20、S30)。リセットが解除されるとCPU1はプログラムの実行を開始し、テスト状態レジスタSRのENAをチェックする(S21)。ENAはパワーオンリセットにより“0”に初期化されているためテスト起動レジスタCRのSTAを設定する処理(S22)に進む。STAの判定処理(S23)によりテストを実行しない場合にはテスト終了となる。一方、テスト回路A7は起動リセット後、起動レジスタCRのSTAのチェック(S31)を行っており、“1”が設定されるまでチェック処理を続ける。STAに“1”が設定されるとテスト回路A7はテスト回路A7のためのテストAを実行する(S32)。テストAが完了するとCPU1および論理回路2のリセットを行う(S33)。またテストAの完了によりテスト制御回路6がSTAを“0”にクリアしているため、テスト回路A7は再びSTAのチェックを行う(S31)。CPU1はリセット(S20)が解除されると再びプログラムの実行を開始し、テスト状態レジスタSRのENAをチェックする(S21)。ENAが“1”に設定されているためテストAの結果確認処理(S24)を実行する。結果が一致していれば次のテストを実行するか否かの判定(S26)を行う。ここで図1におけるテスト汎用レジスタ11が用いられる。テスト汎用レジスタはテスト完了後にリセットされないため、テスト開始前の状態を保持している。テスト汎用レジスタ11は複数あり、例えば2本をテストの総数、実行完了したテスト数の記憶に割り当てることによって、複数回の実行を制御できる。次のテストがある場合にはSTAの設定等のテスト設定(S22)を行ってテストの起動をかける。次のテストが無い場合にはテスト終了となる。テストAの結果確認処理(S24)において結果が不一致だった場合にはリトライを行うか否かの判定(S27)を行う。ここでもテスト汎用レジスタ11が用いられる。例えば2本をリトライ回数の上限、リトライした回数の記憶に割り当てることによって、リトライの実行を制御できる。リトライを行う場合にはテスト設定(S22)を行ってテストの起動をかける。リトライしない場合にはエラー処理(29)に移る。エラー処理は、特に制限されないが、CPU1が所要の例外処理を実行して、故障のあることを外部に通知する処理とされる。ここれは、テスト結果の比較をCPU1が行うから、CPU1は故障していないことを前提としている。

【0044】

実際は、当然ながら、テスト回路A7だけでなく、テスト回路B8のテストも考慮してテスト動作が行われることになり、図示は省略するが、ステップS21,S23,S31の判定においてENB、STBも考慮するようにすればよい。すなわち、ステップS21でテスト状態レジスタ10のビットENAの後にENBの状態を判定し、ENAの場合と同様にENBの状態に従った制御を行い、ステップS23でテスト起動レジスタ9のビットSTAの後にSTBの状態を判定し、STAの場合と同様にSTBの状態に従った制御を行い、ステップS31でテスト起動レジスタ9のビットSTAの後にSTBの状態を判定し、STAの場合と同様にSTBの状態に従った制御をおこなえばよい。

【0045】

図5は本発明に係る半導体データ処理デバイスの別の実施の形態であるマイクロコンピュータのブロック図である。図1のマイコンとの相違点について説明する。比較器40はテスト回路A7の結果704と期待値を比較する専用の比較器である。期待値はCPU1がバス101を介して比較器40に書き込んでおく。テスト回路A7の実行が完了すると、テスト制御回路6は比較器40に比較許可信号605を出力し、比較器40は比較を行う。比較結果はバス101を経由してCPU1が読み出すことが可能である。また、比較器40からエラー信号4001をマイクロコンピュータ100の外部に出力することもできる。CPU1の故障によってテスト結果の判定ができない場合に、マイクロコンピュータ1の特定の外部端子からテスト結果を確認することが可能になる。

【0046】

比較器40は全てのテスト結果に対して比較動作を行うことを要しない。例えばCPU1のテスト結果だけを比較対象にしてもよい。CPU1のテストを他のテストを区別できるようにテスト制御回路6によりテスト回路A7を用いてテストを行い、CPU1に対するテスト結果に対してだけ信号605で比較回路40の動作を指示すればよい。

【0047】

図6は本発明に係る自己診断機能を有するマイクロコンピュータを使用した制御装置を示す。自動車42において、エンジン43を電子制御する制御装置44内に本発明を適用したマイクロコンピュータ100が搭載されている。

【0048】

上述のように、本発明によれば、パワーオンリセット後にCPUのプログラム処理によってメモリとCPUと論理回路のBISTを実行し、CPUが結果を判定することが可能であるとともに、テストを1回限りではなく必要に応じて何回でも実行できる。特に図5の場合は、テスト結果の判定をCPUとは別の専用比較器で比較できる。これらにより、テスト実行の自由度と信頼性を向上させることが可能になる。

【0049】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0050】

論理回路は上記説明に限定されず、その他の周辺回路やアクセラレータなどであってもよい。本発明はエンジンの制御装置に適用される場合に限定されず、自動車のシャーシ系の制御装置、自動車以外の機器制御にも広く適用することができる。

【図面の簡単な説明】

【0051】

【図1】図1は本発明に係る半導体データ処理デバイスの一実施の形態であるマイクロコンピュータのブロック図である。

【図2】図2は図1におけるテスト起動レジスタの一例を示す説明図である。

【図3】図3は図1におけるテスト状態レジスタを示す説明図である。

【図4】図4は図1におけるCPUとテスト回路A7の処理フローを例示するフローチャートである。

【図5】図5は本発明に係る半導体データ処理デバイスの別の実施の形態であるマイクロコンピュータのブロック図である。

【図6】図6は本発明に係る半導体データ処理デバイスを使用した自動車用の制御装置を示す説明図である。

【図7】図7はテスト回路A7、テスト回路B8に対するテスト対象回路部分をテスト起動レジスタ9によって指定可能にする場合のレジスタ構成を例示する説明図である。

【符号の説明】

【0052】

1…CPU

2…論理回路

3…RAM

4…RAMインタフェースセレクタ

5…リセット制御回路

6…テスト制御回路

7…テスト回路A(CPUと論理回路用)

8…テスト回路B(RAM用)

9…テスト起動レジスタ

10…テスト状態レジスタ

11…テスト汎用レジスタ

40…比較器

100…マイクロコンピュータ

【技術分野】

【0001】

本発明は、自己診断機能を備えた半導体データ処理デバイスに係り、例えば自動車の制御システムに適用して有効な技術に関する。

【背景技術】

【0002】

半導体データ処理デバイスたとえばマイクロコンピュータは、家電製品、AV機器、携帯電話、自動車、産業機械等の機器に組み込まれ、メモリに記憶されているプログラムにしたがって処理を行うことで、それぞれの機器の制御を行う半導体集積回路である。

【0003】

自動車では、制御装置の故障が事故につながる可能性があるため、マイクロコンピュータを含む部品に高い信頼性が求められるとともに、故障が発生した場合にはこれを検出して自動車が危険な状態にならないように安全機能を働かせるように設計されている。マイクロコンピュータはセンサやアクチュエータの診断を行ってこれらの故障を検出するだけでなく、マイクロコンピュータ自身の故障も検出する必要がある。

【0004】

マイクロコンピュータの故障検出には様々な方法があるが、マイクロコンピュータの内部でテストパターンを発生させてメモリや論理回路をテストするBIST(Built In Self Test)という手法が用いられるようになってきた。CPUのプログラム処理による方法に比べて短時間でテストを実行することが可能である。

【0005】

特許文献1には、メモリとCPUと論理回路を含むマイクロコンピュータにおいて、メモリとCPUと論理回路のBISTを行う方法が示されている。同文献においては、CPU及び当該CPUが制御する周辺回路などの論理回路にテスト回路がテストパターンを与えて動作させ、動作結果をテスト回路が圧縮し、圧縮結果をCPUが比較するテスト動作と、テスト回路がRAMにテストパターンを与えて動作させ、動作結果をテスト回路が圧縮し、圧縮結果をCPUが比較するテスト動作とを行う、自己診断機能を備える。この自己診断機能を用いるために、パワーオンリセット後にCPUが操作するテスト起動レジスタを備える。テスト起動レジスタにスタートビットをセットすることにより、テスト制御回路はテスト回路を動作させてテストを実行させる。テスト回路によるテスト動作が終了すると、テスト制御回路はCPU等を再度初期化し、そのとき、テスト起動レジスタは初期化対象とはされず、そこにセット状態のテストスタートビットが残されていれば、CPUはテスト回路にテスト動作の結果があることを認識し、これを期待値と比較してテスト結果の正否を判別する。

【0006】

【特許文献1】特開2001−27958号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

上記特許文献1に記載の技術は、パワーオンリセット後にCPUのプログラム処理によってメモリ、CPU、及び論理回路のBISTを実行し、結果をCPUで判定することが可能である。しかしながら、テスト結果が不一致であった場合にテストをリトライしたり、複数のテストを1つずつCPUが結果を確認しながら実行すること、には対応できない。また、テストの結果の判定をCPUのプログラム処理で行うため、CPUがテスト結果の判定のための演算処理機能の一部に故障を有している場合を想定したときには正しく判定が行われていない可能性もある。

【0008】

本発明の目的は、システムに実装された状態で、パワーオンリセット後に内部回路のセルフテストを実行することができ、そのテストが1回限りではなく必要に応じて何回でも実行できるなどの、テストの自由度が高い半導体データ処理デバイスを提供することにある。

【0009】

本発明の別の目的は、上述したテストの自由度が高く、その上、CPUによるテスト結果の判定機能に故障が発生した場合にもテスト結果の判定を行うことができる半導体データ処理デバイスを提供することにある。

【0010】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0012】

すなわち、CPUと内部回路を備えた半導体データ処理デバイスはセルフテスト機能を実現するために、前記CPU及び内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路と、テスト回路に起動をかけるテスト制御回路とともに、テスト起動レジスタ、テスト状態レジスタ、およびテスト汎用レジスタを備える。パワーオンリセット解除後のCPUのプログラム制御によってテスト起動レジスタにスタートビットがセットされることにより、テスト制御回路は、前記テスト回路によるCPUなどのテスト動作を起動してテスト結果を内部に蓄積し、前記テスト回路によるテスト動作の終了に応答して前記CPUと前記内部回路をリセットする。この後、CPUは、リセット解除後のプログラム実行においてテスト状態レジスタの値によりテストが行われたことを確認すると、前記テスト回路よりテスト結果を読み出して判定を行い、テスト汎用レジスタの設定に従って、続けてテストを行うかどうかを判定し、前記テスト起動レジスタに書き込むことによってテストを続けることが可能とされる。

【0013】

上記より、パワーオンリセット後のCPUのプログラム処理によってセルフテストを開始することができ、テスト動作の終了によるリセット解除後には、先にテストが行われたか否か、どの回路部分のテストが行われたか否かをテスト状態レジスタで判別でき、それによってテスト結果の判定を行ったり、また、テスト汎用レジスタの設定に従ってリトライを行ったり、リトライを繰り返したりする動作を、その設定に従って自由に行うことができる。

【0014】

テスト結果の判定はCPUが行ってもよいし、また、それ専用の比較器を配置してもよい。

【発明の効果】

【0015】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

【0016】

すなわち、システムに実装された状態で、パワーオンリセット後に内部回路のセルフテストを実行することができ、そのテストが1回限りではなく必要に応じて何回でも実行できるなどの自由度が高いセルフテストが可能である。

【0017】

また、テスト結果の判定に専用化された比較器をそなえることにより、CPUによるテスト結果の判定機能に故障が発生した場合にもテスト結果の判定を行うことができる。

【発明を実施するための最良の形態】

【0018】

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0019】

〔1〕本発明に係る半導体データ処理デバイス(100)は、命令をフェッチして実行するCPU(1)と、前記CPUの制御に基づいて動作する内部回路(2,3)とを含み、更に、前記CPUと内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路(7,8)と、前記テスト回路に起動をかけるテスト制御回路(6)と、前記CPUが前記テスト回路に起動をかけるためのテスト起動レジスタ(9)と、前記テスト回路によるテストが完了したことを示すフラグを含むテスト状態レジスタ(10)と、前記CPUが読み出しまたは書き込み可能なテスト汎用レジスタ(11)と、前記CPU、前記内部回路、前記テスト回路、前記テスト制御回路、前記テスト起動レジスタ、及び前記テスト状態レジスタをリセットするリセット制御回路(5)と、を含む。前記テスト制御回路は、前記CPUの前記テスト起動レジスタへの書き込みによって前記テスト回路によるテスト動作を起動し、前記テスト回路によるテスト動作の終了に応答して前記CPUと前記内部回路をリセットする。前記CPUは、リセット解除後のプログラム実行において前記テスト状態レジスタの値によりテストが行われたことを確認して前記テスト回路より結果を読み出して判定を行い、前記テスト汎用レジスタの設定状態に基づいて続けてテストを行うかどうかを判定し、前記テスト起動レジスタを操作することによってテストを続けることが可能である。

【0020】

〔2〕項1の半導体データ処理デバイスにおいて、前記内部回路は、前記CPUによって制御される論理回路(2)と、前記CPUによってアクセス可能にされるメモリ(3)である。前記テスト回路は、前記CPU及び論理回路をテスト対象とする第1のテスト回路(7)と、前記メモリをテスト対象とする第2のテスト回路(8)である。前記テスト起動レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々のスタートフラグビット(STA,STB)を有する。前記テスト状態レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々の状態フラグビット(ENA,ENB)を有する。

【0021】

〔3〕項1の半導体データ処理デバイスにおいて、前記テスト汎用レジスタは、テスト動作のリトライ上限回数データとテスト動作の現在のリトライ回数データを保持するレジスタである。

【0022】

〔4〕本発明の別の観点による半導体データ処理デバイスは、項1の半導体データ処理デバイスの構成に加えて、前記CPUが前記テスト回路のテスト結果の期待値を設定し、前記テスト回路がテストを終了したとき、前記CPUが設定したテスト結果の期待値とテスト回路の出力を比較して結果を出力する比較器(40)を有する。

【0023】

〔5〕項4の半導体データ処理デバイスにおいて、前記比較器による比較結果を前記半導体データ処理デバイスの外部に出力する出力端子を有する。

【0024】

〔6〕項4の半導体データ処理デバイスにおいて、前記内部回路は、前記CPUによって制御される論理回路と、前記CPUによってアクセス可能にされるメモリである。前記テスト回路は、前記CPU及び論理回路をテスト対象とする第1のテスト回路と、前記メモリをテスト対象とする第2のテスト回路である。前記テスト起動レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々のスタートフラグビットを有する。前記テスト状態レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々の状態フラグビットを有する。

【0025】

〔7〕項4の半導体データ処理デバイスにおいて、前記テスト汎用レジスタは、テスト動作のリトライ上限回数データとテスト動作の現在のリトライ回数データを保持するレジスタである。

【0026】

2.実施の形態の詳細

実施の形態について更に詳述する。

【0027】

図1は本発明に係る半導体データ処理デバイスの一実施の形態であるマイクロコンピュータのブロック図である。マイクロコンピュータ100は、中央処理装置(CPU)1、論理回路2、RAM3及びリセット制御回路5と共に、BIST(Built In Self Test)回路として、テスト制御回路6、テスト回路A7、テスト回路B8、テスト起動レジスタ9、テスト状態レジスタ10、及びテスト汎用レジスタ11を有する。

【0028】

CPU1は命令を実行して演算やデータ転送などの処理を行う回路である。論理回路2はCPU1の設定に従って特定の機能を実行する回路モジュールであり、例えばダイレクトメモリアクセスコントローラ、A/Dコンバータ、タイマ、通信モジュール、外部入出力回路などである。RAM3はCPU1が実行する命令および処理するデータを記憶する記憶回路である。CPU1、論理回路2、RAM3、テスト制御回路6,7はバス101に接続されている。リセット制御回路5はCPU1及び論理回路2を初期化するためのリセット信号501と、テスト起動レジスタ9及びテスト状態レジスタ10を初期化するためのリセット信号503と、テスト制御回路6、テスト回路A7及びテスト回路B8を初期化するためのリセット信号502を生成する。外部からのリセット要求信号RESによる初期化が指定されたときリセット制御回路5はリセット信号501、502及び503を活性化し、テスト制御回路6からのリセット要求信号601により初期化が指定されたときリセット制御回路5はリセット信号503を活性化する。

【0029】

テスト制御回路6はCPU1、論理回路2、RAM3のテストの起動などの制御を行う。テスト回路A7はCPU1と論理回路2をテストする回路である。テスト制御回路6からのテスト起動信号602により、インタフェース配線701を用いてCPU1にテストパターンを注入し、インタフェース信号配線702を用いて論理回路2にテストパターンを注入する。テストパターンの注入が完了するとCPU1と論理回路2にクロックを与えて動作させ、動作結果をインタフェース配線701、702から取り込み、圧縮して保持する。この動作をテストの数だけ繰り返す。テストが終了するとテスト回路A7はテスト制御回路6に完了信号703を通知する。テスト回路B8はRAM3をテストする回路である。テスト制御回路6からの起動信号603により、インタフェース配線801を用いてRAM3にテストパターンを注入してテストを行い、その結果をインタフェース配線801から取り込む。セレクタ4はRAM3のインタフェース配線401を、通常動作時にはバス101と接続し、テスト時にはテスト回路B8とのインタフェース配線801と接続する。テストが終了するとテスト回路B8はテスト制御回路6に完了信号802を通知する。

【0030】

テスト制御回路6は、特に制限されないが、ステートマシン又はプログラム制御回路で構成される。テスト回路A7及びテスト回路B8は、テストパターンを記憶し若しくは発生するテストパターン回路と、テスト動作結果の圧縮回路を有し、テスト制御回路6の制御に従って動作される。

【0031】

テスト起動レジスタ9はCPU1がバス101を介して書き込み可能なレジスタで、起動を意味する値が設定されるとテスト制御回路6に起動信号901を出力する。パワーオンリセットを行うと、リセット信号503によりテスト起動レジスタは起動しないを意味する値に初期設定される。また、リセット信号502によりテスト制御回路6、テスト回路A7、テスト回路B8が初期化される。CPU1がテスト起動レジスタ9に起動を意味する値を設定するとテストが開始され、完了するとテスト制御回路6はリセット制御回路5にリセット要求601を出力して、リセット信号501により再びCPU1と論理回路2を初期化する。テスト状態レジスタ10はテストが完了したか否かを示すレジスタであり、その値は最初テスト未完を意味する値に初期化され、テストが完了するとテスト制御回路6が信号604によりテスト完了を意味する値に設定変更する。

【0032】

テスト汎用レジスタ11はCPU1が読み出しおよび書き込み可能なレジスタで、リセット制御回路5による初期化は行われない。テスト結果が不一致だった場合にリトライするかどうかを決定したり、複数のテストを実行する場合にテストの総数や完了したテストの番号を記憶するために使用する。CPU1や論理回路2の内部レジスタ(図示せず)はリセット信号501によってテスト終了後に初期化され、RAM3はテストによってデータが書き換えられてしまうため上記目的に使用することはできない。テストを実行しても値を保持することのできるテスト汎用レジスタ11によって上記目的を達成する。

【0033】

リセット要求が解除されるとCPU1はプログラムの実行を開始するが、テスト状態レジスタがテスト完了を意味する値に設定されていることを確認したときは、テストの結果判定を行う。テストの結果判定はCPU1がテスト回路A7から結果データを読み出し、期待値と比較することによって行う。RAMのテスト結果はCPU1がテスト回路B8から合否判定データを読み出すことによって行う。

【0034】

図2は図1におけるテスト起動レジスタ(CR:Control Register)9の一例を示す。テスト起動レジスタ9はCPU1がバス101を介して読み出しおよび書き込み可能な8ビットのレジスタである。ビット7から2は予約でありレジスタの実体は無くても良い。読み出す場合には不定値あるいは“0”などの固定値を読み出すようにする。ビット1はテスト回路B8の起動許可ビット(STB)である。初期値は“0”であり起動しないを意味する。“1”はテスト回路B8によるテストの起動を意味する。起動許可ビットSTBが“1”に設定されると、信号901によって、テスト回路B8にテスト動作が指示され、これによってテスト回路B8がRAM3のテストを開始する。ビット0はテスト回路A7の起動許可ビット(STA)である。初期値は“0”であり起動しないを意味し、“1”はテスト回路A7によるテスト動作の起動を意味する。起動許可ビットSTAが“1”に設定されると、信号901によって、テスト回路A7にテスト動作が指示され、これによってテスト回路A7がCPU1と論理回路2のテストを開始する。信号901はテスト起動レジスタ9の起動許可ビットのビット数に応ずる数複数ビットを有する信号である。

【0035】

図3は図1におけるテスト状態レジスタ(SR:Status Register)10を示す。テスト状態レジスタ10はCPU1がバス101を介して読み出し可能な8ビットのレジスタである。ビット7から2は予約でありレジスタの実体は無くても良い。読み出す場合には不定値あるいは“0”などの固定値を読み出すようにする。ビット1はテスト回路B8の終了フラグ(ENB)である。初期値は“0”であり、テスト回路B8によるテスト動作が終了していないを意味する。“1”はテスト回路B8によるテストの終了を意味し、テスト回路B8のテスト実行が完了するとテスト制御回路6が終了フラグENBを“1”に設定する。ビット0はテスト回路A7の終了フラグ(ENA)である。初期値は“0”であり、テスト回路A7によるテスト動作が終了していないを意味する。“1”はテスト回路A7によるテストの完了を意味し、テスト回路A7のテスト実行が完了するとテスト制御回路6がENAを“1”に設定する。

【0036】

例えば,テスト回路A7及びテスト回路B8のテスト実行が完了すると、STAとENAおよびSTBとENBはそれぞれ値が“1”“1”に設定されることになる。テストを再実行させる場合には、CPU1がSTAとSTBを一旦“0”に戻した後、テスト制御回路6がENAとENBを“0”に設定し、その後に、CPU1がSTAまたはSTBに“1”を設定する手順を採用することができる。上記CPU1がSTAとSTBを一旦“0”に戻す処理は、テストが完了する毎にテスト制御回路6がSTA,STBを順次“0”にクリアする手順に代えてもよい。また、STAとSTBは同時に“1”に設定する必要性は無く、必要な方だけを“1”に設定してもよい。例えば、テスト回路A7の結果が不一致だった場合にCPU1と論理回路2のテストのみリトライする方法が考えられる。STAとSTBが同時に“1”に設定されたとき、テスト制御回路6は、テスト回路A7の動作を先に行ってから、テスト回路B8の動作を開始し、双方のつと実行が完了したときリセット要求601を出力する。

【0037】

特に制限されないが、図2及び図3の例は、テスト回路A7、テスト回路B8に対するテスト対象回路部分をテスト起動レジスタ9によって指定する構成にはなっていない。

【0038】

図7にはテスト回路A7、テスト回路B8に対するテスト対象回路部分(例えば第1回路ブロック、第2回路ブロック、及び第3回路ブロック)をテスト起動レジスタ9によって指定可能にする場合のレジスタ構成が例示される。テスト回路A7、テスト回路B8は夫々3ブロックに分けてテスト可能とする場合について説明する。

【0039】

テスト起動レジスタ(CR)9は、テスト回路A7の起動許可ビットとしてSTA0,STA1,STA2の3ビットを有し、テスト回路B8の起動許可ビットとしてSTB0,STB1,STB2の3ビットを有する。起動許可ビットSTA0,STA1,STA2はテスト回路A7の第1回路ブロック、第2回路ブロック、第3回路ブロックの起動許可/不許可を指示する。起動許可ビットSTB0,STB1,STB2はテスト回路B8の第1回路ブロック、第2回路ブロック、第3回路ブロックの起動許可/不許可を指示する。夫々のビットの論理値の意味は前記と同じである。この場合、前記信号901は6ビットになる。

【0040】

テスト状態レジスタ(SR)10は、テスト回路A7の終了フラグとしてENA0,ENA1,ENA2の3ビットを有し、テスト回路B8の終了フラグとしてENB0,ENB1,ENB2の3ビットを有する。終了フラグENA0,ENA1,ENA2はテスト回路A7の第1回路ブロック、第2回路ブロック、第3回路ブロックのテスト実行完了/未完を意味する。終了フラグENB0,ENB1,ENB2はテスト回路B8の第1回路ブロック、第2回路ブロック、第3回路ブロックのテスト実行完了/未完を意味する。夫々のビットの論理値の意味は前記と同じである。

【0041】

テスト汎用レジスタ(GR)11は、テスト回路A7の現リトライ回数データRTYAを保持するレジスタ(GR1)、テスト回路B8の現リトライ回数データRTYBを保持するレジスタ(GR2)、テスト回路A7のテスト実行に関するリトライ上限回数データLIMAを保持するレジスタGR3、及びテスト回路B8のテスト実行に関するリトライ上限回数データLIMBを保持するレジスタ(GR4)から構成される。

【0042】

図4は図1におけるCPUとテスト回路A7の処理フローを例示する。ここでは、例えばテスト起動レジスタ9として図2の構成、テスト状態レジスタ10として図3の構成を採用し、テスト回路A7のテストを実行する場合について説明する。

【0043】

まずパワーオンリセットによってCPU1とテスト回路A7は共にリセットされる(S20、S30)。リセットが解除されるとCPU1はプログラムの実行を開始し、テスト状態レジスタSRのENAをチェックする(S21)。ENAはパワーオンリセットにより“0”に初期化されているためテスト起動レジスタCRのSTAを設定する処理(S22)に進む。STAの判定処理(S23)によりテストを実行しない場合にはテスト終了となる。一方、テスト回路A7は起動リセット後、起動レジスタCRのSTAのチェック(S31)を行っており、“1”が設定されるまでチェック処理を続ける。STAに“1”が設定されるとテスト回路A7はテスト回路A7のためのテストAを実行する(S32)。テストAが完了するとCPU1および論理回路2のリセットを行う(S33)。またテストAの完了によりテスト制御回路6がSTAを“0”にクリアしているため、テスト回路A7は再びSTAのチェックを行う(S31)。CPU1はリセット(S20)が解除されると再びプログラムの実行を開始し、テスト状態レジスタSRのENAをチェックする(S21)。ENAが“1”に設定されているためテストAの結果確認処理(S24)を実行する。結果が一致していれば次のテストを実行するか否かの判定(S26)を行う。ここで図1におけるテスト汎用レジスタ11が用いられる。テスト汎用レジスタはテスト完了後にリセットされないため、テスト開始前の状態を保持している。テスト汎用レジスタ11は複数あり、例えば2本をテストの総数、実行完了したテスト数の記憶に割り当てることによって、複数回の実行を制御できる。次のテストがある場合にはSTAの設定等のテスト設定(S22)を行ってテストの起動をかける。次のテストが無い場合にはテスト終了となる。テストAの結果確認処理(S24)において結果が不一致だった場合にはリトライを行うか否かの判定(S27)を行う。ここでもテスト汎用レジスタ11が用いられる。例えば2本をリトライ回数の上限、リトライした回数の記憶に割り当てることによって、リトライの実行を制御できる。リトライを行う場合にはテスト設定(S22)を行ってテストの起動をかける。リトライしない場合にはエラー処理(29)に移る。エラー処理は、特に制限されないが、CPU1が所要の例外処理を実行して、故障のあることを外部に通知する処理とされる。ここれは、テスト結果の比較をCPU1が行うから、CPU1は故障していないことを前提としている。

【0044】

実際は、当然ながら、テスト回路A7だけでなく、テスト回路B8のテストも考慮してテスト動作が行われることになり、図示は省略するが、ステップS21,S23,S31の判定においてENB、STBも考慮するようにすればよい。すなわち、ステップS21でテスト状態レジスタ10のビットENAの後にENBの状態を判定し、ENAの場合と同様にENBの状態に従った制御を行い、ステップS23でテスト起動レジスタ9のビットSTAの後にSTBの状態を判定し、STAの場合と同様にSTBの状態に従った制御を行い、ステップS31でテスト起動レジスタ9のビットSTAの後にSTBの状態を判定し、STAの場合と同様にSTBの状態に従った制御をおこなえばよい。

【0045】

図5は本発明に係る半導体データ処理デバイスの別の実施の形態であるマイクロコンピュータのブロック図である。図1のマイコンとの相違点について説明する。比較器40はテスト回路A7の結果704と期待値を比較する専用の比較器である。期待値はCPU1がバス101を介して比較器40に書き込んでおく。テスト回路A7の実行が完了すると、テスト制御回路6は比較器40に比較許可信号605を出力し、比較器40は比較を行う。比較結果はバス101を経由してCPU1が読み出すことが可能である。また、比較器40からエラー信号4001をマイクロコンピュータ100の外部に出力することもできる。CPU1の故障によってテスト結果の判定ができない場合に、マイクロコンピュータ1の特定の外部端子からテスト結果を確認することが可能になる。

【0046】

比較器40は全てのテスト結果に対して比較動作を行うことを要しない。例えばCPU1のテスト結果だけを比較対象にしてもよい。CPU1のテストを他のテストを区別できるようにテスト制御回路6によりテスト回路A7を用いてテストを行い、CPU1に対するテスト結果に対してだけ信号605で比較回路40の動作を指示すればよい。

【0047】

図6は本発明に係る自己診断機能を有するマイクロコンピュータを使用した制御装置を示す。自動車42において、エンジン43を電子制御する制御装置44内に本発明を適用したマイクロコンピュータ100が搭載されている。

【0048】

上述のように、本発明によれば、パワーオンリセット後にCPUのプログラム処理によってメモリとCPUと論理回路のBISTを実行し、CPUが結果を判定することが可能であるとともに、テストを1回限りではなく必要に応じて何回でも実行できる。特に図5の場合は、テスト結果の判定をCPUとは別の専用比較器で比較できる。これらにより、テスト実行の自由度と信頼性を向上させることが可能になる。

【0049】

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

【0050】

論理回路は上記説明に限定されず、その他の周辺回路やアクセラレータなどであってもよい。本発明はエンジンの制御装置に適用される場合に限定されず、自動車のシャーシ系の制御装置、自動車以外の機器制御にも広く適用することができる。

【図面の簡単な説明】

【0051】

【図1】図1は本発明に係る半導体データ処理デバイスの一実施の形態であるマイクロコンピュータのブロック図である。

【図2】図2は図1におけるテスト起動レジスタの一例を示す説明図である。

【図3】図3は図1におけるテスト状態レジスタを示す説明図である。

【図4】図4は図1におけるCPUとテスト回路A7の処理フローを例示するフローチャートである。

【図5】図5は本発明に係る半導体データ処理デバイスの別の実施の形態であるマイクロコンピュータのブロック図である。

【図6】図6は本発明に係る半導体データ処理デバイスを使用した自動車用の制御装置を示す説明図である。

【図7】図7はテスト回路A7、テスト回路B8に対するテスト対象回路部分をテスト起動レジスタ9によって指定可能にする場合のレジスタ構成を例示する説明図である。

【符号の説明】

【0052】

1…CPU

2…論理回路

3…RAM

4…RAMインタフェースセレクタ

5…リセット制御回路

6…テスト制御回路

7…テスト回路A(CPUと論理回路用)

8…テスト回路B(RAM用)

9…テスト起動レジスタ

10…テスト状態レジスタ

11…テスト汎用レジスタ

40…比較器

100…マイクロコンピュータ

【特許請求の範囲】

【請求項1】

命令をフェッチして実行するCPUと、前記CPUの制御に基づいて動作する内部回路とを含む半導体データ処理デバイスであって、

前記CPUと内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路と、

前記テスト回路に起動をかけるテスト制御回路と、

前記CPUが前記テスト回路に起動をかけるためのテスト起動レジスタと、

前記テスト回路によるテストが完了したことを示すフラグを含むテスト状態レジスタと、

前記CPUが読み出しまたは書き込み可能なテスト汎用レジスタと、

前記CPU、前記内部回路、前記テスト回路、前記テスト制御回路、前記テスト起動レジスタ、及び前記テスト状態レジスタをリセットするリセット制御回路と、を含み、

前記テスト制御回路は、前記CPUの前記テスト起動レジスタへの書き込みによって前記テスト回路によるテスト動作を起動し、前記テスト回路によるテスト動作の終了に応答して前記CPUと前記内部回路をリセットし、

前記CPUは、リセット解除後のプログラム実行において前記テスト状態レジスタの値によりテストが行われたことを確認して前記テスト回路より結果を読み出して判定を行い、前記テスト汎用レジスタの設定状態に基づいて続けてテストを行うかどうかを判定し、前記テスト起動レジスタを操作することによってテストを続けることが可能である、半導体データ処理デバイス。

【請求項2】

前記内部回路は、前記CPUによって制御される論理回路と、前記CPUによってアクセス可能にされるメモリであり、

前記テスト回路は、前記CPU及び論理回路をテスト対象とする第1のテスト回路と、前記メモリをテスト対象とする第2のテスト回路であり、

前記テスト起動レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々のスタートフラグビットを有し、

前記テスト状態レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々の状態フラグビットを有する、請求項1記載の半導体データ処理デバイス。

【請求項3】

前記テスト汎用レジスタは、テスト動作のリトライ上限回数データとテスト動作の現在のリトライ回数データを保持するレジスタである、請求項1記載の半導体データ処理デバイス。

【請求項4】

命令をフェッチして実行するCPUと、前記CPUの制御を受けて動作する内部回路とを含む半導体データ処理デバイスであって、

前記CPUと前記内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路と、

前記テスト回路に起動をかけるテスト制御回路と、

前記CPUが前記テスト回路に起動をかけるためのテスト起動レジスタと、

前記テスト回路によるテストが完了したことを示すフラグを含むテスト状態レジスタと、

前記CPUが読み出しまたは書き込み可能なテスト汎用レジスタと、

前記CPUが前記テスト回路のテスト結果の期待値を設定し、前記テスト回路がテストを終了したとき、前記CPUが設定したテスト結果の期待値とテスト回路の出力を比較して結果を出力する比較器と

前記CPU、前記内部回路、前記テスト回路、前記テスト制御回路、前記テスト起動レジスタ、前記テスト状態レジスタ、前記比較器をリセットするリセット制御回路と、を含み、

前記テスト制御回路は、前記CPUの前記テスト起動レジスタへの書き込みによって前記テスト回路によるテスト動作を起動し、前記テスト回路によるテスト動作の終了に応答して前記CPUと前記内部回路をリセットし、

前記CPUは、リセット解除後のプログラム実行において前記テスト状態レジスタの値によりテストが行われたことを確認して前記比較器より結果を読み出して判定を行い、前記テスト汎用レジスタの設定状態に基づいて続けてテストを行うかどうかを判定し、前記テスト起動レジスタを操作することによってテストを続けることが可能である、半導体データ処理デバイス。

【請求項5】

前記比較器による比較結果を前記半導体データ処理デバイスの外部に出力する出力端子を有する、請求項4記載の半導体データ処理デバイス。

【請求項6】

前記内部回路は、前記CPUによって制御される論理回路と、前記CPUによってアクセス可能にされるメモリであり、

前記テスト回路は、前記CPU及び論理回路をテスト対象とする第1のテスト回路と、前記メモリをテスト対象とする第2のテスト回路であり、

前記テスト起動レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々のスタートフラグビットを有し、

前記テスト状態レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々の状態フラグビットを有する、請求項4記載の半導体データ処理デバイス。

【請求項7】

前記テスト汎用レジスタは、テスト動作のリトライ上限回数データとテスト動作の現在のリトライ回数データを保持するレジスタである、請求項4記載の半導体データ処理デバイス。

【請求項1】

命令をフェッチして実行するCPUと、前記CPUの制御に基づいて動作する内部回路とを含む半導体データ処理デバイスであって、

前記CPUと内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路と、

前記テスト回路に起動をかけるテスト制御回路と、

前記CPUが前記テスト回路に起動をかけるためのテスト起動レジスタと、

前記テスト回路によるテストが完了したことを示すフラグを含むテスト状態レジスタと、

前記CPUが読み出しまたは書き込み可能なテスト汎用レジスタと、

前記CPU、前記内部回路、前記テスト回路、前記テスト制御回路、前記テスト起動レジスタ、及び前記テスト状態レジスタをリセットするリセット制御回路と、を含み、

前記テスト制御回路は、前記CPUの前記テスト起動レジスタへの書き込みによって前記テスト回路によるテスト動作を起動し、前記テスト回路によるテスト動作の終了に応答して前記CPUと前記内部回路をリセットし、

前記CPUは、リセット解除後のプログラム実行において前記テスト状態レジスタの値によりテストが行われたことを確認して前記テスト回路より結果を読み出して判定を行い、前記テスト汎用レジスタの設定状態に基づいて続けてテストを行うかどうかを判定し、前記テスト起動レジスタを操作することによってテストを続けることが可能である、半導体データ処理デバイス。

【請求項2】

前記内部回路は、前記CPUによって制御される論理回路と、前記CPUによってアクセス可能にされるメモリであり、

前記テスト回路は、前記CPU及び論理回路をテスト対象とする第1のテスト回路と、前記メモリをテスト対象とする第2のテスト回路であり、

前記テスト起動レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々のスタートフラグビットを有し、

前記テスト状態レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々の状態フラグビットを有する、請求項1記載の半導体データ処理デバイス。

【請求項3】

前記テスト汎用レジスタは、テスト動作のリトライ上限回数データとテスト動作の現在のリトライ回数データを保持するレジスタである、請求項1記載の半導体データ処理デバイス。

【請求項4】

命令をフェッチして実行するCPUと、前記CPUの制御を受けて動作する内部回路とを含む半導体データ処理デバイスであって、

前記CPUと前記内部回路にテストパターンを発生してテストを行って結果を保持するテスト回路と、

前記テスト回路に起動をかけるテスト制御回路と、

前記CPUが前記テスト回路に起動をかけるためのテスト起動レジスタと、

前記テスト回路によるテストが完了したことを示すフラグを含むテスト状態レジスタと、

前記CPUが読み出しまたは書き込み可能なテスト汎用レジスタと、

前記CPUが前記テスト回路のテスト結果の期待値を設定し、前記テスト回路がテストを終了したとき、前記CPUが設定したテスト結果の期待値とテスト回路の出力を比較して結果を出力する比較器と

前記CPU、前記内部回路、前記テスト回路、前記テスト制御回路、前記テスト起動レジスタ、前記テスト状態レジスタ、前記比較器をリセットするリセット制御回路と、を含み、

前記テスト制御回路は、前記CPUの前記テスト起動レジスタへの書き込みによって前記テスト回路によるテスト動作を起動し、前記テスト回路によるテスト動作の終了に応答して前記CPUと前記内部回路をリセットし、

前記CPUは、リセット解除後のプログラム実行において前記テスト状態レジスタの値によりテストが行われたことを確認して前記比較器より結果を読み出して判定を行い、前記テスト汎用レジスタの設定状態に基づいて続けてテストを行うかどうかを判定し、前記テスト起動レジスタを操作することによってテストを続けることが可能である、半導体データ処理デバイス。

【請求項5】

前記比較器による比較結果を前記半導体データ処理デバイスの外部に出力する出力端子を有する、請求項4記載の半導体データ処理デバイス。

【請求項6】

前記内部回路は、前記CPUによって制御される論理回路と、前記CPUによってアクセス可能にされるメモリであり、

前記テスト回路は、前記CPU及び論理回路をテスト対象とする第1のテスト回路と、前記メモリをテスト対象とする第2のテスト回路であり、

前記テスト起動レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々のスタートフラグビットを有し、

前記テスト状態レジスタは前記第1のテスト回路用と前記第2のテスト回路用に別々の状態フラグビットを有する、請求項4記載の半導体データ処理デバイス。

【請求項7】

前記テスト汎用レジスタは、テスト動作のリトライ上限回数データとテスト動作の現在のリトライ回数データを保持するレジスタである、請求項4記載の半導体データ処理デバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−140219(P2010−140219A)

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願番号】特願2008−315287(P2008−315287)

【出願日】平成20年12月11日(2008.12.11)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年6月24日(2010.6.24)

【国際特許分類】

【出願日】平成20年12月11日(2008.12.11)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]