半導体パッケージ、半導体パッケージの製造方法及び半導体装置

【課題】反りを低減することができる半導体パッケージ、半導体パッケージの製造方法及び半導体装置を提供する。

【解決手段】半導体パッケージ1は、半導体チップ2と、半導体チップ2を覆うように形成された第1絶縁層11と、第1絶縁層11上に積層され、半導体チップ2と電気的に接続された第2〜第5配線層20,30,40,50と第2〜第4絶縁層21,31,41とが交互に積層されてなる配線構造と、を有する。第1絶縁層11の面11Aとは反対側の最外層の第4絶縁層41には、その第4絶縁層41を厚さ方向に貫通する溝部41Xが形成されている。

【解決手段】半導体パッケージ1は、半導体チップ2と、半導体チップ2を覆うように形成された第1絶縁層11と、第1絶縁層11上に積層され、半導体チップ2と電気的に接続された第2〜第5配線層20,30,40,50と第2〜第4絶縁層21,31,41とが交互に積層されてなる配線構造と、を有する。第1絶縁層11の面11Aとは反対側の最外層の第4絶縁層41には、その第4絶縁層41を厚さ方向に貫通する溝部41Xが形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体パッケージ、半導体パッケージの製造方法及び半導体装置に関するものである。

【背景技術】

【0002】

従来、半導体チップと、その半導体チップを覆う樹脂層とを有する半導体パッケージが知られている。

このような半導体パッケージの一例としては、半導体チップの能動面(回路形成面)及び側面が絶縁層により覆われており、その絶縁層上に、半導体チップと電気的に接続された配線構造が積層されてなる構造が提案されている(例えば、特許文献1参照)。

【0003】

このような半導体パッケージの製造方法としては、以下のような方法が知られている。

例えば支持基板を準備し、その支持基板上に、半導体チップの能動面と反対側の面が支持基板の表面に接するように半導体チップを搭載する。続いて、搭載した半導体チップを絶縁層により封止し、絶縁層上に配線層と層間絶縁層とを積層して配線構造を形成する。そして、支持基板を除去することによって、半導体パッケージを製造する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−300854号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来の半導体パッケージの製造工程では、支持基板上に半導体チップを固定し、絶縁層及び配線構造を形成した状態では、支持基板の剛性が高いため、半導体パッケージには反りがほとんど発生しない。しかし、支持基板を除去すると、その除去した部分の応力が解放されるため、その応力解放に伴って半導体パッケージに反りが生じるという問題があった。

【課題を解決するための手段】

【0006】

本発明の一観点によれば、半導体チップと、前記半導体チップを覆うように形成された第1絶縁層と、前記第1絶縁層上に積層され、前記半導体チップと電気的に接続された配線層と該配線層上に積層された層間絶縁層とが交互に積層されてなる配線構造と、を有し、前記半導体チップの搭載面とは反対側の最外層の前記層間絶縁層には、該層間絶縁層を厚さ方向に貫通する溝部が形成されている。

【発明の効果】

【0007】

本発明の一観点によれば、反りを低減することができるという効果を奏する。

【図面の簡単な説明】

【0008】

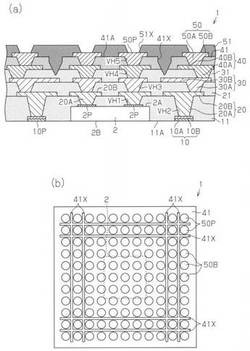

【図1】(a)は、一実施形態の半導体パッケージを示す概略断面図、(b)は、一実施形態の半導体パッケージを示す概略平面図。なお、(b)では、埋込樹脂層の図示を省略している。

【図2】一実施形態の半導体装置を示す概略断面図。

【図3】(a)〜(e)は、一実施形態の半導体パッケージの製造方法を示す概略断面図。

【図4】(a)〜(c)は、一実施形態の半導体パッケージの製造方法を示す概略断面図。

【図5】(a)、(b)は、一実施形態の半導体パッケージの製造方法を示す概略断面図。

【図6】(a)、(b)は、一実施形態の半導体パッケージの製造方法を示す概略断面図。

【図7】(a)、(b)は、一実施形態の半導体装置の製造方法を示す概略断面図。

【図8】変形例の半導体パッケージを示す概略断面図。

【図9】変形例の半導体パッケージを示す概略断面図。

【図10】(a)、(b)は、変形例の半導体パッケージを示す概略断面図。

【図11】(a)、(b)は、変形例の半導体パッケージを示す概略平面図。なお、(a)、(b)では、埋込樹脂層の図示を省略している。

【図12】変形例の半導体パッケージを示す概略断面図。

【図13】比較例1の半導体パッケージを示す概略断面図。

【図14】比較例2の半導体パッケージを示す概略断面図。

【図15】反りのシミュレーション結果を示すテーブル。

【発明を実施するための形態】

【0009】

以下、添付図面を参照して各実施形態を説明する。なお、添付図面は、特徴を分かりやすくするために便宜上特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、断面図では、各部材の断面構造を分かりやすくするために、一部の樹脂層のハッチングを省略している。

【0010】

以下、一実施形態を図1〜図7に従って説明する。

(半導体パッケージの構造)

図1(a)に示すように、半導体パッケージ1は、半導体チップ2を有している。この半導体チップ2としては、例えばCPU(Central Processing Unit)チップやGPU(Graphics Processing Unit)チップなどのロジックチップを用いることができる。また、半導体チップ2としては、例えばDRAM(Dynamic Random Access Memory)チップ、SRAM(Static Random Access Memory)チップやフラッシュメモリチップなどのメモリチップを用いることができる。

【0011】

このような半導体チップ2は、例えば半導体基板からなる。半導体基板の材料としては、例えばシリコン(Si)等を用いることができる。また、半導体チップ2は、第1主面2A(図1(a)では、上面)側に半導体集積回路(図示略)が形成されている。この半導体集積回路は、図示は省略するが、上記半導体基板に形成された拡散層、半導体基板上に積層された絶縁層、及び積層された絶縁層に設けられたビア及び配線等を有している。そして、この半導体集積回路上には、該半導体集積回路と電気的に接続された電極パッド2Pが設けられている。なお、この電極パッド2Pの材料としては、例えばアルミニウム(Al)、銅(Cu)とAlの合金や、CuとAlとSiの合金を用いることができる。

【0012】

上記半導体チップ2の大きさは、例えば平面視で9mm×9mm程度とすることができる。半導体チップ2の厚さは、例えば50〜200μm程度とすることができる。また、本実施形態では、半導体チップ2がシリコンからなり、その半導体チップ2の熱膨張係数が約3.4ppm/℃になる。なお、以下の説明では、半導体チップ2の第1主面2Aを回路形成面2Aと称する場合もある。

【0013】

また、半導体パッケージ1は、第1配線層10と、第1絶縁層11と、第2配線層20と、第2絶縁層21と、第3配線層30と、第3絶縁層31と、第4配線層40と、第4絶縁層41と、第5配線層50とが順次積層された配線構造を有している。このように、本実施形態の半導体パッケージ1は、一般的なビルドアップ法を用いて作製される配線基板(支持基材としてのコア基板の両面又は片面に所要数のビルドアップ層を順次形成して積層したもの)とは異なり、支持基材を含まない「コアレス構造」の形態を有している。

【0014】

なお、第2〜第5配線層20,30,40,50の材料としては、例えば銅や銅合金を用いることができる。

半導体パッケージ1において、第1配線層10は、最外層(図1では最下層)に形成されている。この第1配線層10は、第1導電層10Aと第2導電層10Bとを有している。第1導電層10Aとしては、例えば金(Au)膜、ニッケル(Ni)膜を、Au膜が半導体パッケージ1の外部に露出するように、この順番で順次積層した導電層を用いることができる。また、第2導電層10Bとしては、例えばCu層等を含む導電層を用いることができる。なお、上記Au膜の厚さは例えば0.1〜1μm程度とすることができ、上記Ni膜の厚さは例えば1〜10μm程度とすることができる。また、第2導電層10B(Cu層)の厚さは例えば10〜40μm程度とすることができる。

【0015】

第1配線層10の第1主面(図1(a)では上面)及び側面は第1絶縁層11によって覆われている。一方、第1配線層10の第2主面(図1(a)では下面)は第1絶縁層11から露出しており、他の半導体パッケージ4(図2参照)等と電気的に接続される接続パッド10Pとして機能する。第1配線層10の平面形状は例えば円形であり、その直径は例えば40〜120μm程度とすることができる。この第1配線層10は、半導体チップ2の外周に沿った環状の形態、いわゆるペリフェラル状に形成されている。

【0016】

第1絶縁層11は、半導体チップ2の第1主面2A及び側面を覆い、半導体チップ2の第2主面2B(図中の下面)を露出するように形成されている。また、第1絶縁層11は、第1配線層10の第1主面(図1(a)では上面)及び側面を覆い、第1配線層10の第2主面(図1(a)では下面)を露出するように形成されている。すなわち、第1絶縁層11の面11A(図1(a)では下面)、半導体チップ2の第2主面2B及び第1配線層10の第2主面は略面一になるように形成されている。換言すると、半導体チップ2と第1配線層10(接続パッド10P)とは同一平面上に形成されている。第1絶縁層11の材料としては、熱硬化性を有するエポキシ系の絶縁性樹脂を用いることができる。このエポキシ系樹脂の熱膨張係数は、ガラス転移温度Tg(例えば150℃)よりも低い場合には46ppm/℃程度、ガラス転移温度Tg以上の場合に120ppm/℃程度となる。なお、上記絶縁性樹脂としては、熱硬化性を有する樹脂に限定されず、感光性を有する絶縁性樹脂を用いることができる。第1絶縁層11の厚さは、例えば100〜180μm程度とすることができる。なお、以下の説明では、第1絶縁層11の面11Aをチップ搭載面11Aと称する場合もある。

【0017】

第1絶縁層11には、該第1絶縁層11を貫通して半導体チップ2の電極パッド2Pの上面を露出するビアホールVH1が形成されている。また、第1絶縁層11には、該第1絶縁層11を貫通して第1配線層10の第1主面を露出するビアホールVH2が形成されている。

【0018】

第2配線層20は、第1絶縁層11上に形成されている。第2配線層20は、ビアホールVH1,VH2内に充填されたビア配線20Aと、第1絶縁層上に形成された配線パターン20Bとを有している。ビア配線20Aは、ビアホールVH1の底部に露出した電極パッド2P又はビアホールVH2の底部に露出した第1配線層10と電気的に接続されるとともに、配線パターン20Bと電気的に接続されている。なお、ビアホールVH1,VH2及びビア配線20Aは、図1(a)において下側(接続パッド10P側)から上側(第5配線層50側)に向かうにつれて径が大きくなるテーパ状に形成されている。また、これらビアホールVH1,VH2及びビア配線20Aの平面形状は例えば円形である。ビアホールVH1及びそのビアホールVH1に形成されたビア配線20Aの直径は例えば20〜50μm程度とすることができ、ビアホールVH2及びそのビアホールVH2に形成されたビア配線20Aの直径は例えば75〜150μm程度とすることができる。第2配線層20の配線パターン20Bの厚さは、例えば15〜35μm程度とすることができる。

【0019】

第2絶縁層21(層間絶縁層)は、第1絶縁層11上に、第2配線層20を覆うように形成されている。第2絶縁層21の材料としては、例えば第1絶縁層11と同一組成の絶縁性樹脂を用いることができる。第2絶縁層21の厚さは、例えば15〜35μm程度とすることができる。

【0020】

第3配線層30は、第2絶縁層21上に形成されている。第3配線層30は、第2絶縁層21を貫通して第2配線層20の上面を露出するビアホールVH3内に充填されたビア配線30Aと、第2絶縁層21上に形成された配線パターン30Bとを有している。ビア配線30Aは、ビアホールVH3の底部に露出した第2配線層20と電気的に接続されるとともに、配線パターン30Bと電気的に接続されている。なお、ビアホールVH3及びビア配線30Aは、図1(a)において下側から上側に向かうに連れて径が大きくなるテーパ状に形成されている。また、これらビアホールVH3及びビア配線30Aの平面形状は例えば円形であり、その直径は例えば20〜50μm程度とすることができる。第3配線層30の配線パターン30Bの厚さは、例えば15〜35μm程度とすることができる。

【0021】

第3絶縁層31(層間絶縁層)は、第2絶縁層21上に、第3配線層30を覆うように形成されている。第3絶縁層31の材料としては、例えば第1絶縁層11と同一組成の絶縁性樹脂を用いることができる。第3絶縁層31の厚さは、例えば15〜35μm程度とすることができる。

【0022】

第4配線層40は、第3絶縁層31上に形成されている。第4配線層40は、第3絶縁層31を貫通して第3配線層30の上面を露出するビアホールVH4内に充填されたビア配線40Aと、第3絶縁層31上に形成された配線パターン40Bとを有している。ビア配線40Aは、ビアホールVH4の底部に露出した第3配線層30と電気的に接続されるとともに、配線パターン40Bと電気的に接続されている。なお、ビアホールVH4及びビア配線40Aは、図1(a)において下側から上側に向かうに連れて径が大きくなるテーパ状に形成されている。また、これらビアホールVH4及びビア配線40Aの平面形状は例えば円形であり、その直径は例えば20〜50μm程度とすることができる。第4配線層40の配線パターン40Bの厚さは、例えば15〜35μm程度とすることができる。

【0023】

第4絶縁層41は、第4配線層40を覆うように第3絶縁層31上に形成された最上層(最外層)の層間絶縁層である。第4絶縁層41は、補強材入りの絶縁層であって、その他の第1〜第3絶縁層11,21,31よりも機械的強度(剛性や硬度等)が高い絶縁層である。この第4絶縁層41の材料としては、例えば熱硬化性樹脂に対し、補強材を入れた絶縁性樹脂を用いることができる。具体的には、第4絶縁層41の材料としては、ガラス、アラミド、LCP(Liquid Crystal Polymer)繊維の織布や不織布に、エポキシ系やポリイミド系の熱硬化性樹脂を含浸させた補強材入りの絶縁性樹脂を用いることができる。また、第4絶縁層41の材料としては、当該第4絶縁層41の熱膨張係数が第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近づくように調整された絶縁性樹脂であることが好ましい。換言すると、第4絶縁層41の材料としては、当該第4絶縁層41の熱膨張係数が第1〜第3絶縁層11,21,31の熱膨張係数よりも低くなるように調整された絶縁性樹脂であることが好ましい。具体的には、第4絶縁層41の熱膨張係数は、例えば18〜30ppm/℃程度に設定されている。なお、第4絶縁層41の厚さは、例えば50〜100μm程度とすることができる。

【0024】

第3絶縁層31及び第4絶縁層41には、第4絶縁層41を厚さ方向に貫通する溝部41Xが形成されている。この溝部41Xは、最外層の層間絶縁層である第4絶縁層41の面41Aから、その第4絶縁層41の下層の絶縁層である第3絶縁層31の厚さ方向の中途位置まで形成されている。溝部41Xは、配線層(ここでは、第4配線層40及び第5配線層50)に干渉しないように形成されている。この溝部41Xは、例えば断面視して略楔状に形成されている。また、図1(b)に示すように、溝部41Xは、半導体チップ2と対向する領域よりも外側の領域に形成されている。具体的には、溝部41Xは、上記外側の領域において、例えば平面視して格子状に形成されている。

【0025】

図1(a)に示すように、第5配線層50は、第4絶縁層41上に形成された最上層(最外層)の配線層である。第5配線層50は、第4絶縁層41を貫通して第4配線層40の上面を露出するビアホールVH5内に充填されたビア配線50Aと、第4絶縁層41上に形成された配線パターン50Bとを有している。ビア配線50Aは、ビアホールVH5の底部に露出した第4配線層40と電気的に接続されるとともに、配線パターン50Bと電気的に接続されている。なお、ビアホールVH5及びビア配線50Aは、図1(a)において下側から上側に向かうに連れて径が大きくなるテーパ状に形成されている。また、これらビアホールVH5及びビア配線50Aの平面形状は例えば円形であり、その直径は例えば50〜75μm程度とすることができる。

【0026】

第5配線層50の配線パターン50Bの厚さは、例えば15〜35μm程度とすることができる。図1(b)に示すように、配線パターン50Bの平面形状は例えば円形である。この配線パターン50Bは、マトリクス状に配置されている。このため、上記溝部41Xは、半導体チップ2と対向する領域よりも外側の領域において、隣接する配線パターン50B間を、左右方向及び上下方向に延在するように形成されている。

【0027】

半導体チップ2が搭載されている面と反対側(図1(a)では上側)の最外層の第4絶縁層41上には、埋込樹脂層51が積層されている。この埋込樹脂層51は、上記溝部41Xを充填するように形成されるとともに、配線パターン50Bの一部を覆うように形成されている。埋込樹脂層51の材料としては、例えば熱硬化性を有するエポキシ系樹脂にシリカやアルミナ等のフィラーを混入した樹脂材を用いることができる。また、埋込樹脂層51の材料としては、当該埋込樹脂層51の熱膨張係数が第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近づくように、エポキシ樹脂及びフィラーの含有量などが調整された絶縁性樹脂であることが好ましい。換言すると、埋込樹脂層51の材料としては、当該埋込樹脂層51の熱膨張係数が第1〜第3絶縁層11,21,31の熱膨張係数よりも低くなるように調整された絶縁性樹脂であることが好ましい。さらに、埋込樹脂層51の材料としては、当該埋込樹脂層51のガラス転移温度Tgが第1〜第3絶縁層11,21,31のガラス転移温度Tg(例えば150℃程度)よりも高い温度(例えば200℃程度)になるように調整された絶縁性樹脂であることが好ましい。具体的には、埋込樹脂層51の熱膨張係数は、ガラス転移温度Tg(ここでは、200℃)よりも低い場合には12ppm/℃程度、ガラス転移温度Tg以上の場合には40ppm/℃程度になるように設定されている。

【0028】

上記埋込樹脂層51には、第5配線層50の配線パターン50Bの一部を外部接続用パッド50Pとして露出させるための開口部51Xが形成されている。この外部接続用パッド50Pには、当該半導体パッケージ1をマザーボード等に実装する際に使用されるはんだボールやリードピン等の外部接続端子が接続されるようになっている。なお、必要に応じて、上記開口部51Xから露出する配線パターン50B上にOSP(Organic Solderbility Preservative)処理を施してOSP膜を形成し、そのOSP膜に上記外部接続端子を接続するようにしてもよい。また、上記開口部51Xから露出する配線パターン50B上に金属層を形成し、その金属層に上記外部接続端子を接続するようにしてもよい。金属層の例としては、Au層、Ni/Au層(Ni層とAu層をこの順番で積層した金属層)や、Ni/パラジウム(Pd)/Au層(Ni層とPd層とAu層をこの順番で積層した金属層)などを挙げることができる。なお、上記開口部51Xから露出する配線パターン50B(あるいは、配線パターン50B上にOSP膜や金属層が形成されている場合には、それらOSP膜又は金属層)自体を、外部接続端子としてもよい。

【0029】

このような構造を有する半導体パッケージ1の大きさは、例えば平面視で12×12mm程度とすることができる。また、半導体パッケージ1全体の厚さは、例えば300〜700μm程度とすることができる。

【0030】

(半導体装置の構造)

次に、半導体装置3の構造を図2に従って説明する。なお、図2において、半導体パッケージ1は図1(a)とは上下を反転して描かれている。

【0031】

半導体装置3は、上述した半導体パッケージ1と、その半導体パッケージ1に積層接合された半導体パッケージ4とを有している。

半導体パッケージ4は、配線基板60と、その配線基板60にフリップチップ実装された第1の半導体チップ71と、第1の半導体チップ71の上に接着された第2の半導体チップ72とを有している。また、半導体パッケージ4は、第1の半導体チップ71と配線基板60との隙間を充填するように設けられたアンダーフィル樹脂73と、第1の半導体チップ71及び第2の半導体チップ72等を封止する封止樹脂74とを有している。なお、第1の半導体チップ71の平面形状は、第2の半導体チップ72の平面形状よりも大きく形成されている。

【0032】

配線基板60は、基板本体61と、基板本体61の上面に形成されたチップ用パッド62及びボンディング用パッド63と、基板本体61の下面に形成された外部接続端子64とを有している。

【0033】

基板本体61は、図示は省略するが、複数の絶縁層と、複数の絶縁層に形成されたビア及び配線等から構成されている。基板本体61に設けられたビア及び配線は、チップ用パッド62、ボンディング用パッド63及び外部接続端子64を電気的に接続している。基板本体61としては、例えばコアレス基板や、コア基板を有するコア付きビルドアップ基板等を用いることができる。

【0034】

チップ用パッド62には、第1の半導体チップ71のバンプ71Aがフリップチップ接合されている。また、ボンディング用パッド63は、ボンディングワイヤ75を介して、第2の半導体チップ72の上面に形成された電極パッド(図示略)と電気的に接続されている。これらチップ用パッド62及びボンディング用パッド63の材料としては、例えば銅又は銅合金を用いることができる。また、チップ用パッド62及びボンディング用パッド63は、銅層の表面に金属層(例えば、Au層、Ni/Au層やNi/Pd/Au層など)を施して形成するようにしてもよい。

【0035】

外部接続端子64は、半導体パッケージ1,4間を接続するための接続端子(例えば、はんだボールやリードピン)である。それぞれの外部接続端子64は、上記半導体パッケージ1に配設されている接続パッド10Pの各々に対向するように設けられている。

【0036】

アンダーフィル樹脂73は、第1の半導体チップ71のバンプ71Aとチップ用パッド62との接続部分の接続強度を向上させるための樹脂であり、配線基板60の上面と第1の半導体チップ71の下面との隙間を充填するように設けられている。なお、アンダーフィル樹脂73の材料としては、例えばエポキシ系の絶縁性樹脂を用いることができる。

【0037】

封止樹脂74は、第1の半導体チップ71、第2の半導体チップ72、ボンディングワイヤ75及びボンディング用パッド63を封止するように基板本体61の上面に設けられている。この封止樹脂74の材料としては、例えばエポキシ系樹脂などの絶縁性樹脂を用いることができる。封止方法としては、例えばトランスファーモールド法を用いることができる。

【0038】

そして、半導体装置3では、半導体パッケージ4の下面に形成された外部接続端子64が、半導体パッケージ1の上面に形成された接続パッド10Pに接合されている。これにより、半導体パッケージ1と半導体パッケージ4とが積層接合され、POP(Package on Package)構造の半導体装置3が形成されている。

【0039】

ここで、従来の半導体パッケージの場合、つまり半導体パッケージ1の溝部41Xが形成されておらず、第4絶縁層41及び埋込樹脂層51の代わりに第2絶縁層21と同一組成の絶縁性樹脂からなる絶縁層が形成された半導体パッケージの反りについて説明する。このような半導体パッケージでは、例えば熱処理後の冷却の際に発生する収縮量は、半導体チップ2側ではその半導体チップ2の熱膨張係数、つまりシリコンの熱膨張係数に依存する。一方、従来の半導体パッケージの配線構造側では、例えば熱処理後の冷却の際に発生する収縮量は、配線構造の熱膨張係数、つまり第2絶縁層21等の各絶縁層の熱膨張係数に依存する。上述したように、シリコンの熱膨張係数が3.4ppm/℃であるのに対し、第2絶縁層21としてエポキシ系樹脂を用いる場合には、その熱膨張係数は、ガラス転移温度Tg(150℃)よりも低い場合に46ppm/℃、ガラス転移温度Tg以上で120ppm/℃となる。このように、従来の半導体パッケージの配線構造側の熱膨張係数は、半導体チップ2側の熱膨張係数と著しく異なる。これに起因して、例えば熱処理後の冷却の際に配線構造側に発生する収縮量が、半導体チップ2側に発生する収縮量と異なるため、半導体パッケージ1に反りが生じやすい。

【0040】

(作用)

これに対し、本実施形態の半導体パッケージ1では、最外層の層間絶縁層である第4絶縁層41及びその第4絶縁層41の下層に形成された第3絶縁層31に、その第4絶縁層41を厚さ方向に貫通する溝部41Xを形成するようにした。これにより、第3絶縁層31及び第4絶縁層41が溝部41Xによって複数の領域に分断される。このため、溝部41Xが形成されずに第3絶縁層31及び第4絶縁層41が広い領域にわたって一体的に形成された場合と比較して、第3絶縁層31及び第4絶縁層41が収縮することによって生じる応力を緩和することができる。この結果、半導体パッケージ1に生じる反りを低減することができる。

【0041】

さらに、半導体パッケージ1では、最外層の層間絶縁層である第4絶縁層41及び溝部41Xを充填する埋込樹脂層51の熱膨張係数を、第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近くなるように設定した。これにより、半導体パッケージ1の埋込樹脂層51側、つまり半導体チップ2と反対側の熱膨張係数を、半導体チップ2側の熱膨張係数に近づけることができる。したがって、例えば熱処理後の冷却の際に埋込樹脂層51側に発生する収縮量を、半導体チップ2側に発生する収縮量に近づけることができる。この結果、半導体パッケージ1に生じる反りを低減することができる。

【0042】

(半導体パッケージの製造方法)

次に、上記半導体パッケージ1の製造方法を説明する。

まず、半導体パッケージ1を製造するためには、図3(a)に示すように、支持基板80を用意する。この支持基板80としては、例えば金属板や金属箔を用いることができ、本実施形態では、例えば銅箔を用いる。この支持基板80の厚さは、例えば35〜200μm程度である。

【0043】

次に、図3(b)に示す工程では、支持基板80の一方の面80A(図中の上面)に、開口部81Xを有するレジスト層81を形成する。開口部81Xは、上記第1配線層10(図1参照)の形成領域に対応する部分の支持基板80の面80Aを露出するように形成される。レジスト層81の材料としては、感光性のドライフィルムレジスト又は液状のフォトレジスト(例えばノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト)等を用いることができる。例えば感光性のドライフィルムレジストを用いる場合には、支持基板80の面80Aにドライフィルムを熱圧着によりラミネートし、そのドライフィルムを露光・現像によりパターニングして、上記開口部81Xを持つレジスト層81を形成する。なお、液状のフォトレジストを用いる場合にも、同様の工程を経て、レジスト層81を形成することができる。

【0044】

続いて、図3(c)に示す工程では、上記レジスト層81をめっきマスクとして、支持基板80の面80Aに、該支持基板80をめっき給電層に利用する電解めっきを施す。具体的には、レジスト層81の開口部81Xから露出された支持基板80の面80Aに電解めっき法を施すことにより、開口部81X内に第1導電層10Aと第2導電層10Bとを順に積層して第1配線層10を形成する。例えば第1導電層10AがAu膜、Ni膜をこの順番で順次積層した構造であり、第2導電層10BがCu層である場合には、まず、支持基板80をめっき給電層に利用する電解めっき法により、Au膜、Ni膜を順に積層して第1導電層10Aを形成する。次いで、支持基板80をめっき給電層に利用する電解めっき法により、第1導電層10A上にCu層を形成して第2導電層10Bを形成する。その後、レジスト層81を除去する。

【0045】

次に、図3(d)に示す工程では、支持基板80の面80A上に半導体チップ2を固定する。具体的には、半導体チップ2の回路形成面2Aとは反対側の第2主面2Bが支持基板80の面80Aと対向するように、つまりフェイスアップの状態で半導体チップ2を支持基板80の面80A上に固定する。例えば半導体チップ2の第2主面2Bに予め粘着層(図示略)を形成しておき、フェイスアップの状態で支持基板80の面80A上に配置された半導体チップ2を加圧することにより、上記粘着層を介して支持基板80の面80A上に半導体チップ2を固定する。

【0046】

続いて、図3(e)に示す工程では、支持基板80の面80A上に、半導体チップ2及び第1配線層10を覆うように第1絶縁層11を形成する。なお、第1絶縁層11は、例えば支持基板80に樹脂フィルムをラミネートした後に、樹脂フィルムを押圧しながら130〜150℃程度の温度で熱処理して硬化させることにより形成することができる。

【0047】

次に、図4(a)に示す工程では、半導体チップ2の回路形成面2Aに形成された電極パッド2Pの上面が露出されるように、第1絶縁層11の所定箇所にビアホールVH1を形成する。また、第1配線層10の第2導電層10Bの上面が露出されるように、第1絶縁層11の所定箇所にビアホールVH2を形成する。これらビアホールVH1,VH2は、例えばCO2レーザ、YAGレーザ、エキシマレーザ等によるレーザ加工法によって形成することができる。なお、第1絶縁層11が感光性樹脂を用いて形成されている場合には、例えばフォトリソグラフィ法により所要のビアホールVH1,VH2を形成するようにしてもよい。

【0048】

続いて、ビアホールVH1,VH2をレーザ加工法によって形成した場合には、デスミア処理を行って、ビアホールVH1,VH2内の樹脂残渣(樹脂スミア)を除去する。このデスミア処理は、例えば過マンガン酸塩法などを用いて行うことができる。

【0049】

次いで、図4(b)に示す工程では、第1絶縁層11のビアホールVH1,VH2にビア導体を充填してビア配線20Aを形成するとともに、そのビア配線20Aを介して第1配線層10に電気的に接続される配線パターン20Bを第1絶縁層11上に形成する。これらビア配線20A及び配線パターン20B、つまり第2配線層20は、例えばセミアディティブ法やサブトラクティブ法などの各種の配線形成方法を用いて形成することができる。

【0050】

次に、図3(e)〜図4(b)に示した工程を繰り返すことにより、絶縁層と配線層とを交互に積層する。すなわち、図4(c)に示すように、第1絶縁層11及び第2配線層20上に第2絶縁層21を形成し、この第2絶縁層21に、配線パターン20Bの上面に達するビアホールVH3を形成する。その後、上記ビアホールVH3にビア配線30Aを形成するとともに、そのビア配線30Aに電気的に接続される配線パターン30Bを形成する。次に、第2絶縁層21及び第3配線層30上に第3絶縁層31を形成し、この第3絶縁層31にビアホールVH4を形成した後、そのビアホールVH4にビア配線40Aを形成するとともに、そのビア配線40Aに接続される配線パターン40Bを形成する。続いて、第3絶縁層31及び第4配線層40上に第4絶縁層41を形成し、この第4絶縁層41にビアホールVH5を形成した後、そのビアホールVH5にビア配線50Aを形成するとともに、そのビア配線50Aに接続される配線パターン50Bを形成する。

【0051】

次に、図5(a)に示す工程では、第3絶縁層31及び第4絶縁層41に、第4絶縁層41の面41A側(図中の上面側)から溝部41Xを形成する。この溝部41Xは、例えば例えばCO2レーザ、YAGレーザ、エキシマレーザ等によるレーザ加工法、プラズマエッチング(ドライエッチング)や、ブラスト処理などにより形成することができる。この溝部41Xの形成によって内部応力が解放される。このとき、半導体チップ2及び配線構造が支持基板80上に固定されているため、つまり溝部41Xの形成される面とは反対側に厚い支持基板80が形成されているため、上記応力解放に伴って生じるおそれのある反りを低減することができる。

【0052】

次に、図5(b)に示す工程では、溝部41Xを充填するとともに、第5配線層50を覆うように埋込樹脂層51を第4絶縁層41の面41A上に形成する。この埋込樹脂層51は、例えば感光性のレジストフィルムをラミネートし、又は液状レジストを塗布することにより形成することができる。

【0053】

続いて、図6(a)に示す工程では、第5配線層50の配線パターン50Bの上面が露出されるように、埋込樹脂層51の所要箇所に開口部51Xを形成する。この開口部51Xは、例えばCO2レーザ、YAGレーザ、エキシマレーザ等によるレーザ加工法によって形成することができる。なお、埋込樹脂層51が感光性樹脂を用いて形成されている場合には、例えばフォトリソグラフィ法により所要の開口部51Xを形成するようにしてもよい。これにより、埋込樹脂層51の開口部51Xから第5配線層50の一部が外部接続用パッド50Pとして露出される。なお、必要に応じて、外部接続用パッド50P上に、例えばNi層とAu層をこの順番で積層した金属層を形成するようにしてもよい。この金属層は、例えば無電解めっき法により形成することができる。

【0054】

次いで、図6(b)に示す工程では、仮基板として用いた支持基板(図6(a)参照)を除去する。例えば支持基板80として銅箔を用いる場合には、塩化第二鉄水溶液、塩化第二銅水溶液、過硫酸アンモニウム水溶液等を用いたウェットエッチングにより、支持基板80の除去を行うことができる。この際、第1絶縁層11から露出する半導体チップ2がシリコンからなり、第1配線層10の最表層がAu膜等であるため、銅箔である支持基板80のみを選択的にエッチングすることができる。但し、第5配線層50が銅層である場合には、開口部51Xの底部に露出する第5配線層50が支持基板80とともにエッチングされることを防止するため、第5配線層50をマスクして上記ウェットエッチングを行う必要がある。

【0055】

このとき、第3絶縁層31及び第4絶縁層41に溝部41Xが形成され、その溝部41Xには半導体チップ2の熱膨張係数に近い熱膨張係数を有する埋込樹脂層51が充填されている。このため、第3絶縁層31及び第4絶縁層41が複数の領域に分断されており、埋込樹脂層51側の熱膨張係数が半導体チップ2側の熱膨張係数に近い値になっている。これにより、支持基板80の除去に伴う応力解放によって生じうる半導体パッケージ1の反りを低減することができる。したがって、半導体パッケージ1が平坦な状態に保持される。

【0056】

以上の製造工程により、本実施形態の半導体パッケージ1を製造することができる。

(半導体装置の製造方法)

次に、図7(a)に示すように、半導体パッケージ4を用意する。ここでは、図示を省略して詳細な説明を割愛するが、半導体パッケージ4は例えば以下のような方法で製造される。すなわち、チップ用パッド62、ボンディング用パッド63及び外部接続端子64を有する配線基板60を形成し、その配線基板60の上面に形成されたチップ用パッド62に第1の半導体チップ71のバンプ71Aをフリップチップ接合する。続いて、配線基板60と第1の半導体チップ71との間にアンダーフィル樹脂73を形成した後、第1の半導体チップ71の上に第2の半導体チップ72を接着剤により接着する。次いで、第2の半導体チップ72の上面に形成された電極パッド(図示略)と配線基板60の上面に形成されたボンディング用パッド63との間をボンディングワイヤ75によりワイヤボンディング接続した後、第1及び第2の半導体チップ71,72及びボンディングワイヤ75等を封止樹脂74で樹脂封止する。

【0057】

続いて、半導体パッケージ1の各接続パッド10Pに、半導体パッケージ4の外部接続端子64が対向するように、半導体パッケージ1,4を位置合わせする。このとき、半導体パッケージ4の外部接続端子64には図示しないフラックスが転写されている。

【0058】

次いで、図7(b)に示す工程では、上述のように位置合わせされて半導体パッケージ4が半導体パッケージ1上に載置されると、その構造体がリフロー炉(図示略)に搬送される。そして、このリフロー炉内では外部接続端子64(ここでは、はんだボール)がリフローされ、接続パッド10P部分で半導体パッケージ1,4が接合される。これにより、POP構造の半導体装置3が製造される。

【0059】

このとき、半導体パッケージ1が平坦な状態に保持されているため、その半導体パッケージ1に半導体パッケージ4を容易に積層接合させることができる。

以上説明した本実施形態によれば、以下の効果を奏することができる。

【0060】

(1)最外層の層間絶縁層である第4絶縁層41及びその第4絶縁層41の下層に形成された第3絶縁層31に、その第4絶縁層41を厚さ方向に貫通する溝部41Xを形成するようにした。これにより、第3絶縁層31及び第4絶縁層41が収縮することによって生じる応力を緩和することができ、半導体パッケージ1に生じる反りを低減することができる。この結果、半導体パッケージ1を平坦な状態に保持することができる。

【0061】

(2)溝部41Xに充填され、半導体チップ2と反対側に形成される埋込樹脂層51の熱膨張係数を、第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近くなるように設定した。これにより、例えば熱処理後の冷却の際に埋込樹脂層51側に発生する収縮量を、半導体チップ2側に発生する収縮量に近づけることができ、半導体パッケージ1に生じる反りを低減することができる。

【0062】

(3)最外層の層間絶縁層である第4絶縁層41の熱膨張係数を、第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近くなるように設定した。これにより、例えば熱処理後の冷却の際に埋込樹脂層51側に発生する収縮量を、半導体チップ2側に発生する収縮量に近づけることができ、半導体パッケージ1に生じる反りを低減することができる。

【0063】

(4)ところで、図6(b)に示した工程において、支持基板80を除去すると、埋込樹脂層51側の熱膨張係数と半導体チップ2側の熱膨張係数の違いに起因して反りが生じうる。このとき、埋込樹脂層51側の収縮量が半導体チップ2側の収縮量よりも大きくなるため、埋込樹脂層51側が凹状に反る傾向にある。

【0064】

これに対し、本実施形態の半導体パッケージ1では、最外層の第4絶縁層41、つまり反りの生じやすい側に形成された第4絶縁層41を補強材入りの絶縁層とした。これにより、第4絶縁層41の剛性を高めることができるため、半導体パッケージ1の反りを効果的に抑制することができる。すなわち、支持基板80を除去したときに半導体パッケージ1が反った場合に、凹状となる埋込樹脂層51側に形成された第4絶縁層41の剛性を高めることにより、半導体パッケージ1を反らす応力に効果的に対抗でき、半導体パッケージ1の反りを低減できる効果が大きい。

【0065】

(5)溝部41Xを、半導体チップ2と対向する領域よりも外側の領域に形成するようにした。ここで、半導体パッケージ1の外周部に近づくほど反り量は大きくなる傾向にある。このため、上記溝部41Xによって半導体パッケージ1の反りを効果的に低減することができる。

【0066】

(6)支持基板80の存在する状態で、溝部41Xを形成するようにした。これにより、溝部41Xの形成による応力解放に伴って生じるおそれのある反りを低減することができる。

【0067】

(7)溝部41Xの平面形状を、加工の容易な格子状に形成するようにした。このため、溝部41Xを容易に形成することができる。

(8)溝部41Xの断面形状を略楔状に形成するようにした。これにより、第4絶縁層41及び第3絶縁層31を複数の領域に確実に分断することができる。このため、第3絶縁層31及び第4絶縁層41が収縮することによって生じる応力を効果的に緩和することができ、半導体パッケージ1に生じる反りを低減することができる。

【0068】

(他の実施形態)

なお、上記実施形態は、これを適宜変更した以下の態様にて実施することもできる。

・図8に示されるように、上記実施形態における埋込樹脂層51を省略するようにしてもよい。このような構造であっても、上記実施形態の(1)、(3)〜(8)と同様の効果を奏することができる。

【0069】

・図9に示されるように、上記実施形態における第4絶縁層41を、第1〜第3絶縁層11,21,31と同一組成の絶縁性樹脂からなる第4絶縁層41Bに変更するようにしてもよい。

【0070】

・上記実施形態における溝部41Xの形状(断面形状及び平面形状)は特に限定されない。

例えば上記実施形態では、第3絶縁層31及び第4絶縁層41の2層分の層間絶縁層に溝部41Xを形成するようにしたが、図10(a)に示されるように、3層以上の層間絶縁層に溝部41Xを形成するようにしてもよい。図10(a)に示した変形例では、溝部41Xは、第4絶縁層41の面41Aから第4絶縁層41及び第3絶縁層31を厚さ方向に貫通して、第2絶縁層21の厚さ方向の中途位置まで形成されている。このように溝部41Xが深く形成されると、その溝部41Xによって分断される層間絶縁層の数が増加するため、効果的に反りを抑制することができる。

【0071】

また、上記実施形態では、溝部41Xの断面形状を略楔状に形成するようにしたが、例えば図10(b)に示されるように、溝部41Xの断面形状を四角形状に形成するようにしてもよい。また、溝部41Xの断面形状を、台形状、U字状や半円状に形成するようにしてもよい。

【0072】

また、上記実施形態では、溝部41Xの平面形状を格子状に形成するようにした。これに限らず、例えば図11(a)に示されるように、溝部41Xの平面形状を略枠状に形成するようにしてもよい。なお、図11(a)に示した変形例では、平面視略枠状の溝部41Xが2つ形成されているが、この溝部41Xの数は1つであってもよく、3つ以上であってもよい。

【0073】

また、図11(b)に示されるように、溝部41Xの平面形状を略L字状に形成するようにしてもよい。図11(b)に示した変形例では、平面視略L字状の溝部41Xが半導体パッケージ1の四隅に形成されている。なお、図11(b)に示した変形例では、各角部に2つの溝部41Xが形成されているが、この各角部に形成される溝部41Xの数は1つであってもよく、3つ以上であってもよい。

【0074】

・上記実施形態では、半導体チップ2と対向する領域よりも外側の領域に溝部41Xを形成するようにした。これに限らず、半導体チップ2と対向する領域にも溝部41Xを形成するようにしてもよい。

【0075】

・図12に示されるように、上記実施形態における第1配線層10(接続パッド10P)を省略するようにしてもよい。この場合の半導体パッケージ1Bでは、第1配線層10の上面を露出するビアホールVH2及びそのビアホールVH2に形成されるビア配線20Aも省略される。

【0076】

・上記実施形態では、支持基板80上に1つの半導体パッケージ1を作製する例を示したが、支持基板80上に半導体パッケージ1となる部材を作製し、それを個片化して複数の半導体パッケージ1を得るような工程に変更してもよい。

【0077】

・上記実施形態の半導体パッケージ1の製造方法では、支持基板80の片側に半導体チップ2を固定するとともに、主にビルドアップ工法により支持基板80の片側に配線層及び絶縁層を積層し、最後に支持基板80を除去して半導体パッケージ1を製造するようにした。これに限らず、例えば支持基板80の両側にそれぞれ半導体チップ2を固定するとともに、主にビルドアップ工法により支持基板80の両側それぞれに配線層及び絶縁層を積層し、最後に支持基板80を除去して複数の半導体パッケージ1を製造するようにしてもよい。

【0078】

・上記実施形態における半導体パッケージ1の層の数や配線の取り回しなどは様々に変形・変更することが可能である。

・上記実施形態における半導体パッケージ4の配線基板60に実装される半導体チップの数や、その半導体チップの実装の形態(例えばフリップチップ実装、ワイヤボンディングによる実装、又はこれらの組み合わせ)などは様々に変形・変更することが可能である。

【0079】

[実施例]

次に、実施例及び比較例を挙げて上記実施形態及びその変形例をさらに具体的に説明する。

【0080】

ここでは、溝部41Xを設けた半導体パッケージ(実施例1,2)と、溝部41Xを設けていない半導体パッケージ(比較例1,2)の各々について反りのシミュレーションを行った。

【0081】

(実施例1)

実施例1の半導体パッケージは、図1(a)に示した半導体パッケージ1である。シミュレーション条件としては、半導体パッケージ1の平面形状を12mm×12mmの正方形状とし、半導体チップ2の平面形状を9mm×9mmの正方形状とし、半導体チップ2の厚さを100μmとした。また、半導体パッケージ1全体の厚さを550μmとした。具体的には、第2〜第5配線層20,30,40,50の厚さをそれぞれ15μmとし、第1絶縁層11の厚さを180μm、第2及び第3絶縁層21,31の厚さを30μm、第4絶縁層41の厚さを100μm、埋込樹脂層51の厚さを50μmとした。なお、溝部41XはCO2レーザによるレーザ加工により形成し、その溝部41Xの深さを120μmとした。

【0082】

(実施例2)

実施例2の半導体パッケージは、図8に示した半導体パッケージ1Aであり、実施例1の半導体パッケージから埋込樹脂層51を除去した構造を有している。シミュレーション条件としては、上記半導体パッケージ1Aを厚さ200μmの支持基板80に固定した状態で反りを測定する点のみが上記実施例1と異なる。

【0083】

(比較例1)

比較例1の半導体パッケージは、図13に示される半導体パッケージ5である。この半導体パッケージ5は、溝部41X(図1(a)参照)が形成されていない点を除き、実施例1の半導体パッケージ1と同一の構造を有する。なお、シミュレーション条件については、実施例1と同一の条件である。

【0084】

(比較例2)

比較例2の半導体パッケージは、図14に示される半導体パッケージ6である。この半導体パッケージ6は、溝部41X(図8参照)が形成されていない点を除き、実施例2の半導体パッケージ1Aと同一の構造を有する。なお、シミュレーション条件については、実施例2と同一の条件である。

【0085】

(測定方法)

各例の半導体パッケージを190℃の環境下に置いて応力を解放後、温度を25℃に下げたときの反りを測定した。反りは、各半導体パッケージの半導体チップ2の搭載されたチップ搭載面11Aとは反対側の面の高さを対角線に沿って順次測定し、最も高い点と最も低い点との高さの差を測定した。なお、チップ搭載面11Aとは反対側の面が凸状に沿った場合の反り量をプラスとし、チップ搭載面とは反対側の面が凹状に沿った場合の反り量をマイナスとして、図15にシミュレーション結果を示した。

【0086】

(シミュレーション結果)

図15に示すように、実施例1と比較例1、及び、実施例2と比較例2をそれぞれ比較すると、溝部41Xを設けることにより(実施例1,2)、溝部41Xを設けない場合(比較例1,2)に比べ、半導体パッケージの反り量を大幅に低減できることが確認された。すなわち、溝部41Xの形成によって、高い反り改善効果が得られることが確認された。

【符号の説明】

【0087】

1,1A,1B 半導体パッケージ(第1半導体パッケージ)

2 半導体チップ

4 半導体パッケージ(他の半導体パッケージ又は第2半導体パッケージ)

10 第1配線層

10P 接続パッド(パッド)

11 第1絶縁層

20,30,40,50 配線層

21 第2絶縁層(層間絶縁層)

31 第3絶縁層(層間絶縁層)

41 第4絶縁層(最外層の層間絶縁層)

41X 溝部

51 埋込樹脂層

80 支持基板

【技術分野】

【0001】

本発明は、半導体パッケージ、半導体パッケージの製造方法及び半導体装置に関するものである。

【背景技術】

【0002】

従来、半導体チップと、その半導体チップを覆う樹脂層とを有する半導体パッケージが知られている。

このような半導体パッケージの一例としては、半導体チップの能動面(回路形成面)及び側面が絶縁層により覆われており、その絶縁層上に、半導体チップと電気的に接続された配線構造が積層されてなる構造が提案されている(例えば、特許文献1参照)。

【0003】

このような半導体パッケージの製造方法としては、以下のような方法が知られている。

例えば支持基板を準備し、その支持基板上に、半導体チップの能動面と反対側の面が支持基板の表面に接するように半導体チップを搭載する。続いて、搭載した半導体チップを絶縁層により封止し、絶縁層上に配線層と層間絶縁層とを積層して配線構造を形成する。そして、支持基板を除去することによって、半導体パッケージを製造する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008−300854号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来の半導体パッケージの製造工程では、支持基板上に半導体チップを固定し、絶縁層及び配線構造を形成した状態では、支持基板の剛性が高いため、半導体パッケージには反りがほとんど発生しない。しかし、支持基板を除去すると、その除去した部分の応力が解放されるため、その応力解放に伴って半導体パッケージに反りが生じるという問題があった。

【課題を解決するための手段】

【0006】

本発明の一観点によれば、半導体チップと、前記半導体チップを覆うように形成された第1絶縁層と、前記第1絶縁層上に積層され、前記半導体チップと電気的に接続された配線層と該配線層上に積層された層間絶縁層とが交互に積層されてなる配線構造と、を有し、前記半導体チップの搭載面とは反対側の最外層の前記層間絶縁層には、該層間絶縁層を厚さ方向に貫通する溝部が形成されている。

【発明の効果】

【0007】

本発明の一観点によれば、反りを低減することができるという効果を奏する。

【図面の簡単な説明】

【0008】

【図1】(a)は、一実施形態の半導体パッケージを示す概略断面図、(b)は、一実施形態の半導体パッケージを示す概略平面図。なお、(b)では、埋込樹脂層の図示を省略している。

【図2】一実施形態の半導体装置を示す概略断面図。

【図3】(a)〜(e)は、一実施形態の半導体パッケージの製造方法を示す概略断面図。

【図4】(a)〜(c)は、一実施形態の半導体パッケージの製造方法を示す概略断面図。

【図5】(a)、(b)は、一実施形態の半導体パッケージの製造方法を示す概略断面図。

【図6】(a)、(b)は、一実施形態の半導体パッケージの製造方法を示す概略断面図。

【図7】(a)、(b)は、一実施形態の半導体装置の製造方法を示す概略断面図。

【図8】変形例の半導体パッケージを示す概略断面図。

【図9】変形例の半導体パッケージを示す概略断面図。

【図10】(a)、(b)は、変形例の半導体パッケージを示す概略断面図。

【図11】(a)、(b)は、変形例の半導体パッケージを示す概略平面図。なお、(a)、(b)では、埋込樹脂層の図示を省略している。

【図12】変形例の半導体パッケージを示す概略断面図。

【図13】比較例1の半導体パッケージを示す概略断面図。

【図14】比較例2の半導体パッケージを示す概略断面図。

【図15】反りのシミュレーション結果を示すテーブル。

【発明を実施するための形態】

【0009】

以下、添付図面を参照して各実施形態を説明する。なお、添付図面は、特徴を分かりやすくするために便宜上特徴となる部分を拡大して示している場合があり、各構成要素の寸法比率などが実際と同じであるとは限らない。また、断面図では、各部材の断面構造を分かりやすくするために、一部の樹脂層のハッチングを省略している。

【0010】

以下、一実施形態を図1〜図7に従って説明する。

(半導体パッケージの構造)

図1(a)に示すように、半導体パッケージ1は、半導体チップ2を有している。この半導体チップ2としては、例えばCPU(Central Processing Unit)チップやGPU(Graphics Processing Unit)チップなどのロジックチップを用いることができる。また、半導体チップ2としては、例えばDRAM(Dynamic Random Access Memory)チップ、SRAM(Static Random Access Memory)チップやフラッシュメモリチップなどのメモリチップを用いることができる。

【0011】

このような半導体チップ2は、例えば半導体基板からなる。半導体基板の材料としては、例えばシリコン(Si)等を用いることができる。また、半導体チップ2は、第1主面2A(図1(a)では、上面)側に半導体集積回路(図示略)が形成されている。この半導体集積回路は、図示は省略するが、上記半導体基板に形成された拡散層、半導体基板上に積層された絶縁層、及び積層された絶縁層に設けられたビア及び配線等を有している。そして、この半導体集積回路上には、該半導体集積回路と電気的に接続された電極パッド2Pが設けられている。なお、この電極パッド2Pの材料としては、例えばアルミニウム(Al)、銅(Cu)とAlの合金や、CuとAlとSiの合金を用いることができる。

【0012】

上記半導体チップ2の大きさは、例えば平面視で9mm×9mm程度とすることができる。半導体チップ2の厚さは、例えば50〜200μm程度とすることができる。また、本実施形態では、半導体チップ2がシリコンからなり、その半導体チップ2の熱膨張係数が約3.4ppm/℃になる。なお、以下の説明では、半導体チップ2の第1主面2Aを回路形成面2Aと称する場合もある。

【0013】

また、半導体パッケージ1は、第1配線層10と、第1絶縁層11と、第2配線層20と、第2絶縁層21と、第3配線層30と、第3絶縁層31と、第4配線層40と、第4絶縁層41と、第5配線層50とが順次積層された配線構造を有している。このように、本実施形態の半導体パッケージ1は、一般的なビルドアップ法を用いて作製される配線基板(支持基材としてのコア基板の両面又は片面に所要数のビルドアップ層を順次形成して積層したもの)とは異なり、支持基材を含まない「コアレス構造」の形態を有している。

【0014】

なお、第2〜第5配線層20,30,40,50の材料としては、例えば銅や銅合金を用いることができる。

半導体パッケージ1において、第1配線層10は、最外層(図1では最下層)に形成されている。この第1配線層10は、第1導電層10Aと第2導電層10Bとを有している。第1導電層10Aとしては、例えば金(Au)膜、ニッケル(Ni)膜を、Au膜が半導体パッケージ1の外部に露出するように、この順番で順次積層した導電層を用いることができる。また、第2導電層10Bとしては、例えばCu層等を含む導電層を用いることができる。なお、上記Au膜の厚さは例えば0.1〜1μm程度とすることができ、上記Ni膜の厚さは例えば1〜10μm程度とすることができる。また、第2導電層10B(Cu層)の厚さは例えば10〜40μm程度とすることができる。

【0015】

第1配線層10の第1主面(図1(a)では上面)及び側面は第1絶縁層11によって覆われている。一方、第1配線層10の第2主面(図1(a)では下面)は第1絶縁層11から露出しており、他の半導体パッケージ4(図2参照)等と電気的に接続される接続パッド10Pとして機能する。第1配線層10の平面形状は例えば円形であり、その直径は例えば40〜120μm程度とすることができる。この第1配線層10は、半導体チップ2の外周に沿った環状の形態、いわゆるペリフェラル状に形成されている。

【0016】

第1絶縁層11は、半導体チップ2の第1主面2A及び側面を覆い、半導体チップ2の第2主面2B(図中の下面)を露出するように形成されている。また、第1絶縁層11は、第1配線層10の第1主面(図1(a)では上面)及び側面を覆い、第1配線層10の第2主面(図1(a)では下面)を露出するように形成されている。すなわち、第1絶縁層11の面11A(図1(a)では下面)、半導体チップ2の第2主面2B及び第1配線層10の第2主面は略面一になるように形成されている。換言すると、半導体チップ2と第1配線層10(接続パッド10P)とは同一平面上に形成されている。第1絶縁層11の材料としては、熱硬化性を有するエポキシ系の絶縁性樹脂を用いることができる。このエポキシ系樹脂の熱膨張係数は、ガラス転移温度Tg(例えば150℃)よりも低い場合には46ppm/℃程度、ガラス転移温度Tg以上の場合に120ppm/℃程度となる。なお、上記絶縁性樹脂としては、熱硬化性を有する樹脂に限定されず、感光性を有する絶縁性樹脂を用いることができる。第1絶縁層11の厚さは、例えば100〜180μm程度とすることができる。なお、以下の説明では、第1絶縁層11の面11Aをチップ搭載面11Aと称する場合もある。

【0017】

第1絶縁層11には、該第1絶縁層11を貫通して半導体チップ2の電極パッド2Pの上面を露出するビアホールVH1が形成されている。また、第1絶縁層11には、該第1絶縁層11を貫通して第1配線層10の第1主面を露出するビアホールVH2が形成されている。

【0018】

第2配線層20は、第1絶縁層11上に形成されている。第2配線層20は、ビアホールVH1,VH2内に充填されたビア配線20Aと、第1絶縁層上に形成された配線パターン20Bとを有している。ビア配線20Aは、ビアホールVH1の底部に露出した電極パッド2P又はビアホールVH2の底部に露出した第1配線層10と電気的に接続されるとともに、配線パターン20Bと電気的に接続されている。なお、ビアホールVH1,VH2及びビア配線20Aは、図1(a)において下側(接続パッド10P側)から上側(第5配線層50側)に向かうにつれて径が大きくなるテーパ状に形成されている。また、これらビアホールVH1,VH2及びビア配線20Aの平面形状は例えば円形である。ビアホールVH1及びそのビアホールVH1に形成されたビア配線20Aの直径は例えば20〜50μm程度とすることができ、ビアホールVH2及びそのビアホールVH2に形成されたビア配線20Aの直径は例えば75〜150μm程度とすることができる。第2配線層20の配線パターン20Bの厚さは、例えば15〜35μm程度とすることができる。

【0019】

第2絶縁層21(層間絶縁層)は、第1絶縁層11上に、第2配線層20を覆うように形成されている。第2絶縁層21の材料としては、例えば第1絶縁層11と同一組成の絶縁性樹脂を用いることができる。第2絶縁層21の厚さは、例えば15〜35μm程度とすることができる。

【0020】

第3配線層30は、第2絶縁層21上に形成されている。第3配線層30は、第2絶縁層21を貫通して第2配線層20の上面を露出するビアホールVH3内に充填されたビア配線30Aと、第2絶縁層21上に形成された配線パターン30Bとを有している。ビア配線30Aは、ビアホールVH3の底部に露出した第2配線層20と電気的に接続されるとともに、配線パターン30Bと電気的に接続されている。なお、ビアホールVH3及びビア配線30Aは、図1(a)において下側から上側に向かうに連れて径が大きくなるテーパ状に形成されている。また、これらビアホールVH3及びビア配線30Aの平面形状は例えば円形であり、その直径は例えば20〜50μm程度とすることができる。第3配線層30の配線パターン30Bの厚さは、例えば15〜35μm程度とすることができる。

【0021】

第3絶縁層31(層間絶縁層)は、第2絶縁層21上に、第3配線層30を覆うように形成されている。第3絶縁層31の材料としては、例えば第1絶縁層11と同一組成の絶縁性樹脂を用いることができる。第3絶縁層31の厚さは、例えば15〜35μm程度とすることができる。

【0022】

第4配線層40は、第3絶縁層31上に形成されている。第4配線層40は、第3絶縁層31を貫通して第3配線層30の上面を露出するビアホールVH4内に充填されたビア配線40Aと、第3絶縁層31上に形成された配線パターン40Bとを有している。ビア配線40Aは、ビアホールVH4の底部に露出した第3配線層30と電気的に接続されるとともに、配線パターン40Bと電気的に接続されている。なお、ビアホールVH4及びビア配線40Aは、図1(a)において下側から上側に向かうに連れて径が大きくなるテーパ状に形成されている。また、これらビアホールVH4及びビア配線40Aの平面形状は例えば円形であり、その直径は例えば20〜50μm程度とすることができる。第4配線層40の配線パターン40Bの厚さは、例えば15〜35μm程度とすることができる。

【0023】

第4絶縁層41は、第4配線層40を覆うように第3絶縁層31上に形成された最上層(最外層)の層間絶縁層である。第4絶縁層41は、補強材入りの絶縁層であって、その他の第1〜第3絶縁層11,21,31よりも機械的強度(剛性や硬度等)が高い絶縁層である。この第4絶縁層41の材料としては、例えば熱硬化性樹脂に対し、補強材を入れた絶縁性樹脂を用いることができる。具体的には、第4絶縁層41の材料としては、ガラス、アラミド、LCP(Liquid Crystal Polymer)繊維の織布や不織布に、エポキシ系やポリイミド系の熱硬化性樹脂を含浸させた補強材入りの絶縁性樹脂を用いることができる。また、第4絶縁層41の材料としては、当該第4絶縁層41の熱膨張係数が第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近づくように調整された絶縁性樹脂であることが好ましい。換言すると、第4絶縁層41の材料としては、当該第4絶縁層41の熱膨張係数が第1〜第3絶縁層11,21,31の熱膨張係数よりも低くなるように調整された絶縁性樹脂であることが好ましい。具体的には、第4絶縁層41の熱膨張係数は、例えば18〜30ppm/℃程度に設定されている。なお、第4絶縁層41の厚さは、例えば50〜100μm程度とすることができる。

【0024】

第3絶縁層31及び第4絶縁層41には、第4絶縁層41を厚さ方向に貫通する溝部41Xが形成されている。この溝部41Xは、最外層の層間絶縁層である第4絶縁層41の面41Aから、その第4絶縁層41の下層の絶縁層である第3絶縁層31の厚さ方向の中途位置まで形成されている。溝部41Xは、配線層(ここでは、第4配線層40及び第5配線層50)に干渉しないように形成されている。この溝部41Xは、例えば断面視して略楔状に形成されている。また、図1(b)に示すように、溝部41Xは、半導体チップ2と対向する領域よりも外側の領域に形成されている。具体的には、溝部41Xは、上記外側の領域において、例えば平面視して格子状に形成されている。

【0025】

図1(a)に示すように、第5配線層50は、第4絶縁層41上に形成された最上層(最外層)の配線層である。第5配線層50は、第4絶縁層41を貫通して第4配線層40の上面を露出するビアホールVH5内に充填されたビア配線50Aと、第4絶縁層41上に形成された配線パターン50Bとを有している。ビア配線50Aは、ビアホールVH5の底部に露出した第4配線層40と電気的に接続されるとともに、配線パターン50Bと電気的に接続されている。なお、ビアホールVH5及びビア配線50Aは、図1(a)において下側から上側に向かうに連れて径が大きくなるテーパ状に形成されている。また、これらビアホールVH5及びビア配線50Aの平面形状は例えば円形であり、その直径は例えば50〜75μm程度とすることができる。

【0026】

第5配線層50の配線パターン50Bの厚さは、例えば15〜35μm程度とすることができる。図1(b)に示すように、配線パターン50Bの平面形状は例えば円形である。この配線パターン50Bは、マトリクス状に配置されている。このため、上記溝部41Xは、半導体チップ2と対向する領域よりも外側の領域において、隣接する配線パターン50B間を、左右方向及び上下方向に延在するように形成されている。

【0027】

半導体チップ2が搭載されている面と反対側(図1(a)では上側)の最外層の第4絶縁層41上には、埋込樹脂層51が積層されている。この埋込樹脂層51は、上記溝部41Xを充填するように形成されるとともに、配線パターン50Bの一部を覆うように形成されている。埋込樹脂層51の材料としては、例えば熱硬化性を有するエポキシ系樹脂にシリカやアルミナ等のフィラーを混入した樹脂材を用いることができる。また、埋込樹脂層51の材料としては、当該埋込樹脂層51の熱膨張係数が第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近づくように、エポキシ樹脂及びフィラーの含有量などが調整された絶縁性樹脂であることが好ましい。換言すると、埋込樹脂層51の材料としては、当該埋込樹脂層51の熱膨張係数が第1〜第3絶縁層11,21,31の熱膨張係数よりも低くなるように調整された絶縁性樹脂であることが好ましい。さらに、埋込樹脂層51の材料としては、当該埋込樹脂層51のガラス転移温度Tgが第1〜第3絶縁層11,21,31のガラス転移温度Tg(例えば150℃程度)よりも高い温度(例えば200℃程度)になるように調整された絶縁性樹脂であることが好ましい。具体的には、埋込樹脂層51の熱膨張係数は、ガラス転移温度Tg(ここでは、200℃)よりも低い場合には12ppm/℃程度、ガラス転移温度Tg以上の場合には40ppm/℃程度になるように設定されている。

【0028】

上記埋込樹脂層51には、第5配線層50の配線パターン50Bの一部を外部接続用パッド50Pとして露出させるための開口部51Xが形成されている。この外部接続用パッド50Pには、当該半導体パッケージ1をマザーボード等に実装する際に使用されるはんだボールやリードピン等の外部接続端子が接続されるようになっている。なお、必要に応じて、上記開口部51Xから露出する配線パターン50B上にOSP(Organic Solderbility Preservative)処理を施してOSP膜を形成し、そのOSP膜に上記外部接続端子を接続するようにしてもよい。また、上記開口部51Xから露出する配線パターン50B上に金属層を形成し、その金属層に上記外部接続端子を接続するようにしてもよい。金属層の例としては、Au層、Ni/Au層(Ni層とAu層をこの順番で積層した金属層)や、Ni/パラジウム(Pd)/Au層(Ni層とPd層とAu層をこの順番で積層した金属層)などを挙げることができる。なお、上記開口部51Xから露出する配線パターン50B(あるいは、配線パターン50B上にOSP膜や金属層が形成されている場合には、それらOSP膜又は金属層)自体を、外部接続端子としてもよい。

【0029】

このような構造を有する半導体パッケージ1の大きさは、例えば平面視で12×12mm程度とすることができる。また、半導体パッケージ1全体の厚さは、例えば300〜700μm程度とすることができる。

【0030】

(半導体装置の構造)

次に、半導体装置3の構造を図2に従って説明する。なお、図2において、半導体パッケージ1は図1(a)とは上下を反転して描かれている。

【0031】

半導体装置3は、上述した半導体パッケージ1と、その半導体パッケージ1に積層接合された半導体パッケージ4とを有している。

半導体パッケージ4は、配線基板60と、その配線基板60にフリップチップ実装された第1の半導体チップ71と、第1の半導体チップ71の上に接着された第2の半導体チップ72とを有している。また、半導体パッケージ4は、第1の半導体チップ71と配線基板60との隙間を充填するように設けられたアンダーフィル樹脂73と、第1の半導体チップ71及び第2の半導体チップ72等を封止する封止樹脂74とを有している。なお、第1の半導体チップ71の平面形状は、第2の半導体チップ72の平面形状よりも大きく形成されている。

【0032】

配線基板60は、基板本体61と、基板本体61の上面に形成されたチップ用パッド62及びボンディング用パッド63と、基板本体61の下面に形成された外部接続端子64とを有している。

【0033】

基板本体61は、図示は省略するが、複数の絶縁層と、複数の絶縁層に形成されたビア及び配線等から構成されている。基板本体61に設けられたビア及び配線は、チップ用パッド62、ボンディング用パッド63及び外部接続端子64を電気的に接続している。基板本体61としては、例えばコアレス基板や、コア基板を有するコア付きビルドアップ基板等を用いることができる。

【0034】

チップ用パッド62には、第1の半導体チップ71のバンプ71Aがフリップチップ接合されている。また、ボンディング用パッド63は、ボンディングワイヤ75を介して、第2の半導体チップ72の上面に形成された電極パッド(図示略)と電気的に接続されている。これらチップ用パッド62及びボンディング用パッド63の材料としては、例えば銅又は銅合金を用いることができる。また、チップ用パッド62及びボンディング用パッド63は、銅層の表面に金属層(例えば、Au層、Ni/Au層やNi/Pd/Au層など)を施して形成するようにしてもよい。

【0035】

外部接続端子64は、半導体パッケージ1,4間を接続するための接続端子(例えば、はんだボールやリードピン)である。それぞれの外部接続端子64は、上記半導体パッケージ1に配設されている接続パッド10Pの各々に対向するように設けられている。

【0036】

アンダーフィル樹脂73は、第1の半導体チップ71のバンプ71Aとチップ用パッド62との接続部分の接続強度を向上させるための樹脂であり、配線基板60の上面と第1の半導体チップ71の下面との隙間を充填するように設けられている。なお、アンダーフィル樹脂73の材料としては、例えばエポキシ系の絶縁性樹脂を用いることができる。

【0037】

封止樹脂74は、第1の半導体チップ71、第2の半導体チップ72、ボンディングワイヤ75及びボンディング用パッド63を封止するように基板本体61の上面に設けられている。この封止樹脂74の材料としては、例えばエポキシ系樹脂などの絶縁性樹脂を用いることができる。封止方法としては、例えばトランスファーモールド法を用いることができる。

【0038】

そして、半導体装置3では、半導体パッケージ4の下面に形成された外部接続端子64が、半導体パッケージ1の上面に形成された接続パッド10Pに接合されている。これにより、半導体パッケージ1と半導体パッケージ4とが積層接合され、POP(Package on Package)構造の半導体装置3が形成されている。

【0039】

ここで、従来の半導体パッケージの場合、つまり半導体パッケージ1の溝部41Xが形成されておらず、第4絶縁層41及び埋込樹脂層51の代わりに第2絶縁層21と同一組成の絶縁性樹脂からなる絶縁層が形成された半導体パッケージの反りについて説明する。このような半導体パッケージでは、例えば熱処理後の冷却の際に発生する収縮量は、半導体チップ2側ではその半導体チップ2の熱膨張係数、つまりシリコンの熱膨張係数に依存する。一方、従来の半導体パッケージの配線構造側では、例えば熱処理後の冷却の際に発生する収縮量は、配線構造の熱膨張係数、つまり第2絶縁層21等の各絶縁層の熱膨張係数に依存する。上述したように、シリコンの熱膨張係数が3.4ppm/℃であるのに対し、第2絶縁層21としてエポキシ系樹脂を用いる場合には、その熱膨張係数は、ガラス転移温度Tg(150℃)よりも低い場合に46ppm/℃、ガラス転移温度Tg以上で120ppm/℃となる。このように、従来の半導体パッケージの配線構造側の熱膨張係数は、半導体チップ2側の熱膨張係数と著しく異なる。これに起因して、例えば熱処理後の冷却の際に配線構造側に発生する収縮量が、半導体チップ2側に発生する収縮量と異なるため、半導体パッケージ1に反りが生じやすい。

【0040】

(作用)

これに対し、本実施形態の半導体パッケージ1では、最外層の層間絶縁層である第4絶縁層41及びその第4絶縁層41の下層に形成された第3絶縁層31に、その第4絶縁層41を厚さ方向に貫通する溝部41Xを形成するようにした。これにより、第3絶縁層31及び第4絶縁層41が溝部41Xによって複数の領域に分断される。このため、溝部41Xが形成されずに第3絶縁層31及び第4絶縁層41が広い領域にわたって一体的に形成された場合と比較して、第3絶縁層31及び第4絶縁層41が収縮することによって生じる応力を緩和することができる。この結果、半導体パッケージ1に生じる反りを低減することができる。

【0041】

さらに、半導体パッケージ1では、最外層の層間絶縁層である第4絶縁層41及び溝部41Xを充填する埋込樹脂層51の熱膨張係数を、第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近くなるように設定した。これにより、半導体パッケージ1の埋込樹脂層51側、つまり半導体チップ2と反対側の熱膨張係数を、半導体チップ2側の熱膨張係数に近づけることができる。したがって、例えば熱処理後の冷却の際に埋込樹脂層51側に発生する収縮量を、半導体チップ2側に発生する収縮量に近づけることができる。この結果、半導体パッケージ1に生じる反りを低減することができる。

【0042】

(半導体パッケージの製造方法)

次に、上記半導体パッケージ1の製造方法を説明する。

まず、半導体パッケージ1を製造するためには、図3(a)に示すように、支持基板80を用意する。この支持基板80としては、例えば金属板や金属箔を用いることができ、本実施形態では、例えば銅箔を用いる。この支持基板80の厚さは、例えば35〜200μm程度である。

【0043】

次に、図3(b)に示す工程では、支持基板80の一方の面80A(図中の上面)に、開口部81Xを有するレジスト層81を形成する。開口部81Xは、上記第1配線層10(図1参照)の形成領域に対応する部分の支持基板80の面80Aを露出するように形成される。レジスト層81の材料としては、感光性のドライフィルムレジスト又は液状のフォトレジスト(例えばノボラック系樹脂やアクリル系樹脂等のドライフィルムレジストや液状レジスト)等を用いることができる。例えば感光性のドライフィルムレジストを用いる場合には、支持基板80の面80Aにドライフィルムを熱圧着によりラミネートし、そのドライフィルムを露光・現像によりパターニングして、上記開口部81Xを持つレジスト層81を形成する。なお、液状のフォトレジストを用いる場合にも、同様の工程を経て、レジスト層81を形成することができる。

【0044】

続いて、図3(c)に示す工程では、上記レジスト層81をめっきマスクとして、支持基板80の面80Aに、該支持基板80をめっき給電層に利用する電解めっきを施す。具体的には、レジスト層81の開口部81Xから露出された支持基板80の面80Aに電解めっき法を施すことにより、開口部81X内に第1導電層10Aと第2導電層10Bとを順に積層して第1配線層10を形成する。例えば第1導電層10AがAu膜、Ni膜をこの順番で順次積層した構造であり、第2導電層10BがCu層である場合には、まず、支持基板80をめっき給電層に利用する電解めっき法により、Au膜、Ni膜を順に積層して第1導電層10Aを形成する。次いで、支持基板80をめっき給電層に利用する電解めっき法により、第1導電層10A上にCu層を形成して第2導電層10Bを形成する。その後、レジスト層81を除去する。

【0045】

次に、図3(d)に示す工程では、支持基板80の面80A上に半導体チップ2を固定する。具体的には、半導体チップ2の回路形成面2Aとは反対側の第2主面2Bが支持基板80の面80Aと対向するように、つまりフェイスアップの状態で半導体チップ2を支持基板80の面80A上に固定する。例えば半導体チップ2の第2主面2Bに予め粘着層(図示略)を形成しておき、フェイスアップの状態で支持基板80の面80A上に配置された半導体チップ2を加圧することにより、上記粘着層を介して支持基板80の面80A上に半導体チップ2を固定する。

【0046】

続いて、図3(e)に示す工程では、支持基板80の面80A上に、半導体チップ2及び第1配線層10を覆うように第1絶縁層11を形成する。なお、第1絶縁層11は、例えば支持基板80に樹脂フィルムをラミネートした後に、樹脂フィルムを押圧しながら130〜150℃程度の温度で熱処理して硬化させることにより形成することができる。

【0047】

次に、図4(a)に示す工程では、半導体チップ2の回路形成面2Aに形成された電極パッド2Pの上面が露出されるように、第1絶縁層11の所定箇所にビアホールVH1を形成する。また、第1配線層10の第2導電層10Bの上面が露出されるように、第1絶縁層11の所定箇所にビアホールVH2を形成する。これらビアホールVH1,VH2は、例えばCO2レーザ、YAGレーザ、エキシマレーザ等によるレーザ加工法によって形成することができる。なお、第1絶縁層11が感光性樹脂を用いて形成されている場合には、例えばフォトリソグラフィ法により所要のビアホールVH1,VH2を形成するようにしてもよい。

【0048】

続いて、ビアホールVH1,VH2をレーザ加工法によって形成した場合には、デスミア処理を行って、ビアホールVH1,VH2内の樹脂残渣(樹脂スミア)を除去する。このデスミア処理は、例えば過マンガン酸塩法などを用いて行うことができる。

【0049】

次いで、図4(b)に示す工程では、第1絶縁層11のビアホールVH1,VH2にビア導体を充填してビア配線20Aを形成するとともに、そのビア配線20Aを介して第1配線層10に電気的に接続される配線パターン20Bを第1絶縁層11上に形成する。これらビア配線20A及び配線パターン20B、つまり第2配線層20は、例えばセミアディティブ法やサブトラクティブ法などの各種の配線形成方法を用いて形成することができる。

【0050】

次に、図3(e)〜図4(b)に示した工程を繰り返すことにより、絶縁層と配線層とを交互に積層する。すなわち、図4(c)に示すように、第1絶縁層11及び第2配線層20上に第2絶縁層21を形成し、この第2絶縁層21に、配線パターン20Bの上面に達するビアホールVH3を形成する。その後、上記ビアホールVH3にビア配線30Aを形成するとともに、そのビア配線30Aに電気的に接続される配線パターン30Bを形成する。次に、第2絶縁層21及び第3配線層30上に第3絶縁層31を形成し、この第3絶縁層31にビアホールVH4を形成した後、そのビアホールVH4にビア配線40Aを形成するとともに、そのビア配線40Aに接続される配線パターン40Bを形成する。続いて、第3絶縁層31及び第4配線層40上に第4絶縁層41を形成し、この第4絶縁層41にビアホールVH5を形成した後、そのビアホールVH5にビア配線50Aを形成するとともに、そのビア配線50Aに接続される配線パターン50Bを形成する。

【0051】

次に、図5(a)に示す工程では、第3絶縁層31及び第4絶縁層41に、第4絶縁層41の面41A側(図中の上面側)から溝部41Xを形成する。この溝部41Xは、例えば例えばCO2レーザ、YAGレーザ、エキシマレーザ等によるレーザ加工法、プラズマエッチング(ドライエッチング)や、ブラスト処理などにより形成することができる。この溝部41Xの形成によって内部応力が解放される。このとき、半導体チップ2及び配線構造が支持基板80上に固定されているため、つまり溝部41Xの形成される面とは反対側に厚い支持基板80が形成されているため、上記応力解放に伴って生じるおそれのある反りを低減することができる。

【0052】

次に、図5(b)に示す工程では、溝部41Xを充填するとともに、第5配線層50を覆うように埋込樹脂層51を第4絶縁層41の面41A上に形成する。この埋込樹脂層51は、例えば感光性のレジストフィルムをラミネートし、又は液状レジストを塗布することにより形成することができる。

【0053】

続いて、図6(a)に示す工程では、第5配線層50の配線パターン50Bの上面が露出されるように、埋込樹脂層51の所要箇所に開口部51Xを形成する。この開口部51Xは、例えばCO2レーザ、YAGレーザ、エキシマレーザ等によるレーザ加工法によって形成することができる。なお、埋込樹脂層51が感光性樹脂を用いて形成されている場合には、例えばフォトリソグラフィ法により所要の開口部51Xを形成するようにしてもよい。これにより、埋込樹脂層51の開口部51Xから第5配線層50の一部が外部接続用パッド50Pとして露出される。なお、必要に応じて、外部接続用パッド50P上に、例えばNi層とAu層をこの順番で積層した金属層を形成するようにしてもよい。この金属層は、例えば無電解めっき法により形成することができる。

【0054】

次いで、図6(b)に示す工程では、仮基板として用いた支持基板(図6(a)参照)を除去する。例えば支持基板80として銅箔を用いる場合には、塩化第二鉄水溶液、塩化第二銅水溶液、過硫酸アンモニウム水溶液等を用いたウェットエッチングにより、支持基板80の除去を行うことができる。この際、第1絶縁層11から露出する半導体チップ2がシリコンからなり、第1配線層10の最表層がAu膜等であるため、銅箔である支持基板80のみを選択的にエッチングすることができる。但し、第5配線層50が銅層である場合には、開口部51Xの底部に露出する第5配線層50が支持基板80とともにエッチングされることを防止するため、第5配線層50をマスクして上記ウェットエッチングを行う必要がある。

【0055】

このとき、第3絶縁層31及び第4絶縁層41に溝部41Xが形成され、その溝部41Xには半導体チップ2の熱膨張係数に近い熱膨張係数を有する埋込樹脂層51が充填されている。このため、第3絶縁層31及び第4絶縁層41が複数の領域に分断されており、埋込樹脂層51側の熱膨張係数が半導体チップ2側の熱膨張係数に近い値になっている。これにより、支持基板80の除去に伴う応力解放によって生じうる半導体パッケージ1の反りを低減することができる。したがって、半導体パッケージ1が平坦な状態に保持される。

【0056】

以上の製造工程により、本実施形態の半導体パッケージ1を製造することができる。

(半導体装置の製造方法)

次に、図7(a)に示すように、半導体パッケージ4を用意する。ここでは、図示を省略して詳細な説明を割愛するが、半導体パッケージ4は例えば以下のような方法で製造される。すなわち、チップ用パッド62、ボンディング用パッド63及び外部接続端子64を有する配線基板60を形成し、その配線基板60の上面に形成されたチップ用パッド62に第1の半導体チップ71のバンプ71Aをフリップチップ接合する。続いて、配線基板60と第1の半導体チップ71との間にアンダーフィル樹脂73を形成した後、第1の半導体チップ71の上に第2の半導体チップ72を接着剤により接着する。次いで、第2の半導体チップ72の上面に形成された電極パッド(図示略)と配線基板60の上面に形成されたボンディング用パッド63との間をボンディングワイヤ75によりワイヤボンディング接続した後、第1及び第2の半導体チップ71,72及びボンディングワイヤ75等を封止樹脂74で樹脂封止する。

【0057】

続いて、半導体パッケージ1の各接続パッド10Pに、半導体パッケージ4の外部接続端子64が対向するように、半導体パッケージ1,4を位置合わせする。このとき、半導体パッケージ4の外部接続端子64には図示しないフラックスが転写されている。

【0058】

次いで、図7(b)に示す工程では、上述のように位置合わせされて半導体パッケージ4が半導体パッケージ1上に載置されると、その構造体がリフロー炉(図示略)に搬送される。そして、このリフロー炉内では外部接続端子64(ここでは、はんだボール)がリフローされ、接続パッド10P部分で半導体パッケージ1,4が接合される。これにより、POP構造の半導体装置3が製造される。

【0059】

このとき、半導体パッケージ1が平坦な状態に保持されているため、その半導体パッケージ1に半導体パッケージ4を容易に積層接合させることができる。

以上説明した本実施形態によれば、以下の効果を奏することができる。

【0060】

(1)最外層の層間絶縁層である第4絶縁層41及びその第4絶縁層41の下層に形成された第3絶縁層31に、その第4絶縁層41を厚さ方向に貫通する溝部41Xを形成するようにした。これにより、第3絶縁層31及び第4絶縁層41が収縮することによって生じる応力を緩和することができ、半導体パッケージ1に生じる反りを低減することができる。この結果、半導体パッケージ1を平坦な状態に保持することができる。

【0061】

(2)溝部41Xに充填され、半導体チップ2と反対側に形成される埋込樹脂層51の熱膨張係数を、第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近くなるように設定した。これにより、例えば熱処理後の冷却の際に埋込樹脂層51側に発生する収縮量を、半導体チップ2側に発生する収縮量に近づけることができ、半導体パッケージ1に生じる反りを低減することができる。

【0062】

(3)最外層の層間絶縁層である第4絶縁層41の熱膨張係数を、第1〜第3絶縁層11,21,31の熱膨張係数よりも半導体チップ2の熱膨張係数に近くなるように設定した。これにより、例えば熱処理後の冷却の際に埋込樹脂層51側に発生する収縮量を、半導体チップ2側に発生する収縮量に近づけることができ、半導体パッケージ1に生じる反りを低減することができる。

【0063】

(4)ところで、図6(b)に示した工程において、支持基板80を除去すると、埋込樹脂層51側の熱膨張係数と半導体チップ2側の熱膨張係数の違いに起因して反りが生じうる。このとき、埋込樹脂層51側の収縮量が半導体チップ2側の収縮量よりも大きくなるため、埋込樹脂層51側が凹状に反る傾向にある。

【0064】

これに対し、本実施形態の半導体パッケージ1では、最外層の第4絶縁層41、つまり反りの生じやすい側に形成された第4絶縁層41を補強材入りの絶縁層とした。これにより、第4絶縁層41の剛性を高めることができるため、半導体パッケージ1の反りを効果的に抑制することができる。すなわち、支持基板80を除去したときに半導体パッケージ1が反った場合に、凹状となる埋込樹脂層51側に形成された第4絶縁層41の剛性を高めることにより、半導体パッケージ1を反らす応力に効果的に対抗でき、半導体パッケージ1の反りを低減できる効果が大きい。

【0065】

(5)溝部41Xを、半導体チップ2と対向する領域よりも外側の領域に形成するようにした。ここで、半導体パッケージ1の外周部に近づくほど反り量は大きくなる傾向にある。このため、上記溝部41Xによって半導体パッケージ1の反りを効果的に低減することができる。

【0066】

(6)支持基板80の存在する状態で、溝部41Xを形成するようにした。これにより、溝部41Xの形成による応力解放に伴って生じるおそれのある反りを低減することができる。

【0067】

(7)溝部41Xの平面形状を、加工の容易な格子状に形成するようにした。このため、溝部41Xを容易に形成することができる。

(8)溝部41Xの断面形状を略楔状に形成するようにした。これにより、第4絶縁層41及び第3絶縁層31を複数の領域に確実に分断することができる。このため、第3絶縁層31及び第4絶縁層41が収縮することによって生じる応力を効果的に緩和することができ、半導体パッケージ1に生じる反りを低減することができる。

【0068】

(他の実施形態)

なお、上記実施形態は、これを適宜変更した以下の態様にて実施することもできる。

・図8に示されるように、上記実施形態における埋込樹脂層51を省略するようにしてもよい。このような構造であっても、上記実施形態の(1)、(3)〜(8)と同様の効果を奏することができる。

【0069】

・図9に示されるように、上記実施形態における第4絶縁層41を、第1〜第3絶縁層11,21,31と同一組成の絶縁性樹脂からなる第4絶縁層41Bに変更するようにしてもよい。

【0070】

・上記実施形態における溝部41Xの形状(断面形状及び平面形状)は特に限定されない。

例えば上記実施形態では、第3絶縁層31及び第4絶縁層41の2層分の層間絶縁層に溝部41Xを形成するようにしたが、図10(a)に示されるように、3層以上の層間絶縁層に溝部41Xを形成するようにしてもよい。図10(a)に示した変形例では、溝部41Xは、第4絶縁層41の面41Aから第4絶縁層41及び第3絶縁層31を厚さ方向に貫通して、第2絶縁層21の厚さ方向の中途位置まで形成されている。このように溝部41Xが深く形成されると、その溝部41Xによって分断される層間絶縁層の数が増加するため、効果的に反りを抑制することができる。

【0071】

また、上記実施形態では、溝部41Xの断面形状を略楔状に形成するようにしたが、例えば図10(b)に示されるように、溝部41Xの断面形状を四角形状に形成するようにしてもよい。また、溝部41Xの断面形状を、台形状、U字状や半円状に形成するようにしてもよい。

【0072】

また、上記実施形態では、溝部41Xの平面形状を格子状に形成するようにした。これに限らず、例えば図11(a)に示されるように、溝部41Xの平面形状を略枠状に形成するようにしてもよい。なお、図11(a)に示した変形例では、平面視略枠状の溝部41Xが2つ形成されているが、この溝部41Xの数は1つであってもよく、3つ以上であってもよい。

【0073】

また、図11(b)に示されるように、溝部41Xの平面形状を略L字状に形成するようにしてもよい。図11(b)に示した変形例では、平面視略L字状の溝部41Xが半導体パッケージ1の四隅に形成されている。なお、図11(b)に示した変形例では、各角部に2つの溝部41Xが形成されているが、この各角部に形成される溝部41Xの数は1つであってもよく、3つ以上であってもよい。

【0074】

・上記実施形態では、半導体チップ2と対向する領域よりも外側の領域に溝部41Xを形成するようにした。これに限らず、半導体チップ2と対向する領域にも溝部41Xを形成するようにしてもよい。

【0075】

・図12に示されるように、上記実施形態における第1配線層10(接続パッド10P)を省略するようにしてもよい。この場合の半導体パッケージ1Bでは、第1配線層10の上面を露出するビアホールVH2及びそのビアホールVH2に形成されるビア配線20Aも省略される。

【0076】

・上記実施形態では、支持基板80上に1つの半導体パッケージ1を作製する例を示したが、支持基板80上に半導体パッケージ1となる部材を作製し、それを個片化して複数の半導体パッケージ1を得るような工程に変更してもよい。

【0077】

・上記実施形態の半導体パッケージ1の製造方法では、支持基板80の片側に半導体チップ2を固定するとともに、主にビルドアップ工法により支持基板80の片側に配線層及び絶縁層を積層し、最後に支持基板80を除去して半導体パッケージ1を製造するようにした。これに限らず、例えば支持基板80の両側にそれぞれ半導体チップ2を固定するとともに、主にビルドアップ工法により支持基板80の両側それぞれに配線層及び絶縁層を積層し、最後に支持基板80を除去して複数の半導体パッケージ1を製造するようにしてもよい。

【0078】

・上記実施形態における半導体パッケージ1の層の数や配線の取り回しなどは様々に変形・変更することが可能である。

・上記実施形態における半導体パッケージ4の配線基板60に実装される半導体チップの数や、その半導体チップの実装の形態(例えばフリップチップ実装、ワイヤボンディングによる実装、又はこれらの組み合わせ)などは様々に変形・変更することが可能である。

【0079】

[実施例]

次に、実施例及び比較例を挙げて上記実施形態及びその変形例をさらに具体的に説明する。

【0080】

ここでは、溝部41Xを設けた半導体パッケージ(実施例1,2)と、溝部41Xを設けていない半導体パッケージ(比較例1,2)の各々について反りのシミュレーションを行った。

【0081】

(実施例1)

実施例1の半導体パッケージは、図1(a)に示した半導体パッケージ1である。シミュレーション条件としては、半導体パッケージ1の平面形状を12mm×12mmの正方形状とし、半導体チップ2の平面形状を9mm×9mmの正方形状とし、半導体チップ2の厚さを100μmとした。また、半導体パッケージ1全体の厚さを550μmとした。具体的には、第2〜第5配線層20,30,40,50の厚さをそれぞれ15μmとし、第1絶縁層11の厚さを180μm、第2及び第3絶縁層21,31の厚さを30μm、第4絶縁層41の厚さを100μm、埋込樹脂層51の厚さを50μmとした。なお、溝部41XはCO2レーザによるレーザ加工により形成し、その溝部41Xの深さを120μmとした。

【0082】

(実施例2)

実施例2の半導体パッケージは、図8に示した半導体パッケージ1Aであり、実施例1の半導体パッケージから埋込樹脂層51を除去した構造を有している。シミュレーション条件としては、上記半導体パッケージ1Aを厚さ200μmの支持基板80に固定した状態で反りを測定する点のみが上記実施例1と異なる。

【0083】

(比較例1)

比較例1の半導体パッケージは、図13に示される半導体パッケージ5である。この半導体パッケージ5は、溝部41X(図1(a)参照)が形成されていない点を除き、実施例1の半導体パッケージ1と同一の構造を有する。なお、シミュレーション条件については、実施例1と同一の条件である。

【0084】

(比較例2)

比較例2の半導体パッケージは、図14に示される半導体パッケージ6である。この半導体パッケージ6は、溝部41X(図8参照)が形成されていない点を除き、実施例2の半導体パッケージ1Aと同一の構造を有する。なお、シミュレーション条件については、実施例2と同一の条件である。

【0085】

(測定方法)

各例の半導体パッケージを190℃の環境下に置いて応力を解放後、温度を25℃に下げたときの反りを測定した。反りは、各半導体パッケージの半導体チップ2の搭載されたチップ搭載面11Aとは反対側の面の高さを対角線に沿って順次測定し、最も高い点と最も低い点との高さの差を測定した。なお、チップ搭載面11Aとは反対側の面が凸状に沿った場合の反り量をプラスとし、チップ搭載面とは反対側の面が凹状に沿った場合の反り量をマイナスとして、図15にシミュレーション結果を示した。

【0086】

(シミュレーション結果)

図15に示すように、実施例1と比較例1、及び、実施例2と比較例2をそれぞれ比較すると、溝部41Xを設けることにより(実施例1,2)、溝部41Xを設けない場合(比較例1,2)に比べ、半導体パッケージの反り量を大幅に低減できることが確認された。すなわち、溝部41Xの形成によって、高い反り改善効果が得られることが確認された。

【符号の説明】

【0087】

1,1A,1B 半導体パッケージ(第1半導体パッケージ)

2 半導体チップ

4 半導体パッケージ(他の半導体パッケージ又は第2半導体パッケージ)

10 第1配線層

10P 接続パッド(パッド)

11 第1絶縁層

20,30,40,50 配線層

21 第2絶縁層(層間絶縁層)

31 第3絶縁層(層間絶縁層)

41 第4絶縁層(最外層の層間絶縁層)

41X 溝部

51 埋込樹脂層

80 支持基板

【特許請求の範囲】

【請求項1】

半導体チップと、

前記半導体チップを覆うように形成された第1絶縁層と、

前記第1絶縁層上に積層され、前記半導体チップと電気的に接続された配線層と該配線層上に積層される層間絶縁層とが交互に積層されてなる配線構造と、を有し、

前記半導体チップの搭載面とは反対側の最外層の前記層間絶縁層には、該最外層の層間絶縁層を厚さ方向に貫通する溝部が形成されていることを特徴とする半導体パッケージ。

【請求項2】

前記溝部に充填されるとともに、前記最外層の層間絶縁層上に形成された埋込樹脂層を有し、

前記埋込樹脂層は、前記層間絶縁層の熱膨張係数よりも前記半導体チップの熱膨張係数に近い熱膨張係数を有することを特徴とする請求項1に記載の半導体パッケージ。

【請求項3】

前記溝部は、前記最外層の層間絶縁層の下層に形成された層間絶縁層の厚さ方向の中途位置まで形成されていることを特徴とする請求項1又は2に記載の半導体パッケージ。

【請求項4】

前記溝部は、前記最外層の層間絶縁層の下層に形成された層間絶縁層を厚さ方向に貫通するように形成されていることを特徴とする請求項1又は2に記載の半導体パッケージ。

【請求項5】

前記溝部は、前記半導体チップと対向する領域よりも外側の領域に形成されていることを特徴とする請求項1〜4のいずれか1つに記載の半導体パッケージ。

【請求項6】

前記溝部は、断面視して楔状に形成されていることを特徴とする請求項1〜5のいずれか1つに記載の半導体パッケージ。

【請求項7】

前記最外層の層間絶縁層は、補強材入りの樹脂材からなり、他の前記層間絶縁層の熱膨張係数よりも前記半導体チップの熱膨張係数に近い熱膨張係数を有する絶縁層であることを特徴とする請求項1〜6のいずれか1つに記載の半導体パッケージ。

【請求項8】

前記半導体チップと同一平面上に、他の半導体パッケージと接続されるパッドが形成されていることを特徴とする請求項1〜7のいずれか1つに記載の半導体パッケージ。

【請求項9】

支持基板上に半導体チップを固定する工程と、

前記半導体チップが固定された前記支持基板上に、前記半導体チップを覆うように第1絶縁層を形成する工程と、

前記第1絶縁層上に、前記半導体チップと電気的に接続するように配線層と該配線層上に積層される層間絶縁層とを交互に積層する工程と、

前記層間絶縁層のうち最後に積層した最外層の層間絶縁層に、該最外層の層間絶縁層を厚さ方向に貫通する溝部を形成する工程と、

前記支持基板を除去する工程と、

を有することを特徴とする半導体パッケージの製造方法。

【請求項10】

前記溝部を形成した後に、前記最外層の層間絶縁層上に、前記溝部を充填するように埋込樹脂層を形成する工程を有し、

前記埋込樹脂層は、前記層間絶縁層の熱膨張係数よりも前記半導体チップの熱膨張係数に近い熱膨張係数を有することを特徴とする請求項9に記載の半導体パッケージの製造方法。

【請求項11】

前記溝部を形成する工程では、前記最外層の層間絶縁層の下層に形成された層間絶縁層の厚さ方向の中途位置まで前記溝部を形成することを特徴とする請求項9又は10に記載の半導体パッケージの製造方法。

【請求項12】

前記支持基板上に前記半導体チップを固定する工程の前に、前記支持基板上に他の半導体パッケージと接続されるパッドを形成する工程を有することを特徴とする請求項9〜11のいずれか1項に記載の半導体パッケージの製造方法。

【請求項13】

半導体チップと、

前記半導体チップを覆うように形成された第1絶縁層と、

前記第1絶縁層上に積層され、前記半導体チップと電気的に接続された配線層と該配線層上に積層される層間絶縁層とが交互に積層されてなる配線構造と、

前記半導体チップの搭載面とは反対側の最外層の前記層間絶縁層を厚さ方向に貫通する溝部と、

前記半導体チップと同一平面上に形成されたパッドと、を有する第1半導体パッケージと、

前記パッドと電気的に接続され、前記第1半導体パッケージ上に積層される第2半導体パッケージと、

を有することを特徴とする半導体装置。

【請求項1】

半導体チップと、

前記半導体チップを覆うように形成された第1絶縁層と、

前記第1絶縁層上に積層され、前記半導体チップと電気的に接続された配線層と該配線層上に積層される層間絶縁層とが交互に積層されてなる配線構造と、を有し、

前記半導体チップの搭載面とは反対側の最外層の前記層間絶縁層には、該最外層の層間絶縁層を厚さ方向に貫通する溝部が形成されていることを特徴とする半導体パッケージ。

【請求項2】

前記溝部に充填されるとともに、前記最外層の層間絶縁層上に形成された埋込樹脂層を有し、

前記埋込樹脂層は、前記層間絶縁層の熱膨張係数よりも前記半導体チップの熱膨張係数に近い熱膨張係数を有することを特徴とする請求項1に記載の半導体パッケージ。

【請求項3】

前記溝部は、前記最外層の層間絶縁層の下層に形成された層間絶縁層の厚さ方向の中途位置まで形成されていることを特徴とする請求項1又は2に記載の半導体パッケージ。

【請求項4】

前記溝部は、前記最外層の層間絶縁層の下層に形成された層間絶縁層を厚さ方向に貫通するように形成されていることを特徴とする請求項1又は2に記載の半導体パッケージ。

【請求項5】

前記溝部は、前記半導体チップと対向する領域よりも外側の領域に形成されていることを特徴とする請求項1〜4のいずれか1つに記載の半導体パッケージ。

【請求項6】

前記溝部は、断面視して楔状に形成されていることを特徴とする請求項1〜5のいずれか1つに記載の半導体パッケージ。

【請求項7】

前記最外層の層間絶縁層は、補強材入りの樹脂材からなり、他の前記層間絶縁層の熱膨張係数よりも前記半導体チップの熱膨張係数に近い熱膨張係数を有する絶縁層であることを特徴とする請求項1〜6のいずれか1つに記載の半導体パッケージ。

【請求項8】

前記半導体チップと同一平面上に、他の半導体パッケージと接続されるパッドが形成されていることを特徴とする請求項1〜7のいずれか1つに記載の半導体パッケージ。

【請求項9】

支持基板上に半導体チップを固定する工程と、

前記半導体チップが固定された前記支持基板上に、前記半導体チップを覆うように第1絶縁層を形成する工程と、

前記第1絶縁層上に、前記半導体チップと電気的に接続するように配線層と該配線層上に積層される層間絶縁層とを交互に積層する工程と、

前記層間絶縁層のうち最後に積層した最外層の層間絶縁層に、該最外層の層間絶縁層を厚さ方向に貫通する溝部を形成する工程と、

前記支持基板を除去する工程と、

を有することを特徴とする半導体パッケージの製造方法。

【請求項10】

前記溝部を形成した後に、前記最外層の層間絶縁層上に、前記溝部を充填するように埋込樹脂層を形成する工程を有し、

前記埋込樹脂層は、前記層間絶縁層の熱膨張係数よりも前記半導体チップの熱膨張係数に近い熱膨張係数を有することを特徴とする請求項9に記載の半導体パッケージの製造方法。

【請求項11】

前記溝部を形成する工程では、前記最外層の層間絶縁層の下層に形成された層間絶縁層の厚さ方向の中途位置まで前記溝部を形成することを特徴とする請求項9又は10に記載の半導体パッケージの製造方法。

【請求項12】

前記支持基板上に前記半導体チップを固定する工程の前に、前記支持基板上に他の半導体パッケージと接続されるパッドを形成する工程を有することを特徴とする請求項9〜11のいずれか1項に記載の半導体パッケージの製造方法。

【請求項13】

半導体チップと、

前記半導体チップを覆うように形成された第1絶縁層と、

前記第1絶縁層上に積層され、前記半導体チップと電気的に接続された配線層と該配線層上に積層される層間絶縁層とが交互に積層されてなる配線構造と、

前記半導体チップの搭載面とは反対側の最外層の前記層間絶縁層を厚さ方向に貫通する溝部と、

前記半導体チップと同一平面上に形成されたパッドと、を有する第1半導体パッケージと、

前記パッドと電気的に接続され、前記第1半導体パッケージ上に積層される第2半導体パッケージと、

を有することを特徴とする半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−105840(P2013−105840A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−247666(P2011−247666)

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月11日(2011.11.11)

【出願人】(000190688)新光電気工業株式会社 (1,516)

【Fターム(参考)】

[ Back to top ]