半導体パッケージ、及びこれを用いた表示装置

【課題】半導体パッケージ及びこれを用いた表示装置において、ICチップの入力端子と出力端子数が異なる場合、インターポーザ基板を必要以上に大型化させることなく、接続端子及び配線を配置することを可能とするテープキャリア型半導体パッケージを提供する。

【解決手段】半導体チップ2が、インターポーザ基板3を介してフィルム基板4に接続される半導体パッケージにおいて、半導体チップは、対向する2辺に、複数の端子6,7をそれぞれ有し、さらに、インターポーザ基板において、インターポーザ基板の中心より、2辺のうち端子数が少ない一方の側にずれて接続されていることを特徴とする。

【解決手段】半導体チップ2が、インターポーザ基板3を介してフィルム基板4に接続される半導体パッケージにおいて、半導体チップは、対向する2辺に、複数の端子6,7をそれぞれ有し、さらに、インターポーザ基板において、インターポーザ基板の中心より、2辺のうち端子数が少ない一方の側にずれて接続されていることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体パッケージ及びこれを用いた表示装置に関する。特にインターポーザ基板を介して、ICチップとフィルム基板とを接続するテープキャリア型半導体パッケージ及びこれを用いた表示装置に関する。

【背景技術】

【0002】

近年、半導体装置が搭載される電子機器の高機能化に伴い、半導体装置の小型化及び集積化が図られ、様々なタイプの半導体パッケージが開発されている。そのパッケージの一つとして、TCP(Tape Carrier Package)あるいはCOF(Chip On Film)と呼ばれるテープキャリア型の半導体パッケージが提案されている。

【0003】

TCP半導体パッケージは、フィルム基材上に銅箔等の金属パターンにより形成されたリードを有するパッケージであり、フィルム基材に形成された貫通孔(デバイスホール)からリード先端が突出して形成されたフライングリードに、ICチップがフリップチップ接続されて実装される。フィルム基材が柔軟性を有するため折り曲げが可能であり、また多端子ファインピッチ化が可能であるとともに、既存のフリップチップボンディング技術で対応可能なことから、液晶表示装置に代表される薄型表示装置のドライバIC用パッケージとして多用されてきた。

【0004】

COF半導体パッケージは、従来のTCP半導体パッケージのようなフライングリードを持たず、リードがフィルム基材により支持された構造を持つ。このため、より薄い配線材(銅箔)を用いることができるので、さらにファインピッチのリード形成を可能とするパッケージ技術であり、半導体パッケージの小型化及び集積化の要求により、近年多く利用されるようになってきている。

【0005】

また、COF半導体パッケージの一つの形態として、図8に示したような、インターポーザ基板(中間基板)を有するCOF半導体パッケージがある(特許文献1参照)。この形態のCOF半導体パッケージ31は、1つの半導体パッケージの中に中間基板33(インターポーザ基板)を内蔵させ、パッケージ内部でICチップ32とインターポーザ基板33との接続を行うことにより、半導体素子を高密度に実装することが可能である。

【0006】

また、半導体パッケージは、例えば液晶表示装置のような、搭載される電子機器の高性能化に伴うICチップの入出力端子の多ピン化によって、さらなるファインピッチ化が求められる傾向にある。

【特許文献1】特開2004−207566号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

上記のようなインターポーザ基板を有するテープキャリア型半導体パッケージでは、インターポーザ基板上に接続端子及び配線を設けるが、接続端子数の増加により、インターポーザ基板の大型化に伴う半導体パッケージの大型化が避けられないという問題があった。

【0008】

さらに、インターポーザ基板は、例えばシリコン等の半導体材料で形成されるため、インターポーザ基板の大型化によるコスト増加が避けられないという問題があった。

【0009】

特に、ICチップの入力端子数と出力端子数が異なる場合においては、インターポーザ基板の端子数が少ない側のインターポーザ基板のスペースは、端子数が多い側のインターポーザ基板のスペースに対して、不必要に大きく、半導体パッケージを大型化させる要因となっていた。

【0010】

そこで、インターポーザ基板を必要以上に大型化させることなく、接続端子及び配線を配置することを可能とするテープキャリア型半導体パッケージを提供することを目的とする。

【0011】

特に、ICチップの入力端子数と出力端子数が異なる場合において、インターポーザ基板を必要以上に大型化させることなく、接続端子及び配線を配置することを可能とするテープキャリア型半導体パッケージを提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明の第1の局面に係る半導体パッケージは、半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、半導体チップの中心位置とインターポーザ基板の中心位置が異なることを特徴とする。

【0013】

本発明の第2の局面に係る半導体パッケージは、半導体チップがインターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、半導体チップは少なくとも対向する2辺に複数の端子をそれぞれ有し、さらに、インターポーザ基板において、インターポーザ基板の中心より、対向する2辺のうち端子数が少ない一方の側にずれて接続されていることを特徴とする。なお、対向する2辺以外の辺にも端子を配置してもよい。

【0014】

本発明の第3の局面に係る半導体パッケージは、半導体チップがインターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、半導体チップは少なくとも対向する2辺に複数の端子をそれぞれ有し、インターポーザ基板はすくなくとも対向する2辺にフィルム基板に接続されるフィルム基板接続端子をそれぞれ有し、さらに、フィルム基板接続端子の内側に、半導体チップの対向する2辺に配置された複数の端子と接続される半導体チップ接続端子を複数有し、インターポーザ基板の対向する2辺それぞれにおける、フィルム基板接続端子と半導体チップ接続端子との距離は、半導体チップ接続端子の端子数の少ない方において、もう一方よりも短いことを特徴とする。

【0015】

本発明の第4の局面に係る半導体パッケージは、半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、半導体チップは、少なくとも対向する2辺に複数の端子をそれぞれ有し、フィルム基板はデバイスホールを有するとともに、半導体チップはデバイスホール内に位置し、さらにデバイスホールの対向する2辺それぞれにおける、半導体チップ端面とデバイスホール端面との距離は、前記半導体チップの対向する2辺のうち端子数の少ない方において、もう一方よりも短いことを特徴とする。

【0016】

本発明の半導体パッケージは、さらに、半導体チップの対向する2辺のうちの一方の辺には半導体チップへの入力信号端子が配置され、他方の辺には半導体チップからの出力信号端子が配置されていることを特徴とする。

【0017】

本発明の半導体パッケージは、さらに、出力信号端子の端子数は、入力信号端子の端子数より多いことを特徴とする。

【0018】

本発明の半導体パッケージは、さらに、インターポーザ基板は、シリコンからなることを特徴とする。

【0019】

本発明の半導体パッケージは、さらに、半導体チップが、液晶ドライバであることを特徴とする。

【0020】

本発明の表示装置は、上記の何れかの半導体パッケージを備えたことを特徴とする。

【発明の効果】

【0021】

本発明の半導体パッケージによれば、インターポーザ基板を必要以上に大型化させることなく、接続端子及び配線を配置することが可能となる。

【0022】

また、インターポーザ基板に用いられる高価なシリコン等の半導体材料の量を抑えることができ、コスト増加を抑えることが可能となる。

【発明を実施するための最良の形態】

【0023】

以下、本発明の実施の形態について図を参照して説明する。なお、ここでは、本発明の半導体パッケージを採用した液晶ドライバパッケージを例示して説明を行う。

【0024】

(実施の形態1)

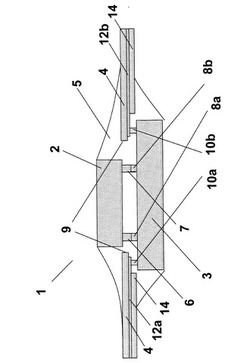

図1は、本発明の実施の形態1に係る液晶ドライバパッケージの平面図である。図2は、図1に示した液晶ドライバパッケージを切断面線A−A´から見た断面図である。さらに図3は、液晶ドライバ2とインターポーザ基板3の接続を説明するための図である。以下、図1、図2及び図3を参照して、液晶ドライバパッケージの概略構成について説明を行う。

【0025】

本実施形態の液晶ドライバパッケージ1は、COF(Chip On Film)半導体パッケージであり、少なくとも液晶ドライバ2(半導体チップ)とインターポーザ基板3とフィルム基板4を有し、液晶ドライバ2はインターポーザ基板3を介してフィルム基板4に接続されている。また、液晶ドライバ2、インターポーザ基板3及びフィルム基板4の間には、封止樹脂5が充填され、それぞれの間の接続部が補強・固定されている。ここで、封止樹脂5は、一般にアンダーフィル材と呼ばれ、絶縁性の樹脂(例えば、エポキシ樹脂、シリコーン樹脂、ポリイミド樹脂等)が用いられる。

【0026】

液晶ドライバ2は、少なくとも1つ以上の液晶駆動回路(不図示)を備えており、液晶表示装置を駆動する。そのため、液晶ドライバには、インターポーザ基板と対向する面(以下、下面と記す)に、画像データ信号等を入力するための画像信号入力用接続端子6と、液晶駆動信号を出力するための駆動信号出力用接続端子7とが設けられている。液晶駆動回路の数は、搭載される液晶表示装置によって異なり、限定されるものではない。

【0027】

インターポーザ基板3は、半導体材料、好ましくはシリコンから構成される。インターポーザ基板3上には、液晶ドライバ2の下面に設けられた画像信号入力用接続端子6及び駆動信号出力用接続端子7とフリップチップ実装するための液晶ドライバ接続端子8a(入力側)・8b(出力側)が形成されている。さらに、液晶ドライバ接続端子8a・8bが設けられている面と同一面内に、液晶ドライバ接続端子8a・8bから配線11が設けられており、その配線11の先端部13上にフィルム基板接続端子10a・10bを介してフィルム基板4と接続されている。

【0028】

フィルム基板4は、液晶ドライバ2を収めるデバイスホール9を有し、デバイスホール9周辺部にインターポーザ基板3のフィルム基板接続端子10a(入力側)・10b(出力側)との接続端子が設けられている。接続端子ピッチは、インターポーザ基板3の配線先端部13上のフィルム基板接続端子ピッチ(35μm以上)と対応しており、インターポーザ基板3と接続可能となっている。

【0029】

フィルム基板4には、インターポーザ基板3のフィルム基板接続端子10a・10bから液晶表示装置(不図示)と接続されるための配線12b、及び画像入力制御部(不図示)と接続されるための配線12aが設けられている。さらに、フィルム基板4上には、インターポーザ基板3との接続部を除いて、絶縁性のソルダーレジスト14(熱性コーティング材)が設けられ、フィルム基板4に設けられている配線をほこりや水から保護し、ショート等の欠陥が起こり難い構成となっている。

【0030】

また、フィルム基板4上の配線12a・12bは好ましくは銅箔であり、蒸着、エッチングまたは印刷等の方法により、配線パターンが形成される。特に、配線を銅箔に限らない場合、印刷による形成が簡易であり好適である。さらに、フィルム基板4には、曲げ加工し易いように、ポリイミド(PI)やポリエチレンテレフタレート(PET)等の有機フィルムなどの可撓性が高い素材が用いられる。

【0031】

次に、液晶ドライバ2とインターポーザ基板3の接続及びインターポーザ基板3とフィルム基板4の接続について、図3を参照してさらに詳しく説明する。

【0032】

ここで、インターポーザ基板3に設けられた液晶ドライバ接続端子8a・8bから伸びる配線11は、フィルム基板4に接続される先端部13に近づくに従って、その配線間隔は広がっている。具体的に示すと、液晶ドライバ接続端子8bのピッチは25μm以下であるが、配線11の先端部13のピッチは35μm以上にすることも可能である。このように、インターポーザ基板3を仲介することによって、ICプロセスレベルのファインピッチをフィルム基板レベルの電極ピッチに変換することが可能となる。従って、フィルム基板のフィルム及び配線について、従来の材料を用いることでき、また、その実装方法に関しても、既存の技術が適用可能である。

【0033】

液晶ドライバ2とインターポーザ基板3の接続には、ファインピッチに対応するため、比較的硬く且つ融点の高い金属または合金製バンプが用いられる。例えば、金(Au)バンプを用いたAu−Au接合を適用することができる。これにより、バンプの変形が抑えられ、隣り合うバンプ間での接触の問題を解決できるので、25μm程度まで端子ピッチを縮小することが可能となり、液晶ドライバの多出力化を可能にしている。

【0034】

一方、インターポーザ基板3とフィルム基板(不図示)の接続は、液晶ドライバ2との接続端子より広いピッチ、例えば35〜100μm程度のピッチを持つ端子間の接続とすることができる。接続はインターポーザ基板3の配線11の先端部13のフィルム基板接続端子10a・10bのAuバンプとフィルム基板4上の配線12a・12bの先端部に施されたスズとの金−スズ共晶接続で行う。また、Auバンプのような高価な接続電極を形成せず、異方性導電フィルム(ACF:Anisotropic Conductive Film)あるいは異方性導電ペースト(ACP:Anisotropic Conductive Paste)を用いた一括ボンディングを適用することも可能である。

【0035】

また、このようなACF/ACPボンディングを採用することによって、接続する電極に突起電極が不要であることから、インターポーザ基板3の工程簡略化も期待できる。

【0036】

次に、インターポーザ基板上の液晶ドライバ2の接続位置について詳細に述べる。

【0037】

図4は、液晶ドライバパッケージの平面図(図1)と断面図(図2)の一部構成部品を対応するように示し、さらに、断面から見た、液晶ドライバ2の中心線Bとインターポーザ基板の中心線Cを表した図である。

【0038】

図4を参照して、インターポーザ基板3上の液晶ドライバ2は、液晶ドライバ2の短辺中心線Bが、インターポーザ基板3の短辺中心線Cよりも左側(入力側)になるように設けられている。または、端子間の距離で定義すると、画像信号入力用端子6(又は液晶ドライバ接続端子8a)からフィルム基板接続端子10aまでの距離L1は、駆動信号出力用接続端子7(又は液晶ドライバ接続端子8b)からフィルム基板接続端子10bまでの距離L2より短くなるように、液晶ドライバ2はインターポーザ基板3上に設けられている。

【0039】

あるいは、デバイスホール9と、その中に位置する液晶ドライバ2との関係でみれば、液晶ドライバ2の端面と前記デバイスホール端面との距離は、液晶ドライバの対向する2辺のうち画像信号入力用端子6(又は液晶ドライバ接続端子8a)側L3において、駆動信号出力用接続端子7(又は液晶ドライバ接続端子8b)側L4よりも短くなるように、液晶ドライバ2とインターポーザ基板3はフィルム基板4上に設けられている。

【0040】

液晶ドライバ2は、搭載される液晶表示装置の高微細化に対応するために、多出力化が求められ、出力端子数が入力端子数に比べて多い構成である。従って、インターポーザ基板3に配線を設けるのに、端子数(配線数)の多い出力側においては、入力側に比べて、ピッチ変換の為の十分な領域を用意する必要がある。

【0041】

そこで、上記構成にすることにより、インターポーザ基板3の液晶ドライバ出力側において、より多くの領域を割り当てることが可能となる。また、入力側においては、端子数(配線数)が少ないために、ピッチ変換のための領域は、出力側に比べて小さくてよい。よって、入力側には出力側の領域より小さい領域を割り当てることにより、効率的にインターポーザ基板上の領域を用いることができ、インターポーザ基板3の大型化を避けることが可能となる。

【0042】

ここで、インターポーザ基板上の配線のパターンについて詳細に説明し、端子数(配線数)が多い方において、ピッチ変換の為により大きい領域が必要となる理由について述べる。図5(a)・(b)は、2種類のインターポーザ基板上の配線パターンの一部を示した図である。

【0043】

インターポーザ基板(半導体基板)上の配線の斜線部(インターポーザ基板からフィルム基板までの直線部に対して斜めに設けられている配線部分)は、直線部に対して45°の角度を持って配置される(デザインルール)。また、本実施形態では、配線幅は5μm、配線間隔は2μmであり、配線幅が配線間隔より広い為に、配線が折り曲げられて設けられる箇所(直線部と斜線部の交点、以下交点と記す)では、配線同士が接触しないように、交点をずらして配線を設ける必要がある。

【0044】

従って、図5に示したような2種類の配線パターンが考えられる。共に交点をずらして配線が設けられている為、端子数(配線数)が多くなるにしたがって、距離La及びLbが長くなり、インターポーザ基板上に配線ピッチ変換の為の領域がより多く必要となる。

【0045】

よって、インターポーザ基板上に、端子数(配線数)の多い出力側で、端子数の少ない入力側に比べて、ピッチ変換の為により大きい領域が必要となる。

【0046】

また、液晶ドライバの多出力化に伴い、図6のような出力端子のパターンが考えられる。図3のように一列に出力端子を配列するより、出力端子を千鳥状に配列することにより、配線部分より大きな電極幅を必要とする端子部において隣接する端子同士が干渉しなので、さらにファインピッチ化が可能となり、これにより液晶ドライバの大型化を避けることが可能となる。

【0047】

このような千鳥状の駆動信号出力用接続端子7のパターンを採用した場合でも、液晶ドライバ2がインターポーザ基板3上で入力側にずらして設けられている本発明の構成は適用可能である。本発明は、出力端子数が入力端子数に比べて多いほど効果的であるので、多出力化に対応した配線数の多い千鳥状の端子パターンでは特に有効である。

【0048】

また、液晶ドライバの多出力化に伴い、インターポーザ基板3上の配線先端部13、フィルム基板接続端子10a・10bと接続されるフィルム基板4の先端部が千鳥状のパターンにしてもよい。(不図示)

【0049】

さらに、液晶ドライバ2をインターポーザ基板3上で入力側にずらして設けることにより、図4に示したように基板間に異なった長さの間隔L3(入力側)及び間隔L4(出力側)が生じる。半導体パッケージ1の製造工程として、液晶ドライバ2、インターポーザ基板3及びフィルム基板4をそれぞれ接続した後に、その間に封止樹脂5を充填するが、封止樹脂5を注入するため、ある程度の大きさの間隔が必要となる。つまり、液晶ドライバ2とフィルム基板4の間隔をある程度保つ必要があるが、間隔L4において封止樹脂5を注入できるほどの間隔が確保できるので、一方の間隔L3が狭くても樹脂注入は実現される。従って、液晶ドライバの入力側のフィルム基板との間隔がより狭くなる本実施形態は、半導体パッケージの小型化に有効である。

【0050】

上記の例では、インターポーザ基板の2辺に配置された複数の端子それぞれが、入力用及び出力用と分けられているが、これに限定されない。例えば、出力用の端子の増加に伴い、入力側の一部の領域を出力側の端子領域に設定することも可能である。この構成により、インターポーザ基板上を入力側から一部出力側に配線が引き回されて設けられることになる。よって、インターポーザ基板上のスペースを、さらに効率的に活用することができ、半導体パッケージの大型化を避けることが可能となる。

【0051】

(実施の形態2)

実施の形態1では、COF液晶ドライバパッケージを例示して説明したが、本発明は、TCP半導体パッケージにも適用が可能である。実施の形態2は、本発明を適用したTCP液晶ドライバパッケージについて説明する。

【0052】

図7は、実施の形態1の説明で用いた図4に対応した図であり、TCP液晶ドライバパッケージ21の平面図と断面図を示し、各構成部品の位置関係を表した図である。

【0053】

図7を参照して、本実施形態のTCP半導体パッケージ21も、液晶ドライバ22がインターポーザ基板23を介して、フィルム基板24に接続されている構成である。しかし、フィルム基板24はデバイスホールに突出したフライングリード25を有し、インターポーザ基板23とフィルム基板24は、フライングリード25を介して、フィルム基板24の配線が形成された面の裏面からボンディング接続されている点で、COF半導体パッケージと異なる。

【0054】

本実施形態においても、インターポーザ基板上の領域を効率的に活用し、半導体パッケージの大型化を避ける本発明が適用されている。実施の形態1のCOF液晶ドライバパッケージと同様に、インターポーザ基板23上の液晶ドライバ22は、液晶ドライバ22の中心線Dが、インターポーザ基板23の中心線Eよりも左側(入力側)になるように設けられている。または、端子間の距離で定義すると、画像信号入力用端子26(又は液晶ドライバ接続端子28a)からフィルム基板接続端子30aまでの距離L5は、駆動信号出力用接続端子27(又は液晶ドライバ接続端子28b)からフィルム基板接続端子30bまでの距離L6より短くなるように、液晶ドライバ22はインターポーザ基板23上に設けられている。

【0055】

本構成にすることにより、インターポーザ基板23上で、出力端子側のピッチ変換の為の領域を効率的に用いることができ、結果として、インターポーザ基板23を必要以上に大型化させることなく、接続端子及び配線を配置することが可能となる。

【0056】

本明細書においては、液晶ドライバを例示して説明したが、インターポーザ基板を用いたテープキャリア型半導体パッケージであれば、本発明は適用可能である。また、半導体チップの出力端子数が入力端子数より多い半導体パッケージに限らず、対向する2辺に配置された端子数が異なる半導体チップを収容する半導体パッケージであれば、本発明は適用可能である。

【0057】

なお、今回開示された実施形態はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の技術的範囲は特許請求の範囲によって画定され、また特許請求の範囲の記載等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0058】

【図1】本発明の実施の形態1の半導体パッケージの平面図である。

【図2】本発明の実施の形態1の半導体パッケージの断面図である。

【図3】本発明の実施の形態1の半導体パッケージの半導体チップとインターポーザ基板の接続を示す図である。

【図4】本発明の実施の形態1の半導体パッケージの半導体チップとインターポーザ基板との接続位置関係を示す図である。

【図5】インターポーザ基板上の配線パターンの一部を示した図である。

【図6】本発明の実施の形態1の半導体パッケージの半導体チップとインターポーザ基板の接続を示す図である。

【図7】本発明の実施の形態2の半導体パッケージの半導体チップとインターポーザ基板との接続位置関係を示す図である。

【図8】特開2004−207566号公報に記載のCOF半導体パッケージの断面図である。

【符号の説明】

【0059】

1.液晶ドライバパッケージ

2.液晶ドライバ

3.インターポーザ基板

4.フィルム基板

5.封止樹脂

6.画像信号入力用接続端子

7.駆動信号出力用接続端子

8a.液晶ドライバ接続端子(入力)

8b.液晶ドライバ接続端子(出力)

9.デバイスホール

10a.フィルム基板接続端子(入力)

10b.フィルム基板接続端子(出力)

11.配線(インターポーザ基板)

12a.配線(フィルム基板・入力)

12b.配線(フィルム基板・出力)

13.配線先端部(インターポーザ基板)

14.ソルダーレジスト

21.液晶ドライバパッケージ(TCP)

22.液晶ドライバ

23.インターポーザ基板

24.フィルム基板

25.フライングリード

26.画像信号入力用接続端子

27.駆動信号出力用接続端子

28a.液晶ドライバ接続端子(入力)

28b.液晶ドライバ接続端子(出力)

30a.フィルム基板接続端子(入力)

30b.フィルム基板接続端子(出力)

31.半導体パッケージ

32.ICチップ

33.インターポーザ基板

【技術分野】

【0001】

この発明は、半導体パッケージ及びこれを用いた表示装置に関する。特にインターポーザ基板を介して、ICチップとフィルム基板とを接続するテープキャリア型半導体パッケージ及びこれを用いた表示装置に関する。

【背景技術】

【0002】

近年、半導体装置が搭載される電子機器の高機能化に伴い、半導体装置の小型化及び集積化が図られ、様々なタイプの半導体パッケージが開発されている。そのパッケージの一つとして、TCP(Tape Carrier Package)あるいはCOF(Chip On Film)と呼ばれるテープキャリア型の半導体パッケージが提案されている。

【0003】

TCP半導体パッケージは、フィルム基材上に銅箔等の金属パターンにより形成されたリードを有するパッケージであり、フィルム基材に形成された貫通孔(デバイスホール)からリード先端が突出して形成されたフライングリードに、ICチップがフリップチップ接続されて実装される。フィルム基材が柔軟性を有するため折り曲げが可能であり、また多端子ファインピッチ化が可能であるとともに、既存のフリップチップボンディング技術で対応可能なことから、液晶表示装置に代表される薄型表示装置のドライバIC用パッケージとして多用されてきた。

【0004】

COF半導体パッケージは、従来のTCP半導体パッケージのようなフライングリードを持たず、リードがフィルム基材により支持された構造を持つ。このため、より薄い配線材(銅箔)を用いることができるので、さらにファインピッチのリード形成を可能とするパッケージ技術であり、半導体パッケージの小型化及び集積化の要求により、近年多く利用されるようになってきている。

【0005】

また、COF半導体パッケージの一つの形態として、図8に示したような、インターポーザ基板(中間基板)を有するCOF半導体パッケージがある(特許文献1参照)。この形態のCOF半導体パッケージ31は、1つの半導体パッケージの中に中間基板33(インターポーザ基板)を内蔵させ、パッケージ内部でICチップ32とインターポーザ基板33との接続を行うことにより、半導体素子を高密度に実装することが可能である。

【0006】

また、半導体パッケージは、例えば液晶表示装置のような、搭載される電子機器の高性能化に伴うICチップの入出力端子の多ピン化によって、さらなるファインピッチ化が求められる傾向にある。

【特許文献1】特開2004−207566号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

上記のようなインターポーザ基板を有するテープキャリア型半導体パッケージでは、インターポーザ基板上に接続端子及び配線を設けるが、接続端子数の増加により、インターポーザ基板の大型化に伴う半導体パッケージの大型化が避けられないという問題があった。

【0008】

さらに、インターポーザ基板は、例えばシリコン等の半導体材料で形成されるため、インターポーザ基板の大型化によるコスト増加が避けられないという問題があった。

【0009】

特に、ICチップの入力端子数と出力端子数が異なる場合においては、インターポーザ基板の端子数が少ない側のインターポーザ基板のスペースは、端子数が多い側のインターポーザ基板のスペースに対して、不必要に大きく、半導体パッケージを大型化させる要因となっていた。

【0010】

そこで、インターポーザ基板を必要以上に大型化させることなく、接続端子及び配線を配置することを可能とするテープキャリア型半導体パッケージを提供することを目的とする。

【0011】

特に、ICチップの入力端子数と出力端子数が異なる場合において、インターポーザ基板を必要以上に大型化させることなく、接続端子及び配線を配置することを可能とするテープキャリア型半導体パッケージを提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明の第1の局面に係る半導体パッケージは、半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、半導体チップの中心位置とインターポーザ基板の中心位置が異なることを特徴とする。

【0013】

本発明の第2の局面に係る半導体パッケージは、半導体チップがインターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、半導体チップは少なくとも対向する2辺に複数の端子をそれぞれ有し、さらに、インターポーザ基板において、インターポーザ基板の中心より、対向する2辺のうち端子数が少ない一方の側にずれて接続されていることを特徴とする。なお、対向する2辺以外の辺にも端子を配置してもよい。

【0014】

本発明の第3の局面に係る半導体パッケージは、半導体チップがインターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、半導体チップは少なくとも対向する2辺に複数の端子をそれぞれ有し、インターポーザ基板はすくなくとも対向する2辺にフィルム基板に接続されるフィルム基板接続端子をそれぞれ有し、さらに、フィルム基板接続端子の内側に、半導体チップの対向する2辺に配置された複数の端子と接続される半導体チップ接続端子を複数有し、インターポーザ基板の対向する2辺それぞれにおける、フィルム基板接続端子と半導体チップ接続端子との距離は、半導体チップ接続端子の端子数の少ない方において、もう一方よりも短いことを特徴とする。

【0015】

本発明の第4の局面に係る半導体パッケージは、半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、半導体チップは、少なくとも対向する2辺に複数の端子をそれぞれ有し、フィルム基板はデバイスホールを有するとともに、半導体チップはデバイスホール内に位置し、さらにデバイスホールの対向する2辺それぞれにおける、半導体チップ端面とデバイスホール端面との距離は、前記半導体チップの対向する2辺のうち端子数の少ない方において、もう一方よりも短いことを特徴とする。

【0016】

本発明の半導体パッケージは、さらに、半導体チップの対向する2辺のうちの一方の辺には半導体チップへの入力信号端子が配置され、他方の辺には半導体チップからの出力信号端子が配置されていることを特徴とする。

【0017】

本発明の半導体パッケージは、さらに、出力信号端子の端子数は、入力信号端子の端子数より多いことを特徴とする。

【0018】

本発明の半導体パッケージは、さらに、インターポーザ基板は、シリコンからなることを特徴とする。

【0019】

本発明の半導体パッケージは、さらに、半導体チップが、液晶ドライバであることを特徴とする。

【0020】

本発明の表示装置は、上記の何れかの半導体パッケージを備えたことを特徴とする。

【発明の効果】

【0021】

本発明の半導体パッケージによれば、インターポーザ基板を必要以上に大型化させることなく、接続端子及び配線を配置することが可能となる。

【0022】

また、インターポーザ基板に用いられる高価なシリコン等の半導体材料の量を抑えることができ、コスト増加を抑えることが可能となる。

【発明を実施するための最良の形態】

【0023】

以下、本発明の実施の形態について図を参照して説明する。なお、ここでは、本発明の半導体パッケージを採用した液晶ドライバパッケージを例示して説明を行う。

【0024】

(実施の形態1)

図1は、本発明の実施の形態1に係る液晶ドライバパッケージの平面図である。図2は、図1に示した液晶ドライバパッケージを切断面線A−A´から見た断面図である。さらに図3は、液晶ドライバ2とインターポーザ基板3の接続を説明するための図である。以下、図1、図2及び図3を参照して、液晶ドライバパッケージの概略構成について説明を行う。

【0025】

本実施形態の液晶ドライバパッケージ1は、COF(Chip On Film)半導体パッケージであり、少なくとも液晶ドライバ2(半導体チップ)とインターポーザ基板3とフィルム基板4を有し、液晶ドライバ2はインターポーザ基板3を介してフィルム基板4に接続されている。また、液晶ドライバ2、インターポーザ基板3及びフィルム基板4の間には、封止樹脂5が充填され、それぞれの間の接続部が補強・固定されている。ここで、封止樹脂5は、一般にアンダーフィル材と呼ばれ、絶縁性の樹脂(例えば、エポキシ樹脂、シリコーン樹脂、ポリイミド樹脂等)が用いられる。

【0026】

液晶ドライバ2は、少なくとも1つ以上の液晶駆動回路(不図示)を備えており、液晶表示装置を駆動する。そのため、液晶ドライバには、インターポーザ基板と対向する面(以下、下面と記す)に、画像データ信号等を入力するための画像信号入力用接続端子6と、液晶駆動信号を出力するための駆動信号出力用接続端子7とが設けられている。液晶駆動回路の数は、搭載される液晶表示装置によって異なり、限定されるものではない。

【0027】

インターポーザ基板3は、半導体材料、好ましくはシリコンから構成される。インターポーザ基板3上には、液晶ドライバ2の下面に設けられた画像信号入力用接続端子6及び駆動信号出力用接続端子7とフリップチップ実装するための液晶ドライバ接続端子8a(入力側)・8b(出力側)が形成されている。さらに、液晶ドライバ接続端子8a・8bが設けられている面と同一面内に、液晶ドライバ接続端子8a・8bから配線11が設けられており、その配線11の先端部13上にフィルム基板接続端子10a・10bを介してフィルム基板4と接続されている。

【0028】

フィルム基板4は、液晶ドライバ2を収めるデバイスホール9を有し、デバイスホール9周辺部にインターポーザ基板3のフィルム基板接続端子10a(入力側)・10b(出力側)との接続端子が設けられている。接続端子ピッチは、インターポーザ基板3の配線先端部13上のフィルム基板接続端子ピッチ(35μm以上)と対応しており、インターポーザ基板3と接続可能となっている。

【0029】

フィルム基板4には、インターポーザ基板3のフィルム基板接続端子10a・10bから液晶表示装置(不図示)と接続されるための配線12b、及び画像入力制御部(不図示)と接続されるための配線12aが設けられている。さらに、フィルム基板4上には、インターポーザ基板3との接続部を除いて、絶縁性のソルダーレジスト14(熱性コーティング材)が設けられ、フィルム基板4に設けられている配線をほこりや水から保護し、ショート等の欠陥が起こり難い構成となっている。

【0030】

また、フィルム基板4上の配線12a・12bは好ましくは銅箔であり、蒸着、エッチングまたは印刷等の方法により、配線パターンが形成される。特に、配線を銅箔に限らない場合、印刷による形成が簡易であり好適である。さらに、フィルム基板4には、曲げ加工し易いように、ポリイミド(PI)やポリエチレンテレフタレート(PET)等の有機フィルムなどの可撓性が高い素材が用いられる。

【0031】

次に、液晶ドライバ2とインターポーザ基板3の接続及びインターポーザ基板3とフィルム基板4の接続について、図3を参照してさらに詳しく説明する。

【0032】

ここで、インターポーザ基板3に設けられた液晶ドライバ接続端子8a・8bから伸びる配線11は、フィルム基板4に接続される先端部13に近づくに従って、その配線間隔は広がっている。具体的に示すと、液晶ドライバ接続端子8bのピッチは25μm以下であるが、配線11の先端部13のピッチは35μm以上にすることも可能である。このように、インターポーザ基板3を仲介することによって、ICプロセスレベルのファインピッチをフィルム基板レベルの電極ピッチに変換することが可能となる。従って、フィルム基板のフィルム及び配線について、従来の材料を用いることでき、また、その実装方法に関しても、既存の技術が適用可能である。

【0033】

液晶ドライバ2とインターポーザ基板3の接続には、ファインピッチに対応するため、比較的硬く且つ融点の高い金属または合金製バンプが用いられる。例えば、金(Au)バンプを用いたAu−Au接合を適用することができる。これにより、バンプの変形が抑えられ、隣り合うバンプ間での接触の問題を解決できるので、25μm程度まで端子ピッチを縮小することが可能となり、液晶ドライバの多出力化を可能にしている。

【0034】

一方、インターポーザ基板3とフィルム基板(不図示)の接続は、液晶ドライバ2との接続端子より広いピッチ、例えば35〜100μm程度のピッチを持つ端子間の接続とすることができる。接続はインターポーザ基板3の配線11の先端部13のフィルム基板接続端子10a・10bのAuバンプとフィルム基板4上の配線12a・12bの先端部に施されたスズとの金−スズ共晶接続で行う。また、Auバンプのような高価な接続電極を形成せず、異方性導電フィルム(ACF:Anisotropic Conductive Film)あるいは異方性導電ペースト(ACP:Anisotropic Conductive Paste)を用いた一括ボンディングを適用することも可能である。

【0035】

また、このようなACF/ACPボンディングを採用することによって、接続する電極に突起電極が不要であることから、インターポーザ基板3の工程簡略化も期待できる。

【0036】

次に、インターポーザ基板上の液晶ドライバ2の接続位置について詳細に述べる。

【0037】

図4は、液晶ドライバパッケージの平面図(図1)と断面図(図2)の一部構成部品を対応するように示し、さらに、断面から見た、液晶ドライバ2の中心線Bとインターポーザ基板の中心線Cを表した図である。

【0038】

図4を参照して、インターポーザ基板3上の液晶ドライバ2は、液晶ドライバ2の短辺中心線Bが、インターポーザ基板3の短辺中心線Cよりも左側(入力側)になるように設けられている。または、端子間の距離で定義すると、画像信号入力用端子6(又は液晶ドライバ接続端子8a)からフィルム基板接続端子10aまでの距離L1は、駆動信号出力用接続端子7(又は液晶ドライバ接続端子8b)からフィルム基板接続端子10bまでの距離L2より短くなるように、液晶ドライバ2はインターポーザ基板3上に設けられている。

【0039】

あるいは、デバイスホール9と、その中に位置する液晶ドライバ2との関係でみれば、液晶ドライバ2の端面と前記デバイスホール端面との距離は、液晶ドライバの対向する2辺のうち画像信号入力用端子6(又は液晶ドライバ接続端子8a)側L3において、駆動信号出力用接続端子7(又は液晶ドライバ接続端子8b)側L4よりも短くなるように、液晶ドライバ2とインターポーザ基板3はフィルム基板4上に設けられている。

【0040】

液晶ドライバ2は、搭載される液晶表示装置の高微細化に対応するために、多出力化が求められ、出力端子数が入力端子数に比べて多い構成である。従って、インターポーザ基板3に配線を設けるのに、端子数(配線数)の多い出力側においては、入力側に比べて、ピッチ変換の為の十分な領域を用意する必要がある。

【0041】

そこで、上記構成にすることにより、インターポーザ基板3の液晶ドライバ出力側において、より多くの領域を割り当てることが可能となる。また、入力側においては、端子数(配線数)が少ないために、ピッチ変換のための領域は、出力側に比べて小さくてよい。よって、入力側には出力側の領域より小さい領域を割り当てることにより、効率的にインターポーザ基板上の領域を用いることができ、インターポーザ基板3の大型化を避けることが可能となる。

【0042】

ここで、インターポーザ基板上の配線のパターンについて詳細に説明し、端子数(配線数)が多い方において、ピッチ変換の為により大きい領域が必要となる理由について述べる。図5(a)・(b)は、2種類のインターポーザ基板上の配線パターンの一部を示した図である。

【0043】

インターポーザ基板(半導体基板)上の配線の斜線部(インターポーザ基板からフィルム基板までの直線部に対して斜めに設けられている配線部分)は、直線部に対して45°の角度を持って配置される(デザインルール)。また、本実施形態では、配線幅は5μm、配線間隔は2μmであり、配線幅が配線間隔より広い為に、配線が折り曲げられて設けられる箇所(直線部と斜線部の交点、以下交点と記す)では、配線同士が接触しないように、交点をずらして配線を設ける必要がある。

【0044】

従って、図5に示したような2種類の配線パターンが考えられる。共に交点をずらして配線が設けられている為、端子数(配線数)が多くなるにしたがって、距離La及びLbが長くなり、インターポーザ基板上に配線ピッチ変換の為の領域がより多く必要となる。

【0045】

よって、インターポーザ基板上に、端子数(配線数)の多い出力側で、端子数の少ない入力側に比べて、ピッチ変換の為により大きい領域が必要となる。

【0046】

また、液晶ドライバの多出力化に伴い、図6のような出力端子のパターンが考えられる。図3のように一列に出力端子を配列するより、出力端子を千鳥状に配列することにより、配線部分より大きな電極幅を必要とする端子部において隣接する端子同士が干渉しなので、さらにファインピッチ化が可能となり、これにより液晶ドライバの大型化を避けることが可能となる。

【0047】

このような千鳥状の駆動信号出力用接続端子7のパターンを採用した場合でも、液晶ドライバ2がインターポーザ基板3上で入力側にずらして設けられている本発明の構成は適用可能である。本発明は、出力端子数が入力端子数に比べて多いほど効果的であるので、多出力化に対応した配線数の多い千鳥状の端子パターンでは特に有効である。

【0048】

また、液晶ドライバの多出力化に伴い、インターポーザ基板3上の配線先端部13、フィルム基板接続端子10a・10bと接続されるフィルム基板4の先端部が千鳥状のパターンにしてもよい。(不図示)

【0049】

さらに、液晶ドライバ2をインターポーザ基板3上で入力側にずらして設けることにより、図4に示したように基板間に異なった長さの間隔L3(入力側)及び間隔L4(出力側)が生じる。半導体パッケージ1の製造工程として、液晶ドライバ2、インターポーザ基板3及びフィルム基板4をそれぞれ接続した後に、その間に封止樹脂5を充填するが、封止樹脂5を注入するため、ある程度の大きさの間隔が必要となる。つまり、液晶ドライバ2とフィルム基板4の間隔をある程度保つ必要があるが、間隔L4において封止樹脂5を注入できるほどの間隔が確保できるので、一方の間隔L3が狭くても樹脂注入は実現される。従って、液晶ドライバの入力側のフィルム基板との間隔がより狭くなる本実施形態は、半導体パッケージの小型化に有効である。

【0050】

上記の例では、インターポーザ基板の2辺に配置された複数の端子それぞれが、入力用及び出力用と分けられているが、これに限定されない。例えば、出力用の端子の増加に伴い、入力側の一部の領域を出力側の端子領域に設定することも可能である。この構成により、インターポーザ基板上を入力側から一部出力側に配線が引き回されて設けられることになる。よって、インターポーザ基板上のスペースを、さらに効率的に活用することができ、半導体パッケージの大型化を避けることが可能となる。

【0051】

(実施の形態2)

実施の形態1では、COF液晶ドライバパッケージを例示して説明したが、本発明は、TCP半導体パッケージにも適用が可能である。実施の形態2は、本発明を適用したTCP液晶ドライバパッケージについて説明する。

【0052】

図7は、実施の形態1の説明で用いた図4に対応した図であり、TCP液晶ドライバパッケージ21の平面図と断面図を示し、各構成部品の位置関係を表した図である。

【0053】

図7を参照して、本実施形態のTCP半導体パッケージ21も、液晶ドライバ22がインターポーザ基板23を介して、フィルム基板24に接続されている構成である。しかし、フィルム基板24はデバイスホールに突出したフライングリード25を有し、インターポーザ基板23とフィルム基板24は、フライングリード25を介して、フィルム基板24の配線が形成された面の裏面からボンディング接続されている点で、COF半導体パッケージと異なる。

【0054】

本実施形態においても、インターポーザ基板上の領域を効率的に活用し、半導体パッケージの大型化を避ける本発明が適用されている。実施の形態1のCOF液晶ドライバパッケージと同様に、インターポーザ基板23上の液晶ドライバ22は、液晶ドライバ22の中心線Dが、インターポーザ基板23の中心線Eよりも左側(入力側)になるように設けられている。または、端子間の距離で定義すると、画像信号入力用端子26(又は液晶ドライバ接続端子28a)からフィルム基板接続端子30aまでの距離L5は、駆動信号出力用接続端子27(又は液晶ドライバ接続端子28b)からフィルム基板接続端子30bまでの距離L6より短くなるように、液晶ドライバ22はインターポーザ基板23上に設けられている。

【0055】

本構成にすることにより、インターポーザ基板23上で、出力端子側のピッチ変換の為の領域を効率的に用いることができ、結果として、インターポーザ基板23を必要以上に大型化させることなく、接続端子及び配線を配置することが可能となる。

【0056】

本明細書においては、液晶ドライバを例示して説明したが、インターポーザ基板を用いたテープキャリア型半導体パッケージであれば、本発明は適用可能である。また、半導体チップの出力端子数が入力端子数より多い半導体パッケージに限らず、対向する2辺に配置された端子数が異なる半導体チップを収容する半導体パッケージであれば、本発明は適用可能である。

【0057】

なお、今回開示された実施形態はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の技術的範囲は特許請求の範囲によって画定され、また特許請求の範囲の記載等の意味および範囲内でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0058】

【図1】本発明の実施の形態1の半導体パッケージの平面図である。

【図2】本発明の実施の形態1の半導体パッケージの断面図である。

【図3】本発明の実施の形態1の半導体パッケージの半導体チップとインターポーザ基板の接続を示す図である。

【図4】本発明の実施の形態1の半導体パッケージの半導体チップとインターポーザ基板との接続位置関係を示す図である。

【図5】インターポーザ基板上の配線パターンの一部を示した図である。

【図6】本発明の実施の形態1の半導体パッケージの半導体チップとインターポーザ基板の接続を示す図である。

【図7】本発明の実施の形態2の半導体パッケージの半導体チップとインターポーザ基板との接続位置関係を示す図である。

【図8】特開2004−207566号公報に記載のCOF半導体パッケージの断面図である。

【符号の説明】

【0059】

1.液晶ドライバパッケージ

2.液晶ドライバ

3.インターポーザ基板

4.フィルム基板

5.封止樹脂

6.画像信号入力用接続端子

7.駆動信号出力用接続端子

8a.液晶ドライバ接続端子(入力)

8b.液晶ドライバ接続端子(出力)

9.デバイスホール

10a.フィルム基板接続端子(入力)

10b.フィルム基板接続端子(出力)

11.配線(インターポーザ基板)

12a.配線(フィルム基板・入力)

12b.配線(フィルム基板・出力)

13.配線先端部(インターポーザ基板)

14.ソルダーレジスト

21.液晶ドライバパッケージ(TCP)

22.液晶ドライバ

23.インターポーザ基板

24.フィルム基板

25.フライングリード

26.画像信号入力用接続端子

27.駆動信号出力用接続端子

28a.液晶ドライバ接続端子(入力)

28b.液晶ドライバ接続端子(出力)

30a.フィルム基板接続端子(入力)

30b.フィルム基板接続端子(出力)

31.半導体パッケージ

32.ICチップ

33.インターポーザ基板

【特許請求の範囲】

【請求項1】

半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、

前記半導体チップの中心位置と前記インターポーザ基板の中心位置が異なることを特徴とする半導体パッケージ。

【請求項2】

半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、

前記半導体チップは、少なくとも対向する2辺に、複数の端子をそれぞれ有し、

さらに、前記インターポーザ基板において、前記インターポーザ基板の中心より、前記対向する2辺のうち端子数が少ない一方の側にずれて接続されていることを特徴とする半導体パッケージ。

【請求項3】

半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、

前記半導体チップは、少なくとも対向する2辺に、複数の端子をそれぞれ有し、

前記インターポーザ基板は、少なくとも対向する2辺に、前記フィルム基板に接続されるフィルム基板接続端子をそれぞれ有し、さらに、前記フィルム基板接続端子の内側に、前記半導体チップの対向する2辺に配置された複数の端子と接続される半導体チップ接続端子を複数有し、

前記インターポーザ基板の対向する2辺それぞれにおける、前記フィルム基板接続端子と前記半導体チップ接続端子との距離は、前記半導体チップ接続端子の端子数の少ない方において、もう一方よりも短いことを特徴とする半導体パッケージ。

【請求項4】

半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、

前記半導体チップは、少なくとも対向する2辺に、複数の端子をそれぞれ有し、

前記フィルム基板はデバイスホールを有するとともに、前記半導体チップは前記デバイスホール内に位置し、

さらに前記デバイスホールの対向する2辺それぞれにおける、前記半導体チップ端面と前記デバイスホール端面との距離は、前記半導体チップの対向する2辺のうち端子数の少ない方において、もう一方よりも短いことを特徴とする半導体パッケージ。

【請求項5】

前記半導体チップの対向する2辺のうちの一方の辺には、前記半導体チップへの入力信号端子が配置され、他方の辺には前記半導体チップからの出力信号端子が配置されていることを特徴とする請求項2から4の何れかに記載の半導体パッケージ。

【請求項6】

前記出力信号端子の端子数は、前記入力信号端子の端子数より多いことを特徴とする請求項5に記載の半導体パッケージ。

【請求項7】

前記インターポーザ基板は、シリコンからなることを特徴とする請求項1から6の何れかに記載の半導体パッケージ。

【請求項8】

前記半導体チップが、液晶ドライバであることを特徴とする請求項1から7の何れかに記載の半導体パッケージ。

【請求項9】

請求項1から8の何れかに記載の半導体パッケージを備えた表示装置。

【請求項1】

半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、

前記半導体チップの中心位置と前記インターポーザ基板の中心位置が異なることを特徴とする半導体パッケージ。

【請求項2】

半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、

前記半導体チップは、少なくとも対向する2辺に、複数の端子をそれぞれ有し、

さらに、前記インターポーザ基板において、前記インターポーザ基板の中心より、前記対向する2辺のうち端子数が少ない一方の側にずれて接続されていることを特徴とする半導体パッケージ。

【請求項3】

半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、

前記半導体チップは、少なくとも対向する2辺に、複数の端子をそれぞれ有し、

前記インターポーザ基板は、少なくとも対向する2辺に、前記フィルム基板に接続されるフィルム基板接続端子をそれぞれ有し、さらに、前記フィルム基板接続端子の内側に、前記半導体チップの対向する2辺に配置された複数の端子と接続される半導体チップ接続端子を複数有し、

前記インターポーザ基板の対向する2辺それぞれにおける、前記フィルム基板接続端子と前記半導体チップ接続端子との距離は、前記半導体チップ接続端子の端子数の少ない方において、もう一方よりも短いことを特徴とする半導体パッケージ。

【請求項4】

半導体チップが、インターポーザ基板を介してフィルム基板に接続される半導体パッケージにおいて、

前記半導体チップは、少なくとも対向する2辺に、複数の端子をそれぞれ有し、

前記フィルム基板はデバイスホールを有するとともに、前記半導体チップは前記デバイスホール内に位置し、

さらに前記デバイスホールの対向する2辺それぞれにおける、前記半導体チップ端面と前記デバイスホール端面との距離は、前記半導体チップの対向する2辺のうち端子数の少ない方において、もう一方よりも短いことを特徴とする半導体パッケージ。

【請求項5】

前記半導体チップの対向する2辺のうちの一方の辺には、前記半導体チップへの入力信号端子が配置され、他方の辺には前記半導体チップからの出力信号端子が配置されていることを特徴とする請求項2から4の何れかに記載の半導体パッケージ。

【請求項6】

前記出力信号端子の端子数は、前記入力信号端子の端子数より多いことを特徴とする請求項5に記載の半導体パッケージ。

【請求項7】

前記インターポーザ基板は、シリコンからなることを特徴とする請求項1から6の何れかに記載の半導体パッケージ。

【請求項8】

前記半導体チップが、液晶ドライバであることを特徴とする請求項1から7の何れかに記載の半導体パッケージ。

【請求項9】

請求項1から8の何れかに記載の半導体パッケージを備えた表示装置。

【図1】

【図2】

【図4】

【図5】

【図7】

【図8】

【図3】

【図6】

【図2】

【図4】

【図5】

【図7】

【図8】

【図3】

【図6】

【公開番号】特開2008−91790(P2008−91790A)

【公開日】平成20年4月17日(2008.4.17)

【国際特許分類】

【出願番号】特願2006−273306(P2006−273306)

【出願日】平成18年10月4日(2006.10.4)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成20年4月17日(2008.4.17)

【国際特許分類】

【出願日】平成18年10月4日(2006.10.4)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]