半導体パッケージ、及び半導体パッケージの製造方法

【課題】高周波電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージ(P)を提供すること。

【解決手段】接地導体(131)と、前記接地導体(131)の上部に設けられた2層の高周波基板(130)と、上層の前記高周波基板(130)を挟むように設けられた一対の導体(134)と、を含む、半導体パッケージ(P)が提供される。また、この半導体パッケージ(P)を含む高周波電力増幅器(100)が提供される。

【解決手段】接地導体(131)と、前記接地導体(131)の上部に設けられた2層の高周波基板(130)と、上層の前記高周波基板(130)を挟むように設けられた一対の導体(134)と、を含む、半導体パッケージ(P)が提供される。また、この半導体パッケージ(P)を含む高周波電力増幅器(100)が提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体パッケージ、及び半導体パッケージの製造方法に関する。

【背景技術】

【0002】

無線通信の分野においては、無線周波数の有効活用、情報通信の高速化及び大容量化への要望から、周波数の高周波化及び低歪化が進められている。また、通信機器の消費電力低減への要望から、低消費電力化が望まれている。こうした事情から、無線通信システムや、無線通信システムに用いられる電力増幅モジュールの高機能化(高周波化、低歪化、低消費電力化)が求められている。こうした無線通信システムに用いられる電力増幅モジュールについては、例えば、下記の特許文献1〜3に記載がある。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−165037号公報

【特許文献2】特開2005−303771号公報

【特許文献3】特開2008−112810号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

一般に、高出力電力が必要とされる場合、電力増幅モジュールには、複数の電力増幅器(半導体装置)が搭載される。こうした電力増幅モジュールは、複数の電力増幅器で増幅された電力を合成することで高出力電力を得る仕組みとなっている。また、上記の特許文献1及び2に記載の電力増幅モジュールは、上記のような高機能化を図るため、複数の電力増幅器を搭載するだけでなく、位相や振幅を調整する回路を搭載しており、ドハティアンプやプッシュプルアンプのような機能を実現している。また、上記の特許文献3に記載の電力増幅モジュールは、電力増幅器の性能を引き出すために電力増幅素子を収納する半導体パッケージの構成にも工夫を凝らしている。

【0005】

しかしながら、ドハティアンプやプッシュプルアンプなどの異なる動作をする電力増幅器を複数搭載し、複数の電力増幅器で増幅された電力を合成するような回路構成にすると、回路基板の面積が大きくなってしまうという問題がある。ドハティアンプやプッシュプルアンプは、それぞれ電力増幅器の位相を位相変換回路にて変換して動作させるのであるが、例えば、上記の特許文献2に記載の電力増幅モジュールの場合、半導体パッケージ内に位相変換回路も組み込んでしまっている。このような半導体パッケージの構成にすると、汎用性が低下するばかりか、高コストになってしまうという問題がある。

【0006】

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な、新規かつ改良された半導体パッケージ、及び半導体パッケージの製造方法を提供することにある。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明のある観点によれば、接地導体と、前記接地導体の上部に設けられた2層の高周波基板と、上層の前記高周波基板を挟むように設けられた一対の導体と、を含む、半導体パッケージが提供される。

【0008】

また、上記の半導体パッケージは、上層の前記高周波基板を挟むように設けられた前記一対の導体のそれぞれに接続された一対の接続端子と、下層の前記高周波基板に接して設けられた他方の前記導体とワイヤを介して接続された整合回路基板と、前記整合回路基板とワイヤを介して接続された半導体素子と、をさらに含んでいてもよい。

【0009】

また、前記接続端子は、前記半導体パッケージの外部にある位相変換回路に接続されていてもよい。

【0010】

また、上記の半導体パッケージは、一対の前記半導体素子を含んでいてもよい。さらに、前記各半導体素子に対応して、前記2層の高周波基板、前記一対の導体、前記一対の接続端子、及び前記整合回路基板がそれぞれ設けられていてもよい。

【0011】

また、前記半導体パッケージは、ドハティアンプ及び/又はプッシュプルアンプの一部を成す電力増幅器であってもよい。

【0012】

また、上記課題を解決するために、本発明の別の観点によれば、下層の高周波基板上に第1の導体を設置する工程と、前記第1の導体上に上層の高周波基板を設置する工程と、前記上層の高周波基板上に第2の導体を設置する工程と、前記下層の高周波基板を接地導体と接続する工程と、を含む、半導体パッケージの製造方法が提供される。

【0013】

また、上記の半導体パッケージの製造方法は、前記接地導体上にフレームを接続する工程と、前記第1の導体に第1の接続端子を接続する工程と、前記第2の導体に第2の接続端子を接続する工程と、をさらに含んでいてもよい。

【0014】

また、前記第1及び第2の接続端子は、前記半導体パッケージの外部にある位相変換回路に接続されていてもよい。

【発明の効果】

【0015】

以上説明したように本発明によれば、電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージの提供が可能になる。

【図面の簡単な説明】

【0016】

【図1】従来の高周波電力増幅器の構成例を示した説明図である。

【図2】本実施形態の高周波電力増幅器の構成例を示した説明図である。

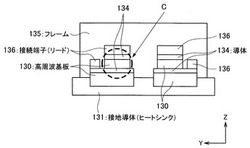

【図3】本実施形態の半導体パッケージの構成例を示した説明図である。

【図4】本実施形態の半導体パッケージの構成例を示した説明図である。

【図5】本実施形態の半導体パッケージの構成例を示した説明図である。

【図6】本実施形態の半導体パッケージの製造工程を示した説明図である。

【図7】本実施形態の一変形例に係る半導体パッケージの構成例を示した説明図である。

【発明を実施するための形態】

【0017】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0018】

[説明の流れについて]

ここで、以下に記載する本発明の実施形態に関する説明の流れについて簡単に述べる。まず、図1を参照しながら、従来の高周波電力増幅器10の構成例について説明する。次いで、図2を参照しながら、本実施形態に係る高周波電力増幅器100の構成例及び半導体パッケージPの構成例について説明する。次いで、図3〜図5を参照しながら、本実施形態に係る半導体パッケージPの構造について説明する。次いで、図6を参照しながら、本実施形態に係る半導体パッケージPの製造工程について説明する。次いで、図7を参照しながら、本実施形態の一変形例に係る半導体パッケージPの構造について説明する。

【0019】

<1:従来例(高周波電力増幅器10の構成例)>

まず、図1を参照しながら、従来の高周波電力増幅器10の構成について述べる。図1に示した高周波電力増幅器10の構成は、一般的なドハティアンプやプッシュプルアンプの回路構成の一例である。

【0020】

図1に示すように、高周波電力増幅器10は、電力分配器11、キャパシタ12A及び12B、直流電源13A及び13B、位相変換回路14A及び14B、整合回路15A及び15B、半導体装置16A及び16B、整合回路17A及び17B、位相変換回路18A及び18B、直流電源19A及び19B、キャパシタ20A及び20B、そして、電力合成器21により構成される。

【0021】

キャパシタ12A及び12Bには、電力分配器11で分配されたRF信号がそれぞれ入力される。また、キャパシタ12A及び12Bの出力は、それぞれ位相変換回路14A及び14Bの入力に接続される。また、キャパシタ12A及び12Bの出力と位相変換回路14A及び14Bの入力とを接続する線路には、それぞれ直流電源13A及び13Bが接続される。また、位相変換回路14A及び14Bの出力は、それぞれ整合回路15A及び15Bの入力に接続される。また、整合回路15A及び15Bの出力は、それぞれ半導体装置16A及び16Bの入力に接続される。なお、これら半導体装置16A及び16Bは、電力増幅器である。

【0022】

半導体装置16A及び16Bの出力は、それぞれ整合回路17A及び17Bの入力に接続される。また、整合回路17A及び17Bの出力は、それぞれ位相変換回路18A及び18Bの入力に接続される。また、位相変換回路18A及び18Bの出力は、それぞれキャパシタ20A及び20Bの入力に接続される。また、位相変換回路18A及び18Bの出力とキャパシタ20A及び20Bの入力とを接続する線路には、それぞれ直流電源19A及び19Bが接続される。また、キャパシタ20A及び20Bから出力されたRF信号は、電力合成器21に入力され、合成されて出力される。

【0023】

以上、従来の高周波電力増幅器10の構成について説明した。ドハティアンプの場合にはRF信号の位相差は90度に調整され、プッシュプルアンプの場合にはRF信号の位相差は180度に調整される。このような構成の高周波電力増幅器10を半導体パッケージにする場合、位相変換回路14A、14B、18A、18Bを半導体パッケージに含める必要がある。そのため、従来の高周波電力増幅器10を構成する半導体パッケージは、汎用性が低く、小型化が難しく、高コストになっていた。本実施形態に係る高周波電力増幅器100及びこれを成す半導体パッケージPは、上記のような従来の問題を解決するものである。

【0024】

<2:実施形態>

以下、本発明の一実施形態について説明する。本実施形態は、無線通信システムなどに用いられる高周波電力増幅器に関し、特に、複数の半導体装置を収納する半導体パッケージの構造に関する。

【0025】

[2−1:高周波電力増幅器100の構成例]

図2に示すように、本実施形態に係る高周波電力増幅器100は、電力分配器101、位相変換回路102A及び102B、キャパシタ103A及び103B、直流電源104A及び104B、整合回路105A及び105B、半導体装置106A及び106B、整合回路107A及び107B、直流電源108A及び108B、キャパシタ109A及び109B、位相変換回路110A及び110B、電力合成器111により構成される。なお、各構成要素の接続関係については、図2に示した通りである。

【0026】

図1に示した従来の高周波電力増幅器10と、図2に示した本実施形態に係る高周波電力増幅器100との主要な違いは、位相変換回路102A、102B、110A、110Bの接続関係にある。図2に示すように、本実施形態に係る高周波電力増幅器100の場合、位相変換回路102A及び102Bは電力分配器101の直後に設けられ、位相変換回路110A及び110Bは電力合成器111の直前に設けられている。そのため、位相変換回路102A、102B、110A、110Bを半導体パッケージPの外側に設けることが可能になる。

【0027】

言い換えると、本実施形態の場合、キャパシタ103A及び103B、直流電源104A及び104B、整合回路105A及び105B、半導体装置106A及び106B、整合回路107A及び107B、直流電源108A及び108B、キャパシタ109A及び109Bを含む半導体パッケージPを構成することが可能になる。位相変換回路102A、102B、110A、110Bが半導体パッケージPの外部に設置可能になることで、半導体パッケージP内の再設計を必要とせずに回路構成を変更することができるようになる。その結果、高周波電力増幅器100の汎用性が向上する。

【0028】

[2−2:半導体パッケージPの構造]

次に、図3〜図5を参照しながら、本実施形態に係る半導体パッケージPの構造について説明する。図3は、本実施形態に係る半導体パッケージPの上面図である。図4は、図3の半導体パッケージPをX方向に見た側面図である。図5は、図3の半導体パッケージPをI−I線に沿って切断した場合の断面を示す断面図である。

【0029】

まず、図3を参照する。図3に示すように、半導体パッケージPは、接地導体131(ヒートシンク)と、整合回路基板132と、半導体素子133(電力増幅器)と、導体134と、フレーム135と、接続端子136(リード)と、金ワイヤ137とを含む。また、図4及び図5に示すように、半導体パッケージPは、高周波基板130をさらに含む。なお、半導体パッケージPの筐体は、接地導体131及びフレーム135で形成された容器により構成される。

【0030】

図3に示すように、接地導体131上には、2つの半導体素子133が設けられている。また、各半導体素子133の前段には整合回路基板132が設けられており、互いに金ワイヤ137を介して電気的に接続されている。同様に、各半導体素子133の後段にも整合回路基板132が設けられており、互いに金ワイヤ137を介して電気的に接続されている。また、各整合回路基板132は、金ワイヤ137を介して導体134(後述する下層の導体134)に電気的に接続されている。

【0031】

また、図4及び図5に示すように、半導体パッケージPには、下層の導体134を挟むように2層の高周波基板130が設けられている。また、上層及び下層の導体134には、それぞれ接続端子136が電気的に接続されている。なお、図4の符号Cで示した領域において、高周波基板130を挟む上層及び下層の導体134によりキャパシタが形成される。また、上層の導体134には高周波成分が流れ、下層の導体134には高周波成分と直流成分とが流れる。このように、上層及び下層の導体134によりキャパシタを形成することにより、半導体パッケージPの外部に直流成分が漏れないようにしている。

【0032】

先に述べたように、位相変換回路110A及び110Bを半導体パッケージPの外部に出したことで、汎用性の向上と半導体パッケージPの小型化が実現可能になる。つまり、ドハティアンプに必要な90度の位相差にも、プッシュプルアンプに必要な180度の位相差にも、パッケージ内を再設計すること無しに、半導体パッケージPの外の回路構成を変更するだけで対応可能になるため、高周波電力増幅器100の汎用性を損なわず、低コストとなる。さらに、高周波基板130を挟んだ一対の導体134によりキャパシタが形成されるため、キャパシタを半導体パッケージPに含む更なる小型化が可能になる。

【0033】

[2−3:半導体パッケージPの製造工程]

次に、図6を参照しながら、本実施形態に係る半導体パッケージPの製造工程について説明する。なお、各構成要素の接続は、半田付けやロウ付けで実現される。

【0034】

図6に示すように、まず、接地導体131を用意する(工程S1)。このとき、位置合わせや高さ合わせのために、必要に応じて高周波基板130が入るくぼみを加工する。次に、リード(接続端子136)及び金ワイヤ137が接続される接続部を加工した2層の高周波基板130(例えば、セラミック基板等)を用意し、下層の導体134を2層の高周波基板130で挟み、上層の導体134を上層の高周波基板130上に設置する(工程S2)。次に、工程S1で用意したヒートシンク基材(接地導体131)と、工程S2で用意した高周波基板130とを接続する(工程S3)。次に、ヒートシンク基材(接地導体131)にフレーム135を接続する(工程S4)。次に、リード(接続端子136)を上層及び下層の導体134に接続する(工程S5)。

【0035】

以上、本実施形態に係る半導体パッケージPの製造工程について説明した。

【0036】

[2−4:変形例(半導体パッケージPの構造)]

ここで、図7を参照しながら、本実施形態の一変形例に係る半導体パッケージPの構造について説明する。図3〜図5に示した半導体パッケージPは、上層の導体134に高周波成分、下層の導体134に高周波成分及び直流成分が流れる構造であった。しかし、図7に示した半導体パッケージPの構造にすると、上層の導体134に高周波成分及び直流成分が流れ、下層の導体134に高周波成分が流れるようになる。このような変形例についても、本実施形態の技術的範囲に属する。

【0037】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されないことは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

【0038】

例えば、上記の説明においては、複数の半導体素子をパッケージ内に収容する構成について述べてきたが、1つの半導体素子をパッケージ内に収容する構成の場合にも、パッケージ内に直流カットのキャパシタを設ける構成とすることで小型化に寄与する。つまり、図3〜図5及び図7に示した半導体パッケージPにおいて、一方の半導体素子133に対応する構成要素を省略した構成も有用である。

【符号の説明】

【0039】

100 高周波電力増幅器

101 電力分配器

102A、102B 位相変換回路

103A、103B キャパシタ

104A、104B 直流電源

105A、105B 整合回路

106A、106B 半導体装置

107A、107B 整合回路

108A、108B 直流電源

109A、109B キャパシタ

110A、110B 位相変換回路

111 電力合成器

130 高周波基板

131 接地導体

132 整合回路基板

133 半導体素子

134 導体

135 フレーム

136 接続端子

137 金ワイヤ

【技術分野】

【0001】

本発明は、半導体パッケージ、及び半導体パッケージの製造方法に関する。

【背景技術】

【0002】

無線通信の分野においては、無線周波数の有効活用、情報通信の高速化及び大容量化への要望から、周波数の高周波化及び低歪化が進められている。また、通信機器の消費電力低減への要望から、低消費電力化が望まれている。こうした事情から、無線通信システムや、無線通信システムに用いられる電力増幅モジュールの高機能化(高周波化、低歪化、低消費電力化)が求められている。こうした無線通信システムに用いられる電力増幅モジュールについては、例えば、下記の特許文献1〜3に記載がある。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−165037号公報

【特許文献2】特開2005−303771号公報

【特許文献3】特開2008−112810号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

一般に、高出力電力が必要とされる場合、電力増幅モジュールには、複数の電力増幅器(半導体装置)が搭載される。こうした電力増幅モジュールは、複数の電力増幅器で増幅された電力を合成することで高出力電力を得る仕組みとなっている。また、上記の特許文献1及び2に記載の電力増幅モジュールは、上記のような高機能化を図るため、複数の電力増幅器を搭載するだけでなく、位相や振幅を調整する回路を搭載しており、ドハティアンプやプッシュプルアンプのような機能を実現している。また、上記の特許文献3に記載の電力増幅モジュールは、電力増幅器の性能を引き出すために電力増幅素子を収納する半導体パッケージの構成にも工夫を凝らしている。

【0005】

しかしながら、ドハティアンプやプッシュプルアンプなどの異なる動作をする電力増幅器を複数搭載し、複数の電力増幅器で増幅された電力を合成するような回路構成にすると、回路基板の面積が大きくなってしまうという問題がある。ドハティアンプやプッシュプルアンプは、それぞれ電力増幅器の位相を位相変換回路にて変換して動作させるのであるが、例えば、上記の特許文献2に記載の電力増幅モジュールの場合、半導体パッケージ内に位相変換回路も組み込んでしまっている。このような半導体パッケージの構成にすると、汎用性が低下するばかりか、高コストになってしまうという問題がある。

【0006】

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な、新規かつ改良された半導体パッケージ、及び半導体パッケージの製造方法を提供することにある。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明のある観点によれば、接地導体と、前記接地導体の上部に設けられた2層の高周波基板と、上層の前記高周波基板を挟むように設けられた一対の導体と、を含む、半導体パッケージが提供される。

【0008】

また、上記の半導体パッケージは、上層の前記高周波基板を挟むように設けられた前記一対の導体のそれぞれに接続された一対の接続端子と、下層の前記高周波基板に接して設けられた他方の前記導体とワイヤを介して接続された整合回路基板と、前記整合回路基板とワイヤを介して接続された半導体素子と、をさらに含んでいてもよい。

【0009】

また、前記接続端子は、前記半導体パッケージの外部にある位相変換回路に接続されていてもよい。

【0010】

また、上記の半導体パッケージは、一対の前記半導体素子を含んでいてもよい。さらに、前記各半導体素子に対応して、前記2層の高周波基板、前記一対の導体、前記一対の接続端子、及び前記整合回路基板がそれぞれ設けられていてもよい。

【0011】

また、前記半導体パッケージは、ドハティアンプ及び/又はプッシュプルアンプの一部を成す電力増幅器であってもよい。

【0012】

また、上記課題を解決するために、本発明の別の観点によれば、下層の高周波基板上に第1の導体を設置する工程と、前記第1の導体上に上層の高周波基板を設置する工程と、前記上層の高周波基板上に第2の導体を設置する工程と、前記下層の高周波基板を接地導体と接続する工程と、を含む、半導体パッケージの製造方法が提供される。

【0013】

また、上記の半導体パッケージの製造方法は、前記接地導体上にフレームを接続する工程と、前記第1の導体に第1の接続端子を接続する工程と、前記第2の導体に第2の接続端子を接続する工程と、をさらに含んでいてもよい。

【0014】

また、前記第1及び第2の接続端子は、前記半導体パッケージの外部にある位相変換回路に接続されていてもよい。

【発明の効果】

【0015】

以上説明したように本発明によれば、電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージの提供が可能になる。

【図面の簡単な説明】

【0016】

【図1】従来の高周波電力増幅器の構成例を示した説明図である。

【図2】本実施形態の高周波電力増幅器の構成例を示した説明図である。

【図3】本実施形態の半導体パッケージの構成例を示した説明図である。

【図4】本実施形態の半導体パッケージの構成例を示した説明図である。

【図5】本実施形態の半導体パッケージの構成例を示した説明図である。

【図6】本実施形態の半導体パッケージの製造工程を示した説明図である。

【図7】本実施形態の一変形例に係る半導体パッケージの構成例を示した説明図である。

【発明を実施するための形態】

【0017】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0018】

[説明の流れについて]

ここで、以下に記載する本発明の実施形態に関する説明の流れについて簡単に述べる。まず、図1を参照しながら、従来の高周波電力増幅器10の構成例について説明する。次いで、図2を参照しながら、本実施形態に係る高周波電力増幅器100の構成例及び半導体パッケージPの構成例について説明する。次いで、図3〜図5を参照しながら、本実施形態に係る半導体パッケージPの構造について説明する。次いで、図6を参照しながら、本実施形態に係る半導体パッケージPの製造工程について説明する。次いで、図7を参照しながら、本実施形態の一変形例に係る半導体パッケージPの構造について説明する。

【0019】

<1:従来例(高周波電力増幅器10の構成例)>

まず、図1を参照しながら、従来の高周波電力増幅器10の構成について述べる。図1に示した高周波電力増幅器10の構成は、一般的なドハティアンプやプッシュプルアンプの回路構成の一例である。

【0020】

図1に示すように、高周波電力増幅器10は、電力分配器11、キャパシタ12A及び12B、直流電源13A及び13B、位相変換回路14A及び14B、整合回路15A及び15B、半導体装置16A及び16B、整合回路17A及び17B、位相変換回路18A及び18B、直流電源19A及び19B、キャパシタ20A及び20B、そして、電力合成器21により構成される。

【0021】

キャパシタ12A及び12Bには、電力分配器11で分配されたRF信号がそれぞれ入力される。また、キャパシタ12A及び12Bの出力は、それぞれ位相変換回路14A及び14Bの入力に接続される。また、キャパシタ12A及び12Bの出力と位相変換回路14A及び14Bの入力とを接続する線路には、それぞれ直流電源13A及び13Bが接続される。また、位相変換回路14A及び14Bの出力は、それぞれ整合回路15A及び15Bの入力に接続される。また、整合回路15A及び15Bの出力は、それぞれ半導体装置16A及び16Bの入力に接続される。なお、これら半導体装置16A及び16Bは、電力増幅器である。

【0022】

半導体装置16A及び16Bの出力は、それぞれ整合回路17A及び17Bの入力に接続される。また、整合回路17A及び17Bの出力は、それぞれ位相変換回路18A及び18Bの入力に接続される。また、位相変換回路18A及び18Bの出力は、それぞれキャパシタ20A及び20Bの入力に接続される。また、位相変換回路18A及び18Bの出力とキャパシタ20A及び20Bの入力とを接続する線路には、それぞれ直流電源19A及び19Bが接続される。また、キャパシタ20A及び20Bから出力されたRF信号は、電力合成器21に入力され、合成されて出力される。

【0023】

以上、従来の高周波電力増幅器10の構成について説明した。ドハティアンプの場合にはRF信号の位相差は90度に調整され、プッシュプルアンプの場合にはRF信号の位相差は180度に調整される。このような構成の高周波電力増幅器10を半導体パッケージにする場合、位相変換回路14A、14B、18A、18Bを半導体パッケージに含める必要がある。そのため、従来の高周波電力増幅器10を構成する半導体パッケージは、汎用性が低く、小型化が難しく、高コストになっていた。本実施形態に係る高周波電力増幅器100及びこれを成す半導体パッケージPは、上記のような従来の問題を解決するものである。

【0024】

<2:実施形態>

以下、本発明の一実施形態について説明する。本実施形態は、無線通信システムなどに用いられる高周波電力増幅器に関し、特に、複数の半導体装置を収納する半導体パッケージの構造に関する。

【0025】

[2−1:高周波電力増幅器100の構成例]

図2に示すように、本実施形態に係る高周波電力増幅器100は、電力分配器101、位相変換回路102A及び102B、キャパシタ103A及び103B、直流電源104A及び104B、整合回路105A及び105B、半導体装置106A及び106B、整合回路107A及び107B、直流電源108A及び108B、キャパシタ109A及び109B、位相変換回路110A及び110B、電力合成器111により構成される。なお、各構成要素の接続関係については、図2に示した通りである。

【0026】

図1に示した従来の高周波電力増幅器10と、図2に示した本実施形態に係る高周波電力増幅器100との主要な違いは、位相変換回路102A、102B、110A、110Bの接続関係にある。図2に示すように、本実施形態に係る高周波電力増幅器100の場合、位相変換回路102A及び102Bは電力分配器101の直後に設けられ、位相変換回路110A及び110Bは電力合成器111の直前に設けられている。そのため、位相変換回路102A、102B、110A、110Bを半導体パッケージPの外側に設けることが可能になる。

【0027】

言い換えると、本実施形態の場合、キャパシタ103A及び103B、直流電源104A及び104B、整合回路105A及び105B、半導体装置106A及び106B、整合回路107A及び107B、直流電源108A及び108B、キャパシタ109A及び109Bを含む半導体パッケージPを構成することが可能になる。位相変換回路102A、102B、110A、110Bが半導体パッケージPの外部に設置可能になることで、半導体パッケージP内の再設計を必要とせずに回路構成を変更することができるようになる。その結果、高周波電力増幅器100の汎用性が向上する。

【0028】

[2−2:半導体パッケージPの構造]

次に、図3〜図5を参照しながら、本実施形態に係る半導体パッケージPの構造について説明する。図3は、本実施形態に係る半導体パッケージPの上面図である。図4は、図3の半導体パッケージPをX方向に見た側面図である。図5は、図3の半導体パッケージPをI−I線に沿って切断した場合の断面を示す断面図である。

【0029】

まず、図3を参照する。図3に示すように、半導体パッケージPは、接地導体131(ヒートシンク)と、整合回路基板132と、半導体素子133(電力増幅器)と、導体134と、フレーム135と、接続端子136(リード)と、金ワイヤ137とを含む。また、図4及び図5に示すように、半導体パッケージPは、高周波基板130をさらに含む。なお、半導体パッケージPの筐体は、接地導体131及びフレーム135で形成された容器により構成される。

【0030】

図3に示すように、接地導体131上には、2つの半導体素子133が設けられている。また、各半導体素子133の前段には整合回路基板132が設けられており、互いに金ワイヤ137を介して電気的に接続されている。同様に、各半導体素子133の後段にも整合回路基板132が設けられており、互いに金ワイヤ137を介して電気的に接続されている。また、各整合回路基板132は、金ワイヤ137を介して導体134(後述する下層の導体134)に電気的に接続されている。

【0031】

また、図4及び図5に示すように、半導体パッケージPには、下層の導体134を挟むように2層の高周波基板130が設けられている。また、上層及び下層の導体134には、それぞれ接続端子136が電気的に接続されている。なお、図4の符号Cで示した領域において、高周波基板130を挟む上層及び下層の導体134によりキャパシタが形成される。また、上層の導体134には高周波成分が流れ、下層の導体134には高周波成分と直流成分とが流れる。このように、上層及び下層の導体134によりキャパシタを形成することにより、半導体パッケージPの外部に直流成分が漏れないようにしている。

【0032】

先に述べたように、位相変換回路110A及び110Bを半導体パッケージPの外部に出したことで、汎用性の向上と半導体パッケージPの小型化が実現可能になる。つまり、ドハティアンプに必要な90度の位相差にも、プッシュプルアンプに必要な180度の位相差にも、パッケージ内を再設計すること無しに、半導体パッケージPの外の回路構成を変更するだけで対応可能になるため、高周波電力増幅器100の汎用性を損なわず、低コストとなる。さらに、高周波基板130を挟んだ一対の導体134によりキャパシタが形成されるため、キャパシタを半導体パッケージPに含む更なる小型化が可能になる。

【0033】

[2−3:半導体パッケージPの製造工程]

次に、図6を参照しながら、本実施形態に係る半導体パッケージPの製造工程について説明する。なお、各構成要素の接続は、半田付けやロウ付けで実現される。

【0034】

図6に示すように、まず、接地導体131を用意する(工程S1)。このとき、位置合わせや高さ合わせのために、必要に応じて高周波基板130が入るくぼみを加工する。次に、リード(接続端子136)及び金ワイヤ137が接続される接続部を加工した2層の高周波基板130(例えば、セラミック基板等)を用意し、下層の導体134を2層の高周波基板130で挟み、上層の導体134を上層の高周波基板130上に設置する(工程S2)。次に、工程S1で用意したヒートシンク基材(接地導体131)と、工程S2で用意した高周波基板130とを接続する(工程S3)。次に、ヒートシンク基材(接地導体131)にフレーム135を接続する(工程S4)。次に、リード(接続端子136)を上層及び下層の導体134に接続する(工程S5)。

【0035】

以上、本実施形態に係る半導体パッケージPの製造工程について説明した。

【0036】

[2−4:変形例(半導体パッケージPの構造)]

ここで、図7を参照しながら、本実施形態の一変形例に係る半導体パッケージPの構造について説明する。図3〜図5に示した半導体パッケージPは、上層の導体134に高周波成分、下層の導体134に高周波成分及び直流成分が流れる構造であった。しかし、図7に示した半導体パッケージPの構造にすると、上層の導体134に高周波成分及び直流成分が流れ、下層の導体134に高周波成分が流れるようになる。このような変形例についても、本実施形態の技術的範囲に属する。

【0037】

以上、添付図面を参照しながら本発明の好適な実施形態について説明したが、本発明は係る例に限定されないことは言うまでもない。当業者であれば、特許請求の範囲に記載された範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

【0038】

例えば、上記の説明においては、複数の半導体素子をパッケージ内に収容する構成について述べてきたが、1つの半導体素子をパッケージ内に収容する構成の場合にも、パッケージ内に直流カットのキャパシタを設ける構成とすることで小型化に寄与する。つまり、図3〜図5及び図7に示した半導体パッケージPにおいて、一方の半導体素子133に対応する構成要素を省略した構成も有用である。

【符号の説明】

【0039】

100 高周波電力増幅器

101 電力分配器

102A、102B 位相変換回路

103A、103B キャパシタ

104A、104B 直流電源

105A、105B 整合回路

106A、106B 半導体装置

107A、107B 整合回路

108A、108B 直流電源

109A、109B キャパシタ

110A、110B 位相変換回路

111 電力合成器

130 高周波基板

131 接地導体

132 整合回路基板

133 半導体素子

134 導体

135 フレーム

136 接続端子

137 金ワイヤ

【特許請求の範囲】

【請求項1】

接地導体と、

前記接地導体の上部に設けられた2層の高周波基板と、

上層の前記高周波基板を挟むように設けられた一対の導体と、

を含む

ことを特徴とする、半導体パッケージ。

【請求項2】

上層の前記高周波基板を挟むように設けられた前記一対の導体のそれぞれに接続された一対の接続端子と、

下層の前記高周波基板に接して設けられた他方の前記導体とワイヤを介して接続された整合回路基板と、

前記整合回路基板とワイヤを介して接続された半導体素子と、

をさらに含む

ことを特徴とする、請求項1に記載の半導体パッケージ。

【請求項3】

前記接続端子は、前記半導体パッケージの外部にある位相変換回路に接続される

ことを特徴とする、請求項2に記載の半導体パッケージ。

【請求項4】

一対の前記半導体素子を含み、

前記各半導体素子に対応して、前記2層の高周波基板、前記一対の導体、前記一対の接続端子、及び前記整合回路基板がそれぞれ設けられている

ことを特徴とする、請求項2又は3に記載の半導体パッケージ。

【請求項5】

前記半導体パッケージは、ドハティアンプ及び/又はプッシュプルアンプの一部を成す電力増幅器である

ことを特徴とする、請求項1〜4のいずれか1項に記載の半導体パッケージ。

【請求項6】

下層の高周波基板上に第1の導体を設置する工程と、

前記第1の導体上に上層の高周波基板を設置する工程と、

前記上層の高周波基板上に第2の導体を設置する工程と、

前記下層の高周波基板を接地導体と接続する工程と、

を含む

ことを特徴とする、半導体パッケージの製造方法。

【請求項7】

前記接地導体上にフレームを接続する工程と、

前記第1の導体に第1の接続端子を接続する工程と、

前記第2の導体に第2の接続端子を接続する工程と、

をさらに含む

ことを特徴とする、請求項6に記載の半導体パッケージの製造方法。

【請求項8】

前記第1及び第2の接続端子は、前記半導体パッケージの外部にある位相変換回路に接続される

ことを特徴とする、請求項7に記載の半導体パッケージの製造方法。

【請求項1】

接地導体と、

前記接地導体の上部に設けられた2層の高周波基板と、

上層の前記高周波基板を挟むように設けられた一対の導体と、

を含む

ことを特徴とする、半導体パッケージ。

【請求項2】

上層の前記高周波基板を挟むように設けられた前記一対の導体のそれぞれに接続された一対の接続端子と、

下層の前記高周波基板に接して設けられた他方の前記導体とワイヤを介して接続された整合回路基板と、

前記整合回路基板とワイヤを介して接続された半導体素子と、

をさらに含む

ことを特徴とする、請求項1に記載の半導体パッケージ。

【請求項3】

前記接続端子は、前記半導体パッケージの外部にある位相変換回路に接続される

ことを特徴とする、請求項2に記載の半導体パッケージ。

【請求項4】

一対の前記半導体素子を含み、

前記各半導体素子に対応して、前記2層の高周波基板、前記一対の導体、前記一対の接続端子、及び前記整合回路基板がそれぞれ設けられている

ことを特徴とする、請求項2又は3に記載の半導体パッケージ。

【請求項5】

前記半導体パッケージは、ドハティアンプ及び/又はプッシュプルアンプの一部を成す電力増幅器である

ことを特徴とする、請求項1〜4のいずれか1項に記載の半導体パッケージ。

【請求項6】

下層の高周波基板上に第1の導体を設置する工程と、

前記第1の導体上に上層の高周波基板を設置する工程と、

前記上層の高周波基板上に第2の導体を設置する工程と、

前記下層の高周波基板を接地導体と接続する工程と、

を含む

ことを特徴とする、半導体パッケージの製造方法。

【請求項7】

前記接地導体上にフレームを接続する工程と、

前記第1の導体に第1の接続端子を接続する工程と、

前記第2の導体に第2の接続端子を接続する工程と、

をさらに含む

ことを特徴とする、請求項6に記載の半導体パッケージの製造方法。

【請求項8】

前記第1及び第2の接続端子は、前記半導体パッケージの外部にある位相変換回路に接続される

ことを特徴とする、請求項7に記載の半導体パッケージの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−74249(P2013−74249A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−214353(P2011−214353)

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000000295)沖電気工業株式会社 (6,645)

【Fターム(参考)】

[ Back to top ]