半導体パッケージ、配線基板、及びリフロー炉

【課題】複数の金属ボール端子を備えた半導体パッケージをリフロー法により配線基板に実装する際に、金属ボール端子の溶融状態を正確に把握する。

【解決手段】複数の金属ボール端子のうち四隅の金属ボール端子15A〜15Dはその他の金属ボール端子14よりも相対的に径が小さい導通検出用の金属ボール端子であり、導通検出用の金属ボール端子15A〜15Dの径が式(X)を充足し、互いに対角にある2個の導通検出用の金属ボール端子15Aと15C、15Bと15Dが配線16を介して接続されている。

d2≧d1−x・・・(X)

(上記式中、d1は導通検出用ではない金属ボール端子の径、d2は導通検出用の金属ボール端子の径、xは配線基板上に半導体パッケージを載置した時点に対する金属ボール端子の溶融後の半導体パッケージの沈み込み量を各々示す。)

【解決手段】複数の金属ボール端子のうち四隅の金属ボール端子15A〜15Dはその他の金属ボール端子14よりも相対的に径が小さい導通検出用の金属ボール端子であり、導通検出用の金属ボール端子15A〜15Dの径が式(X)を充足し、互いに対角にある2個の導通検出用の金属ボール端子15Aと15C、15Bと15Dが配線16を介して接続されている。

d2≧d1−x・・・(X)

(上記式中、d1は導通検出用ではない金属ボール端子の径、d2は導通検出用の金属ボール端子の径、xは配線基板上に半導体パッケージを載置した時点に対する金属ボール端子の溶融後の半導体パッケージの沈み込み量を各々示す。)

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体基板の底面に格子状に配置された複数の金属ボール端子を備え、リフロー法により、複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装される半導体パッケージ、及びこの半導体パッケージが実装される配線基板に関するものである。

本発明はまた、上記半導体パッケージを配線基板に実装する際に用いるリフロー炉に関するものである。

【背景技術】

【0002】

LSIの多ピン化や実装の高密度化の要求が高まり、BGA(Ball Grid Array)パッケージと呼ばれる格子状に配置される複数の半田ボール端子により多端子・高密度実装を可能とするICパッケージが実用化されている。

図7、図8を参照して、一般的なBGAパッケージの構造について説明する。図7は概略断面図、図8は底面図である。

【0003】

図示するBGAパッケージ100において、半導体基板(サブストレート基板)101に搭載された半導体チップ102上のボンディングパッド(図示せず)と半導体基板101上のボンディングパッド(図示せず)とがボンディングワイヤ103により電気的に接続されている。

半導体基板101上のボンディングパッドは、基板101上の配線や基板101内に開孔されたビアホールによる層間接続を介して、基板101底面に格子状に配置された複数の半田ボール端子104に電気的に接続されている。

図8に示すように、半導体基板101の底面には、サイズが均等な複数の半田ボール端子104が格子状に配置されている。

BGAパッケージ100は以上の構成により、半導体チップ102からの信号をパッケージ外部に引き出す電気的導通構造を有している。

BGAパッケージ100では、内部構造保護のため、半導体チップ102やボンディングワイヤ103は封止樹脂105により樹脂封止されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002-289645号公報

【特許文献2】特開2003-068806号公報

【特許文献3】特開2005-235854号公報

【特許文献4】特開平08-037357号公報

【特許文献5】特開平11-054881号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図7、図8に示したBGAパッケージは、BGAパッケージの複数の半田ボール端子が接合される複数のランドを備えた配線基板に実装される。この実装は通常、以下に記載のリフロー法によってなされる。

まず配線基板上の複数のランドにそれぞれクリーム半田を塗布し、その上にBGAパッケージを搭載する。このとき、各ランドとそれに対応したBGAパッケージの半田ボール端子とを正確に位置合わせして、配線基板上にBGAパッケージを載置する。この状態で、配線基板とBGAパッケージとをリフロー炉の中に入れ、半田が溶融する高温に加熱して半田を溶融し、その後炉の温度を下げて半田を再度凝固させることにより、配線基板とBGAパッケージの半田ボールとが接合される。

【0006】

従来、BGAパッケージの配線基板への実装においては、リフロー工程において半田溶融の状況を把握することができない。そのため、リフローによる半田溶融が不充分となり、接合不良が生じる恐れがある。また、確実に接合するためにリフロー加熱の時間を長くすると、BGAパッケージと配線基板に熱ダメージを与える恐れがあり、エネルギー効率が低下し、リフロー時間も長くなってしまう。

【0007】

本発明は上記事情に鑑みてなされたものであり、半導体基板の底面に格子状に配置された複数の金属ボール端子を備えた半導体パッケージを、リフロー法により、複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装する際に、金属ボール端子の溶融状態を正確に把握して、半導体パッケージの金属ボール端子と配線基板のランドとを確実に接合でき、かつ半導体パッケージと配線基板の過度な加熱を抑制することが可能な半導体パッケージ、配線基板、及びリフロー炉を提供することを目的とするものである。

【課題を解決するための手段】

【0008】

本発明の半導体パッケージは、

半導体基板の底面に格子状に配置された複数の金属ボール端子を備え、リフロー法により、前記複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装される半導体パッケージであって、

前記複数の金属ボール端子のうち四隅の金属ボール端子はその他の金属ボール端子よりも相対的に径が小さい導通検出用の金属ボール端子であり、当該導通検出用の金属ボール端子の径が下記関係式(X)を充足するものであり、かつ互いに対角にある2個の導通検出用の金属ボール端子同士が配線を介して接続されたものである。

d2≧d1−x・・・(X)

(上記式中、d1は導通検出用ではない金属ボール端子の径、d2は導通検出用の金属ボール端子の径、xは配線基板上に半導体パッケージを載置した時点に対する金属ボール端子の溶融後の半導体パッケージの沈み込み量を各々示す。)

【0009】

本発明の配線基板は、

リフロー法により上記の本発明の半導体パッケージが実装される前記配線基板であって、

前記導通検出用の金属ボール端子と当該金属ボール端子が接合される導通検出用のランドとの導通を検出するための配線構造を備えたものである。

【0010】

本発明のリフロー炉は、

リフロー法により上記の本発明の配線基板に上記の本発明の半導体パッケージを実装するためのリフロー炉であって、

前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を検出するための検出機構を備えたものである。

【発明の効果】

【0011】

本発明によれば、半導体基板の底面に格子状に配置された複数の金属ボール端子を備えた半導体パッケージを、リフロー法により、複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装する際に、金属ボール端子の溶融状態を正確に把握して、半導体パッケージの金属ボール端子と配線基板のランドとを確実に接合でき、かつ半導体パッケージと配線基板との過度な加熱を抑制することが可能な半導体パッケージ、配線基板、及びリフロー炉を提供することができる。

本発明の半導体パッケージでは、互いに対角にある2個の導通検出用の半田ボール端子同士を接続するようにしている。かかる構成では、配線基板に対して半導体パッケージをどの向きで搭載しても配線基板側の導通配線パターンを同じ配線ルールで対応できるため、配線パターンの設計が容易であり、半導体パッケージの搭載向きや配線パターンの人為的ミスを防止できる。

【図面の簡単な説明】

【0012】

【図1】本発明に係る一実施形態のBGAパッケージの概略断面図である。

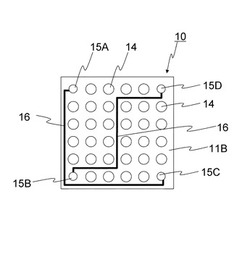

【図2】図1のBGAパッケージの底面図である。

【図3】本発明に係る一実施形態の配線基板の上面図である。

【図4】配線基板のその他の例を示す上面図である。

【図5】BGAパッケージの配線基板への実装工程を示す断面図であり、(A)は半田溶融前、(B)は半田溶融後を各々示す図である。

【図6】リフロー炉の斜視図である。

【図7】従来のBGAパッケージの概略断面図である。

【図8】図7のBGAパッケージの底面図である。

【発明を実施するための形態】

【0013】

「第1実施形態」

図面を参照して、本発明に係る一実施形態のBGAパッケージ、配線基板、及びリフロー炉の構成について説明する。

図1はBGAパッケージの概略断面図、図2はBGAパッケージの底面図である。

図3は配線基板の一例を示す上面図、図4は配線基板のその他の例を示す上面図である。

図5はBGAパッケージの配線基板への実装工程を示す断面図であり、(A)は半田溶融前、(B)は半田溶融後を各々示している。

図6はリフロー炉の斜視図であり、内部透視図である。

視認しやすくするため、図面上は各構成の縮尺や位置を実際のものとは適宜異ならせてある。

【0014】

図1に示すように、本実施形態のBGAパッケージ(半導体パッケージ)10において、半導体基板(サブストレート基板)11に搭載された半導体チップ12上のボンディングパッド(図示せず)と半導体基板11上のボンディングパッド(図示せず)とがボンディングワイヤ13により電気的に接続されている。

半導体基板11上のボンディングパッドは、基板11上の配線や基板11内に開孔されたビアホールによる層間接続を介して、基板底面11Bに格子状に配置された複数の半田ボール端子(金属ボール端子)14、15に電気的に接続されている。

複数の半田ボール端子14、15は外部接続用の端子であり、図2に示すように基板底面11Bに格子状に配置されている。

BGAパッケージ10は以上の構成により、半導体チップ12からの信号をパッケージ外部に引き出す電気的導通構造を有している。

BGAパッケージ10では、内部構造保護のため半導体チップ12やボンディングワイヤ13は封止樹脂17により樹脂封止されている。

【0015】

図1中、複数の半田ボール端子のうち四隅の半田ボール端子に符号15を付し、その他の半田ボール端子に符号14を付してある。図2中、四隅の半田ボール端子に符号15A〜15Dを付してある。

【0016】

図1、図2に示すように、本実施形態において、四隅の半田ボール端子15A〜15D以外の半田ボール端子14は通常使用されるサイズであり、四隅の半田ボール端子15A〜15Dはそれよりも径が小さく設定されている。径の小さい四隅の半田ボール端子15A〜15Dは、導通検出用の半田ボール端子である。

【0017】

図2に示すように、基板底面11Bにおいて、互いに対角にある導通検出用の半田ボール端子15Aと導通検出用の半田ボール端子15Cとは配線16を介して電気的に接続され、同様に、互いに対角にある導通検出用の半田ボール端子15Bと導通検出用の半田ボール端子15Dとは配線16を介して電気的に接続されている。

なお、互いに対角にある2個の導通検出用の半田ボール端子間の配線接続については、図示するものに限定されず、適宜設計できる。

【0018】

図3に示す配線基板20において、符号21はBGAパッケージ10の搭載位置を示している。配線基板20上には、BGAパッケージ10の複数の半田ボール端子14、15が半田付けされるランド24、25が格子状に設けられている。

各半田ボール端子14と各ランド24とが対応し、各半田ボール端子15と各ランド25とが対応している。ランド25は導通検出用の半田ボール端子15が接合される導通検出用のランドである。導通検出用のランド25として、四隅の半田ボール端子15A〜15Dに対応して、4個のランド25A〜25Dが設けられている。

【0019】

配線基板20には、導通検出用の半田ボール端子15A〜15Dと導通検出用のランド25A〜25Dとの導通を検出するための一対の検出用端子22が設けられている。

配線基板20にはまた、配線基板20にBGAパッケージ10を実装した状態で、半田ボール端子15A〜15Dとランド25A〜25Dと一対の検出用端子22とが電気的に接続されるよう、配線23が形成されている。

本実施形態において、一方の検出用端子22と導通検出用のランド25Aとが配線23を介して接続され、他方の検出用端子22と導通検出用のランド25Bとが配線23を介して接続されている。導通検出用のランド25Cと導通検出用のランド25Dとが配線23を介して接続されている。

【0020】

図2に示したように、半導体パッケージ10の底面11Bにおいて、互いに対角にある導通検出用の半田ボール端子15Aと15C、互いに対角にある導通検出用の半田ボール端子15Bと15Dはそれぞれ配線16を介して接続されている。したがって、配線基板20にBGAパッケージ10が実装され、配線基板20上の導通検出用のランド25A〜25Dに導通検出用の半田ボール端子15A〜15Dが半田付けされると、4個の導通検出用の半田ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dと2個の検出用端子22とが導通される。すなわち、配線基板20には、一箇所に設けた一対の検出用端子22により、4個の導通検出用の半田ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとの導通が一括検出される配線構造が形成されている。

なお、配線基板20における一対の検出用端子22の位置や配線構造については適宜設計変更できる。

【0021】

図3に示す配線基板20は1個のBGAパッケージ10を搭載可能なものであるが、複数のBGAパッケージ10を搭載可能なものでもよい。

図4に示す配線基板26は2個のBGAパッケージ10を搭載可能なものである。

図4に示す例においては、一箇所に設けた一対の検出用端子22により、2個のBGAパッケージ10の4個の導通検出用の半田ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとの導通が一括検出される配線構造が形成されている。一対の検出用端子22はBGAパッケージ10ごとに設けても構わない。

【0022】

図5(A)、(B)を参照して、BGAパッケージ10の配線基板20への実装方法と、半田ボール端子14、15のサイズ関係について説明する。

【0023】

BGAパッケージ10を配線基板20に実装する方法は以下の通りである。

まず図5(A)に示すように、配線基板20上の複数のランド24、25にそれぞれクリーム半田を塗布し、その上にBGAパッケージ10を載置する。このとき、各ランド24、25とそれに対応したBGAパッケージ10の半田ボール端子14、15とを正確に位置合わせして、配線基板20上にBGAパッケージ10を載置する。

上記状態で、配線基板20とBGAパッケージ10とをリフロー炉の加熱室内に載置し、半田が溶融する高温に加熱して半田を融かし、その後温度を下げて半田を再度凝固させることにより、図5(B)に示すように、配線基板20のランド24、25とBGAパッケージ10の半田ボール端子14、15とを接合する。

【0024】

図5(A)、(B)に示すように、BGAパッケージ10をリフロー炉にて高温に晒し半田ボール端子14、15が溶融すると、自重によりBGAパッケージ10の沈み込みが発生する。

半田溶融後のBGAパッケージ10の沈み込み量をxとする。通常サイズの半田ボール端子14の径をd1、四隅の小さい半田ボール端子15の径をd2とすると、d2は下記関係式(X)を充足するようにする。

d2≧d1−x・・・(X)

【0025】

上記関係式を充足する四角の径の小さい導通検出用の半田ボール端子15は、図5(A)に示す時点、すなわちBGAパッケージ10を配線基板20に載置した半田溶融前の時点においては、配線基板20上の導通検出用のランド25と接触せず電気的導通はない。

四角の径の小さい導通検出用の半田ボール端子15は、図5(B)に示す時点、すなわちリフロー加熱によりBGAパッケージ10の沈み込みが発生した半田溶融後の時点において、配線基板20上の導通検出用のランド25と接触し電気的導通が得られるようになる。導通検出用の半田ボール端子15と導通検出用のランド25との導通が検出された時点でリフロー加熱が充分に行われたことが判断できる。

【0026】

したがって、本実施形態では、BGAパッケージ10をリフロー法により配線基板20に実装する際に、半田ボール端子14、15の溶融状態を正確に把握することができる。そのため、半導体パッケージ10の金属ボール端子14、15と配線基板20のランド24、25とを確実に接合できる。また、必要最小限だけリフロー加熱することが可能となるので、半導体パッケージ10と配線基板20とが過度に加熱されてこれらが熱ダメージを受ける恐れがなく、エネルギー効率も良く、リフロー時間も短縮できる。

【0027】

本実施形態では、BGAパッケージ10の四隅に導通検出用の半田ボール端子15A〜15Dを設けているので、パッケージ10全体の導通を良好に検出できる。

【0028】

本実施形態ではまた、互いに対角にある導通検出用の半田ボール端子15Aと導通検出用の半田ボール端子15Cとを接続し、互いに対角にある導通検出用の半田ボール端子15Bと導通検出用の半田ボール端子15Dとを接続している。

かかる構成では、図3に示す配線基板20に対して半導体パッケージ10をどの向きで搭載しても、配線基板20側の導通配線パターンを同じ配線ルールで対応できる。そのため、半導体パッケージ10の搭載向きはどの向きでもよく、半導体パッケージ10の搭載向きによらず、配線基板20に同じパターンで配線パターンを形成すればよい。したがって、本実施形態では、配線パターンの設計が容易であり、半導体パッケージ10の搭載向きや配線パターンの人為的ミスを防止できる。

半導体パッケージ10の搭載向きによらず同じ配線パターンを適用できることは、図4に示した配線基板26でも同様である。したがって、1つの配線基板に複数の半導体パッケージを搭載する場合も、配線パターンの設計が容易であり、半導体パッケージ10の搭載向きや配線パターンの人為的ミスを防止できる。

【0029】

本実施形態ではまた、配線基板20に、すべての導通導通検出用の金属ボール端子15A〜15Dと導通導通検出用のランド25A〜25Dとの導通を一括検出できる配線構造を設けている。

すなわち、本実施形態では、半田接合が良好なときには、4個の導通検出用の金属ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとが電気的に繋がり、これらの導通が一括検出され、一箇所でも導通検出用の金属ボール端子15と導通検出用のランド25とが良好に接合されていなければ、導通は検出されない。したがって、検出が確実で、しかもシンプルである。

一括検出が可能なことは、図4に示した配線基板26でも同様である。

【0030】

図6に示すリフロー炉30はリフロー法により配線基板20にBGAパッケージ10を実装するための炉である。リフロー炉30は加熱室31を有し、その内部にはヒータ32が設けられている。

【0031】

リフロー法によりBGAパッケージ10を配線基板20に実装する際には、配線基板20のランド24、25にクリーム半田を塗布し、配線基板20にBGAパッケージ10を載置した状態で、これらをリフロー炉30の加熱室31内に搭載し、半田が溶融する温度に加熱して半田のリフローが行われる。

リフロー炉30の加熱室31内には、配線基板20の一対の検出用端子22と接続される一対の検出用端子34が設けられている。配線基板20の一対の検出用端子22とリフロー炉30の一対の検出用端子34とは、一対の耐熱ケーブル33を介して接続される。

図では、一対の検出用端子22、一対の耐熱ケーブル33、及び一対の検出用端子34をそれぞれ1つにまとめて図示してある。

一対の検出用端子34は、4個の導通検出用の金属ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとの導通を電気的に検出する検出器35に接続されている。

【0032】

リフロー炉30では、一対の耐熱ケーブル33、一対の検出用端子34、及び検出器35により、4個の導通検出用の金属ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとの導通を電気的に検出する検出機構が構成されている。そして、検出器35による検出結果は表示部37に表示されるようになっている。

【0033】

リフロー炉30にはまた、検出器35による検出結果が入力され、この検出結果に基づいてヒータ32の加熱を制御する制御回路(加熱制御機構)36が設けられている。この制御回路36は、すべての導通検出用の金属ボール端子15A〜15Dと導通検出用のランド25A〜25Dとの導通が検出された時点で、配線基板20と半導体パッケージ10のリフロー加熱を終了するよう、ヒータ32の加熱を制御する。

かかる制御機構により、半導体パッケージ10の金属ボール端子14、15と配線基板20のランド24、25とを確実に接合でき、かつ半導体パッケージ10と配線基板20とが過度に加熱されることを安定的に抑制することができる。

【0034】

リフロー炉30には上記加熱制御機構を設ける代わりに、検出器35によりすべての導通検出用の金属ボール端子15A〜15Dと導通検出用のランド25A〜25Dとの導通が検出された時点で、配線基板20と半導体パッケージ10を取り出す機構を備える構成としてもよい。

かかる構成でも、半導体パッケージ10の金属ボール端子14、15と配線基板20のランド24、25とを確実に接合でき、かつ半導体パッケージ10と配線基板20とが過度に加熱されることを安定的に抑制することができる。

【0035】

リフロー炉30に上記加熱制御機構や配線基板20と半導体パッケージ10の取出し機構を設ける代わりに、表示部37に表示された検出結果に基づいて、作業者が、導通検出用の金属ボール端子15A〜15Dと導通検出用のランド25A〜25Dとの導通が検出された時点で、配線基板20と半導体パッケージ10のリフロー加熱を終了するか、あるいはリフロー炉30の加熱室31から配線基板20とBGAパッケージ10とを取り出すようにしてもよい。

【0036】

本発明の関連技術としては、「背景技術」の項に挙げた特許文献1〜5がある。

【0037】

特許文献1には、配線基板の四隅にそれぞれ、その他のランドを2個連結した大きさを有する2つの補強用ランド(22)が設けられ、補強用ランド(22)の隣のランド(23)と、この補強用ランドから対角線上に離隔する位置の他の補強用ランド(22)とが配線(24)により接続された構成が記載されている(図1、段落0022)。

特許文献1には、BGA型パッケージの四隅にそれぞれ、4個の補強用ハンダボール(15)が設けられ、補強用ハンダボール(15)の隣のハンダボール(16)と、この補強用ハンダボール(15)から対角線上に離隔する位置の他の補強用ハンダボール(15)とが基板に設けられた配線(図示なし)により接続された構成が記載されている(図2、段落0022)。

特許文献1に記載の構成では、2個の補強用半田ボール(15)が1個の補強用ランド(22)に接合される。

【0038】

特許文献1の[発明の効果]の項(段落0034)には、強い衝撃力を受けて、補強用半田ボールが補強用ランドから剥がれるのに加えて、その隣の半田ボールが隣のランドから剥がれた場合でも、他の補強用ランドとこれに接続された他の補強用半田ボールを介して信号を迂回させて隣の半田ボールに信号を伝達するので、隣のランドと隣の半田ボールとの間の接続関係が維持されることが記載されている。

【0039】

特許文献1は半田ボールとランドとの導通を検出可能としたものではない。

また、「互いに対角にある半田ボール同士を接続することで、配線基板に対して半導体パッケージをどの向きで搭載しても配線基板側の導通配線パターンを同じ配線ルールで対応できるため、半導体パッケージの搭載向きや配線基板の配線パターンの人為的ミスを防止できる。」という本発明の効果については記載がない。

【0040】

特許文献2〜5には、BGAパッケージの半田ボールの一部を導通検出用の半田ボールとし、配線基板のランドの一部を導通検出用ランドとし、配線基板に導通検出用の半田ボールと導通検出用ランドとの導通を検査するための配線構造を設けた構成が記載されている。

【0041】

特許文献2には、BGAパッケージの四隅にそれぞれ互いに配線を介して接続された2個の導通検出用の半田ボール(11a〜11h)を設け、配線基板に導通検出用の半田ボールが接合される導通検出用ランド(21a〜21h)を設け、配線基板に導通検出用の半田ボールと導通検出用ランドとの導通を検査するための複数の配線(25a〜25e)と2個の導通検出用パッド(23a、23b)を設け、一括検出を可能とした構成が記載されている(図5〜図6)。

特許文献2において、導通検出用の半田ボールの径は通常の半田ボールと同一である。

【0042】

特許文献3には、BGAパッケージの四隅と中央部にそれぞれ互いに配線を介して接続された2個の導通検出用の半田ボール(半田ボールのランド3a、3bを参照)を設け、配線基板に導通検出用の半田ボールが接合される導通検出用ランド(5a、5b)を設け、配線基板に導通検出用の半田ボールと導通検出用ランドとの導通を検査するための複数の配線と複数の導通検出用端子(5c、5c')を設けた構成が記載されている(図1〜図2)。

特許文献3では、互いに配線を介して接続された2つの導通検出用の半田ボールごとに一対の導通検出用端子(5c、5c')を設けられており、導通試験装置6で各対の導通検出用端子(5c、5c')間の導通を検査するようになっている(段落0018)。

特許文献3において、導通検出用の半田ボールの径は通常の半田ボールと同一である。

【0043】

特許文献4には、BGAパッケージの四隅にそれぞれ径の小さい導通検出用の半田ボール(2b)を設け、この導通検出用の半田ボール(2b)と隣の半田ボールとを接続し、配線基板に導通検出用の半田ボールが接合される導通検出用ランド(符号なし)を設け、配線基板に導通検出用の半田ボールと導通検出用ランドとの導通を検査するための複数の配線(図示なし)を設けた構成が記載されている(図3、図4、段落0028−0030)。

【0044】

特許文献5には、BGAパッケージの四隅及び各辺の中央部にそれぞれ径の小さい導通検出用の半田ボール(14)を設け、BGAパッケージの基板の上面に導通検出用の半田ボールに導通された導通検出用電極(30)を設け、配線基板に導通検出用の半田ボールが接合される導通検出用ランド(22)を設けた構成が記載されている(図2、図3)。

特許文献5では、テスター(70)を用いて導通検出用電極(30)と導通検出用ランド(22)との導通が検査されるようになっている(図3)。

【0045】

特許文献2〜5には、互いに対角にある導通検出用の半田ボール同士を接続した構成や、配線基板とリフロー炉とを接続して導通の有無を検出可能とした構成は記載されていない。

特許文献2〜5に記載の配線構造では、「配線基板に対して半導体パッケージをどの向きで搭載しても配線基板側の導通配線パターンを同じ配線ルールで対応できるため、配線パターンの設計が容易であり、半導体パッケージの搭載向きや配線パターンの人為的ミスを防止できる。」という本発明の効果は得られず、配線接続等のミスが起こりやすい。

【0046】

以上説明したように、本実施形態によれば、BGA半導体パッケージ10をリフロー法により配線基板20に実装する際に、半田ボール端子14、15の溶融状態を正確に把握して、半導体パッケージ10の半田ボール端子14、15と配線基板20のランド24、25とを確実に接合でき、かつ半導体パッケージ10と配線基板20との過度な加熱を抑制することが可能な半導体パッケージ10、配線基板20、及びリフロー炉30を提供することができる。

本実施形態では、互いに対角にある2個の導通検出用の半田ボール端子15同士を接続するようにしている。かかる構成では、配線基板20に対して半導体パッケージ10をどの向きで搭載しても配線基板20側の導通配線パターンを同じ配線ルールで対応できるため、配線パターンの設計が容易であり、半導体パッケージ10の搭載向きや配線基板20の配線パターンの人為的ミスを防止できる。

【0047】

(設計変更)

本発明は上記実施形態に限らず、本発明の趣旨を逸脱しない範囲内において適宜設計変更が可能である。

【符号の説明】

【0048】

10 BGAパッケージ(半導体パッケージ)

11 半導体基板

11B 基板底面

12 半導体チップ

13 ボンディングワイヤ

14 半田ボール端子(金属ボール端子)

15、15A〜15D 導通検出用の半田ボール端子(金属ボール端子)

16 配線

20、26 配線基板

22 検出用端子

23 配線

24 ランド

25、25A〜25D 導通検出用のランド

30 リフロー炉

31 加熱室

32 ヒータ

33 耐熱ケーブル

34 検出用端子

35 検出器

36 制御回路

37 表示部

【技術分野】

【0001】

本発明は、半導体基板の底面に格子状に配置された複数の金属ボール端子を備え、リフロー法により、複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装される半導体パッケージ、及びこの半導体パッケージが実装される配線基板に関するものである。

本発明はまた、上記半導体パッケージを配線基板に実装する際に用いるリフロー炉に関するものである。

【背景技術】

【0002】

LSIの多ピン化や実装の高密度化の要求が高まり、BGA(Ball Grid Array)パッケージと呼ばれる格子状に配置される複数の半田ボール端子により多端子・高密度実装を可能とするICパッケージが実用化されている。

図7、図8を参照して、一般的なBGAパッケージの構造について説明する。図7は概略断面図、図8は底面図である。

【0003】

図示するBGAパッケージ100において、半導体基板(サブストレート基板)101に搭載された半導体チップ102上のボンディングパッド(図示せず)と半導体基板101上のボンディングパッド(図示せず)とがボンディングワイヤ103により電気的に接続されている。

半導体基板101上のボンディングパッドは、基板101上の配線や基板101内に開孔されたビアホールによる層間接続を介して、基板101底面に格子状に配置された複数の半田ボール端子104に電気的に接続されている。

図8に示すように、半導体基板101の底面には、サイズが均等な複数の半田ボール端子104が格子状に配置されている。

BGAパッケージ100は以上の構成により、半導体チップ102からの信号をパッケージ外部に引き出す電気的導通構造を有している。

BGAパッケージ100では、内部構造保護のため、半導体チップ102やボンディングワイヤ103は封止樹脂105により樹脂封止されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002-289645号公報

【特許文献2】特開2003-068806号公報

【特許文献3】特開2005-235854号公報

【特許文献4】特開平08-037357号公報

【特許文献5】特開平11-054881号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図7、図8に示したBGAパッケージは、BGAパッケージの複数の半田ボール端子が接合される複数のランドを備えた配線基板に実装される。この実装は通常、以下に記載のリフロー法によってなされる。

まず配線基板上の複数のランドにそれぞれクリーム半田を塗布し、その上にBGAパッケージを搭載する。このとき、各ランドとそれに対応したBGAパッケージの半田ボール端子とを正確に位置合わせして、配線基板上にBGAパッケージを載置する。この状態で、配線基板とBGAパッケージとをリフロー炉の中に入れ、半田が溶融する高温に加熱して半田を溶融し、その後炉の温度を下げて半田を再度凝固させることにより、配線基板とBGAパッケージの半田ボールとが接合される。

【0006】

従来、BGAパッケージの配線基板への実装においては、リフロー工程において半田溶融の状況を把握することができない。そのため、リフローによる半田溶融が不充分となり、接合不良が生じる恐れがある。また、確実に接合するためにリフロー加熱の時間を長くすると、BGAパッケージと配線基板に熱ダメージを与える恐れがあり、エネルギー効率が低下し、リフロー時間も長くなってしまう。

【0007】

本発明は上記事情に鑑みてなされたものであり、半導体基板の底面に格子状に配置された複数の金属ボール端子を備えた半導体パッケージを、リフロー法により、複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装する際に、金属ボール端子の溶融状態を正確に把握して、半導体パッケージの金属ボール端子と配線基板のランドとを確実に接合でき、かつ半導体パッケージと配線基板の過度な加熱を抑制することが可能な半導体パッケージ、配線基板、及びリフロー炉を提供することを目的とするものである。

【課題を解決するための手段】

【0008】

本発明の半導体パッケージは、

半導体基板の底面に格子状に配置された複数の金属ボール端子を備え、リフロー法により、前記複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装される半導体パッケージであって、

前記複数の金属ボール端子のうち四隅の金属ボール端子はその他の金属ボール端子よりも相対的に径が小さい導通検出用の金属ボール端子であり、当該導通検出用の金属ボール端子の径が下記関係式(X)を充足するものであり、かつ互いに対角にある2個の導通検出用の金属ボール端子同士が配線を介して接続されたものである。

d2≧d1−x・・・(X)

(上記式中、d1は導通検出用ではない金属ボール端子の径、d2は導通検出用の金属ボール端子の径、xは配線基板上に半導体パッケージを載置した時点に対する金属ボール端子の溶融後の半導体パッケージの沈み込み量を各々示す。)

【0009】

本発明の配線基板は、

リフロー法により上記の本発明の半導体パッケージが実装される前記配線基板であって、

前記導通検出用の金属ボール端子と当該金属ボール端子が接合される導通検出用のランドとの導通を検出するための配線構造を備えたものである。

【0010】

本発明のリフロー炉は、

リフロー法により上記の本発明の配線基板に上記の本発明の半導体パッケージを実装するためのリフロー炉であって、

前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を検出するための検出機構を備えたものである。

【発明の効果】

【0011】

本発明によれば、半導体基板の底面に格子状に配置された複数の金属ボール端子を備えた半導体パッケージを、リフロー法により、複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装する際に、金属ボール端子の溶融状態を正確に把握して、半導体パッケージの金属ボール端子と配線基板のランドとを確実に接合でき、かつ半導体パッケージと配線基板との過度な加熱を抑制することが可能な半導体パッケージ、配線基板、及びリフロー炉を提供することができる。

本発明の半導体パッケージでは、互いに対角にある2個の導通検出用の半田ボール端子同士を接続するようにしている。かかる構成では、配線基板に対して半導体パッケージをどの向きで搭載しても配線基板側の導通配線パターンを同じ配線ルールで対応できるため、配線パターンの設計が容易であり、半導体パッケージの搭載向きや配線パターンの人為的ミスを防止できる。

【図面の簡単な説明】

【0012】

【図1】本発明に係る一実施形態のBGAパッケージの概略断面図である。

【図2】図1のBGAパッケージの底面図である。

【図3】本発明に係る一実施形態の配線基板の上面図である。

【図4】配線基板のその他の例を示す上面図である。

【図5】BGAパッケージの配線基板への実装工程を示す断面図であり、(A)は半田溶融前、(B)は半田溶融後を各々示す図である。

【図6】リフロー炉の斜視図である。

【図7】従来のBGAパッケージの概略断面図である。

【図8】図7のBGAパッケージの底面図である。

【発明を実施するための形態】

【0013】

「第1実施形態」

図面を参照して、本発明に係る一実施形態のBGAパッケージ、配線基板、及びリフロー炉の構成について説明する。

図1はBGAパッケージの概略断面図、図2はBGAパッケージの底面図である。

図3は配線基板の一例を示す上面図、図4は配線基板のその他の例を示す上面図である。

図5はBGAパッケージの配線基板への実装工程を示す断面図であり、(A)は半田溶融前、(B)は半田溶融後を各々示している。

図6はリフロー炉の斜視図であり、内部透視図である。

視認しやすくするため、図面上は各構成の縮尺や位置を実際のものとは適宜異ならせてある。

【0014】

図1に示すように、本実施形態のBGAパッケージ(半導体パッケージ)10において、半導体基板(サブストレート基板)11に搭載された半導体チップ12上のボンディングパッド(図示せず)と半導体基板11上のボンディングパッド(図示せず)とがボンディングワイヤ13により電気的に接続されている。

半導体基板11上のボンディングパッドは、基板11上の配線や基板11内に開孔されたビアホールによる層間接続を介して、基板底面11Bに格子状に配置された複数の半田ボール端子(金属ボール端子)14、15に電気的に接続されている。

複数の半田ボール端子14、15は外部接続用の端子であり、図2に示すように基板底面11Bに格子状に配置されている。

BGAパッケージ10は以上の構成により、半導体チップ12からの信号をパッケージ外部に引き出す電気的導通構造を有している。

BGAパッケージ10では、内部構造保護のため半導体チップ12やボンディングワイヤ13は封止樹脂17により樹脂封止されている。

【0015】

図1中、複数の半田ボール端子のうち四隅の半田ボール端子に符号15を付し、その他の半田ボール端子に符号14を付してある。図2中、四隅の半田ボール端子に符号15A〜15Dを付してある。

【0016】

図1、図2に示すように、本実施形態において、四隅の半田ボール端子15A〜15D以外の半田ボール端子14は通常使用されるサイズであり、四隅の半田ボール端子15A〜15Dはそれよりも径が小さく設定されている。径の小さい四隅の半田ボール端子15A〜15Dは、導通検出用の半田ボール端子である。

【0017】

図2に示すように、基板底面11Bにおいて、互いに対角にある導通検出用の半田ボール端子15Aと導通検出用の半田ボール端子15Cとは配線16を介して電気的に接続され、同様に、互いに対角にある導通検出用の半田ボール端子15Bと導通検出用の半田ボール端子15Dとは配線16を介して電気的に接続されている。

なお、互いに対角にある2個の導通検出用の半田ボール端子間の配線接続については、図示するものに限定されず、適宜設計できる。

【0018】

図3に示す配線基板20において、符号21はBGAパッケージ10の搭載位置を示している。配線基板20上には、BGAパッケージ10の複数の半田ボール端子14、15が半田付けされるランド24、25が格子状に設けられている。

各半田ボール端子14と各ランド24とが対応し、各半田ボール端子15と各ランド25とが対応している。ランド25は導通検出用の半田ボール端子15が接合される導通検出用のランドである。導通検出用のランド25として、四隅の半田ボール端子15A〜15Dに対応して、4個のランド25A〜25Dが設けられている。

【0019】

配線基板20には、導通検出用の半田ボール端子15A〜15Dと導通検出用のランド25A〜25Dとの導通を検出するための一対の検出用端子22が設けられている。

配線基板20にはまた、配線基板20にBGAパッケージ10を実装した状態で、半田ボール端子15A〜15Dとランド25A〜25Dと一対の検出用端子22とが電気的に接続されるよう、配線23が形成されている。

本実施形態において、一方の検出用端子22と導通検出用のランド25Aとが配線23を介して接続され、他方の検出用端子22と導通検出用のランド25Bとが配線23を介して接続されている。導通検出用のランド25Cと導通検出用のランド25Dとが配線23を介して接続されている。

【0020】

図2に示したように、半導体パッケージ10の底面11Bにおいて、互いに対角にある導通検出用の半田ボール端子15Aと15C、互いに対角にある導通検出用の半田ボール端子15Bと15Dはそれぞれ配線16を介して接続されている。したがって、配線基板20にBGAパッケージ10が実装され、配線基板20上の導通検出用のランド25A〜25Dに導通検出用の半田ボール端子15A〜15Dが半田付けされると、4個の導通検出用の半田ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dと2個の検出用端子22とが導通される。すなわち、配線基板20には、一箇所に設けた一対の検出用端子22により、4個の導通検出用の半田ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとの導通が一括検出される配線構造が形成されている。

なお、配線基板20における一対の検出用端子22の位置や配線構造については適宜設計変更できる。

【0021】

図3に示す配線基板20は1個のBGAパッケージ10を搭載可能なものであるが、複数のBGAパッケージ10を搭載可能なものでもよい。

図4に示す配線基板26は2個のBGAパッケージ10を搭載可能なものである。

図4に示す例においては、一箇所に設けた一対の検出用端子22により、2個のBGAパッケージ10の4個の導通検出用の半田ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとの導通が一括検出される配線構造が形成されている。一対の検出用端子22はBGAパッケージ10ごとに設けても構わない。

【0022】

図5(A)、(B)を参照して、BGAパッケージ10の配線基板20への実装方法と、半田ボール端子14、15のサイズ関係について説明する。

【0023】

BGAパッケージ10を配線基板20に実装する方法は以下の通りである。

まず図5(A)に示すように、配線基板20上の複数のランド24、25にそれぞれクリーム半田を塗布し、その上にBGAパッケージ10を載置する。このとき、各ランド24、25とそれに対応したBGAパッケージ10の半田ボール端子14、15とを正確に位置合わせして、配線基板20上にBGAパッケージ10を載置する。

上記状態で、配線基板20とBGAパッケージ10とをリフロー炉の加熱室内に載置し、半田が溶融する高温に加熱して半田を融かし、その後温度を下げて半田を再度凝固させることにより、図5(B)に示すように、配線基板20のランド24、25とBGAパッケージ10の半田ボール端子14、15とを接合する。

【0024】

図5(A)、(B)に示すように、BGAパッケージ10をリフロー炉にて高温に晒し半田ボール端子14、15が溶融すると、自重によりBGAパッケージ10の沈み込みが発生する。

半田溶融後のBGAパッケージ10の沈み込み量をxとする。通常サイズの半田ボール端子14の径をd1、四隅の小さい半田ボール端子15の径をd2とすると、d2は下記関係式(X)を充足するようにする。

d2≧d1−x・・・(X)

【0025】

上記関係式を充足する四角の径の小さい導通検出用の半田ボール端子15は、図5(A)に示す時点、すなわちBGAパッケージ10を配線基板20に載置した半田溶融前の時点においては、配線基板20上の導通検出用のランド25と接触せず電気的導通はない。

四角の径の小さい導通検出用の半田ボール端子15は、図5(B)に示す時点、すなわちリフロー加熱によりBGAパッケージ10の沈み込みが発生した半田溶融後の時点において、配線基板20上の導通検出用のランド25と接触し電気的導通が得られるようになる。導通検出用の半田ボール端子15と導通検出用のランド25との導通が検出された時点でリフロー加熱が充分に行われたことが判断できる。

【0026】

したがって、本実施形態では、BGAパッケージ10をリフロー法により配線基板20に実装する際に、半田ボール端子14、15の溶融状態を正確に把握することができる。そのため、半導体パッケージ10の金属ボール端子14、15と配線基板20のランド24、25とを確実に接合できる。また、必要最小限だけリフロー加熱することが可能となるので、半導体パッケージ10と配線基板20とが過度に加熱されてこれらが熱ダメージを受ける恐れがなく、エネルギー効率も良く、リフロー時間も短縮できる。

【0027】

本実施形態では、BGAパッケージ10の四隅に導通検出用の半田ボール端子15A〜15Dを設けているので、パッケージ10全体の導通を良好に検出できる。

【0028】

本実施形態ではまた、互いに対角にある導通検出用の半田ボール端子15Aと導通検出用の半田ボール端子15Cとを接続し、互いに対角にある導通検出用の半田ボール端子15Bと導通検出用の半田ボール端子15Dとを接続している。

かかる構成では、図3に示す配線基板20に対して半導体パッケージ10をどの向きで搭載しても、配線基板20側の導通配線パターンを同じ配線ルールで対応できる。そのため、半導体パッケージ10の搭載向きはどの向きでもよく、半導体パッケージ10の搭載向きによらず、配線基板20に同じパターンで配線パターンを形成すればよい。したがって、本実施形態では、配線パターンの設計が容易であり、半導体パッケージ10の搭載向きや配線パターンの人為的ミスを防止できる。

半導体パッケージ10の搭載向きによらず同じ配線パターンを適用できることは、図4に示した配線基板26でも同様である。したがって、1つの配線基板に複数の半導体パッケージを搭載する場合も、配線パターンの設計が容易であり、半導体パッケージ10の搭載向きや配線パターンの人為的ミスを防止できる。

【0029】

本実施形態ではまた、配線基板20に、すべての導通導通検出用の金属ボール端子15A〜15Dと導通導通検出用のランド25A〜25Dとの導通を一括検出できる配線構造を設けている。

すなわち、本実施形態では、半田接合が良好なときには、4個の導通検出用の金属ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとが電気的に繋がり、これらの導通が一括検出され、一箇所でも導通検出用の金属ボール端子15と導通検出用のランド25とが良好に接合されていなければ、導通は検出されない。したがって、検出が確実で、しかもシンプルである。

一括検出が可能なことは、図4に示した配線基板26でも同様である。

【0030】

図6に示すリフロー炉30はリフロー法により配線基板20にBGAパッケージ10を実装するための炉である。リフロー炉30は加熱室31を有し、その内部にはヒータ32が設けられている。

【0031】

リフロー法によりBGAパッケージ10を配線基板20に実装する際には、配線基板20のランド24、25にクリーム半田を塗布し、配線基板20にBGAパッケージ10を載置した状態で、これらをリフロー炉30の加熱室31内に搭載し、半田が溶融する温度に加熱して半田のリフローが行われる。

リフロー炉30の加熱室31内には、配線基板20の一対の検出用端子22と接続される一対の検出用端子34が設けられている。配線基板20の一対の検出用端子22とリフロー炉30の一対の検出用端子34とは、一対の耐熱ケーブル33を介して接続される。

図では、一対の検出用端子22、一対の耐熱ケーブル33、及び一対の検出用端子34をそれぞれ1つにまとめて図示してある。

一対の検出用端子34は、4個の導通検出用の金属ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとの導通を電気的に検出する検出器35に接続されている。

【0032】

リフロー炉30では、一対の耐熱ケーブル33、一対の検出用端子34、及び検出器35により、4個の導通検出用の金属ボール端子15A〜15Dと4個の導通検出用のランド25A〜25Dとの導通を電気的に検出する検出機構が構成されている。そして、検出器35による検出結果は表示部37に表示されるようになっている。

【0033】

リフロー炉30にはまた、検出器35による検出結果が入力され、この検出結果に基づいてヒータ32の加熱を制御する制御回路(加熱制御機構)36が設けられている。この制御回路36は、すべての導通検出用の金属ボール端子15A〜15Dと導通検出用のランド25A〜25Dとの導通が検出された時点で、配線基板20と半導体パッケージ10のリフロー加熱を終了するよう、ヒータ32の加熱を制御する。

かかる制御機構により、半導体パッケージ10の金属ボール端子14、15と配線基板20のランド24、25とを確実に接合でき、かつ半導体パッケージ10と配線基板20とが過度に加熱されることを安定的に抑制することができる。

【0034】

リフロー炉30には上記加熱制御機構を設ける代わりに、検出器35によりすべての導通検出用の金属ボール端子15A〜15Dと導通検出用のランド25A〜25Dとの導通が検出された時点で、配線基板20と半導体パッケージ10を取り出す機構を備える構成としてもよい。

かかる構成でも、半導体パッケージ10の金属ボール端子14、15と配線基板20のランド24、25とを確実に接合でき、かつ半導体パッケージ10と配線基板20とが過度に加熱されることを安定的に抑制することができる。

【0035】

リフロー炉30に上記加熱制御機構や配線基板20と半導体パッケージ10の取出し機構を設ける代わりに、表示部37に表示された検出結果に基づいて、作業者が、導通検出用の金属ボール端子15A〜15Dと導通検出用のランド25A〜25Dとの導通が検出された時点で、配線基板20と半導体パッケージ10のリフロー加熱を終了するか、あるいはリフロー炉30の加熱室31から配線基板20とBGAパッケージ10とを取り出すようにしてもよい。

【0036】

本発明の関連技術としては、「背景技術」の項に挙げた特許文献1〜5がある。

【0037】

特許文献1には、配線基板の四隅にそれぞれ、その他のランドを2個連結した大きさを有する2つの補強用ランド(22)が設けられ、補強用ランド(22)の隣のランド(23)と、この補強用ランドから対角線上に離隔する位置の他の補強用ランド(22)とが配線(24)により接続された構成が記載されている(図1、段落0022)。

特許文献1には、BGA型パッケージの四隅にそれぞれ、4個の補強用ハンダボール(15)が設けられ、補強用ハンダボール(15)の隣のハンダボール(16)と、この補強用ハンダボール(15)から対角線上に離隔する位置の他の補強用ハンダボール(15)とが基板に設けられた配線(図示なし)により接続された構成が記載されている(図2、段落0022)。

特許文献1に記載の構成では、2個の補強用半田ボール(15)が1個の補強用ランド(22)に接合される。

【0038】

特許文献1の[発明の効果]の項(段落0034)には、強い衝撃力を受けて、補強用半田ボールが補強用ランドから剥がれるのに加えて、その隣の半田ボールが隣のランドから剥がれた場合でも、他の補強用ランドとこれに接続された他の補強用半田ボールを介して信号を迂回させて隣の半田ボールに信号を伝達するので、隣のランドと隣の半田ボールとの間の接続関係が維持されることが記載されている。

【0039】

特許文献1は半田ボールとランドとの導通を検出可能としたものではない。

また、「互いに対角にある半田ボール同士を接続することで、配線基板に対して半導体パッケージをどの向きで搭載しても配線基板側の導通配線パターンを同じ配線ルールで対応できるため、半導体パッケージの搭載向きや配線基板の配線パターンの人為的ミスを防止できる。」という本発明の効果については記載がない。

【0040】

特許文献2〜5には、BGAパッケージの半田ボールの一部を導通検出用の半田ボールとし、配線基板のランドの一部を導通検出用ランドとし、配線基板に導通検出用の半田ボールと導通検出用ランドとの導通を検査するための配線構造を設けた構成が記載されている。

【0041】

特許文献2には、BGAパッケージの四隅にそれぞれ互いに配線を介して接続された2個の導通検出用の半田ボール(11a〜11h)を設け、配線基板に導通検出用の半田ボールが接合される導通検出用ランド(21a〜21h)を設け、配線基板に導通検出用の半田ボールと導通検出用ランドとの導通を検査するための複数の配線(25a〜25e)と2個の導通検出用パッド(23a、23b)を設け、一括検出を可能とした構成が記載されている(図5〜図6)。

特許文献2において、導通検出用の半田ボールの径は通常の半田ボールと同一である。

【0042】

特許文献3には、BGAパッケージの四隅と中央部にそれぞれ互いに配線を介して接続された2個の導通検出用の半田ボール(半田ボールのランド3a、3bを参照)を設け、配線基板に導通検出用の半田ボールが接合される導通検出用ランド(5a、5b)を設け、配線基板に導通検出用の半田ボールと導通検出用ランドとの導通を検査するための複数の配線と複数の導通検出用端子(5c、5c')を設けた構成が記載されている(図1〜図2)。

特許文献3では、互いに配線を介して接続された2つの導通検出用の半田ボールごとに一対の導通検出用端子(5c、5c')を設けられており、導通試験装置6で各対の導通検出用端子(5c、5c')間の導通を検査するようになっている(段落0018)。

特許文献3において、導通検出用の半田ボールの径は通常の半田ボールと同一である。

【0043】

特許文献4には、BGAパッケージの四隅にそれぞれ径の小さい導通検出用の半田ボール(2b)を設け、この導通検出用の半田ボール(2b)と隣の半田ボールとを接続し、配線基板に導通検出用の半田ボールが接合される導通検出用ランド(符号なし)を設け、配線基板に導通検出用の半田ボールと導通検出用ランドとの導通を検査するための複数の配線(図示なし)を設けた構成が記載されている(図3、図4、段落0028−0030)。

【0044】

特許文献5には、BGAパッケージの四隅及び各辺の中央部にそれぞれ径の小さい導通検出用の半田ボール(14)を設け、BGAパッケージの基板の上面に導通検出用の半田ボールに導通された導通検出用電極(30)を設け、配線基板に導通検出用の半田ボールが接合される導通検出用ランド(22)を設けた構成が記載されている(図2、図3)。

特許文献5では、テスター(70)を用いて導通検出用電極(30)と導通検出用ランド(22)との導通が検査されるようになっている(図3)。

【0045】

特許文献2〜5には、互いに対角にある導通検出用の半田ボール同士を接続した構成や、配線基板とリフロー炉とを接続して導通の有無を検出可能とした構成は記載されていない。

特許文献2〜5に記載の配線構造では、「配線基板に対して半導体パッケージをどの向きで搭載しても配線基板側の導通配線パターンを同じ配線ルールで対応できるため、配線パターンの設計が容易であり、半導体パッケージの搭載向きや配線パターンの人為的ミスを防止できる。」という本発明の効果は得られず、配線接続等のミスが起こりやすい。

【0046】

以上説明したように、本実施形態によれば、BGA半導体パッケージ10をリフロー法により配線基板20に実装する際に、半田ボール端子14、15の溶融状態を正確に把握して、半導体パッケージ10の半田ボール端子14、15と配線基板20のランド24、25とを確実に接合でき、かつ半導体パッケージ10と配線基板20との過度な加熱を抑制することが可能な半導体パッケージ10、配線基板20、及びリフロー炉30を提供することができる。

本実施形態では、互いに対角にある2個の導通検出用の半田ボール端子15同士を接続するようにしている。かかる構成では、配線基板20に対して半導体パッケージ10をどの向きで搭載しても配線基板20側の導通配線パターンを同じ配線ルールで対応できるため、配線パターンの設計が容易であり、半導体パッケージ10の搭載向きや配線基板20の配線パターンの人為的ミスを防止できる。

【0047】

(設計変更)

本発明は上記実施形態に限らず、本発明の趣旨を逸脱しない範囲内において適宜設計変更が可能である。

【符号の説明】

【0048】

10 BGAパッケージ(半導体パッケージ)

11 半導体基板

11B 基板底面

12 半導体チップ

13 ボンディングワイヤ

14 半田ボール端子(金属ボール端子)

15、15A〜15D 導通検出用の半田ボール端子(金属ボール端子)

16 配線

20、26 配線基板

22 検出用端子

23 配線

24 ランド

25、25A〜25D 導通検出用のランド

30 リフロー炉

31 加熱室

32 ヒータ

33 耐熱ケーブル

34 検出用端子

35 検出器

36 制御回路

37 表示部

【特許請求の範囲】

【請求項1】

半導体基板の底面に格子状に配置された複数の金属ボール端子を備え、リフロー法により、前記複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装される半導体パッケージであって、

前記複数の金属ボール端子のうち四隅の金属ボール端子はその他の金属ボール端子よりも相対的に径が小さい導通検出用の金属ボール端子であり、当該導通検出用の金属ボール端子の径が下記関係式(X)を充足するものであり、

かつ互いに対角にある2個の導通検出用の金属ボール端子同士が配線を介して接続された半導体パッケージ。

d2≧d1−x・・・(X)

(上記式中、d1は導通検出用ではない金属ボール端子の径、d2は導通検出用の金属ボール端子の径、xは配線基板上に半導体パッケージを載置した時点に対する金属ボール端子の溶融後の半導体パッケージの沈み込み量を各々示す。)

【請求項2】

リフロー法により請求項1に記載の半導体パッケージが実装される前記配線基板であって、

前記導通検出用の金属ボール端子と当該金属ボール端子が接合される導通検出用のランドとの導通を検出するための配線構造を備えた配線基板。

【請求項3】

前記配線構造として、前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を検出するための検出用端子と、当該検出用端子と前記導通検出用のランドとを電気的に接続する配線とを備えた請求項2に記載の配線基板。

【請求項4】

前記配線構造は、すべての前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を一括検出できる配線構造である請求項2又は3に記載の配線基板。

【請求項5】

リフロー法により請求項2又は4に記載の配線基板に請求項1に記載の半導体パッケージを実装するためのリフロー炉であって、

前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を検出するための検出機構を備えたリフロー炉。

【請求項6】

リフロー法により請求項3に記載の配線基板に請求項1に記載の半導体パッケージを実装するためのリフロー炉であって、

前記配線基板の前記検出用端子に電気的に接続される検出用端子を含む、前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を検出するための検出機構を備えたリフロー炉。

【請求項7】

前記検出機構によりすべての前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通が検出された時点で、前記配線基板と前記半導体パッケージのリフロー加熱を終了する加熱制御機構を備えた請求項5又は6に記載のリフロー炉。

【請求項8】

前記検出機構によりすべての前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通が検出された時点で、前記配線基板と前記半導体パッケージを取り出す機構を備えた請求項5又は6に記載のリフロー炉。

【請求項1】

半導体基板の底面に格子状に配置された複数の金属ボール端子を備え、リフロー法により、前記複数の金属ボール端子が接合される複数のランドを備えた配線基板に実装される半導体パッケージであって、

前記複数の金属ボール端子のうち四隅の金属ボール端子はその他の金属ボール端子よりも相対的に径が小さい導通検出用の金属ボール端子であり、当該導通検出用の金属ボール端子の径が下記関係式(X)を充足するものであり、

かつ互いに対角にある2個の導通検出用の金属ボール端子同士が配線を介して接続された半導体パッケージ。

d2≧d1−x・・・(X)

(上記式中、d1は導通検出用ではない金属ボール端子の径、d2は導通検出用の金属ボール端子の径、xは配線基板上に半導体パッケージを載置した時点に対する金属ボール端子の溶融後の半導体パッケージの沈み込み量を各々示す。)

【請求項2】

リフロー法により請求項1に記載の半導体パッケージが実装される前記配線基板であって、

前記導通検出用の金属ボール端子と当該金属ボール端子が接合される導通検出用のランドとの導通を検出するための配線構造を備えた配線基板。

【請求項3】

前記配線構造として、前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を検出するための検出用端子と、当該検出用端子と前記導通検出用のランドとを電気的に接続する配線とを備えた請求項2に記載の配線基板。

【請求項4】

前記配線構造は、すべての前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を一括検出できる配線構造である請求項2又は3に記載の配線基板。

【請求項5】

リフロー法により請求項2又は4に記載の配線基板に請求項1に記載の半導体パッケージを実装するためのリフロー炉であって、

前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を検出するための検出機構を備えたリフロー炉。

【請求項6】

リフロー法により請求項3に記載の配線基板に請求項1に記載の半導体パッケージを実装するためのリフロー炉であって、

前記配線基板の前記検出用端子に電気的に接続される検出用端子を含む、前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通を検出するための検出機構を備えたリフロー炉。

【請求項7】

前記検出機構によりすべての前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通が検出された時点で、前記配線基板と前記半導体パッケージのリフロー加熱を終了する加熱制御機構を備えた請求項5又は6に記載のリフロー炉。

【請求項8】

前記検出機構によりすべての前記導通検出用の金属ボール端子と前記導通検出用のランドとの導通が検出された時点で、前記配線基板と前記半導体パッケージを取り出す機構を備えた請求項5又は6に記載のリフロー炉。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−254053(P2011−254053A)

【公開日】平成23年12月15日(2011.12.15)

【国際特許分類】

【出願番号】特願2010−128858(P2010−128858)

【出願日】平成22年6月4日(2010.6.4)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

【公開日】平成23年12月15日(2011.12.15)

【国際特許分類】

【出願日】平成22年6月4日(2010.6.4)

【出願人】(000004237)日本電気株式会社 (19,353)

【Fターム(参考)】

[ Back to top ]