半導体パッケージモジュール

【課題】半導体パッケージモジュールの設置面積を縮小させる技術を提供する。

【解決手段】半導体パッケージモジュール1は、半導体素子を収容する扁平状の第1のパッケージ210、及び半導体素子を収容する扁平状の第2のパッケージ210を、互いの主表面同士が対向するように配置された状態でケース体100に収容している。

【解決手段】半導体パッケージモジュール1は、半導体素子を収容する扁平状の第1のパッケージ210、及び半導体素子を収容する扁平状の第2のパッケージ210を、互いの主表面同士が対向するように配置された状態でケース体100に収容している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体パッケージモジュールに関する。

【背景技術】

【0002】

従来、インバータ用のスイッチング素子を備えた半導体パッケージモジュール等の、複数の半導体パッケージを備えた半導体パッケージモジュールが知られている。例えば、特許文献1には、半導体素子と当該半導体素子に接続されたリード端子とが封止されたパッケージと、外部端子が設けられた枠体からなるケースとを含み、ケースの枠体にパッケージが配置され、リード端子と外部端子とが接続された半導体装置(半導体パッケージモジュール)が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003−100987号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上述した特許文献1の半導体パッケージモジュールでは、扁平状の複数のパッケージが、隣接するパッケージの側面同士が対向するように配置されて、すなわち、各パッケージの主表面が同一平面上に位置するように配置されて、ケースの枠体に収容されていた。そのため、従来の半導体パッケージモジュールには、設置面積が大きいという課題があった。

【0005】

本発明はこうした課題に鑑みてなされたものであり、その目的は、半導体パッケージモジュールの設置面積を縮小させる技術を提供することにある。

【課題を解決するための手段】

【0006】

本発明のある態様は、半導体パッケージモジュールである。当該半導体パッケージモジュールは、半導体素子を収容する扁平状の第1のパッケージ、及び半導体素子を収容する扁平状の第2のパッケージを、互いの主表面同士が対向するように配置された状態でケース体に収容することを特徴とする。

【発明の効果】

【0007】

本発明によれば、半導体パッケージモジュールの設置面積を縮小させることができる。

【図面の簡単な説明】

【0008】

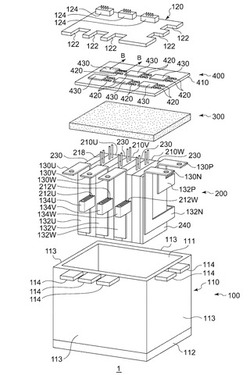

【図1】実施形態1に係る半導体装置の外観を示す概略斜視図である。

【図2】半導体装置の概略構造を示す分解斜視図である。

【図3】パッケージ積層体の概略斜視図である。

【図4】半導体パッケージモジュールの平面図である。

【図5】図5(A)は、パッケージの主表面に平行な面に沿ったパッケージの概略断面図である。図5(B)は、図5(A)のA−A線に沿った概略断面図である。

【図6】図6(A)は、制御用ICと制御用端子との接続部近傍の概略断面図である。図6(B)は、制御用ICと制御用端子との接続部近傍の概略平面図である。

【図7】図7(A)〜図7(D)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。

【図8】図8(A)及び図8(B)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。

【図9】図9(A)及び図9(B)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。

【図10】図10(A)及び図10(B)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。

【図11】図11(A)は、実施形態2に係る半導体パッケージモジュールのパッケージ積層体をU相端子、V相端子、W相端子が突出する側面側から見た概略斜視図である。図11(B)は、パッケージ積層体をP電極端子及びN電極端子が突出する側面側から見た概略斜視図である。

【発明を実施するための形態】

【0009】

以下、本発明の実施形態を図面を参照して説明する。なお、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0010】

(実施形態1)

図1は、実施形態1に係る半導体装置の外観を示す概略斜視図である。図2は、半導体装置の概略構造を示す分解斜視図である。図3は、パッケージ積層体の概略斜視図である。図4は、半導体パッケージモジュールの平面図である。なお、封止材300は、パッケージ積層体200の上方、及びパッケージ積層体200の側方とケース体100との隙間に充填されるが、図2では便宜的に封止材300の形状を板状としている。図2及び図3では、ケース体100の外部端子がパッケージ積層体200に接続された状態を示している。図4では、ケース体100の蓋部120及び制御基板400が取り外された状態を示し、パッケージ積層体200の上方を被覆する封止材300の図示を省略している。

【0011】

本実施形態に係る半導体パッケージモジュール1は、ケース体100と、パッケージ積層体200と、封止材300と、制御基板400とを備える。

【0012】

(ケース体)

ケース体100は、本体部110と、蓋部120と、P外部電極130Pと、N外部電極130Nと、U出力端子130Uと、V出力端子130Vと、W出力端子130Wとを有する。以下では適宜、P外部電極130P、N外部電極130N、U出力端子130U、V出力端子130V、及びW出力端子130Wをまとめて外部端子130という。

【0013】

本体部110は、底部112及び4つの側壁113からなり、パッケージ積層体200を収容するための収容空間111を有する。底部112は、パッケージ積層体200を放熱するための放熱板として機能する。隣接する2つの側壁113の上端縁、すなわち底部112とは反対側の縁部には、側壁113に対して略垂直に突出する複数の突出部114が設けられる。突出部114は、パッケージ積層体200が収容空間111に収容された状態で、外部端子130を支える補強部材として機能する。

【0014】

蓋部120は、本体部110に嵌め合わされた状態で、突出部114が設けられた2つの側壁113と接する2辺に、外部端子130が嵌め合わされる複数の凹部122を有する。また、蓋部120は、その主表面上に複数の制御用入出力端子124が設けられる。複数の制御用入出力端子124は、本体部110に嵌め合わされた状態で、制御基板400の後述する複数の制御用IC430に電気的に接続される。

【0015】

P外部電極130Pは、収容空間111内を引き回される配線部132Pを有する。N外部電極130Nは、収容空間111内を引き回される配線部132Nを有する。U出力端子130Uは、収容空間111内を引き回される配線部132Uを有する。V出力端子130Vは、収容空間111内を引き回される配線部132Vを有する。W出力端子130Wは、収容空間111内を引き回される配線部132Wを有する。以下では適宜、配線部132P、配線部132N、配線部132U、配線部132V、及び配線部132Wをまとめて配線部132という。

【0016】

配線部132Pは、後述するP電極端子212Pが挟み込まれる、略U字状の折曲部134Pを有する。配線部132Nは、後述するN電極端子212Nが挟み込まれる、略U字状の折曲部134Nを有する。配線部132Uは、後述するU相端子212Uが挟み込まれる、略U字状の折曲部134Uを有する。配線部132Vは、後述するV相端子212Vが挟み込まれる、略U字状の折曲部134Vを有する。配線部132Wは、後述するW相端子212Wが挟み込まれる、略U字状の折曲部134Wを有する。以下では適宜、折曲部134P、折曲部134N、折曲部134U、折曲部134V、及び折曲部134Wをまとめて折曲部134という。なお、本実施形態では、銅を主成分とする金属からなる一枚の金属板が折り曲げ加工されて、外部端子130、配線部132、及び折曲部134が一体的に形成される。ここで、「銅を主成分とする」は、銅の含有量が50%よりも大きいことを意味する。

【0017】

(パッケージ積層体)

パッケージ積層体200は、3相インバータ回路の各相を構成するU相パッケージ210U、V相パッケージ210V、及びW相パッケージ210Wと、複数の放熱板230と、絶縁板240とを有する。以下では適宜、U相パッケージ210U、V相パッケージ210V、及びW相パッケージ210Wをまとめてパッケージ210という。なお、本実施形態の半導体パッケージモジュール1は、U相パッケージ210U、V相パッケージ210V、及びW相パッケージ210Wを含むが、複数のパッケージを含んでいればその数及び種類は限定されず、半導体パッケージモジュール1の用途に応じて適宜変更することができる。

【0018】

各パッケージ210は、複数のリード端子を有する。具体的には、U相パッケージ210Uは、リード端子としてP電極端子212P、N電極端子212N及びU相端子212Uを有する。V相パッケージ210Vは、P電極端子212P、N電極端子212N及びV相端子212Vを有する。W相パッケージ210Wは、P電極端子212P、N電極端子212N及びW相端子212Wを有する。以下では適宜、P電極端子212P、N電極端子212N、U相端子212U、V相端子212V及びW相端子212Wをまとめてリード端子212という。リード端子212は、銅を主成分とする金属からなる。

【0019】

各パッケージ210は、扁平状であり、リード端子はパッケージ210の側面から突出する。本実施形態では、パッケージ積層体200がケース体100に収容された状態でケース体100の底部112と略直交する2つの側面のうち、一方の側面からP電極端子212P及びN電極端子212Nが突出し、他方の側面からU相端子212U、V相端子212V及びW相端子212Wのいずれかが突出する。

【0020】

また、各パッケージ210は、複数のリード端子212に電気的に接続される半導体素子を収容する。具体的には、U相パッケージ210Uは、インバータのU相のスイッチング動作を行う2つの半導体素子214Uを収容する。V相パッケージ210Vは、インバータのV相のスイッチング動作を行う2つの半導体素子214Vを収容する。W相パッケージ210Wは、インバータのW相のスイッチング動作を行う2つの半導体素子214Wを収容する。以下では適宜、半導体素子214U、半導体素子214V、及び半導体素子214Wをまとめて半導体素子214という。

【0021】

また、各パッケージ210は、金属等の導電性材料からなる板状のノイズ抑制部材216を有する。さらに、各パッケージ210は、半導体素子214の動作を制御する制御信号が入力される制御用端子218を有する。制御用端子218は、パッケージ積層体200がケース体100に収容された状態でケース体100の底部112と平行な2つの側面のうち、底部112から遠い側の側面、すなわち上側の側面から上方に突出する。

【0022】

各パッケージ210は、隣接するパッケージ210の主表面同士が対向するように配置された状態でケース体100に収容される。これにより、扁平なパッケージを互いの側面が対向するように配置して収容する従来の半導体パッケージモジュールに比べて、半導体パッケージモジュール1の設置面積を縮小させることができる。

【0023】

また、本実施形態では、複数の放熱板230と複数のパッケージ210とが、互いの主表面が対向するようにして交互に配列される。放熱板230は、パッケージ210を放熱するための部材であり、金属等の伝熱性の高い材料からなる。これにより、各パッケージ210は、主表面側が2枚の放熱板230で挟まれた状態となる。さらに、各パッケージ210の下側の側面は、放熱板として機能する底部112に当接する。上述した従来の半導体パッケージモジュールでは、各パッケージの一方の主表面を放熱板に当接させることができたが、他方の主表面側には制御基板が搭載されるため、パッケージの放熱効率が低かった。これに対し、本実施形態の半導体パッケージモジュール1では、各パッケージ210の2つの主表面と1つの側面を放熱板に当接させることができるため、従来の構造に比べてパッケージの放熱効率を高めることができる。

【0024】

複数のパッケージ210の各リード端子212には、ケース体100の外部端子130が電気的に接続される。具体的には、P外部電極130Pの配線部132Pは、一端側に3つの折曲部134Pを有し、各折曲部134Pに各パッケージ210のP電極端子212Pが挟み込まれ、後述する固相拡散接合により折曲部134PとP電極端子212Pとが接合される。配線部132Pの他端側は、最外側のパッケージであるW相パッケージ210Wの主表面側に引き回され、P外部電極130Pに接続される。したがって、各パッケージ210のP電極端子212Pは、P外部電極130Pに並列に接続される。

【0025】

N外部電極130Nの配線部132Nは、一端側に3つの折曲部134Nを有し、各折曲部134Nに各パッケージ210のN電極端子212Nが挟み込まれ、固相拡散接合により折曲部134NとN電極端子212Nとが接合される。配線部132Nの他端側は、最外側のパッケージであるW相パッケージ210Wの主表面側に引き回され、N外部電極130Nに接続される。したがって、各パッケージ210のN電極端子212Nは、N外部電極130Nに並列に接続される。

【0026】

U出力端子130Uの配線部132Uは、一端側に折曲部134Uを有し、折曲部134UにU相パッケージ210UのU相端子212Uが挟み込まれ、固相拡散接合により折曲部134UとU相端子212Uとが接合される。配線部132Uの他端側は、U相パッケージ210Uの側面側で上方(底部112と反対の方向)に引き回されてU出力端子130Uに接続される。

【0027】

V出力端子130Vの配線部132Vは、一端側に折曲部134Vを有し、折曲部134VにV相パッケージ210VのV相端子212Vが挟み込まれ、固相拡散接合により折曲部134VとV相端子212Vとが接合される。配線部132Vの他端側は、V相パッケージ210Vの側面側で上方に引き回されてV出力端子130Vに接続される。

【0028】

W出力端子130Wの配線部132Wは、一端側に折曲部134Wを有し、折曲部134WにW相パッケージ210WのW相端子212Wが挟み込まれ、固相拡散接合により折曲部134WとW相端子212Wとが接合される。配線部132Wの他端側は、W相パッケージ210Wの側面側で上方に引き回されてW出力端子130Wに接続される。

【0029】

W相パッケージ210W側の最外側の放熱板230と、配線部132P,132Nとの間には、絶縁板240が配置される。これにより、当該放熱板230の主表面側における放熱板230と配線部132P,132Nとの絶縁が確保される。また、配線部132は、放熱板230の側面側において、放熱板230の側面から離間して配置される。これにより、放熱板230の側面側における放熱板230と配線部132との絶縁が確保される。

【0030】

続いて、パッケージ210の内部構造について詳細に説明する。図5(A)は、パッケージの主表面に平行な面に沿ったパッケージの概略断面図である。図5(B)は、図5(A)のA−A線に沿った概略断面図である。U相パッケージ210U、V相パッケージ210V及びW相パッケージ210Wは、同様の内部構造を取るため、ここではU相パッケージ210Uを例にして説明し、V相パッケージ210V及びW相パッケージ210Wの説明を省略する。

【0031】

U相パッケージ210UのP電極端子212P及びU相端子212Uには、それぞれ半導体素子214Uが電気的に接続される。P電極端子212P上の半導体素子214Uは、電源線220を介してU相端子212Uに接続される。U相端子212U上の半導体素子214Uは、電源線220を介してN電極端子212Nに接続される。各半導体素子214Uは、ゲート電極Gを有する。各ゲート電極Gには、制御用信号線222を介して制御用端子218が接続される。また、各半導体素子214Uのゲート電極G以外の所定領域で、電源線220が接続された領域と同一の領域から制御用信号線222を介して制御用端子218が接続される。

【0032】

このような構成において、制御基板400(図2参照)から送信される制御信号は、制御用端子218を介してU相パッケージ210Uに入力され、半導体素子214Uのスイッチング動作が実行される。これにより、U相端子212UからU相電力が出力される。

【0033】

板状のノイズ抑制部材216は、U相パッケージ210Uの主表面と平行に配置される。また、U相パッケージ210Uの主表面と交わる方向から見て(図5(A)参照)、ノイズ抑制部材216は、2つの半導体素子214Uと重なるように配置される。さらに、ノイズ抑制部材216は、電源線220及び制御用信号線222と重なるように配置される。また、ノイズ抑制部材216は、接続部材217を介してN電極端子212Nに電気的に接続される。本実施形態では、N外部電極130Nの電位は固定電位である。したがって、N外部電極130Nに接続されるN電極端子212Nは、電位が固定電位である固定電位リード端子に相当する。固定電位は、例えばグランドである。

【0034】

このように、固定電位リード端子であるN電極端子212Nに電気的に接続されたノイズ抑制部材216を設けることで、隣接するパッケージ210や外部からの電磁波を遮蔽して、ノイズの発生を抑制することができる。もしくは、他のパッケージ210への電磁波の伝搬を抑制することにより、他のパッケージ210におけるノイズの発生を抑制することができる。また、固定電位であるノイズ抑制部材216と、固定電位に対して電位差を有するP電極端子212P、U相端子212U、半導体素子214U、電源線220、制御用信号線222との間にはコンデンサ(キャパシタ)が形成される。このコンデンサにより、電磁波により発生する誘導電流が流れることを抑制することができ、ノイズの発生を抑制することができる。

【0035】

各パッケージ210において、ノイズ抑制部材216は、パッケージ積層体200がケース体100に収容された状態で、半導体素子214よりもP外部電極130P及びN外部電極130Nから遠い側に配置される(図4参照)。したがって、U相パッケージ210Uの半導体素子214Uは、U相パッケージ210U及びV相パッケージ210Vのノイズ抑制部材216により電磁波から保護される。また、V相パッケージ210Vの半導体素子214Vは、V相パッケージ210V及びW相パッケージ210Wのノイズ抑制部材216により電磁波から保護される。また、W相パッケージ210Wの半導体素子214Uについては、パッケージ210の積層方向から見て、一部ではあるが配線部132NがW相パッケージ210Wの主表面を覆っている。したがって、W相パッケージ210Wの半導体素子214Uは、W相パッケージ210Wのノイズ抑制部材216と、配線部132Nとにより電磁波から保護される。

【0036】

(封止材)

封止材300は、図2及び図4に示すように、ケース体100の側壁113とパッケージ積層体200との隙間に充填され、またパッケージ積層体200の上面を覆い尽くす。これにより、パッケージ積層体200は、ケース体100内に封止され、またケース体100内で固定される。封止材300は、例えばシリコンゲルである。各パッケージ210の制御用端子218は、封止材300を貫通して封止材300の上側の主表面よりも上方に突出する。

【0037】

(制御基板)

制御基板400は、図2に示すように、基板410と、複数の配線パターン420と、複数の制御用IC430とを有する。基板410上に設けられた複数の制御用IC430は、それぞれ配線パターン420を介して各パッケージ210の制御用端子218に電気的に接続される。制御用IC430は、スイッチング動作を制御する制御信号を各パッケージ210に出力する。制御基板400は、その主表面が各パッケージ210の側面と対向するように配置される。これにより、各パッケージ210の両主表面に放熱板230を当接させることができる。

【0038】

図6(A)は、制御用ICと制御用端子との接続部近傍の概略断面図である。図6(B)は、制御用ICと制御用端子との接続部近傍の概略平面図である。なお、図6(A)は、図2のB−B線に沿った概略断面図、及び図6(B)のC−C線に沿った概略断面図に相当する。

【0039】

基板410は、所定位置に貫通孔412を有する。配線パターン420は、IC側ランド領域422、パターン部424、及び端子側ランド領域426を有する。端子側ランド領域426には、貫通孔427が設けられる。配線パターン420は、端子側ランド領域426の貫通孔427と、基板410の貫通孔412とが重なるように配置される。制御用IC430は、表面に素子電極432を有する。素子電極432と配線パターン420のIC側ランド領域422とは、金線428によりワイヤボンディング接続される。

【0040】

制御基板400が封止材300上に配置された状態で、封止材300の表面から突出する制御用端子218が貫通孔412及び貫通孔427に挿通され、端子側ランド領域426の表面上に突出する。端子側ランド領域426において突出する制御用端子218は、はんだ440により固定される。これにより、配線パターン420及び金線428を介して制御用端子218と素子電極432とが電気的に接続される。

【0041】

上述の構成を備えた半導体パッケージモジュール1は、U出力端子130U、V出力端子130V及びW出力端子130Wが、例えば3相交流モータの各端子に接続される。また、P外部電極130P及びN外部電極130Nが、太陽電池等の外部電源に接続される。半導体パッケージモジュール1は、外部電源から供給される直流電力を交流電力に変換して3相交流モータに供給する。

【0042】

(半導体パッケージモジュールの製造方法)

本実施形態に係る半導体パッケージモジュール1は、例えば次のようにして製造することができる。図7(A)〜図7(D)、図8(A)及び図8(B)、図9(A)及び図9(B)、図10(A)及び図10(B)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。なお、図7(B)〜図7(D)では、山折り部分を実線で示し、谷折り部分を破線で示す。

【0043】

まず、図7(A)に示すように、U相パッケージ210U、V相パッケージ210V及びW相パッケージ210Wを用意する。

【0044】

また、図7(B)に示すように、U出力端子130U用の金属板131U、V出力端子130V用の金属板131V、及びW出力端子130W用の金属板131Wをそれぞれ用意する。金属板131U,131V,131Wは、銅を主成分とする材料からなる。そして、金属板131U,131V,131Wの一端側を矢印iで示すように谷折りしてU出力端子130U、V出力端子130V及びW出力端子130Wを形成する。また、他端側を矢印iiで示すように谷折りし、矢印iiiで示すように山折りして、折曲部134U,134V,134Wを形成する。

【0045】

また、図7(C)に示すように、N外部電極130N用の金属板131Nを用意する。金属板131Nは、銅を主成分とする材料からなる。そして、金属板131Nの一端側を矢印iで示すように山折りしてN外部電極130Nを形成する。また、途中部分を矢印iiで示すように谷折りしてパッケージ積層体200の角部に対応する屈曲部を形成する。さらに、他端側を矢印iiiで示すように山折りし、矢印ivで示すように谷折りして、3つの折曲部134Nを形成する。

【0046】

また、図7(D)に示すように、P外部電極130P用の金属板131Pを用意する。金属板131Pは、銅を主成分とする材料からなる。そして、金属板131Pの一端側を矢印iで示すように山折りしてP外部電極130Pを形成する。また、途中部分を矢印iiで示すように谷折りしてパッケージ積層体200の角部に対応する屈曲部を形成する。さらに、他端側を矢印iiiで示すように山折りし、矢印ivで示すように谷折りして、3つの折曲部134Pを形成する。

【0047】

なお、図7(A)〜図7(D)に示す各工程は、順不同である。

【0048】

次に、図8(A)に示すように、絶縁板240の上に、4枚の放熱板230と3つのパッケージ210とを交互に積層してパッケージ積層体200を形成する。パッケージ210は、W相パッケージ210W、V相パッケージ210V、U相パッケージ210Uの順とする。そして、外部端子130を各パッケージのリード端子212に嵌め合わせる。P外部電極130P及びN外部電極130Nは、絶縁板240側に位置するように嵌め合わされる。また、嵌め合わせの際、各配線部132の被接合領域、すなわち折曲部134の内側と、リード端子212の被接合領域に、スプレー塗布等により溶液500を塗布もしくは充填する。この溶液500は、酸化銅を主成分とする酸化物が溶出する溶液であり、例えばアンモニア水である。

【0049】

上述のように、折曲部134及びリード端子212は、銅を主成分とする材料からなる。そのため、折曲部134及びリード端子212の最表面は、銅が大気中で酸化することで形成される自然酸化膜で構成される。この自然酸化膜は、酸化銅を主成分とする酸化物で構成される膜である。ここで、「酸化銅を主成分とする」は、酸化銅の含有量が50%よりも大きいことを意味する。なお、折曲部134及びリード端子212の最表面を構成する酸化銅は、自然酸化以外の方法で形成されたものであってもよい。

【0050】

溶液500を塗布すると、折曲部134の最表面を構成する酸化銅が溶液500中に溶出する。また、リード端子212の最表面を構成する酸化銅が溶液500中に溶出する。折曲部134の最表面を構成する酸化銅及びリード端子212の最表面を構成する酸化銅が溶液500に溶出することにより、折曲部134の露出面及びリード端子212の露出面にそれぞれ銅が露出する。また、溶液500中では、配位子となるアンモニアイオンと銅イオンとにより銅錯体が形成される。本実施形態では、銅錯体は、[Cu(NH3)4]2+で表される加熱分解性のテトラアンミン銅錯イオンとして存在すると考えられる。なお、アンモニア水は銅に対して不活性であるため、折曲部134及びリード端子212を構成する銅はアンモニア水と反応せずに残存する。

【0051】

次に、図8(B)に示すように、各折曲部134をステンレスブロック体510で挟み、プレス機を用いて、折曲部134にステンレスブロック体510を押し当て、折曲部134の被接合部とリード端子212の被接合部との間の距離を縮めるように折曲部134とリード端子212とを加圧する。この工程における加圧時の圧力は、たとえば、1MPaである。なお、折曲部134とリード端子212との被接合面には上述した溶液500が介在する。

【0052】

続いて、折曲部134とリード端子212とを加圧した状態で、200℃〜300℃の比較的低温な条件下で加熱することにより、折曲部134の被接合部およびリード端子212の被接合部への銅の固相拡散を進行させる。この固相拡散により、折曲部134の被接合部とリード端子212の被接合部とが接合される。固相拡散による接合が完了した後、加熱を停止して加圧を解除し、ステンレスブロック体510を取り除いて、折曲部134とリード端子212の接合工程が完了する。

【0053】

次に、図9(A)に示すように、外部端子130が接続されたパッケージ積層体200を、ケース体100の収容空間111に収容する。パッケージ積層体200は、パッケージ210の制御用端子218が突出する側面とは反対の側面が、本体部110の底部112側を向くようにして、収容空間111に収容される。収容空間111内で、パッケージ210の側面と底部112とが当接する。

【0054】

次に、図9(B)に示すように、収容空間111に封止材300を充填する。

【0055】

次に、図10(A)に示すように、制御基板400を収容空間111に収容し、制御用端子218と配線パターン420とをはんだ付けする。これにより、制御用端子218と制御用IC430とが電気的に接続される。そして、蓋部120を本体部110に嵌め合わせる。

【0056】

以上の工程により、図10(B)に示すように、本実施形態に係る半導体パッケージモジュール1が完成する。

【0057】

なお、本実施形態では、リード端子212と配線部132の折曲部134とを固相拡散接合により接合させているが、外部端子130とリード端子212とを直に接続する場合は、外部端子130とリード端子212とが固相拡散接合により接合される。

【0058】

上述した半導体パッケージモジュール1の製造方法では、折曲部134及びリード端子212の最表面に形成された酸化銅を主成分とする酸化物を溶液500中に溶出させて、折曲部134及びリード端子212の被接合面を活性化させ、両者を銅の固相拡散により接合する。そのため、比較的低温な条件下で折曲部134及びリード端子212を接合することができる。これにより、折曲部134の被接合面とリード端子212の被接合面との間にボイドが発生したり副生成物が介在することが抑制されるため、両者の接続信頼性を高めることができる。また、折曲部134とリード端子212との間の接触抵抗を小さくすることができるため、本実施形態の半導体パッケージモジュール1は、インバータ用の半導体パッケージモジュール等の、大電流を流すパッケージモジュールに好適に採用することができる。

【0059】

また、折曲部134及びリード端子212の表面に形成された酸化被膜をプレス加工によって破壊することなく、上述のように溶液500を用いて溶出させるため、折曲部134とリード端子212とを接合する際に必要な荷重が1MPa程度で済む。このため、折曲部134とリード端子212との接合部分に機械的なダメージが入ることが抑制され、ひいては、リーク電流が増大することを抑制することができる。

【0060】

なお、上述した製造方法では、溶液500としてアンモニア水が用いられているが、銅と錯体を形成する配位子を含む溶液であれば、これに限られず、たとえば、カルボン酸水溶液であってもよい。カルボン酸水溶液の調製に用いられるカルボン酸としては、酢酸などのモノカルボン酸、また、シュウ酸、マロン酸、コハク酸、グルタル酸、フタル酸、マレイン酸などのジカルボン酸、さらに、酒石酸、クエン酸、乳酸、サリチル酸などのオキシカルボン酸が挙げられる。

【0061】

このうち、カルボン酸水溶液は多座配位子となるカルボン酸を有することが好ましい。多座配位子となるカルボン酸を有するカルボン酸水溶液では、カルボン酸と銅がキレートを形成することにより銅錯体の安定性が非常に大きくなる。この結果、接合に必要な温度をより低温化させることができる。なお、酒石酸がキレートを形成することについては、「理化学辞典 第4版(岩波書店)」の第593頁に記載されている。また、酒石酸、シュウ酸などがキレートを形成することは「ヘスロップジョーンズ 無機化学(下) 齋藤喜彦 訳」の第666頁に記載されている。ここで、キレート化とは、多座配位子によって環が形成されることによって錯体の安定度が非常に大きくなることをいう。

【0062】

以上説明したように、本実施形態に係る半導体パッケージモジュール1では、半導体素子214を収容する扁平状の複数のパッケージ210は、隣接するパッケージ210の主表面同士が対向するように配置された状態でケース体100に収容される。そのため、複数のパッケージを、隣接するパッケージの側面同士を対向させていた従来の構造に比べて、設置面積を縮小することができる。

【0063】

また、本実施形態の半導体パッケージモジュール1では、各パッケージの一側面がケース体100の底部112に当接し、当該側面と対向する側面上に制御基板400が配置される。そのため、各パッケージの両主表面に放熱板230を当接させることができ、パッケージの放熱性を向上させることができる。また、半導体パッケージモジュール1全体での熱の不均衡を是正することができる。

【0064】

さらに、各パッケージ210を、主表面同士が対向するように配置している。そのため、上述した従来の構造では、厚さの異なるパッケージを配列させた場合、厚さの差に起因した段差によりパッケージ上への制御基板の積層に支障が生じるおそれがあったが、本実施形態ではそのような支障が生じることはない。したがって、パッケージの組み合わせの自由度が高いため、半導体パッケージモジュール1の拡張性を向上させることができる。

【0065】

(実施形態2)

実施形態2に係る半導体パッケージモジュール1は、N外部電極130Nの配線部132Nの形状を除き、実施形態1に係る半導体パッケージモジュール1の構成と共通する。以下、実施形態2に係る半導体パッケージモジュールについて実施形態1と異なる構成を中心に説明する。実施形態1と同一の構成については同一の符号を付し、その説明は適宜省略する。

【0066】

図11(A)は、実施形態2に係る半導体パッケージモジュールのパッケージ積層体をU相端子、V相端子、W相端子が突出する側面側から見た概略斜視図である。図11(B)は、パッケージ積層体をP電極端子及びN電極端子が突出する側面側から見た概略斜視図である。なお、図10(A)及び図10(B)では、ケース体100の外部端子が接続されたパッケージ積層体200が底部112上に載置された状態を示している。

【0067】

本実施形態に係る半導体パッケージモジュール1において、電位が固定電位であるN外部電極130Nの配線部132Nは、パッケージ210の積層方向から見て、パッケージ210の主表面と重なる領域にノイズ抑制部136を有する。ノイズ抑制部136は、略平板状であり、絶縁板240の主表面を覆う。本実施形態では、ノイズ抑制部136は、配線部132と一体的に形成される。したがってノイズ抑制部136は、配線部132Nにおける配線幅が広くなった部分である。

【0068】

各パッケージ210において、U相パッケージ210Uの半導体素子214Uは、U相パッケージ210U及びV相パッケージ210Vのノイズ抑制部材216により電磁波から保護される。また、V相パッケージ210Vの半導体素子214Vは、V相パッケージ210V及びW相パッケージ210Wのノイズ抑制部材216により電磁波から保護される。また、W相パッケージ210Wの半導体素子214Uは、W相パッケージ210Wのノイズ抑制部材216と、ノイズ抑制部136とにより電磁波から保護される。

【0069】

以上説明した本実施形態に係る半導体パッケージモジュール1によれば、実施形態1で得られる効果に加えて、各パッケージ210の半導体素子214を電磁ノイズからより確実に保護することができるという効果が得られる。これにより、半導体パッケージモジュール1の動作信頼性をより向上させることができる。

【0070】

本発明は、上述の各実施形態に限定されるものではなく、当業者の知識に基づいて各種の設計変更等の変形を加えることも可能であり、そのような変形が加えられた実施形態も本発明の範囲に含まれうるものである。

【0071】

上述の各実施形態では、半導体パッケージモジュール1は3つのパッケージ210を有し、全てのパッケージ210を、隣接するパッケージの主表面同士が対向するように配置された状態でケース体100に収容している。しかしながら、半導体パッケージモジュール1の構成は特にこれに限定されず、3つ以上のパッケージ210をケース体100に収容する場合において、少なくとも2つのパッケージ210が、すなわち、第1のパッケージ210と第2のパッケージ210とが、互いの主表面同士が対向するように配置された状態でケース体100に収容されていればよい。この場合であっても上述した各実施形態の効果を得ることができる。

【符号の説明】

【0072】

1 半導体パッケージモジュール、 100 ケース体、 130 外部端子、 130N N外部電極、 130P P外部電極、 130U U出力端子、 130V V出力端子、 130W W出力端子、 132,132N,132P,132U,132V,132W 配線部、 136 ノイズ抑制部、 210 パッケージ、 210U U相パッケージ、 210V V相パッケージ、 210W W相パッケージ、 212 リード端子、 212N N電極端子、 212P P電極端子、 212U U相端子、 212V V相端子、 212W W相端子、 214,214U,214V,214W 半導体素子、 216 ノイズ抑制部材、 218 制御用端子、 230 放熱板、 400 制御基板。

【技術分野】

【0001】

本発明は、半導体パッケージモジュールに関する。

【背景技術】

【0002】

従来、インバータ用のスイッチング素子を備えた半導体パッケージモジュール等の、複数の半導体パッケージを備えた半導体パッケージモジュールが知られている。例えば、特許文献1には、半導体素子と当該半導体素子に接続されたリード端子とが封止されたパッケージと、外部端子が設けられた枠体からなるケースとを含み、ケースの枠体にパッケージが配置され、リード端子と外部端子とが接続された半導体装置(半導体パッケージモジュール)が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003−100987号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

上述した特許文献1の半導体パッケージモジュールでは、扁平状の複数のパッケージが、隣接するパッケージの側面同士が対向するように配置されて、すなわち、各パッケージの主表面が同一平面上に位置するように配置されて、ケースの枠体に収容されていた。そのため、従来の半導体パッケージモジュールには、設置面積が大きいという課題があった。

【0005】

本発明はこうした課題に鑑みてなされたものであり、その目的は、半導体パッケージモジュールの設置面積を縮小させる技術を提供することにある。

【課題を解決するための手段】

【0006】

本発明のある態様は、半導体パッケージモジュールである。当該半導体パッケージモジュールは、半導体素子を収容する扁平状の第1のパッケージ、及び半導体素子を収容する扁平状の第2のパッケージを、互いの主表面同士が対向するように配置された状態でケース体に収容することを特徴とする。

【発明の効果】

【0007】

本発明によれば、半導体パッケージモジュールの設置面積を縮小させることができる。

【図面の簡単な説明】

【0008】

【図1】実施形態1に係る半導体装置の外観を示す概略斜視図である。

【図2】半導体装置の概略構造を示す分解斜視図である。

【図3】パッケージ積層体の概略斜視図である。

【図4】半導体パッケージモジュールの平面図である。

【図5】図5(A)は、パッケージの主表面に平行な面に沿ったパッケージの概略断面図である。図5(B)は、図5(A)のA−A線に沿った概略断面図である。

【図6】図6(A)は、制御用ICと制御用端子との接続部近傍の概略断面図である。図6(B)は、制御用ICと制御用端子との接続部近傍の概略平面図である。

【図7】図7(A)〜図7(D)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。

【図8】図8(A)及び図8(B)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。

【図9】図9(A)及び図9(B)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。

【図10】図10(A)及び図10(B)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。

【図11】図11(A)は、実施形態2に係る半導体パッケージモジュールのパッケージ積層体をU相端子、V相端子、W相端子が突出する側面側から見た概略斜視図である。図11(B)は、パッケージ積層体をP電極端子及びN電極端子が突出する側面側から見た概略斜視図である。

【発明を実施するための形態】

【0009】

以下、本発明の実施形態を図面を参照して説明する。なお、すべての図面において、同様な構成要素には同様の符号を付し、適宜説明を省略する。

【0010】

(実施形態1)

図1は、実施形態1に係る半導体装置の外観を示す概略斜視図である。図2は、半導体装置の概略構造を示す分解斜視図である。図3は、パッケージ積層体の概略斜視図である。図4は、半導体パッケージモジュールの平面図である。なお、封止材300は、パッケージ積層体200の上方、及びパッケージ積層体200の側方とケース体100との隙間に充填されるが、図2では便宜的に封止材300の形状を板状としている。図2及び図3では、ケース体100の外部端子がパッケージ積層体200に接続された状態を示している。図4では、ケース体100の蓋部120及び制御基板400が取り外された状態を示し、パッケージ積層体200の上方を被覆する封止材300の図示を省略している。

【0011】

本実施形態に係る半導体パッケージモジュール1は、ケース体100と、パッケージ積層体200と、封止材300と、制御基板400とを備える。

【0012】

(ケース体)

ケース体100は、本体部110と、蓋部120と、P外部電極130Pと、N外部電極130Nと、U出力端子130Uと、V出力端子130Vと、W出力端子130Wとを有する。以下では適宜、P外部電極130P、N外部電極130N、U出力端子130U、V出力端子130V、及びW出力端子130Wをまとめて外部端子130という。

【0013】

本体部110は、底部112及び4つの側壁113からなり、パッケージ積層体200を収容するための収容空間111を有する。底部112は、パッケージ積層体200を放熱するための放熱板として機能する。隣接する2つの側壁113の上端縁、すなわち底部112とは反対側の縁部には、側壁113に対して略垂直に突出する複数の突出部114が設けられる。突出部114は、パッケージ積層体200が収容空間111に収容された状態で、外部端子130を支える補強部材として機能する。

【0014】

蓋部120は、本体部110に嵌め合わされた状態で、突出部114が設けられた2つの側壁113と接する2辺に、外部端子130が嵌め合わされる複数の凹部122を有する。また、蓋部120は、その主表面上に複数の制御用入出力端子124が設けられる。複数の制御用入出力端子124は、本体部110に嵌め合わされた状態で、制御基板400の後述する複数の制御用IC430に電気的に接続される。

【0015】

P外部電極130Pは、収容空間111内を引き回される配線部132Pを有する。N外部電極130Nは、収容空間111内を引き回される配線部132Nを有する。U出力端子130Uは、収容空間111内を引き回される配線部132Uを有する。V出力端子130Vは、収容空間111内を引き回される配線部132Vを有する。W出力端子130Wは、収容空間111内を引き回される配線部132Wを有する。以下では適宜、配線部132P、配線部132N、配線部132U、配線部132V、及び配線部132Wをまとめて配線部132という。

【0016】

配線部132Pは、後述するP電極端子212Pが挟み込まれる、略U字状の折曲部134Pを有する。配線部132Nは、後述するN電極端子212Nが挟み込まれる、略U字状の折曲部134Nを有する。配線部132Uは、後述するU相端子212Uが挟み込まれる、略U字状の折曲部134Uを有する。配線部132Vは、後述するV相端子212Vが挟み込まれる、略U字状の折曲部134Vを有する。配線部132Wは、後述するW相端子212Wが挟み込まれる、略U字状の折曲部134Wを有する。以下では適宜、折曲部134P、折曲部134N、折曲部134U、折曲部134V、及び折曲部134Wをまとめて折曲部134という。なお、本実施形態では、銅を主成分とする金属からなる一枚の金属板が折り曲げ加工されて、外部端子130、配線部132、及び折曲部134が一体的に形成される。ここで、「銅を主成分とする」は、銅の含有量が50%よりも大きいことを意味する。

【0017】

(パッケージ積層体)

パッケージ積層体200は、3相インバータ回路の各相を構成するU相パッケージ210U、V相パッケージ210V、及びW相パッケージ210Wと、複数の放熱板230と、絶縁板240とを有する。以下では適宜、U相パッケージ210U、V相パッケージ210V、及びW相パッケージ210Wをまとめてパッケージ210という。なお、本実施形態の半導体パッケージモジュール1は、U相パッケージ210U、V相パッケージ210V、及びW相パッケージ210Wを含むが、複数のパッケージを含んでいればその数及び種類は限定されず、半導体パッケージモジュール1の用途に応じて適宜変更することができる。

【0018】

各パッケージ210は、複数のリード端子を有する。具体的には、U相パッケージ210Uは、リード端子としてP電極端子212P、N電極端子212N及びU相端子212Uを有する。V相パッケージ210Vは、P電極端子212P、N電極端子212N及びV相端子212Vを有する。W相パッケージ210Wは、P電極端子212P、N電極端子212N及びW相端子212Wを有する。以下では適宜、P電極端子212P、N電極端子212N、U相端子212U、V相端子212V及びW相端子212Wをまとめてリード端子212という。リード端子212は、銅を主成分とする金属からなる。

【0019】

各パッケージ210は、扁平状であり、リード端子はパッケージ210の側面から突出する。本実施形態では、パッケージ積層体200がケース体100に収容された状態でケース体100の底部112と略直交する2つの側面のうち、一方の側面からP電極端子212P及びN電極端子212Nが突出し、他方の側面からU相端子212U、V相端子212V及びW相端子212Wのいずれかが突出する。

【0020】

また、各パッケージ210は、複数のリード端子212に電気的に接続される半導体素子を収容する。具体的には、U相パッケージ210Uは、インバータのU相のスイッチング動作を行う2つの半導体素子214Uを収容する。V相パッケージ210Vは、インバータのV相のスイッチング動作を行う2つの半導体素子214Vを収容する。W相パッケージ210Wは、インバータのW相のスイッチング動作を行う2つの半導体素子214Wを収容する。以下では適宜、半導体素子214U、半導体素子214V、及び半導体素子214Wをまとめて半導体素子214という。

【0021】

また、各パッケージ210は、金属等の導電性材料からなる板状のノイズ抑制部材216を有する。さらに、各パッケージ210は、半導体素子214の動作を制御する制御信号が入力される制御用端子218を有する。制御用端子218は、パッケージ積層体200がケース体100に収容された状態でケース体100の底部112と平行な2つの側面のうち、底部112から遠い側の側面、すなわち上側の側面から上方に突出する。

【0022】

各パッケージ210は、隣接するパッケージ210の主表面同士が対向するように配置された状態でケース体100に収容される。これにより、扁平なパッケージを互いの側面が対向するように配置して収容する従来の半導体パッケージモジュールに比べて、半導体パッケージモジュール1の設置面積を縮小させることができる。

【0023】

また、本実施形態では、複数の放熱板230と複数のパッケージ210とが、互いの主表面が対向するようにして交互に配列される。放熱板230は、パッケージ210を放熱するための部材であり、金属等の伝熱性の高い材料からなる。これにより、各パッケージ210は、主表面側が2枚の放熱板230で挟まれた状態となる。さらに、各パッケージ210の下側の側面は、放熱板として機能する底部112に当接する。上述した従来の半導体パッケージモジュールでは、各パッケージの一方の主表面を放熱板に当接させることができたが、他方の主表面側には制御基板が搭載されるため、パッケージの放熱効率が低かった。これに対し、本実施形態の半導体パッケージモジュール1では、各パッケージ210の2つの主表面と1つの側面を放熱板に当接させることができるため、従来の構造に比べてパッケージの放熱効率を高めることができる。

【0024】

複数のパッケージ210の各リード端子212には、ケース体100の外部端子130が電気的に接続される。具体的には、P外部電極130Pの配線部132Pは、一端側に3つの折曲部134Pを有し、各折曲部134Pに各パッケージ210のP電極端子212Pが挟み込まれ、後述する固相拡散接合により折曲部134PとP電極端子212Pとが接合される。配線部132Pの他端側は、最外側のパッケージであるW相パッケージ210Wの主表面側に引き回され、P外部電極130Pに接続される。したがって、各パッケージ210のP電極端子212Pは、P外部電極130Pに並列に接続される。

【0025】

N外部電極130Nの配線部132Nは、一端側に3つの折曲部134Nを有し、各折曲部134Nに各パッケージ210のN電極端子212Nが挟み込まれ、固相拡散接合により折曲部134NとN電極端子212Nとが接合される。配線部132Nの他端側は、最外側のパッケージであるW相パッケージ210Wの主表面側に引き回され、N外部電極130Nに接続される。したがって、各パッケージ210のN電極端子212Nは、N外部電極130Nに並列に接続される。

【0026】

U出力端子130Uの配線部132Uは、一端側に折曲部134Uを有し、折曲部134UにU相パッケージ210UのU相端子212Uが挟み込まれ、固相拡散接合により折曲部134UとU相端子212Uとが接合される。配線部132Uの他端側は、U相パッケージ210Uの側面側で上方(底部112と反対の方向)に引き回されてU出力端子130Uに接続される。

【0027】

V出力端子130Vの配線部132Vは、一端側に折曲部134Vを有し、折曲部134VにV相パッケージ210VのV相端子212Vが挟み込まれ、固相拡散接合により折曲部134VとV相端子212Vとが接合される。配線部132Vの他端側は、V相パッケージ210Vの側面側で上方に引き回されてV出力端子130Vに接続される。

【0028】

W出力端子130Wの配線部132Wは、一端側に折曲部134Wを有し、折曲部134WにW相パッケージ210WのW相端子212Wが挟み込まれ、固相拡散接合により折曲部134WとW相端子212Wとが接合される。配線部132Wの他端側は、W相パッケージ210Wの側面側で上方に引き回されてW出力端子130Wに接続される。

【0029】

W相パッケージ210W側の最外側の放熱板230と、配線部132P,132Nとの間には、絶縁板240が配置される。これにより、当該放熱板230の主表面側における放熱板230と配線部132P,132Nとの絶縁が確保される。また、配線部132は、放熱板230の側面側において、放熱板230の側面から離間して配置される。これにより、放熱板230の側面側における放熱板230と配線部132との絶縁が確保される。

【0030】

続いて、パッケージ210の内部構造について詳細に説明する。図5(A)は、パッケージの主表面に平行な面に沿ったパッケージの概略断面図である。図5(B)は、図5(A)のA−A線に沿った概略断面図である。U相パッケージ210U、V相パッケージ210V及びW相パッケージ210Wは、同様の内部構造を取るため、ここではU相パッケージ210Uを例にして説明し、V相パッケージ210V及びW相パッケージ210Wの説明を省略する。

【0031】

U相パッケージ210UのP電極端子212P及びU相端子212Uには、それぞれ半導体素子214Uが電気的に接続される。P電極端子212P上の半導体素子214Uは、電源線220を介してU相端子212Uに接続される。U相端子212U上の半導体素子214Uは、電源線220を介してN電極端子212Nに接続される。各半導体素子214Uは、ゲート電極Gを有する。各ゲート電極Gには、制御用信号線222を介して制御用端子218が接続される。また、各半導体素子214Uのゲート電極G以外の所定領域で、電源線220が接続された領域と同一の領域から制御用信号線222を介して制御用端子218が接続される。

【0032】

このような構成において、制御基板400(図2参照)から送信される制御信号は、制御用端子218を介してU相パッケージ210Uに入力され、半導体素子214Uのスイッチング動作が実行される。これにより、U相端子212UからU相電力が出力される。

【0033】

板状のノイズ抑制部材216は、U相パッケージ210Uの主表面と平行に配置される。また、U相パッケージ210Uの主表面と交わる方向から見て(図5(A)参照)、ノイズ抑制部材216は、2つの半導体素子214Uと重なるように配置される。さらに、ノイズ抑制部材216は、電源線220及び制御用信号線222と重なるように配置される。また、ノイズ抑制部材216は、接続部材217を介してN電極端子212Nに電気的に接続される。本実施形態では、N外部電極130Nの電位は固定電位である。したがって、N外部電極130Nに接続されるN電極端子212Nは、電位が固定電位である固定電位リード端子に相当する。固定電位は、例えばグランドである。

【0034】

このように、固定電位リード端子であるN電極端子212Nに電気的に接続されたノイズ抑制部材216を設けることで、隣接するパッケージ210や外部からの電磁波を遮蔽して、ノイズの発生を抑制することができる。もしくは、他のパッケージ210への電磁波の伝搬を抑制することにより、他のパッケージ210におけるノイズの発生を抑制することができる。また、固定電位であるノイズ抑制部材216と、固定電位に対して電位差を有するP電極端子212P、U相端子212U、半導体素子214U、電源線220、制御用信号線222との間にはコンデンサ(キャパシタ)が形成される。このコンデンサにより、電磁波により発生する誘導電流が流れることを抑制することができ、ノイズの発生を抑制することができる。

【0035】

各パッケージ210において、ノイズ抑制部材216は、パッケージ積層体200がケース体100に収容された状態で、半導体素子214よりもP外部電極130P及びN外部電極130Nから遠い側に配置される(図4参照)。したがって、U相パッケージ210Uの半導体素子214Uは、U相パッケージ210U及びV相パッケージ210Vのノイズ抑制部材216により電磁波から保護される。また、V相パッケージ210Vの半導体素子214Vは、V相パッケージ210V及びW相パッケージ210Wのノイズ抑制部材216により電磁波から保護される。また、W相パッケージ210Wの半導体素子214Uについては、パッケージ210の積層方向から見て、一部ではあるが配線部132NがW相パッケージ210Wの主表面を覆っている。したがって、W相パッケージ210Wの半導体素子214Uは、W相パッケージ210Wのノイズ抑制部材216と、配線部132Nとにより電磁波から保護される。

【0036】

(封止材)

封止材300は、図2及び図4に示すように、ケース体100の側壁113とパッケージ積層体200との隙間に充填され、またパッケージ積層体200の上面を覆い尽くす。これにより、パッケージ積層体200は、ケース体100内に封止され、またケース体100内で固定される。封止材300は、例えばシリコンゲルである。各パッケージ210の制御用端子218は、封止材300を貫通して封止材300の上側の主表面よりも上方に突出する。

【0037】

(制御基板)

制御基板400は、図2に示すように、基板410と、複数の配線パターン420と、複数の制御用IC430とを有する。基板410上に設けられた複数の制御用IC430は、それぞれ配線パターン420を介して各パッケージ210の制御用端子218に電気的に接続される。制御用IC430は、スイッチング動作を制御する制御信号を各パッケージ210に出力する。制御基板400は、その主表面が各パッケージ210の側面と対向するように配置される。これにより、各パッケージ210の両主表面に放熱板230を当接させることができる。

【0038】

図6(A)は、制御用ICと制御用端子との接続部近傍の概略断面図である。図6(B)は、制御用ICと制御用端子との接続部近傍の概略平面図である。なお、図6(A)は、図2のB−B線に沿った概略断面図、及び図6(B)のC−C線に沿った概略断面図に相当する。

【0039】

基板410は、所定位置に貫通孔412を有する。配線パターン420は、IC側ランド領域422、パターン部424、及び端子側ランド領域426を有する。端子側ランド領域426には、貫通孔427が設けられる。配線パターン420は、端子側ランド領域426の貫通孔427と、基板410の貫通孔412とが重なるように配置される。制御用IC430は、表面に素子電極432を有する。素子電極432と配線パターン420のIC側ランド領域422とは、金線428によりワイヤボンディング接続される。

【0040】

制御基板400が封止材300上に配置された状態で、封止材300の表面から突出する制御用端子218が貫通孔412及び貫通孔427に挿通され、端子側ランド領域426の表面上に突出する。端子側ランド領域426において突出する制御用端子218は、はんだ440により固定される。これにより、配線パターン420及び金線428を介して制御用端子218と素子電極432とが電気的に接続される。

【0041】

上述の構成を備えた半導体パッケージモジュール1は、U出力端子130U、V出力端子130V及びW出力端子130Wが、例えば3相交流モータの各端子に接続される。また、P外部電極130P及びN外部電極130Nが、太陽電池等の外部電源に接続される。半導体パッケージモジュール1は、外部電源から供給される直流電力を交流電力に変換して3相交流モータに供給する。

【0042】

(半導体パッケージモジュールの製造方法)

本実施形態に係る半導体パッケージモジュール1は、例えば次のようにして製造することができる。図7(A)〜図7(D)、図8(A)及び図8(B)、図9(A)及び図9(B)、図10(A)及び図10(B)は、半導体パッケージモジュールの製造工程を説明するための工程模式図である。なお、図7(B)〜図7(D)では、山折り部分を実線で示し、谷折り部分を破線で示す。

【0043】

まず、図7(A)に示すように、U相パッケージ210U、V相パッケージ210V及びW相パッケージ210Wを用意する。

【0044】

また、図7(B)に示すように、U出力端子130U用の金属板131U、V出力端子130V用の金属板131V、及びW出力端子130W用の金属板131Wをそれぞれ用意する。金属板131U,131V,131Wは、銅を主成分とする材料からなる。そして、金属板131U,131V,131Wの一端側を矢印iで示すように谷折りしてU出力端子130U、V出力端子130V及びW出力端子130Wを形成する。また、他端側を矢印iiで示すように谷折りし、矢印iiiで示すように山折りして、折曲部134U,134V,134Wを形成する。

【0045】

また、図7(C)に示すように、N外部電極130N用の金属板131Nを用意する。金属板131Nは、銅を主成分とする材料からなる。そして、金属板131Nの一端側を矢印iで示すように山折りしてN外部電極130Nを形成する。また、途中部分を矢印iiで示すように谷折りしてパッケージ積層体200の角部に対応する屈曲部を形成する。さらに、他端側を矢印iiiで示すように山折りし、矢印ivで示すように谷折りして、3つの折曲部134Nを形成する。

【0046】

また、図7(D)に示すように、P外部電極130P用の金属板131Pを用意する。金属板131Pは、銅を主成分とする材料からなる。そして、金属板131Pの一端側を矢印iで示すように山折りしてP外部電極130Pを形成する。また、途中部分を矢印iiで示すように谷折りしてパッケージ積層体200の角部に対応する屈曲部を形成する。さらに、他端側を矢印iiiで示すように山折りし、矢印ivで示すように谷折りして、3つの折曲部134Pを形成する。

【0047】

なお、図7(A)〜図7(D)に示す各工程は、順不同である。

【0048】

次に、図8(A)に示すように、絶縁板240の上に、4枚の放熱板230と3つのパッケージ210とを交互に積層してパッケージ積層体200を形成する。パッケージ210は、W相パッケージ210W、V相パッケージ210V、U相パッケージ210Uの順とする。そして、外部端子130を各パッケージのリード端子212に嵌め合わせる。P外部電極130P及びN外部電極130Nは、絶縁板240側に位置するように嵌め合わされる。また、嵌め合わせの際、各配線部132の被接合領域、すなわち折曲部134の内側と、リード端子212の被接合領域に、スプレー塗布等により溶液500を塗布もしくは充填する。この溶液500は、酸化銅を主成分とする酸化物が溶出する溶液であり、例えばアンモニア水である。

【0049】

上述のように、折曲部134及びリード端子212は、銅を主成分とする材料からなる。そのため、折曲部134及びリード端子212の最表面は、銅が大気中で酸化することで形成される自然酸化膜で構成される。この自然酸化膜は、酸化銅を主成分とする酸化物で構成される膜である。ここで、「酸化銅を主成分とする」は、酸化銅の含有量が50%よりも大きいことを意味する。なお、折曲部134及びリード端子212の最表面を構成する酸化銅は、自然酸化以外の方法で形成されたものであってもよい。

【0050】

溶液500を塗布すると、折曲部134の最表面を構成する酸化銅が溶液500中に溶出する。また、リード端子212の最表面を構成する酸化銅が溶液500中に溶出する。折曲部134の最表面を構成する酸化銅及びリード端子212の最表面を構成する酸化銅が溶液500に溶出することにより、折曲部134の露出面及びリード端子212の露出面にそれぞれ銅が露出する。また、溶液500中では、配位子となるアンモニアイオンと銅イオンとにより銅錯体が形成される。本実施形態では、銅錯体は、[Cu(NH3)4]2+で表される加熱分解性のテトラアンミン銅錯イオンとして存在すると考えられる。なお、アンモニア水は銅に対して不活性であるため、折曲部134及びリード端子212を構成する銅はアンモニア水と反応せずに残存する。

【0051】

次に、図8(B)に示すように、各折曲部134をステンレスブロック体510で挟み、プレス機を用いて、折曲部134にステンレスブロック体510を押し当て、折曲部134の被接合部とリード端子212の被接合部との間の距離を縮めるように折曲部134とリード端子212とを加圧する。この工程における加圧時の圧力は、たとえば、1MPaである。なお、折曲部134とリード端子212との被接合面には上述した溶液500が介在する。

【0052】

続いて、折曲部134とリード端子212とを加圧した状態で、200℃〜300℃の比較的低温な条件下で加熱することにより、折曲部134の被接合部およびリード端子212の被接合部への銅の固相拡散を進行させる。この固相拡散により、折曲部134の被接合部とリード端子212の被接合部とが接合される。固相拡散による接合が完了した後、加熱を停止して加圧を解除し、ステンレスブロック体510を取り除いて、折曲部134とリード端子212の接合工程が完了する。

【0053】

次に、図9(A)に示すように、外部端子130が接続されたパッケージ積層体200を、ケース体100の収容空間111に収容する。パッケージ積層体200は、パッケージ210の制御用端子218が突出する側面とは反対の側面が、本体部110の底部112側を向くようにして、収容空間111に収容される。収容空間111内で、パッケージ210の側面と底部112とが当接する。

【0054】

次に、図9(B)に示すように、収容空間111に封止材300を充填する。

【0055】

次に、図10(A)に示すように、制御基板400を収容空間111に収容し、制御用端子218と配線パターン420とをはんだ付けする。これにより、制御用端子218と制御用IC430とが電気的に接続される。そして、蓋部120を本体部110に嵌め合わせる。

【0056】

以上の工程により、図10(B)に示すように、本実施形態に係る半導体パッケージモジュール1が完成する。

【0057】

なお、本実施形態では、リード端子212と配線部132の折曲部134とを固相拡散接合により接合させているが、外部端子130とリード端子212とを直に接続する場合は、外部端子130とリード端子212とが固相拡散接合により接合される。

【0058】

上述した半導体パッケージモジュール1の製造方法では、折曲部134及びリード端子212の最表面に形成された酸化銅を主成分とする酸化物を溶液500中に溶出させて、折曲部134及びリード端子212の被接合面を活性化させ、両者を銅の固相拡散により接合する。そのため、比較的低温な条件下で折曲部134及びリード端子212を接合することができる。これにより、折曲部134の被接合面とリード端子212の被接合面との間にボイドが発生したり副生成物が介在することが抑制されるため、両者の接続信頼性を高めることができる。また、折曲部134とリード端子212との間の接触抵抗を小さくすることができるため、本実施形態の半導体パッケージモジュール1は、インバータ用の半導体パッケージモジュール等の、大電流を流すパッケージモジュールに好適に採用することができる。

【0059】

また、折曲部134及びリード端子212の表面に形成された酸化被膜をプレス加工によって破壊することなく、上述のように溶液500を用いて溶出させるため、折曲部134とリード端子212とを接合する際に必要な荷重が1MPa程度で済む。このため、折曲部134とリード端子212との接合部分に機械的なダメージが入ることが抑制され、ひいては、リーク電流が増大することを抑制することができる。

【0060】

なお、上述した製造方法では、溶液500としてアンモニア水が用いられているが、銅と錯体を形成する配位子を含む溶液であれば、これに限られず、たとえば、カルボン酸水溶液であってもよい。カルボン酸水溶液の調製に用いられるカルボン酸としては、酢酸などのモノカルボン酸、また、シュウ酸、マロン酸、コハク酸、グルタル酸、フタル酸、マレイン酸などのジカルボン酸、さらに、酒石酸、クエン酸、乳酸、サリチル酸などのオキシカルボン酸が挙げられる。

【0061】

このうち、カルボン酸水溶液は多座配位子となるカルボン酸を有することが好ましい。多座配位子となるカルボン酸を有するカルボン酸水溶液では、カルボン酸と銅がキレートを形成することにより銅錯体の安定性が非常に大きくなる。この結果、接合に必要な温度をより低温化させることができる。なお、酒石酸がキレートを形成することについては、「理化学辞典 第4版(岩波書店)」の第593頁に記載されている。また、酒石酸、シュウ酸などがキレートを形成することは「ヘスロップジョーンズ 無機化学(下) 齋藤喜彦 訳」の第666頁に記載されている。ここで、キレート化とは、多座配位子によって環が形成されることによって錯体の安定度が非常に大きくなることをいう。

【0062】

以上説明したように、本実施形態に係る半導体パッケージモジュール1では、半導体素子214を収容する扁平状の複数のパッケージ210は、隣接するパッケージ210の主表面同士が対向するように配置された状態でケース体100に収容される。そのため、複数のパッケージを、隣接するパッケージの側面同士を対向させていた従来の構造に比べて、設置面積を縮小することができる。

【0063】

また、本実施形態の半導体パッケージモジュール1では、各パッケージの一側面がケース体100の底部112に当接し、当該側面と対向する側面上に制御基板400が配置される。そのため、各パッケージの両主表面に放熱板230を当接させることができ、パッケージの放熱性を向上させることができる。また、半導体パッケージモジュール1全体での熱の不均衡を是正することができる。

【0064】

さらに、各パッケージ210を、主表面同士が対向するように配置している。そのため、上述した従来の構造では、厚さの異なるパッケージを配列させた場合、厚さの差に起因した段差によりパッケージ上への制御基板の積層に支障が生じるおそれがあったが、本実施形態ではそのような支障が生じることはない。したがって、パッケージの組み合わせの自由度が高いため、半導体パッケージモジュール1の拡張性を向上させることができる。

【0065】

(実施形態2)

実施形態2に係る半導体パッケージモジュール1は、N外部電極130Nの配線部132Nの形状を除き、実施形態1に係る半導体パッケージモジュール1の構成と共通する。以下、実施形態2に係る半導体パッケージモジュールについて実施形態1と異なる構成を中心に説明する。実施形態1と同一の構成については同一の符号を付し、その説明は適宜省略する。

【0066】

図11(A)は、実施形態2に係る半導体パッケージモジュールのパッケージ積層体をU相端子、V相端子、W相端子が突出する側面側から見た概略斜視図である。図11(B)は、パッケージ積層体をP電極端子及びN電極端子が突出する側面側から見た概略斜視図である。なお、図10(A)及び図10(B)では、ケース体100の外部端子が接続されたパッケージ積層体200が底部112上に載置された状態を示している。

【0067】

本実施形態に係る半導体パッケージモジュール1において、電位が固定電位であるN外部電極130Nの配線部132Nは、パッケージ210の積層方向から見て、パッケージ210の主表面と重なる領域にノイズ抑制部136を有する。ノイズ抑制部136は、略平板状であり、絶縁板240の主表面を覆う。本実施形態では、ノイズ抑制部136は、配線部132と一体的に形成される。したがってノイズ抑制部136は、配線部132Nにおける配線幅が広くなった部分である。

【0068】

各パッケージ210において、U相パッケージ210Uの半導体素子214Uは、U相パッケージ210U及びV相パッケージ210Vのノイズ抑制部材216により電磁波から保護される。また、V相パッケージ210Vの半導体素子214Vは、V相パッケージ210V及びW相パッケージ210Wのノイズ抑制部材216により電磁波から保護される。また、W相パッケージ210Wの半導体素子214Uは、W相パッケージ210Wのノイズ抑制部材216と、ノイズ抑制部136とにより電磁波から保護される。

【0069】

以上説明した本実施形態に係る半導体パッケージモジュール1によれば、実施形態1で得られる効果に加えて、各パッケージ210の半導体素子214を電磁ノイズからより確実に保護することができるという効果が得られる。これにより、半導体パッケージモジュール1の動作信頼性をより向上させることができる。

【0070】

本発明は、上述の各実施形態に限定されるものではなく、当業者の知識に基づいて各種の設計変更等の変形を加えることも可能であり、そのような変形が加えられた実施形態も本発明の範囲に含まれうるものである。

【0071】

上述の各実施形態では、半導体パッケージモジュール1は3つのパッケージ210を有し、全てのパッケージ210を、隣接するパッケージの主表面同士が対向するように配置された状態でケース体100に収容している。しかしながら、半導体パッケージモジュール1の構成は特にこれに限定されず、3つ以上のパッケージ210をケース体100に収容する場合において、少なくとも2つのパッケージ210が、すなわち、第1のパッケージ210と第2のパッケージ210とが、互いの主表面同士が対向するように配置された状態でケース体100に収容されていればよい。この場合であっても上述した各実施形態の効果を得ることができる。

【符号の説明】

【0072】

1 半導体パッケージモジュール、 100 ケース体、 130 外部端子、 130N N外部電極、 130P P外部電極、 130U U出力端子、 130V V出力端子、 130W W出力端子、 132,132N,132P,132U,132V,132W 配線部、 136 ノイズ抑制部、 210 パッケージ、 210U U相パッケージ、 210V V相パッケージ、 210W W相パッケージ、 212 リード端子、 212N N電極端子、 212P P電極端子、 212U U相端子、 212V V相端子、 212W W相端子、 214,214U,214V,214W 半導体素子、 216 ノイズ抑制部材、 218 制御用端子、 230 放熱板、 400 制御基板。

【特許請求の範囲】

【請求項1】

半導体素子を収容する扁平状の第1のパッケージ、及び半導体素子を収容する扁平状の第2のパッケージを、互いの主表面同士が対向するように配置された状態でケース体に収容することを特徴とする半導体パッケージモジュール。

【請求項2】

複数のリード端子を有し、前記複数のリード端子に電気的に接続される半導体素子を収容する扁平状の複数のパッケージと、

前記複数のパッケージを隣接するパッケージの主表面同士が対向するように配置された状態で収容し、前記複数のパッケージの各リード端子に接続される複数の外部端子を有するケース体と、

を備えることを特徴とする半導体パッケージモジュール。

【請求項3】

前記複数のパッケージは、インバータのU相のスイッチング動作を行う半導体素子を収容し、前記リード端子としてP電極端子、N電極端子及びU相端子を有するU相パッケージ、インバータのV相のスイッチング動作を行う半導体素子を収容し、前記リード端子としてP電極端子、N電極端子及びV相端子を有するV相パッケージ、及びインバータのW相のスイッチング動作を行う半導体素子を収容し、前記リード端子としてP電極端子、N電極端子及びW相端子を有するW相パッケージを含み、

前記ケース体は、前記外部端子として、各パッケージのP電極端子が並列に接続されるP外部電極、各パッケージのN電極端子が並列に接続されるN外部電極、前記U相端子が電気的に接続されるU出力端子、前記V相端子が電気的に接続されるV出力端子、及び前記W相端子が電気的に接続されるW出力端子を有する請求項2に記載の半導体パッケージモジュール。

【請求項4】

各パッケージは、前記半導体素子の動作を制御する制御信号が入力される制御用端子を有し、

各パッケージの前記制御用端子に接続され、前記制御信号を各パーケージに出力する制御基板をさらに備え、

前記制御基板は、その主表面が各パッケージの側面と対向するように配置される請求項2又は3に記載の半導体パッケージモジュール。

【請求項5】

前記複数のリード端子と、前記複数の外部端子又は各外部端子の配線部とは、被接合部が銅を主成分とする金属からなり、互いの被接合部が固相拡散接合される請求項2乃至4のいずれか1項に記載の半導体パッケージモジュール。

【請求項6】

前記パッケージを放熱する複数の放熱板をさらに備え、

前記複数の放熱板と複数のパッケージとは、互いの主表面が対向するようにして配列される請求項2乃至5のいずれか1項に記載の半導体パッケージモジュール。

【請求項7】

前記複数のパッケージは、前記複数のリード端子のうち電位が固定電位である固定電位リード端子に電気的に接続され、パッケージの主表面と平行に配置される、ノイズ抑制部材を有する請求項2乃至6のいずれか1項に記載の半導体パッケージモジュール。

【請求項8】

前記複数の外部端子のうち電位が固定電位である外部端子の配線部は、各パッケージのリード端子と電気的に接続されるとともに、最外側のパッケージの主表面側に引き回され、パッケージの積層方向から見て、パッケージの主表面と重なる領域にノイズ抑制部を有する請求項2乃至7のいずれかに記載の半導体パッケージモジュール。

【請求項1】

半導体素子を収容する扁平状の第1のパッケージ、及び半導体素子を収容する扁平状の第2のパッケージを、互いの主表面同士が対向するように配置された状態でケース体に収容することを特徴とする半導体パッケージモジュール。

【請求項2】

複数のリード端子を有し、前記複数のリード端子に電気的に接続される半導体素子を収容する扁平状の複数のパッケージと、

前記複数のパッケージを隣接するパッケージの主表面同士が対向するように配置された状態で収容し、前記複数のパッケージの各リード端子に接続される複数の外部端子を有するケース体と、

を備えることを特徴とする半導体パッケージモジュール。

【請求項3】

前記複数のパッケージは、インバータのU相のスイッチング動作を行う半導体素子を収容し、前記リード端子としてP電極端子、N電極端子及びU相端子を有するU相パッケージ、インバータのV相のスイッチング動作を行う半導体素子を収容し、前記リード端子としてP電極端子、N電極端子及びV相端子を有するV相パッケージ、及びインバータのW相のスイッチング動作を行う半導体素子を収容し、前記リード端子としてP電極端子、N電極端子及びW相端子を有するW相パッケージを含み、

前記ケース体は、前記外部端子として、各パッケージのP電極端子が並列に接続されるP外部電極、各パッケージのN電極端子が並列に接続されるN外部電極、前記U相端子が電気的に接続されるU出力端子、前記V相端子が電気的に接続されるV出力端子、及び前記W相端子が電気的に接続されるW出力端子を有する請求項2に記載の半導体パッケージモジュール。

【請求項4】

各パッケージは、前記半導体素子の動作を制御する制御信号が入力される制御用端子を有し、

各パッケージの前記制御用端子に接続され、前記制御信号を各パーケージに出力する制御基板をさらに備え、

前記制御基板は、その主表面が各パッケージの側面と対向するように配置される請求項2又は3に記載の半導体パッケージモジュール。

【請求項5】

前記複数のリード端子と、前記複数の外部端子又は各外部端子の配線部とは、被接合部が銅を主成分とする金属からなり、互いの被接合部が固相拡散接合される請求項2乃至4のいずれか1項に記載の半導体パッケージモジュール。

【請求項6】

前記パッケージを放熱する複数の放熱板をさらに備え、

前記複数の放熱板と複数のパッケージとは、互いの主表面が対向するようにして配列される請求項2乃至5のいずれか1項に記載の半導体パッケージモジュール。

【請求項7】

前記複数のパッケージは、前記複数のリード端子のうち電位が固定電位である固定電位リード端子に電気的に接続され、パッケージの主表面と平行に配置される、ノイズ抑制部材を有する請求項2乃至6のいずれか1項に記載の半導体パッケージモジュール。

【請求項8】

前記複数の外部端子のうち電位が固定電位である外部端子の配線部は、各パッケージのリード端子と電気的に接続されるとともに、最外側のパッケージの主表面側に引き回され、パッケージの積層方向から見て、パッケージの主表面と重なる領域にノイズ抑制部を有する請求項2乃至7のいずれかに記載の半導体パッケージモジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−115322(P2013−115322A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−261929(P2011−261929)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

[ Back to top ]