半導体パッケージ及びこれを含む半導体パッケージモジュール

【課題】工程コストが低減するとともに、製造工程が簡素化された半導体パッケージ及びこれを含む半導体パッケージモジュールを提供する。

【解決手段】本発明の半導体パッケージ100は、ボンディングパッド120を有する半導体チップ110と、ボンディングパッド120に電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターン141と、ショート(short)型再配線パターン141と同一層上で多数個に分離形成されたオープン(open)型再配線パターンAとを含む再配線層140と、オープン(open)型再配線パターンAそれぞれに形成された信号連結用接続端子1D、2Dとを有する第1基板150と、を含む。

【解決手段】本発明の半導体パッケージ100は、ボンディングパッド120を有する半導体チップ110と、ボンディングパッド120に電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターン141と、ショート(short)型再配線パターン141と同一層上で多数個に分離形成されたオープン(open)型再配線パターンAとを含む再配線層140と、オープン(open)型再配線パターンAそれぞれに形成された信号連結用接続端子1D、2Dとを有する第1基板150と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体パッケージ及びこれを含む半導体パッケージモジュールに関する。

【背景技術】

【0002】

半導体産業において技術開発の主な傾向の一つは、半導体素子のサイズを縮小することである。半導体パッケージ分野においても小型コンピュータ及び携帯用電子機器などの需要急増に伴い、小型のサイズを有するとともに多数のピン(pin)を具現することができるファインピッチボールグリッドアレイ(Fine pitch Ball Grid Array;FBGA)パッケージまたはチップスケールパッケージ(Chip Scale Package;CSP)などの半導体パッケージが開発されている。

【0003】

現在開発中のファインピッチボールグリッドアレイパッケージまたはチップスケールパッケージなどのような半導体パッケージは、小型化及び軽量化などの物理的利点がある反面、まだ、従来のプラスチックパッケージ(plastic package)と同等な信頼性を確保できておらず、生産過程で要する原料及び工程のコストが高いため、価格競争力に劣るという短所がある。

【0004】

特に、現在チップスケールパッケージの代表的な種類であるマイクロボールグリッドアレイ(micro BGA;μ BGA)パッケージは、ファインピッチボールグリッドアレイまたはチップスケールパッケージに比べ改善した特性を有してはいるが、依然として信頼度及び価格競争力に劣っているという短所がある。

【0005】

このような短所を克服するために開発されたパッケージの一つとして、ウェハ上に形成された半導体チップのボンディングパッド(bonding pad)を再配置(redistribution)または再配線(rerouting)する方法を用いるウェハレベルチップスケールパッケージ(Wafer Level CSP;WL−CSP)がある。

【0006】

再配置を用いるウェハレベルチップスケールパッケージは、半導体素子の製造工程において、直接半導体基板上のボンディングパッドをより大きいサイズの他のパッドで再配置した後、その上にソルダボール(solder ball)のような外部接続端子を形成することをその構造的特徴とする。

【0007】

一方、従来技術による半導体パッケージが、特許文献1に開示されている。

【0008】

このように従来技術による半導体パッケージは、再配線パターンの拡張性により2層以上の多層に構成されることができ、多層に製造されることにより、工程コストが増加し、工程数の増加に伴って工程時間が増加するという問題があった。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】韓国公開特許第2011−0032158号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は、前記従来技術の問題点を解決するためのものであって、製造工程が簡素化された半導体パッケージ及びこれを含む半導体パッケージモジュールを提供することを目的とする。

【0011】

また、本発明は、製造工程コストが低減された半導体パッケージ及びこれを含む半導体パッケージモジュールを提供することを他の目的とする。

【課題を解決するための手段】

【0012】

本発明の半導体パッケージは、ボンディングパッドを有する半導体チップと、前記ボンディングパッドに電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターンと、前記ショート(short)型再配線パターンと同一層上で多数個に分離形成されたオープン(open)型再配線パターンとを含む再配線層と、前記オープン(open)型再配線パターンそれぞれに形成された信号連結用接続端子とを有する第1基板と、を含む。

【0013】

ここで、前記半導体パッケージは、ウェハレベルパッケージ(wafer Level Package;WLP)であってもよい。

【0014】

また、前記半導体パッケージは、半導体ウェハを用いて形成されることが好ましい。

【0015】

また、前記第1基板は、前記再配線層が形成される絶縁層と、前記ショート(short)型再配線パターンに形成された外部接続端子と、をさらに含むことが好ましい。

【0016】

また、前記再配線層をカバーするように前記絶縁層上に形成され、前記外部接続端子及び信号連結用接続端子が形成される部分を露出する開口部を有するソルダレジスト層をさらに含むことが好ましい。

【0017】

この際、前記外部接続端子は、ソルダボール(solder ball)であってもよく、また、前記信号連結用接続端子は、ソルダボール(solder ball)であってもよい。

【0018】

また、本発明の半導体パッケージモジュールは、ボンディングパッドを有する半導体チップと、前記ボンディングパッドに電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターンと、前記ショート(short)型再配線パターンと同一層上で多数個で分離形成されたオープン(open)型再配線パターンとを含む再配線層と、前記オープン(open)型再配線パターンそれぞれに形成された信号連結用接続端子とを有する第1基板と、からなる半導体パッケージと、前記信号連結用接続端子に接するとともに分離形成された前記オープン(open)型再配線パターンを電気的に連結するための信号連結用接続パッドを有する第2基板と、を含む。

【0019】

ここで、前記半導体パッケージは、ウェハレベルパッケージ(wafer Level Package;WLP)であってもよい。

【0020】

また、前記半導体パッケージは、半導体ウェハを用いて形成されることが好ましい。

【0021】

また、前記第1基板は、前記再配線層が形成される絶縁層と、前記ショート(short)型再配線パターンに形成された外部接続端子と、をさらに含むことが好ましい。

【0022】

また、前記再配線層をカバーするように前記絶縁層上に形成され、前記外部接続端子及び信号連結用接続端子が形成される部分を露出する開口部を有するソルダレジスト層をさらに含むことが好ましい。

【0023】

この際、前記外部接続端子は、ソルダボール(solder ball)であってもよく、また、前記信号連結用接続端子は、ソルダボール(solder ball)であってもよい。

【0024】

また、前記第2基板は、印刷回路基板(Printed Circuit Board;PCB)であってもよい。

【0025】

本発明の特徴及び利点は、添付図面に基づいた以下の詳細な説明によってさらに明らかになるであろう。

【0026】

本発明の詳細な説明に先立ち、本明細書及び特許請求の範囲に用いられた用語や単語は、通常的かつ辞書的な意味に解釈されてはならず、発明者が自らの発明を最善の方法で説明するために用語の概念を適切に定義することができるという原則にしたがって本発明の技術的思想にかなう意味と概念に解釈されるべきである。

【発明の効果】

【0027】

本発明は、同一層で電気的に連結されることができないパターンを多数個に分離形成し、分離形成された各パターンごとに信号連結用接続端子を形成した半導体パッケージを、前記分離形成されたパターンを電気的に連結することができる信号連結用接続パッドが形成されたメイン基板に接合することにより、従来複数層にわたって形成しなければならなかったパターンを一つの層で具現することができるため、層数の減少により工程コストが低減するという効果を有する。

【0028】

また、本発明は、複数層にわたって形成しなければならないパターンを一つの層にオープン型パターンで具現することにより、製造工程の時間及び工程数の縮小に伴う工程簡素化により、工程効率が向上するという効果を有する。

【図面の簡単な説明】

【0029】

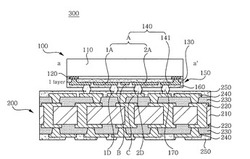

【図1】本発明の半導体パッケージモジュールの構造を示す断面図である。

【図2】本発明の半導体パッケージモジュールの構造と比較するための既存の半導体パッケージモジュール構造を示す断面図である。

【図3】本発明の半導体パッケージモジュールの半導体パッケージの下面を示す平面図である。

【発明を実施するための形態】

【0030】

本発明の目的、特定の長所及び新規の特徴は、添付図面に係わる以下の詳細な説明及び好ましい実施例によってさらに明らかになるであろう。本明細書において、各図面の構成要素に参照番号を付け加えるに際し、同一の構成要素に限っては、たとえ異なる図面に示されても、できるだけ同一の番号を付けるようにしていることに留意しなければならない。また、本発明を説明するにあたり、係わる公知技術についての具体的な説明が本発明の要旨を不明瞭にする可能性があると判断される場合には、その詳細な説明を省略する。本明細書において、第1、第2などの用語は、一つの構成要素を他の構成要素から区別するために用いられるものであり、前記構成要素は前記用語によって限定されない。

【0031】

以下、図面を参照して、本発明について詳細に説明する。

【0032】

図1は、本発明の半導体パッケージモジュールの構造を示す断面図であり、図2は、本発明の半導体パッケージモジュール構造と比較するための既存の半導体パッケージモジュール構造を示す断面図であり、図3は、本発明の半導体パッケージモジュールの半導体パッケージの下面を示す平面図である。

【0033】

図1を参照すると、本発明による半導体パッケージモジュール300は、半導体パッケージ100及び半導体パッケージ100に接合した第2基板200を含む。

【0034】

本発明において、半導体パッケージ100は、ウェハレベルパッケージ(wafer Level Package;WLP)であってもよく、特にこれに限定されず、例えば、ボールグリッドアレイ(Ball Grid Array:BGA)、チップスケールパッケージ(Chip Scale Package;CSP)などであってもよい。

【0035】

本発明による半導体パッケージ100は、半導体チップ110と第1基板150とを含むことが好ましい。

【0036】

半導体チップ110には、回路部(不図示)が形成されており、前記回路部(不図示)は、外部から入力された入力信号を処理してデータ信号を発生するものであって、ボンディングパッド120は、前記回路部(不図示)に電気的に連結され、外部入力信号を前記回路部(不図示)に伝達したり、または前記回路部(不図示)から処理されたデータ信号を外部に出力することができる。

【0037】

ここで、ボンディングパッド120は、導電物質で形成することが好ましく、例えば、アルミニウム(Al)、金(Au)、銀(Ag)、銅(Cu)またはこれらの合金を用いることが好ましいが、特にこれに限定されない。

【0038】

本発明において第1基板150は、絶縁層130及び絶縁層130に形成された再配線層140を含むことが好ましい。

【0039】

ここで、絶縁層130としては、樹脂絶縁層を用いることが好ましい。前記樹脂絶縁層としては、エポキシ樹脂のような熱硬化性樹脂、ポリイミドのような熱可塑性樹脂、またはこれらにガラス繊維または無機フィラーのような補強材が含浸された樹脂、例えば、プリプレグを用いることが好ましく、また、熱硬化性樹脂及び/または光硬化性樹脂などを用いることが好ましいが、特にこれに限定されない。

【0040】

本発明において前記再配線層140は、半導体チップ110のボンディングパッド120に電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターン141、Bと、前記ショート(short)型再配線パターン141、Bと同一層上で多数個に分離形成されたオープン(open)型再配線パターンAとを含むことが好ましい。

【0041】

本発明において前記再配線層140は、半導体チップ110と外部装置とを電気的に連結する一つの手段であることが好ましい。

【0042】

本発明において前記再配線層140は、アルミニウム(Al)、銅(Cu)、スズ(Sn)、ニッケル(Ni)、金(Au)、白金(Pt)及びこれらの合金からなってもよく、特にこれに限定されず、例えば、銅/金/ニッケルが順に形成された多層膜からなることが好ましい。

【0043】

本発明において前記ショート型再配線パターン141、Bは、同一層で断線することなく完全に繋がって電気的に連結されることができるパターンを意味する用語として用いられる。

【0044】

また、本発明において前記オープン型再配線パターンAは、実質的には同一信号を伝達するために同一層で断線することなく繋がって連結されるべきパターンであるにもかかわらず、それらを横切るまた他のパターンによって連結されることができず、分離して形成されたパターンを意味する用語として用いられる。

【0045】

例えば、図3に図示したように、オープン(open)型再配線パターン1A、2Aは、実質的には、同一層で同一信号を伝達するために電気的に連結された一つのパターン1A、2A、3Aに形成されるべきであるにもかかわらず、その間を横切って形成される他のパターンである「B」とのショート(short)を防止するために、(パターン「3A」が形成されず)断線された状態で形成されたパターンを意味する。

【0046】

しかし、図2を参照すると、従来は、同一層で連結されることができないパターン1A′及びパターン2A′を電気的に連結するために、絶縁層13をさらに一層形成し、前記絶縁層13上に前記パッド1A′及びパッド2A′にそれぞれ接するビア及び前記ビアに連結形成されたパッドを含むパターン3A′を形成することにより、1−レイヤ(layer)に位置した1A′及び2A′が2−レイヤ(layer)に位置した3A′を介して電気的に連結されるようにしている。

【0047】

しかし、このように層数を増やすことによって、工程時間及び工程数が増加して、工程効率が減少し、工程コストが増加するという問題が生じ得る。

【0048】

従って、本発明では、前記のように、1−レイヤ(layer)に形成されたパターン1A及び2Aはこれらを横切るパターンBに接しないように分離形成した後、形成されたパターン1A及び2Aの一部にそれぞれ信号連結用接続端子1D、2Dを形成する。

【0049】

本発明においてオープン型再配線パターンAの各パターン1A、2Aの一部には、前記のように、信号連結用接続端子1D、2Dを形成することが好ましい。

【0050】

ここで、信号連結用接続端子1D、2Dは、図1に図示したように、ソルダボール(solder ball)であってもよく、特にこれに限定されず、金属バンプ、ACF(Anisotropic Conductive Film)、NCF(Non Conductive Film)からなってもよい。

【0051】

また、前記再配線層140のうちオープン型再配線パターンAを除いたショート型再配線パターン141、Bの一部にも図1のように外部接続端子170を形成することが好ましく、この際、外部接続端子170もまたソルダボールであってもよく、特にこれに限定されず、前記のように金属バンプ、ACF(Anisotropic Conductive Film)、NCF(Non Conductive Film)からなってもよい。

【0052】

また、本発明において信号連結用接続端子1D、2Dと外部接続端子170は、互いに同一の材質からなってもよく、相違する材質からなってもよい。

【0053】

本発明において、半導体パッケージ100は、半導体ウェハを用いて形成することが好ましいが、特にこれに限定されない。

【0054】

例えば、半導体チップ110が形成されたウェハ(不図示)上に絶縁層130及び再配線層を順に形成した後、半導体ウェハを切断して個別半導体パッケージ100を製造することが好ましい。

【0055】

ここで、再配線層140を形成する工程は、特に制限されず、当業界で一般的に用いられる回路形成工程は、全て適用することができ、前記回路形成工程は、当業界に既に公知された技術であるため、その詳細な説明は省略する。

【0056】

また、本発明では、第1基板150の絶縁層130上に前記再配線層140をカバーするソルダレジスト層160がさらに形成されることが好ましい。

【0057】

ここで、ソルダレジスト層160は、構造的支持及び電気的分離のために形成されるものであって、前記オープン型再配線パターンA及びショート型再配線パターン141、Bをカバーするが、オープン型再配線パターンAの一部及びショート型再配線パターン141、Bの一部を露出するように形成されることが好ましい。

【0058】

このようにオープン型再配線パターンA及びショート型再配線パターン141、Bの露出した部分それぞれには、前記信号連結用接続端子1D、2D及び外部接続端子170を形成することが好ましい。

【0059】

本発明による半導体パッケージモジュール300における第2基板200は、印刷回路基板(Printed Circuit Board;PCB)であってもよい。

【0060】

本発明において第2基板200は、図1に図示したように、第1絶縁層210、第1絶縁層210を貫通するビア及びパターンを含む第1回路層220、第1回路層220をカバーするように形成された第2絶縁層230、第2絶縁層230上に形成され、ビア及びパターンを含む第2回路層240及び第2回路層240の一部を露出する開口部を有するように形成されたソルダレジスト層250を含むものである。

【0061】

本発明では、図1のように、コア層の両面に絶縁層及び回路層が形成された印刷回路基板を例に挙げているが、特にこれに限定されず、単層または多層コアレス基板であってもよい。

【0062】

また、本発明において第2基板200は、最外層の回路層をカバーし、前記回路層の一部は露出させるソルダレジスト層250をさらに含むことが好ましい。

【0063】

図1を参照すると、前記オープン型再配線パターン1A、2Aは、それぞれ信号連結用接続端子1D、2Dを介して第2基板200の信号連結用接続パッドCに連結されることが分かる。

【0064】

具体的に説明すると、次のとおりである。

【0065】

半導体パッケージ100の第1基板150の絶縁層130を横切るショート型再配線パターン「B」に接しないように分離して離隔形成されたオープン型再配線パターン1A、2A(図3参照)は、半導体パッケージ100内では互いに電気的に連結されず開放(open)された構造を有しており、オープン型再配線パターン1A、2Aに連結形成された各バンプパッドP1、P3には信号連結用接続端子1D、2Dが形成されている。

【0066】

また、後工程で半導体パッケージ100に接合される第2基板200には、電気的に連結された信号連結用接続パッドCが形成されている。

【0067】

従って、半導体パッケージ100と第2基板200とを接合して信号連結用接続端子1D、2Dに信号連結用接続パッドCが接するようにすることにより、結果的に開放された状態のオープン型再配線パターン1A、2Aは、信号連結用接続パッドCによって電気的に連結することができる。

【0068】

図2に図示した従来の半導体パッケージモジュール30と、本発明による半導体パッケージモジュール300との電気的な連結構造の差を説明すると、図2に図示された半導体パッケージモジュール30における半導体パッケージ10の第1基板15は、本発明とは異なり、2−レイヤ(layer)からなっている。

【0069】

これは、同一層で電気的に連結されるべきパターン1A′、2A′が、これを横切る他のパターンB′によって一層で連結されず、絶縁層13をさらに一層形成した後、形成された絶縁層13にこれらのパターン1A′、2A′を電気的に連結するためのパターン3A′を形成するためである。

【0070】

即ち、同一層で連結されなかったパターンを電気的に連結するためには、半導体パッケージ10の第1基板15は、多層構造にするしかなかった。

【0071】

これと異なり、本発明では、実質的には同一層で同一信号を伝達するために電気的に連結されるべきであるが、他のパターンによって連結することができないパターンを層に追加して半導体パッケージ内で連結せず、以降に接合されるメインボードに分離形成されたパターンを電気的に連結するパターンを形成することにより、半導体パッケージの基板を単層に具現することができ、これによって、既存の多層基板の製造に比べ、工程数及び工程時間が減少して、結果的に工程効率が向上する。

【0072】

また、半導体パッケージで半導体チップが実装される基板を単層に具現することができるため、モジュールの製造コストを低減することができる。

【0073】

一方、本発明では、2−レイヤ(layer)からなる半導体パッケージの基板を単層に具現することについて記述しているが、これは、一つの例に過ぎず、3層以上の多層基板をそれより少ない層数を有する多層基板に具現することもまた可能であると言える。

【0074】

以上、本発明を具体的な実施例に基づいて詳細に説明したが、これは、本発明を具体的に説明するためのものであり、本発明による半導体パッケージ及びこれを含む半導体パッケージモジュールは、これに限定されず、該当分野における通常の知識を有する者であれば、本発明の技術的思想内にての変形や改良が可能であることは明白であろう。

【0075】

本発明の単純な変形乃至変更は、いずれも本発明の領域に属するものであり、本発明の具体的な保護範囲は、添付の特許請求の範囲により明確になるであろう。

【産業上の利用可能性】

【0076】

本発明は、工程コストが低減するとともに、製造工程が簡素化された半導体パッケージ及びこれを含む半導体パッケージモジュールに適用可能である。

【符号の説明】

【0077】

100 半導体パッケージ

110 半導体チップ

120 ボンディングパッド

130 絶縁層

140 再配線層

141 ショート型再配線パターン

150 第1基板

160 ソルダレジスト層

170 外部接続端子

200 第2基板

210 第1絶縁層

220 第1回路層

230 第2絶縁層

240 第2回路層

250 ソルダレジスト層

300 半導体パッケージモジュール

A(1A、2A) オープン型再配線パターン

B ショート型再配線パターン

C 信号連結用接続パッド

1D、2D 信号連結用接続端子

P1、P2、P3 バンプパッド

【技術分野】

【0001】

本発明は、半導体パッケージ及びこれを含む半導体パッケージモジュールに関する。

【背景技術】

【0002】

半導体産業において技術開発の主な傾向の一つは、半導体素子のサイズを縮小することである。半導体パッケージ分野においても小型コンピュータ及び携帯用電子機器などの需要急増に伴い、小型のサイズを有するとともに多数のピン(pin)を具現することができるファインピッチボールグリッドアレイ(Fine pitch Ball Grid Array;FBGA)パッケージまたはチップスケールパッケージ(Chip Scale Package;CSP)などの半導体パッケージが開発されている。

【0003】

現在開発中のファインピッチボールグリッドアレイパッケージまたはチップスケールパッケージなどのような半導体パッケージは、小型化及び軽量化などの物理的利点がある反面、まだ、従来のプラスチックパッケージ(plastic package)と同等な信頼性を確保できておらず、生産過程で要する原料及び工程のコストが高いため、価格競争力に劣るという短所がある。

【0004】

特に、現在チップスケールパッケージの代表的な種類であるマイクロボールグリッドアレイ(micro BGA;μ BGA)パッケージは、ファインピッチボールグリッドアレイまたはチップスケールパッケージに比べ改善した特性を有してはいるが、依然として信頼度及び価格競争力に劣っているという短所がある。

【0005】

このような短所を克服するために開発されたパッケージの一つとして、ウェハ上に形成された半導体チップのボンディングパッド(bonding pad)を再配置(redistribution)または再配線(rerouting)する方法を用いるウェハレベルチップスケールパッケージ(Wafer Level CSP;WL−CSP)がある。

【0006】

再配置を用いるウェハレベルチップスケールパッケージは、半導体素子の製造工程において、直接半導体基板上のボンディングパッドをより大きいサイズの他のパッドで再配置した後、その上にソルダボール(solder ball)のような外部接続端子を形成することをその構造的特徴とする。

【0007】

一方、従来技術による半導体パッケージが、特許文献1に開示されている。

【0008】

このように従来技術による半導体パッケージは、再配線パターンの拡張性により2層以上の多層に構成されることができ、多層に製造されることにより、工程コストが増加し、工程数の増加に伴って工程時間が増加するという問題があった。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】韓国公開特許第2011−0032158号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は、前記従来技術の問題点を解決するためのものであって、製造工程が簡素化された半導体パッケージ及びこれを含む半導体パッケージモジュールを提供することを目的とする。

【0011】

また、本発明は、製造工程コストが低減された半導体パッケージ及びこれを含む半導体パッケージモジュールを提供することを他の目的とする。

【課題を解決するための手段】

【0012】

本発明の半導体パッケージは、ボンディングパッドを有する半導体チップと、前記ボンディングパッドに電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターンと、前記ショート(short)型再配線パターンと同一層上で多数個に分離形成されたオープン(open)型再配線パターンとを含む再配線層と、前記オープン(open)型再配線パターンそれぞれに形成された信号連結用接続端子とを有する第1基板と、を含む。

【0013】

ここで、前記半導体パッケージは、ウェハレベルパッケージ(wafer Level Package;WLP)であってもよい。

【0014】

また、前記半導体パッケージは、半導体ウェハを用いて形成されることが好ましい。

【0015】

また、前記第1基板は、前記再配線層が形成される絶縁層と、前記ショート(short)型再配線パターンに形成された外部接続端子と、をさらに含むことが好ましい。

【0016】

また、前記再配線層をカバーするように前記絶縁層上に形成され、前記外部接続端子及び信号連結用接続端子が形成される部分を露出する開口部を有するソルダレジスト層をさらに含むことが好ましい。

【0017】

この際、前記外部接続端子は、ソルダボール(solder ball)であってもよく、また、前記信号連結用接続端子は、ソルダボール(solder ball)であってもよい。

【0018】

また、本発明の半導体パッケージモジュールは、ボンディングパッドを有する半導体チップと、前記ボンディングパッドに電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターンと、前記ショート(short)型再配線パターンと同一層上で多数個で分離形成されたオープン(open)型再配線パターンとを含む再配線層と、前記オープン(open)型再配線パターンそれぞれに形成された信号連結用接続端子とを有する第1基板と、からなる半導体パッケージと、前記信号連結用接続端子に接するとともに分離形成された前記オープン(open)型再配線パターンを電気的に連結するための信号連結用接続パッドを有する第2基板と、を含む。

【0019】

ここで、前記半導体パッケージは、ウェハレベルパッケージ(wafer Level Package;WLP)であってもよい。

【0020】

また、前記半導体パッケージは、半導体ウェハを用いて形成されることが好ましい。

【0021】

また、前記第1基板は、前記再配線層が形成される絶縁層と、前記ショート(short)型再配線パターンに形成された外部接続端子と、をさらに含むことが好ましい。

【0022】

また、前記再配線層をカバーするように前記絶縁層上に形成され、前記外部接続端子及び信号連結用接続端子が形成される部分を露出する開口部を有するソルダレジスト層をさらに含むことが好ましい。

【0023】

この際、前記外部接続端子は、ソルダボール(solder ball)であってもよく、また、前記信号連結用接続端子は、ソルダボール(solder ball)であってもよい。

【0024】

また、前記第2基板は、印刷回路基板(Printed Circuit Board;PCB)であってもよい。

【0025】

本発明の特徴及び利点は、添付図面に基づいた以下の詳細な説明によってさらに明らかになるであろう。

【0026】

本発明の詳細な説明に先立ち、本明細書及び特許請求の範囲に用いられた用語や単語は、通常的かつ辞書的な意味に解釈されてはならず、発明者が自らの発明を最善の方法で説明するために用語の概念を適切に定義することができるという原則にしたがって本発明の技術的思想にかなう意味と概念に解釈されるべきである。

【発明の効果】

【0027】

本発明は、同一層で電気的に連結されることができないパターンを多数個に分離形成し、分離形成された各パターンごとに信号連結用接続端子を形成した半導体パッケージを、前記分離形成されたパターンを電気的に連結することができる信号連結用接続パッドが形成されたメイン基板に接合することにより、従来複数層にわたって形成しなければならなかったパターンを一つの層で具現することができるため、層数の減少により工程コストが低減するという効果を有する。

【0028】

また、本発明は、複数層にわたって形成しなければならないパターンを一つの層にオープン型パターンで具現することにより、製造工程の時間及び工程数の縮小に伴う工程簡素化により、工程効率が向上するという効果を有する。

【図面の簡単な説明】

【0029】

【図1】本発明の半導体パッケージモジュールの構造を示す断面図である。

【図2】本発明の半導体パッケージモジュールの構造と比較するための既存の半導体パッケージモジュール構造を示す断面図である。

【図3】本発明の半導体パッケージモジュールの半導体パッケージの下面を示す平面図である。

【発明を実施するための形態】

【0030】

本発明の目的、特定の長所及び新規の特徴は、添付図面に係わる以下の詳細な説明及び好ましい実施例によってさらに明らかになるであろう。本明細書において、各図面の構成要素に参照番号を付け加えるに際し、同一の構成要素に限っては、たとえ異なる図面に示されても、できるだけ同一の番号を付けるようにしていることに留意しなければならない。また、本発明を説明するにあたり、係わる公知技術についての具体的な説明が本発明の要旨を不明瞭にする可能性があると判断される場合には、その詳細な説明を省略する。本明細書において、第1、第2などの用語は、一つの構成要素を他の構成要素から区別するために用いられるものであり、前記構成要素は前記用語によって限定されない。

【0031】

以下、図面を参照して、本発明について詳細に説明する。

【0032】

図1は、本発明の半導体パッケージモジュールの構造を示す断面図であり、図2は、本発明の半導体パッケージモジュール構造と比較するための既存の半導体パッケージモジュール構造を示す断面図であり、図3は、本発明の半導体パッケージモジュールの半導体パッケージの下面を示す平面図である。

【0033】

図1を参照すると、本発明による半導体パッケージモジュール300は、半導体パッケージ100及び半導体パッケージ100に接合した第2基板200を含む。

【0034】

本発明において、半導体パッケージ100は、ウェハレベルパッケージ(wafer Level Package;WLP)であってもよく、特にこれに限定されず、例えば、ボールグリッドアレイ(Ball Grid Array:BGA)、チップスケールパッケージ(Chip Scale Package;CSP)などであってもよい。

【0035】

本発明による半導体パッケージ100は、半導体チップ110と第1基板150とを含むことが好ましい。

【0036】

半導体チップ110には、回路部(不図示)が形成されており、前記回路部(不図示)は、外部から入力された入力信号を処理してデータ信号を発生するものであって、ボンディングパッド120は、前記回路部(不図示)に電気的に連結され、外部入力信号を前記回路部(不図示)に伝達したり、または前記回路部(不図示)から処理されたデータ信号を外部に出力することができる。

【0037】

ここで、ボンディングパッド120は、導電物質で形成することが好ましく、例えば、アルミニウム(Al)、金(Au)、銀(Ag)、銅(Cu)またはこれらの合金を用いることが好ましいが、特にこれに限定されない。

【0038】

本発明において第1基板150は、絶縁層130及び絶縁層130に形成された再配線層140を含むことが好ましい。

【0039】

ここで、絶縁層130としては、樹脂絶縁層を用いることが好ましい。前記樹脂絶縁層としては、エポキシ樹脂のような熱硬化性樹脂、ポリイミドのような熱可塑性樹脂、またはこれらにガラス繊維または無機フィラーのような補強材が含浸された樹脂、例えば、プリプレグを用いることが好ましく、また、熱硬化性樹脂及び/または光硬化性樹脂などを用いることが好ましいが、特にこれに限定されない。

【0040】

本発明において前記再配線層140は、半導体チップ110のボンディングパッド120に電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターン141、Bと、前記ショート(short)型再配線パターン141、Bと同一層上で多数個に分離形成されたオープン(open)型再配線パターンAとを含むことが好ましい。

【0041】

本発明において前記再配線層140は、半導体チップ110と外部装置とを電気的に連結する一つの手段であることが好ましい。

【0042】

本発明において前記再配線層140は、アルミニウム(Al)、銅(Cu)、スズ(Sn)、ニッケル(Ni)、金(Au)、白金(Pt)及びこれらの合金からなってもよく、特にこれに限定されず、例えば、銅/金/ニッケルが順に形成された多層膜からなることが好ましい。

【0043】

本発明において前記ショート型再配線パターン141、Bは、同一層で断線することなく完全に繋がって電気的に連結されることができるパターンを意味する用語として用いられる。

【0044】

また、本発明において前記オープン型再配線パターンAは、実質的には同一信号を伝達するために同一層で断線することなく繋がって連結されるべきパターンであるにもかかわらず、それらを横切るまた他のパターンによって連結されることができず、分離して形成されたパターンを意味する用語として用いられる。

【0045】

例えば、図3に図示したように、オープン(open)型再配線パターン1A、2Aは、実質的には、同一層で同一信号を伝達するために電気的に連結された一つのパターン1A、2A、3Aに形成されるべきであるにもかかわらず、その間を横切って形成される他のパターンである「B」とのショート(short)を防止するために、(パターン「3A」が形成されず)断線された状態で形成されたパターンを意味する。

【0046】

しかし、図2を参照すると、従来は、同一層で連結されることができないパターン1A′及びパターン2A′を電気的に連結するために、絶縁層13をさらに一層形成し、前記絶縁層13上に前記パッド1A′及びパッド2A′にそれぞれ接するビア及び前記ビアに連結形成されたパッドを含むパターン3A′を形成することにより、1−レイヤ(layer)に位置した1A′及び2A′が2−レイヤ(layer)に位置した3A′を介して電気的に連結されるようにしている。

【0047】

しかし、このように層数を増やすことによって、工程時間及び工程数が増加して、工程効率が減少し、工程コストが増加するという問題が生じ得る。

【0048】

従って、本発明では、前記のように、1−レイヤ(layer)に形成されたパターン1A及び2Aはこれらを横切るパターンBに接しないように分離形成した後、形成されたパターン1A及び2Aの一部にそれぞれ信号連結用接続端子1D、2Dを形成する。

【0049】

本発明においてオープン型再配線パターンAの各パターン1A、2Aの一部には、前記のように、信号連結用接続端子1D、2Dを形成することが好ましい。

【0050】

ここで、信号連結用接続端子1D、2Dは、図1に図示したように、ソルダボール(solder ball)であってもよく、特にこれに限定されず、金属バンプ、ACF(Anisotropic Conductive Film)、NCF(Non Conductive Film)からなってもよい。

【0051】

また、前記再配線層140のうちオープン型再配線パターンAを除いたショート型再配線パターン141、Bの一部にも図1のように外部接続端子170を形成することが好ましく、この際、外部接続端子170もまたソルダボールであってもよく、特にこれに限定されず、前記のように金属バンプ、ACF(Anisotropic Conductive Film)、NCF(Non Conductive Film)からなってもよい。

【0052】

また、本発明において信号連結用接続端子1D、2Dと外部接続端子170は、互いに同一の材質からなってもよく、相違する材質からなってもよい。

【0053】

本発明において、半導体パッケージ100は、半導体ウェハを用いて形成することが好ましいが、特にこれに限定されない。

【0054】

例えば、半導体チップ110が形成されたウェハ(不図示)上に絶縁層130及び再配線層を順に形成した後、半導体ウェハを切断して個別半導体パッケージ100を製造することが好ましい。

【0055】

ここで、再配線層140を形成する工程は、特に制限されず、当業界で一般的に用いられる回路形成工程は、全て適用することができ、前記回路形成工程は、当業界に既に公知された技術であるため、その詳細な説明は省略する。

【0056】

また、本発明では、第1基板150の絶縁層130上に前記再配線層140をカバーするソルダレジスト層160がさらに形成されることが好ましい。

【0057】

ここで、ソルダレジスト層160は、構造的支持及び電気的分離のために形成されるものであって、前記オープン型再配線パターンA及びショート型再配線パターン141、Bをカバーするが、オープン型再配線パターンAの一部及びショート型再配線パターン141、Bの一部を露出するように形成されることが好ましい。

【0058】

このようにオープン型再配線パターンA及びショート型再配線パターン141、Bの露出した部分それぞれには、前記信号連結用接続端子1D、2D及び外部接続端子170を形成することが好ましい。

【0059】

本発明による半導体パッケージモジュール300における第2基板200は、印刷回路基板(Printed Circuit Board;PCB)であってもよい。

【0060】

本発明において第2基板200は、図1に図示したように、第1絶縁層210、第1絶縁層210を貫通するビア及びパターンを含む第1回路層220、第1回路層220をカバーするように形成された第2絶縁層230、第2絶縁層230上に形成され、ビア及びパターンを含む第2回路層240及び第2回路層240の一部を露出する開口部を有するように形成されたソルダレジスト層250を含むものである。

【0061】

本発明では、図1のように、コア層の両面に絶縁層及び回路層が形成された印刷回路基板を例に挙げているが、特にこれに限定されず、単層または多層コアレス基板であってもよい。

【0062】

また、本発明において第2基板200は、最外層の回路層をカバーし、前記回路層の一部は露出させるソルダレジスト層250をさらに含むことが好ましい。

【0063】

図1を参照すると、前記オープン型再配線パターン1A、2Aは、それぞれ信号連結用接続端子1D、2Dを介して第2基板200の信号連結用接続パッドCに連結されることが分かる。

【0064】

具体的に説明すると、次のとおりである。

【0065】

半導体パッケージ100の第1基板150の絶縁層130を横切るショート型再配線パターン「B」に接しないように分離して離隔形成されたオープン型再配線パターン1A、2A(図3参照)は、半導体パッケージ100内では互いに電気的に連結されず開放(open)された構造を有しており、オープン型再配線パターン1A、2Aに連結形成された各バンプパッドP1、P3には信号連結用接続端子1D、2Dが形成されている。

【0066】

また、後工程で半導体パッケージ100に接合される第2基板200には、電気的に連結された信号連結用接続パッドCが形成されている。

【0067】

従って、半導体パッケージ100と第2基板200とを接合して信号連結用接続端子1D、2Dに信号連結用接続パッドCが接するようにすることにより、結果的に開放された状態のオープン型再配線パターン1A、2Aは、信号連結用接続パッドCによって電気的に連結することができる。

【0068】

図2に図示した従来の半導体パッケージモジュール30と、本発明による半導体パッケージモジュール300との電気的な連結構造の差を説明すると、図2に図示された半導体パッケージモジュール30における半導体パッケージ10の第1基板15は、本発明とは異なり、2−レイヤ(layer)からなっている。

【0069】

これは、同一層で電気的に連結されるべきパターン1A′、2A′が、これを横切る他のパターンB′によって一層で連結されず、絶縁層13をさらに一層形成した後、形成された絶縁層13にこれらのパターン1A′、2A′を電気的に連結するためのパターン3A′を形成するためである。

【0070】

即ち、同一層で連結されなかったパターンを電気的に連結するためには、半導体パッケージ10の第1基板15は、多層構造にするしかなかった。

【0071】

これと異なり、本発明では、実質的には同一層で同一信号を伝達するために電気的に連結されるべきであるが、他のパターンによって連結することができないパターンを層に追加して半導体パッケージ内で連結せず、以降に接合されるメインボードに分離形成されたパターンを電気的に連結するパターンを形成することにより、半導体パッケージの基板を単層に具現することができ、これによって、既存の多層基板の製造に比べ、工程数及び工程時間が減少して、結果的に工程効率が向上する。

【0072】

また、半導体パッケージで半導体チップが実装される基板を単層に具現することができるため、モジュールの製造コストを低減することができる。

【0073】

一方、本発明では、2−レイヤ(layer)からなる半導体パッケージの基板を単層に具現することについて記述しているが、これは、一つの例に過ぎず、3層以上の多層基板をそれより少ない層数を有する多層基板に具現することもまた可能であると言える。

【0074】

以上、本発明を具体的な実施例に基づいて詳細に説明したが、これは、本発明を具体的に説明するためのものであり、本発明による半導体パッケージ及びこれを含む半導体パッケージモジュールは、これに限定されず、該当分野における通常の知識を有する者であれば、本発明の技術的思想内にての変形や改良が可能であることは明白であろう。

【0075】

本発明の単純な変形乃至変更は、いずれも本発明の領域に属するものであり、本発明の具体的な保護範囲は、添付の特許請求の範囲により明確になるであろう。

【産業上の利用可能性】

【0076】

本発明は、工程コストが低減するとともに、製造工程が簡素化された半導体パッケージ及びこれを含む半導体パッケージモジュールに適用可能である。

【符号の説明】

【0077】

100 半導体パッケージ

110 半導体チップ

120 ボンディングパッド

130 絶縁層

140 再配線層

141 ショート型再配線パターン

150 第1基板

160 ソルダレジスト層

170 外部接続端子

200 第2基板

210 第1絶縁層

220 第1回路層

230 第2絶縁層

240 第2回路層

250 ソルダレジスト層

300 半導体パッケージモジュール

A(1A、2A) オープン型再配線パターン

B ショート型再配線パターン

C 信号連結用接続パッド

1D、2D 信号連結用接続端子

P1、P2、P3 バンプパッド

【特許請求の範囲】

【請求項1】

ボンディングパッドを有する半導体チップと、

前記ボンディングパッドに電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターンと、前記ショート(short)型再配線パターンと同一層上で多数個に分離形成されたオープン(open)型再配線パターンとを含む再配線層と、前記オープン(open)型再配線パターンそれぞれに形成された信号連結用接続端子とを有する第1基板と、

を含む半導体パッケージ。

【請求項2】

前記半導体パッケージは、ウェハレベルパッケージ(wafer Level Package;WLP)である請求項1に記載の半導体パッケージ。

【請求項3】

前記半導体パッケージは、半導体ウェハを用いて形成される請求項1に記載の半導体パッケージ。

【請求項4】

前記第1基板は、

前記再配線層が形成される絶縁層と、

前記ショート(short)型再配線パターンに形成された外部接続端子と、

をさらに含む請求項1に記載の半導体パッケージ。

【請求項5】

前記再配線層をカバーするように前記絶縁層上に形成され、前記外部接続端子及び信号連結用接続端子が形成される部分を露出する開口部を有するソルダレジスト層をさらに含む請求項4に記載の半導体パッケージ。

【請求項6】

前記外部接続端子は、ソルダボール(solder ball)である請求項4に記載の半導体パッケージ。

【請求項7】

前記信号連結用接続端子は、ソルダボール(solder ball)である請求項1に記載の半導体パッケージ。

【請求項8】

ボンディングパッドを有する半導体チップと、前記ボンディングパッドに電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターンと、前記ショート(short)型再配線パターンと同一層上で多数個に分離形成されたオープン(open)型再配線パターンとを含む再配線層と、前記オープン(open)型再配線パターンそれぞれに形成された信号連結用接続端子とを有する第1基板と、からなる半導体パッケージと、

前記信号連結用接続端子に接するとともに分離形成された前記オープン(open)型再配線パターンを電気的に連結するための信号連結用接続パッドを有する第2基板と、

を含む半導体パッケージモジュール。

【請求項9】

前記半導体パッケージは、ウェハレベルパッケージ(wafer Level Package;WLP)である請求項8に記載の半導体パッケージモジュール。

【請求項10】

前記半導体パッケージは、半導体ウェハを用いて形成される請求項8に記載の半導体パッケージモジュール。

【請求項11】

前記第1基板は、

前記再配線層が形成される絶縁層と、

前記ショート(short)型再配線パターンに形成された外部接続端子と、

をさらに含む請求項8に記載の半導体パッケージモジュール。

【請求項12】

前記再配線層をカバーするように前記絶縁層上に形成され、前記外部接続端子及び信号連結用接続端子が形成される部分を露出する開口部を有するソルダレジスト層をさらに含む請求項11に記載の半導体パッケージモジュール。

【請求項13】

前記外部接続端子は、ソルダボール(solder ball)である請求項11に記載の半導体パッケージモジュール。

【請求項14】

前記信号連結用接続端子は、ソルダボール(solder ball)である請求項8に記載の半導体パッケージモジュール。

【請求項15】

前記第2基板は、印刷回路基板(Printed Circuit Board;PCB)である請求項8に記載の半導体パッケージモジュール。

【請求項1】

ボンディングパッドを有する半導体チップと、

前記ボンディングパッドに電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターンと、前記ショート(short)型再配線パターンと同一層上で多数個に分離形成されたオープン(open)型再配線パターンとを含む再配線層と、前記オープン(open)型再配線パターンそれぞれに形成された信号連結用接続端子とを有する第1基板と、

を含む半導体パッケージ。

【請求項2】

前記半導体パッケージは、ウェハレベルパッケージ(wafer Level Package;WLP)である請求項1に記載の半導体パッケージ。

【請求項3】

前記半導体パッケージは、半導体ウェハを用いて形成される請求項1に記載の半導体パッケージ。

【請求項4】

前記第1基板は、

前記再配線層が形成される絶縁層と、

前記ショート(short)型再配線パターンに形成された外部接続端子と、

をさらに含む請求項1に記載の半導体パッケージ。

【請求項5】

前記再配線層をカバーするように前記絶縁層上に形成され、前記外部接続端子及び信号連結用接続端子が形成される部分を露出する開口部を有するソルダレジスト層をさらに含む請求項4に記載の半導体パッケージ。

【請求項6】

前記外部接続端子は、ソルダボール(solder ball)である請求項4に記載の半導体パッケージ。

【請求項7】

前記信号連結用接続端子は、ソルダボール(solder ball)である請求項1に記載の半導体パッケージ。

【請求項8】

ボンディングパッドを有する半導体チップと、前記ボンディングパッドに電気的に連結され、断線することなく繋がるように形成されたショート(short)型再配線パターンと、前記ショート(short)型再配線パターンと同一層上で多数個に分離形成されたオープン(open)型再配線パターンとを含む再配線層と、前記オープン(open)型再配線パターンそれぞれに形成された信号連結用接続端子とを有する第1基板と、からなる半導体パッケージと、

前記信号連結用接続端子に接するとともに分離形成された前記オープン(open)型再配線パターンを電気的に連結するための信号連結用接続パッドを有する第2基板と、

を含む半導体パッケージモジュール。

【請求項9】

前記半導体パッケージは、ウェハレベルパッケージ(wafer Level Package;WLP)である請求項8に記載の半導体パッケージモジュール。

【請求項10】

前記半導体パッケージは、半導体ウェハを用いて形成される請求項8に記載の半導体パッケージモジュール。

【請求項11】

前記第1基板は、

前記再配線層が形成される絶縁層と、

前記ショート(short)型再配線パターンに形成された外部接続端子と、

をさらに含む請求項8に記載の半導体パッケージモジュール。

【請求項12】

前記再配線層をカバーするように前記絶縁層上に形成され、前記外部接続端子及び信号連結用接続端子が形成される部分を露出する開口部を有するソルダレジスト層をさらに含む請求項11に記載の半導体パッケージモジュール。

【請求項13】

前記外部接続端子は、ソルダボール(solder ball)である請求項11に記載の半導体パッケージモジュール。

【請求項14】

前記信号連結用接続端子は、ソルダボール(solder ball)である請求項8に記載の半導体パッケージモジュール。

【請求項15】

前記第2基板は、印刷回路基板(Printed Circuit Board;PCB)である請求項8に記載の半導体パッケージモジュール。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−110375(P2013−110375A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2012−15211(P2012−15211)

【出願日】平成24年1月27日(2012.1.27)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成24年1月27日(2012.1.27)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

[ Back to top ]