半導体パッケージ基板及び半導体パッケージ基板の製造方法

【課題】本発明は、半導体パッケージ基板及び半導体パッケージ基板の製造方法に関する。

【解決手段】本発明の一実施例によると、パッドが形成されたキャリア基板を準備する段階と、前記パッドの上部に絶縁層を形成する段階と、前記キャリア基板を除去する段階と、前記絶縁層及び前記パッドの上部に回路層を形成する段階と、前記パッドの一部をエッチングし、前記絶縁層の内部に開口部を形成する段階と、を含む半導体パッケージ基板の製造方法が提供される。

【解決手段】本発明の一実施例によると、パッドが形成されたキャリア基板を準備する段階と、前記パッドの上部に絶縁層を形成する段階と、前記キャリア基板を除去する段階と、前記絶縁層及び前記パッドの上部に回路層を形成する段階と、前記パッドの一部をエッチングし、前記絶縁層の内部に開口部を形成する段階と、を含む半導体パッケージ基板の製造方法が提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体パッケージ基板及び半導体パッケージ基板の製造方法に関する。

【背景技術】

【0002】

高密度集積化及び薄型化されている半導体素子の技術進歩に伴い、半導体パッケージを製造するための組み立て技術も大きく発展している。これとともに、全世界的にポータブル電子機器の市場が拡大するに伴い、小型化及び軽量化が急速に推進されている。これにより、ファインピッチ(fine pitch)化、小型化及び薄型化を実現するための様々な形態の半導体パッケージング方法が開発された(米国登録特許第6225144号)。しかし、従来の半導体パッケージング方法は、電子機器の小型化により基板と基板に実装される半導体素子との間の離隔空間が小さくなっている。これにより、半導体素子を基板に実装した後モールドする(molding)際、エポキシが半導体素子と基板との間の空間に均一に染み込むことができず、信頼性を有する半導体パッケージングが困難となっている。

【発明の開示】

【発明が解決しようとする課題】

【0003】

本発明の一側面は、絶縁層の内部をエッチングすることにより、半導体素子と絶縁層との間の離隔空間を安定して形成することができる半導体パッケージ基板及び半導体パッケージ基板の製造方法を提供することをその目的とする。

【0004】

本発明の他の側面は、パッド及び回路層の厚さを利用して半導体素子と絶縁層との間の離隔空間を確保することにより、半導体パッケージの厚さを増加させることなく半導体素子と絶縁層との間の十分な離隔空間を形成することができる半導体パッケージ基板及び半導体パッケージ基板の製造方法を提供することをその目的とする。

【課題を解決するための手段】

【0005】

本発明の一側面によると、パッドが形成されたキャリア基板を準備する段階と、パッドの上部に絶縁層を形成する段階と、キャリア基板を除去する段階と、絶縁層及びパッドの上部に回路層を形成する段階と、パッドの一部をエッチングし、絶縁層の内部に開口部を形成する段階と、を含む半導体パッケージ基板の製造方法が提供される。

【0006】

絶縁層を形成する段階で、パッドは絶縁層に埋め込まれることができる。

キャリア基板を除去する段階の後、絶縁層を貫通するビアホールを形成する段階をさらに含むことができる。

回路層を形成する段階で、ビアホールの内部がメッキされることができる。

【0007】

開口部を形成する段階は、パッド一部の上部が開口されるように、回路層の上部にエッチングレジストを塗布する段階と、パッドをエッチングする段階と、エッチングレジストを除去する段階と、を含むことができる。

開口部を形成する段階の後、回路層の上部及び開口部の内壁に接合パッドを形成する段階と、接合パッドの上部に半導体素子を実装する段階と、をさらに含むことができる。

【0008】

本発明の他の側面によると、ベース絶縁層を準備する段階と、ベース絶縁層の一側に、第1のキャリア基板、第1のシード層、第1のパッド、第1のパッドが埋め込まれる第1の絶縁層、第3のシード層、第3の絶縁層及び第5のシード層が積層され形成された第1のビルドアップ層を形成し、ベース絶縁層の他側に、第2のキャリア基板、第2のシード層、第2のパッド、第2のパッドが埋め込まれる第2の絶縁層、第4のシード層、第4の絶縁層及び第6のシード層が積層され形成された第2のビルドアップ層を形成する段階と、第1のキャリア基板及び第2のキャリア基板をベース絶縁層から分離する段階と、第1のビルドアップ層から第1のキャリア基板を除去し、第2のビルドアップ層から第2のキャリア基板を除去する段階と、第1のキャリア基板が除去された第1のビルドアップ層上に第1の回路層を形成し、第2のキャリア基板が除去された第2のビルドアップ層上に第2の回路層を形成する段階と、第1のパッドの一部をエッチングして第1の絶縁層の一部に第1の開口部を形成し、第2のパッドの一部をエッチングして第2の絶縁層の一部に第2の開口部を形成する段階と、を含む半導体パッケージ基板の製造方法が提供される。

【0009】

第1の絶縁層及び第2の絶縁層を形成する段階で、第1のパッドは第1の絶縁層に埋め込まれることができる。

第1の絶縁層及び第2の絶縁層を形成する段階で、第2のパッドは第2の絶縁層に埋め込まれることができる。

【0010】

第1のキャリア基板及び第2のキャリア基板をベース絶縁層から分離する段階の後、第1のビルドアップ層を貫通する第1のビアホールを形成する段階をさらに含むことができる。

第1の回路層を形成する段階で、第1のビアホールの内部がメッキされることができる。

【0011】

第1の回路層を形成する段階で、第1の回路層は、第1のシード層上に形成される上部回路層及び第5のシード層上に形成される下部回路層を含むことができる。

第1のキャリア基板及び第2のキャリア基板をベース絶縁層から分離する段階の後、第2のビルドアップ層を貫通する第2のビアホールを形成する段階をさらに含むことができる。

【0012】

第2の回路層を形成する段階で、第2のビアホールの内部がメッキされることができる。

第2の回路層を形成する段階で、第2の回路層は、第2のシード層上に形成される上部回路層及び第6のシード層上に形成される下部回路層を含むことができる。

【0013】

第1の開口部を形成する段階は、第1のパッド一部の上部が開口されるように、第1の回路層の上部にエッチングレジストを塗布する段階と、第1のパッドをエッチングする段階と、エッチングレジストを除去する段階と、を含むことができる。

第2の開口部を形成する段階は、第2のパッド一部の上部が開口されるように、第2の回路層の上部にエッチングレジストを塗布する段階と、第2のパッドをエッチングする段階と、エッチングレジストを除去する段階と、を含むことができる。

【0014】

本発明のさらに他の側面によると、絶縁層と、絶縁層の内部に埋め込まれ、第1の開口部を有するパッドと、絶縁層及びパッドの上部に形成され、第1の開口部上に形成された第2の開口部を有する上部回路層と、を含む半導体パッケージ基板が提供される。

【0015】

絶縁層の下部に形成される下部回路層をさらに含むことができる。

絶縁層を貫通するように形成され、上部回路層及び下部回路層を電気的に連結するビアをさらに含むことができる。

上部回路層の上部には半導体素子が実装されることができる。

【0016】

本発明のさらに他の側面によると、下部絶縁層と、下部絶縁層の上部に形成され、貫通孔を含むようにパターン化されたシード層と、シード層の上部に形成され、シード層が埋め込まれるように形成される上部絶縁層と、上部絶縁層の内部に埋め込まれ、第1の開口部が形成されたパッドと、上部絶縁層及びパッドの上部に形成され、第1の開口部上に形成された第2の開口部を有する上部回路層と、下部絶縁層の下部に形成された下部回路層と、を含む半導体パッケージ基板が提供される。

【0017】

上部絶縁層、下部絶縁層及びシード層を貫通するように形成され、上部回路層と下部回路層とを電気的に連結するビアをさらに含むことができる。

上部回路層の上部に半導体素子が実装されることができる。

【0018】

本発明の特徴及び利点は添付図面に基づいた以下の詳細な説明によってさらに明らかになるであろう。

本発明の詳細な説明に先立ち、本明細書及び請求範囲に用いられた用語や単語は通常的かつ辞書的な意味に解釈されてはならず、発明者が自らの発明を最善の方法で説明するために用語の概念を適切に定義することができるという原則にしたがって本発明の技術的思想にかなう意味と概念に解釈されるべきである。

【発明の効果】

【0019】

本発明の半導体パッケージ基板及び半導体パッケージ基板の製造方法は、パッドを利用して絶縁層の内部をエッチングすることにより、半導体素子と絶縁層との間の離隔空間を安定して形成することができる。

【0020】

また、本発明の半導体パッケージ基板及び半導体パッケージ基板の製造方法は、パッド及び回路層の厚さを利用して半導体素子と絶縁層との間の離隔空間を確保することにより、半導体パッケージの厚さを増加させることなく半導体素子と絶縁層との間の十分な離隔空間を形成することができる。

【発明を実施するための最良の形態】

【0021】

本発明の目的、特定の長所及び新規の特徴は添付図面に係る以下の詳細な説明及び実施例によってさらに明らかになるであろう。本明細書において、各図面の構成要素に参照番号を付け加えるに際し、同一の構成要素に限っては、たとえ異なる図面に示されても、できるだけ同一の番号を付けるようにしていることに留意しなければならない。

また、本発明を説明するにあたり、係わる公知技術についての具体的な説明が本発明の要旨を不明瞭にする可能性があると判断される場合には、その詳細な説明は省略する。本明細書において、第1、第2などの用語は一つの構成要素を他の構成要素から区別するために用いられるものであり、構成要素が前記用語によって限定されるものではない。

【0022】

以下、添付図面を参照して本発明の実施例による半導体パッケージ基板及び半導体パッケージ基板の製造方法について詳細に説明する。

【0023】

半導体パッケージ基板の製造方法

図1から図9は本発明の一実施例による半導体パッケージ基板の製造方法を工程順に図示した工程断面図である。

【0024】

図1を参照すると、シード層120が形成されたキャリア基板110にパッド130が形成される。

キャリア基板110は、熱可塑性ポリマーまたは金属を利用して形成されることができる。キャリア基板110の材料としては、特に限定されるものではないが、熱可塑性ポリマーとしてはPVC(poly vinyl chloride)、PE(poly ethylene)、PP(ploy propylene)、PS(poly styrene)、ABS(acrylonitrile butadiene styrene copolymer)、Nylon(poly amide)またはPET(poly ethylene terephthalate)などを含むことができる。また、キャリア基板110を形成する金属としては、銅、アルミニウム、ニッケル、亜鉛、クロム、コバルト、タングステン及びこれらの混合物からなる群から選択することができる。

【0025】

シード層120はキャリア基板110上に形成される。ここで、シード層120はスパッタリングまたは無電解メッキ方式を利用して形成されることができる。

シード層120が形成されたキャリア基板110の上部にパッド130が形成される。

パッド130はキャリア基板110から突出された形態に形成されることができる。パッド130は、後でエッチングされることにより、絶縁層(図9の140)と半導体パッケージ基板に実装される半導体素子(図9の190)との間の十分な離隔空間のための開口部(図9の300)を形成するために利用される。キャリア基板110から突出されるパッド130の高さに応じて、絶縁層(図9の140)と半導体素子(図9の190)との離隔空間である開口部(図9の300)の深さが調節されることができる。

【0026】

パッド130は電解メッキ方法を利用してパターニングされ形成されることができる。本発明の実施例におけるパッド130は、シード層120と同一の材質で形成されることができる。

【0027】

図2を参照すると、パッド130が形成されたキャリア基板110に絶縁層140が形成される。

絶縁層140は、パッド130が形成されたキャリア基板110の上部に絶縁物質を積層した後、圧力を加えることにより、パッド130が絶縁層140に埋め込まれる形態に形成されることができる。ここで、絶縁層140は、絶縁素材として通常に用いられる複合高分子樹脂で形成されることができる。絶縁層140は、例えば、プリプレグ、または FR−4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

図3を参照すると、絶縁層140を形成した後、シード層120からキャリア基板(図2の110)が除去される。

【0028】

図4を参照すると、キャリア基板(図2の110)が除去された後、外部に露出されたシード層120に回路層(150)を形成するためのフォトレジスト160を形成する。この際、フォトレジスト160は露光及び現像を施すことにより形成されることができる。このようにフォトレジスト160を形成した後、回路層150を形成するためにメッキを行うことができる。この際、メッキは電解メッキ方法を利用して行われることができる。本発明の実施例では電解メッキ方法を利用しているが、メッキ方法はこれに限定されず、公知されたメッキ方法により行われることができる。また、メッキは、シード層120と同一の物質を用いて行われることができる。本発明の実施例によると、シード層120の厚さと回路層150の厚さを合わせて5〜25μmとなるように回路層150のメッキを行うことができる。しかし、このような回路層150の厚さは本発明の実施例に過ぎず、これに限定されない。

【0029】

図5を参考すると、シード層120上に形成されたフォトレジスト(図4の160)を除去することができる。

図6を参考すると、回路層150の上部にエッチングレジスト170が形成されることができる。ここで、エッチングレジスト170は、絶縁層140の内部に離隔空間が形成される領域が開口されるように形成されることができる。

【0030】

図7を参照すると、絶縁層140の内部に離隔空間を形成するために開口された領域をエッチングする。このようなエッチングにより、開口された領域に該当する絶縁層140の内部に埋め込まれたパッド130がエッチングされる。これにより、絶縁層140の内部に後で実装される半導体素子(図9の190)との離隔空間である開口部300が形成される。このように絶縁層140の内部に開口部300を形成した後、回路層150の上部に形成されたエッチングレジスト(図6の170)を除去する。

【0031】

図8を参照すると、回路層150の上部に形成されたエッチングレジスト(図6の170)が除去されることにより露出されたシード層120をエッチングする。

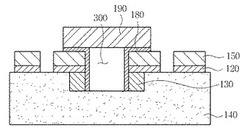

図9を参照すると、回路層150の上部及び開口部300の内壁に、半導体素子190とボンディングされる接合パッド180を形成する。接合パッド180は金メッキにより形成されることができる。このように形成された接合パッド180に半導体素子190を接合させることにより、半導体パッケージ基板に半導体素子190を実装することができる。

このような本発明の一実施例による半導体パッケージ基板の製造方法によりパッドの厚さと回路層の厚さを調節して、基板の厚さを増加させることなく基板と半導体素子との間の離隔空間が十分に形成されることができる。

【0032】

図10から図18は本発明の他の実施例による半導体パッケージ基板の製造方法を工程順に図示した工程断面図である。

図10を参照すると、第1のキャリア基板110、第1のシード層120、パッド130、絶縁層140、第2のキャリア基板111及び第2のシード層121が提供される。第1のキャリア基板110上の第1のシード層120にパッド130が形成され、第2のキャリア基板111上に第2のシード層121が形成される。

【0033】

図11を参照すると、パッド130が形成された第1のキャリア基板(図10の110)の上部に絶縁層140が積層され、絶縁層140の上部に第2のシード層121が形成された第2のキャリア基板(図10の111)が積層される。このように積層した後、絶縁層140及び第2のキャリア基板(図10の111)に圧力を加えることにより、絶縁層140の内部にパッド130が埋め込まれ、絶縁層140と第2のシード層121とが接合される形態になることができる。その後、第1のキャリア基板(図10の110)及び第2のキャリア基板(図10の111)を除去する。

図12を参照すると、第1のシード層120、第2のシード層121及び絶縁層140を貫通するビアホール191を加工する。ビアホール191は、レーザー加工またはルータ加工により加工されることができる。

【0034】

図13を参照すると、第1のシード層120及び第2のシード層121に、回路層(150、151)を形成するための第1のフォトレジスト160及び第2のフォトレジスト161を形成する。この際、第1のフォトレジスト160及び第2のフォトレジスト161は、露光及び現像を施すことにより形成されることができる。このように第1のフォトレジスト160を形成した後、上部回路層150を形成するためのメッキを行うことができる。また、第2のフォトレジスト161を形成した後、下部回路層151を形成するためのメッキを行うことができる。この際、ビアホール(図12の191)も、メッキにより内部が充填されることができる。ここで、メッキは、第1のシード層120及び第2のシード層121と同一の物質を用いて行われることができる。

【0035】

図14を参照すると、第1のフォトレジスト(図3の160)及び第2のフォトレジスト(図3の161)を除去する。

図15を参照すると、第1のフォトレジスト160及び第2のフォトレジスト161を除去した後、第1のエッチングレジスト170及び第2のエッチングレジスト171が形成されることができる。ここで、第1のエッチングレジスト170は、絶縁層140の内部に離隔空間が形成される領域が開口されるように形成されることができる。このような構造に第1のエッチングレジスト170を形成した後、開口された領域にエッチングを行うことができる。この際、第1のエッチングレジスト170により開口された領域に位置した絶縁層140がエッチングされることができる。また、エッチングされた絶縁層140の下部に位置したパッド130もエッチングされることができる。このようなエッチングにより、絶縁層140の内部に後程実装される半導体素子(図18の190)との離隔空間である開口部300が形成される。

【0036】

図16を参考すると、絶縁層140の内部に開口部300を形成した後、第1のエッチングレジスト(図15の170)及び第2のエッチングレジスト(図15の171)を除去する。

図17を参照すると、第1のエッチングレジスト(図15の170)及び第2のエッチングレジスト(図15の171)が除去されることにより露出された第1のシード層120及び第2のシード層121をエッチングすることにより、上部回路層150及び下部回路層151を形成する。

図18を参照すると、上部回路層150の上部及び開口部300の内壁に、半導体素子190とボンディングされる接合パッド180を形成する。接合パッド180は金メッキにより形成されることができる。このように形成された接合パッド180に半導体素子190を接合させた後、ソルダーレジスト192を塗布することにより、半導体パッケージ基板に半導体素子190を実装することができる。

【0037】

図19から図25は本発明のさらに他の実施例による半導体パッケージ基板の製造方法を工程順に図示した工程断面図である。

図19を参照すると、ベース絶縁層210が提供される。ここで、ベース絶縁層210はデュアルコアであり、両側面に夫々ビルドアップ層が形成されることができる。デュアルコアであるベース絶縁層210の一側に、第1のシード層215及び第1のパッド216が形成された第1のキャリア基板214が形成され、ベース絶縁層210の他側に第2のシード層212及び第2のパッド213が形成された第2のキャリア基板211が形成される。

【0038】

図20を参照すると、第1のシード層215及び第1のパッド216の上部に第1の絶縁層231が積層され、第2のシード層212及び第2のパッド213の上部に第2の絶縁層221が積層される。このように第1の絶縁層231及び第2の絶縁層221を積層した後、圧力を加えることにより、第1の絶縁層231の内部に第1のパッド216が埋め込まれ、第2の絶縁層221の内部に第2のパッド213が埋め込まれる形態になることができる。その後、第1の絶縁層231上には、第1の貫通孔237を含むようにパターニングされた第3のシード層232が形成される。また、第2の絶縁層221上には、第2の貫通孔227を含むようにパターニングされた第4のシード層222が形成される。

ここで、図面には図示されていないが、第3のシード層232及び第4のシード層222の上部には内部回路層が形成されることができる。または、第3のシード層232及び第4のシード層222がパターン化することにより、回路層の役割を遂行することもできる。

【0039】

図21を参照すると、第3のシード層232上に第3の絶縁層233を形成し、第4のシード層222上に第4の絶縁層223を積層する。この際、第3の絶縁層233及び第4の絶縁層223が夫々積層された後、圧力を加えることにより、第3の絶縁層233は第1の貫通孔(図20の237)を介して第1の絶縁層231と接合され、第4の絶縁層223は第2の貫通孔(図20の227)を介して第2の絶縁層221と接合される。このように第3の絶縁層233及び第4の絶縁層223を積層した後、第3の絶縁層233の上部に第5のシード層234が形成され、第4の絶縁層223の上部に第6のシード層224が形成される。ここで、第1のキャリア基板214に形成された第1のシード層215、第1の絶縁層231、第3のシード層232、第3の絶縁層233及び第5のシード層234を第1のビルドアップ層と称する。また、第2のキャリア基板211に形成された第2のシード層212、第2の絶縁層221、第4のシード層222、第4の絶縁層223及び第6のシード層224を第2のビルドアップ層と称する。

【0040】

図22を参照すると、第1のキャリア基板(図21の214)及び第2のキャリア基板(図21の211)を夫々ベース絶縁層(図21の210)から分離する。また、第1のキャリア基板(図21の214)及び第2のキャリア基板(図21の211)を夫々ベース絶縁層(図21の210)から分離した後、第1のキャリア基板(図21の214)及び第2のキャリア基板(図21の211)を除去する。

その後、第1のビルドアップ層200を貫通する第1のビアホール191が形成される。図面に図示されていないが、第2のビルドアップ層にも第2のビアホールが形成される。

【0041】

図23を参照すると、第1のシード層215及び第5のシード層234上に、第1の回路層である上部回路層236及び下部回路層235をメッキにより形成することができる。即ち、第1のシード層215上に上部回路層236をメッキにより形成し、第5のシード層234上に下部回路層235をメッキにより形成することができる。この際、第1のビアホール191も、メッキによりその内部が充電されることができる。その後、第1の絶縁層231に埋め込まれている第1のパッド216をエッチングすることにより、開口部300を形成する。

【0042】

図24を参照すると、メッキ後に露出された第1のシード層215及び第5のシード層234を除去することにより、上部回路層236及び下部回路層235を形成する。

図25を参照すると、上部回路層236の上部及び開口部300の内壁に、半導体素子250とボンディングされる接合パッド240を形成する。接合パッド240は金メッキにより形成されることができる。このように形成された接合パッド240に半導体素子250を接合させた後、ソルダーレジスト270を塗布することにより、半導体パッケージ基板に半導体素子250を実装することができる。

ここで、第1のビルドアップ層200を例にとり説明したが、第2のビルドアップ層も同一の工程順序に従って半導体素子が実装されることができる。

【0043】

半導体パッケージ基板

図26は本発明の実施例による半導体パッケージ基板を示した例示図である。

図26を参照すると、本発明の実施例による半導体パッケージ基板400は、絶縁層440と、パッド430と、シード層420と、回路層450と、及び接合パッド480と、を含むことができる。

【0044】

絶縁層440は、絶縁素材として通常用いられる複合高分子樹脂で形成されることができる。絶縁層440は、例えば、プリプレグ、またはFR−4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

【0045】

パッド430は絶縁層の内部に埋め込まれ、第1の開口部401を有することができる。パッド430に形成された第1の開口部401の深さはパッド430の厚さによって変わることができる。例えば、第1の開口部401の深さは、パッド430の厚さと同一であるか、またはパッド430の厚さより小さいことができる。しかし、第1の開口部401の深さはこれに限定されず、当業者によって変更されることができる。

シード層420は、絶縁層440及びパッド430の上部に形成されることができる。この際、シード層420は第1開口部401が露出されるようにパターニングされることができる。

【0046】

回路層450は、絶縁層440及びパッド430の上部に形成されることができる。即ち、回路層450は、絶縁層440及びパッド430の上部に形成されたシード層420上に形成されることができる。また、回路層450は、第1開口部401上に位置するように形成された第2の開口部402を有するように形成されることができる。

接合パッド480は、回路層450の上部、第1の開口部401の内壁及び第2の開口部402の内壁に形成されることができる。接合パッド480は金メッキにより形成されることができる。このように形成された接合パッド480には半導体素子490が実装されることができる。

【0047】

図面には図示されていないが、半導体素子490が実装された後、絶縁層440及び回路層450の上部にソルダーレジストが塗布されることができる。

【0048】

図27は本発明の他の実施例による半導体パッケージ基板を示した例示図である。

図27を参照すると、本発明の実施例による半導体パッケージ基板500は、絶縁層540と、パッド530と、第1のシード層520と、上部回路層550と、接合パッド580と、第2のシード層521と、下部回路層551と、ビア552と、ソルダーレジスト592と、を含むことができる。

【0049】

絶縁層540は、絶縁素材として通常用いられる複合高分子樹脂で形成されることができる。絶縁層540は、例えば、プリプレグ、またはFR-4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

パッド530は絶縁層540の内部に埋め込まれ、第1の開口部501を有することができる。パッド530に形成された第1の開口部501の深さはパッド530の厚さによって変わることができる。例えば、第1の開口部501の深さは、パッド530の厚さと同一であるか、またはパッド530の厚さより小さいことができる。しかし、第1の開口部501の深さはこれに限定されず、当業者によって変更されることができる。

【0050】

第1のシード層520は、絶縁層540及びパッド530の上部に形成されることができる。この際、第1のシード層520は第1の開口部501が露出されるようにパターニングされることができる。

上部回路層550は、絶縁層540及びパッド530の上部に形成されることができる。即ち、上部回路層550は、絶縁層540及びパッド530の上部に形成された第1のシード層520上に形成されることができる。また、上部回路層550は、第1の開口部501上に位置するように形成された第2の開口部502を有するように形成されることができる。

【0051】

接合パッド580は、上部回路層550、第1の開口部501及び第2の開口部502上に形成されることができる。接合パッド580は金メッキにより形成されることができる。このように形成された接合パッド580には半導体素子590が実装されることができる。

第2のシード層521は絶縁層540の下部に形成されることができ、第2のシード層521は所定の形態にパターニングされるように形成されることができる。

【0052】

下部回路層551は絶縁層540の下部に形成されることができる。即ち、下部回路層551は、絶縁層540の下部に形成された第2のシード層521の下部に形成されることができる。

本発明の実施例によると、上部回路層550と下部回路層551とはビア552により連結されることができる。即ち、絶縁層540を貫通するように形成されたビア552により、上部回路層550と下部回路層551とが電気的に連結されるように形成されることができる。

ソルダーレジスト592は第1の絶縁層540の上部及び下部に形成されることができる。

【0053】

図28は本発明のさらに他の実施例による半導体パッケージ基板を示した例示図である。

図28を参照すると、本発明の実施例による半導体パッケージ基板600は、上部絶縁層631と、下部絶縁層633と、シード層632と、上部回路層636と、下部回路層635と、パッド616と、接合パッド640と、ビア637と、ソルダーレジスト670と、を含むことができる。

下部絶縁層633は、絶縁素材として通常用いられる複合高分子樹脂で形成されることができる。下部絶縁層633は、例えば、プリプレグ、またはFR-4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

シード層632は下部絶縁層633の上部に形成されることができる。シード層632は、下部絶縁層633の上部にパターン化されて形成されることができる。図28には図示されていないが、シード層632の上部には内部回路層が形成されることができる。または、シード層632がパターン化されることにより、回路層の役割を遂行することもできる。

【0054】

上部絶縁層631はシード層632上に形成されることができる。上部絶縁層631は、絶縁素材として通常用いられる複合高分子樹脂で形成されることができる。上部絶縁層631は、例えば、プリプレグ、またはFR-4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

本発明の実施例よると、上部絶縁層631は、シード層632を埋め込む形態に形成されることができる。例えば、シード層632上に内部回路層(不図示)が形成された場合、上部絶縁層631は、シード層632及び内部回路層(不図示)を全て埋め込む形態に形成されることができる。

【0055】

パッド616は上部絶縁層631の内部に埋め込まれ、第1の開口部601を有することができる。パッド616に形成された第1の開口部601の深さはパッド616の厚さによって変わることができる。例えば、第1の開口部601の深さは、パッド616の厚さと同一であるか、またはパッド616の厚さより小さいことができる。

上部回路層636は、上部絶縁層631及びパッド616の上部に形成されることができる。上部回路層636は、第1の開口部601上に位置するように形成された第2の開口部602を有するように形成されることができる。ここで、上部回路層636は、上部絶縁層631及びパッド616上に形成された上部シード層615上に形成されるということは、当業者において自明である。

【0056】

接合パッド640は、上部回路層636の上部、第1の開口部601の内壁及び第2の開口部602の内壁に形成されることができる。接合パッド640は金メッキにより形成されることができる。このように形成された接合パッド640には半導体素子650が実装されることができる。

下部回路層635は下部絶縁層633の下部に形成されることができる。下部回路層635は、下部絶縁層633の下部に形成された下部シード層634上に形成されるということは、当業者において自明である。

【0057】

ビア637は、上部絶縁層631及び下部絶縁層633を貫通するように形成されることができる。このように上部絶縁層631及び下部絶縁層633を貫通するように形成されたビア637により、上部回路層636と下部回路層635とが電気的に連結されるように形成されることができる。

ソルダーレジスト670は、上部絶縁層631及び下部絶縁層633に形成されることができる。図28には、ソルダーレジスト670が、上部絶縁層631に形成された上部回路層636及び下部絶縁層633に形成された下部回路層635が埋め込まれるように形成されることで図示されているが、これに限定されない。即ち、ソルダーレジスト670が形成される程度は当業者によって容易に変更されることができる。

【0058】

以上、本発明を実施例に基づいて詳細に説明したが、これは本発明を具体的に説明するためのものであり、本発明による半導体パッケージ基板及び半導体パッケージ基板の製造方法はこれに限定されず、該当技術分野において通常の知識を有する者であれば、添付の特許請求範囲に記載された本発明の思想及び領域を外れない範囲内で多様な修正及び変形が可能であることを理解するであろう。

このような本発明の単純な変形乃至変更はいずれも本発明の領域に属するものであり、本発明の具体的な保護範囲は添付の特許請求の範囲により明確になるであろう

【図面の簡単な説明】

【0059】

【図1】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図2】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図3】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図4】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図5】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図6】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図7】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図8】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図9】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図10】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図11】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図12】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図13】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図14】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図15】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図16】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図17】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図18】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図19】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図20】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図21】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図22】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図23】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図24】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図25】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図26】本発明の実施例による半導体パッケージ基板を示した例示図である。

【図27】本発明の他の実施例による半導体パッケージ基板を示した例示図である。

【図28】本発明のさらに他の実施例による半導体パッケージ基板を示した例示図である。

【符号の説明】

【0060】

110、111、211、214 キャリア基板

120、121、212、215、222、224、232、420、632 シード層

130、213、216、430、530、616 パッド

140、221、223、231、223、233、440、540 絶縁層

150、236、450、550、636 上部回路層

151、235、551、635 下部回路層

160、161 フォトレジスト

170、171 エッチングレジスト

180、240、480、580、640 接合パッド

190、250、490、590、650 半導体素子

191 ビアホール

192、592、670 ソルダーレジスト

200、260 ビルドアップ層

210 ベース絶縁層

227 第2の貫通孔

237 第1の貫通孔

300 開口部

400、500、600 半導体パッケージ基板

401、501、601 第1の開口部

402、502、602 第2の開口部

520 第1のシード層

552、637 ビア

615 上部シード層

631 上部絶縁層

633 下部絶縁層

634 下部シード層

【技術分野】

【0001】

本発明は、半導体パッケージ基板及び半導体パッケージ基板の製造方法に関する。

【背景技術】

【0002】

高密度集積化及び薄型化されている半導体素子の技術進歩に伴い、半導体パッケージを製造するための組み立て技術も大きく発展している。これとともに、全世界的にポータブル電子機器の市場が拡大するに伴い、小型化及び軽量化が急速に推進されている。これにより、ファインピッチ(fine pitch)化、小型化及び薄型化を実現するための様々な形態の半導体パッケージング方法が開発された(米国登録特許第6225144号)。しかし、従来の半導体パッケージング方法は、電子機器の小型化により基板と基板に実装される半導体素子との間の離隔空間が小さくなっている。これにより、半導体素子を基板に実装した後モールドする(molding)際、エポキシが半導体素子と基板との間の空間に均一に染み込むことができず、信頼性を有する半導体パッケージングが困難となっている。

【発明の開示】

【発明が解決しようとする課題】

【0003】

本発明の一側面は、絶縁層の内部をエッチングすることにより、半導体素子と絶縁層との間の離隔空間を安定して形成することができる半導体パッケージ基板及び半導体パッケージ基板の製造方法を提供することをその目的とする。

【0004】

本発明の他の側面は、パッド及び回路層の厚さを利用して半導体素子と絶縁層との間の離隔空間を確保することにより、半導体パッケージの厚さを増加させることなく半導体素子と絶縁層との間の十分な離隔空間を形成することができる半導体パッケージ基板及び半導体パッケージ基板の製造方法を提供することをその目的とする。

【課題を解決するための手段】

【0005】

本発明の一側面によると、パッドが形成されたキャリア基板を準備する段階と、パッドの上部に絶縁層を形成する段階と、キャリア基板を除去する段階と、絶縁層及びパッドの上部に回路層を形成する段階と、パッドの一部をエッチングし、絶縁層の内部に開口部を形成する段階と、を含む半導体パッケージ基板の製造方法が提供される。

【0006】

絶縁層を形成する段階で、パッドは絶縁層に埋め込まれることができる。

キャリア基板を除去する段階の後、絶縁層を貫通するビアホールを形成する段階をさらに含むことができる。

回路層を形成する段階で、ビアホールの内部がメッキされることができる。

【0007】

開口部を形成する段階は、パッド一部の上部が開口されるように、回路層の上部にエッチングレジストを塗布する段階と、パッドをエッチングする段階と、エッチングレジストを除去する段階と、を含むことができる。

開口部を形成する段階の後、回路層の上部及び開口部の内壁に接合パッドを形成する段階と、接合パッドの上部に半導体素子を実装する段階と、をさらに含むことができる。

【0008】

本発明の他の側面によると、ベース絶縁層を準備する段階と、ベース絶縁層の一側に、第1のキャリア基板、第1のシード層、第1のパッド、第1のパッドが埋め込まれる第1の絶縁層、第3のシード層、第3の絶縁層及び第5のシード層が積層され形成された第1のビルドアップ層を形成し、ベース絶縁層の他側に、第2のキャリア基板、第2のシード層、第2のパッド、第2のパッドが埋め込まれる第2の絶縁層、第4のシード層、第4の絶縁層及び第6のシード層が積層され形成された第2のビルドアップ層を形成する段階と、第1のキャリア基板及び第2のキャリア基板をベース絶縁層から分離する段階と、第1のビルドアップ層から第1のキャリア基板を除去し、第2のビルドアップ層から第2のキャリア基板を除去する段階と、第1のキャリア基板が除去された第1のビルドアップ層上に第1の回路層を形成し、第2のキャリア基板が除去された第2のビルドアップ層上に第2の回路層を形成する段階と、第1のパッドの一部をエッチングして第1の絶縁層の一部に第1の開口部を形成し、第2のパッドの一部をエッチングして第2の絶縁層の一部に第2の開口部を形成する段階と、を含む半導体パッケージ基板の製造方法が提供される。

【0009】

第1の絶縁層及び第2の絶縁層を形成する段階で、第1のパッドは第1の絶縁層に埋め込まれることができる。

第1の絶縁層及び第2の絶縁層を形成する段階で、第2のパッドは第2の絶縁層に埋め込まれることができる。

【0010】

第1のキャリア基板及び第2のキャリア基板をベース絶縁層から分離する段階の後、第1のビルドアップ層を貫通する第1のビアホールを形成する段階をさらに含むことができる。

第1の回路層を形成する段階で、第1のビアホールの内部がメッキされることができる。

【0011】

第1の回路層を形成する段階で、第1の回路層は、第1のシード層上に形成される上部回路層及び第5のシード層上に形成される下部回路層を含むことができる。

第1のキャリア基板及び第2のキャリア基板をベース絶縁層から分離する段階の後、第2のビルドアップ層を貫通する第2のビアホールを形成する段階をさらに含むことができる。

【0012】

第2の回路層を形成する段階で、第2のビアホールの内部がメッキされることができる。

第2の回路層を形成する段階で、第2の回路層は、第2のシード層上に形成される上部回路層及び第6のシード層上に形成される下部回路層を含むことができる。

【0013】

第1の開口部を形成する段階は、第1のパッド一部の上部が開口されるように、第1の回路層の上部にエッチングレジストを塗布する段階と、第1のパッドをエッチングする段階と、エッチングレジストを除去する段階と、を含むことができる。

第2の開口部を形成する段階は、第2のパッド一部の上部が開口されるように、第2の回路層の上部にエッチングレジストを塗布する段階と、第2のパッドをエッチングする段階と、エッチングレジストを除去する段階と、を含むことができる。

【0014】

本発明のさらに他の側面によると、絶縁層と、絶縁層の内部に埋め込まれ、第1の開口部を有するパッドと、絶縁層及びパッドの上部に形成され、第1の開口部上に形成された第2の開口部を有する上部回路層と、を含む半導体パッケージ基板が提供される。

【0015】

絶縁層の下部に形成される下部回路層をさらに含むことができる。

絶縁層を貫通するように形成され、上部回路層及び下部回路層を電気的に連結するビアをさらに含むことができる。

上部回路層の上部には半導体素子が実装されることができる。

【0016】

本発明のさらに他の側面によると、下部絶縁層と、下部絶縁層の上部に形成され、貫通孔を含むようにパターン化されたシード層と、シード層の上部に形成され、シード層が埋め込まれるように形成される上部絶縁層と、上部絶縁層の内部に埋め込まれ、第1の開口部が形成されたパッドと、上部絶縁層及びパッドの上部に形成され、第1の開口部上に形成された第2の開口部を有する上部回路層と、下部絶縁層の下部に形成された下部回路層と、を含む半導体パッケージ基板が提供される。

【0017】

上部絶縁層、下部絶縁層及びシード層を貫通するように形成され、上部回路層と下部回路層とを電気的に連結するビアをさらに含むことができる。

上部回路層の上部に半導体素子が実装されることができる。

【0018】

本発明の特徴及び利点は添付図面に基づいた以下の詳細な説明によってさらに明らかになるであろう。

本発明の詳細な説明に先立ち、本明細書及び請求範囲に用いられた用語や単語は通常的かつ辞書的な意味に解釈されてはならず、発明者が自らの発明を最善の方法で説明するために用語の概念を適切に定義することができるという原則にしたがって本発明の技術的思想にかなう意味と概念に解釈されるべきである。

【発明の効果】

【0019】

本発明の半導体パッケージ基板及び半導体パッケージ基板の製造方法は、パッドを利用して絶縁層の内部をエッチングすることにより、半導体素子と絶縁層との間の離隔空間を安定して形成することができる。

【0020】

また、本発明の半導体パッケージ基板及び半導体パッケージ基板の製造方法は、パッド及び回路層の厚さを利用して半導体素子と絶縁層との間の離隔空間を確保することにより、半導体パッケージの厚さを増加させることなく半導体素子と絶縁層との間の十分な離隔空間を形成することができる。

【発明を実施するための最良の形態】

【0021】

本発明の目的、特定の長所及び新規の特徴は添付図面に係る以下の詳細な説明及び実施例によってさらに明らかになるであろう。本明細書において、各図面の構成要素に参照番号を付け加えるに際し、同一の構成要素に限っては、たとえ異なる図面に示されても、できるだけ同一の番号を付けるようにしていることに留意しなければならない。

また、本発明を説明するにあたり、係わる公知技術についての具体的な説明が本発明の要旨を不明瞭にする可能性があると判断される場合には、その詳細な説明は省略する。本明細書において、第1、第2などの用語は一つの構成要素を他の構成要素から区別するために用いられるものであり、構成要素が前記用語によって限定されるものではない。

【0022】

以下、添付図面を参照して本発明の実施例による半導体パッケージ基板及び半導体パッケージ基板の製造方法について詳細に説明する。

【0023】

半導体パッケージ基板の製造方法

図1から図9は本発明の一実施例による半導体パッケージ基板の製造方法を工程順に図示した工程断面図である。

【0024】

図1を参照すると、シード層120が形成されたキャリア基板110にパッド130が形成される。

キャリア基板110は、熱可塑性ポリマーまたは金属を利用して形成されることができる。キャリア基板110の材料としては、特に限定されるものではないが、熱可塑性ポリマーとしてはPVC(poly vinyl chloride)、PE(poly ethylene)、PP(ploy propylene)、PS(poly styrene)、ABS(acrylonitrile butadiene styrene copolymer)、Nylon(poly amide)またはPET(poly ethylene terephthalate)などを含むことができる。また、キャリア基板110を形成する金属としては、銅、アルミニウム、ニッケル、亜鉛、クロム、コバルト、タングステン及びこれらの混合物からなる群から選択することができる。

【0025】

シード層120はキャリア基板110上に形成される。ここで、シード層120はスパッタリングまたは無電解メッキ方式を利用して形成されることができる。

シード層120が形成されたキャリア基板110の上部にパッド130が形成される。

パッド130はキャリア基板110から突出された形態に形成されることができる。パッド130は、後でエッチングされることにより、絶縁層(図9の140)と半導体パッケージ基板に実装される半導体素子(図9の190)との間の十分な離隔空間のための開口部(図9の300)を形成するために利用される。キャリア基板110から突出されるパッド130の高さに応じて、絶縁層(図9の140)と半導体素子(図9の190)との離隔空間である開口部(図9の300)の深さが調節されることができる。

【0026】

パッド130は電解メッキ方法を利用してパターニングされ形成されることができる。本発明の実施例におけるパッド130は、シード層120と同一の材質で形成されることができる。

【0027】

図2を参照すると、パッド130が形成されたキャリア基板110に絶縁層140が形成される。

絶縁層140は、パッド130が形成されたキャリア基板110の上部に絶縁物質を積層した後、圧力を加えることにより、パッド130が絶縁層140に埋め込まれる形態に形成されることができる。ここで、絶縁層140は、絶縁素材として通常に用いられる複合高分子樹脂で形成されることができる。絶縁層140は、例えば、プリプレグ、または FR−4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

図3を参照すると、絶縁層140を形成した後、シード層120からキャリア基板(図2の110)が除去される。

【0028】

図4を参照すると、キャリア基板(図2の110)が除去された後、外部に露出されたシード層120に回路層(150)を形成するためのフォトレジスト160を形成する。この際、フォトレジスト160は露光及び現像を施すことにより形成されることができる。このようにフォトレジスト160を形成した後、回路層150を形成するためにメッキを行うことができる。この際、メッキは電解メッキ方法を利用して行われることができる。本発明の実施例では電解メッキ方法を利用しているが、メッキ方法はこれに限定されず、公知されたメッキ方法により行われることができる。また、メッキは、シード層120と同一の物質を用いて行われることができる。本発明の実施例によると、シード層120の厚さと回路層150の厚さを合わせて5〜25μmとなるように回路層150のメッキを行うことができる。しかし、このような回路層150の厚さは本発明の実施例に過ぎず、これに限定されない。

【0029】

図5を参考すると、シード層120上に形成されたフォトレジスト(図4の160)を除去することができる。

図6を参考すると、回路層150の上部にエッチングレジスト170が形成されることができる。ここで、エッチングレジスト170は、絶縁層140の内部に離隔空間が形成される領域が開口されるように形成されることができる。

【0030】

図7を参照すると、絶縁層140の内部に離隔空間を形成するために開口された領域をエッチングする。このようなエッチングにより、開口された領域に該当する絶縁層140の内部に埋め込まれたパッド130がエッチングされる。これにより、絶縁層140の内部に後で実装される半導体素子(図9の190)との離隔空間である開口部300が形成される。このように絶縁層140の内部に開口部300を形成した後、回路層150の上部に形成されたエッチングレジスト(図6の170)を除去する。

【0031】

図8を参照すると、回路層150の上部に形成されたエッチングレジスト(図6の170)が除去されることにより露出されたシード層120をエッチングする。

図9を参照すると、回路層150の上部及び開口部300の内壁に、半導体素子190とボンディングされる接合パッド180を形成する。接合パッド180は金メッキにより形成されることができる。このように形成された接合パッド180に半導体素子190を接合させることにより、半導体パッケージ基板に半導体素子190を実装することができる。

このような本発明の一実施例による半導体パッケージ基板の製造方法によりパッドの厚さと回路層の厚さを調節して、基板の厚さを増加させることなく基板と半導体素子との間の離隔空間が十分に形成されることができる。

【0032】

図10から図18は本発明の他の実施例による半導体パッケージ基板の製造方法を工程順に図示した工程断面図である。

図10を参照すると、第1のキャリア基板110、第1のシード層120、パッド130、絶縁層140、第2のキャリア基板111及び第2のシード層121が提供される。第1のキャリア基板110上の第1のシード層120にパッド130が形成され、第2のキャリア基板111上に第2のシード層121が形成される。

【0033】

図11を参照すると、パッド130が形成された第1のキャリア基板(図10の110)の上部に絶縁層140が積層され、絶縁層140の上部に第2のシード層121が形成された第2のキャリア基板(図10の111)が積層される。このように積層した後、絶縁層140及び第2のキャリア基板(図10の111)に圧力を加えることにより、絶縁層140の内部にパッド130が埋め込まれ、絶縁層140と第2のシード層121とが接合される形態になることができる。その後、第1のキャリア基板(図10の110)及び第2のキャリア基板(図10の111)を除去する。

図12を参照すると、第1のシード層120、第2のシード層121及び絶縁層140を貫通するビアホール191を加工する。ビアホール191は、レーザー加工またはルータ加工により加工されることができる。

【0034】

図13を参照すると、第1のシード層120及び第2のシード層121に、回路層(150、151)を形成するための第1のフォトレジスト160及び第2のフォトレジスト161を形成する。この際、第1のフォトレジスト160及び第2のフォトレジスト161は、露光及び現像を施すことにより形成されることができる。このように第1のフォトレジスト160を形成した後、上部回路層150を形成するためのメッキを行うことができる。また、第2のフォトレジスト161を形成した後、下部回路層151を形成するためのメッキを行うことができる。この際、ビアホール(図12の191)も、メッキにより内部が充填されることができる。ここで、メッキは、第1のシード層120及び第2のシード層121と同一の物質を用いて行われることができる。

【0035】

図14を参照すると、第1のフォトレジスト(図3の160)及び第2のフォトレジスト(図3の161)を除去する。

図15を参照すると、第1のフォトレジスト160及び第2のフォトレジスト161を除去した後、第1のエッチングレジスト170及び第2のエッチングレジスト171が形成されることができる。ここで、第1のエッチングレジスト170は、絶縁層140の内部に離隔空間が形成される領域が開口されるように形成されることができる。このような構造に第1のエッチングレジスト170を形成した後、開口された領域にエッチングを行うことができる。この際、第1のエッチングレジスト170により開口された領域に位置した絶縁層140がエッチングされることができる。また、エッチングされた絶縁層140の下部に位置したパッド130もエッチングされることができる。このようなエッチングにより、絶縁層140の内部に後程実装される半導体素子(図18の190)との離隔空間である開口部300が形成される。

【0036】

図16を参考すると、絶縁層140の内部に開口部300を形成した後、第1のエッチングレジスト(図15の170)及び第2のエッチングレジスト(図15の171)を除去する。

図17を参照すると、第1のエッチングレジスト(図15の170)及び第2のエッチングレジスト(図15の171)が除去されることにより露出された第1のシード層120及び第2のシード層121をエッチングすることにより、上部回路層150及び下部回路層151を形成する。

図18を参照すると、上部回路層150の上部及び開口部300の内壁に、半導体素子190とボンディングされる接合パッド180を形成する。接合パッド180は金メッキにより形成されることができる。このように形成された接合パッド180に半導体素子190を接合させた後、ソルダーレジスト192を塗布することにより、半導体パッケージ基板に半導体素子190を実装することができる。

【0037】

図19から図25は本発明のさらに他の実施例による半導体パッケージ基板の製造方法を工程順に図示した工程断面図である。

図19を参照すると、ベース絶縁層210が提供される。ここで、ベース絶縁層210はデュアルコアであり、両側面に夫々ビルドアップ層が形成されることができる。デュアルコアであるベース絶縁層210の一側に、第1のシード層215及び第1のパッド216が形成された第1のキャリア基板214が形成され、ベース絶縁層210の他側に第2のシード層212及び第2のパッド213が形成された第2のキャリア基板211が形成される。

【0038】

図20を参照すると、第1のシード層215及び第1のパッド216の上部に第1の絶縁層231が積層され、第2のシード層212及び第2のパッド213の上部に第2の絶縁層221が積層される。このように第1の絶縁層231及び第2の絶縁層221を積層した後、圧力を加えることにより、第1の絶縁層231の内部に第1のパッド216が埋め込まれ、第2の絶縁層221の内部に第2のパッド213が埋め込まれる形態になることができる。その後、第1の絶縁層231上には、第1の貫通孔237を含むようにパターニングされた第3のシード層232が形成される。また、第2の絶縁層221上には、第2の貫通孔227を含むようにパターニングされた第4のシード層222が形成される。

ここで、図面には図示されていないが、第3のシード層232及び第4のシード層222の上部には内部回路層が形成されることができる。または、第3のシード層232及び第4のシード層222がパターン化することにより、回路層の役割を遂行することもできる。

【0039】

図21を参照すると、第3のシード層232上に第3の絶縁層233を形成し、第4のシード層222上に第4の絶縁層223を積層する。この際、第3の絶縁層233及び第4の絶縁層223が夫々積層された後、圧力を加えることにより、第3の絶縁層233は第1の貫通孔(図20の237)を介して第1の絶縁層231と接合され、第4の絶縁層223は第2の貫通孔(図20の227)を介して第2の絶縁層221と接合される。このように第3の絶縁層233及び第4の絶縁層223を積層した後、第3の絶縁層233の上部に第5のシード層234が形成され、第4の絶縁層223の上部に第6のシード層224が形成される。ここで、第1のキャリア基板214に形成された第1のシード層215、第1の絶縁層231、第3のシード層232、第3の絶縁層233及び第5のシード層234を第1のビルドアップ層と称する。また、第2のキャリア基板211に形成された第2のシード層212、第2の絶縁層221、第4のシード層222、第4の絶縁層223及び第6のシード層224を第2のビルドアップ層と称する。

【0040】

図22を参照すると、第1のキャリア基板(図21の214)及び第2のキャリア基板(図21の211)を夫々ベース絶縁層(図21の210)から分離する。また、第1のキャリア基板(図21の214)及び第2のキャリア基板(図21の211)を夫々ベース絶縁層(図21の210)から分離した後、第1のキャリア基板(図21の214)及び第2のキャリア基板(図21の211)を除去する。

その後、第1のビルドアップ層200を貫通する第1のビアホール191が形成される。図面に図示されていないが、第2のビルドアップ層にも第2のビアホールが形成される。

【0041】

図23を参照すると、第1のシード層215及び第5のシード層234上に、第1の回路層である上部回路層236及び下部回路層235をメッキにより形成することができる。即ち、第1のシード層215上に上部回路層236をメッキにより形成し、第5のシード層234上に下部回路層235をメッキにより形成することができる。この際、第1のビアホール191も、メッキによりその内部が充電されることができる。その後、第1の絶縁層231に埋め込まれている第1のパッド216をエッチングすることにより、開口部300を形成する。

【0042】

図24を参照すると、メッキ後に露出された第1のシード層215及び第5のシード層234を除去することにより、上部回路層236及び下部回路層235を形成する。

図25を参照すると、上部回路層236の上部及び開口部300の内壁に、半導体素子250とボンディングされる接合パッド240を形成する。接合パッド240は金メッキにより形成されることができる。このように形成された接合パッド240に半導体素子250を接合させた後、ソルダーレジスト270を塗布することにより、半導体パッケージ基板に半導体素子250を実装することができる。

ここで、第1のビルドアップ層200を例にとり説明したが、第2のビルドアップ層も同一の工程順序に従って半導体素子が実装されることができる。

【0043】

半導体パッケージ基板

図26は本発明の実施例による半導体パッケージ基板を示した例示図である。

図26を参照すると、本発明の実施例による半導体パッケージ基板400は、絶縁層440と、パッド430と、シード層420と、回路層450と、及び接合パッド480と、を含むことができる。

【0044】

絶縁層440は、絶縁素材として通常用いられる複合高分子樹脂で形成されることができる。絶縁層440は、例えば、プリプレグ、またはFR−4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

【0045】

パッド430は絶縁層の内部に埋め込まれ、第1の開口部401を有することができる。パッド430に形成された第1の開口部401の深さはパッド430の厚さによって変わることができる。例えば、第1の開口部401の深さは、パッド430の厚さと同一であるか、またはパッド430の厚さより小さいことができる。しかし、第1の開口部401の深さはこれに限定されず、当業者によって変更されることができる。

シード層420は、絶縁層440及びパッド430の上部に形成されることができる。この際、シード層420は第1開口部401が露出されるようにパターニングされることができる。

【0046】

回路層450は、絶縁層440及びパッド430の上部に形成されることができる。即ち、回路層450は、絶縁層440及びパッド430の上部に形成されたシード層420上に形成されることができる。また、回路層450は、第1開口部401上に位置するように形成された第2の開口部402を有するように形成されることができる。

接合パッド480は、回路層450の上部、第1の開口部401の内壁及び第2の開口部402の内壁に形成されることができる。接合パッド480は金メッキにより形成されることができる。このように形成された接合パッド480には半導体素子490が実装されることができる。

【0047】

図面には図示されていないが、半導体素子490が実装された後、絶縁層440及び回路層450の上部にソルダーレジストが塗布されることができる。

【0048】

図27は本発明の他の実施例による半導体パッケージ基板を示した例示図である。

図27を参照すると、本発明の実施例による半導体パッケージ基板500は、絶縁層540と、パッド530と、第1のシード層520と、上部回路層550と、接合パッド580と、第2のシード層521と、下部回路層551と、ビア552と、ソルダーレジスト592と、を含むことができる。

【0049】

絶縁層540は、絶縁素材として通常用いられる複合高分子樹脂で形成されることができる。絶縁層540は、例えば、プリプレグ、またはFR-4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

パッド530は絶縁層540の内部に埋め込まれ、第1の開口部501を有することができる。パッド530に形成された第1の開口部501の深さはパッド530の厚さによって変わることができる。例えば、第1の開口部501の深さは、パッド530の厚さと同一であるか、またはパッド530の厚さより小さいことができる。しかし、第1の開口部501の深さはこれに限定されず、当業者によって変更されることができる。

【0050】

第1のシード層520は、絶縁層540及びパッド530の上部に形成されることができる。この際、第1のシード層520は第1の開口部501が露出されるようにパターニングされることができる。

上部回路層550は、絶縁層540及びパッド530の上部に形成されることができる。即ち、上部回路層550は、絶縁層540及びパッド530の上部に形成された第1のシード層520上に形成されることができる。また、上部回路層550は、第1の開口部501上に位置するように形成された第2の開口部502を有するように形成されることができる。

【0051】

接合パッド580は、上部回路層550、第1の開口部501及び第2の開口部502上に形成されることができる。接合パッド580は金メッキにより形成されることができる。このように形成された接合パッド580には半導体素子590が実装されることができる。

第2のシード層521は絶縁層540の下部に形成されることができ、第2のシード層521は所定の形態にパターニングされるように形成されることができる。

【0052】

下部回路層551は絶縁層540の下部に形成されることができる。即ち、下部回路層551は、絶縁層540の下部に形成された第2のシード層521の下部に形成されることができる。

本発明の実施例によると、上部回路層550と下部回路層551とはビア552により連結されることができる。即ち、絶縁層540を貫通するように形成されたビア552により、上部回路層550と下部回路層551とが電気的に連結されるように形成されることができる。

ソルダーレジスト592は第1の絶縁層540の上部及び下部に形成されることができる。

【0053】

図28は本発明のさらに他の実施例による半導体パッケージ基板を示した例示図である。

図28を参照すると、本発明の実施例による半導体パッケージ基板600は、上部絶縁層631と、下部絶縁層633と、シード層632と、上部回路層636と、下部回路層635と、パッド616と、接合パッド640と、ビア637と、ソルダーレジスト670と、を含むことができる。

下部絶縁層633は、絶縁素材として通常用いられる複合高分子樹脂で形成されることができる。下部絶縁層633は、例えば、プリプレグ、またはFR-4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

シード層632は下部絶縁層633の上部に形成されることができる。シード層632は、下部絶縁層633の上部にパターン化されて形成されることができる。図28には図示されていないが、シード層632の上部には内部回路層が形成されることができる。または、シード層632がパターン化されることにより、回路層の役割を遂行することもできる。

【0054】

上部絶縁層631はシード層632上に形成されることができる。上部絶縁層631は、絶縁素材として通常用いられる複合高分子樹脂で形成されることができる。上部絶縁層631は、例えば、プリプレグ、またはFR-4、BT(Bismaleimide Triazine)、ABF(Ajinomoto Build up Film)などのエポキシ系樹脂を用いることができる。

本発明の実施例よると、上部絶縁層631は、シード層632を埋め込む形態に形成されることができる。例えば、シード層632上に内部回路層(不図示)が形成された場合、上部絶縁層631は、シード層632及び内部回路層(不図示)を全て埋め込む形態に形成されることができる。

【0055】

パッド616は上部絶縁層631の内部に埋め込まれ、第1の開口部601を有することができる。パッド616に形成された第1の開口部601の深さはパッド616の厚さによって変わることができる。例えば、第1の開口部601の深さは、パッド616の厚さと同一であるか、またはパッド616の厚さより小さいことができる。

上部回路層636は、上部絶縁層631及びパッド616の上部に形成されることができる。上部回路層636は、第1の開口部601上に位置するように形成された第2の開口部602を有するように形成されることができる。ここで、上部回路層636は、上部絶縁層631及びパッド616上に形成された上部シード層615上に形成されるということは、当業者において自明である。

【0056】

接合パッド640は、上部回路層636の上部、第1の開口部601の内壁及び第2の開口部602の内壁に形成されることができる。接合パッド640は金メッキにより形成されることができる。このように形成された接合パッド640には半導体素子650が実装されることができる。

下部回路層635は下部絶縁層633の下部に形成されることができる。下部回路層635は、下部絶縁層633の下部に形成された下部シード層634上に形成されるということは、当業者において自明である。

【0057】

ビア637は、上部絶縁層631及び下部絶縁層633を貫通するように形成されることができる。このように上部絶縁層631及び下部絶縁層633を貫通するように形成されたビア637により、上部回路層636と下部回路層635とが電気的に連結されるように形成されることができる。

ソルダーレジスト670は、上部絶縁層631及び下部絶縁層633に形成されることができる。図28には、ソルダーレジスト670が、上部絶縁層631に形成された上部回路層636及び下部絶縁層633に形成された下部回路層635が埋め込まれるように形成されることで図示されているが、これに限定されない。即ち、ソルダーレジスト670が形成される程度は当業者によって容易に変更されることができる。

【0058】

以上、本発明を実施例に基づいて詳細に説明したが、これは本発明を具体的に説明するためのものであり、本発明による半導体パッケージ基板及び半導体パッケージ基板の製造方法はこれに限定されず、該当技術分野において通常の知識を有する者であれば、添付の特許請求範囲に記載された本発明の思想及び領域を外れない範囲内で多様な修正及び変形が可能であることを理解するであろう。

このような本発明の単純な変形乃至変更はいずれも本発明の領域に属するものであり、本発明の具体的な保護範囲は添付の特許請求の範囲により明確になるであろう

【図面の簡単な説明】

【0059】

【図1】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図2】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図3】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図4】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図5】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図6】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図7】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図8】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図9】本発明の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図10】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図11】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図12】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図13】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図14】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図15】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図16】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図17】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図18】本発明の他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図19】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図20】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図21】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図22】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図23】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図24】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図25】本発明のさらに他の実施例による半導体パッケージ基板の製造方法の工程順序を説明するための例示図である。

【図26】本発明の実施例による半導体パッケージ基板を示した例示図である。

【図27】本発明の他の実施例による半導体パッケージ基板を示した例示図である。

【図28】本発明のさらに他の実施例による半導体パッケージ基板を示した例示図である。

【符号の説明】

【0060】

110、111、211、214 キャリア基板

120、121、212、215、222、224、232、420、632 シード層

130、213、216、430、530、616 パッド

140、221、223、231、223、233、440、540 絶縁層

150、236、450、550、636 上部回路層

151、235、551、635 下部回路層

160、161 フォトレジスト

170、171 エッチングレジスト

180、240、480、580、640 接合パッド

190、250、490、590、650 半導体素子

191 ビアホール

192、592、670 ソルダーレジスト

200、260 ビルドアップ層

210 ベース絶縁層

227 第2の貫通孔

237 第1の貫通孔

300 開口部

400、500、600 半導体パッケージ基板

401、501、601 第1の開口部

402、502、602 第2の開口部

520 第1のシード層

552、637 ビア

615 上部シード層

631 上部絶縁層

633 下部絶縁層

634 下部シード層

【特許請求の範囲】

【請求項1】

パッドが形成されたキャリア基板を準備する段階と、

前記パッドの上部に絶縁層を形成する段階と、

前記キャリア基板を除去する段階と、

前記絶縁層及び前記パッドの上部に回路層を形成する段階と、

前記パッドの一部をエッチングし、前記絶縁層の内部に開口部を形成する段階と、を含む半導体パッケージ基板の製造方法。

【請求項2】

前記絶縁層を形成する段階で、前記パッドは前記絶縁層に埋め込まれることを特徴とする請求項1に記載の半導体パッケージ基板の製造方法。

【請求項3】

前記キャリア基板を除去する段階の後、

前記絶縁層を貫通するビアホールを形成する段階をさらに含むことを特徴とする請求項1に記載の半導体パッケージ基板の製造方法。

【請求項4】

前記回路層を形成する段階で、前記ビアホールの内部がメッキされることを特徴とする請求項3に記載の半導体パッケージ基板の製造方法。

【請求項5】

前記開口部を形成する段階は、

前記パッド一部の上部が開口されるように、前記 回路層の上部にエッチングレジストを塗布する段階と、

前記パッドをエッチングする段階と、

前記エッチングレジストを除去する段階と、を含むことを特徴とする請求項1に記載の半導体パッケージ基板の製造方法。

【請求項6】

前記開口部を形成する段階の後、

前記回路層の上部及び開口部の内壁に接合パッドを形成する段階と、

前記接合パッドの上部に前記半導体素子を実装する段階と、をさらに含むことを特徴とする請求項1に記載の半導体パッケージ基板の製造方法。

【請求項7】

ベース絶縁層を準備する段階と、

前記ベース絶縁層の一側に、第1のキャリア基板、第1のシード層、第1のパッド、前記第1のパッドが埋め込まれる第1の絶縁層、第3のシード層、第3の絶縁層及び第5のシード層が積層され形成された第1のビルドアップ層を形成し、前記ベース絶縁層の他側に、第2のキャリア基板、第2のシード層、第2のパッド、前記第2のパッドが埋め込まれる第2の絶縁層、第4のシード層、第4の絶縁層及び第6のシード層が積層され形成された第2のビルドアップ層を形成する段階と、

前記第1のキャリア基板及び第2のキャリア基板を前記ベース絶縁層から分離する段階と、

前記第1のビルドアップ層から前記第1のキャリア基板を除去し、前記第2のビルドアップ層から前記第2のキャリア基板を除去する段階と、

前記第1のキャリア基板が除去された前記第1のビルドアップ層上に第1の回路層を形成し、前記第2のキャリア基板が除去された前記第2のビルドアップ層上に第2の回路層を形成する段階と、

前記第1のパッドの一部をエッチングして前記第1の絶縁層の一部に第1の開口部を形成し、前記第2のパッドの一部をエッチングして前記第2の絶縁層の一部に第2の開口部を形成する段階と、を含むことを特徴とする半導体パッケージ基板の製造方法。

【請求項8】

前記第1の絶縁層及び前記第2の絶縁層を形成する段階で、前記第1のパッドは前記第1の絶縁層に埋め込まれることを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項9】

前記第1の絶縁層及び前記第2の絶縁層を形成する段階で、前記第2のパッドは前記第2の絶縁層に埋め込まれることを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項10】

前記第1のキャリア基板及び前記第2のキャリア基板を前記ベース絶縁層から分離する段階の後、

前記第1のビルドアップ層を貫通する第1のビアホールを形成する段階をさらに含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項11】

前記第1の回路層を形成する段階で、前記第1のビアホールの内部がメッキされることを特徴とする請求項10に記載の半導体パッケージ基板の製造方法。

【請求項12】

前記第1の回路層を形成する段階で、前記第1の回路層は、前記第1のシード層上に形成される上部回路層及び前記第5のシード層上に形成される下部回路層を含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項13】

前記第1のキャリア基板及び前記第2のキャリア基板を前記ベース絶縁層から分離する段階の後、

前記第2のビルドアップ層を貫通する第2のビアホールを形成する段階をさらに含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項14】

前記第2の回路層を形成する段階で、前記第2のビアホールの内部がメッキされることを特徴とする請求項13に記載の半導体パッケージ基板の製造方法。

【請求項15】

前記第2の回路層を形成する段階で、前記第2の回路層は、前記第2のシード層上に形成される上部回路層及び前記第6のシード層上に形成される下部回路層を含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項16】

前記第1の開口部を形成する段階は、

前記第1のパッド一部の上部が開口されるように、前記第1の回路層の上部にエッチングレジストを塗布する段階と、

前記第1のパッドをエッチングする段階と、

前記エッチングレジストを除去する段階と、を含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項17】

前記第2の開口部を形成する段階は、

前記第2のパッド一部の上部が開口されるように、前記第2の回路層の上部にエッチングレジストを塗布する段階と、

前記第2のパッドをエッチングする段階と、

前記エッチングレジストを除去する段階と、を含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項18】

絶縁層と、

前記絶縁層の内部に埋め込まれ、第1の開口部を有するパッドと、

前記絶縁層及び前記パッドの上部に形成され、前記第1の開口部上に形成された第2の開口部を有する上部回路層と、を含むことを特徴とする半導体パッケージ基板。

【請求項19】

前記絶縁層の下部に形成される下部回路層をさらに含むことを特徴とする請求項18に記載の半導体パッケージ基板。

【請求項20】

前記絶縁層を貫通するように形成され、前記上部回路層及び前記下部回路層を電気的に連結するビアをさらに含むことを特徴とする請求項19に記載の半導体パッケージ基板。

【請求項21】

前記上部回路層の上部には半導体素子が実装されることを特徴とする請求項18に記載の半導体パッケージ基板。

【請求項22】

下部絶縁層と、

前記下部絶縁層の上部に形成され、貫通孔を含むようにパターン化されたシード層と、

前記シード層の上部に形成され、前記シード層が埋め込まれるように形成される上部絶縁層と、

前記上部絶縁層の内部に埋め込まれ、第1の開口部が形成されたパッドと、

前記上部絶縁層及び前記パッドの上部に形成され、前記第1の開口部上に形成された第2の開口部を有する上部回路層と、

前記下部絶縁層の下部に形成された下部回路層と、

を含む半導体パッケージ基板。

【請求項23】

前記上部絶縁層、前記下部絶縁層及び前記シード層を貫通するように形成され、前記上部回路層と前記下部回路層とを電気的に連結するビアをさらに含むことを特徴とする請求項22に記載の半導体パッケージ基板。

【請求項24】

前記上部回路層の上部に半導体素子が実装されることを特徴とする請求項22に記載の半導体パッケージ基板。

【請求項1】

パッドが形成されたキャリア基板を準備する段階と、

前記パッドの上部に絶縁層を形成する段階と、

前記キャリア基板を除去する段階と、

前記絶縁層及び前記パッドの上部に回路層を形成する段階と、

前記パッドの一部をエッチングし、前記絶縁層の内部に開口部を形成する段階と、を含む半導体パッケージ基板の製造方法。

【請求項2】

前記絶縁層を形成する段階で、前記パッドは前記絶縁層に埋め込まれることを特徴とする請求項1に記載の半導体パッケージ基板の製造方法。

【請求項3】

前記キャリア基板を除去する段階の後、

前記絶縁層を貫通するビアホールを形成する段階をさらに含むことを特徴とする請求項1に記載の半導体パッケージ基板の製造方法。

【請求項4】

前記回路層を形成する段階で、前記ビアホールの内部がメッキされることを特徴とする請求項3に記載の半導体パッケージ基板の製造方法。

【請求項5】

前記開口部を形成する段階は、

前記パッド一部の上部が開口されるように、前記 回路層の上部にエッチングレジストを塗布する段階と、

前記パッドをエッチングする段階と、

前記エッチングレジストを除去する段階と、を含むことを特徴とする請求項1に記載の半導体パッケージ基板の製造方法。

【請求項6】

前記開口部を形成する段階の後、

前記回路層の上部及び開口部の内壁に接合パッドを形成する段階と、

前記接合パッドの上部に前記半導体素子を実装する段階と、をさらに含むことを特徴とする請求項1に記載の半導体パッケージ基板の製造方法。

【請求項7】

ベース絶縁層を準備する段階と、

前記ベース絶縁層の一側に、第1のキャリア基板、第1のシード層、第1のパッド、前記第1のパッドが埋め込まれる第1の絶縁層、第3のシード層、第3の絶縁層及び第5のシード層が積層され形成された第1のビルドアップ層を形成し、前記ベース絶縁層の他側に、第2のキャリア基板、第2のシード層、第2のパッド、前記第2のパッドが埋め込まれる第2の絶縁層、第4のシード層、第4の絶縁層及び第6のシード層が積層され形成された第2のビルドアップ層を形成する段階と、

前記第1のキャリア基板及び第2のキャリア基板を前記ベース絶縁層から分離する段階と、

前記第1のビルドアップ層から前記第1のキャリア基板を除去し、前記第2のビルドアップ層から前記第2のキャリア基板を除去する段階と、

前記第1のキャリア基板が除去された前記第1のビルドアップ層上に第1の回路層を形成し、前記第2のキャリア基板が除去された前記第2のビルドアップ層上に第2の回路層を形成する段階と、

前記第1のパッドの一部をエッチングして前記第1の絶縁層の一部に第1の開口部を形成し、前記第2のパッドの一部をエッチングして前記第2の絶縁層の一部に第2の開口部を形成する段階と、を含むことを特徴とする半導体パッケージ基板の製造方法。

【請求項8】

前記第1の絶縁層及び前記第2の絶縁層を形成する段階で、前記第1のパッドは前記第1の絶縁層に埋め込まれることを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項9】

前記第1の絶縁層及び前記第2の絶縁層を形成する段階で、前記第2のパッドは前記第2の絶縁層に埋め込まれることを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項10】

前記第1のキャリア基板及び前記第2のキャリア基板を前記ベース絶縁層から分離する段階の後、

前記第1のビルドアップ層を貫通する第1のビアホールを形成する段階をさらに含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項11】

前記第1の回路層を形成する段階で、前記第1のビアホールの内部がメッキされることを特徴とする請求項10に記載の半導体パッケージ基板の製造方法。

【請求項12】

前記第1の回路層を形成する段階で、前記第1の回路層は、前記第1のシード層上に形成される上部回路層及び前記第5のシード層上に形成される下部回路層を含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項13】

前記第1のキャリア基板及び前記第2のキャリア基板を前記ベース絶縁層から分離する段階の後、

前記第2のビルドアップ層を貫通する第2のビアホールを形成する段階をさらに含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項14】

前記第2の回路層を形成する段階で、前記第2のビアホールの内部がメッキされることを特徴とする請求項13に記載の半導体パッケージ基板の製造方法。

【請求項15】

前記第2の回路層を形成する段階で、前記第2の回路層は、前記第2のシード層上に形成される上部回路層及び前記第6のシード層上に形成される下部回路層を含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項16】

前記第1の開口部を形成する段階は、

前記第1のパッド一部の上部が開口されるように、前記第1の回路層の上部にエッチングレジストを塗布する段階と、

前記第1のパッドをエッチングする段階と、

前記エッチングレジストを除去する段階と、を含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項17】

前記第2の開口部を形成する段階は、

前記第2のパッド一部の上部が開口されるように、前記第2の回路層の上部にエッチングレジストを塗布する段階と、

前記第2のパッドをエッチングする段階と、

前記エッチングレジストを除去する段階と、を含むことを特徴とする請求項7に記載の半導体パッケージ基板の製造方法。

【請求項18】

絶縁層と、

前記絶縁層の内部に埋め込まれ、第1の開口部を有するパッドと、

前記絶縁層及び前記パッドの上部に形成され、前記第1の開口部上に形成された第2の開口部を有する上部回路層と、を含むことを特徴とする半導体パッケージ基板。

【請求項19】

前記絶縁層の下部に形成される下部回路層をさらに含むことを特徴とする請求項18に記載の半導体パッケージ基板。

【請求項20】

前記絶縁層を貫通するように形成され、前記上部回路層及び前記下部回路層を電気的に連結するビアをさらに含むことを特徴とする請求項19に記載の半導体パッケージ基板。

【請求項21】

前記上部回路層の上部には半導体素子が実装されることを特徴とする請求項18に記載の半導体パッケージ基板。

【請求項22】

下部絶縁層と、

前記下部絶縁層の上部に形成され、貫通孔を含むようにパターン化されたシード層と、

前記シード層の上部に形成され、前記シード層が埋め込まれるように形成される上部絶縁層と、

前記上部絶縁層の内部に埋め込まれ、第1の開口部が形成されたパッドと、

前記上部絶縁層及び前記パッドの上部に形成され、前記第1の開口部上に形成された第2の開口部を有する上部回路層と、

前記下部絶縁層の下部に形成された下部回路層と、

を含む半導体パッケージ基板。

【請求項23】

前記上部絶縁層、前記下部絶縁層及び前記シード層を貫通するように形成され、前記上部回路層と前記下部回路層とを電気的に連結するビアをさらに含むことを特徴とする請求項22に記載の半導体パッケージ基板。

【請求項24】

前記上部回路層の上部に半導体素子が実装されることを特徴とする請求項22に記載の半導体パッケージ基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【公開番号】特開2013−46054(P2013−46054A)

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願番号】特願2012−118390(P2012−118390)

【出願日】平成24年5月24日(2012.5.24)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

【公開日】平成25年3月4日(2013.3.4)

【国際特許分類】

【出願日】平成24年5月24日(2012.5.24)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

[ Back to top ]