半導体パッケージ製造装置及び半導体パッケージの製造方法

【課題】半導体パッケージの製造プロセスにおける静電破壊を防止することが必要とされている。

【解決手段】半導体パッケージ製造装置は、半導体チップを搭載した基板50を吸引固定する金型20と、金型10とを具備する。基板50は、半導体チップの内部回路と導通する導通部分を備える。金型20は、電気的に接地された導電性端子31を備える。金型10及び金型20に基板50が挟まれた状態で、半導体チップを封入するモールド樹脂70が金型10により成型される。金型10及び金型20を相対的に遠ざけてモールド樹脂70を金型10から離型する間、導電性端子31は基板50の導通部分に接触し続ける。

【解決手段】半導体パッケージ製造装置は、半導体チップを搭載した基板50を吸引固定する金型20と、金型10とを具備する。基板50は、半導体チップの内部回路と導通する導通部分を備える。金型20は、電気的に接地された導電性端子31を備える。金型10及び金型20に基板50が挟まれた状態で、半導体チップを封入するモールド樹脂70が金型10により成型される。金型10及び金型20を相対的に遠ざけてモールド樹脂70を金型10から離型する間、導電性端子31は基板50の導通部分に接触し続ける。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体パッケージに関する。

【背景技術】

【0002】

半導体パッケージの製造プロセスにおいて、半導体チップが基板に搭載され、半導体チップがモールド樹脂で封入される。モールド樹脂を成型する金型からモールド樹脂が容易に離型されるように、モールド樹脂と金型との間にリリースフィルムが配置される。リリースフィルムをモールド樹脂から剥がすとき、又は金型からリリースフィルムを剥がすときの剥離帯電に起因して半導体チップが静電破壊される場合がある。

【0003】

特開2007−287944号公報、特開2000−243871号公報、特開2000−133666号公報、特開平11−312698号公報は、静電破壊を防止するための技術を開示している。

【0004】

例えば、特開2007−287944号公報に記載された半導体製造装置は、半導体チップを上側に搭載した基板を下側から支持する下部金型と、可撓性フィルムを介して半導体チップに供給された樹脂を成型する上部金型とを備える。下部金型は、電気的絶縁領域を含み、電気的絶縁領域を介して基板を支持する。下部金型が電気的絶縁領域を介して基板を支持するため、可撓性フィルムに帯電した電荷が基板を通じて下部金型へ導通するのが阻止され、基板上の半導体チップの静電破壊が抑制される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007‐287944号公報

【特許文献2】特開2000−243871号公報

【特許文献3】特開2000−133666号公報

【特許文献4】特開平11−312698号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特開2007−287944号公報によれば、モールド樹脂を成形するプロセスでの半導体チップの静電破壊の抑制には効果があるが、成形後の基板は帯電したままの状態のため、金型から成形済みの基板を取り出す際のハンドリングなどにおいて放電が起こり、半導体チップが破壊される恐れがある。このため、半導体パッケージの製造プロセスにおける静電破壊を防止することが必要とされている。

【課題を解決するための手段】

【0007】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0008】

半導体パッケージ製造装置は、半導体チップ(60)を搭載した基板(50)を吸引固定する第1金型(20、210)と、第2金型(10、220)とを具備する。前記基板は、前記半導体チップの内部回路(61)と導通する導通部分(52a、54a)を備える。前記第1金型又は前記第2金型は、電気的に接地された導電性端子(31、32、33)を備える。前記第1金型及び前記第2金型に前記基板が挟まれた状態で、前記半導体チップを封入するモールド樹脂(70)が前記第2金型により成型される。前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型する間、前記導電性端子は前記導通部分に接触し続ける。

【0009】

半導体パッケージの製造方法は、半導体チップ(60)を搭載した基板(50)を第1金型(20、210)に吸引固定することと、前記第1金型及び第2金型(10、220)の間に前記基板を挟むことと、前記半導体チップを封入するモールド樹脂(70)を前記第2金型により成型することと、前記半導体チップの内部回路(61)が電気的に接地した状態を維持しながら前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型することとを具備する。前記基板は、前記内部回路と導通する導通部分(52a、54a)を備える。前記第1金型又は前記第2金型は、電気的に接地された導電性端子(31、32、33)を備える。前記導電性端子が前記導通部分に接触することで前記内部回路が電気的に接地する。

【発明の効果】

【0010】

本発明によれば、半導体パッケージの製造プロセスにおける静電破壊が防止される。

【図面の簡単な説明】

【0011】

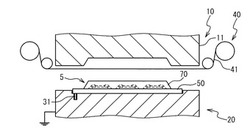

【図1】図1は、本発明の第1の実施形態に係る半導体パッケージ製造装置の断面図である。

【図2】図2は、半導体チップ組立体の側面図である。

【図3】図3は、半導体チップ組立体の下面図である。

【図4】図4は、半導体チップ組立体の断面図である。

【図5】図5は、半導体パッケージ製造装置の下金型に半導体チップ組立体を固定した状態を示す断面図である。

【図6】図6は、半導体チップ組立体の基板を半導体パッケージ製造装置の上金型と下金型とで挟んだ状態を示す断面図である。

【図7】図7は、半導体チップ組立体の半導体チップをモールド樹脂で封入した状態を示す断面図である。

【図8】図8は、モールド樹脂が上金型から離型された状態を示す断面図である。

【図9】図9は、本発明の比較例に係る半導体パッケージ製造装置の下金型に半導体チップ組立体を固定した状態を示す断面図である。

【図10】図10は、本発明の第2の実施形態に係る下金型に半導体チップ組立体を固定した状態を示す断面図である。

【図11】図11は、本発明の第3の実施形態に係る上金型と半導体チップ組立体との電気的接続状態を示す断面図である。

【図12】図12は、第1乃至第3の実施形態の変形例に係る半導体パッケージ製造装置の断面図である。

【発明を実施するための形態】

【0012】

添付図面を参照して、本発明による半導体パッケージ製造装置及び半導体パッケージの製造方法を実施するための形態を以下に説明する。

【0013】

(第1の実施形態)

図1を参照して、本発明の第1の実施形態に係る半導体パッケージ製造装置1を説明する。半導体パッケージ製造装置1は、上金型10と、下金型20と、リリースフィルム支持装置40を備える。上金型10は、上金型本体11を備える。上金型本体11は、下金型20の方向を向く平面11aを備える。上金型本体11に、平面11aに開口する凹部11bが形成されている。凹部11bは、キャビティを形成する。下金型20は、下金型本体21と、導電性端子31を備える。下金型本体21は、上金型10の方向を向く平面21aと、平面21aから上金型10に向かって突き出た位置決めピン22を備える。下金型本体21に、平面21aに開口する導電性端子配置穴21bと、平面21aに開口する排気通路21cとが形成されている。排気通路21cは、図示されない真空ポンプに接続されている。導電性端子31は、平面21aから上金型10に向かって突き出すように導電性端子配置穴21bに配置され、下金型本体21に脱着可能に固定され、下金型本体21を介して電気的に接地されている。リリースフィルム支持装置40は、リリースフィルム41を凹部11bと平面21aとの間に支持する。後述するモールド樹脂の成型時において、リリースフィルム41は、図1に二点鎖線で示されるように、上金型10に吸着されて平面11a及び凹部11bに密着する。

【0014】

図2は、半導体パッケージ製造装置1によって処理される半導体チップ組立体5を示す。半導体チップ組立体5は、多層配線基板のような基板50と、基板50に搭載された複数の半導体チップ60を備える。半導体チップ60は、例えば、半導体ウエハを個片化することで提供される。複数の半導体チップ60は、基板50の搭載側50aに搭載される。基板50の非搭載側50bは、搭載側50aの反対側である。各半導体チップ60は、内部回路61を備える。内部回路61は、ワイヤー62を介して基板50に接続される。

【0015】

図2において半導体チップ60の上に別の半導体チップが搭載されているが、この別の半導体チップは無くてもよい。また、半導体チップ60は基板50にフリップチップマウントされてもよい。半導体チップ60が基板50にフリップチップマウントされる場合、内部回路61はワイヤー62を介さずに例えばはんだバンプなどを介して基板50に接続される。

【0016】

図3は、基板50の非搭載側50bを示している。基板50は、複数の半導体チップ60が搭載される搭載部分50xと、基板50の縁に位置する縁部分50yとを備える。縁部分50yは、搭載部分50xの周囲を囲んでいる。基板50は、非搭載側50bに表面保護層55を備える。表面保護層55に溝50dが形成されている。溝50dは、搭載部分50xと縁部分50yの間の境界に沿って形成されている。縁部分50yには、基板50を貫通するように位置決め孔50cが形成されている。縁部分50yは、非搭載側50bに露出した導通部分54aを含む。

【0017】

図4は、基板50の断面図を示す。基板50は、表面保護層53と、導電層52と、中間絶縁層51と、導電層54と、表面保護層55を備える。表面保護層53と、導電層52と、中間絶縁層51と、導電層54と、表面保護層55は、搭載側50aから非搭載側50bに向かって順番に配置される。導電層52及び54は、例えば銅のような金属により形成される。表面保護層53及び55は、ソルダーレジストのような絶縁層である。導電層52及び54の各々は、複数の半導体チップ60のそれぞれの内部回路61とワイヤー(62)を介して導通している。例えば、導電層52及び54の各々は、複数の半導体チップ60のそれぞれのグランド配線と導通している。導電層52は表面保護層53によって部分的に覆われており、導電層52の一部としての導通部分52aは表面保護層53に覆われずに搭載側50aに露出している。導通部分52aは縁部分50yに含まれる。導電層54は表面保護層55によって部分的に覆われており、導電層54の一部としての導通部分54aは表面保護層55に覆われずに非搭載側50bに露出している。導通部分54aは縁部分50yに含まれる。ここで、導通部分52a及び54aの表面に金メッキ層が形成されていることが好ましい。このようにすることで、後述する導通部分52a及び54aの接地が確実になる。なお、中間絶縁層51は、一又は複数の導電層を含んでもよい。

【0018】

以下、図5乃至図8を用いて本実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法を説明する。

【0019】

図5を参照して、位置決めピン22が位置決め孔50cに配置されるように、非搭載側50bが平面21aと向かい合う姿勢で半導体チップ組立体5を下金型本体21に載せる。このとき、排気通路21cは溝50dに接続され、導通部分54aは導電性端子31と向かい合う。

【0020】

図示されない真空ポンプが排気通路21cを介して溝50dから空気を排気することで、下金型20は基板50を吸引固定する。このとき、平面21aが表面保護層55に密着し、導電性端子31は平面21aから突き出た状態(導電性端子配置穴21bから突き出た状態)で導通部分54aに接触する。導電性端子31が平面21a(導電性端子配置穴21b)から突き出ているため、半導体チップ60の内部回路61が確実に電気的に接地される。ここで、導電性端子31の平面21a(導電性端子配置穴21b)から突き出ている部分の高さは、内部回路61の接地を確保し、且つ、基板50を破壊しないために、表面保護層55の厚さより僅かに大きいことが好ましい。

【0021】

図6を参照して、上金型10と下金型20とを相対的に近づけて、上金型10及び下金型20で基板50を挟む。このとき、複数の半導体チップ60が凹部11bに配置され、平面11a及び凹部11bがリリースフィルム41に密着し、リリースフィルム41が表面保護層53に密着し、平面21aが表面保護層55に密着する。

【0022】

図7を参照して、上金型10及び下金型20に基板50が挟まれた状態で、凹部11bに樹脂材料を注入して複数の半導体チップ60を封入するモールド樹脂70を形成する。モールド樹脂70は、上金型本体11により、凹部11bの形状に対応する形状に成型される。ここで、リリースフィルム41はモールド樹脂70と凹部11bの間に配置される。

【0023】

図8を参照して、上金型10及び下金型20を相対的に遠ざけてモールド樹脂70を上金型本体11から離型する。このとき、リリースフィルム41がモールド樹脂70と上金型本体11とから剥がれる。モールド樹脂70を離型する間、導電性端子31は導通部分54aに接触し続け、半導体チップ60の内部回路61が電気的に接地した状態が維持される。

【0024】

したがって、リリースフィルム41がモールド樹脂70から剥がれるとき、又はリリースフィルム41が上金型本体11から剥がれるときの剥離帯電による電荷が下金型本体21を介してグランドに逃がされるため、内部回路61が静電破壊されることが防止される。

【0025】

更に、下金型20による基板50の吸引固定を解除してモールド樹脂70が形成された半導体チップ組立体5を下金型20から取り外した後、縁部分55yを搭載部分55xから切り離す。つまり、縁部分50yは製品に含まれない。したがって、導電性端子31が導通部分54aに強く押し付けられたために縁部分50yに損傷が発生しても、内部回路61の電気的接地が確保されれば問題ない。

【0026】

導電性端子31が下金型本体21に脱着可能に固定されるため、導電性端子31の交換が容易である。したがって、本実施形態に係る半導体パッケージ製造装置1はメンテナンス性が優れている。

【0027】

上述した本実施形態による効果は、図9に示す本発明の比較例についての説明から更に明らかになる。この比較例においては、下金型本体21のかわりに下金型本体121が用いられる。下金型本体121には導電性端子31が設けられていないため、下金型本体121が備える平面121aは、基板50が下金型本体121に吸引固定されたときに基板50の表面保護層55に密着するが、導通部分54aに接触しない。したがって、下金型本体121が電気的に接地されている場合であっても、半導体チップ60の内部回路61は電気的に接地されない。なお、基板50を間に挟んで上金型10及び下金型20を互いに押し付けあうことで平面121aが導通部分54aに接触する可能性もあるが、モールド樹脂70を上金型本体11から離型する際には上金型10及び下金型20を互いに押し付けあう力が作用しなくなって平面121aが導通部分54aから離れてしまうので、剥離帯電による静電破壊を防止することができない。

【0028】

位置決め孔50cが基板50の両側(図3の左右の2辺)に設けられ、両側に設けられた位置決め孔50cに対応して位置決めピン22が2列に設けられる場合を図に示したが、位置決め孔50cが基板50の片側だけに設けられ、片側だけに設けられた位置決め孔50cに対応して位置決めピン22が1列に設けられても良い。

【0029】

半導体パッケージ製造装置1によるモールド樹脂70の成形(成型)は、周囲が真空の状態で実行されてもよく、周囲が大気圧の状態で実行されてもよい。

【0030】

(第2の実施形態)

図10を参照して、本発明の第2の実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法を説明する。本実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法は、以下に説明する点を除いて第1の実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法と同様である。本実施形態に係る半導体パッケージ製造装置1は、導電性端子31のかわりに導電性端子32を備える。導電性端子32は、導電性端子配置穴21bに配置され、伸縮機構を備える。導電性端子32としてポゴピンのようなスプリングコンタクトピンが用いられる。導電性端子32は、バレル32aと、プランジャ32bと、スプリング32cを備える。バレル32aは、導電性端子配置穴21b内に配置されて下金型本体21に脱着可能に固定され、プランジャ32bが上金型本体11に向かって進退可能なようにプランジャ32bを支持する。プランジャ32bは、平面21a(導電性端子配置穴21b)から突き出た部分の高さが表面保護層55の厚さより大きくなる位置と、平面21a(導電性端子配置穴21b)から突き出ない位置とをとることが可能である。スプリング32cは、バレル32a及びプランジャ32bに接触し、プランジャ32bを上金型本体11に向かって付勢する。プランジャ32bは、スプリング32c、バレル32a、及び下金型本体21を介して電気的に接地される。

【0031】

基板50を下金型本体21に吸引固定したとき、プランジャ32bは、スプリング32cによって導通部分54aに向かって付勢された状態で導通部分54aに接触する。プランジャ32bは、平面21a(導電性端子配置穴21b)から突き出た状態で導通部分54aに接触する。ここで、プランジャ32bは導通部分54aに接触して導電性端子配置穴21b内に沈み込むため、導電性端子32による基板50の破損が防がれる。モールド樹脂70を離型する間、プランジャ32bはスプリング32cによって付勢されて導通部分54aに接触し続け、半導体チップ60の内部回路61が電気的に接地した状態が維持される。

【0032】

表面保護層55の厚さは製品ごとに異なるが、本実施形態によれば、導電性端子32と導通部分54aが確実に接触し、且つ、導電性端子32による基板50の破損が防がれる。

【0033】

導電性端子32が下金型本体21に脱着可能に固定されるため、導電性端子32の交換が容易である。したがって、本実施形態に係る半導体パッケージ製造装置1はメンテナンス性が優れている。

【0034】

第1の実施形態及び第2の実施形態において、半導体パッケージ製造装置1は、リリースフィルム支持装置40を備えなくても良い。この場合も、モールド樹脂70が上金型本体11から剥がれるときの剥離帯電により内部回路61が静電破壊されることが防止される。

【0035】

(第3の実施形態)

図11を参照して、本発明の第3の実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法を説明する。本実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法は、以下に説明する点を除いて第1の実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法と同様である。本実施形態において、リリースフィルム支持装置40は用いられない。本実施形態に係る半導体パッケージ製造装置1の上金型10は導電性端子33を備え、本実施形態に係る半導体パッケージ製造装置1の下金型20は導電性端子31を備えない。本実施形態においては、上金型本体11は電気的に接地され、上金型本体11に導電性端子配置穴11cが形成される。導電性端子配置穴11cは平面11aに開口する。導電性端子33は、導電性端子配置穴11cに配置され、伸縮機構を備える。導電性端子33としてポゴピンのようなスプリングコンタクトピンが用いられる。導電性端子33は、バレル33aと、プランジャ33bと、スプリング33cを備える。バレル33aは、導電性端子配置穴11c内に配置されて上金型本体11に脱着可能に固定され、プランジャ33bが下金型本体21に向かって進退可能なようにプランジャ33bを支持する。プランジャ33bは、平面11a(導電性端子配置穴11c)から突き出た部分の高さが表面保護層53の厚さより大きくなる位置と、平面11a(導電性端子配置穴11c)から突き出ない位置とをとることが可能である。スプリング33cは、バレル33a及びプランジャ33bに接触し、プランジャ33bを下金型本体21に向かって付勢する。プランジャ33bは、スプリング33c、バレル33a、及び上金型本体11を介して電気的に接地される。

【0036】

上金型10及び下金型20の間に基板50が挟まれたとき、平面11aは表面保護層53に密着し、プランジャ33bはスプリング33cによって導通部分52aに向かって付勢された状態で導通部分52aに接触する。プランジャ33bは、平面11a(導電性端子配置穴11c)から突き出た状態で導通部分52aに接触する。ここで、プランジャ33bは導通部分52aに接触して導電性端子配置穴11c内に沈み込むため、導電性端子33による基板50の破損が防がれる。モールド樹脂70を離型する間、導通部分52aは上金型本体11から遠ざかるが、プランジャ33bはスプリング33cによって付勢されているために導通部分52aに接触し続け、半導体チップ60の内部回路61が電気的に接地した状態が維持される。

【0037】

表面保護層53の厚さは製品ごとに異なるが、本実施形態によれば、導電性端子33と導通部分52aが確実に接触し、且つ、導電性端子33による基板50の破損が防がれる。

【0038】

導電性端子33が上金型本体11に脱着可能に固定されるため、導電性端子33の交換が容易である。したがって、本実施形態に係る半導体パッケージ製造装置1はメンテナンス性が優れている。

【0039】

上記各実施形態に様々な変更を加えることが可能である。例えば、第3の実施形態に係る下金型20は、導電性端子31又は32を備えることが可能である。基板50は半導体チップ60を一つだけ搭載してもよい。導通部分54aは、搭載部分50xに配置されてもよい。基板50は、導通部分52a及び54aの一方だけを備えてもよい。

【0040】

また、上記実施形態に係る導電性端子31乃至33を図12に示す半導体パッケージ製造装置201に適用することが可能である。半導体パッケージ製造装置201は、モールド樹脂70の圧縮成形を行う。半導体パッケージ製造装置201は、上金型210と、下金型220と、リリースフィルム支持装置240を備える。上金型210は、上金型本体211を備える。上金型本体211は半導体チップ組立体5の基板50を吸引固定する。下金型220は、下金型本体221を備える。下金型本体221は、上金型110の方向を向く平面221aを備える。下金型本体221に平面221aに開口する凹部221bが形成されている。リリースフィルム支持装置240は、リリースフィルム241を上金型210と下金型220の間に支持する。リリースフィルム241は、平面221a及び凹部221bに密着する。凹部221bにおいてモールド樹脂70が溶かされる。上金型210と下金型220とが接近し、基板50上の半導体チップ60が溶けた状態のモールド樹脂70に浸かる。モールド樹脂70が固まったら、上金型210及び下金型220を相対的に遠ざけてモールド樹脂70を下金型220から離型する。半導体パッケージ製造装置201によるモールド樹脂70の成形(成型)は、周囲が真空の状態で実行される。上金型210は、導電性端子31又は32を備えることが可能である。下金型220は、導電性端子33を備えることが可能である。

【符号の説明】

【0041】

1…半導体パッケージ製造装置

10…上金型

11…上金型本体

11a…平面

11b…凹部

11c…導電性端子配置穴

20…下金型

21…下金型本体

21a…平面

21b…導電性端子配置穴

21c…排気通路

22…位置決めピン

31、32、33…導電性端子

32a、33a…バレル

32b、33b…プランジャー

32c、33c…スプリング

40…リリースフィルム支持装置

41…リリースフィルム

5…半導体チップ組立体

50…基板

50a…搭載側

50b…非搭載側

50c…位置決め孔

50d…溝

50x…搭載部分

50y…縁部分

51…中間絶縁層

52、54…導電層

52a、54a…導通部分

53、55…表面保護層

60…半導体チップ

61…内部回路

62…ワイヤー

70…モールド樹脂

121…下金型本体

121a…平面

201…半導体パッケージ製造装置

210…上金型

211…上金型本体

220…下金型

221…下金型本体

221a…平面

221b…凹部

240…リリースフィルム支持装置

241…リリースフィルム

【技術分野】

【0001】

本発明は半導体パッケージに関する。

【背景技術】

【0002】

半導体パッケージの製造プロセスにおいて、半導体チップが基板に搭載され、半導体チップがモールド樹脂で封入される。モールド樹脂を成型する金型からモールド樹脂が容易に離型されるように、モールド樹脂と金型との間にリリースフィルムが配置される。リリースフィルムをモールド樹脂から剥がすとき、又は金型からリリースフィルムを剥がすときの剥離帯電に起因して半導体チップが静電破壊される場合がある。

【0003】

特開2007−287944号公報、特開2000−243871号公報、特開2000−133666号公報、特開平11−312698号公報は、静電破壊を防止するための技術を開示している。

【0004】

例えば、特開2007−287944号公報に記載された半導体製造装置は、半導体チップを上側に搭載した基板を下側から支持する下部金型と、可撓性フィルムを介して半導体チップに供給された樹脂を成型する上部金型とを備える。下部金型は、電気的絶縁領域を含み、電気的絶縁領域を介して基板を支持する。下部金型が電気的絶縁領域を介して基板を支持するため、可撓性フィルムに帯電した電荷が基板を通じて下部金型へ導通するのが阻止され、基板上の半導体チップの静電破壊が抑制される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2007‐287944号公報

【特許文献2】特開2000−243871号公報

【特許文献3】特開2000−133666号公報

【特許文献4】特開平11−312698号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特開2007−287944号公報によれば、モールド樹脂を成形するプロセスでの半導体チップの静電破壊の抑制には効果があるが、成形後の基板は帯電したままの状態のため、金型から成形済みの基板を取り出す際のハンドリングなどにおいて放電が起こり、半導体チップが破壊される恐れがある。このため、半導体パッケージの製造プロセスにおける静電破壊を防止することが必要とされている。

【課題を解決するための手段】

【0007】

以下に、(発明を実施するための形態)で使用される番号を用いて、課題を解決するための手段を説明する。これらの番号は、(特許請求の範囲)の記載と(発明を実施するための形態)との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、(特許請求の範囲)に記載されている発明の技術的範囲の解釈に用いてはならない。

【0008】

半導体パッケージ製造装置は、半導体チップ(60)を搭載した基板(50)を吸引固定する第1金型(20、210)と、第2金型(10、220)とを具備する。前記基板は、前記半導体チップの内部回路(61)と導通する導通部分(52a、54a)を備える。前記第1金型又は前記第2金型は、電気的に接地された導電性端子(31、32、33)を備える。前記第1金型及び前記第2金型に前記基板が挟まれた状態で、前記半導体チップを封入するモールド樹脂(70)が前記第2金型により成型される。前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型する間、前記導電性端子は前記導通部分に接触し続ける。

【0009】

半導体パッケージの製造方法は、半導体チップ(60)を搭載した基板(50)を第1金型(20、210)に吸引固定することと、前記第1金型及び第2金型(10、220)の間に前記基板を挟むことと、前記半導体チップを封入するモールド樹脂(70)を前記第2金型により成型することと、前記半導体チップの内部回路(61)が電気的に接地した状態を維持しながら前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型することとを具備する。前記基板は、前記内部回路と導通する導通部分(52a、54a)を備える。前記第1金型又は前記第2金型は、電気的に接地された導電性端子(31、32、33)を備える。前記導電性端子が前記導通部分に接触することで前記内部回路が電気的に接地する。

【発明の効果】

【0010】

本発明によれば、半導体パッケージの製造プロセスにおける静電破壊が防止される。

【図面の簡単な説明】

【0011】

【図1】図1は、本発明の第1の実施形態に係る半導体パッケージ製造装置の断面図である。

【図2】図2は、半導体チップ組立体の側面図である。

【図3】図3は、半導体チップ組立体の下面図である。

【図4】図4は、半導体チップ組立体の断面図である。

【図5】図5は、半導体パッケージ製造装置の下金型に半導体チップ組立体を固定した状態を示す断面図である。

【図6】図6は、半導体チップ組立体の基板を半導体パッケージ製造装置の上金型と下金型とで挟んだ状態を示す断面図である。

【図7】図7は、半導体チップ組立体の半導体チップをモールド樹脂で封入した状態を示す断面図である。

【図8】図8は、モールド樹脂が上金型から離型された状態を示す断面図である。

【図9】図9は、本発明の比較例に係る半導体パッケージ製造装置の下金型に半導体チップ組立体を固定した状態を示す断面図である。

【図10】図10は、本発明の第2の実施形態に係る下金型に半導体チップ組立体を固定した状態を示す断面図である。

【図11】図11は、本発明の第3の実施形態に係る上金型と半導体チップ組立体との電気的接続状態を示す断面図である。

【図12】図12は、第1乃至第3の実施形態の変形例に係る半導体パッケージ製造装置の断面図である。

【発明を実施するための形態】

【0012】

添付図面を参照して、本発明による半導体パッケージ製造装置及び半導体パッケージの製造方法を実施するための形態を以下に説明する。

【0013】

(第1の実施形態)

図1を参照して、本発明の第1の実施形態に係る半導体パッケージ製造装置1を説明する。半導体パッケージ製造装置1は、上金型10と、下金型20と、リリースフィルム支持装置40を備える。上金型10は、上金型本体11を備える。上金型本体11は、下金型20の方向を向く平面11aを備える。上金型本体11に、平面11aに開口する凹部11bが形成されている。凹部11bは、キャビティを形成する。下金型20は、下金型本体21と、導電性端子31を備える。下金型本体21は、上金型10の方向を向く平面21aと、平面21aから上金型10に向かって突き出た位置決めピン22を備える。下金型本体21に、平面21aに開口する導電性端子配置穴21bと、平面21aに開口する排気通路21cとが形成されている。排気通路21cは、図示されない真空ポンプに接続されている。導電性端子31は、平面21aから上金型10に向かって突き出すように導電性端子配置穴21bに配置され、下金型本体21に脱着可能に固定され、下金型本体21を介して電気的に接地されている。リリースフィルム支持装置40は、リリースフィルム41を凹部11bと平面21aとの間に支持する。後述するモールド樹脂の成型時において、リリースフィルム41は、図1に二点鎖線で示されるように、上金型10に吸着されて平面11a及び凹部11bに密着する。

【0014】

図2は、半導体パッケージ製造装置1によって処理される半導体チップ組立体5を示す。半導体チップ組立体5は、多層配線基板のような基板50と、基板50に搭載された複数の半導体チップ60を備える。半導体チップ60は、例えば、半導体ウエハを個片化することで提供される。複数の半導体チップ60は、基板50の搭載側50aに搭載される。基板50の非搭載側50bは、搭載側50aの反対側である。各半導体チップ60は、内部回路61を備える。内部回路61は、ワイヤー62を介して基板50に接続される。

【0015】

図2において半導体チップ60の上に別の半導体チップが搭載されているが、この別の半導体チップは無くてもよい。また、半導体チップ60は基板50にフリップチップマウントされてもよい。半導体チップ60が基板50にフリップチップマウントされる場合、内部回路61はワイヤー62を介さずに例えばはんだバンプなどを介して基板50に接続される。

【0016】

図3は、基板50の非搭載側50bを示している。基板50は、複数の半導体チップ60が搭載される搭載部分50xと、基板50の縁に位置する縁部分50yとを備える。縁部分50yは、搭載部分50xの周囲を囲んでいる。基板50は、非搭載側50bに表面保護層55を備える。表面保護層55に溝50dが形成されている。溝50dは、搭載部分50xと縁部分50yの間の境界に沿って形成されている。縁部分50yには、基板50を貫通するように位置決め孔50cが形成されている。縁部分50yは、非搭載側50bに露出した導通部分54aを含む。

【0017】

図4は、基板50の断面図を示す。基板50は、表面保護層53と、導電層52と、中間絶縁層51と、導電層54と、表面保護層55を備える。表面保護層53と、導電層52と、中間絶縁層51と、導電層54と、表面保護層55は、搭載側50aから非搭載側50bに向かって順番に配置される。導電層52及び54は、例えば銅のような金属により形成される。表面保護層53及び55は、ソルダーレジストのような絶縁層である。導電層52及び54の各々は、複数の半導体チップ60のそれぞれの内部回路61とワイヤー(62)を介して導通している。例えば、導電層52及び54の各々は、複数の半導体チップ60のそれぞれのグランド配線と導通している。導電層52は表面保護層53によって部分的に覆われており、導電層52の一部としての導通部分52aは表面保護層53に覆われずに搭載側50aに露出している。導通部分52aは縁部分50yに含まれる。導電層54は表面保護層55によって部分的に覆われており、導電層54の一部としての導通部分54aは表面保護層55に覆われずに非搭載側50bに露出している。導通部分54aは縁部分50yに含まれる。ここで、導通部分52a及び54aの表面に金メッキ層が形成されていることが好ましい。このようにすることで、後述する導通部分52a及び54aの接地が確実になる。なお、中間絶縁層51は、一又は複数の導電層を含んでもよい。

【0018】

以下、図5乃至図8を用いて本実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法を説明する。

【0019】

図5を参照して、位置決めピン22が位置決め孔50cに配置されるように、非搭載側50bが平面21aと向かい合う姿勢で半導体チップ組立体5を下金型本体21に載せる。このとき、排気通路21cは溝50dに接続され、導通部分54aは導電性端子31と向かい合う。

【0020】

図示されない真空ポンプが排気通路21cを介して溝50dから空気を排気することで、下金型20は基板50を吸引固定する。このとき、平面21aが表面保護層55に密着し、導電性端子31は平面21aから突き出た状態(導電性端子配置穴21bから突き出た状態)で導通部分54aに接触する。導電性端子31が平面21a(導電性端子配置穴21b)から突き出ているため、半導体チップ60の内部回路61が確実に電気的に接地される。ここで、導電性端子31の平面21a(導電性端子配置穴21b)から突き出ている部分の高さは、内部回路61の接地を確保し、且つ、基板50を破壊しないために、表面保護層55の厚さより僅かに大きいことが好ましい。

【0021】

図6を参照して、上金型10と下金型20とを相対的に近づけて、上金型10及び下金型20で基板50を挟む。このとき、複数の半導体チップ60が凹部11bに配置され、平面11a及び凹部11bがリリースフィルム41に密着し、リリースフィルム41が表面保護層53に密着し、平面21aが表面保護層55に密着する。

【0022】

図7を参照して、上金型10及び下金型20に基板50が挟まれた状態で、凹部11bに樹脂材料を注入して複数の半導体チップ60を封入するモールド樹脂70を形成する。モールド樹脂70は、上金型本体11により、凹部11bの形状に対応する形状に成型される。ここで、リリースフィルム41はモールド樹脂70と凹部11bの間に配置される。

【0023】

図8を参照して、上金型10及び下金型20を相対的に遠ざけてモールド樹脂70を上金型本体11から離型する。このとき、リリースフィルム41がモールド樹脂70と上金型本体11とから剥がれる。モールド樹脂70を離型する間、導電性端子31は導通部分54aに接触し続け、半導体チップ60の内部回路61が電気的に接地した状態が維持される。

【0024】

したがって、リリースフィルム41がモールド樹脂70から剥がれるとき、又はリリースフィルム41が上金型本体11から剥がれるときの剥離帯電による電荷が下金型本体21を介してグランドに逃がされるため、内部回路61が静電破壊されることが防止される。

【0025】

更に、下金型20による基板50の吸引固定を解除してモールド樹脂70が形成された半導体チップ組立体5を下金型20から取り外した後、縁部分55yを搭載部分55xから切り離す。つまり、縁部分50yは製品に含まれない。したがって、導電性端子31が導通部分54aに強く押し付けられたために縁部分50yに損傷が発生しても、内部回路61の電気的接地が確保されれば問題ない。

【0026】

導電性端子31が下金型本体21に脱着可能に固定されるため、導電性端子31の交換が容易である。したがって、本実施形態に係る半導体パッケージ製造装置1はメンテナンス性が優れている。

【0027】

上述した本実施形態による効果は、図9に示す本発明の比較例についての説明から更に明らかになる。この比較例においては、下金型本体21のかわりに下金型本体121が用いられる。下金型本体121には導電性端子31が設けられていないため、下金型本体121が備える平面121aは、基板50が下金型本体121に吸引固定されたときに基板50の表面保護層55に密着するが、導通部分54aに接触しない。したがって、下金型本体121が電気的に接地されている場合であっても、半導体チップ60の内部回路61は電気的に接地されない。なお、基板50を間に挟んで上金型10及び下金型20を互いに押し付けあうことで平面121aが導通部分54aに接触する可能性もあるが、モールド樹脂70を上金型本体11から離型する際には上金型10及び下金型20を互いに押し付けあう力が作用しなくなって平面121aが導通部分54aから離れてしまうので、剥離帯電による静電破壊を防止することができない。

【0028】

位置決め孔50cが基板50の両側(図3の左右の2辺)に設けられ、両側に設けられた位置決め孔50cに対応して位置決めピン22が2列に設けられる場合を図に示したが、位置決め孔50cが基板50の片側だけに設けられ、片側だけに設けられた位置決め孔50cに対応して位置決めピン22が1列に設けられても良い。

【0029】

半導体パッケージ製造装置1によるモールド樹脂70の成形(成型)は、周囲が真空の状態で実行されてもよく、周囲が大気圧の状態で実行されてもよい。

【0030】

(第2の実施形態)

図10を参照して、本発明の第2の実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法を説明する。本実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法は、以下に説明する点を除いて第1の実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法と同様である。本実施形態に係る半導体パッケージ製造装置1は、導電性端子31のかわりに導電性端子32を備える。導電性端子32は、導電性端子配置穴21bに配置され、伸縮機構を備える。導電性端子32としてポゴピンのようなスプリングコンタクトピンが用いられる。導電性端子32は、バレル32aと、プランジャ32bと、スプリング32cを備える。バレル32aは、導電性端子配置穴21b内に配置されて下金型本体21に脱着可能に固定され、プランジャ32bが上金型本体11に向かって進退可能なようにプランジャ32bを支持する。プランジャ32bは、平面21a(導電性端子配置穴21b)から突き出た部分の高さが表面保護層55の厚さより大きくなる位置と、平面21a(導電性端子配置穴21b)から突き出ない位置とをとることが可能である。スプリング32cは、バレル32a及びプランジャ32bに接触し、プランジャ32bを上金型本体11に向かって付勢する。プランジャ32bは、スプリング32c、バレル32a、及び下金型本体21を介して電気的に接地される。

【0031】

基板50を下金型本体21に吸引固定したとき、プランジャ32bは、スプリング32cによって導通部分54aに向かって付勢された状態で導通部分54aに接触する。プランジャ32bは、平面21a(導電性端子配置穴21b)から突き出た状態で導通部分54aに接触する。ここで、プランジャ32bは導通部分54aに接触して導電性端子配置穴21b内に沈み込むため、導電性端子32による基板50の破損が防がれる。モールド樹脂70を離型する間、プランジャ32bはスプリング32cによって付勢されて導通部分54aに接触し続け、半導体チップ60の内部回路61が電気的に接地した状態が維持される。

【0032】

表面保護層55の厚さは製品ごとに異なるが、本実施形態によれば、導電性端子32と導通部分54aが確実に接触し、且つ、導電性端子32による基板50の破損が防がれる。

【0033】

導電性端子32が下金型本体21に脱着可能に固定されるため、導電性端子32の交換が容易である。したがって、本実施形態に係る半導体パッケージ製造装置1はメンテナンス性が優れている。

【0034】

第1の実施形態及び第2の実施形態において、半導体パッケージ製造装置1は、リリースフィルム支持装置40を備えなくても良い。この場合も、モールド樹脂70が上金型本体11から剥がれるときの剥離帯電により内部回路61が静電破壊されることが防止される。

【0035】

(第3の実施形態)

図11を参照して、本発明の第3の実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法を説明する。本実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法は、以下に説明する点を除いて第1の実施形態に係る半導体パッケージ製造装置1及び半導体パッケージの製造方法と同様である。本実施形態において、リリースフィルム支持装置40は用いられない。本実施形態に係る半導体パッケージ製造装置1の上金型10は導電性端子33を備え、本実施形態に係る半導体パッケージ製造装置1の下金型20は導電性端子31を備えない。本実施形態においては、上金型本体11は電気的に接地され、上金型本体11に導電性端子配置穴11cが形成される。導電性端子配置穴11cは平面11aに開口する。導電性端子33は、導電性端子配置穴11cに配置され、伸縮機構を備える。導電性端子33としてポゴピンのようなスプリングコンタクトピンが用いられる。導電性端子33は、バレル33aと、プランジャ33bと、スプリング33cを備える。バレル33aは、導電性端子配置穴11c内に配置されて上金型本体11に脱着可能に固定され、プランジャ33bが下金型本体21に向かって進退可能なようにプランジャ33bを支持する。プランジャ33bは、平面11a(導電性端子配置穴11c)から突き出た部分の高さが表面保護層53の厚さより大きくなる位置と、平面11a(導電性端子配置穴11c)から突き出ない位置とをとることが可能である。スプリング33cは、バレル33a及びプランジャ33bに接触し、プランジャ33bを下金型本体21に向かって付勢する。プランジャ33bは、スプリング33c、バレル33a、及び上金型本体11を介して電気的に接地される。

【0036】

上金型10及び下金型20の間に基板50が挟まれたとき、平面11aは表面保護層53に密着し、プランジャ33bはスプリング33cによって導通部分52aに向かって付勢された状態で導通部分52aに接触する。プランジャ33bは、平面11a(導電性端子配置穴11c)から突き出た状態で導通部分52aに接触する。ここで、プランジャ33bは導通部分52aに接触して導電性端子配置穴11c内に沈み込むため、導電性端子33による基板50の破損が防がれる。モールド樹脂70を離型する間、導通部分52aは上金型本体11から遠ざかるが、プランジャ33bはスプリング33cによって付勢されているために導通部分52aに接触し続け、半導体チップ60の内部回路61が電気的に接地した状態が維持される。

【0037】

表面保護層53の厚さは製品ごとに異なるが、本実施形態によれば、導電性端子33と導通部分52aが確実に接触し、且つ、導電性端子33による基板50の破損が防がれる。

【0038】

導電性端子33が上金型本体11に脱着可能に固定されるため、導電性端子33の交換が容易である。したがって、本実施形態に係る半導体パッケージ製造装置1はメンテナンス性が優れている。

【0039】

上記各実施形態に様々な変更を加えることが可能である。例えば、第3の実施形態に係る下金型20は、導電性端子31又は32を備えることが可能である。基板50は半導体チップ60を一つだけ搭載してもよい。導通部分54aは、搭載部分50xに配置されてもよい。基板50は、導通部分52a及び54aの一方だけを備えてもよい。

【0040】

また、上記実施形態に係る導電性端子31乃至33を図12に示す半導体パッケージ製造装置201に適用することが可能である。半導体パッケージ製造装置201は、モールド樹脂70の圧縮成形を行う。半導体パッケージ製造装置201は、上金型210と、下金型220と、リリースフィルム支持装置240を備える。上金型210は、上金型本体211を備える。上金型本体211は半導体チップ組立体5の基板50を吸引固定する。下金型220は、下金型本体221を備える。下金型本体221は、上金型110の方向を向く平面221aを備える。下金型本体221に平面221aに開口する凹部221bが形成されている。リリースフィルム支持装置240は、リリースフィルム241を上金型210と下金型220の間に支持する。リリースフィルム241は、平面221a及び凹部221bに密着する。凹部221bにおいてモールド樹脂70が溶かされる。上金型210と下金型220とが接近し、基板50上の半導体チップ60が溶けた状態のモールド樹脂70に浸かる。モールド樹脂70が固まったら、上金型210及び下金型220を相対的に遠ざけてモールド樹脂70を下金型220から離型する。半導体パッケージ製造装置201によるモールド樹脂70の成形(成型)は、周囲が真空の状態で実行される。上金型210は、導電性端子31又は32を備えることが可能である。下金型220は、導電性端子33を備えることが可能である。

【符号の説明】

【0041】

1…半導体パッケージ製造装置

10…上金型

11…上金型本体

11a…平面

11b…凹部

11c…導電性端子配置穴

20…下金型

21…下金型本体

21a…平面

21b…導電性端子配置穴

21c…排気通路

22…位置決めピン

31、32、33…導電性端子

32a、33a…バレル

32b、33b…プランジャー

32c、33c…スプリング

40…リリースフィルム支持装置

41…リリースフィルム

5…半導体チップ組立体

50…基板

50a…搭載側

50b…非搭載側

50c…位置決め孔

50d…溝

50x…搭載部分

50y…縁部分

51…中間絶縁層

52、54…導電層

52a、54a…導通部分

53、55…表面保護層

60…半導体チップ

61…内部回路

62…ワイヤー

70…モールド樹脂

121…下金型本体

121a…平面

201…半導体パッケージ製造装置

210…上金型

211…上金型本体

220…下金型

221…下金型本体

221a…平面

221b…凹部

240…リリースフィルム支持装置

241…リリースフィルム

【特許請求の範囲】

【請求項1】

半導体チップを搭載した基板を吸引固定する第1金型と、

第2金型と

を具備し、

前記基板は、前記半導体チップの内部回路と導通する導通部分を備え、

前記第1金型又は前記第2金型は、電気的に接地された導電性端子を備え、

前記第1金型及び前記第2金型に前記基板が挟まれた状態で、前記半導体チップを封入するモールド樹脂が前記第2金型により成型され、

前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型する間、前記導電性端子は前記導通部分に接触し続ける

半導体パッケージ製造装置。

【請求項2】

前記基板は、

前記内部回路と導通する導電層と、

前記導電層を部分的に覆う表面保護層と

を備え、

前記導通部分は前記導電層の前記表面保護層に覆われない部分であり、

前記第1金型は、

前記基板を吸引固定したときに前記表面保護層に密着する平面と、

前記導電性端子と

を備え、

前記導電性端子は前記平面に開口する穴に配置され、

前記導電性端子は、前記平面から突き出た状態で前記導通部分に接触する

請求項1の半導体パッケージ製造装置。

【請求項3】

前記第2金型に密着するリリースフィルムを支持するリリースフィルム支持装置を更に具備する

請求項1又は2の半導体パッケージ製造装置。

【請求項4】

前記基板は、

前記内部回路と導通する導電層と、

前記導電層を部分的に覆う表面保護層と

を備え、

前記導通部分は前記導電層の前記表面保護層に覆われない部分であり、

前記第2金型は、

前記第1金型及び前記第2金型に前記基板が挟まれたときに前記表面保護層に密着する平面と、

前記導電性端子と

を備え、

前記導電性端子は前記平面に開口する穴に配置され、

前記導電性端子は、前記平面から突き出た状態で前記導通部分に接触する

請求項1の半導体パッケージ製造装置。

【請求項5】

前記導電性端子は、

前記導通部分に接触するプランジャと、

前記プランジャを前記導通部分に向かって付勢するスプリングと

を備える

請求項1から4のいずれか一項に記載の半導体パッケージ製造装置。

【請求項6】

前記プランジャは、前記平面から突き出た状態で前記導通部分に接触する

請求項5の半導体パッケージ製造装置。

【請求項7】

半導体チップを搭載し、前記半導体チップの内部回路と導通する導通部分を備えた基板に対して、樹脂封止する半導体パッケージ製造装置において、

前記基板を吸引固定する第1金型と、

前記基板を前記第1金型と共に挟み込むように配置される第2金型と、を具備し、

前記第1金型または前記第2金型は、電気的に接地された導電性端子を備え、

前記第1金型と前記第2金型とに前記基板が挟まれた状態で、前記半導体チップをモールド樹脂により樹脂封止し、

前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型する間、前記導電性端子は前記導通部分に接触し続ける、

半導体パッケージ製造装置。

【請求項8】

半導体チップを搭載した基板を第1金型に吸引固定することと、

前記第1金型及び第2金型の間に前記基板を挟むことと、

前記半導体チップを封入するモールド樹脂を前記第2金型により成型することと、

前記半導体チップの内部回路が電気的に接地した状態を維持しながら前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型することと

を具備し、

前記基板は、前記内部回路と導通する導通部分を備え、

前記第1金型又は前記第2金型は、電気的に接地された導電性端子を備え、

前記導電性端子が前記導通部分に接触することで前記内部回路が電気的に接地する

半導体パッケージの製造方法。

【請求項9】

前記基板は、

前記内部回路と導通する導電層と、

前記導電層を部分的に覆う表面保護層と

を備え、

前記導通部分は前記導電層の前記表面保護層に覆われない部分であり、

前記第1金型は、

前記基板が前記第1金型に吸引固定されたときに前記表面保護層に密着する平面と、

前記導電性端子と

を備え、

前記導電性端子は前記平面に開口する穴に配置され、

前記基板を前記第1金型に吸引固定することは、前記導電性端子を前記平面より突き出た状態で前記導通部分に接触させることを含む

請求項8の半導体パッケージの製造方法。

【請求項10】

前記導電性端子は、

前記導通部分に接触するプランジャと、

前記プランジャを前記導通部分に向かって付勢するスプリングと

を備える

請求項9の半導体パッケージの製造方法。

【請求項11】

前記基板は、

前記内部回路と導通する導電層と、

前記導電層を部分的に覆う表面保護層と

を備え、

前記導通部分は前記導電層の前記表面保護層に覆われない部分であり、

前記第2金型は、

前記第1金型及び前記第2金型の間に前記基板が挟まれたとき前記表面保護層に密着する平面と、

前記導電性端子と

を備え、

前記導電性端子は前記平面に開口する穴に配置され、

前記導電性端子は、

前記導通部分に接触するプランジャと、

前記プランジャを前記導通部分に向かって付勢するスプリングと

を備え、

前記第1金型及び前記第2金型の間に前記基板を挟むことは、前記プランジャを前記導通部分に接触させることを含む

請求項8の半導体パッケージの製造方法。

【請求項12】

前記基板は、

前記半導体チップを搭載した搭載部分と、

前記基板の縁に位置する縁部分と

を含み、

前記縁部分は前記導通部分を含み、

前記縁部分を前記搭載部分から切り離すことを更に具備する

請求項8乃至11のいずれかに記載の半導体パッケージの製造方法。

【請求項1】

半導体チップを搭載した基板を吸引固定する第1金型と、

第2金型と

を具備し、

前記基板は、前記半導体チップの内部回路と導通する導通部分を備え、

前記第1金型又は前記第2金型は、電気的に接地された導電性端子を備え、

前記第1金型及び前記第2金型に前記基板が挟まれた状態で、前記半導体チップを封入するモールド樹脂が前記第2金型により成型され、

前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型する間、前記導電性端子は前記導通部分に接触し続ける

半導体パッケージ製造装置。

【請求項2】

前記基板は、

前記内部回路と導通する導電層と、

前記導電層を部分的に覆う表面保護層と

を備え、

前記導通部分は前記導電層の前記表面保護層に覆われない部分であり、

前記第1金型は、

前記基板を吸引固定したときに前記表面保護層に密着する平面と、

前記導電性端子と

を備え、

前記導電性端子は前記平面に開口する穴に配置され、

前記導電性端子は、前記平面から突き出た状態で前記導通部分に接触する

請求項1の半導体パッケージ製造装置。

【請求項3】

前記第2金型に密着するリリースフィルムを支持するリリースフィルム支持装置を更に具備する

請求項1又は2の半導体パッケージ製造装置。

【請求項4】

前記基板は、

前記内部回路と導通する導電層と、

前記導電層を部分的に覆う表面保護層と

を備え、

前記導通部分は前記導電層の前記表面保護層に覆われない部分であり、

前記第2金型は、

前記第1金型及び前記第2金型に前記基板が挟まれたときに前記表面保護層に密着する平面と、

前記導電性端子と

を備え、

前記導電性端子は前記平面に開口する穴に配置され、

前記導電性端子は、前記平面から突き出た状態で前記導通部分に接触する

請求項1の半導体パッケージ製造装置。

【請求項5】

前記導電性端子は、

前記導通部分に接触するプランジャと、

前記プランジャを前記導通部分に向かって付勢するスプリングと

を備える

請求項1から4のいずれか一項に記載の半導体パッケージ製造装置。

【請求項6】

前記プランジャは、前記平面から突き出た状態で前記導通部分に接触する

請求項5の半導体パッケージ製造装置。

【請求項7】

半導体チップを搭載し、前記半導体チップの内部回路と導通する導通部分を備えた基板に対して、樹脂封止する半導体パッケージ製造装置において、

前記基板を吸引固定する第1金型と、

前記基板を前記第1金型と共に挟み込むように配置される第2金型と、を具備し、

前記第1金型または前記第2金型は、電気的に接地された導電性端子を備え、

前記第1金型と前記第2金型とに前記基板が挟まれた状態で、前記半導体チップをモールド樹脂により樹脂封止し、

前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型する間、前記導電性端子は前記導通部分に接触し続ける、

半導体パッケージ製造装置。

【請求項8】

半導体チップを搭載した基板を第1金型に吸引固定することと、

前記第1金型及び第2金型の間に前記基板を挟むことと、

前記半導体チップを封入するモールド樹脂を前記第2金型により成型することと、

前記半導体チップの内部回路が電気的に接地した状態を維持しながら前記第1金型及び前記第2金型を相対的に遠ざけて前記モールド樹脂を前記第2金型から離型することと

を具備し、

前記基板は、前記内部回路と導通する導通部分を備え、

前記第1金型又は前記第2金型は、電気的に接地された導電性端子を備え、

前記導電性端子が前記導通部分に接触することで前記内部回路が電気的に接地する

半導体パッケージの製造方法。

【請求項9】

前記基板は、

前記内部回路と導通する導電層と、

前記導電層を部分的に覆う表面保護層と

を備え、

前記導通部分は前記導電層の前記表面保護層に覆われない部分であり、

前記第1金型は、

前記基板が前記第1金型に吸引固定されたときに前記表面保護層に密着する平面と、

前記導電性端子と

を備え、

前記導電性端子は前記平面に開口する穴に配置され、

前記基板を前記第1金型に吸引固定することは、前記導電性端子を前記平面より突き出た状態で前記導通部分に接触させることを含む

請求項8の半導体パッケージの製造方法。

【請求項10】

前記導電性端子は、

前記導通部分に接触するプランジャと、

前記プランジャを前記導通部分に向かって付勢するスプリングと

を備える

請求項9の半導体パッケージの製造方法。

【請求項11】

前記基板は、

前記内部回路と導通する導電層と、

前記導電層を部分的に覆う表面保護層と

を備え、

前記導通部分は前記導電層の前記表面保護層に覆われない部分であり、

前記第2金型は、

前記第1金型及び前記第2金型の間に前記基板が挟まれたとき前記表面保護層に密着する平面と、

前記導電性端子と

を備え、

前記導電性端子は前記平面に開口する穴に配置され、

前記導電性端子は、

前記導通部分に接触するプランジャと、

前記プランジャを前記導通部分に向かって付勢するスプリングと

を備え、

前記第1金型及び前記第2金型の間に前記基板を挟むことは、前記プランジャを前記導通部分に接触させることを含む

請求項8の半導体パッケージの製造方法。

【請求項12】

前記基板は、

前記半導体チップを搭載した搭載部分と、

前記基板の縁に位置する縁部分と

を含み、

前記縁部分は前記導通部分を含み、

前記縁部分を前記搭載部分から切り離すことを更に具備する

請求項8乃至11のいずれかに記載の半導体パッケージの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−124319(P2011−124319A)

【公開日】平成23年6月23日(2011.6.23)

【国際特許分類】

【出願番号】特願2009−279354(P2009−279354)

【出願日】平成21年12月9日(2009.12.9)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年6月23日(2011.6.23)

【国際特許分類】

【出願日】平成21年12月9日(2009.12.9)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]