半導体メモリカード及びその製造方法

【課題】半導体メモリを搭載する基板上においてデータ信号の劣化を防止した半導体メモリカード及びその製造方法を提供する。

【解決手段】実施の形態によれば、半導体メモリと、通常モード及び通常モードよりもデータ転送速度が速い高速モードの両方での半導体メモリへのデータの読み書きを制御するメモリコントローラと、少なくとも一つの内層を有する多層プリント基板に半導体メモリ及びメモリコントローラを表裏に分けて実装した回路基板とを備える。回路基板は、メモリコントローラと外部機器との間での高速モードによるデータ入出力用としてメモリコントローラの実装面に設けられ、金めっき加工が施された高速モード用の金端子と、高速モード用の金端子とメモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線と、高速差動信号配線から分岐し、回路基板の面内において分岐点の近傍で切断された金めっき加工用のめっきリードを有する。

【解決手段】実施の形態によれば、半導体メモリと、通常モード及び通常モードよりもデータ転送速度が速い高速モードの両方での半導体メモリへのデータの読み書きを制御するメモリコントローラと、少なくとも一つの内層を有する多層プリント基板に半導体メモリ及びメモリコントローラを表裏に分けて実装した回路基板とを備える。回路基板は、メモリコントローラと外部機器との間での高速モードによるデータ入出力用としてメモリコントローラの実装面に設けられ、金めっき加工が施された高速モード用の金端子と、高速モード用の金端子とメモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線と、高速差動信号配線から分岐し、回路基板の面内において分岐点の近傍で切断された金めっき加工用のめっきリードを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体メモリカード及びその製造方法に関する。

【背景技術】

【0002】

近年、例えばNANDフラッシュメモリなどの半導体メモリを用いたメモリカードは、連続撮影した静止画像や高解像度の動画像の記録といった用途にも用いられており、これらの用途においては短時間に多くの情報を読み出したり書き込んだりすること、即ちデータ転送速度の高速化が求められている。一例としては、300MB/secのデータ転送速度を実現することが求められている。

【0003】

旧来のSDTMメモリカード(以下、SDメモリカードと表記する。)は、データ転送速度が高々20MB/sec程度であるため、通常の動作モード(通常モード)とは別に、これよりも高速に情報を読み書き可能な動作モード(高速モード)でも使用可能とすることで、通常のホスト機器との互換性を保ちつつ高速度のデータ転送を可能とすることが提案されている。

【0004】

半導体メモリカードにおいてデータ転送速度の高速化を実現するためには、半導体メモリを搭載する基板上においてデータ信号の劣化を防止する必要がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2005−84935号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

一つの実施形態は、半導体メモリを搭載する基板上においてデータ信号の劣化を防止した半導体メモリカード及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一つの実施形態によれば、半導体メモリと、通常モード及び通常モードよりもデータ転送速度が速い高速モードの両方での半導体メモリへのデータの読み書きを制御するメモリコントローラと、少なくとも一つの内層を有する多層プリント基板に半導体メモリ及びメモリコントローラを表裏に分けて実装した回路基板とを備える。回路基板は、メモリコントローラと外部機器との間での高速モードによるデータ入出力用としてメモリコントローラの実装面に設けられ、金めっき加工が施された高速モード用の金端子と、高速モード用の金端子とメモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線と、高速差動信号配線から分岐し、回路基板の面内において高速差動信号配線との分岐点の近傍で切断された金めっき加工用のめっきリードを有する。

【図面の簡単な説明】

【0008】

【図1】図1は、第1の実施形態の半導体メモリカードを適用したSDメモリカードの構成を模式的に示す図。

【図2】図2は、下ケース側を視点としたSDメモリカードの外観を示す図。

【図3】図3は、回路基板の上面側の部品配置状態を示す図。

【図4】図4は、回路基板の下面側の部品配置状態を示す図。

【図5】図5は、回路基板の断面模式図。

【図6】図6は、L1層の配線パターンの一例を示す図。

【図7】図7は、L2層の配線パターンの一例を示す図。

【図8】図8は、TDR法による差動インピーダンスの解析結果の一例を示す図。

【図9】図9は、L3層の配線パターンの一例を示す図。

【図10】図10は、L4層の配線パターンの一例を示す図。

【図11】図11は、回路基板の上側表面に設けられるソルダレジストの開口状態を示す図。

【図12】図12は、回路基板の下側表面に設けられるソルダレジストの開口状態を示す図。

【図13】図13は、高速差動信号用の金端子及び高速差動信号用のメモリコントローラワイヤボンディングパッドに電解金めっきを施すためのめっきリードの配線状態を示す図。

【図14】図14は、信号受信端での波形アイパターンを示す図。

【図15】図15は、回路基板の製造工程を示す図。

【図16】図16は、第2の実施形態の半導体メモリカードを適用したSDメモリカードの高速差動信号用の金端子及び高速差動信号用のメモリコントローラワイヤボンディングパッドに電解金めっきを施すためのめっきリードを示す図。

【発明を実施するための形態】

【0009】

以下に添付図面を参照して、実施形態にかかる半導体メモリカード及びその製造方法を詳細に説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0010】

(第1の実施形態)

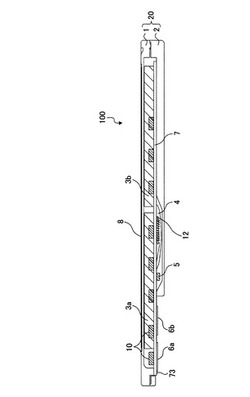

図1は、第1の実施形態の半導体メモリカードを適用したSDメモリカードの構成を模式的に示す断面図である。ここで、図1の紙面における左方向はコネクタへの挿入方向であり、左側を「前」と定義する。同様に図1の紙面右方向はコネクタからの抜き取り方向であり、右側を「後」と定義する。さらに、図1の紙面上方向を「上」、紙面下方向を「下」と定義する。なお、以下の説明ではSDメモリカードを例として説明するが、本発明はSDメモリカードに限定されることはない。

【0011】

図1に示すように、SDメモリカード100の外装20は、上ケース1と下ケース2とによって形成される。

【0012】

外装20内には、不揮発性の半導体メモリ(例えばNAND型フラッシュメモリ)で形成された半導体メモリとしてのメモリパッケージ3a、3b、及びそれらを制御するメモリコントローラ12が実装された回路基板7が収容されている。SDメモリカード100の前方下部には、不図示の外部機器と電気的に接続され、メモリパッケージ3a、3bのデータを通常モードで入出力するための金端子6aと、メモリパッケージ3a、3bのデータを高速モードで入出力するための金端子6bとが形成されている。金端子6a、6bは、回路基板7の下側の表面の配線パターンの一部を露出させ、めっき加工を施して表面を金にしたものである。

【0013】

メモリパッケージ3a、3bは回路基板7の上面(上ケース1側)に実装されており、メモリパッケージ3a、3bを制御するメモリコントローラ12は、回路基板7の裏面(下ケース2側)であってメモリパッケージ3aの真下となる部分に実装されている。メモリコントローラ12は、回路基板7の金端子6a、6bと同じ面(下面)に接着材料によって搭載され、メモリコントローラ12の入出力パッドは回路基板7上のパッド部分にワイヤボンディングによって接続されている。これらの部分は樹脂ポッティング4によって封止されて保護されている。

【0014】

SDメモリカード100の前後方向中央の部分は、ホスト機器への着脱の際に曲げ応力やねじり応力等が作用しやすく、またメモリパッケージ3a、3bが存在していないために構造的に弱い部分でもある。樹脂ポッティング4は、この部分にかかるように設けられているためSDメモリカード100の剛性の低下は軽減されている。これにより、SDメモリカード100に曲げ応力が加わった際にクラックが発生することが防止される。

【0015】

メモリパッケージ3a、3bに格納するデータはメモリコントローラ12及び金端子6a、6bを介して不図示の外部機器(ホスト機器)とやり取りされる。回路基板7の裏面には、金端子6aのうちの電源及びグランド以外の各々の端子とメモリコントローラ12との間に配置される複数の抵抗素子5が搭載されている。ここで抵抗素子5は、例えば数[Ω]〜数10[Ω]の抵抗値を有する。抵抗素子5は、ダンピング抵抗として機能する。一方、回路基板7の表面には後述するコンデンサ10が複数個はんだ付けによって実装されている。

【0016】

また、上ケース1は、SDメモリカード100の仕様などを印刷したラベルを貼るためのラベル貼り付け溝8を備えている。

【0017】

図2は、下ケース2側を視点としたSDメモリカード100の外観を示す図である。なお、図1に示した断面構造は、本図におけるI−I線に沿った断面である。SDメモリカード100は、通常モード用として1〜9番ピン、高速モード用として10〜17番ピンを備えている。通常モード用の1〜9番ピンは、下ケース2の前方の端部近傍に形成した開口73において金端子6aを露出させたものであり、高速モード用の10〜17番ピンは下ケース2の開口73において金端子6bを露出させたものである。

【0018】

1〜9番ピンは、通常のSDメモリカードが備えるピンと同様の位置、形状、機能となっている。すなわち、1番ピンはDAT3(データ)、2番ピンにはCMD(コマンド)、3番ピンにはVSS1(グランド)、4番ピンにはVDD1(電源)、5番ピンにはCLK(クロック)、6番ピンにはVSS2(グランド)、7番ピンにはDAT0(データ)、8番ピンにはDAT1(データ)、9番ピンにはDAT2(データ)がそれぞれ割り当てられている。

【0019】

10〜17番ピンは、高速モードでのみ使用されるピンであり、10番ピンにはVSS3(グランド)、11番ピンにはD0+(差動データ+)、12番ピンにはD0−(差動データ−)、13番ピンにはVSS4(グランド)、14番ピンにはVDD2(電源)、15番ピンにはD1+(差動データ+)、16番ピンにはD1−(差動データ−)、17番ピンはVSS5(グランド)がそれぞれ割り当てられている。SDメモリカード100は、差動信号用として隣接するピンの対を二対(11番ピンと12番ピンとの対、15番ピンと16番ピンとの対)有する。11番ピンと12番ピンとの対は、VSS3とVSS4とで挟まれた配置となっており、15番ピンと16番ピンとの対は、VDD2が割り当てられた14番ピンとともにVSS4とVSS5とで挟まれた配置となっている。

【0020】

VDD1とVDD2とは、同じ電位であっても異なる電位であっても良い。また、VSS1〜VSS5は、同じ電位(GND)を想定しているが、高速モード用の作動データピンの両側のグランドは作動信号のシールドとして機能するため、実際には完全に同じ電位になるとは限らない。このため、便宜上VSS1〜VSS5として区別している。

【0021】

なお、1、2、5、7〜9番ピンからメモリコントローラ12用のボンディングパッド(後述するワイヤボンディングパッド14)に達する信号経路は、全てほぼ等しくされることが好ましい。なお、各信号経路の配線長が異なっても特性に支障が無い場合は、配線長が異なるように設計することも可能である。

【0022】

差動信号用のピン(11、12、15、16番ピン)をなす金端子6bは、通常モード用のデータピン(1、7〜9番ピン)をなす金端子6aよりも小さく形成されており、負荷容量を減少させたことで高速動作を実現しやすくなっている。なお、10〜17番ピンは、高速モードにおいてのみ使用されるため、差動信号用のピンをなす金端子6bを通常モード用のデータピンをなす金端子6aと比較して小さくしたとしても、従来のホスト機器(通常のSDカードのみに対応したホスト機器)との互換性は失われない。また、所望のデータ転送速度を実現できるのであれば、差動信号用のピンをなす金端子6bを通常モード用のデータピンをなす金端子6aと同じ大きさで形成することも可能である。

【0023】

差動信号用のピンの対は、各々1チャンネル分のデータ転送機能を備えており、SDメモリカード100は高速モード用として合計2チャンネル分のデータ転送機能を持っている。

【0024】

後段で説明するように、11、12、15、16番ピンから、高速モード用ボンディングパッド(後述する高速差動信号用ボンディングパッド13)に達する信号経路の各々は、全てほぼ等しくされる。なお、各信号経路の配線長が異なっても特性に支障が無い場合は、配線長が異なるように設計することも可能である。また、11番ピンに接続された配線と12番ピンに接続された配線とは、差動信号を効率よく伝送するために並行に配線を行う。同様に、15番ピンに接続された配線と16番ピンに接続された配線も並行に配線を行う。さらに、11番ピンから延びるD0+と12番ピンから延びるD0−との配線のペアは、10番ピンから延びるVSS3の配線と13番ピンから延びるVSS4の配線の間に配置する。同様に、15番ピンから延びるD1+と16番ピンから延びるD1−との配線のペアは、13番ピンから延びるVSS4の配線と17番ピンから延びるVSS5の配線の間に配置する。

【0025】

図3は、回路基板7の上面側の部品配置状態を示す図である。回路基板7の上面には、同じサイズのメモリパッケージ3a、3bが二つ並べて配置されている。メモリパッケージ3a、3bは、入出力ピン3cを用いて回路基板7にはんだ実装されている。回路基板7の上面周縁部にはコンデンサ10及びメモリパッケージ3a、3bの保護用のヒューズ11が複数個はんだ付けによって実装されている。コンデンサ10は、主として電源ノイズを低減して電源電圧を安定化するためのバイパスコンデンサ又はデカップリングコンデンサとして機能する。

【0026】

図4は、回路基板7の下面側の部品配置状態を示す図である。メモリコントローラ12は回路基板7の下面に設けられた高速差動信号用ボンディングパッド13及びワイヤボンディングパッド14にボンディングワイヤ15を介して接続され、樹脂ポッティング4で封止されている。また、回路基板7の下面には、メモリコントローラ12をテストするためテスト用パッド16が設けられており、メモリコントローラ12を回路基板7に実装した後で検査することが可能となっている。

【0027】

図5は、回路基板7の断面模式図である。本実施形態において、回路基板7は、上側から順にL1層50、L2層51、L3層52及びL4層53の四つの配線層を有する多層プリント基板を用いて構成されている。L1層50はソルダレジスト31で覆われており、開口32を介して配線パターンの一部が露出している。また、L4層53はソルダレジスト33で覆われており、開口34を介して配線パターンの一部が露出している。内層であるL2層51及びL3層52の配線パターンは露出していない。なお、以下の説明では四つの配線層を備えた回路基板7を例とするが、配線層の数はこれに限定されることはない。

【0028】

図6は、L1層50の配線パターンの一例を示す図である。なお、特徴を説明する上で不要な配線については図示を省略している。L1層50には、メモリパッケージ3a、3b各々の入出力ピンが電気的に接続されるメモリパッケージ実装用パッド17が複数設けられている。また、L1層50には、コンデンサ10及びヒューズ11の実装用にコンデンサ実装用パッド18及びヒューズ実装用パッド19も設けられている。L1層50には、配線が存在しない部分にはGND電位を持つCuプレーンがほぼ全面に設けられていてグランドプレーン20aを形成している。ただし、通常モードのデータピン及び信号用ピン(1、2、5、7〜9番ピン)をなす金端子6aに対応する部分には、グランドプレーン20aが存在しないグランドプレーン省略部20bを設けたレイアウトとなっている。金端子6a、6bが二列に配置されていることにより、金端子6aとメモリコントローラ12との距離が通常モード専用のSDメモリカードよりも長くなるが、通常モードのデータピン及び信号用ピンをなす金端子6aに対応する部分にグランドプレーン省略部20bが設けられているため、配線長の増加による信号特性の劣化を防止できる。また、L1層50には、後述するめっきリード29の一部をなす配線29aが形成されている。さらに、L1層50には、メモリパッケージ3a、3bやコンデンサ10などに電力を供給するために電源配線61が形成されている。

【0029】

図7は、L2層51の配線パターンの一例を示す図である。なお、特徴を説明する上で不要な配線については図示を省略している。配線が存在しない部分にはGND電位を持つCuプレーンがほぼ全面に設けられていてグランドプレーン21aを形成している。L1層50と同様にL2層51は、通常モードのデータピン及び信号用ピンをなす金端子6aに対応する部分には、グランドプレーン21aが存在しないグランドプレーン省略部21bを設けたレイアウトとなっている。さらに、L2層51は、抵抗素子5の実装箇所と対応する位置にもグランドプレーン21aが存在しないグランドプレーン省略部21cを設けたレイアウトとなっており、金端子6aとメモリコントローラ12との間の配線長の増加による信号特性の劣化を防止する効果を高めている。

【0030】

加えて、L2層51は、高速モードの差動信号用ピン(11、12、15、16番ピン)をなす金端子6bと対応する位置にもグランドプレーン21aが存在しないグランドプレーン省略部21dを設けたレイアウトとなっている。差動信号用ピンをなす金端子6bと対応する位置にもグランドプレーン省略部21dを設けたレイアウトとすることにより、グランドプレーン21aの容量による差動インピーダンスの低下を防止し、差動インピーダンスを他の差動配線部分と同様に保って高速信号伝送のためのインピーダンス整合を図る効果が得られる。さらに、L2層51には、メモリパッケージ3a、3bやコンデンサ10などに電力を供給するために電源配線62が形成されている。

【0031】

図8は、TDR法による差動インピーダンスの解析結果の一例を示す図であり、図8(a)は高速モードの差動信号用の金端子部分のグランドプレーンを省いた場合の解析結果、図8(b)は高速モードの差動信号用の金端子部分にもグランドプレーンを設けた場合の解析結果である。図8(a)、(b)においてホスト側から見た場合とは、メモリカードを挿入したコネクタとホスト装置との間でインピーダンスを測定した場合の測定結果であり、カード側から見た場合とは、高速差動信号用ボンディングパッド13の部分でインピーダンスを測定した場合の測定結果である。高速モードの差動信号用の金端子部分のグランドプレーンを省くことにより、カード側から見た場合、ホスト側から見た場合ともに差動インピーダンスの低下量は45Ω程度小さくなっており、インピーダンス特性が改善されていることが確認できる。

【0032】

また、図7に示すL2層51では、通常モード用の金端子6aに対応する部分のうち、データピン及び信号用ピン以外のピン(3、4、6番ピン)に対応する部分についてはフローティング電位の配線22が設けられている。3、4、6番ピンをなす金端子6aに対応する部分にフローティング電位の配線22を設けることにより、グランドプレーン21aを設ける場合よりも端子部分の容量を低減できる。また、3、4、6番ピンをなす金端子6aに対応する部分の配線を無くしてしまうと、回路基板7の断面方向で層構成がアンバランスとなり、回路基板7の厚さにばらつきが生じたり、回路基板7の反りが大きくなったりするが、フローティング電位の配線22を設けることによって、これらの問題を回避できる。

【0033】

図9は、L3層52の配線パターンの一例を示す図である。なお、特徴を説明する上で不要な配線については図示を省略している。グランドプレーン省略部23b〜23dを設けてグランドプレーン23aの一部を省くことと、フローティング電位の配線24を設けることについては図7に示したL2層51と同様である。加えて、L3層52には、後述するL4層53に形成される高速差動信号配線27の近傍領域と断面方向に隣接するように高速モード用のグランドプレーン25が設けられる。高速モード用のグランドプレーン25は、グランドプレーン23aとは電気的に分離されている。このため、高速モードの差動信号に周辺の電源・GNDのノイズの影響が及ぶことは防止される。なお、ここでは差動信号用以外の高速モード用ピン(10、13、14、17番ピン)に対応する部分にも高速モード用のグランドプレーン25を設けているが、少なくとも高速差動信号配線27の近傍領域に対応する部分に設けられていれば良い。さらに、L3層51には、メモリパッケージ3a、3bやコンデンサ10などに電力を供給するために電源配線63が形成されている。

【0034】

図10は、L4層53の配線パターンの一例を示す図である。配線が存在しない部分にはGND電位を持つCuプレーンがほぼ全面に設けられていてグランドプレーン26を形成している。金端子6a及び金端子6bの各々に対応する位置には、基となる端子パターン54、55が形成されている。高速モードの差動信号用のピン(11、12、15、16番ピン)をなす金端子6bの基となる端子パターン55の対とメモリコントローラ12の実装用の高速差動信号用ボンディングパッド13とを結ぶ一対の配線(高速差動信号配線27)は、二対ともに2本の配線が互いに平行かつ等長であり、可能な限り短く形成されている。高速差動信号配線27の両脇には、シールドとなるシールドGND配線28が高速差動信号配線27に沿って形成されている。このため、高速差動信号配線27はスルーホールを介して他の配線層を経由することなく、L4層53のみに配線されている。高速差動信号配線27は、均一の差動インピーダンスを保つように、高速モードの差動信号用のピンをなす金端子6bの基となる端子パターン55と高速差動信号用ボンディングパッド13との間を接続している。

【0035】

また、L4層53には、メモリコントローラ12をワイヤボンディング15で接続するためのワイヤボンディングパッド14が設けられている。さらに、金端子6bの基となる端子パターン55と高速差動信号用ボンディングパッド13とに電解金めっきを施すための後述するめっきリード29の一部をなす配線29bが回路基板7の外周部に向かって配線されている。さらに、L4層53には、抵抗素子5の実装用に抵抗素子実装用パッド30も設けられている。

【0036】

図11は、回路基板7の上側表面に設けられるソルダレジスト31の開口状態を示す図である。ソルダレジスト31は、メモリパッケージ実装用パッド17に対応する開口32a、コンデンサ実装用パッド18に対応する開口32b、ヒューズ実装用パッド19に対応する開口32cに加えて、配線29aの途中に当たる部分にも開口32dが設けられている。

【0037】

図12は、回路基板7の下側表面に設けられるソルダレジスト33の開口状態を示す図である。ソルダレジスト33は、金端子6aに対応する開口34a、金端子6bに対応する開口34b、抵抗素子5に対応する開口34c、高速差動信号用ボンディングパッド13に対応する開口34d、ワイヤボンディングパッド14に対応する開口34e、テスト用パッド16に対応する開口34fが設けられる。

【0038】

図13は、高速差動信号用の金端子及び高速差動信号用のメモリコントローラワイヤボンディングパッドに電解金めっきを施すためのめっきリードの配線状態を示す図である。図13においては、L1層50の配線29aとL4層53の配線29bとを一つの図に示すことでめっきリード29全体を表している。めっきリード29は分岐配線として形成することになるため、特に高速差動信号配線27においては、めっきリード29で反射した信号がノイズとなって差動信号に重畳し、高速動作時の不具合の原因となる。このため、上記のように本実施形態では、金端子6bの基となる端子パターン55と高速差動信号用ボンディングパッド13とに電解金めっきを施した後に開口32dの部分で配線29aをカットすることによって、SDメモリカード100の完成状態におけるめっきリード29の分岐配線としての長さを短くし、反射ノイズの影響を低減している。

【0039】

高速差動信号配線27の両脇にはシールドGND配線28が設けられているため、同一の配線層内(L4層53内)だけでめっきリード29を分岐させることができない。したがって、ペアとなった差動信号用の2本の配線の各々の途中にスルーホールを設け、他の配線層を利用して立体的にシールドGND配線28と交差するようにめっきリード29を分岐させている。図13に示す構成においては、L4層53からスルーホール35によってL1層50にめっきリード29を導いている。L1層50に形成した配線29aによってシールドGND配線28と立体的に交差しためっきリード29は、スルーホール36によってL4層53に導かれ、L4層53に形成された配線29bによって回路基板7の外周部まで延在している。

【0040】

反射ノイズを低減するためには、めっきリード29をスルーホール35に近い位置、すなわち回路基板7の周縁部ではなく基板面内で切断することが有効であるため、本実施形態では、上述のようにソルダレジスト31の開口32dの部分において配線29aを切断している。

【0041】

なお、シールドGND配線28は、高速差動信号用ボンディングパッド13から配線とは逆方向にめっきリード37が設けられており、スルーホール38を介して他の配線層へ導かれて回路基板7の周縁部において切断されている。

【0042】

図14は、信号受信端での波形アイパターンを示す図である。図14(a)はめっきリード29をカットした場合のアイパターンを示し、図14(b)はめっきリード29をカットしていない場合のアイパターンを示す。両者を比較すると、めっきリード29をカットしていない場合はめっきリード29をカットした場合と比較してジッタが大きく、立ち上がり時間や立ち下がり時間は長くなっている。また、めっきリード29をカットしていない場合は信号のバラツキやノイズが大きいのに対し、めっきリード29をカットすることによりこれらが改善されている。これにより、めっきリード29をカットすることにより、高速差動信号配線27における信号の劣化を低減できることが確認できる。

【0043】

図15は、回路基板7の製造工程を示す図である。まず、内層(L2層51、L3層52)用銅張積層板を所定のパネル寸法に切断する(ステップS1)。そして、所定の寸法に切断した内層用銅張積層板の両面にドライフィルム(エッチングレジスト)をラミネートする(ステップS2)。その後、L2層51、L3層52用の配線パターンをドライフィルムに焼き付ける。パターン以外の不要部分を除去してパターン形成用レジストとし、エッチングによってパターン以外の部分の銅箔を除去してグランドプレーン21a、23a、25や各種配線、グランドプレーン省略部21b〜21d、23b〜23dなどを形成する。さらに、残ったパターン形成用レジストを剥離してパターン形成済の内層基板を得る(ステップS3)。

【0044】

パターン形成済の内層基板と外層用銅張積層板とをプリプレグを用いた積層プレスによって接着する(ステップS4)。得られた積層体に貫通スルーホールやビアホール、取り付け穴などの穴あけ加工を施す(ステップS5)。そして、貫通スルーホールの穴内部に銅めっき加工を施し、外層(L1層50、L4層53)及び内層(L2層51、L3層52)の銅箔面を電気的に接続する(ステップS6)。その後、積層体の両面(外層用銅張積層板の表面)にドライフィルム(エッチングレジスト)をラミネートする(ステップS7)。その後、L1層50、L4層53用の配線パターンをドライフィルムに焼き付ける。パターン以外の不要部分を除去してパターン形成用レジストとし、エッチングによってパターン以外の部分の銅箔を除去して、グランドプレーン20a、26、高速差動信号配線27、シールドGND配線28、めっきリード29などの各種配線やグランドプレーン省略部20bなどを形成する。さらに、残ったパターン形成用レジストを剥離してパターン形成済の積層体を得る(ステップS8)。

【0045】

次に、パターン形成済の積層体に両面にカーテンコート方式などの方法でレジスト液を塗布し、乾燥させてソルダレジスト31、33を形成する(ステップS9)。そして、最終的にソルダレジスト31、33を除去する部分(開口32a〜32d、34a〜34fなど)以外の部分をUV露光により硬化させた上で、未硬化部分を除去し、L1層50及びL4層53の銅箔面を部分的に露出させる(ステップS10)。さらに、銅箔面を部分的に露出させたL1層50及びL4層53の上にめっきマスク用レジスト層を形成し、めっき加工を施す部分(金端子6a、6b、高速差動信号用ボンディングパッド13、ワイヤボンディングパッド14)以外の部分を露光によって硬化させた上で、未硬化部分を除去しめっき加工を施す部分のみを露出させた上で、めっきマスク用レジスト層を除去する(ステップS11)。そして、めっき加工を施す部分に下地めっきとして電解ニッケルめっき加工を施し、さらに電解金めっき加工を施す(ステップS12)。めっき加工が完了した後、めっきリード切断用のエッチングレジストを形成して開口32d以外の部分を覆い、ソルダレジスト31に設けた開口32dにおいて露出しているめっきリード29(配線29a)をエッチングによって切断した上でエッチングレジストを除去する(ステップS13)。その後、ルーター加工により所定の外形に切り出して回路基板7が完成する(ステップS14)。

【0046】

上記の手順で作成した回路基板7は、めっきリード29が回路基板7の面内で切断されているため、めっきリード29で反射した信号がノイズとなって差動信号を劣化させることを抑えることができる。また、高速モードの差動信号用の金端子6bに対応する位置にグランドプレーン省略部21c、23cを備えるため、高速差動信号配線27の差動インピーダンスの低下を抑え、差動信号の劣化を防止できる。さらに、高速差動信号配線27専用のグランドプレーン25を有するため、他の信号の影響を受けて差動信号が劣化することを防止できる。

【0047】

SDメモリカード100を高速モードで動作させる場合には、1〜9番ピンのうち、VSS1(3番ピン)、VSS2(6番ピン)及びVDD1(4番ピン)以外のピンについては、通常モードでの機能を無効とする。そして、7番ピンと8番ピンとについては、通常モードとは異なる機能を割り当て、高速動作用の差動クロックCLK+、CLK−として使用する。したがって、1番ピン、2番ピン、5番ピン及び9番ピンについては、高速モード時は機能を停止したままであり、使用されない。なお、差動クロックCLK+、CLK−の周波数は最大で150MHzであるため、通常モード用である7、8番ピンを用いてもデータ転送速度の高速化の妨げとなることはない。通常モード用として既存のピンを用いてCLK+、CLK−を転送することにより、回路基板7上にこれらの転送用の端子を新たに設ける必要が無くなるため、配線レイアウト上の制約が低減される。

【0048】

そして、差動データピンD0±(11番、12番)によるチャンネルと差動データピンD1±(15番、16番)によるチャンネルとで、CLK±に基づいて1チャンネルあたり1.5Gbpsデータを転送し、合わせて300Mbyte/secのデータ転送速度を実現する。

【0049】

本実施形態に係るSDメモリカード100は、高速差動信号が回路基板7上で劣化することを抑制できるため、メモリパッケージ3a、3bに対するデータの入出力速度、すなわちデータ転送速度の高速化を実現可能である。

【0050】

(第2の実施形態)

図16は、第2の実施形態の半導体メモリカードを適用したSDメモリカードの高速差動信号用の金端子及び高速差動信号用のメモリコントローラワイヤボンディングパッドに電解金めっきを施すためのめっきリードを示す図である。

【0051】

両脇にシールドGND配線28を有する高速差動信号配線27は、途中で分岐することなく高速差動信号用ボンディングパッド13まで達している。高速差動信号用ボンディングパッド13からは、別方向に向かってめっきリード29をなす配線29cが引き出されている。L4層53上のソルダレジスト33に設けられた開口部34gと重なる位置で配線29cは切断されている。

【0052】

本実施形態では、めっきリード29の分岐配線としての長さは第1の実施形態と比較して長くなるが、高速差動信号配線27の途中においてスルーホールを介して分岐配線を設ける必要がないため、スルーホール部分でインピーダンス不整合が生じて信号に反射ノイズが生じることを防止できる。

【0053】

めっきリード29以外の部分の構成については第1の実施形態と同様であるため、重複する説明は割愛する。

【0054】

上記第1、第2の実施形態においては、最もノイズの影響を受けやすい差動信号配線のみめっきリードを切断しているが、他の配線のめっきリードに関しても、同様に回路基板の面内で切断することが可能であり、反射ノイズや外部からのノイズの侵入を防ぐことができる。

【0055】

また、上記第1、第2の実施形態において、配線が存在しない部分がグランドプレーンとなっている構成を例としたが、グランドプレーンとなっている部分の一部をVDD1又はVDD2電位のCuプレーンとすることも可能であり、GNDだけでなくVDDの電位を安定化させるのに効果的である。

【0056】

さらに、上記第1、第2の実施形態では、VDD1及びVDD2の二つの電源電位を有する構成としたが、動作させるIC(メモリコントローラ及びメモリパッケージ)の仕様に応じて、VDD3やVDD4などの複数の別の電源電位を持つ配線やCuプレーンを設けることも可能である。

【0057】

また、上記第1、第2の実施形態では、高速差動信号用の金端子に対応する部分のグランドプレーンを省き、高速差動信号配線に対応する領域に専用のグランドプレーンを設け、かつ高速差動信号配線のめっきリードを回路基板の面内で切断した構成を例としたが、これらを全て兼ね備えている必要はなく、これらの少なくとも一つを満たす構成として実施することも可能である。上記の三つのうち少なくとも一つを満たすことで、高速モード用の差動信号が回路基板上で劣化することを防止する効果が得られる。

【0058】

また、上記第1、第2の実施形態における部品の配置や基板レイアウトはあくまでも一例であり、本発明はこれらに限定されることはない。

【0059】

また、上記各実施形態においては、通常モード用のピンの一部を高速モードでは別の機能に切り換えて使用する構成を例としたが、全ての通常モード用のピンが通常モード専用であってもよい。

【0060】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0061】

3a、3b メモリパッケージ、6a、6b 金端子、7 回路基板、12 メモリコントローラ、13 高速差動信号用ボンディングパッド、21a、23a、25 グランドプレーン、27 高速差動信号配線、29めっきリード、54、55 金端子の基となる端子パターン、100 SDメモリカード。

【技術分野】

【0001】

本発明の実施形態は、半導体メモリカード及びその製造方法に関する。

【背景技術】

【0002】

近年、例えばNANDフラッシュメモリなどの半導体メモリを用いたメモリカードは、連続撮影した静止画像や高解像度の動画像の記録といった用途にも用いられており、これらの用途においては短時間に多くの情報を読み出したり書き込んだりすること、即ちデータ転送速度の高速化が求められている。一例としては、300MB/secのデータ転送速度を実現することが求められている。

【0003】

旧来のSDTMメモリカード(以下、SDメモリカードと表記する。)は、データ転送速度が高々20MB/sec程度であるため、通常の動作モード(通常モード)とは別に、これよりも高速に情報を読み書き可能な動作モード(高速モード)でも使用可能とすることで、通常のホスト機器との互換性を保ちつつ高速度のデータ転送を可能とすることが提案されている。

【0004】

半導体メモリカードにおいてデータ転送速度の高速化を実現するためには、半導体メモリを搭載する基板上においてデータ信号の劣化を防止する必要がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2005−84935号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

一つの実施形態は、半導体メモリを搭載する基板上においてデータ信号の劣化を防止した半導体メモリカード及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の一つの実施形態によれば、半導体メモリと、通常モード及び通常モードよりもデータ転送速度が速い高速モードの両方での半導体メモリへのデータの読み書きを制御するメモリコントローラと、少なくとも一つの内層を有する多層プリント基板に半導体メモリ及びメモリコントローラを表裏に分けて実装した回路基板とを備える。回路基板は、メモリコントローラと外部機器との間での高速モードによるデータ入出力用としてメモリコントローラの実装面に設けられ、金めっき加工が施された高速モード用の金端子と、高速モード用の金端子とメモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線と、高速差動信号配線から分岐し、回路基板の面内において高速差動信号配線との分岐点の近傍で切断された金めっき加工用のめっきリードを有する。

【図面の簡単な説明】

【0008】

【図1】図1は、第1の実施形態の半導体メモリカードを適用したSDメモリカードの構成を模式的に示す図。

【図2】図2は、下ケース側を視点としたSDメモリカードの外観を示す図。

【図3】図3は、回路基板の上面側の部品配置状態を示す図。

【図4】図4は、回路基板の下面側の部品配置状態を示す図。

【図5】図5は、回路基板の断面模式図。

【図6】図6は、L1層の配線パターンの一例を示す図。

【図7】図7は、L2層の配線パターンの一例を示す図。

【図8】図8は、TDR法による差動インピーダンスの解析結果の一例を示す図。

【図9】図9は、L3層の配線パターンの一例を示す図。

【図10】図10は、L4層の配線パターンの一例を示す図。

【図11】図11は、回路基板の上側表面に設けられるソルダレジストの開口状態を示す図。

【図12】図12は、回路基板の下側表面に設けられるソルダレジストの開口状態を示す図。

【図13】図13は、高速差動信号用の金端子及び高速差動信号用のメモリコントローラワイヤボンディングパッドに電解金めっきを施すためのめっきリードの配線状態を示す図。

【図14】図14は、信号受信端での波形アイパターンを示す図。

【図15】図15は、回路基板の製造工程を示す図。

【図16】図16は、第2の実施形態の半導体メモリカードを適用したSDメモリカードの高速差動信号用の金端子及び高速差動信号用のメモリコントローラワイヤボンディングパッドに電解金めっきを施すためのめっきリードを示す図。

【発明を実施するための形態】

【0009】

以下に添付図面を参照して、実施形態にかかる半導体メモリカード及びその製造方法を詳細に説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0010】

(第1の実施形態)

図1は、第1の実施形態の半導体メモリカードを適用したSDメモリカードの構成を模式的に示す断面図である。ここで、図1の紙面における左方向はコネクタへの挿入方向であり、左側を「前」と定義する。同様に図1の紙面右方向はコネクタからの抜き取り方向であり、右側を「後」と定義する。さらに、図1の紙面上方向を「上」、紙面下方向を「下」と定義する。なお、以下の説明ではSDメモリカードを例として説明するが、本発明はSDメモリカードに限定されることはない。

【0011】

図1に示すように、SDメモリカード100の外装20は、上ケース1と下ケース2とによって形成される。

【0012】

外装20内には、不揮発性の半導体メモリ(例えばNAND型フラッシュメモリ)で形成された半導体メモリとしてのメモリパッケージ3a、3b、及びそれらを制御するメモリコントローラ12が実装された回路基板7が収容されている。SDメモリカード100の前方下部には、不図示の外部機器と電気的に接続され、メモリパッケージ3a、3bのデータを通常モードで入出力するための金端子6aと、メモリパッケージ3a、3bのデータを高速モードで入出力するための金端子6bとが形成されている。金端子6a、6bは、回路基板7の下側の表面の配線パターンの一部を露出させ、めっき加工を施して表面を金にしたものである。

【0013】

メモリパッケージ3a、3bは回路基板7の上面(上ケース1側)に実装されており、メモリパッケージ3a、3bを制御するメモリコントローラ12は、回路基板7の裏面(下ケース2側)であってメモリパッケージ3aの真下となる部分に実装されている。メモリコントローラ12は、回路基板7の金端子6a、6bと同じ面(下面)に接着材料によって搭載され、メモリコントローラ12の入出力パッドは回路基板7上のパッド部分にワイヤボンディングによって接続されている。これらの部分は樹脂ポッティング4によって封止されて保護されている。

【0014】

SDメモリカード100の前後方向中央の部分は、ホスト機器への着脱の際に曲げ応力やねじり応力等が作用しやすく、またメモリパッケージ3a、3bが存在していないために構造的に弱い部分でもある。樹脂ポッティング4は、この部分にかかるように設けられているためSDメモリカード100の剛性の低下は軽減されている。これにより、SDメモリカード100に曲げ応力が加わった際にクラックが発生することが防止される。

【0015】

メモリパッケージ3a、3bに格納するデータはメモリコントローラ12及び金端子6a、6bを介して不図示の外部機器(ホスト機器)とやり取りされる。回路基板7の裏面には、金端子6aのうちの電源及びグランド以外の各々の端子とメモリコントローラ12との間に配置される複数の抵抗素子5が搭載されている。ここで抵抗素子5は、例えば数[Ω]〜数10[Ω]の抵抗値を有する。抵抗素子5は、ダンピング抵抗として機能する。一方、回路基板7の表面には後述するコンデンサ10が複数個はんだ付けによって実装されている。

【0016】

また、上ケース1は、SDメモリカード100の仕様などを印刷したラベルを貼るためのラベル貼り付け溝8を備えている。

【0017】

図2は、下ケース2側を視点としたSDメモリカード100の外観を示す図である。なお、図1に示した断面構造は、本図におけるI−I線に沿った断面である。SDメモリカード100は、通常モード用として1〜9番ピン、高速モード用として10〜17番ピンを備えている。通常モード用の1〜9番ピンは、下ケース2の前方の端部近傍に形成した開口73において金端子6aを露出させたものであり、高速モード用の10〜17番ピンは下ケース2の開口73において金端子6bを露出させたものである。

【0018】

1〜9番ピンは、通常のSDメモリカードが備えるピンと同様の位置、形状、機能となっている。すなわち、1番ピンはDAT3(データ)、2番ピンにはCMD(コマンド)、3番ピンにはVSS1(グランド)、4番ピンにはVDD1(電源)、5番ピンにはCLK(クロック)、6番ピンにはVSS2(グランド)、7番ピンにはDAT0(データ)、8番ピンにはDAT1(データ)、9番ピンにはDAT2(データ)がそれぞれ割り当てられている。

【0019】

10〜17番ピンは、高速モードでのみ使用されるピンであり、10番ピンにはVSS3(グランド)、11番ピンにはD0+(差動データ+)、12番ピンにはD0−(差動データ−)、13番ピンにはVSS4(グランド)、14番ピンにはVDD2(電源)、15番ピンにはD1+(差動データ+)、16番ピンにはD1−(差動データ−)、17番ピンはVSS5(グランド)がそれぞれ割り当てられている。SDメモリカード100は、差動信号用として隣接するピンの対を二対(11番ピンと12番ピンとの対、15番ピンと16番ピンとの対)有する。11番ピンと12番ピンとの対は、VSS3とVSS4とで挟まれた配置となっており、15番ピンと16番ピンとの対は、VDD2が割り当てられた14番ピンとともにVSS4とVSS5とで挟まれた配置となっている。

【0020】

VDD1とVDD2とは、同じ電位であっても異なる電位であっても良い。また、VSS1〜VSS5は、同じ電位(GND)を想定しているが、高速モード用の作動データピンの両側のグランドは作動信号のシールドとして機能するため、実際には完全に同じ電位になるとは限らない。このため、便宜上VSS1〜VSS5として区別している。

【0021】

なお、1、2、5、7〜9番ピンからメモリコントローラ12用のボンディングパッド(後述するワイヤボンディングパッド14)に達する信号経路は、全てほぼ等しくされることが好ましい。なお、各信号経路の配線長が異なっても特性に支障が無い場合は、配線長が異なるように設計することも可能である。

【0022】

差動信号用のピン(11、12、15、16番ピン)をなす金端子6bは、通常モード用のデータピン(1、7〜9番ピン)をなす金端子6aよりも小さく形成されており、負荷容量を減少させたことで高速動作を実現しやすくなっている。なお、10〜17番ピンは、高速モードにおいてのみ使用されるため、差動信号用のピンをなす金端子6bを通常モード用のデータピンをなす金端子6aと比較して小さくしたとしても、従来のホスト機器(通常のSDカードのみに対応したホスト機器)との互換性は失われない。また、所望のデータ転送速度を実現できるのであれば、差動信号用のピンをなす金端子6bを通常モード用のデータピンをなす金端子6aと同じ大きさで形成することも可能である。

【0023】

差動信号用のピンの対は、各々1チャンネル分のデータ転送機能を備えており、SDメモリカード100は高速モード用として合計2チャンネル分のデータ転送機能を持っている。

【0024】

後段で説明するように、11、12、15、16番ピンから、高速モード用ボンディングパッド(後述する高速差動信号用ボンディングパッド13)に達する信号経路の各々は、全てほぼ等しくされる。なお、各信号経路の配線長が異なっても特性に支障が無い場合は、配線長が異なるように設計することも可能である。また、11番ピンに接続された配線と12番ピンに接続された配線とは、差動信号を効率よく伝送するために並行に配線を行う。同様に、15番ピンに接続された配線と16番ピンに接続された配線も並行に配線を行う。さらに、11番ピンから延びるD0+と12番ピンから延びるD0−との配線のペアは、10番ピンから延びるVSS3の配線と13番ピンから延びるVSS4の配線の間に配置する。同様に、15番ピンから延びるD1+と16番ピンから延びるD1−との配線のペアは、13番ピンから延びるVSS4の配線と17番ピンから延びるVSS5の配線の間に配置する。

【0025】

図3は、回路基板7の上面側の部品配置状態を示す図である。回路基板7の上面には、同じサイズのメモリパッケージ3a、3bが二つ並べて配置されている。メモリパッケージ3a、3bは、入出力ピン3cを用いて回路基板7にはんだ実装されている。回路基板7の上面周縁部にはコンデンサ10及びメモリパッケージ3a、3bの保護用のヒューズ11が複数個はんだ付けによって実装されている。コンデンサ10は、主として電源ノイズを低減して電源電圧を安定化するためのバイパスコンデンサ又はデカップリングコンデンサとして機能する。

【0026】

図4は、回路基板7の下面側の部品配置状態を示す図である。メモリコントローラ12は回路基板7の下面に設けられた高速差動信号用ボンディングパッド13及びワイヤボンディングパッド14にボンディングワイヤ15を介して接続され、樹脂ポッティング4で封止されている。また、回路基板7の下面には、メモリコントローラ12をテストするためテスト用パッド16が設けられており、メモリコントローラ12を回路基板7に実装した後で検査することが可能となっている。

【0027】

図5は、回路基板7の断面模式図である。本実施形態において、回路基板7は、上側から順にL1層50、L2層51、L3層52及びL4層53の四つの配線層を有する多層プリント基板を用いて構成されている。L1層50はソルダレジスト31で覆われており、開口32を介して配線パターンの一部が露出している。また、L4層53はソルダレジスト33で覆われており、開口34を介して配線パターンの一部が露出している。内層であるL2層51及びL3層52の配線パターンは露出していない。なお、以下の説明では四つの配線層を備えた回路基板7を例とするが、配線層の数はこれに限定されることはない。

【0028】

図6は、L1層50の配線パターンの一例を示す図である。なお、特徴を説明する上で不要な配線については図示を省略している。L1層50には、メモリパッケージ3a、3b各々の入出力ピンが電気的に接続されるメモリパッケージ実装用パッド17が複数設けられている。また、L1層50には、コンデンサ10及びヒューズ11の実装用にコンデンサ実装用パッド18及びヒューズ実装用パッド19も設けられている。L1層50には、配線が存在しない部分にはGND電位を持つCuプレーンがほぼ全面に設けられていてグランドプレーン20aを形成している。ただし、通常モードのデータピン及び信号用ピン(1、2、5、7〜9番ピン)をなす金端子6aに対応する部分には、グランドプレーン20aが存在しないグランドプレーン省略部20bを設けたレイアウトとなっている。金端子6a、6bが二列に配置されていることにより、金端子6aとメモリコントローラ12との距離が通常モード専用のSDメモリカードよりも長くなるが、通常モードのデータピン及び信号用ピンをなす金端子6aに対応する部分にグランドプレーン省略部20bが設けられているため、配線長の増加による信号特性の劣化を防止できる。また、L1層50には、後述するめっきリード29の一部をなす配線29aが形成されている。さらに、L1層50には、メモリパッケージ3a、3bやコンデンサ10などに電力を供給するために電源配線61が形成されている。

【0029】

図7は、L2層51の配線パターンの一例を示す図である。なお、特徴を説明する上で不要な配線については図示を省略している。配線が存在しない部分にはGND電位を持つCuプレーンがほぼ全面に設けられていてグランドプレーン21aを形成している。L1層50と同様にL2層51は、通常モードのデータピン及び信号用ピンをなす金端子6aに対応する部分には、グランドプレーン21aが存在しないグランドプレーン省略部21bを設けたレイアウトとなっている。さらに、L2層51は、抵抗素子5の実装箇所と対応する位置にもグランドプレーン21aが存在しないグランドプレーン省略部21cを設けたレイアウトとなっており、金端子6aとメモリコントローラ12との間の配線長の増加による信号特性の劣化を防止する効果を高めている。

【0030】

加えて、L2層51は、高速モードの差動信号用ピン(11、12、15、16番ピン)をなす金端子6bと対応する位置にもグランドプレーン21aが存在しないグランドプレーン省略部21dを設けたレイアウトとなっている。差動信号用ピンをなす金端子6bと対応する位置にもグランドプレーン省略部21dを設けたレイアウトとすることにより、グランドプレーン21aの容量による差動インピーダンスの低下を防止し、差動インピーダンスを他の差動配線部分と同様に保って高速信号伝送のためのインピーダンス整合を図る効果が得られる。さらに、L2層51には、メモリパッケージ3a、3bやコンデンサ10などに電力を供給するために電源配線62が形成されている。

【0031】

図8は、TDR法による差動インピーダンスの解析結果の一例を示す図であり、図8(a)は高速モードの差動信号用の金端子部分のグランドプレーンを省いた場合の解析結果、図8(b)は高速モードの差動信号用の金端子部分にもグランドプレーンを設けた場合の解析結果である。図8(a)、(b)においてホスト側から見た場合とは、メモリカードを挿入したコネクタとホスト装置との間でインピーダンスを測定した場合の測定結果であり、カード側から見た場合とは、高速差動信号用ボンディングパッド13の部分でインピーダンスを測定した場合の測定結果である。高速モードの差動信号用の金端子部分のグランドプレーンを省くことにより、カード側から見た場合、ホスト側から見た場合ともに差動インピーダンスの低下量は45Ω程度小さくなっており、インピーダンス特性が改善されていることが確認できる。

【0032】

また、図7に示すL2層51では、通常モード用の金端子6aに対応する部分のうち、データピン及び信号用ピン以外のピン(3、4、6番ピン)に対応する部分についてはフローティング電位の配線22が設けられている。3、4、6番ピンをなす金端子6aに対応する部分にフローティング電位の配線22を設けることにより、グランドプレーン21aを設ける場合よりも端子部分の容量を低減できる。また、3、4、6番ピンをなす金端子6aに対応する部分の配線を無くしてしまうと、回路基板7の断面方向で層構成がアンバランスとなり、回路基板7の厚さにばらつきが生じたり、回路基板7の反りが大きくなったりするが、フローティング電位の配線22を設けることによって、これらの問題を回避できる。

【0033】

図9は、L3層52の配線パターンの一例を示す図である。なお、特徴を説明する上で不要な配線については図示を省略している。グランドプレーン省略部23b〜23dを設けてグランドプレーン23aの一部を省くことと、フローティング電位の配線24を設けることについては図7に示したL2層51と同様である。加えて、L3層52には、後述するL4層53に形成される高速差動信号配線27の近傍領域と断面方向に隣接するように高速モード用のグランドプレーン25が設けられる。高速モード用のグランドプレーン25は、グランドプレーン23aとは電気的に分離されている。このため、高速モードの差動信号に周辺の電源・GNDのノイズの影響が及ぶことは防止される。なお、ここでは差動信号用以外の高速モード用ピン(10、13、14、17番ピン)に対応する部分にも高速モード用のグランドプレーン25を設けているが、少なくとも高速差動信号配線27の近傍領域に対応する部分に設けられていれば良い。さらに、L3層51には、メモリパッケージ3a、3bやコンデンサ10などに電力を供給するために電源配線63が形成されている。

【0034】

図10は、L4層53の配線パターンの一例を示す図である。配線が存在しない部分にはGND電位を持つCuプレーンがほぼ全面に設けられていてグランドプレーン26を形成している。金端子6a及び金端子6bの各々に対応する位置には、基となる端子パターン54、55が形成されている。高速モードの差動信号用のピン(11、12、15、16番ピン)をなす金端子6bの基となる端子パターン55の対とメモリコントローラ12の実装用の高速差動信号用ボンディングパッド13とを結ぶ一対の配線(高速差動信号配線27)は、二対ともに2本の配線が互いに平行かつ等長であり、可能な限り短く形成されている。高速差動信号配線27の両脇には、シールドとなるシールドGND配線28が高速差動信号配線27に沿って形成されている。このため、高速差動信号配線27はスルーホールを介して他の配線層を経由することなく、L4層53のみに配線されている。高速差動信号配線27は、均一の差動インピーダンスを保つように、高速モードの差動信号用のピンをなす金端子6bの基となる端子パターン55と高速差動信号用ボンディングパッド13との間を接続している。

【0035】

また、L4層53には、メモリコントローラ12をワイヤボンディング15で接続するためのワイヤボンディングパッド14が設けられている。さらに、金端子6bの基となる端子パターン55と高速差動信号用ボンディングパッド13とに電解金めっきを施すための後述するめっきリード29の一部をなす配線29bが回路基板7の外周部に向かって配線されている。さらに、L4層53には、抵抗素子5の実装用に抵抗素子実装用パッド30も設けられている。

【0036】

図11は、回路基板7の上側表面に設けられるソルダレジスト31の開口状態を示す図である。ソルダレジスト31は、メモリパッケージ実装用パッド17に対応する開口32a、コンデンサ実装用パッド18に対応する開口32b、ヒューズ実装用パッド19に対応する開口32cに加えて、配線29aの途中に当たる部分にも開口32dが設けられている。

【0037】

図12は、回路基板7の下側表面に設けられるソルダレジスト33の開口状態を示す図である。ソルダレジスト33は、金端子6aに対応する開口34a、金端子6bに対応する開口34b、抵抗素子5に対応する開口34c、高速差動信号用ボンディングパッド13に対応する開口34d、ワイヤボンディングパッド14に対応する開口34e、テスト用パッド16に対応する開口34fが設けられる。

【0038】

図13は、高速差動信号用の金端子及び高速差動信号用のメモリコントローラワイヤボンディングパッドに電解金めっきを施すためのめっきリードの配線状態を示す図である。図13においては、L1層50の配線29aとL4層53の配線29bとを一つの図に示すことでめっきリード29全体を表している。めっきリード29は分岐配線として形成することになるため、特に高速差動信号配線27においては、めっきリード29で反射した信号がノイズとなって差動信号に重畳し、高速動作時の不具合の原因となる。このため、上記のように本実施形態では、金端子6bの基となる端子パターン55と高速差動信号用ボンディングパッド13とに電解金めっきを施した後に開口32dの部分で配線29aをカットすることによって、SDメモリカード100の完成状態におけるめっきリード29の分岐配線としての長さを短くし、反射ノイズの影響を低減している。

【0039】

高速差動信号配線27の両脇にはシールドGND配線28が設けられているため、同一の配線層内(L4層53内)だけでめっきリード29を分岐させることができない。したがって、ペアとなった差動信号用の2本の配線の各々の途中にスルーホールを設け、他の配線層を利用して立体的にシールドGND配線28と交差するようにめっきリード29を分岐させている。図13に示す構成においては、L4層53からスルーホール35によってL1層50にめっきリード29を導いている。L1層50に形成した配線29aによってシールドGND配線28と立体的に交差しためっきリード29は、スルーホール36によってL4層53に導かれ、L4層53に形成された配線29bによって回路基板7の外周部まで延在している。

【0040】

反射ノイズを低減するためには、めっきリード29をスルーホール35に近い位置、すなわち回路基板7の周縁部ではなく基板面内で切断することが有効であるため、本実施形態では、上述のようにソルダレジスト31の開口32dの部分において配線29aを切断している。

【0041】

なお、シールドGND配線28は、高速差動信号用ボンディングパッド13から配線とは逆方向にめっきリード37が設けられており、スルーホール38を介して他の配線層へ導かれて回路基板7の周縁部において切断されている。

【0042】

図14は、信号受信端での波形アイパターンを示す図である。図14(a)はめっきリード29をカットした場合のアイパターンを示し、図14(b)はめっきリード29をカットしていない場合のアイパターンを示す。両者を比較すると、めっきリード29をカットしていない場合はめっきリード29をカットした場合と比較してジッタが大きく、立ち上がり時間や立ち下がり時間は長くなっている。また、めっきリード29をカットしていない場合は信号のバラツキやノイズが大きいのに対し、めっきリード29をカットすることによりこれらが改善されている。これにより、めっきリード29をカットすることにより、高速差動信号配線27における信号の劣化を低減できることが確認できる。

【0043】

図15は、回路基板7の製造工程を示す図である。まず、内層(L2層51、L3層52)用銅張積層板を所定のパネル寸法に切断する(ステップS1)。そして、所定の寸法に切断した内層用銅張積層板の両面にドライフィルム(エッチングレジスト)をラミネートする(ステップS2)。その後、L2層51、L3層52用の配線パターンをドライフィルムに焼き付ける。パターン以外の不要部分を除去してパターン形成用レジストとし、エッチングによってパターン以外の部分の銅箔を除去してグランドプレーン21a、23a、25や各種配線、グランドプレーン省略部21b〜21d、23b〜23dなどを形成する。さらに、残ったパターン形成用レジストを剥離してパターン形成済の内層基板を得る(ステップS3)。

【0044】

パターン形成済の内層基板と外層用銅張積層板とをプリプレグを用いた積層プレスによって接着する(ステップS4)。得られた積層体に貫通スルーホールやビアホール、取り付け穴などの穴あけ加工を施す(ステップS5)。そして、貫通スルーホールの穴内部に銅めっき加工を施し、外層(L1層50、L4層53)及び内層(L2層51、L3層52)の銅箔面を電気的に接続する(ステップS6)。その後、積層体の両面(外層用銅張積層板の表面)にドライフィルム(エッチングレジスト)をラミネートする(ステップS7)。その後、L1層50、L4層53用の配線パターンをドライフィルムに焼き付ける。パターン以外の不要部分を除去してパターン形成用レジストとし、エッチングによってパターン以外の部分の銅箔を除去して、グランドプレーン20a、26、高速差動信号配線27、シールドGND配線28、めっきリード29などの各種配線やグランドプレーン省略部20bなどを形成する。さらに、残ったパターン形成用レジストを剥離してパターン形成済の積層体を得る(ステップS8)。

【0045】

次に、パターン形成済の積層体に両面にカーテンコート方式などの方法でレジスト液を塗布し、乾燥させてソルダレジスト31、33を形成する(ステップS9)。そして、最終的にソルダレジスト31、33を除去する部分(開口32a〜32d、34a〜34fなど)以外の部分をUV露光により硬化させた上で、未硬化部分を除去し、L1層50及びL4層53の銅箔面を部分的に露出させる(ステップS10)。さらに、銅箔面を部分的に露出させたL1層50及びL4層53の上にめっきマスク用レジスト層を形成し、めっき加工を施す部分(金端子6a、6b、高速差動信号用ボンディングパッド13、ワイヤボンディングパッド14)以外の部分を露光によって硬化させた上で、未硬化部分を除去しめっき加工を施す部分のみを露出させた上で、めっきマスク用レジスト層を除去する(ステップS11)。そして、めっき加工を施す部分に下地めっきとして電解ニッケルめっき加工を施し、さらに電解金めっき加工を施す(ステップS12)。めっき加工が完了した後、めっきリード切断用のエッチングレジストを形成して開口32d以外の部分を覆い、ソルダレジスト31に設けた開口32dにおいて露出しているめっきリード29(配線29a)をエッチングによって切断した上でエッチングレジストを除去する(ステップS13)。その後、ルーター加工により所定の外形に切り出して回路基板7が完成する(ステップS14)。

【0046】

上記の手順で作成した回路基板7は、めっきリード29が回路基板7の面内で切断されているため、めっきリード29で反射した信号がノイズとなって差動信号を劣化させることを抑えることができる。また、高速モードの差動信号用の金端子6bに対応する位置にグランドプレーン省略部21c、23cを備えるため、高速差動信号配線27の差動インピーダンスの低下を抑え、差動信号の劣化を防止できる。さらに、高速差動信号配線27専用のグランドプレーン25を有するため、他の信号の影響を受けて差動信号が劣化することを防止できる。

【0047】

SDメモリカード100を高速モードで動作させる場合には、1〜9番ピンのうち、VSS1(3番ピン)、VSS2(6番ピン)及びVDD1(4番ピン)以外のピンについては、通常モードでの機能を無効とする。そして、7番ピンと8番ピンとについては、通常モードとは異なる機能を割り当て、高速動作用の差動クロックCLK+、CLK−として使用する。したがって、1番ピン、2番ピン、5番ピン及び9番ピンについては、高速モード時は機能を停止したままであり、使用されない。なお、差動クロックCLK+、CLK−の周波数は最大で150MHzであるため、通常モード用である7、8番ピンを用いてもデータ転送速度の高速化の妨げとなることはない。通常モード用として既存のピンを用いてCLK+、CLK−を転送することにより、回路基板7上にこれらの転送用の端子を新たに設ける必要が無くなるため、配線レイアウト上の制約が低減される。

【0048】

そして、差動データピンD0±(11番、12番)によるチャンネルと差動データピンD1±(15番、16番)によるチャンネルとで、CLK±に基づいて1チャンネルあたり1.5Gbpsデータを転送し、合わせて300Mbyte/secのデータ転送速度を実現する。

【0049】

本実施形態に係るSDメモリカード100は、高速差動信号が回路基板7上で劣化することを抑制できるため、メモリパッケージ3a、3bに対するデータの入出力速度、すなわちデータ転送速度の高速化を実現可能である。

【0050】

(第2の実施形態)

図16は、第2の実施形態の半導体メモリカードを適用したSDメモリカードの高速差動信号用の金端子及び高速差動信号用のメモリコントローラワイヤボンディングパッドに電解金めっきを施すためのめっきリードを示す図である。

【0051】

両脇にシールドGND配線28を有する高速差動信号配線27は、途中で分岐することなく高速差動信号用ボンディングパッド13まで達している。高速差動信号用ボンディングパッド13からは、別方向に向かってめっきリード29をなす配線29cが引き出されている。L4層53上のソルダレジスト33に設けられた開口部34gと重なる位置で配線29cは切断されている。

【0052】

本実施形態では、めっきリード29の分岐配線としての長さは第1の実施形態と比較して長くなるが、高速差動信号配線27の途中においてスルーホールを介して分岐配線を設ける必要がないため、スルーホール部分でインピーダンス不整合が生じて信号に反射ノイズが生じることを防止できる。

【0053】

めっきリード29以外の部分の構成については第1の実施形態と同様であるため、重複する説明は割愛する。

【0054】

上記第1、第2の実施形態においては、最もノイズの影響を受けやすい差動信号配線のみめっきリードを切断しているが、他の配線のめっきリードに関しても、同様に回路基板の面内で切断することが可能であり、反射ノイズや外部からのノイズの侵入を防ぐことができる。

【0055】

また、上記第1、第2の実施形態において、配線が存在しない部分がグランドプレーンとなっている構成を例としたが、グランドプレーンとなっている部分の一部をVDD1又はVDD2電位のCuプレーンとすることも可能であり、GNDだけでなくVDDの電位を安定化させるのに効果的である。

【0056】

さらに、上記第1、第2の実施形態では、VDD1及びVDD2の二つの電源電位を有する構成としたが、動作させるIC(メモリコントローラ及びメモリパッケージ)の仕様に応じて、VDD3やVDD4などの複数の別の電源電位を持つ配線やCuプレーンを設けることも可能である。

【0057】

また、上記第1、第2の実施形態では、高速差動信号用の金端子に対応する部分のグランドプレーンを省き、高速差動信号配線に対応する領域に専用のグランドプレーンを設け、かつ高速差動信号配線のめっきリードを回路基板の面内で切断した構成を例としたが、これらを全て兼ね備えている必要はなく、これらの少なくとも一つを満たす構成として実施することも可能である。上記の三つのうち少なくとも一つを満たすことで、高速モード用の差動信号が回路基板上で劣化することを防止する効果が得られる。

【0058】

また、上記第1、第2の実施形態における部品の配置や基板レイアウトはあくまでも一例であり、本発明はこれらに限定されることはない。

【0059】

また、上記各実施形態においては、通常モード用のピンの一部を高速モードでは別の機能に切り換えて使用する構成を例としたが、全ての通常モード用のピンが通常モード専用であってもよい。

【0060】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0061】

3a、3b メモリパッケージ、6a、6b 金端子、7 回路基板、12 メモリコントローラ、13 高速差動信号用ボンディングパッド、21a、23a、25 グランドプレーン、27 高速差動信号配線、29めっきリード、54、55 金端子の基となる端子パターン、100 SDメモリカード。

【特許請求の範囲】

【請求項1】

半導体メモリと、

通常モード及び該通常モードよりもデータ転送速度が速い高速モードの両方での前記半導体メモリへのデータの読み書きを制御するメモリコントローラと、

少なくとも一つの内層を有する多層プリント基板に前記半導体メモリ及び前記メモリコントローラを表裏に分けて実装した回路基板とを備え、

前記回路基板は、

前記メモリコントローラと外部機器との間での前記高速モードによるデータ入出力用として前記メモリコントローラの実装面に設けられ、金めっき加工が施された高速モード用の金端子と、

前記高速モード用の金端子と前記メモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線と、

前記高速差動信号配線から分岐し、前記回路基板の面内において前記高速差動信号配線との分岐点の近傍で切断された前記金めっき加工用のめっきリードを有することを特徴とする半導体メモリカード。

【請求項2】

前記回路基板は、前記高速モード用の金端子の配置位置に対応する部分がくり抜かれたグランドプレーンを前記内層に有することを特徴とする請求項1記載の半導体メモリカード。

【請求項3】

前記回路基板は、前記高速差動信号配線が設けられた配線層と積層方向に隣接する配線層に、通常モード用のグランドプレーンとは電気的に分離された前記高速差動信号配線用のグランドプレーンを、前記高速差動信号配線の近傍領域と対応する領域に備えることを特徴とする請求項1又は2記載の半導体メモリカード。

【請求項4】

前記めっきリードを、前記高速差動信号配線が設けられた配線層とは別の配線層に導いて分岐させるスルーホールを有し、

前記めっきリードは、前記別の配線層において切断されていることを特徴とする請求項1から3のいずれか1項記載の半導体メモリカード。

【請求項5】

半導体メモリと、

通常モード及び該通常モードよりもデータ転送速度が速い高速モードの両方での前記半導体メモリへのデータの読み書きを制御するメモリコントローラと、少なくとも一つの内層を有する多層プリント基板に前記半導体メモリ及び前記メモリコントローラを表裏に分けて実装した回路基板とを備えた半導体メモリカードの製造方法であって、

前記プリント基板の製造時に、

前記メモリコントローラと外部機器との間での前記高速モードによるデータ入出力用の金端子の基とする端子パターンを前記メモリコントローラの実装面に設け、

前記端子パターンと前記メモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線から分岐するめっきリードを設け、

前記めっきリードを介して前記端子パターンと前記メモリコントローラの実装用のボンディングパッドとに金めっき加工を施し、

前記めっきリードを前記回路基板の面内において切断することを特徴とする半導体メモリカードの製造方法。

【請求項1】

半導体メモリと、

通常モード及び該通常モードよりもデータ転送速度が速い高速モードの両方での前記半導体メモリへのデータの読み書きを制御するメモリコントローラと、

少なくとも一つの内層を有する多層プリント基板に前記半導体メモリ及び前記メモリコントローラを表裏に分けて実装した回路基板とを備え、

前記回路基板は、

前記メモリコントローラと外部機器との間での前記高速モードによるデータ入出力用として前記メモリコントローラの実装面に設けられ、金めっき加工が施された高速モード用の金端子と、

前記高速モード用の金端子と前記メモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線と、

前記高速差動信号配線から分岐し、前記回路基板の面内において前記高速差動信号配線との分岐点の近傍で切断された前記金めっき加工用のめっきリードを有することを特徴とする半導体メモリカード。

【請求項2】

前記回路基板は、前記高速モード用の金端子の配置位置に対応する部分がくり抜かれたグランドプレーンを前記内層に有することを特徴とする請求項1記載の半導体メモリカード。

【請求項3】

前記回路基板は、前記高速差動信号配線が設けられた配線層と積層方向に隣接する配線層に、通常モード用のグランドプレーンとは電気的に分離された前記高速差動信号配線用のグランドプレーンを、前記高速差動信号配線の近傍領域と対応する領域に備えることを特徴とする請求項1又は2記載の半導体メモリカード。

【請求項4】

前記めっきリードを、前記高速差動信号配線が設けられた配線層とは別の配線層に導いて分岐させるスルーホールを有し、

前記めっきリードは、前記別の配線層において切断されていることを特徴とする請求項1から3のいずれか1項記載の半導体メモリカード。

【請求項5】

半導体メモリと、

通常モード及び該通常モードよりもデータ転送速度が速い高速モードの両方での前記半導体メモリへのデータの読み書きを制御するメモリコントローラと、少なくとも一つの内層を有する多層プリント基板に前記半導体メモリ及び前記メモリコントローラを表裏に分けて実装した回路基板とを備えた半導体メモリカードの製造方法であって、

前記プリント基板の製造時に、

前記メモリコントローラと外部機器との間での前記高速モードによるデータ入出力用の金端子の基とする端子パターンを前記メモリコントローラの実装面に設け、

前記端子パターンと前記メモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線から分岐するめっきリードを設け、

前記めっきリードを介して前記端子パターンと前記メモリコントローラの実装用のボンディングパッドとに金めっき加工を施し、

前記めっきリードを前記回路基板の面内において切断することを特徴とする半導体メモリカードの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図8】

【図11】

【図12】

【図14】

【図15】

【図16】

【図6】

【図7】

【図9】

【図10】

【図13】

【図2】

【図3】

【図4】

【図5】

【図8】

【図11】

【図12】

【図14】

【図15】

【図16】

【図6】

【図7】

【図9】

【図10】

【図13】

【公開番号】特開2013−69019(P2013−69019A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−205636(P2011−205636)

【出願日】平成23年9月21日(2011.9.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月21日(2011.9.21)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]