半導体メモリ装置、このためのセットプログラム制御回路及びプログラム方法

【課題】消去命令に応答してセットデータをプログラムできる半導体メモリ装置と、このためのセットプログラム制御回路及びプログラム方法を提供する。

【解決手段】本発明に係る半導体メモリ装置は、プログラミングイネーブル信号に応答して第1書き込み制御信号、第2書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号を指定された回数だけ反復生成するセットプログラム制御回路と、消去命令に応答して第1書き込み制御信号をディスエーブルし、セットプログラミングイネーブル信号に応答してプログラミングイネーブル信号を生成するコントローラとを含むことができる。

【解決手段】本発明に係る半導体メモリ装置は、プログラミングイネーブル信号に応答して第1書き込み制御信号、第2書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号を指定された回数だけ反復生成するセットプログラム制御回路と、消去命令に応答して第1書き込み制御信号をディスエーブルし、セットプログラミングイネーブル信号に応答してプログラミングイネーブル信号を生成するコントローラとを含むことができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体システムに関するもので、より具体的には半導体メモリ装置と、このためのセットプログラム制御回路及びプログラム方法に関するものである。

【背景技術】

【0002】

PCRAM(Phase Change RAM)はメモリセルを構成する特定物質の相(phase)変換特性を用いたメモリ素子である。相変化物質は温度条件によって非晶質状態(Amorphous State)または、結晶質状態(Crystalline State)に転換されることができる物質であり、例えば、カルコゲナイド係合金(Chalcogenidealloy)を挙げることができる。また、代表的な相変化物質としては、ゲルマニウム(Germanium)、アンチモン(Antimony)、テルル(Tellurium)を用いたGe2Sb2Te5(以下、GST)物質を挙げることができる。

【0003】

大部分の物質は、物質ごとにメルティングポイント(溶融点)と結晶化する温度が互いに異なり、冷却される時間と温度によって結晶を形成する程度も互いに異なる。これは各物質等の固有特性の中の1つであり、特にGSTという物質は他の物質より非晶質状態と結晶質状態の区分がさらに優秀である。

【0004】

図1は一般的な相変化物質の温度による相変化状態を説明するための一例示として、GSTという物質を例に挙げて説明している。

【0005】

GSTは、メルティングポイント以上の高温に一定時間(数十〜数百ns)の間維持された後、指定された時間(Tq)に急冷(Quenching)されると非晶質状態がそのまま維持されて抵抗値が数百kΩ〜数MΩになる。

【0006】

また、結晶化温度(Crystallization temperature)範囲に一定時間の間(数百ns〜数μs)維持された後、冷却されると結晶状態になって抵抗が数kΩ〜数十kΩになるが、結晶化温度に維持される時間が長いほど結晶状態がさらに優秀になってより小さな抵抗値を有することができる。

【0007】

図2は、一般的な相変化物質の温度による相変化状態を説明するための他の例示図として、同様にGSTという物質を例に挙げて説明している。

【0008】

図2では、一定時間の間メルティングポイントの近くまで温度を供給した後、徐々に冷却させる方法でGSTを結晶化させる例を表す。このようにする場合にもGSTの抵抗が数kΩ〜数十kΩになるが、やはり冷却させる時間が長いほど結晶状態はさらに優秀になる。また、図1の場合より必要とされる結晶化の時間も短くなる。

【0009】

GSTのこのような特性を利用するために直接的に熱を制御する方法もあるが、導体または半導体に流される電流により発生するジュール熱(Joule heating)を利用した電気的な方法でGSTの状態を非晶質状態と結晶質状態とで変化させる方法が利用されている。

【0010】

前述した図1及び図2には相変化メモリ素子の一般的な動作を図式化したものであって、セットデータプログラム時間、すなわちGSTを結晶化するのに必要となる時間が短い図2の方法を主に使用する。

【0011】

図3は、一般的な相変化メモリ装置のセルアレイ構成図である。

【0012】

図3に図示したように、各メモリセル(MC)は、ワードライン(WL)及びビットライン(BL)の間に接続される相変化物質(GST)とスイチング素子(D)とで構成さることが分かる。

【0013】

このような相変化メモリ装置のプログラム動作を図4を参照して説明する。

【0014】

図4は、一般的な相変化メモリ装置の構成図である。

【0015】

図4を参照すると、相変化メモリ装置1は、プログラムパルス生成部11、ライトドライバー12及びメモリ部13を含む。

【0016】

プログラムパルス生成部11は、コントローラ(不図示)から発生されるプログラミングイネーブル信号(PGMP)に応答して第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<0:n>)を生成してライトドライバー12へ提供する。併せて、第1及び第2制御信号の生成動作が完了されるとプログラム完了信号(PGMNDP)を生成してコントローラへ伝送する。

【0017】

ライトドライバー12は、ライトイネーブル信号(WDEN)に応答して駆動する。そして、プログラムパルス生成部11から第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<0:n>)を受信して、プログラムするデータ(DATA)及びビットライン選択スイッチ制御信号(YSW<0:m>)に応答してメモリ部13へプログラム電流(I_PGM)を供給する。

【0018】

これによって、メモリ部13には、プログラムしようとするデータ(DATA)のレベルによってGSTの抵抗状態が変化されてデータが記録されることができる。

【0019】

図5は、図4に図示したプログラムパルス生成部の一例示図である。

【0020】

図5に図示したように、プログラムパルス生成部11は、初期パルス発生部111、リセットパルス発生部113及びクエンチング(quenching)パルス発生部115を含むように構成される。

【0021】

初期パルス発生部111は、コントローラから提供されるプログラミングイネーブル信号(PGMP)に応答して区間設定信号(QSSETP)を生成する。区間設定信号(QSSETP)は、GSTへ溶融点に近い熱を提供するための時間を決定する信号で、初期パルス発生部111は、プログラミングイネーブル信号(PGMP)に応答して予め設定された時間をカウンティングした後、区間設定信号(QSSETP)をイネーブルさせるようになる。

【0022】

リセットパルス発生部113は、プログラミングイネーブル信号(PGMP)及び区間設定信号(QSSETP)を予め設定された時間を遅延させて生成したリセット信号(IRSTP)に応答して第1書き込み制御信号(RESETEN)を生成する。

【0023】

一方、クエンチングパルス発生部115は、プログラミングイネーブル信号(PGMP)及び区間設定信号(QSSETP)に応答してイネーブル区間が互いに異なる第2書き込み制御信号(SETP<0:n>)を生成する。併せて、クエンチングパルス発生部115は、第2書き込み制御信号(SETP<0:n>)の生成が完了されるとプログラム完了信号(PGMNDP)を生成する。

【0024】

このような構成によって、リセットパルス発生部113は、プログラミングイネーブル信号(PGMP)がイネーブルされた後、リセット信号(IRSTP)がイネーブルされるまでの区間の間第1書き込み制御信号(RESETEN)を生成する。そして、クエンチングパルス発生部115は、プログラミングイネーブル信号(PGMP)がイネーブルされた後、区間設定信号(QSSETP)がイネーブルされるまでは第2書き込み制御信号(SETP<0:n>)を同一なレベルでイネーブルさせ、区間設定信号(QSSETP)が発生した後には、イネーブルの区間が調節された第2書き込み制御信号(SETP<0:n>)を生成する。

【0025】

図6は、一般的な相変化メモリ素子のプログラム動作を説明するためのタイミング図である。

【0026】

プログラム命令(PGM)が印加されることによってコントローラからプログラミングイネーブル信号(PGMP)が生成されて、これによって初期パルス発生部111が動作して内部クロックイネーブル信号(IPWEN)を生成する。そして、これから内部クロック(ICK)が生成された後、予め設定された時間をカウントしてカウンティングコード(Q<0:3>)が生成され、カウンティングが完了されると区間設定信号(QSSETP)が生成される。

【0027】

一方、リセットパルス発生部113は、プログラミングイネーブル信号(PGMP)に応答して第1書き込み制御信号(RESETEN)をイネーブルさせて、区間設定信号(QSSETP)を予め設定された時間の間遅延させて生成したリセット信号(IRSTP)がイネーブルされることによって第1書き込み制御信号(RESETEN)をディスエーブルさせる。そして、第1書き込み制御信号(RESETEN)がイネーブルされている区間の間ライトドライバーからプログラミング電流が生成されてビットライン(BL0)に供給される。

【0028】

クエンチングパルス発生部115は、区間設定信号(QSSETP)に応答してカウントイネーブル信号(CKEN(CNTENB))及び内部クロック(QSCK)を生成する。そして、これによってイネーブル区間が互いに異なる第2書き込み制御信号(SETP<0:3>)を生成する。第2書き込み制御信号(SETP<0:3>)の生成が完了されるとクエンチングパルス完了信号(QSND)がディスエーブルになり、これからリセット信号(QSRSTP)がイネーブルされるとプログラム完了信号(PGMNDP)が出力される。この場合、第2書き込み制御信号(SETP<0:3>)のイネーブル区間によってライトドライバーの電流駆動力が順次に減殺されてGSTにクエンチングパルスが供給されるようになる。

【0029】

プログラム動作の時、ワードラインは、ワードライン選択スイッチがディスエーブル状態である場合、高電位(VCC以上)を維持するが、ワードライン選択スイッチがイネーブルされると接地電圧レベルにディスチャージされる。併せて、ライトドライバーによって選択されるビットラインによりライトドライバー−ビットライン選択スイッチ−ビットライン−スイチング素子−GST−ワードラインに達するまで電流パスが形成される。

【0030】

このように電流パスが形成された状態でプログラムしようとするデータレベル(0/1)によって第1書き込み制御信号(RESETEN)または第2書き込み制御信号(SETP<0:n>)によりライトドライバーで駆動される電流量が決定されてビットラインを通してメモリセルにプログラム電流が供給される。例えば、第1書き込み制御信号(RESETEN)により供給される電流を100と仮定すると、第2書き込み制御信号(SETP<0:3>)がすべてイネーブルされる場合のメモリセルに供給される電流は30〜90%程度の割合で調節される。

【0031】

プログラム動作の時、ビットラインを通して供給される電流は、リセットデータの場合には短形波(Rectangular Type)の様子で供給されて、セットデータの場合には初期には短形波と類似の形態で供給されるが第2書き込み制御信号(SETP<0:n>)により階段波の形態であり、減少する形態で供給される。

【0032】

したがって、セットデータとリセットデータを同時にプログラムする場合、プログラム動作に要する時間は長い時間が要求されるセットデータプログラム時間によって決定されるようになる。

【0033】

一方、相変化メモリ装置はフラッシュメモリの変わりに使われている趨勢がある。この場合、メモリ装置はフラッシュのインターフェースを通してプログラム命令、消去命令を受けて該当する動作を行う。しかし、相変化メモリ装置はライト命令によってセットデータまたはリセットデータをプログラムするだけであり、したがって、相変化メモリ装置をフラッシュメモリのインターフェースで動作させようとする場合、消去命令が印加された場合いかなる動作もすることなく遊休状態となる。

【先行技術文献】

【特許文献】

【0034】

【特許文献1】米国特許第7936619号明細書

【発明の概要】

【発明が解決しようとする課題】

【0035】

本発明は、消去命令に応答して複数の不揮発性メモリセルにセットデータをプログラムできる半導体メモリ装置と、このためのセットプログラム制御回路及びプログラム方法を提供する。

【課題を解決するための手段】

【0036】

本発明の一態様に係る半導体メモリ装置は、プログラミングイネーブル信号に応答して第1書き込み制御信号、第2書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、消去命令及び前記プログラム完了信号に応答してセットプログラミングイネーブル信号を指定された回数だけ反復生成するセットプログラム制御回路と、前記消去命令に応答して前記第1書き込み制御信号をディスエーブルし、前記セットプログラミングイネーブル信号に応答して前記プログラミングイネーブル信号を生成するコントローラとを備えることができる。

【0037】

また、本発明の他の態様に係る半導体メモリ装置は、消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号を生成し、該セットプログラミングイネーブル信号に応答して生成されるプログラミングイネーブル信号によって第1書き込み制御信号及び第2書き込み制御信号を出力するプログラムパルス生成部と、前記第1書き込み制御信号及び前記第2書き込み制御信号に応答して生成されるプログラムパルスをメモリ部へ提供するライトドライバーとを備えることができる。

【0038】

また、本発明の他の態様に係るセットプログラム制御回路は、セットプログラミングイネーブル信号によって生成されるプログラミングイネーブル信号に応答してプログラム完了信号を生成するプログラムパルス生成部と接続され、消去命令及び前記プログラム完了信号に応答して前記セットプログラミングイネーブル信号を生成することができる。

【0039】

また、本発明の他の態様に係るプログラム方法は、プログラムパルス生成部を具備する半導体メモリ装置にセットデータが入力される段階と、前記プログラムパルス生成部が消去動作の基本単位及びセットデータ記録単位によって設定された回数だけプログラミングイネーブル信号を反復生成する段階と、前記プログラミングイネーブル信号に応答して、ライトドライバーがメモリ部の選択された領域にデータをプログラムする段階とを含むことができる。

【発明の効果】

【0040】

本発明によると、消去命令に応答してセットデータをプログラムすることによってデータ記録に要する時間を短縮させることができる。

【図面の簡単な説明】

【0041】

【図1】一般的な相変化物質の温度による相変化状態を説明するための一例示図である。

【図2】一般的な相変化物質の温度による相変化状態を説明するための異なる例示図である。

【図3】一般的な相変化メモリ装置のセルアレイ構成図である。

【図4】一般的な相変化メモリ装置の構成図である。

【図5】図4に図示したプログラムパルス生成部の一例示図である。

【図6】一般的な相変化メモリ素子のプログラム動作を説明するためのタイミング図である。

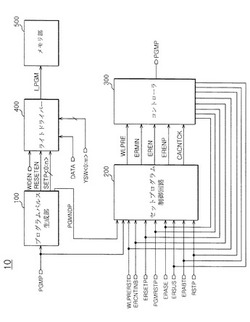

【図7】本発明の一実施形態に係る半導体メモリ装置の構成図である。

【図8】本発明の一実施形態に係るセットプログラム制御回路の構成図である。

【図9】図8に図示した制御信号生成部の一例示図である。

【図10】図8に図示したモード判定部の一例示図である。

【図11】図9に図示したパルス出力部の一例示図である。

【図12】本発明に適用されることができるプログラムパルス生成部の一例示図である。

【図13】図12に図示した第1カウント部の構成を説明するための一例示図である。

【図14】図12に図示した比較部の一例示図である。

【図15】図8に図示したカウント部及び図12に図示した第2カウント部の構成を説明するための図である。

【図16】本発明に適用されることができるライトドライバーの一例示図である。

【図17】本発明の一実施形態によるセットプログラム動作を説明するためのタイミング図である。

【発明を実施するための形態】

【0042】

半導体メモリ装置、特にフラッシュメモリ装置の標準規格ではリセットデータを記録することをプログラム動作と定義しており、特に16ビット単位でプログラムすることをシングルワードプログラム(single word program)、512バイト(256ワード)単位でプログラムすることをバッファープログラム(buffered program)であると定義している。また、リセットデータとセットデータを同時に記録することをオーバーライト(over write)と定義している。そして、16ビット単位でセット/リセットデータを同時に記録することをシングルワードオーバーライト、512バイト(256ワード)単位でセット/リセットデータを同時に記録することをバッファーオーバーライトと定義している。

【0043】

本発明では不揮発性メモリ装置、望ましくは電流駆動方式により駆動される不揮発性メモリ装置をフラッシュメモリのインターフェースを利用して動作させる場合、128KB単位の消去命令に応答してメモリ装置がセットデータを記録するように定義して、消去命令が入力される場合、複数の不揮発性メモリセルにセットデータを記録する方案を提案する。

【0044】

これによって、消去命令が入力される時にもメモリ装置を動作させることができ、動作効率が改善される。さらに、セットデータを記録する時間より相対的に短い時間の間に行われるリセットデータ記録時間がセットデータ記録時間に独立的なのでデータ記録速度を向上させることができる。

【0045】

このために、不揮発性メモリ装置、望ましくはフラッシュメモリ装置の標準規格を基盤として、セットプログラム動作に必要な信号(命令語コード、アドレス等)がレジスターに臨時に保存されて、命令語実行コードがイネーブルされることによってレジスターに保存されている信号を用いてセットプログラムがなされるようになる。

【0046】

一例として、相変化メモリ装置は、電流駆動能力の限界でセットデータの記録が32ビット単位でなされる。ところが不揮発性メモリ装置の標準規格では消去動作が128KB単位でなされるので合計32,768回のセットデータ記録動作が行われるようになる。したがって、消去動作の基本単位(128KB)をセットデータ記録単位(32ビット)で分けた数(32,768回)だけ消去動作が反復的に行われるようになると複数のメモリセルにセットデータを記録できるようになる。フラッシュメモリのインターフェース基盤で、バッファープログラムまたはバッファーオーバーライト動作は512B単位でなされる。したがって、128個(512B/32ビット)ずつワードラインを選択して128KB/512B回だけの消去動作が行われることができる。結局、消去命令に応答して一回の消去動作時32ビットのメモリセルにセットデータが記録される動作を反復的に行って、メモリセルにセットデータを順次に記録することができる。

【0047】

以下、添付された図面を参照して本発明の実施形態をより具体的に説明する。

【0048】

図7は、本発明の一実施形態に係る半導体メモリ装置の構成図である。

【0049】

図7を参照すると、半導体メモリ装置10は、プログラミングイネーブル信号(PGMP)によって第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<0:n>)を生成するプログラムパルス生成部100、消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号(ERENP)を指定された回数で反復生成するセットプログラム制御回路200、プログラミングイネーブル信号(PGMP)をはじめとするプログラム動作関連制御信号、アドレス、データ信号を提供するコントローラ300、プログラムパルス生成部100から提供される書き込み制御信号(RESETEN、SETP<0:n>)及びビットライン選択スイッチ制御信号(YSW<0:m>)に応答して入力データ(DATA)をプログラムするためのプログラム電流(I_PGM)を生成するライトドライバー400及び複数のメモリセルを含んでライトドライバー400から提供される電流によって各メモリセルにデータが記録されるメモリ部500を含む。

【0050】

このような半導体メモリ装置10において、セットプログラム制御回路200は、消去命令(ERASE)に応答して予め設定された回数だけ消去動作、すなわち、セットデータ記録動作が反復的に行われるようにするセットプログラミングイネーブル信号(ERENP)を生成してコントローラ300へ提供する。そして、コントローラ300は、セットプログラミングイネーブル信号(ERENP)に応答して生成したプログラミングイネーブル信号(PGMP)をプログラムパルス生成部100へ提供して、予め設定された回数だけ消去(セットデータ記録)動作が行われるようにする。

【0051】

また、セットプログラム制御回路200は、指定された個数のワードラインが選択されて消去動作が行われた後、次のワードラインを選択するためのアドレスカウント信号(CACNTCK)及び現在消去動作を行ったワードラインをフリーチャージさせるためのワードラインフリーチャージ信号(WLPRE)をコントローラ300へ提供する。

【0052】

併せて、セットプログラム制御回路200は、消去命令によるセットデータ記録が行われる間消去区間イネーブル信号(EREN)をイネーブルさせる一方、最後の消去動作が始まると消去終了信号(ERMIN)を生成してコントローラ300へ提供してこれ以上プログラミングイネーブル信号(PGMP)が生成されないようにする。

【0053】

各構成部の動作をより具体的に説明すれば次の通りである。

【0054】

プログラムパルス生成部100は、コントローラ300から発生されるプログラミングイネーブル信号(PGMP)に応答して第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<0:n>)を生成してライトドライバー400へ提供する。併せて、第1及び第2書き込み制御信号(RESETEN、SETP<0:n>)の生成動作が完了するとプログラム完了信号(PGMNDP)を生成し、これをセットプログラム制御回路200に伝える。

【0055】

本発明の望ましい実施形態において、消去動作時にはセットデータの記録だけなされるので、コントローラ300によって消去命令(ERASE)がイネーブルされると第1書き込み制御信号(RESETEN)はディスエーブルされるように制御する。そして、第2書き込み制御信号(SETP<0:n>)の生成が完了するとプログラム完了信号(PGMNDP)がイネーブルされ、これはセットプログラム制御回路200のクロック信号(図9のERCNTCK)として作用するようになる。

【0056】

ライトドライバー400は、ライトイネーブル信号(WDEN)に応答して駆動される。そして、プログラムパルス生成部100から第1書き込み制御信号(RESETEN)及び/または第2書き込み制御信号(SETP<0:n>)を受けて、プログラムするデータ(DATA)及びビットライン選択スイッチ制御信号(YSW<0:m>)に応答してメモリ部500へプログラム電流(I_PGM)を供給する。

【0057】

これによって、メモリ部500にはプログラムしようとするデータ(DATA)のレベルによってデータが記録されることができる。本発明の一実施形態において、メモリ部500は、電流駆動方式によってデータが記録され、センシングされるメモリセルを用いて構成することができる。電流駆動方式によりプログラム及びセンシングがなされるメモリセルとしては、例えば相変化メモリセル、磁気メモリセルなどを用いることができる。

【0058】

セットプログラム制御回路200は、プログラムパルス生成部100から提供されるプログラム完了信号(PGMNDP)をクロック信号(図9のERCNTCK)として利用して、不揮発性メモリ装置の標準規格で定義している消去動作の基本単位(例えば、128KB)及びセットデータ記録単位(例えば、32ビット)に基づいてセットプログラミングイネーブル信号(ERENP)を生成する。例えば、セットデータ記録単位が32ビットである場合128KBの消去動作のために32,768回のカウンティングを行い、カウンティングが行われる時ごとにセットプログラミングイネーブル信号(ERENP)をイネーブルさせるものである。また、指定された個数(例えば128個)のワードラインを同時に選択して消去動作が行われるように、選択されたワードラインに対する消去動作が完了されるとアドレスカウント信号(CACNTCK)を生成して次の消去対象のワードラインらが選択されることができるようにする。一方、現在消去動作が行われたワードラインをフリーチャージさせるためのワードラインフリーチャージ信号(WLPRE)を生成する。

【0059】

併せて、消去命令(ERASE)に応答して消去動作が始まると、消去区間イネーブル信号(EREN)を生成して消去動作が遂行中であることを知らせて、最後のカウンティングが行われると、すなわち、最後の消去動作が始まると、消去終了信号(ERMIN)を生成してこれ以上プログラミングイネーブル信号(PGMP)が生成されないようにする。

【0060】

なお、図7では、セットプログラム制御回路200をプログラムパルス生成部100と独立的に図示したが、セットプログラム制御回路200がプログラムパルス生成部100に含まれるように構成することも可能である。すなわち、プログラムパルス生成部100は、セットプログラム制御回路200を含むことができる。

【0061】

図8は、本発明の一実施形態に係るセットプログラム制御回路の構成図である。

【0062】

図8を参照すると、セットプログラム制御回路200は、制御信号生成部210、カウント部220、モード判定部230及びセットプログラムパルス発生部240を含むように構成できる。

【0063】

制御信号生成部210は、コントローラ300から提供されるカウントイネーブル信号(ERCNTINB)及び消去命令(ERASE)に応答して消去回数カウント信号(ERCNTB)を生成する。また、プログラム完了信号(PGMNDP)から生成されるクロック信号(ERCNTCK)及び消去命令(ERASE)に応答して消去クロック信号(ERCK)を生成する。これに加えて、カウント部220の動作をリセットさせなければならない多様な場合に現れる得る状況を併合して消去リセット信号(ERRST)を生成する。消去リセット信号(ERRST)の生成に作用する信号は、サスペンド信号(ERSUS)、プログラムリセット信号(PGMRSTP)、エラー信号(ERABT)、リセット信号(RSTP)などであり得るが、これに限定されるものではない。併せて、制御信号生成部210は、コントローラ300から提供される消去モード設定信号(ERSETP)に応答して消去イネーブル信号(IEREN)を生成する。

【0064】

一方、消去回数カウント信号(ERCNTB)、消去クロック信号(ERCK)、消去リセット信号(ERRST)及び消去イネーブル信号(IEREN)は各々、サスペンド信号(ERSUS)が発生しない場合イネーブルされる。サスペンド信号(ERSUS)は、消去命令が入力されて内部的に消去動作をしている間、少しの間消去動作を止めて異なる動作をしようとする時にイネーブルされる。消去動作の中止の時に行われることができる動作としては、データリード(Read)、状態(status)リード、またはローデータバッファー(Row Data Buffer)ライト動作があり得る。

【0065】

図9は、図8に図示した制御信号生成部の一例示図である。

【0066】

カウントイネーブル信号(ERCNTINB)がローレベルでイネーブルされ、クロック信号(ERCNTCK)及び消去命令(ERASE)が入力されると、サスペンド信号(ERSUS)がディスエーブルの状態である場合にだけ消去回数カウント信号(ERCNTB)と消去クロック信号(ERCK)とがカウント部220へ伝えられることが分かる。また、消去リセット信号(ERRST)は、サスペンド信号(ERSUS)、プログラムリセット信号(PGMRSTP)、エラー信号(ERABT)、リセット信号(RSTP)のうちいずれか一つでもイネーブルされるとイネーブルされる。併せて、消去イネーブル信号(IEREN)は、消去モード設定信号(ERSETP)がイネーブルされ、サスペンド信号(ERSUS)がディスエーブル状態である場合、イネーブルされることがわかる。

【0067】

再び、図8を参照すると、カウント部220は、制御信号生成部210から提供される消去回数カウント信号(ERCNTB)、消去クロック信号(ERCK)、消去リセット信号(ERRST)及び消去イネーブル信号(IEREN)と、コントローラから提供されるフリーチャージリセット信号(WLPRERST)とに応答してカウンティング動作を行う。

【0068】

まず、消去回数カウント信号(ERCNTB)がイネーブルされることによってカウント部220が動作可能な状態になり、消去イネーブル信号(IEREN)によって初期値が設定される。そして、消去クロック信号(ERCK)に応答してカウンティングを遂行し、その結果としてカウンティング信号(ERQ<0:x>)を出力する。

【0069】

本発明の一実施形態において、消去モードが128KB単位で行われ、一回の消去動作時に32ビットのメモリセルにセットデータを記録する場合、32,768回のカウンティング動作が必要であり、この場合カウンティング信号(ERQ<0:x>)は15ビットをカウンティングできなければならない。

【0070】

このために、カウント部220を15個のダウンカウンターを用いて構成し、すべてのダウンカウンターの初期値を1で設定した後、出力がすべて0になる時までカウントを行うようにすることができるが、これに限定されるものではない。カウント部220に提供される消去クロック信号(ERCK)がプログラム完了信号(PGMNDP)から生成されることは、先立って説明したとおりである。したがって、カウント部220でカウンティングを行う時ごとにセットプログラムパルス発生部240からセットプログラミングイネーブル信号(ERENP)を生成して、これによってセットデータが記録される。セットデータの記録の後には再びプログラム完了信号(PGMNDP)がイネーブルされ、このような過程はカウント部220の動作が完了される時まで反復される。カウント部220の動作が完了されることは、セットプログラムパルス発生部240の区間設定部241を通して確認することができる。

【0071】

セットプログラムパルス発生部240は、消去命令に応答したセットプログラムの区間であるか否かによってセットプログラミングイネーブル信号(ERENP)を出力する。例えば、セットプログラムが動作初期すなわち、最初のセットプログラム動作の時にはプログラミングイネーブル信号(PGMP)をそのままバイパスし、最初のセットプログラム動作によってプログラム完了信号(PGMNDP)が生成されるとプログラム完了信号(PGMNDP)をセットプログラミングイネーブル信号(ERENP)として出力する。

【0072】

このために、セットプログラムパルス発生部240は、区間設定部241及びパルス出力部243を含むように構成できる。

【0073】

区間設定部241は、例えば、カウント部220を構成するカウンターと同じカウンターを利用して構成することができる。区間設定部241が消去区間イネーブル信号(EREN)を生成する際に、消去区間イネーブル信号(EREN)は、消去動作の開始を知らせる消去モード設定信号(ERSETP)がイネーブルされた状態でイネーブルされ、カウント部220が最後のカウンティング動作を完了すると消去クロック信号(ERCK)によりディスエーブルされてコントローラ300へ提供される。

【0074】

パルス出力部243は、例えば図11のように構成することができる。

【0075】

図11は、図9に図示したパルス出力部の一例示図である。

【0076】

パルス出力部243は、消去区間イネーブル信号(EREN)のイネーブルの可否によって、プログラミングイネーブル信号(PGMP)またはプログラム完了信号(PGMNDP)をセットプログラミングイネーブル信号(ERENP)として出力する。

【0077】

すなわち、パルス出力部243は、消去区間イネーブル信号(EREN)がディスエーブルになった状態ではプログラミングイネーブル信号(PGMP)をセットプログラミングイネーブル信号(ERENP)としてバイパスさせる。一方、消去区間イネーブル信号(EREN)がイネーブルされている区間ではプログラム完了信号(PGMNDP)をセットプログラミングイネーブル信号(ERENP)として出力する。

【0078】

すなわち、消去区間イネーブル信号(EREN)がイネーブルされている区間では、プログラム完了信号(PGMNDP)がイネーブルされるとこれをセットプログラミングイネーブル信号(ERENP)として出力し、消去区間イネーブル信号(EREN)がディスエーブルになった状態すなわち、最初の消去動作時には、プログラミングイネーブル信号(PGMP)をセットプログラミングイネーブル信号(ERENP)としてバイパスさせる。

【0079】

併せて、パルス出力部243は、消去区間イネーブル信号(EREN)とプログラム完了信号(PGMNDP)とのレベルによってアドレスカウント信号(CACNTCK)を生成する。アドレスカウント信号(CACNTCK)は、コラムアドレスカウンターを動作させるための信号であり、モード判定部230へ提供される。アドレスカウント信号(CACNTCK)がイネーブルされると現在消去したワードラインらがフリーチャージされ、次の消去対象ワードラインらが選択される。

【0080】

モード判定部230は、カウント部220から提供されるカウンティング信号(ERQ<0:x>)と、セットプログラムパルス発生部240から提供される消去区間イネーブル信号(EREN)及びアドレスカウント信号(CACNTCK)とに応答してワードラインフリーチャージ信号(WLPRE)及び消去終了信号(ERMIN)を生成する。

【0081】

図10は、図8に図示したモード判定部の一例示図である。

【0082】

モード判定部230は、指定された個数のワードラインに接続されたメモリセルらに対する消去動作が完了されると、次のワードラインらに接続されたメモリセルらに対する消去動作のために現在消去動作が完了されたワードラインをフリーチャージするためのワードラインフリーチャージ信号(WLPRE)を生成する。

【0083】

例えば、128KBのメモリセルにセットデータを記録する消去モードで128個(512B/32ビット)ずつワードラインを選択して消去動作を行う場合、カウント部220が初期値(32,768)から128ずつダウンカウンティングする時点ごとにワードラインフリーチャージ信号(WLPRE)をイネーブルすることができる。32,768回のカウンティングが必要な場合、カウント部220は、15個のダウンカウンターで構成できる。したがってカウンティング信号(ERQ<0:14>)のうち一部のカウンティング信号(ERQ<0:6>)がすべてローレベルからハイレベルに遷移する場合にワードラインフリーチャージ信号(WLPRE)がイネーブルされることができる。

【0084】

ワードラインフリーチャージ信号(WLPRE)がイネーブルされる場合、現在消去動作のために選択されたワードラインをディスエーブルさせ、フリーチャージのための時間が経過した後、次の消去対象ワードラインをイネーブルさせることが望ましい。

【0085】

次の消去対象ワードラインがイネーブルされた状態からカウント部220が動作してセットプログラミングイネーブル信号(ERENP)が生成され、これによってアドレスカウント信号(CACNTCK)がイネーブルされて、その次の消去対象ワードラインが選択される過程が反復される。

【0086】

一方、ワードラインフリーチャージ信号(WLPRE)は、アドレスカウント信号(CACNTCK)によりイネーブルされ、フリーチャージリセット信号(WLPRERST)によってディスエーブルされるように構成することができる。

【0087】

カウント部220が最後のカウンティング動作を行うとカウンティング信号(ERQ<0:14>)はすべてローレベルになり、これらを組み合あわせて消去終了信号(ERMIN)が生成される。

【0088】

消去終了信号(ERMIN)は、最後の消去動作を行う区間であることを知らせる信号である。コントローラ300は、消去終了信号(ERMIN)がイネーブルされた後にはこれ以上プログラミングイネーブル信号(PGMP)がイネーブルできないようにする。

【0089】

このように、本発明では、単位消去動作を指定されたセットデータ記録単位で反復的に行う場合、単位消去動作をセットデータ記録単位で分けた数だけセットプログラミングイネーブル信号(ERENP)を生成し、これをプログラミングイネーブル信号(PGMP)に提供する。プログラミングイネーブル信号(PGMP)がイネーブルされると第2書き込み制御信号(SETP<0:3>)が生成されて、第2書き込み制御信号(SETP<0:3>)によって決定されるプログラム電流(I_PGM)がメモリセルへ提供される。この時、第1書き込み制御信号(RESETP)がディスエーブルの状態であることはもちろんである。

【0090】

併せて、セットプログラミングイネーブル信号(ERENP)を生成する時にアドレスカウント信号(CACNTCK)も生成されて次の消去対象ワードラインらがアクティブになることができるようにし、その一方で、現在消去完了したワードラインらがフリーチャージされるようになる。

【0091】

このような消去モードを通したセットデータ記録動作は消去区間イネーブル信号(EREN)がイネーブルされている間反復的に行われる。この消去区間イネーブル信号(EREN)は、消去モード設定信号(ERSETP)がイネーブルされた後、カウント部220が最後のカウンティング動作を完了することによって消去クロック信号(ERCK)によってディスエーブルになる。

【0092】

図12は、本発明に適用されることができるプログラムパルス生成部の一例示図である。

【0093】

図12に図示したように、プログラムパルス生成部100は、初期パルス発生部110、リセットパルス発生部120及びクエンチングパルス発生部130を含むように構成されることができる。

【0094】

初期パルス発生部110は、コントローラから提供されるプログラミングイネーブル信号(PGMP)に応答して区間設定信号(QSSETP)を生成する。区間設定信号(QSSETP)は、GSTに溶融点に近い熱を提供するための時間を決定する信号である。初期パルス発生部111は、プログラミングイネーブル信号(PGMP)に応答して予め設定された時間をカウンティングした後、区間設定信号(QSSETP)をイネーブルさせるようになる。

【0095】

リセットパルス発生部120は、プログラミングイネーブル信号(PGMP)及び区間設定信号(QSSETP)を予め設定された時間だけ遅延させて生成したリセット信号(IRSTP)に応答して第1書き込み制御信号(RESETEN)を生成する。

【0096】

一方、クエンチングパルス発生部130は、プログラミングイネーブル信号(PGMP)及び区間設定信号(QSSETP)に応答してイネーブル区間が互いに異なる第2書き込み制御信号(SETP<0:n>)を生成する。併せて、クエンチングパルス発生部130は、第2書き込み制御信号(SETP<0:n>)の生成が完了されるとプログラム完了信号(PGMNDP)を生成する。

【0097】

このような構成によって、リセットパルス発生部120は、プログラミングイネーブル信号(PGMP)がイネーブルされた後、リセット信号(IRSTP)がイネーブルされるまでの区間の間第1書き込み制御信号(RESETEN)を生成する。そして、クエンチングパルス発生部130は、プログラミングイネーブル信号(PGMP)がイネーブルされた後、区間設定信号(QSSETP)がイネーブルされるまでは第2書き込み制御信号(SETP<0:n>)を同じレベルでイネーブルさせ、区間設定信号(QSSETP)が発生した後にはイネーブル区間が調節された第2書き込み制御信号(SETP<0:n>)を生成する。

【0098】

より具体的に説明すれば次の通りである。

【0099】

まず、初期パルス発生部110は、入力ラッチ部1101、クロック発生部1103、第1カウント部1105、比較部1107及び遅延部1109を含む。

【0100】

入力ラッチ部1101は、プログラミングイネーブル信号(PGMP)及びリセット信号(IRSTP)に応答して内部クロックイネーブル信号(IPWEN)及びカウントリセット信号(IPWRST)を出力する。すなわち、プログラミングイネーブル信号(PGMP)が例えばハイレベルでイネーブルされると内部クロックイネーブル信号(IPWEN)がハイレベルに活性化され、リセット信号(IRSTP)がハイレベルでイネーブルされるとカウントリセット信号(IPWRST)がハイレベルに活性化される。

【0101】

より具体的に、入力ラッチ部1101は、内部クロックイネーブル信号(IPWEN)がハイレベルで、カウントリセット信号(IPWRST)がローレベルでイネーブルできるように構成することができ、ナンド(NAND)ゲートまたはノア(NOR)ゲートで構成されるR−Sラッチまたはフリップフロップで構成することができる。

【0102】

クロック発生部1103は、内部クロックイネーブル信号(IPWEN)に応答して内部クロック(ICK)を生成する。すなわち、クロック発生部1103は、内部クロックイネーブル信号(IPWEN)がハイレベルで活性化されている間、トグルリングする内部クロック(ICK)を出力する。

【0103】

第1カウント部1105は、内部クロックイネーブル信号(IPWEN)、カウントリセット信号(IPWRST)及び内部クロック(ICK)の制御によってカウンティングされるカウンティングコード(Q<0:3>)を出力する。すなわち、第1カウント部1105は、内部クロックイネーブル信号(IPWEN)がハイレベルで活性化された時、内部クロック(ICK)の制御によってカウンティング動作を行うようになる。カウントリセット信号(IPWRST)がハイレベルで活性化されると、第1カウント部1105から出力されるカウンティングコード(Q<0:3>)は初期化される。このように第1カウント部1105を利用してカウンティングコード(Q<0:3>)を生成する場合、回路の大きさを減少させることができる。併せて、第1カウント部1105は、例えばアップカウンターで構成することができる。

【0104】

比較部1107は、カウンティングコード(Q<0:3>)が予め設定された値に到達すると、区間設定信号(QSSETP)を活性化させて出力する。より具体的に、比較部1107は、カウンティングコード(Q<0:3>)と印加された時間調節コード(IPWSET<0:3>)とを比較して、カウンティングコード(Q<0:3>)が時間調節コード(IPWSET<0:3>)と同一である時に区間設定信号(QSSETP)を活性化させるように構成される。すなわち、時間調節コード(IPSET<0:3>)を調節して区間設定信号(QSSETP)の活性化する時点を調節できる。

【0105】

本発明の一実施形態において、第1カウント部1105を構成するカウンターの個数と時間調節コード(IPWSET)の個数とを同時に増加させると、区間設定信号(QSSETP)の発生時点を遅らせることができる。これはメモリセルを構成するGSTの溶融時間を変更できることを意味する。

【0106】

遅延部1109は、区間設定信号(QSSETP)を一定の時間遅延させてリセット信号(IRSTP)を出力する。遅延部1109の遅延値は、規定されたタイミングマージンを満足させるように設定されるべきである。そして、遅延部1109から生成されたリセット信号(IRSTP)は、入力ラッチ部1101をリセットさせて内部クロックイネーブル信号(IPWEN)をディスエーブルさせる一方、カウントリセット信号(IPWRST)をイネーブルさせる。これにより、クロック発生部1103と第1カウント部1105とがディスエーブルされるようになる。

【0107】

リセットパルス発生部120は、プログラミングイネーブル信号(PGMP)によりイネーブルされる一方、区間設定信号(QSSETP)によってディスエーブルになる。すなわち、時間調節コード(IPWSET<0:3>)によって設定された時間の間第1書き込み制御信号(RESETEN)を生成してライトドライバー400に提供する。

【0108】

次に、クエンチングパルス発生部130は、入力ラッチ部1301、クロック発生部1303、第2カウント部1305、リセット制御部1307及び遅延部1309を含むように構成されることができる。

【0109】

入力ラッチ部1301は、区間設定信号(QSSETP)及びリセット信号(QSRSTP)に応答してカウントイネーブル信号(CNTENB)及び内部クロックイネーブル信号(QSEN)を出力する。クロック発生部1303は、内部クロックイネーブル信号(QSEN)に応答して内部クロック(QSCK)を生成する。すなわち、クロック発生部1303は、内部クロックイネーブル信号(QSEN)がハイレベルで活性化されている間トグルリングする内部クロック(QSCK)を出力する。

【0110】

第2カウント部1305は、カウントイネーブル信号(CNTENB)、内部クロック(QSCK)、プログラミングイネーブル信号(PGMP)及びリセット信号(QSRSTP)に応答して第2書き込み制御信号(SETP<0:3>)を出力する。したがって、第2書き込み制御信号(SETP<0:3>)のアップデート周期は、内部クロック(QSCK)のトグルリング周期に対応して調節される。

【0111】

本発明の一実施形態において、第2カウント部1305は、ダウンカウンターを含むように構成できる。この場合、第2カウント部1305は、0x1111bから0x0000bになるまで動作をし、最終の出力が0x0000bになると、第2書き込み制御信号(SETP<3>)の出力信号がリセット制御部1307を駆動させる。

【0112】

リセット制御部1307は、第2カウント部1305から出力される第2書き込み制御信号(SETP<0:3>)のコード値が予め設定された値に到達すると、すなわち第2書き込み制御信号(SETP<3>)の出力信号がハイレベルからローレベルに遷移することによってリセット信号(QSRSTP)をイネーブルさせる。

【0113】

このために、リセット制御部1307は、カウント終了制御部及びパルス発生部を含むことができる。カウント終了制御部は、第2カウント部1305からカウントが完了されることによってクエンチングパルス完了信号(QSND)を生成する。パルス発生部は、クエンチングパルス完了信号(QSND)に応答してリセット信号(QSRSTP)を生成する。例えば、カウント終了制御部から出力されるクエンチングパルス完了信号(QSND)は、プログラミングイネーブル信号(PGMP)によってハイレベルを維持するが、第2書き込み制御信号(SETP<3>)がローレベルになるとローレベルに遷移する。そして、パルス発生部は、ローレベルに遷移したクエンチングパルス完了信号(QSND)によってリセット信号(QSRSTP)をイネーブルさせる。

【0114】

一方、遅延部1309は、リセット信号(QSRSTP)を予め設定された時間だけ遅延させてプログラム完了信号(PGMNDP)を生成する。プログラム完了信号(PGMNDP)は、コントローラへ伝送されてプログラムが完了されたことを知らせる。

【0115】

図13は、図12に図示した第1カウント部の構成を説明するための一例示図である。

【0116】

本発明の一実施形態において、第1カウント部1105は、複数の1ビットアップカウンターで構成することができ、図13にはアップカウンターの一例が表わされている。

【0117】

図13を参照すると、1ビットアップカウンター150は、信号入力部151、ラッチ部153及びキャリー発生部155を含むことができる。

【0118】

信号入力部151は、カウントイネーブル信号、本発明では内部クロックイネーブル信号(IPWEN)と第1カウンティングコード(Q<0>)に応答してラッチ部153の入力ノード(A)の信号レベルを決定する。

【0119】

ラッチ部153は、内部クロック(ICK)の制御によって信号入力部151から出力される信号をラッチングして第1カウンティングコード(Q<0>)を出力し、キャリー発生部155は、内部クロックイネーブル信号(IPWEN)と第1カウンティングコード(Q<0>)とによってキャリー信号(COUT)を出力する。この時、キャリー信号(COUT)は、次の端の1ビットアップカウンターのカウントイネーブル信号として利用される。一方、ラッチ部153は、カウントリセット信号(IPWRST)に応答して内部ノードが初期化され、または、特定レベルに変化される。

【0120】

より具体的に、信号入力部151は、内部クロックイネーブル信号(IPWEN)がローレベルでディスエーブルされると、出力ノードであるQの結果値をそのまま選択し、内部クロックイネーブル信号(IPWEN)がハイレベルでイネーブルされると、出力ノードであるQの結果値を反対に選択して次の端の1ビットアップカウンターへ伝達する。

【0121】

ラッチ部153は、ノードAの信号がローレベルである場合にはノードAの信号をノードCに伝達する一方、ノードAの信号がハイレベルである場合にはノードAの信号をノードQに伝達する。

【0122】

カウントリセット信号(IPWRST)がハイレベルになると出力ノードQはロー状態にリセットされ、キャリー発生部155は先端の1ビットアップカウンターの出力ノードQに印加される信号をカウントイネーブル信号として動作する。すなわち、先端の1ビットアップカウンターの出力ノードQに印加される信号レベルによって次に次の端の1ビットアップカウンターがトグルされるようになる。

【0123】

図14は、図12に図示した比較部の一例示図である。

【0124】

図14を参照すると、比較部1107は、複数の比較部71、72、73、74と、信号組合せ部75とを含むことができる。複数の比較部71、72、73、74は、カウンティングコード(Q<0:3>)及び時間調節コード(IPWSET<0:3>)の各ビット値を比較して複数の比較結果信号として出力する。信号組合せ部75は、複数の比較部71、72、73、74から出力される複数の比較結果信号を組み合せて区間設定信号(QSSETP)として出力する。すなわち、本実施形態において、比較部1107は、カウンティングコード(Q<0:3>)と時間調節コード(IPWSET<0:3>)とが同一である時、区間設定信号(QSSETP)をアクティブさせて出力する。

【0125】

図15は、図8に図示したカウント部及び図12に図示した第2カウント部の構成を説明するための図面である。

【0126】

本発明の一実施形態において、図8に図示した区間設定部241はダウンカウンターで構成することができ、例えば、1ビットダウンカウンターで構成できる。

【0127】

図15を参照すると、1ビットダウンカウンター160は、信号入力部161、ラッチ部163及びバーロー発生部165を含むことができる。

【0128】

信号入力部161は、カウントイネーブル信号(CNTINB)と出力ノードQに印加されるデータレベルとによってラッチ部163の入力ノード(A)の信号レベルを決定する。

【0129】

ラッチ部163は、クロック信号(CK)の制御によって信号入力部161から出力される信号をラッチングした後、ラッチングしたデータを出力ノードQに伝達する。

【0130】

また、バーロー発生部165は、カウントイネーブル信号(CNTINB)とラッチ部163の出力ノードQに印加される信号レベルとによってバーロー(borrow)信号(BOUTB)を出力する。

【0131】

一方、ラッチ部163は、リセット信号(RSTP)及びセット信号(SETP)に応答して内部ノードが初期化され、または、特定レベルに変化される。

【0132】

より具体的に、信号入力部161は、カウントイネーブル信号(CNTINB)がハイレベルにディスエーブルされると、出力ノードであるQの結果値をそのまま選択し、カウントイネーブル信号(CNTINB)がローレベルでイネーブルされると、出力ノードであるQの結果値を反対に選択して次の端へ伝達する。

【0133】

信号入力部161で選択した信号はノードAに印加される。これによってラッチ部163は、ノードAの信号がローレベルである場合にはノードAの信号をノードCに伝達する一方、ノードAの信号がハイレベルである場合にはノードAの信号をノードQに伝達する。

【0134】

一方、セット信号(SETP)がハイレベルになると出力ノードQがハイレベルに設定される。そして、リセット信号(RSTP)がハイレベルになると出力ノードQはローレベルでリセットされる。

【0135】

バーロー発生部165は、先端のカウンターの出力ノードQがローレベルになると、ローレベルのバーロー信号(BOUTB)を出力する。

【0136】

図16は、本発明に適用されることができるライトドライバーの一例示図である。

【0137】

図16を参照すると、ライトドライバー400は、電流調節部410、電流駆動部420及び選択部430を含むことができる。

【0138】

電流調節部410は、プログラムするデータ(DATA)を入力して、ライトイネーブル信号(WDEN)が活性化された時、第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<:3>)のコード組合せによって制御ノード(N1)の電圧レベルを調節する。この時、第2書き込み制御信号(SETP<0:3>)の制御を受ける複数のNMOSトランジスターは、選択的にターンオン(TURNON)されて制御ノード(N1)の電圧レベルを調節するようになる。また、第1書き込み制御信号(RESETP)の制御を受けるNMOSトランジスターは、第1書き込み制御信号(RESETP)が活性化された時、ターンオン(TURNON)になって制御ノード(N1)の電圧レベルを調節するようになる。

【0139】

ここで、第2書き込み制御コード(SETP<0:3>)は、周期的にアップデートされる信号であり、第1書き込み制御信号(RESETP)は、パルス形態で入力される信号である。

【0140】

電流駆動部420は、制御ノード(N1)の電圧レベルに対応する大きさを有するプログラミング電流パルス(I_PGM)を出力端(N2)に駆動する。この時、プログラミング電流パルス(I_PGM)は、第1書き込み制御信号(RESETP)に対応する第1プログラミング電流パルスと、第2書き込み制御信号(SETP<0:3>)に対応する第2プログラミング電流パルスとで区分できるものである。

【0141】

選択部430は、電流駆動部420で駆動されるプログラミング電流パルス(I_PGM)を複数のビットライン選択スイッチ制御信号(YSW<0:m>)に対応する該当ビットライン(BL0〜BLm)に出力する。

【0142】

図17は、本発明の一実施形態によるセットプログラム動作を説明するためのタイミング図であり、図8を再び参照して説明する。

【0143】

消去命令に応答したセットプログラム動作が開始する前に、セットプログラム動作に必要な信号(命令語コード、アドレス等)がレジスターに臨時に保存される。

【0144】

その後、プログラム命令(PGM)が印加されることによってコントローラからプログラミングイネーブル信号(PGMP)が生成され、セットプログラムパルス発生部240はプログラミングイネーブル信号(PGMP)をセットプログラミングイネーブル信号(ERENP)としてそのまま伝達する。一方、セットプログラムパルス発生部240の区間設定部241は、コントローラ300から提供される消去モード設定信号(ERSETP)に応答して消去区間イネーブル信号(EREN)をイネーブルさせる。

【0145】

一方、カウント部220は、消去回数カウント信号(ERCNTB)と、プログラム完了信号(PGMNDP)から生成されるクロック信号(ERCNTCK)及び消去命令(ERASE)に応答して生成されるクロック信号(ERCK)及び消去イネーブル信号(IEREN)に応答してカウントを行い、その結果カウンティング信号(ERQ<0:14>)を生成してモード判定部(230)に提供する。

【0146】

第1書き込み制御信号(RESETP)はディスエーブル状態であり、セットプログラミングイネーブル信号(ERENP)がイネーブルされる時ごとにイネーブルされるプログラミングイネーブル信号(PGMP)により第2書き込み制御信号(SETP<0:3>)によってメモリセルにプログラム電流(I_PGM)が印加されてセットデータが記録される。

【0147】

すなわち、プログラムパルス生成部100の初期パルス発生部110から内部クロックイネーブル信号(IPWEN)が生成される。そして、これにより内部クロック(ICK)が生成された後、予め設定された時間をカウントしてカウンティングコード(Q<0:3>)が生成され、カウンティングが完了されると区間設定信号(QSSETP)が生成される。

【0148】

一方、リセットパルス発生部120はディスエーブルさせ、クエンチングパルス発生部130は区間設定信号(QSSETP)に応答してカウントイネーブル信号(CKEN)(CNTENB)及び内部クロック(QSCK)を生成する。そして、これによってイネーブルの区間が互いに異なる第2書き込み制御信号(SETP<0:3>)を生成する。第2書き込み制御信号(SETP<0:3>)の生成が完了されるとクエンチングパルス完了信号(QSND)がディスエーブルされ、これによりリセット信号(QSRSTP)がイネーブルされるとプログラム完了信号(PGMNDP)が出力される。この場合、第2書き込み制御信号(SETP<0:3>)のイネーブルの区間によってライトドライバーの電流駆動力が順次に減殺されてメモリセルにクエンチングパルスが供給されるようになる。

【0149】

初回のプログラム動作の後、発生されるプログラム完了信号(PGMNDP)はセットプログラム制御回路200へ提供され、以後にはカウント部220が初期値を0までダウンカウンティングする時ごとにプログラム完了信号(PGMNDP)をセットプログラミングイネーブル信号(ERENP)として出力して、セットデータ記録動作がなされる。

【0150】

したがって、128KB単位の消去モード時にワードラインを128個単位で順次イネーブルさせ、128個のワードラインがイネーブルされた状態で32ビット単位でセットデータを記録する時に、合計32,768回のセットプログラミングイネーブル信号(ERENP)がイネーブルされるはずである。併せて、ワードラインは128個単位で512番にかけて選択されてイネーブルされ、セットプログラミングイネーブル信号(ERENP)がイネーブルされる時、アドレスカウント信号(CACNTCK)によって次のワードラインを選択する一方、現在消去されたワードラインらに対するフリーチャージを行うことができる。

【0151】

このように、本発明の属する技術分野の当業者は、本発明がその技術的思想や必須的特徴を変更せずに、他の具体的な形態で実施され得るということが理解できるであろう。したがって、以上で記述した実施形態は、あらゆる面で例示的なものであり、限定的なものではないものと理解しなければならない。本発明の範囲は、上記の詳細な説明よりは、後述する特許請求の範囲によって表わされ、特許請求の範囲の意味及び範囲、そして、その等価概念から導き出されるあらゆる変更または変形された形態が本発明の範囲に含まれるものと解析されるべきである。

【符号の説明】

【0152】

10 半導体メモリ装置

100 プログラムパルス生成部

200 セットプログラム制御回路

300 コントローラ

400 ライトドライバー

500 メモリ部

210 制御信号生成部

220 カウント部

230 モード判定部

240 セットプログラムパルス発生部

【技術分野】

【0001】

本発明は半導体システムに関するもので、より具体的には半導体メモリ装置と、このためのセットプログラム制御回路及びプログラム方法に関するものである。

【背景技術】

【0002】

PCRAM(Phase Change RAM)はメモリセルを構成する特定物質の相(phase)変換特性を用いたメモリ素子である。相変化物質は温度条件によって非晶質状態(Amorphous State)または、結晶質状態(Crystalline State)に転換されることができる物質であり、例えば、カルコゲナイド係合金(Chalcogenidealloy)を挙げることができる。また、代表的な相変化物質としては、ゲルマニウム(Germanium)、アンチモン(Antimony)、テルル(Tellurium)を用いたGe2Sb2Te5(以下、GST)物質を挙げることができる。

【0003】

大部分の物質は、物質ごとにメルティングポイント(溶融点)と結晶化する温度が互いに異なり、冷却される時間と温度によって結晶を形成する程度も互いに異なる。これは各物質等の固有特性の中の1つであり、特にGSTという物質は他の物質より非晶質状態と結晶質状態の区分がさらに優秀である。

【0004】

図1は一般的な相変化物質の温度による相変化状態を説明するための一例示として、GSTという物質を例に挙げて説明している。

【0005】

GSTは、メルティングポイント以上の高温に一定時間(数十〜数百ns)の間維持された後、指定された時間(Tq)に急冷(Quenching)されると非晶質状態がそのまま維持されて抵抗値が数百kΩ〜数MΩになる。

【0006】

また、結晶化温度(Crystallization temperature)範囲に一定時間の間(数百ns〜数μs)維持された後、冷却されると結晶状態になって抵抗が数kΩ〜数十kΩになるが、結晶化温度に維持される時間が長いほど結晶状態がさらに優秀になってより小さな抵抗値を有することができる。

【0007】

図2は、一般的な相変化物質の温度による相変化状態を説明するための他の例示図として、同様にGSTという物質を例に挙げて説明している。

【0008】

図2では、一定時間の間メルティングポイントの近くまで温度を供給した後、徐々に冷却させる方法でGSTを結晶化させる例を表す。このようにする場合にもGSTの抵抗が数kΩ〜数十kΩになるが、やはり冷却させる時間が長いほど結晶状態はさらに優秀になる。また、図1の場合より必要とされる結晶化の時間も短くなる。

【0009】

GSTのこのような特性を利用するために直接的に熱を制御する方法もあるが、導体または半導体に流される電流により発生するジュール熱(Joule heating)を利用した電気的な方法でGSTの状態を非晶質状態と結晶質状態とで変化させる方法が利用されている。

【0010】

前述した図1及び図2には相変化メモリ素子の一般的な動作を図式化したものであって、セットデータプログラム時間、すなわちGSTを結晶化するのに必要となる時間が短い図2の方法を主に使用する。

【0011】

図3は、一般的な相変化メモリ装置のセルアレイ構成図である。

【0012】

図3に図示したように、各メモリセル(MC)は、ワードライン(WL)及びビットライン(BL)の間に接続される相変化物質(GST)とスイチング素子(D)とで構成さることが分かる。

【0013】

このような相変化メモリ装置のプログラム動作を図4を参照して説明する。

【0014】

図4は、一般的な相変化メモリ装置の構成図である。

【0015】

図4を参照すると、相変化メモリ装置1は、プログラムパルス生成部11、ライトドライバー12及びメモリ部13を含む。

【0016】

プログラムパルス生成部11は、コントローラ(不図示)から発生されるプログラミングイネーブル信号(PGMP)に応答して第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<0:n>)を生成してライトドライバー12へ提供する。併せて、第1及び第2制御信号の生成動作が完了されるとプログラム完了信号(PGMNDP)を生成してコントローラへ伝送する。

【0017】

ライトドライバー12は、ライトイネーブル信号(WDEN)に応答して駆動する。そして、プログラムパルス生成部11から第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<0:n>)を受信して、プログラムするデータ(DATA)及びビットライン選択スイッチ制御信号(YSW<0:m>)に応答してメモリ部13へプログラム電流(I_PGM)を供給する。

【0018】

これによって、メモリ部13には、プログラムしようとするデータ(DATA)のレベルによってGSTの抵抗状態が変化されてデータが記録されることができる。

【0019】

図5は、図4に図示したプログラムパルス生成部の一例示図である。

【0020】

図5に図示したように、プログラムパルス生成部11は、初期パルス発生部111、リセットパルス発生部113及びクエンチング(quenching)パルス発生部115を含むように構成される。

【0021】

初期パルス発生部111は、コントローラから提供されるプログラミングイネーブル信号(PGMP)に応答して区間設定信号(QSSETP)を生成する。区間設定信号(QSSETP)は、GSTへ溶融点に近い熱を提供するための時間を決定する信号で、初期パルス発生部111は、プログラミングイネーブル信号(PGMP)に応答して予め設定された時間をカウンティングした後、区間設定信号(QSSETP)をイネーブルさせるようになる。

【0022】

リセットパルス発生部113は、プログラミングイネーブル信号(PGMP)及び区間設定信号(QSSETP)を予め設定された時間を遅延させて生成したリセット信号(IRSTP)に応答して第1書き込み制御信号(RESETEN)を生成する。

【0023】

一方、クエンチングパルス発生部115は、プログラミングイネーブル信号(PGMP)及び区間設定信号(QSSETP)に応答してイネーブル区間が互いに異なる第2書き込み制御信号(SETP<0:n>)を生成する。併せて、クエンチングパルス発生部115は、第2書き込み制御信号(SETP<0:n>)の生成が完了されるとプログラム完了信号(PGMNDP)を生成する。

【0024】

このような構成によって、リセットパルス発生部113は、プログラミングイネーブル信号(PGMP)がイネーブルされた後、リセット信号(IRSTP)がイネーブルされるまでの区間の間第1書き込み制御信号(RESETEN)を生成する。そして、クエンチングパルス発生部115は、プログラミングイネーブル信号(PGMP)がイネーブルされた後、区間設定信号(QSSETP)がイネーブルされるまでは第2書き込み制御信号(SETP<0:n>)を同一なレベルでイネーブルさせ、区間設定信号(QSSETP)が発生した後には、イネーブルの区間が調節された第2書き込み制御信号(SETP<0:n>)を生成する。

【0025】

図6は、一般的な相変化メモリ素子のプログラム動作を説明するためのタイミング図である。

【0026】

プログラム命令(PGM)が印加されることによってコントローラからプログラミングイネーブル信号(PGMP)が生成されて、これによって初期パルス発生部111が動作して内部クロックイネーブル信号(IPWEN)を生成する。そして、これから内部クロック(ICK)が生成された後、予め設定された時間をカウントしてカウンティングコード(Q<0:3>)が生成され、カウンティングが完了されると区間設定信号(QSSETP)が生成される。

【0027】

一方、リセットパルス発生部113は、プログラミングイネーブル信号(PGMP)に応答して第1書き込み制御信号(RESETEN)をイネーブルさせて、区間設定信号(QSSETP)を予め設定された時間の間遅延させて生成したリセット信号(IRSTP)がイネーブルされることによって第1書き込み制御信号(RESETEN)をディスエーブルさせる。そして、第1書き込み制御信号(RESETEN)がイネーブルされている区間の間ライトドライバーからプログラミング電流が生成されてビットライン(BL0)に供給される。

【0028】

クエンチングパルス発生部115は、区間設定信号(QSSETP)に応答してカウントイネーブル信号(CKEN(CNTENB))及び内部クロック(QSCK)を生成する。そして、これによってイネーブル区間が互いに異なる第2書き込み制御信号(SETP<0:3>)を生成する。第2書き込み制御信号(SETP<0:3>)の生成が完了されるとクエンチングパルス完了信号(QSND)がディスエーブルになり、これからリセット信号(QSRSTP)がイネーブルされるとプログラム完了信号(PGMNDP)が出力される。この場合、第2書き込み制御信号(SETP<0:3>)のイネーブル区間によってライトドライバーの電流駆動力が順次に減殺されてGSTにクエンチングパルスが供給されるようになる。

【0029】

プログラム動作の時、ワードラインは、ワードライン選択スイッチがディスエーブル状態である場合、高電位(VCC以上)を維持するが、ワードライン選択スイッチがイネーブルされると接地電圧レベルにディスチャージされる。併せて、ライトドライバーによって選択されるビットラインによりライトドライバー−ビットライン選択スイッチ−ビットライン−スイチング素子−GST−ワードラインに達するまで電流パスが形成される。

【0030】

このように電流パスが形成された状態でプログラムしようとするデータレベル(0/1)によって第1書き込み制御信号(RESETEN)または第2書き込み制御信号(SETP<0:n>)によりライトドライバーで駆動される電流量が決定されてビットラインを通してメモリセルにプログラム電流が供給される。例えば、第1書き込み制御信号(RESETEN)により供給される電流を100と仮定すると、第2書き込み制御信号(SETP<0:3>)がすべてイネーブルされる場合のメモリセルに供給される電流は30〜90%程度の割合で調節される。

【0031】

プログラム動作の時、ビットラインを通して供給される電流は、リセットデータの場合には短形波(Rectangular Type)の様子で供給されて、セットデータの場合には初期には短形波と類似の形態で供給されるが第2書き込み制御信号(SETP<0:n>)により階段波の形態であり、減少する形態で供給される。

【0032】

したがって、セットデータとリセットデータを同時にプログラムする場合、プログラム動作に要する時間は長い時間が要求されるセットデータプログラム時間によって決定されるようになる。

【0033】

一方、相変化メモリ装置はフラッシュメモリの変わりに使われている趨勢がある。この場合、メモリ装置はフラッシュのインターフェースを通してプログラム命令、消去命令を受けて該当する動作を行う。しかし、相変化メモリ装置はライト命令によってセットデータまたはリセットデータをプログラムするだけであり、したがって、相変化メモリ装置をフラッシュメモリのインターフェースで動作させようとする場合、消去命令が印加された場合いかなる動作もすることなく遊休状態となる。

【先行技術文献】

【特許文献】

【0034】

【特許文献1】米国特許第7936619号明細書

【発明の概要】

【発明が解決しようとする課題】

【0035】

本発明は、消去命令に応答して複数の不揮発性メモリセルにセットデータをプログラムできる半導体メモリ装置と、このためのセットプログラム制御回路及びプログラム方法を提供する。

【課題を解決するための手段】

【0036】

本発明の一態様に係る半導体メモリ装置は、プログラミングイネーブル信号に応答して第1書き込み制御信号、第2書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、消去命令及び前記プログラム完了信号に応答してセットプログラミングイネーブル信号を指定された回数だけ反復生成するセットプログラム制御回路と、前記消去命令に応答して前記第1書き込み制御信号をディスエーブルし、前記セットプログラミングイネーブル信号に応答して前記プログラミングイネーブル信号を生成するコントローラとを備えることができる。

【0037】

また、本発明の他の態様に係る半導体メモリ装置は、消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号を生成し、該セットプログラミングイネーブル信号に応答して生成されるプログラミングイネーブル信号によって第1書き込み制御信号及び第2書き込み制御信号を出力するプログラムパルス生成部と、前記第1書き込み制御信号及び前記第2書き込み制御信号に応答して生成されるプログラムパルスをメモリ部へ提供するライトドライバーとを備えることができる。

【0038】

また、本発明の他の態様に係るセットプログラム制御回路は、セットプログラミングイネーブル信号によって生成されるプログラミングイネーブル信号に応答してプログラム完了信号を生成するプログラムパルス生成部と接続され、消去命令及び前記プログラム完了信号に応答して前記セットプログラミングイネーブル信号を生成することができる。

【0039】

また、本発明の他の態様に係るプログラム方法は、プログラムパルス生成部を具備する半導体メモリ装置にセットデータが入力される段階と、前記プログラムパルス生成部が消去動作の基本単位及びセットデータ記録単位によって設定された回数だけプログラミングイネーブル信号を反復生成する段階と、前記プログラミングイネーブル信号に応答して、ライトドライバーがメモリ部の選択された領域にデータをプログラムする段階とを含むことができる。

【発明の効果】

【0040】

本発明によると、消去命令に応答してセットデータをプログラムすることによってデータ記録に要する時間を短縮させることができる。

【図面の簡単な説明】

【0041】

【図1】一般的な相変化物質の温度による相変化状態を説明するための一例示図である。

【図2】一般的な相変化物質の温度による相変化状態を説明するための異なる例示図である。

【図3】一般的な相変化メモリ装置のセルアレイ構成図である。

【図4】一般的な相変化メモリ装置の構成図である。

【図5】図4に図示したプログラムパルス生成部の一例示図である。

【図6】一般的な相変化メモリ素子のプログラム動作を説明するためのタイミング図である。

【図7】本発明の一実施形態に係る半導体メモリ装置の構成図である。

【図8】本発明の一実施形態に係るセットプログラム制御回路の構成図である。

【図9】図8に図示した制御信号生成部の一例示図である。

【図10】図8に図示したモード判定部の一例示図である。

【図11】図9に図示したパルス出力部の一例示図である。

【図12】本発明に適用されることができるプログラムパルス生成部の一例示図である。

【図13】図12に図示した第1カウント部の構成を説明するための一例示図である。

【図14】図12に図示した比較部の一例示図である。

【図15】図8に図示したカウント部及び図12に図示した第2カウント部の構成を説明するための図である。

【図16】本発明に適用されることができるライトドライバーの一例示図である。

【図17】本発明の一実施形態によるセットプログラム動作を説明するためのタイミング図である。

【発明を実施するための形態】

【0042】

半導体メモリ装置、特にフラッシュメモリ装置の標準規格ではリセットデータを記録することをプログラム動作と定義しており、特に16ビット単位でプログラムすることをシングルワードプログラム(single word program)、512バイト(256ワード)単位でプログラムすることをバッファープログラム(buffered program)であると定義している。また、リセットデータとセットデータを同時に記録することをオーバーライト(over write)と定義している。そして、16ビット単位でセット/リセットデータを同時に記録することをシングルワードオーバーライト、512バイト(256ワード)単位でセット/リセットデータを同時に記録することをバッファーオーバーライトと定義している。

【0043】

本発明では不揮発性メモリ装置、望ましくは電流駆動方式により駆動される不揮発性メモリ装置をフラッシュメモリのインターフェースを利用して動作させる場合、128KB単位の消去命令に応答してメモリ装置がセットデータを記録するように定義して、消去命令が入力される場合、複数の不揮発性メモリセルにセットデータを記録する方案を提案する。

【0044】

これによって、消去命令が入力される時にもメモリ装置を動作させることができ、動作効率が改善される。さらに、セットデータを記録する時間より相対的に短い時間の間に行われるリセットデータ記録時間がセットデータ記録時間に独立的なのでデータ記録速度を向上させることができる。

【0045】

このために、不揮発性メモリ装置、望ましくはフラッシュメモリ装置の標準規格を基盤として、セットプログラム動作に必要な信号(命令語コード、アドレス等)がレジスターに臨時に保存されて、命令語実行コードがイネーブルされることによってレジスターに保存されている信号を用いてセットプログラムがなされるようになる。

【0046】

一例として、相変化メモリ装置は、電流駆動能力の限界でセットデータの記録が32ビット単位でなされる。ところが不揮発性メモリ装置の標準規格では消去動作が128KB単位でなされるので合計32,768回のセットデータ記録動作が行われるようになる。したがって、消去動作の基本単位(128KB)をセットデータ記録単位(32ビット)で分けた数(32,768回)だけ消去動作が反復的に行われるようになると複数のメモリセルにセットデータを記録できるようになる。フラッシュメモリのインターフェース基盤で、バッファープログラムまたはバッファーオーバーライト動作は512B単位でなされる。したがって、128個(512B/32ビット)ずつワードラインを選択して128KB/512B回だけの消去動作が行われることができる。結局、消去命令に応答して一回の消去動作時32ビットのメモリセルにセットデータが記録される動作を反復的に行って、メモリセルにセットデータを順次に記録することができる。

【0047】

以下、添付された図面を参照して本発明の実施形態をより具体的に説明する。

【0048】

図7は、本発明の一実施形態に係る半導体メモリ装置の構成図である。

【0049】

図7を参照すると、半導体メモリ装置10は、プログラミングイネーブル信号(PGMP)によって第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<0:n>)を生成するプログラムパルス生成部100、消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号(ERENP)を指定された回数で反復生成するセットプログラム制御回路200、プログラミングイネーブル信号(PGMP)をはじめとするプログラム動作関連制御信号、アドレス、データ信号を提供するコントローラ300、プログラムパルス生成部100から提供される書き込み制御信号(RESETEN、SETP<0:n>)及びビットライン選択スイッチ制御信号(YSW<0:m>)に応答して入力データ(DATA)をプログラムするためのプログラム電流(I_PGM)を生成するライトドライバー400及び複数のメモリセルを含んでライトドライバー400から提供される電流によって各メモリセルにデータが記録されるメモリ部500を含む。

【0050】

このような半導体メモリ装置10において、セットプログラム制御回路200は、消去命令(ERASE)に応答して予め設定された回数だけ消去動作、すなわち、セットデータ記録動作が反復的に行われるようにするセットプログラミングイネーブル信号(ERENP)を生成してコントローラ300へ提供する。そして、コントローラ300は、セットプログラミングイネーブル信号(ERENP)に応答して生成したプログラミングイネーブル信号(PGMP)をプログラムパルス生成部100へ提供して、予め設定された回数だけ消去(セットデータ記録)動作が行われるようにする。

【0051】

また、セットプログラム制御回路200は、指定された個数のワードラインが選択されて消去動作が行われた後、次のワードラインを選択するためのアドレスカウント信号(CACNTCK)及び現在消去動作を行ったワードラインをフリーチャージさせるためのワードラインフリーチャージ信号(WLPRE)をコントローラ300へ提供する。

【0052】

併せて、セットプログラム制御回路200は、消去命令によるセットデータ記録が行われる間消去区間イネーブル信号(EREN)をイネーブルさせる一方、最後の消去動作が始まると消去終了信号(ERMIN)を生成してコントローラ300へ提供してこれ以上プログラミングイネーブル信号(PGMP)が生成されないようにする。

【0053】

各構成部の動作をより具体的に説明すれば次の通りである。

【0054】

プログラムパルス生成部100は、コントローラ300から発生されるプログラミングイネーブル信号(PGMP)に応答して第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<0:n>)を生成してライトドライバー400へ提供する。併せて、第1及び第2書き込み制御信号(RESETEN、SETP<0:n>)の生成動作が完了するとプログラム完了信号(PGMNDP)を生成し、これをセットプログラム制御回路200に伝える。

【0055】

本発明の望ましい実施形態において、消去動作時にはセットデータの記録だけなされるので、コントローラ300によって消去命令(ERASE)がイネーブルされると第1書き込み制御信号(RESETEN)はディスエーブルされるように制御する。そして、第2書き込み制御信号(SETP<0:n>)の生成が完了するとプログラム完了信号(PGMNDP)がイネーブルされ、これはセットプログラム制御回路200のクロック信号(図9のERCNTCK)として作用するようになる。

【0056】

ライトドライバー400は、ライトイネーブル信号(WDEN)に応答して駆動される。そして、プログラムパルス生成部100から第1書き込み制御信号(RESETEN)及び/または第2書き込み制御信号(SETP<0:n>)を受けて、プログラムするデータ(DATA)及びビットライン選択スイッチ制御信号(YSW<0:m>)に応答してメモリ部500へプログラム電流(I_PGM)を供給する。

【0057】

これによって、メモリ部500にはプログラムしようとするデータ(DATA)のレベルによってデータが記録されることができる。本発明の一実施形態において、メモリ部500は、電流駆動方式によってデータが記録され、センシングされるメモリセルを用いて構成することができる。電流駆動方式によりプログラム及びセンシングがなされるメモリセルとしては、例えば相変化メモリセル、磁気メモリセルなどを用いることができる。

【0058】

セットプログラム制御回路200は、プログラムパルス生成部100から提供されるプログラム完了信号(PGMNDP)をクロック信号(図9のERCNTCK)として利用して、不揮発性メモリ装置の標準規格で定義している消去動作の基本単位(例えば、128KB)及びセットデータ記録単位(例えば、32ビット)に基づいてセットプログラミングイネーブル信号(ERENP)を生成する。例えば、セットデータ記録単位が32ビットである場合128KBの消去動作のために32,768回のカウンティングを行い、カウンティングが行われる時ごとにセットプログラミングイネーブル信号(ERENP)をイネーブルさせるものである。また、指定された個数(例えば128個)のワードラインを同時に選択して消去動作が行われるように、選択されたワードラインに対する消去動作が完了されるとアドレスカウント信号(CACNTCK)を生成して次の消去対象のワードラインらが選択されることができるようにする。一方、現在消去動作が行われたワードラインをフリーチャージさせるためのワードラインフリーチャージ信号(WLPRE)を生成する。

【0059】

併せて、消去命令(ERASE)に応答して消去動作が始まると、消去区間イネーブル信号(EREN)を生成して消去動作が遂行中であることを知らせて、最後のカウンティングが行われると、すなわち、最後の消去動作が始まると、消去終了信号(ERMIN)を生成してこれ以上プログラミングイネーブル信号(PGMP)が生成されないようにする。

【0060】

なお、図7では、セットプログラム制御回路200をプログラムパルス生成部100と独立的に図示したが、セットプログラム制御回路200がプログラムパルス生成部100に含まれるように構成することも可能である。すなわち、プログラムパルス生成部100は、セットプログラム制御回路200を含むことができる。

【0061】

図8は、本発明の一実施形態に係るセットプログラム制御回路の構成図である。

【0062】

図8を参照すると、セットプログラム制御回路200は、制御信号生成部210、カウント部220、モード判定部230及びセットプログラムパルス発生部240を含むように構成できる。

【0063】

制御信号生成部210は、コントローラ300から提供されるカウントイネーブル信号(ERCNTINB)及び消去命令(ERASE)に応答して消去回数カウント信号(ERCNTB)を生成する。また、プログラム完了信号(PGMNDP)から生成されるクロック信号(ERCNTCK)及び消去命令(ERASE)に応答して消去クロック信号(ERCK)を生成する。これに加えて、カウント部220の動作をリセットさせなければならない多様な場合に現れる得る状況を併合して消去リセット信号(ERRST)を生成する。消去リセット信号(ERRST)の生成に作用する信号は、サスペンド信号(ERSUS)、プログラムリセット信号(PGMRSTP)、エラー信号(ERABT)、リセット信号(RSTP)などであり得るが、これに限定されるものではない。併せて、制御信号生成部210は、コントローラ300から提供される消去モード設定信号(ERSETP)に応答して消去イネーブル信号(IEREN)を生成する。

【0064】

一方、消去回数カウント信号(ERCNTB)、消去クロック信号(ERCK)、消去リセット信号(ERRST)及び消去イネーブル信号(IEREN)は各々、サスペンド信号(ERSUS)が発生しない場合イネーブルされる。サスペンド信号(ERSUS)は、消去命令が入力されて内部的に消去動作をしている間、少しの間消去動作を止めて異なる動作をしようとする時にイネーブルされる。消去動作の中止の時に行われることができる動作としては、データリード(Read)、状態(status)リード、またはローデータバッファー(Row Data Buffer)ライト動作があり得る。

【0065】

図9は、図8に図示した制御信号生成部の一例示図である。

【0066】

カウントイネーブル信号(ERCNTINB)がローレベルでイネーブルされ、クロック信号(ERCNTCK)及び消去命令(ERASE)が入力されると、サスペンド信号(ERSUS)がディスエーブルの状態である場合にだけ消去回数カウント信号(ERCNTB)と消去クロック信号(ERCK)とがカウント部220へ伝えられることが分かる。また、消去リセット信号(ERRST)は、サスペンド信号(ERSUS)、プログラムリセット信号(PGMRSTP)、エラー信号(ERABT)、リセット信号(RSTP)のうちいずれか一つでもイネーブルされるとイネーブルされる。併せて、消去イネーブル信号(IEREN)は、消去モード設定信号(ERSETP)がイネーブルされ、サスペンド信号(ERSUS)がディスエーブル状態である場合、イネーブルされることがわかる。

【0067】

再び、図8を参照すると、カウント部220は、制御信号生成部210から提供される消去回数カウント信号(ERCNTB)、消去クロック信号(ERCK)、消去リセット信号(ERRST)及び消去イネーブル信号(IEREN)と、コントローラから提供されるフリーチャージリセット信号(WLPRERST)とに応答してカウンティング動作を行う。

【0068】

まず、消去回数カウント信号(ERCNTB)がイネーブルされることによってカウント部220が動作可能な状態になり、消去イネーブル信号(IEREN)によって初期値が設定される。そして、消去クロック信号(ERCK)に応答してカウンティングを遂行し、その結果としてカウンティング信号(ERQ<0:x>)を出力する。

【0069】

本発明の一実施形態において、消去モードが128KB単位で行われ、一回の消去動作時に32ビットのメモリセルにセットデータを記録する場合、32,768回のカウンティング動作が必要であり、この場合カウンティング信号(ERQ<0:x>)は15ビットをカウンティングできなければならない。

【0070】

このために、カウント部220を15個のダウンカウンターを用いて構成し、すべてのダウンカウンターの初期値を1で設定した後、出力がすべて0になる時までカウントを行うようにすることができるが、これに限定されるものではない。カウント部220に提供される消去クロック信号(ERCK)がプログラム完了信号(PGMNDP)から生成されることは、先立って説明したとおりである。したがって、カウント部220でカウンティングを行う時ごとにセットプログラムパルス発生部240からセットプログラミングイネーブル信号(ERENP)を生成して、これによってセットデータが記録される。セットデータの記録の後には再びプログラム完了信号(PGMNDP)がイネーブルされ、このような過程はカウント部220の動作が完了される時まで反復される。カウント部220の動作が完了されることは、セットプログラムパルス発生部240の区間設定部241を通して確認することができる。

【0071】

セットプログラムパルス発生部240は、消去命令に応答したセットプログラムの区間であるか否かによってセットプログラミングイネーブル信号(ERENP)を出力する。例えば、セットプログラムが動作初期すなわち、最初のセットプログラム動作の時にはプログラミングイネーブル信号(PGMP)をそのままバイパスし、最初のセットプログラム動作によってプログラム完了信号(PGMNDP)が生成されるとプログラム完了信号(PGMNDP)をセットプログラミングイネーブル信号(ERENP)として出力する。

【0072】

このために、セットプログラムパルス発生部240は、区間設定部241及びパルス出力部243を含むように構成できる。

【0073】

区間設定部241は、例えば、カウント部220を構成するカウンターと同じカウンターを利用して構成することができる。区間設定部241が消去区間イネーブル信号(EREN)を生成する際に、消去区間イネーブル信号(EREN)は、消去動作の開始を知らせる消去モード設定信号(ERSETP)がイネーブルされた状態でイネーブルされ、カウント部220が最後のカウンティング動作を完了すると消去クロック信号(ERCK)によりディスエーブルされてコントローラ300へ提供される。

【0074】

パルス出力部243は、例えば図11のように構成することができる。

【0075】

図11は、図9に図示したパルス出力部の一例示図である。

【0076】

パルス出力部243は、消去区間イネーブル信号(EREN)のイネーブルの可否によって、プログラミングイネーブル信号(PGMP)またはプログラム完了信号(PGMNDP)をセットプログラミングイネーブル信号(ERENP)として出力する。

【0077】

すなわち、パルス出力部243は、消去区間イネーブル信号(EREN)がディスエーブルになった状態ではプログラミングイネーブル信号(PGMP)をセットプログラミングイネーブル信号(ERENP)としてバイパスさせる。一方、消去区間イネーブル信号(EREN)がイネーブルされている区間ではプログラム完了信号(PGMNDP)をセットプログラミングイネーブル信号(ERENP)として出力する。

【0078】

すなわち、消去区間イネーブル信号(EREN)がイネーブルされている区間では、プログラム完了信号(PGMNDP)がイネーブルされるとこれをセットプログラミングイネーブル信号(ERENP)として出力し、消去区間イネーブル信号(EREN)がディスエーブルになった状態すなわち、最初の消去動作時には、プログラミングイネーブル信号(PGMP)をセットプログラミングイネーブル信号(ERENP)としてバイパスさせる。

【0079】

併せて、パルス出力部243は、消去区間イネーブル信号(EREN)とプログラム完了信号(PGMNDP)とのレベルによってアドレスカウント信号(CACNTCK)を生成する。アドレスカウント信号(CACNTCK)は、コラムアドレスカウンターを動作させるための信号であり、モード判定部230へ提供される。アドレスカウント信号(CACNTCK)がイネーブルされると現在消去したワードラインらがフリーチャージされ、次の消去対象ワードラインらが選択される。

【0080】

モード判定部230は、カウント部220から提供されるカウンティング信号(ERQ<0:x>)と、セットプログラムパルス発生部240から提供される消去区間イネーブル信号(EREN)及びアドレスカウント信号(CACNTCK)とに応答してワードラインフリーチャージ信号(WLPRE)及び消去終了信号(ERMIN)を生成する。

【0081】

図10は、図8に図示したモード判定部の一例示図である。

【0082】

モード判定部230は、指定された個数のワードラインに接続されたメモリセルらに対する消去動作が完了されると、次のワードラインらに接続されたメモリセルらに対する消去動作のために現在消去動作が完了されたワードラインをフリーチャージするためのワードラインフリーチャージ信号(WLPRE)を生成する。

【0083】

例えば、128KBのメモリセルにセットデータを記録する消去モードで128個(512B/32ビット)ずつワードラインを選択して消去動作を行う場合、カウント部220が初期値(32,768)から128ずつダウンカウンティングする時点ごとにワードラインフリーチャージ信号(WLPRE)をイネーブルすることができる。32,768回のカウンティングが必要な場合、カウント部220は、15個のダウンカウンターで構成できる。したがってカウンティング信号(ERQ<0:14>)のうち一部のカウンティング信号(ERQ<0:6>)がすべてローレベルからハイレベルに遷移する場合にワードラインフリーチャージ信号(WLPRE)がイネーブルされることができる。

【0084】

ワードラインフリーチャージ信号(WLPRE)がイネーブルされる場合、現在消去動作のために選択されたワードラインをディスエーブルさせ、フリーチャージのための時間が経過した後、次の消去対象ワードラインをイネーブルさせることが望ましい。

【0085】

次の消去対象ワードラインがイネーブルされた状態からカウント部220が動作してセットプログラミングイネーブル信号(ERENP)が生成され、これによってアドレスカウント信号(CACNTCK)がイネーブルされて、その次の消去対象ワードラインが選択される過程が反復される。

【0086】

一方、ワードラインフリーチャージ信号(WLPRE)は、アドレスカウント信号(CACNTCK)によりイネーブルされ、フリーチャージリセット信号(WLPRERST)によってディスエーブルされるように構成することができる。

【0087】

カウント部220が最後のカウンティング動作を行うとカウンティング信号(ERQ<0:14>)はすべてローレベルになり、これらを組み合あわせて消去終了信号(ERMIN)が生成される。

【0088】

消去終了信号(ERMIN)は、最後の消去動作を行う区間であることを知らせる信号である。コントローラ300は、消去終了信号(ERMIN)がイネーブルされた後にはこれ以上プログラミングイネーブル信号(PGMP)がイネーブルできないようにする。

【0089】

このように、本発明では、単位消去動作を指定されたセットデータ記録単位で反復的に行う場合、単位消去動作をセットデータ記録単位で分けた数だけセットプログラミングイネーブル信号(ERENP)を生成し、これをプログラミングイネーブル信号(PGMP)に提供する。プログラミングイネーブル信号(PGMP)がイネーブルされると第2書き込み制御信号(SETP<0:3>)が生成されて、第2書き込み制御信号(SETP<0:3>)によって決定されるプログラム電流(I_PGM)がメモリセルへ提供される。この時、第1書き込み制御信号(RESETP)がディスエーブルの状態であることはもちろんである。

【0090】

併せて、セットプログラミングイネーブル信号(ERENP)を生成する時にアドレスカウント信号(CACNTCK)も生成されて次の消去対象ワードラインらがアクティブになることができるようにし、その一方で、現在消去完了したワードラインらがフリーチャージされるようになる。

【0091】

このような消去モードを通したセットデータ記録動作は消去区間イネーブル信号(EREN)がイネーブルされている間反復的に行われる。この消去区間イネーブル信号(EREN)は、消去モード設定信号(ERSETP)がイネーブルされた後、カウント部220が最後のカウンティング動作を完了することによって消去クロック信号(ERCK)によってディスエーブルになる。

【0092】

図12は、本発明に適用されることができるプログラムパルス生成部の一例示図である。

【0093】

図12に図示したように、プログラムパルス生成部100は、初期パルス発生部110、リセットパルス発生部120及びクエンチングパルス発生部130を含むように構成されることができる。

【0094】

初期パルス発生部110は、コントローラから提供されるプログラミングイネーブル信号(PGMP)に応答して区間設定信号(QSSETP)を生成する。区間設定信号(QSSETP)は、GSTに溶融点に近い熱を提供するための時間を決定する信号である。初期パルス発生部111は、プログラミングイネーブル信号(PGMP)に応答して予め設定された時間をカウンティングした後、区間設定信号(QSSETP)をイネーブルさせるようになる。

【0095】

リセットパルス発生部120は、プログラミングイネーブル信号(PGMP)及び区間設定信号(QSSETP)を予め設定された時間だけ遅延させて生成したリセット信号(IRSTP)に応答して第1書き込み制御信号(RESETEN)を生成する。

【0096】

一方、クエンチングパルス発生部130は、プログラミングイネーブル信号(PGMP)及び区間設定信号(QSSETP)に応答してイネーブル区間が互いに異なる第2書き込み制御信号(SETP<0:n>)を生成する。併せて、クエンチングパルス発生部130は、第2書き込み制御信号(SETP<0:n>)の生成が完了されるとプログラム完了信号(PGMNDP)を生成する。

【0097】

このような構成によって、リセットパルス発生部120は、プログラミングイネーブル信号(PGMP)がイネーブルされた後、リセット信号(IRSTP)がイネーブルされるまでの区間の間第1書き込み制御信号(RESETEN)を生成する。そして、クエンチングパルス発生部130は、プログラミングイネーブル信号(PGMP)がイネーブルされた後、区間設定信号(QSSETP)がイネーブルされるまでは第2書き込み制御信号(SETP<0:n>)を同じレベルでイネーブルさせ、区間設定信号(QSSETP)が発生した後にはイネーブル区間が調節された第2書き込み制御信号(SETP<0:n>)を生成する。

【0098】

より具体的に説明すれば次の通りである。

【0099】

まず、初期パルス発生部110は、入力ラッチ部1101、クロック発生部1103、第1カウント部1105、比較部1107及び遅延部1109を含む。

【0100】

入力ラッチ部1101は、プログラミングイネーブル信号(PGMP)及びリセット信号(IRSTP)に応答して内部クロックイネーブル信号(IPWEN)及びカウントリセット信号(IPWRST)を出力する。すなわち、プログラミングイネーブル信号(PGMP)が例えばハイレベルでイネーブルされると内部クロックイネーブル信号(IPWEN)がハイレベルに活性化され、リセット信号(IRSTP)がハイレベルでイネーブルされるとカウントリセット信号(IPWRST)がハイレベルに活性化される。

【0101】

より具体的に、入力ラッチ部1101は、内部クロックイネーブル信号(IPWEN)がハイレベルで、カウントリセット信号(IPWRST)がローレベルでイネーブルできるように構成することができ、ナンド(NAND)ゲートまたはノア(NOR)ゲートで構成されるR−Sラッチまたはフリップフロップで構成することができる。

【0102】

クロック発生部1103は、内部クロックイネーブル信号(IPWEN)に応答して内部クロック(ICK)を生成する。すなわち、クロック発生部1103は、内部クロックイネーブル信号(IPWEN)がハイレベルで活性化されている間、トグルリングする内部クロック(ICK)を出力する。

【0103】

第1カウント部1105は、内部クロックイネーブル信号(IPWEN)、カウントリセット信号(IPWRST)及び内部クロック(ICK)の制御によってカウンティングされるカウンティングコード(Q<0:3>)を出力する。すなわち、第1カウント部1105は、内部クロックイネーブル信号(IPWEN)がハイレベルで活性化された時、内部クロック(ICK)の制御によってカウンティング動作を行うようになる。カウントリセット信号(IPWRST)がハイレベルで活性化されると、第1カウント部1105から出力されるカウンティングコード(Q<0:3>)は初期化される。このように第1カウント部1105を利用してカウンティングコード(Q<0:3>)を生成する場合、回路の大きさを減少させることができる。併せて、第1カウント部1105は、例えばアップカウンターで構成することができる。

【0104】

比較部1107は、カウンティングコード(Q<0:3>)が予め設定された値に到達すると、区間設定信号(QSSETP)を活性化させて出力する。より具体的に、比較部1107は、カウンティングコード(Q<0:3>)と印加された時間調節コード(IPWSET<0:3>)とを比較して、カウンティングコード(Q<0:3>)が時間調節コード(IPWSET<0:3>)と同一である時に区間設定信号(QSSETP)を活性化させるように構成される。すなわち、時間調節コード(IPSET<0:3>)を調節して区間設定信号(QSSETP)の活性化する時点を調節できる。

【0105】

本発明の一実施形態において、第1カウント部1105を構成するカウンターの個数と時間調節コード(IPWSET)の個数とを同時に増加させると、区間設定信号(QSSETP)の発生時点を遅らせることができる。これはメモリセルを構成するGSTの溶融時間を変更できることを意味する。

【0106】

遅延部1109は、区間設定信号(QSSETP)を一定の時間遅延させてリセット信号(IRSTP)を出力する。遅延部1109の遅延値は、規定されたタイミングマージンを満足させるように設定されるべきである。そして、遅延部1109から生成されたリセット信号(IRSTP)は、入力ラッチ部1101をリセットさせて内部クロックイネーブル信号(IPWEN)をディスエーブルさせる一方、カウントリセット信号(IPWRST)をイネーブルさせる。これにより、クロック発生部1103と第1カウント部1105とがディスエーブルされるようになる。

【0107】

リセットパルス発生部120は、プログラミングイネーブル信号(PGMP)によりイネーブルされる一方、区間設定信号(QSSETP)によってディスエーブルになる。すなわち、時間調節コード(IPWSET<0:3>)によって設定された時間の間第1書き込み制御信号(RESETEN)を生成してライトドライバー400に提供する。

【0108】

次に、クエンチングパルス発生部130は、入力ラッチ部1301、クロック発生部1303、第2カウント部1305、リセット制御部1307及び遅延部1309を含むように構成されることができる。

【0109】

入力ラッチ部1301は、区間設定信号(QSSETP)及びリセット信号(QSRSTP)に応答してカウントイネーブル信号(CNTENB)及び内部クロックイネーブル信号(QSEN)を出力する。クロック発生部1303は、内部クロックイネーブル信号(QSEN)に応答して内部クロック(QSCK)を生成する。すなわち、クロック発生部1303は、内部クロックイネーブル信号(QSEN)がハイレベルで活性化されている間トグルリングする内部クロック(QSCK)を出力する。

【0110】

第2カウント部1305は、カウントイネーブル信号(CNTENB)、内部クロック(QSCK)、プログラミングイネーブル信号(PGMP)及びリセット信号(QSRSTP)に応答して第2書き込み制御信号(SETP<0:3>)を出力する。したがって、第2書き込み制御信号(SETP<0:3>)のアップデート周期は、内部クロック(QSCK)のトグルリング周期に対応して調節される。

【0111】

本発明の一実施形態において、第2カウント部1305は、ダウンカウンターを含むように構成できる。この場合、第2カウント部1305は、0x1111bから0x0000bになるまで動作をし、最終の出力が0x0000bになると、第2書き込み制御信号(SETP<3>)の出力信号がリセット制御部1307を駆動させる。

【0112】

リセット制御部1307は、第2カウント部1305から出力される第2書き込み制御信号(SETP<0:3>)のコード値が予め設定された値に到達すると、すなわち第2書き込み制御信号(SETP<3>)の出力信号がハイレベルからローレベルに遷移することによってリセット信号(QSRSTP)をイネーブルさせる。

【0113】

このために、リセット制御部1307は、カウント終了制御部及びパルス発生部を含むことができる。カウント終了制御部は、第2カウント部1305からカウントが完了されることによってクエンチングパルス完了信号(QSND)を生成する。パルス発生部は、クエンチングパルス完了信号(QSND)に応答してリセット信号(QSRSTP)を生成する。例えば、カウント終了制御部から出力されるクエンチングパルス完了信号(QSND)は、プログラミングイネーブル信号(PGMP)によってハイレベルを維持するが、第2書き込み制御信号(SETP<3>)がローレベルになるとローレベルに遷移する。そして、パルス発生部は、ローレベルに遷移したクエンチングパルス完了信号(QSND)によってリセット信号(QSRSTP)をイネーブルさせる。

【0114】

一方、遅延部1309は、リセット信号(QSRSTP)を予め設定された時間だけ遅延させてプログラム完了信号(PGMNDP)を生成する。プログラム完了信号(PGMNDP)は、コントローラへ伝送されてプログラムが完了されたことを知らせる。

【0115】

図13は、図12に図示した第1カウント部の構成を説明するための一例示図である。

【0116】

本発明の一実施形態において、第1カウント部1105は、複数の1ビットアップカウンターで構成することができ、図13にはアップカウンターの一例が表わされている。

【0117】

図13を参照すると、1ビットアップカウンター150は、信号入力部151、ラッチ部153及びキャリー発生部155を含むことができる。

【0118】

信号入力部151は、カウントイネーブル信号、本発明では内部クロックイネーブル信号(IPWEN)と第1カウンティングコード(Q<0>)に応答してラッチ部153の入力ノード(A)の信号レベルを決定する。

【0119】

ラッチ部153は、内部クロック(ICK)の制御によって信号入力部151から出力される信号をラッチングして第1カウンティングコード(Q<0>)を出力し、キャリー発生部155は、内部クロックイネーブル信号(IPWEN)と第1カウンティングコード(Q<0>)とによってキャリー信号(COUT)を出力する。この時、キャリー信号(COUT)は、次の端の1ビットアップカウンターのカウントイネーブル信号として利用される。一方、ラッチ部153は、カウントリセット信号(IPWRST)に応答して内部ノードが初期化され、または、特定レベルに変化される。

【0120】

より具体的に、信号入力部151は、内部クロックイネーブル信号(IPWEN)がローレベルでディスエーブルされると、出力ノードであるQの結果値をそのまま選択し、内部クロックイネーブル信号(IPWEN)がハイレベルでイネーブルされると、出力ノードであるQの結果値を反対に選択して次の端の1ビットアップカウンターへ伝達する。

【0121】

ラッチ部153は、ノードAの信号がローレベルである場合にはノードAの信号をノードCに伝達する一方、ノードAの信号がハイレベルである場合にはノードAの信号をノードQに伝達する。

【0122】

カウントリセット信号(IPWRST)がハイレベルになると出力ノードQはロー状態にリセットされ、キャリー発生部155は先端の1ビットアップカウンターの出力ノードQに印加される信号をカウントイネーブル信号として動作する。すなわち、先端の1ビットアップカウンターの出力ノードQに印加される信号レベルによって次に次の端の1ビットアップカウンターがトグルされるようになる。

【0123】

図14は、図12に図示した比較部の一例示図である。

【0124】

図14を参照すると、比較部1107は、複数の比較部71、72、73、74と、信号組合せ部75とを含むことができる。複数の比較部71、72、73、74は、カウンティングコード(Q<0:3>)及び時間調節コード(IPWSET<0:3>)の各ビット値を比較して複数の比較結果信号として出力する。信号組合せ部75は、複数の比較部71、72、73、74から出力される複数の比較結果信号を組み合せて区間設定信号(QSSETP)として出力する。すなわち、本実施形態において、比較部1107は、カウンティングコード(Q<0:3>)と時間調節コード(IPWSET<0:3>)とが同一である時、区間設定信号(QSSETP)をアクティブさせて出力する。

【0125】

図15は、図8に図示したカウント部及び図12に図示した第2カウント部の構成を説明するための図面である。

【0126】

本発明の一実施形態において、図8に図示した区間設定部241はダウンカウンターで構成することができ、例えば、1ビットダウンカウンターで構成できる。

【0127】

図15を参照すると、1ビットダウンカウンター160は、信号入力部161、ラッチ部163及びバーロー発生部165を含むことができる。

【0128】

信号入力部161は、カウントイネーブル信号(CNTINB)と出力ノードQに印加されるデータレベルとによってラッチ部163の入力ノード(A)の信号レベルを決定する。

【0129】

ラッチ部163は、クロック信号(CK)の制御によって信号入力部161から出力される信号をラッチングした後、ラッチングしたデータを出力ノードQに伝達する。

【0130】

また、バーロー発生部165は、カウントイネーブル信号(CNTINB)とラッチ部163の出力ノードQに印加される信号レベルとによってバーロー(borrow)信号(BOUTB)を出力する。

【0131】

一方、ラッチ部163は、リセット信号(RSTP)及びセット信号(SETP)に応答して内部ノードが初期化され、または、特定レベルに変化される。

【0132】

より具体的に、信号入力部161は、カウントイネーブル信号(CNTINB)がハイレベルにディスエーブルされると、出力ノードであるQの結果値をそのまま選択し、カウントイネーブル信号(CNTINB)がローレベルでイネーブルされると、出力ノードであるQの結果値を反対に選択して次の端へ伝達する。

【0133】

信号入力部161で選択した信号はノードAに印加される。これによってラッチ部163は、ノードAの信号がローレベルである場合にはノードAの信号をノードCに伝達する一方、ノードAの信号がハイレベルである場合にはノードAの信号をノードQに伝達する。

【0134】

一方、セット信号(SETP)がハイレベルになると出力ノードQがハイレベルに設定される。そして、リセット信号(RSTP)がハイレベルになると出力ノードQはローレベルでリセットされる。

【0135】

バーロー発生部165は、先端のカウンターの出力ノードQがローレベルになると、ローレベルのバーロー信号(BOUTB)を出力する。

【0136】

図16は、本発明に適用されることができるライトドライバーの一例示図である。

【0137】

図16を参照すると、ライトドライバー400は、電流調節部410、電流駆動部420及び選択部430を含むことができる。

【0138】

電流調節部410は、プログラムするデータ(DATA)を入力して、ライトイネーブル信号(WDEN)が活性化された時、第1書き込み制御信号(RESETEN)及び第2書き込み制御信号(SETP<:3>)のコード組合せによって制御ノード(N1)の電圧レベルを調節する。この時、第2書き込み制御信号(SETP<0:3>)の制御を受ける複数のNMOSトランジスターは、選択的にターンオン(TURNON)されて制御ノード(N1)の電圧レベルを調節するようになる。また、第1書き込み制御信号(RESETP)の制御を受けるNMOSトランジスターは、第1書き込み制御信号(RESETP)が活性化された時、ターンオン(TURNON)になって制御ノード(N1)の電圧レベルを調節するようになる。

【0139】

ここで、第2書き込み制御コード(SETP<0:3>)は、周期的にアップデートされる信号であり、第1書き込み制御信号(RESETP)は、パルス形態で入力される信号である。

【0140】

電流駆動部420は、制御ノード(N1)の電圧レベルに対応する大きさを有するプログラミング電流パルス(I_PGM)を出力端(N2)に駆動する。この時、プログラミング電流パルス(I_PGM)は、第1書き込み制御信号(RESETP)に対応する第1プログラミング電流パルスと、第2書き込み制御信号(SETP<0:3>)に対応する第2プログラミング電流パルスとで区分できるものである。

【0141】

選択部430は、電流駆動部420で駆動されるプログラミング電流パルス(I_PGM)を複数のビットライン選択スイッチ制御信号(YSW<0:m>)に対応する該当ビットライン(BL0〜BLm)に出力する。

【0142】

図17は、本発明の一実施形態によるセットプログラム動作を説明するためのタイミング図であり、図8を再び参照して説明する。

【0143】

消去命令に応答したセットプログラム動作が開始する前に、セットプログラム動作に必要な信号(命令語コード、アドレス等)がレジスターに臨時に保存される。

【0144】

その後、プログラム命令(PGM)が印加されることによってコントローラからプログラミングイネーブル信号(PGMP)が生成され、セットプログラムパルス発生部240はプログラミングイネーブル信号(PGMP)をセットプログラミングイネーブル信号(ERENP)としてそのまま伝達する。一方、セットプログラムパルス発生部240の区間設定部241は、コントローラ300から提供される消去モード設定信号(ERSETP)に応答して消去区間イネーブル信号(EREN)をイネーブルさせる。

【0145】

一方、カウント部220は、消去回数カウント信号(ERCNTB)と、プログラム完了信号(PGMNDP)から生成されるクロック信号(ERCNTCK)及び消去命令(ERASE)に応答して生成されるクロック信号(ERCK)及び消去イネーブル信号(IEREN)に応答してカウントを行い、その結果カウンティング信号(ERQ<0:14>)を生成してモード判定部(230)に提供する。

【0146】

第1書き込み制御信号(RESETP)はディスエーブル状態であり、セットプログラミングイネーブル信号(ERENP)がイネーブルされる時ごとにイネーブルされるプログラミングイネーブル信号(PGMP)により第2書き込み制御信号(SETP<0:3>)によってメモリセルにプログラム電流(I_PGM)が印加されてセットデータが記録される。

【0147】

すなわち、プログラムパルス生成部100の初期パルス発生部110から内部クロックイネーブル信号(IPWEN)が生成される。そして、これにより内部クロック(ICK)が生成された後、予め設定された時間をカウントしてカウンティングコード(Q<0:3>)が生成され、カウンティングが完了されると区間設定信号(QSSETP)が生成される。

【0148】

一方、リセットパルス発生部120はディスエーブルさせ、クエンチングパルス発生部130は区間設定信号(QSSETP)に応答してカウントイネーブル信号(CKEN)(CNTENB)及び内部クロック(QSCK)を生成する。そして、これによってイネーブルの区間が互いに異なる第2書き込み制御信号(SETP<0:3>)を生成する。第2書き込み制御信号(SETP<0:3>)の生成が完了されるとクエンチングパルス完了信号(QSND)がディスエーブルされ、これによりリセット信号(QSRSTP)がイネーブルされるとプログラム完了信号(PGMNDP)が出力される。この場合、第2書き込み制御信号(SETP<0:3>)のイネーブルの区間によってライトドライバーの電流駆動力が順次に減殺されてメモリセルにクエンチングパルスが供給されるようになる。

【0149】

初回のプログラム動作の後、発生されるプログラム完了信号(PGMNDP)はセットプログラム制御回路200へ提供され、以後にはカウント部220が初期値を0までダウンカウンティングする時ごとにプログラム完了信号(PGMNDP)をセットプログラミングイネーブル信号(ERENP)として出力して、セットデータ記録動作がなされる。

【0150】

したがって、128KB単位の消去モード時にワードラインを128個単位で順次イネーブルさせ、128個のワードラインがイネーブルされた状態で32ビット単位でセットデータを記録する時に、合計32,768回のセットプログラミングイネーブル信号(ERENP)がイネーブルされるはずである。併せて、ワードラインは128個単位で512番にかけて選択されてイネーブルされ、セットプログラミングイネーブル信号(ERENP)がイネーブルされる時、アドレスカウント信号(CACNTCK)によって次のワードラインを選択する一方、現在消去されたワードラインらに対するフリーチャージを行うことができる。

【0151】

このように、本発明の属する技術分野の当業者は、本発明がその技術的思想や必須的特徴を変更せずに、他の具体的な形態で実施され得るということが理解できるであろう。したがって、以上で記述した実施形態は、あらゆる面で例示的なものであり、限定的なものではないものと理解しなければならない。本発明の範囲は、上記の詳細な説明よりは、後述する特許請求の範囲によって表わされ、特許請求の範囲の意味及び範囲、そして、その等価概念から導き出されるあらゆる変更または変形された形態が本発明の範囲に含まれるものと解析されるべきである。

【符号の説明】

【0152】

10 半導体メモリ装置

100 プログラムパルス生成部

200 セットプログラム制御回路

300 コントローラ

400 ライトドライバー

500 メモリ部

210 制御信号生成部

220 カウント部

230 モード判定部

240 セットプログラムパルス発生部

【特許請求の範囲】

【請求項1】

プログラミングイネーブル信号に応答して第1書き込み制御信号、第2書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、

消去命令及び前記プログラム完了信号に応答してセットプログラミングイネーブル信号を指定された回数だけ反復生成するセットプログラム制御回路と、

前記消去命令に応答して前記第1書き込み制御信号をディスエーブルし、前記セットプログラミングイネーブル信号に応答して前記プログラミングイネーブル信号を生成するコントローラと、を備える半導体メモリ装置。

【請求項2】

前記コントローラは、前記セットプログラミングイネーブル信号がイネーブルされる時ごとに前記プログラミングイネーブル信号を生成し、

前記プログラムパルス生成部は、前記プログラミングイネーブル信号がイネーブルされる時ごとに前記第2書き込み制御信号を生成し、前記第2書き込み制御信号生成動作が完了されると前記プログラム完了信号を生成することを特徴とする、請求項1に記載の半導体メモリ装置。

【請求項3】

前記セットプログラム制御回路は、消去動作の基本単位及びセットデータ記録単位によって設定された回数だけ前記セットプログラミングイネーブル信号を生成することを特徴とする、請求項1または請求項2に記載の半導体メモリ装置。

【請求項4】

前記セットプログラム制御回路は、前記消去動作の基本単位を前記セットデータ記録単位で分けた数を初期値としてカウンティングを行い、カウンティングを行う時ごとに前記セットプログラミングイネーブル信号を出力することを特徴とする、請求項3に記載の半導体メモリ装置。

【請求項5】

前記セットプログラム制御回路は、同時にイネーブルされるワードラインの個数に対応する数だけカウンティングを行った後、アドレスカウンティング信号及びワードラインフリーチャージ信号を生成することを特徴とする、請求項3または請求項4に記載の半導体メモリ装置。

【請求項6】

前記セットプログラム制御回路は、前記消去命令に応答して消去区間イネーブル信号をイネーブルさせ、最後のカウンティング動作が行われると消去終了信号を生成して前記コントローラへ提供することを特徴とする、請求項3から請求項5のいずれかに記載の半導体メモリ装置。

【請求項7】

前記第1書き込み制御信号及び前記第2書き込み制御信号に対応するプログラム電流を生成してメモリ部にデータをプログラムするライトドライバーをさらに備えることを特徴とする、請求項1から請求項6のいずれかに記載の半導体メモリ装置。

【請求項8】

前記プログラムパルス生成部は、前記セットプログラミングイネーブル信号がイネーブルされる時ごとに前記第2書き込み制御信号を生成し、

前記ライトドライバーは、複数のセットデータを同時に受けて、予め設定された個数のワードラインが同時に駆動されることによって駆動されたワードラインに接続された前記メモリ部にデータをプログラムすることを特徴とする、請求項7に記載の半導体メモリ装置。

【請求項9】

前記メモリ部は、電流駆動方式によってデータが記録され、センシングされる複数のメモリセルを有することを特徴とする、請求項7または請求項8に記載の半導体メモリ装置。

【請求項10】

消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号を生成するセットプログラム制御回路と、

前記セットプログラミングイネーブル信号に応答して生成されるプログラミングイネーブル信号によって第1書き込み制御信号及び第2書き込み制御信号を出力するプログラムパルス生成部と、

前記第1書き込み制御信号及び前記第2書き込み制御信号に応答して生成されるプログラムパルスをメモリ部へ提供するライトドライバーと、を備える半導体メモリ装置。

【請求項11】

前記セットプログラミングイネーブル信号が、消去動作の基本単位及びセットデータ記録単位により設定された回数に対応してイネーブルされることを特徴とする、請求項10に記載の半導体メモリ装置。

【請求項12】

前記セットプログラム制御回路が、前記消去動作の基本単位を前記セットデータ記録単位で分けた数を初期値としてカウンティングを行い、カウンティングを行う時ごとに前記セットプログラミングイネーブル信号を出力することを特徴とする、請求項11に記載の半導体メモリ装置。

【請求項13】

前記書き込み制御信号が、第1レベルのデータをプログラムするための第1書き込み制御信号及び第2レベルのデータをプログラムするための第2書き込み制御信号を含み、

前記消去命令に応答して前記第1書き込み制御信号をディスエーブルさせるコントローラをさらに含むことを特徴とする、請求項10から請求項12のいずれかに記載の半導体メモリ装置。

【請求項14】

セットプログラミングイネーブル信号によって生成されるプログラミングイネーブル信号に応答してプログラム完了信号を生成するプログラムパルス生成部と接続され、

消去命令及び前記プログラム完了信号に応答して前記セットプログラミングイネーブル信号を生成する、セットプログラム制御回路。

【請求項15】

前記消去命令による消去動作の基本単位をセットデータ記録単位で分けた数を初期値としてカウンティングを行い、カウンティングを行う時ごとに前記セットプログラミングイネーブル信号を出力することを特徴とする、請求項14に記載のセットプログラム制御回路。

【請求項16】

前記消去命令、前記プログラム完了信号及びカウントイネーブル信号に応答して消去回数カウント信号及び消去クロック信号を生成し、消去モード設定信号に応答して消去イネーブル信号を生成する制御信号生成部と、

該制御信号生成部から提供される前記消去回数カウント信号、前記消去クロック信号及び前記消去イネーブル信号に応答したカウンティング動作でカウンティング信号を出力するカウント部と、

前記消去モード設定信号に応答して消去区間イネーブル信号を生成し、該消去区間イネーブル信号、前記プログラミングイネーブル信号及び前記プログラム完了信号に応答して前記セットプログラミングイネーブル信号を出力するセットプログラムパルス発生部と、

前記カウンティング信号及び前記消去区間イネーブル信号に応答して消去終了信号を生成するモード判定部と、を備えることを特徴とする、請求項14または請求項15に記載のセットプログラム制御回路。

【請求項17】

前記消去回数カウント信号、消去クロック信号及び消去イネーブル信号の各々は、サスペンド信号がディスエーブルの状態でイネーブルされることを特徴とする、請求項16に記載のセットプログラム制御回路。

【請求項18】

前記セットプログラムパルス発生部が、

前記消去モード設定信号に応答してイネーブルされ、前記カウント部の最後のカウンティング動作によってディスエーブルになる消去区間イネーブル信号を生成する区間設定部と、

前記消去区間イネーブル信号に応答して前記プログラミングイネーブル信号または前記プログラム完了信号を前記セットプログラミングイネーブル信号として出力するパルス出力部と、を備えることを特徴とする、請求項16または請求項17に記載のセットプログラム制御回路。

【請求項19】

前記パルス出力部が、前記消去区間イネーブル信号と前記プログラム完了信号とに応答してアドレスカウント信号を生成して前記モード判定部へ提供することを特徴とする、請求項18に記載のセットプログラム制御回路。

【請求項20】

前記モード判定部が、前記カウンティング信号、前記消去区間イネーブル信号及び前記アドレスカウント信号に応答してワードラインフリーチャージ信号をさらに生成することを特徴とする、請求項19に記載のセットプログラム制御回路。

【請求項21】

前記モード判定部が、同時にイネーブルできるように予め設定されたワードラインの個数がカウンティングされることによって前記ワードラインフリーチャージ信号を生成することを特徴とする、請求項20に記載のセットプログラム制御回路。

【請求項22】

前記プログラムパルス生成部が、前記プログラミングイネーブル信号によって書き込み制御信号を生成してライトドライバーへ提供することを特徴とする、請求項14から請求項21のいずれかに記載のセットプログラム制御回路。

【請求項23】

プログラムパルス生成部を具備する半導体メモリ装置にセットデータが入力される段階と、

前記プログラムパルス生成部が消去動作の基本単位及びセットデータ記録単位によって設定された回数だけプログラミングイネーブル信号を反復生成する段階と、

前記プログラミングイネーブル信号に応答して、ライトドライバーがメモリ部の選択された領域にデータをプログラムする段階と、を含む半導体メモリ装置のためのプログラム方法。

【請求項24】

前記プログラミングイネーブル信号に応答して生成される書き込み制御信号によって前記メモリ部の選択された領域にデータをプログラムし、

前記プログラムパルス生成部が前記書き込み制御信号を生成した後、プログラム完了信号を出力する段階をさらに含むことを特徴とする、請求項23に記載の半導体メモリ装置のためのプログラム方法。

【請求項25】

前記プログラム完了信号に応答して生成されるセットプログラミングイネーブル信号によって、前記プログラミングイネーブル信号を生成することを特徴とする、請求項24に記載の半導体メモリ装置のためのプログラム方法。

【請求項26】

前記プログラミングイネーブル信号を反復生成する段階が、

前記消去動作の基本単位を前記セットデータ記録単位で分けた数をカウント初期値として順次カウントする段階と、

前記カウントが行われる時ごとに前記プログラミングイネーブル信号を生成する段階と、を含むことを特徴とする、請求項23から請求項25のいずれかに記載の半導体メモリ装置のためのプログラム方法。

【請求項27】

前記カウントする段階が、前記カウント初期値からダウンカウンティングを行う段階であることを特徴とする、請求項26に記載の半導体メモリ装置のためのプログラム方法。

【請求項28】

前記ライトドライバーがメモリ部の選択された領域にデータをプログラムした後、同時にイネーブルできるように予め設定されたワードラインの個数がカウンティングされることによってワードラインフリーチャージ信号を生成する段階をさらに含むことを特徴とする、請求項26または請求項27に記載の半導体メモリ装置のためのプログラム方法。

【請求項1】

プログラミングイネーブル信号に応答して第1書き込み制御信号、第2書き込み制御信号及びプログラム完了信号を生成するプログラムパルス生成部と、

消去命令及び前記プログラム完了信号に応答してセットプログラミングイネーブル信号を指定された回数だけ反復生成するセットプログラム制御回路と、

前記消去命令に応答して前記第1書き込み制御信号をディスエーブルし、前記セットプログラミングイネーブル信号に応答して前記プログラミングイネーブル信号を生成するコントローラと、を備える半導体メモリ装置。

【請求項2】

前記コントローラは、前記セットプログラミングイネーブル信号がイネーブルされる時ごとに前記プログラミングイネーブル信号を生成し、

前記プログラムパルス生成部は、前記プログラミングイネーブル信号がイネーブルされる時ごとに前記第2書き込み制御信号を生成し、前記第2書き込み制御信号生成動作が完了されると前記プログラム完了信号を生成することを特徴とする、請求項1に記載の半導体メモリ装置。

【請求項3】

前記セットプログラム制御回路は、消去動作の基本単位及びセットデータ記録単位によって設定された回数だけ前記セットプログラミングイネーブル信号を生成することを特徴とする、請求項1または請求項2に記載の半導体メモリ装置。

【請求項4】

前記セットプログラム制御回路は、前記消去動作の基本単位を前記セットデータ記録単位で分けた数を初期値としてカウンティングを行い、カウンティングを行う時ごとに前記セットプログラミングイネーブル信号を出力することを特徴とする、請求項3に記載の半導体メモリ装置。

【請求項5】

前記セットプログラム制御回路は、同時にイネーブルされるワードラインの個数に対応する数だけカウンティングを行った後、アドレスカウンティング信号及びワードラインフリーチャージ信号を生成することを特徴とする、請求項3または請求項4に記載の半導体メモリ装置。

【請求項6】

前記セットプログラム制御回路は、前記消去命令に応答して消去区間イネーブル信号をイネーブルさせ、最後のカウンティング動作が行われると消去終了信号を生成して前記コントローラへ提供することを特徴とする、請求項3から請求項5のいずれかに記載の半導体メモリ装置。

【請求項7】

前記第1書き込み制御信号及び前記第2書き込み制御信号に対応するプログラム電流を生成してメモリ部にデータをプログラムするライトドライバーをさらに備えることを特徴とする、請求項1から請求項6のいずれかに記載の半導体メモリ装置。

【請求項8】

前記プログラムパルス生成部は、前記セットプログラミングイネーブル信号がイネーブルされる時ごとに前記第2書き込み制御信号を生成し、

前記ライトドライバーは、複数のセットデータを同時に受けて、予め設定された個数のワードラインが同時に駆動されることによって駆動されたワードラインに接続された前記メモリ部にデータをプログラムすることを特徴とする、請求項7に記載の半導体メモリ装置。

【請求項9】

前記メモリ部は、電流駆動方式によってデータが記録され、センシングされる複数のメモリセルを有することを特徴とする、請求項7または請求項8に記載の半導体メモリ装置。

【請求項10】

消去命令及びプログラム完了信号に応答してセットプログラミングイネーブル信号を生成するセットプログラム制御回路と、

前記セットプログラミングイネーブル信号に応答して生成されるプログラミングイネーブル信号によって第1書き込み制御信号及び第2書き込み制御信号を出力するプログラムパルス生成部と、

前記第1書き込み制御信号及び前記第2書き込み制御信号に応答して生成されるプログラムパルスをメモリ部へ提供するライトドライバーと、を備える半導体メモリ装置。

【請求項11】

前記セットプログラミングイネーブル信号が、消去動作の基本単位及びセットデータ記録単位により設定された回数に対応してイネーブルされることを特徴とする、請求項10に記載の半導体メモリ装置。

【請求項12】

前記セットプログラム制御回路が、前記消去動作の基本単位を前記セットデータ記録単位で分けた数を初期値としてカウンティングを行い、カウンティングを行う時ごとに前記セットプログラミングイネーブル信号を出力することを特徴とする、請求項11に記載の半導体メモリ装置。

【請求項13】

前記書き込み制御信号が、第1レベルのデータをプログラムするための第1書き込み制御信号及び第2レベルのデータをプログラムするための第2書き込み制御信号を含み、

前記消去命令に応答して前記第1書き込み制御信号をディスエーブルさせるコントローラをさらに含むことを特徴とする、請求項10から請求項12のいずれかに記載の半導体メモリ装置。

【請求項14】

セットプログラミングイネーブル信号によって生成されるプログラミングイネーブル信号に応答してプログラム完了信号を生成するプログラムパルス生成部と接続され、

消去命令及び前記プログラム完了信号に応答して前記セットプログラミングイネーブル信号を生成する、セットプログラム制御回路。

【請求項15】

前記消去命令による消去動作の基本単位をセットデータ記録単位で分けた数を初期値としてカウンティングを行い、カウンティングを行う時ごとに前記セットプログラミングイネーブル信号を出力することを特徴とする、請求項14に記載のセットプログラム制御回路。

【請求項16】

前記消去命令、前記プログラム完了信号及びカウントイネーブル信号に応答して消去回数カウント信号及び消去クロック信号を生成し、消去モード設定信号に応答して消去イネーブル信号を生成する制御信号生成部と、

該制御信号生成部から提供される前記消去回数カウント信号、前記消去クロック信号及び前記消去イネーブル信号に応答したカウンティング動作でカウンティング信号を出力するカウント部と、

前記消去モード設定信号に応答して消去区間イネーブル信号を生成し、該消去区間イネーブル信号、前記プログラミングイネーブル信号及び前記プログラム完了信号に応答して前記セットプログラミングイネーブル信号を出力するセットプログラムパルス発生部と、

前記カウンティング信号及び前記消去区間イネーブル信号に応答して消去終了信号を生成するモード判定部と、を備えることを特徴とする、請求項14または請求項15に記載のセットプログラム制御回路。

【請求項17】

前記消去回数カウント信号、消去クロック信号及び消去イネーブル信号の各々は、サスペンド信号がディスエーブルの状態でイネーブルされることを特徴とする、請求項16に記載のセットプログラム制御回路。

【請求項18】

前記セットプログラムパルス発生部が、

前記消去モード設定信号に応答してイネーブルされ、前記カウント部の最後のカウンティング動作によってディスエーブルになる消去区間イネーブル信号を生成する区間設定部と、

前記消去区間イネーブル信号に応答して前記プログラミングイネーブル信号または前記プログラム完了信号を前記セットプログラミングイネーブル信号として出力するパルス出力部と、を備えることを特徴とする、請求項16または請求項17に記載のセットプログラム制御回路。

【請求項19】

前記パルス出力部が、前記消去区間イネーブル信号と前記プログラム完了信号とに応答してアドレスカウント信号を生成して前記モード判定部へ提供することを特徴とする、請求項18に記載のセットプログラム制御回路。

【請求項20】

前記モード判定部が、前記カウンティング信号、前記消去区間イネーブル信号及び前記アドレスカウント信号に応答してワードラインフリーチャージ信号をさらに生成することを特徴とする、請求項19に記載のセットプログラム制御回路。

【請求項21】

前記モード判定部が、同時にイネーブルできるように予め設定されたワードラインの個数がカウンティングされることによって前記ワードラインフリーチャージ信号を生成することを特徴とする、請求項20に記載のセットプログラム制御回路。

【請求項22】

前記プログラムパルス生成部が、前記プログラミングイネーブル信号によって書き込み制御信号を生成してライトドライバーへ提供することを特徴とする、請求項14から請求項21のいずれかに記載のセットプログラム制御回路。

【請求項23】

プログラムパルス生成部を具備する半導体メモリ装置にセットデータが入力される段階と、

前記プログラムパルス生成部が消去動作の基本単位及びセットデータ記録単位によって設定された回数だけプログラミングイネーブル信号を反復生成する段階と、

前記プログラミングイネーブル信号に応答して、ライトドライバーがメモリ部の選択された領域にデータをプログラムする段階と、を含む半導体メモリ装置のためのプログラム方法。

【請求項24】

前記プログラミングイネーブル信号に応答して生成される書き込み制御信号によって前記メモリ部の選択された領域にデータをプログラムし、

前記プログラムパルス生成部が前記書き込み制御信号を生成した後、プログラム完了信号を出力する段階をさらに含むことを特徴とする、請求項23に記載の半導体メモリ装置のためのプログラム方法。

【請求項25】

前記プログラム完了信号に応答して生成されるセットプログラミングイネーブル信号によって、前記プログラミングイネーブル信号を生成することを特徴とする、請求項24に記載の半導体メモリ装置のためのプログラム方法。

【請求項26】

前記プログラミングイネーブル信号を反復生成する段階が、

前記消去動作の基本単位を前記セットデータ記録単位で分けた数をカウント初期値として順次カウントする段階と、

前記カウントが行われる時ごとに前記プログラミングイネーブル信号を生成する段階と、を含むことを特徴とする、請求項23から請求項25のいずれかに記載の半導体メモリ装置のためのプログラム方法。

【請求項27】

前記カウントする段階が、前記カウント初期値からダウンカウンティングを行う段階であることを特徴とする、請求項26に記載の半導体メモリ装置のためのプログラム方法。

【請求項28】

前記ライトドライバーがメモリ部の選択された領域にデータをプログラムした後、同時にイネーブルできるように予め設定されたワードラインの個数がカウンティングされることによってワードラインフリーチャージ信号を生成する段階をさらに含むことを特徴とする、請求項26または請求項27に記載の半導体メモリ装置のためのプログラム方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−114736(P2013−114736A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2012−127159(P2012−127159)

【出願日】平成24年6月4日(2012.6.4)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成24年6月4日(2012.6.4)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

[ Back to top ]