半導体メモリ装置およびその製造方法

【課題】消去、書き込みを繰り返してもON/OFF比を高く維持できる半導体メモリ装置を提供する。

【解決手段】本発明に係る半導体メモリ装置100は、基板10と、基板10の上に形成された炭化シリコン層20と、炭化シリコン層20の上に形成された金属酸化物層30と、金属酸化物層30と電気的に接続された第1電極40と、基板10と電気的に接続された第2電極50と、を含む。

【解決手段】本発明に係る半導体メモリ装置100は、基板10と、基板10の上に形成された炭化シリコン層20と、炭化シリコン層20の上に形成された金属酸化物層30と、金属酸化物層30と電気的に接続された第1電極40と、基板10と電気的に接続された第2電極50と、を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体メモリ装置およびその製造方法に関する。

【背景技術】

【0002】

半導体メモリ装置は、情報の記憶装置として様々な分野で用いられている。従来の半導体メモリ装置としては、フラッシュメモリやRAM(Random Access Memory)、ROM(Read Only Memory)などが用いられており、これらは、3つの電極を有する3端子メモリである。近年、記憶情報の拡大の要請に伴って、2つの電極で制御可能な2端子メモリが期待されている。2端子メモリは、3端子メモリに比較して電極数が減るため、回路基板でのメモリ1個当たりにおける占有面積が少なくなる。したがって、回路基板の単位面積当たりのメモリ数を増加することができ、面積当たりの情報量、すなわち記憶情報密度を拡大することができる。これにより、面積の小さい基板で、取り扱える情報量の多い記憶装置の作製が可能になる。

【0003】

例えば、特許文献1には、2端子メモリとして、SiC層を用いた不揮発性抵抗変化型メモリが記載されている。この2端子メモリは、Si基板上にSiC層を形成し、SiC層上にSiOx層を形成し、SiOx層上にSiO2層を形成して構成されている。SiO2側には電気的に接続された第1電極が、Si基板側には電気的に接続された第2電極が形成されている。この2端子メモリは、電子がSiOx層等に発生するドナー型欠陥に捕獲されるとON状態となり、電子がドナー型欠陥から放出されるとOFF状態となる。具体的には、第2電極に対して第1電極に正の閾値電圧V+以上の電圧を加えると、電子がSi基板側から供給されてドナー型欠陥に捕獲され、ON状態となる。逆に、第2電極に対して第1電極に大きさが閾値電圧V−以上の負の電圧を加えると、ドナー型欠陥に捕獲された電子がSiC層を通過してSi基板側に放出され、OFF状態となる。そして、ON状態を理論値“1”の記憶、OFF状態を理論値“0”の記憶とするメモリ動作として対応させることができる。例えば、OFF状態からON状態に遷移することは、情報“1”の書き込みに対応し、ON状態からOFF状態に遷移することは、情報の消去または情報“0”の書き込みに対応する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−50411号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記のような2端子のメモリ装置では、例えば、消去電圧を印加してもSi酸化層よりSiC層にかかる電圧が低く、SiC層の電界が十分に高くならないために、消去の際に完全に捕獲電子をSiC層からSi基板側(第2電極側)に放出させることができず、捕獲電子がドナー型欠陥に残る場合がある。そのため、完全にOFF状態が得られず、ON/OFF比が小さくなる場合がある。しかも消去の度に、次第に残る電子数が増加するために、少ない書き換え回数でOFF状態が得られなくなり、消去できなくなる。すなわち、少ない書き換え回数で理論値“0”が得られなくなる問題が生じる。

【0006】

本発明のいくつかの態様に係る目的の1つは、消去、書き込みを繰り返してもON/OFF比を高く維持できる半導体メモリ装置を提供することにある。また、本発明のいくつかの態様に係る目的の1つは、上記の半導体メモリ装置の製造方法を提供することにある。

【課題を解決するための手段】

【0007】

本発明に係る半導体メモリ装置は、

基板と、

前記基板の上に形成された炭化シリコン層と、

前記炭化シリコン層の上に形成された金属酸化物層と、

前記金属酸化物層と電気的に接続された第1電極と、

前記基板と電気的に接続された第2電極と、

を含む。

【0008】

このような半導体メモリ装置によれば、後述する実施例に示すように、消去、書き込みを繰り返してもON/OFF比を高く維持することができる。これは、形成された捕獲準位に捕獲した電子を、金属酸化物層側(第1電極側)に放出することができるためだと推測される。

【0009】

なお、本発明に係る記載では、「電気的に接続」という文言を、例えば、「特定の部材(以下「A部材」という)に「電気的に接続」された他の特定の部材(以下「B部材」という)」などと用いている。本発明に係る記載では、この例のような場合に、A部材とB部材とが、直接接して電気的に接続されているような場合と、A部材とB部材とが、他の部材を介して電気的に接続されているような場合とが含まれるものとして、「電気的に接続」という文言を用いている。

【0010】

本発明に係る半導体メモリ装置において、

前記炭化シリコン層は、

前記金属酸化物層との界面に、金属が拡散された金属拡散層を有してもよい。

【0011】

本発明に係る半導体メモリ装置において、

前記金属酸化物層は、酸化アルミニウム層であり、

前記金属拡散層に拡散された前記金属は、アルミニウムであってもよい。

【0012】

本発明に係る半導体メモリ装置において、

前記金属拡散層は、SiOx(ただし、0<x<2)を含んでいてもよい。

【0013】

本発明に係る半導体メモリ装置において、

前記炭化シリコン層は、前記金属酸化物層との界面において、前記第1電極から注入された電子を、捕獲および放出する層であり、

前記金属酸化物層は、前記電子をトンネルする層であり、

前記第1電極と前記第2電極との間に電圧が印加されることによって、情報の書き込みおよび消去を行ってもよい。

【0014】

本発明に係る半導体メモリ装置の製造方法は、

基板の上に炭化シリコン層を形成する工程と、

前記炭化シリコン層の上に金属層を形成する工程と、

前記金属層を酸素雰囲気中で熱処理して、金属酸化物層を形成する工程と、

前記金属酸化物層と電気的に接続する第1電極を形成する工程と、

前記基板と電気的に接続する第2電極を形成する工程と、

を含む。

【0015】

本発明に係る半導体メモリ装置の製造方法において、

前記金属酸化物層を形成する工程における前記熱処理によって、前記金属層を構成する金属の一部は、前記炭化シリコン層に拡散して、金属拡散層が形成されてもよい。

【0016】

本発明に係る半導体メモリ装置の製造方法において、

前記金属層は、アルミニウム層であり、

前記金属酸化物層は、酸化アルミニウム層であり、

前記炭化シリコン層に拡散する前記金属は、アルミニウムであってもよい。

【0017】

本発明に係る半導体メモリ装置の製造方法において、

前記金属酸化物層を形成する工程における前記熱処理によって、前記金属拡散層は、SiOx(ただし、0<x<2)を含んでもよい。

【0018】

本発明に係る半導体メモリ装置の製造方法において、

前記炭化シリコン層は、前記金属酸化物層との界面において、前記第1電極から注入された電子を、捕獲および放出する層であり、

前記金属酸化物層は、前記電子をトンネルする層であり、

前記第1電極と前記第2電極との間に電圧を印加して、情報の書き込みおよび消去を行ってもよい。

【図面の簡単な説明】

【0019】

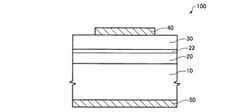

【図1】本実施形態に係る半導体メモリ装置を模式的に示す断面図。

【図2】本実施形態に係る半導体メモリ装置の動作原理を説明するための図。

【図3】本実施形態に係る半導体メモリ装置の動作原理を説明するための図。

【図4】本実施形態に係る半導体メモリ装置の製造工程を模式的に示す断面図。

【図5】本実施形態に係る半導体メモリ装置の製造工程を模式的に示す断面図。

【図6】本実施形態に係る半導体メモリ装置の製造工程を模式的に示す断面図。

【図7】本実施形態の実施例に係る半導体メモリ装置のヒステリシス特性を示すグラフ。

【図8】本実施形態の実施例に係る半導体メモリ装置のエンデュランス特性を示すグラフ。

【図9】本実施形態に係る半導体集積装置を模式的に示す断面図。

【発明を実施するための形態】

【0020】

以下、本発明の好適な実施形態について、図面を参照しながら説明する。

【0021】

1. 半導体メモリ装置

1.1. 半導体メモリ装置の構成

まず、本実施形態に係る半導体メモリ装置について、図面を参照しながら説明する。図1は、本実施形態に係る半導体メモリ装置100を模式的に示す断面図である。

【0022】

半導体メモリ装置100は、2端子メモリであり、不揮発性抵抗変化型メモリとして構成されることができる。半導体メモリ装置100は、図1に示すように、基板10と、炭化シリコン層20と、金属酸化物層30と、第1電極40と、第2電極50と、を含む。

【0023】

基板10は、例えば、n型不純物がドーピングされたn型Si基板である。基板10として、電子濃度の高いn型Si基板を用いることにより、メモリ動作を効果的に発現することができる。なお、基板10は、p型不純物がドーピングされたp型Si基板であってもよい。また、基板10には、n型のウェル領域やp型のウェル領域が形成されていてもよい。

【0024】

基板10の主面(炭化シリコン層20に接触する面)は、例えば、(100)面である。半導体メモリ装置100を、MOSトランジスタなどを有する半導体集積装置へ組み入れる場合、主面の面方位が(100)面である基板を用いることがあるので、基板10としても、主面の面方位が(100)面であることが好ましい。また、基板10の主面の面方位が(100)面であることにより、基板10上に形成される炭化シリコン層20の結晶性を向上させることができる。なお、基板10の主面の面方位は、(100)面に限定されず、例えば、(111)面であってもよい。主面の面方位が(111)面である基板10によっても、炭化シリコン層20の結晶性を向上させることができる。さらにこれらの(100)基板、(111)基板として、それぞれ(100)面、(111)面から多少斜めに切り出された面を使用しても、炭化シリコン層20の結晶性を向上させることができる。例えば(111)面から4度((111)4度オフ基板と呼ばれる)あるいは8度((111)8度オフ基板と呼ばれる)斜めになった面を用いることができる。

【0025】

基板10の厚みは、炭化シリコン層20の厚み、および金属酸化物層30の厚みよりも大きく、特に限定されないが、例えば、50μm以上1000μm以下である。

【0026】

炭化シリコン層20は、基板10上に形成されている。炭化シリコン層20としては、例えば、結晶構造として立方晶系の対称性を有する3C−SiC層を用いることができる。これにより、炭化シリコン層20の膜質を向上させることができる。なお、炭化シリコン層20として、六方対称の4H−SiC層、6H−SiC層でもよい。炭化シリコン層20は、不純物がドーピングされていても、されていなくてもよい。炭化シリコン層20の厚みは、特に限定されないが、例えば、5nm以上1000nm以下である。

【0027】

炭化シリコン層20は、金属酸化物層30との界面に、金属が拡散された金属拡散層22を有することができる。金属酸化物層30は、Al、Ga、In、Be、Ba、Srなどの典型金属元素、または、Ti、Ni、Cu、Crなどの遷移金属元素、または、これらの2種以上を含んでよい。金属酸化物30が2種以上の金属を含む場合は、その内の1種または2種以上の金属が拡散した金属拡散層22が形成されてよい。金属酸化物層30としては、典型金属元素または遷移金属元素またはその双方を含む金属の酸化物の層を用いることができ、例えば、Al2O3層、Ga2O3層、In2O3層、Fe3O4層、TiO2層、Cu2O層、ZnO層、NiO層、BaTiO3層、SrTiO3層などを用いることができる。

【0028】

より具体的には、金属酸化物層30として酸化アルミニウム層(Al2O3層)を用いた場合、金属拡散層22に拡散された金属は、アルミニウムであり、金属拡散層22はアルミニウム拡散層である。この場合、金属拡散層22は、例えば、炭素、シリコン、およびアルミニウムから構成されている。

【0029】

さらに金属拡散層22は、SiOx(ただし、0<x<2)を含むことができる。この場合、金属拡散層22は、例えば、炭素、シリコン、アルミニウム、および酸素から構成されている。

【0030】

金属拡散層22は、金属が拡散された位置において、電子を捕獲する捕獲準位を有することができる。さらに、金属拡散層22は、SiOx(ただし、0<x<2)を含むことによる欠陥(完全に酸化されていないことによる欠陥)によって、電子を捕獲する捕獲準位を有することができる。例えば、金属拡散層22は、xが2の場合であるSiO2を含んでもよいが、SiO2を含むことによって欠陥は生じない。

【0031】

金属拡散層22は、電子を捕獲する層(電子捕獲層)として機能することができ、第1電極40から注入された電子を、捕獲および放出することができる。すなわち、炭化シリコン層20は、金属酸化物層30との界面において、第1電極40から注入された電子を、捕獲および放出することができる。

【0032】

金属拡散層22の厚みは、炭化シリコン層20の厚み、および金属酸化物層30の厚みよりも小さく、特に限定されないが、例えば、1nm以上20nm以下である。金属拡散層22の厚みが1nmより小さいと、捕獲電子の数が少なくなり、半導体メモリ装置は、ON状態(低抵抗状態)となることが困難になる場合がある。金属拡散層22の厚みが20nmより大きいと、消去の際に十分に捕獲電子を放出させることができず捕獲電子が残って、OFF状態(高抵抗状態)となることが困難になる場合がある。

【0033】

なお、炭化シリコン層20は、例えばSiOx(ただし、0<x<2)層(図示せず)を有していてもよく、SiOx層が、酸化物層30との界面に、不純物拡散層22を有していてもよい。

【0034】

金属酸化物層30は、炭化シリコン層20上に(より具体的には金属拡散層22上に)形成されている。金属酸化物層30としては、例えば、酸化アルミニウム層(Al2O3層)を用いる。金属酸化物層30は、電子をトンネルすることができる電子トンネル層として機能することができる。なお、金属酸化物層30としては、電子をトンネルすることができれば、酸化アルミニウム層に限定されず、上述のように、典型金属元素または遷移金属元素またはその双方を含む金属の酸化物からなる層を用いることができ、例えば、Ga2O3層、In2O3層、Fe3O4層、TiO2層、Cu2O層、ZnO層、NiO層、BaTiO3層、SrTiO3層などを用いることができる。

【0035】

金属酸化物層30の厚みは、特に限定されないが、例えば、3nm以上40nm以下である。金属酸化物層30の厚みが3nmより小さいと、ON状態でも金属拡散層22に捕獲された電子が抜けやすくなる場合がある。金属酸化物層30の厚みが40nmより大きいと、ON状態でも電流が流れ難くなる場合がある。

【0036】

第1電極40は、金属酸化物層30と電気的に接続されている。図示の例では、第1電極40は、金属酸化物層30上に形成されている。第1電極40としては、仕事関数の大きな金属を挙げることができ、より具体的には、金、ニッケル、白金などを挙げることができる。

【0037】

第2電極50は、基板10と電気的に接続されている。図示の例では、第2電極50は、基板10の下に形成されている。第2電極50は、図1に示すように、基板10の下面全面に形成されていてもよい。第2電極50は、基板10とオーミックコンタクトが得られれば、どのような金属でもよく、例えば、アルミニウムが挙げられる。第1電極40および第2電極50によって、金属酸化物層30および炭化シリコン層20に電圧を印加することができる。

【0038】

なお、図示はしないが、第2電極50は、基板10の上面に形成されていてもよい。すなわち、基板10の上面の面積は、炭化シリコン層20の下面の面積よりも大きく、基板10の上面の、炭化シリコン層20が形成されていない領域に、第2電極50が形成されていてもよい。

【0039】

1.2. 半導体メモリ装置の動作原理

次に、本実施形態に係る半導体メモリ装置の予想される動作原理について、図面を参照しながら説明する。図2および図3は、本実施形態に係る半導体メモリ装置100の動作原理を説明するための図であって、模式化したエネルギーバンド図を示すものである。なお、図2および図3において、金属拡散層22のバンドギャップは、金属拡散層22が含むSiOx(ただし、0<x<2)の割合によって変化することができる。図2および図3では、金属拡散層22のバンドギャップは、炭化シリコン層20のバンドギャップとほぼ同じと考えられる場合について図示している。また、図2および図3において、点線EFは、フェルミレベルを示している。

【0040】

まず、図2(A)は、第1電極40および第2電極50間に電圧を印加していない状態である。この状態では、半導体メモリ装置100は、OFF状態である。金属拡散層22には、金属が炭化シリコン層に拡散することによってその拡散した不純物の金属の位置で、または、拡散した不純物の金属の位置と、金属拡散層22に含まれるSiOx(ただし、0<x<2)による欠陥と、の双方で、電子を捕獲することができる捕獲準位22aが存在する。図2および図3において、捕獲準位22aは、模式的に四角領域で図示している。

【0041】

次に、図2(B)に示すように、酸化アルミニウム層30の表面に形成された第1電極40側がマイナスとなるように、電極40,50間に負電圧をかけていくと、例えば、基板10は抵抗が低いため、印加した電圧は、金属酸化物層30、および金属拡散層22を有する炭化シリコン層20にかかる。図2(B)に示す状態では、金属酸化物層30および炭化シリコン層20にかかる電圧は不十分で、障壁が厚く、電流はほとんど流れない。半導体メモリ装置100としては、高抵抗状態であり、OFF状態である。

【0042】

次に、図2(C)に示すように、第1電極40側がマイナスとなるように、電極40,50間にかける負電圧を大きくしていくと、ある電圧(例えば図7に示すVth2)を超えたところで、第1電極40からの電子eが金属拡散層22の捕獲準位22aに捕獲される。これにより、炭化シリコン層20のバンドが急峻に曲げられて、障壁が薄くなり、電子eが金属酸化物層30をトンネルする確率が高くなって、電流が流れる。半導体メモリ装置100は、高抵抗状態から低抵抗状態となり、OFF状態からON状態となる。OFF状態からON状態に遷移することは、メモリ装置の動作として、情報“1”の書き込みに対応する。

【0043】

次に、図3(D)に示すように、第1電極40側がプラスとなるように、電極40,50間に正電圧を印加する。このとき、電子eは、捕獲準位22aに捕獲されたままなので、今度は炭化シリコン層20のバンドが下方に曲がりにくくなり、第1電極40側がプラスとなるように印加された電圧の内、金属酸化物層30に印加される電圧の割合が高く、電子eが金属酸化物層30をトンネルする確率は高くなり、電流が流れる。半導体メモリ装置100は、低抵抗状態であり、ON状態である。

【0044】

次に、図3(E)に示すように、第1電極40側がプラスとなるように、電極40,50間にかける正電圧を大きくしていくと、ある電圧(例えば図7に示すVth1)を超えたところで、捕獲準位22aに捕獲されていた電子eが、金属酸化物層30側(第1電極40側)に放出される。これにより、第1電極40側がプラスとなるように印加された電圧が炭化シリコン層20と金属酸化物層30の両方に同様の割合で電圧が印加され、金属酸化物層30に印加される電圧の割合が減って、そのため、電子eが金属酸化物層30をトンネルする確率が低くなり、流れる電流が減少する。半導体メモリ装置100は、低抵抗状態から高抵抗状態となり、ON状態からOFF状態となる。ON状態からOFF状態に遷移することは、メモリ装置の動作として、情報の消去または情報“0”の書き込みに対応する。

【0045】

以上のように、半導体メモリ装置100は、第1電極40にかける電圧を、マイナス側に十分大きくすれば(Vth2を超える電圧を印加すれば)OFF状態からON状態に、逆に、プラス側に十分大きくすれば(Vth1を超える電圧を印加すれば)ON状態からOFF状態に変えることができる。そして、半導体メモリ装置100では、0〜Vth2の間の電圧で電流が流れるが、流れないかを調べれば、メモリ装置の記憶置である“0(OFF状態)”か、“1(ON状態)”か、を読み取ることができる。

【0046】

本実施形態に係る半導体メモリ装置100は、例えば、以下の特徴を有する。

【0047】

半導体メモリ装置100によれば、後述する実施例に示すように、消去、書き込みを繰り返してもON/OFF比を高く維持することができる。これは、捕獲準位22aに捕獲した電子eを、印加電圧によって、金属酸化物層30側(第1電極40側)に容易に放出することができるためだと推測される(図3(E)参照)。特許文献1に記載の従来のメモリのように、捕獲した電子を、逆側(第2電極側)に放出する場合は、酸化物層の障壁より厚い炭化シリコン層などの障壁により、消去の際に十分に捕獲電子を放出させることができず、ON/OFF比が半導体メモリ装置100より小さくなる。

【0048】

2. 半導体メモリ装置の製造方法

次に、本実施形態に係る半導体メモリ装置の製造方法について、図面を参照しながら説明する。図4〜図6は、本実施形態に係る半導体メモリ装置100の製造工程を模式的に示す断面図である。

【0049】

図4に示すように、基板10上に炭化シリコン層20を形成する。炭化シリコン層20は、例えば、CVD(Chemical Vapor Deposition)法、スパッタ法により形成される。

【0050】

図5に示すように、炭化シリコン層20上に金属層32を形成する。金属層32は、例えば、スパッタ法、真空蒸着法により形成される。金属層32としてアルミニウム層を用いた場合、金属酸化物層30は酸化アルミニウム層であり、アルミニウム層32(金属層32)の厚みは、酸化アルミニウム層30(金属酸化物層30、図1参照)の厚みのおよそ1/1.3程度となるため、例えば、2.3nm以上31nm以下である。なお、金属層32の厚みと、後述のように金属層32を熱酸化した後の金属酸化物層30の厚みと、の比は、金属の種類によって異なる。

【0051】

図6に示すように、金属層32を酸素雰囲気中で熱処理して、金属酸化物層30を形成する。より具体的には、例えば、酸素100%の大気圧中において、550℃程度で50分程度熱処理することにより、金属酸化物層30を形成する。形成される金属酸化物層30の厚みは、金属層32がアルミニウム層の場合は、アルミニウム層32(金属層32)の厚みのおよそ1.3倍になる。本工程の熱処理によって、金属層32を構成する金属の一部は、炭化シリコン層20に拡散する。金属層32としてアルミニウム層を用いた場合、アルミニウム層32(金属層32)を構成するアルミニウムの一部が、炭化シリコン層20に拡散する。金属層32が、2種類以上の金属から構成されている場合は、熱処理温度に依存して、主に1種の元素の一部が、または2種以上の元素の一部が炭化シリコン層20に拡散する。これにより、炭化シリコン層20に、金属拡散層22を形成することができる。さらに、本工程の熱処理によって、金属層32を構成する金属の一部が炭化シリコン層20に拡散すると同時に、炭化シリコン層20の金属酸化物層30との界面が酸化される。これにより、SiOx(ただし、0<x<2)を含む金属拡散層22を形成することができる。

【0052】

図1に示すように、金属酸化物層30上に第1電極40を形成する。次に、基板10の下に第2電極50を形成する。第1電極40および第2電極50は、例えば、スパッタ法、真空蒸着法により形成される。なお、第1電極40を形成する工程と、第2電極50を形成する工程とは、その先後を問わない。

【0053】

以上の工程により、本実施形態に係る半導体メモリ装置100を製造することができる。

【0054】

半導体メモリ装置100の製造方法によれば、消去、書き込みを繰り返してもON/OFF比を高く維持することができる半導体メモリ装置100を得ることができる。

【0055】

3. 実施例

以下に実験例を示し、本発明をより具体的に説明する。なお、本発明は、以下の実験例によって何ら限定されるものではない。

【0056】

3.1. 半導体メモリ装置の作製

n型のSi基板上に、炭化シリコン層として厚み10nmの3C−SiC層を、CVD法により形成した。次に、3C−SiC層上に、金属層としてAl層を、スパッタ法により形成した。Al層の厚みを、5nmと10nmとの2水準に振った。次に、酸素100%の大気圧中において、550℃で50分熱処理することにより、金属酸化物層としてAl2O3層を形成した。該熱処理により、Al層の一部が、3C−SiC層に拡散した。さらに、該熱処理により、3C−SiC層のAl層との界面が酸化された。これにより、金属拡散層として、SiO0.5、SiO1.0、およびSiO1.5を含むAl拡散層が形成された。次に、Al2O3層上に、第1電極としてAu層を、スパッタ法により形成した。次に、Si基板の下に、第2電極としてAl層を、スパッタ法により形成した。

【0057】

3.2. I−V特性

上記のように作製した半導体メモリ装置のI−V特性を評価した。図7は、実施例に係る半導体メモリ装置のI−V特性を示すグラフである。

【0058】

図7に示すように、メモリ特性であるヒステリシスを得ることができ、実施例に係る半導体メモリ装置は、良好なメモリ特性を有していることが分かった。

【0059】

なお、上述のとおり、図7に示すVth2は、OFF状態からON状態に遷移する閾値電圧であり、Vth1は、ON状態からOFF状態に遷移する閾値電圧である。そして、0〜Vth2の間の電圧で電流が流れるが、流れないかを調べれば、メモリ装置の記憶置である“0(OFF状態)”か、“1(ON状態)”か、を読み取ることができる。

【0060】

3.3. エンデュランス特性

上記のように作製した半導体メモリ装置のエンデュランス特性(メモリ書き換え回数とON/OFF比との関係)を評価した。図8は、実施例に係る半導体メモリ装置のエンデュランス特性を示すグラフである。なお、ON/OFF比とは、ON状態に対するOFF状態の抵抗の比である。また、図8では、Al層の厚みが10nmの半導体メモリ装置について評価した。

【0061】

図8に示すように、実施例の半導体メモリ装置は、メモリ書き換え回数が10万回で、ON/OFF比が6.5程度であり、良好なエンデュランス特性を有していることがわかった。一方、特許文献1の2端子メモリでは、メモリ書き換え回数が1万回で、ON/OFF比が最大3.5程度である。すなわち、実施例の半導体メモリ装置は、消去、書き込みを繰り返してもON/OFF比を高く維持できることがわかった。

【0062】

4. 半導体集積装置

次に、本実施形態に係る半導体集積装置について、図面を参照しながら説明する。図9は、本実施形態に係る半導体集積装置1000を模式的に示す断面図である。

【0063】

半導体集積装置1000は、本発明に係る半導体メモリ装置と、トランジスタと、を含むことができる。図9に示す例では、半導体集積装置1000は、半導体メモリ装置100と、バイポーラトランジスタ200と、MOSトランジスタ300と、を有している。

【0064】

半導体集積装置1000では、基板10として、例えば、p型Si基板を用いることができる。図示の例では、基板10には、不純物をドーピングすることによって、n型ウェル領域11が形成されている。n型ウェル領域11には、さらに不純物を高濃度にドーピングしたp+型ウェル領域12が形成され、p+型ウェル領域12にはn+型ウェル領域13が形成されている。

【0065】

n型ウェル領域11、p+型ウェル領域12、およびn+型ウェル領域13によって、バイポーラトランジスタ200が構成されている。n型ウェル領域11は、コレクタとして機能することができる。p+型ウェル領域12は、ベースとして機能することができる。n+型ウェル領域13は、エミッタとして機能することができる。

【0066】

p+型ウェル領域12上には、炭化シリコン層20、金属酸化物層30、および第1電極40が、この順で形成されている。さらに、p+型ウェル領域12上には、第2電極50が形成されている。ウェル領域11,12が形成された基板10、炭化シリコン層20、金属酸化物層30、および電極40,50によって、半導体メモリ装置100が構成されている。図示の例では、1つの第2電極50を共通電極として、2つの第1電極40が形成されている。このように、第2電極50を共通電極として、複数の半導体メモリ装置100の集積化を図ることができる。

【0067】

なお、第2電極50は、バイポーラトランジスタ200のベース電極としても機能することができる。また、n+型ウェル領域13上には、図9に示すように、ベース電極70が形成されていてもよい。

【0068】

n型ウェル領域11には、さらに、p+型ウェル領域16,17が形成されている。p+型ウェル領域16は、ソース領域16となり、p+型ウェル領域17は、ドレイン領域17となることができる。さらに、n型ウェル領域11上にはゲート絶縁層60が形成され、ゲート絶縁層60上にはゲート電極72が形成されている。ソース領域16、ドレイン領域17、ゲート絶縁層60、およびゲート電極72によって、MOSトランジスタ300が形成されている。ソース領域16とドレイン領域17との間に位置するn型ウェル領域11は、チャネル領域15となることができる。図9に示すように、ソース領域16上にはソース電極74が形成され、ドレイン領域17上にはドレイン電極76が形成されていてもよい。

【0069】

バイポーラトランジスタ200とMOSトランジスタ300との間には、例えば、素子分離領域80が形成されている。素子分離領域80の材質としては、例えば、酸化シリコンが挙げられる。素子分離領域80によって、バイポーラトランジスタ200とMOSトランジスタ300とを、電気的に分離することができる。

【0070】

層間絶縁層90は、基板10の上方に形成されている。層間絶縁層90の材質としては、例えば、酸化シリコンが挙げられる。図示はしないが、層間絶縁層90の上方には、多層配線構造が形成されていてもよく、これによって、半導体メモリ装置100、バイポーラトランジスタ200、およびMOSトランジスタ300が結線されていてもよい。

【0071】

半導体集積装置1000によれば、消去、書き込みを繰り返してもON/OFF比を高く維持することができる半導体メモリ装置100を有することができる。そのため、半導体集積装置1000は、高い性能を有することができる。

【0072】

なお、本発明は、実施の形態で説明した構成と実質的に同一の構成(例えば、機能、方法及び結果が同一の構成、あるいは目的及び効果が同一の構成)を含む。また、本発明は、実施の形態で説明した構成の本質的でない部分を置き換えた構成を含む。また、本発明は、実施の形態で説明した構成と同一の作用効果を奏する構成又は同一の目的を達成することができる構成を含む。また、本発明は、実施の形態で説明した構成に公知技術を付加した構成を含む。

【符号の説明】

【0073】

10 基板、11 n型ウェル領域、12 p+型ウェル領域、

13 n+型ウェル領域、15 チャネル領域、16 ソース領域、

17 ドレイン領域、20 炭化シリコン層、22 金属拡散層、22a 捕獲準位、

30 金属酸化物層、32 金属層、40 第1電極、50 第2電極、

60 ゲート絶縁層、70 エミッタ電極、72 ゲート電極、74 ソース電極、

76 ドレイン電極、80 素子分離領域、90 層間絶縁層、

100 半導体メモリ素子、200 バイポーラトランジスタ、

300 MOSトランジスタ、1000 半導体集積装置

【技術分野】

【0001】

本発明は、半導体メモリ装置およびその製造方法に関する。

【背景技術】

【0002】

半導体メモリ装置は、情報の記憶装置として様々な分野で用いられている。従来の半導体メモリ装置としては、フラッシュメモリやRAM(Random Access Memory)、ROM(Read Only Memory)などが用いられており、これらは、3つの電極を有する3端子メモリである。近年、記憶情報の拡大の要請に伴って、2つの電極で制御可能な2端子メモリが期待されている。2端子メモリは、3端子メモリに比較して電極数が減るため、回路基板でのメモリ1個当たりにおける占有面積が少なくなる。したがって、回路基板の単位面積当たりのメモリ数を増加することができ、面積当たりの情報量、すなわち記憶情報密度を拡大することができる。これにより、面積の小さい基板で、取り扱える情報量の多い記憶装置の作製が可能になる。

【0003】

例えば、特許文献1には、2端子メモリとして、SiC層を用いた不揮発性抵抗変化型メモリが記載されている。この2端子メモリは、Si基板上にSiC層を形成し、SiC層上にSiOx層を形成し、SiOx層上にSiO2層を形成して構成されている。SiO2側には電気的に接続された第1電極が、Si基板側には電気的に接続された第2電極が形成されている。この2端子メモリは、電子がSiOx層等に発生するドナー型欠陥に捕獲されるとON状態となり、電子がドナー型欠陥から放出されるとOFF状態となる。具体的には、第2電極に対して第1電極に正の閾値電圧V+以上の電圧を加えると、電子がSi基板側から供給されてドナー型欠陥に捕獲され、ON状態となる。逆に、第2電極に対して第1電極に大きさが閾値電圧V−以上の負の電圧を加えると、ドナー型欠陥に捕獲された電子がSiC層を通過してSi基板側に放出され、OFF状態となる。そして、ON状態を理論値“1”の記憶、OFF状態を理論値“0”の記憶とするメモリ動作として対応させることができる。例えば、OFF状態からON状態に遷移することは、情報“1”の書き込みに対応し、ON状態からOFF状態に遷移することは、情報の消去または情報“0”の書き込みに対応する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010−50411号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記のような2端子のメモリ装置では、例えば、消去電圧を印加してもSi酸化層よりSiC層にかかる電圧が低く、SiC層の電界が十分に高くならないために、消去の際に完全に捕獲電子をSiC層からSi基板側(第2電極側)に放出させることができず、捕獲電子がドナー型欠陥に残る場合がある。そのため、完全にOFF状態が得られず、ON/OFF比が小さくなる場合がある。しかも消去の度に、次第に残る電子数が増加するために、少ない書き換え回数でOFF状態が得られなくなり、消去できなくなる。すなわち、少ない書き換え回数で理論値“0”が得られなくなる問題が生じる。

【0006】

本発明のいくつかの態様に係る目的の1つは、消去、書き込みを繰り返してもON/OFF比を高く維持できる半導体メモリ装置を提供することにある。また、本発明のいくつかの態様に係る目的の1つは、上記の半導体メモリ装置の製造方法を提供することにある。

【課題を解決するための手段】

【0007】

本発明に係る半導体メモリ装置は、

基板と、

前記基板の上に形成された炭化シリコン層と、

前記炭化シリコン層の上に形成された金属酸化物層と、

前記金属酸化物層と電気的に接続された第1電極と、

前記基板と電気的に接続された第2電極と、

を含む。

【0008】

このような半導体メモリ装置によれば、後述する実施例に示すように、消去、書き込みを繰り返してもON/OFF比を高く維持することができる。これは、形成された捕獲準位に捕獲した電子を、金属酸化物層側(第1電極側)に放出することができるためだと推測される。

【0009】

なお、本発明に係る記載では、「電気的に接続」という文言を、例えば、「特定の部材(以下「A部材」という)に「電気的に接続」された他の特定の部材(以下「B部材」という)」などと用いている。本発明に係る記載では、この例のような場合に、A部材とB部材とが、直接接して電気的に接続されているような場合と、A部材とB部材とが、他の部材を介して電気的に接続されているような場合とが含まれるものとして、「電気的に接続」という文言を用いている。

【0010】

本発明に係る半導体メモリ装置において、

前記炭化シリコン層は、

前記金属酸化物層との界面に、金属が拡散された金属拡散層を有してもよい。

【0011】

本発明に係る半導体メモリ装置において、

前記金属酸化物層は、酸化アルミニウム層であり、

前記金属拡散層に拡散された前記金属は、アルミニウムであってもよい。

【0012】

本発明に係る半導体メモリ装置において、

前記金属拡散層は、SiOx(ただし、0<x<2)を含んでいてもよい。

【0013】

本発明に係る半導体メモリ装置において、

前記炭化シリコン層は、前記金属酸化物層との界面において、前記第1電極から注入された電子を、捕獲および放出する層であり、

前記金属酸化物層は、前記電子をトンネルする層であり、

前記第1電極と前記第2電極との間に電圧が印加されることによって、情報の書き込みおよび消去を行ってもよい。

【0014】

本発明に係る半導体メモリ装置の製造方法は、

基板の上に炭化シリコン層を形成する工程と、

前記炭化シリコン層の上に金属層を形成する工程と、

前記金属層を酸素雰囲気中で熱処理して、金属酸化物層を形成する工程と、

前記金属酸化物層と電気的に接続する第1電極を形成する工程と、

前記基板と電気的に接続する第2電極を形成する工程と、

を含む。

【0015】

本発明に係る半導体メモリ装置の製造方法において、

前記金属酸化物層を形成する工程における前記熱処理によって、前記金属層を構成する金属の一部は、前記炭化シリコン層に拡散して、金属拡散層が形成されてもよい。

【0016】

本発明に係る半導体メモリ装置の製造方法において、

前記金属層は、アルミニウム層であり、

前記金属酸化物層は、酸化アルミニウム層であり、

前記炭化シリコン層に拡散する前記金属は、アルミニウムであってもよい。

【0017】

本発明に係る半導体メモリ装置の製造方法において、

前記金属酸化物層を形成する工程における前記熱処理によって、前記金属拡散層は、SiOx(ただし、0<x<2)を含んでもよい。

【0018】

本発明に係る半導体メモリ装置の製造方法において、

前記炭化シリコン層は、前記金属酸化物層との界面において、前記第1電極から注入された電子を、捕獲および放出する層であり、

前記金属酸化物層は、前記電子をトンネルする層であり、

前記第1電極と前記第2電極との間に電圧を印加して、情報の書き込みおよび消去を行ってもよい。

【図面の簡単な説明】

【0019】

【図1】本実施形態に係る半導体メモリ装置を模式的に示す断面図。

【図2】本実施形態に係る半導体メモリ装置の動作原理を説明するための図。

【図3】本実施形態に係る半導体メモリ装置の動作原理を説明するための図。

【図4】本実施形態に係る半導体メモリ装置の製造工程を模式的に示す断面図。

【図5】本実施形態に係る半導体メモリ装置の製造工程を模式的に示す断面図。

【図6】本実施形態に係る半導体メモリ装置の製造工程を模式的に示す断面図。

【図7】本実施形態の実施例に係る半導体メモリ装置のヒステリシス特性を示すグラフ。

【図8】本実施形態の実施例に係る半導体メモリ装置のエンデュランス特性を示すグラフ。

【図9】本実施形態に係る半導体集積装置を模式的に示す断面図。

【発明を実施するための形態】

【0020】

以下、本発明の好適な実施形態について、図面を参照しながら説明する。

【0021】

1. 半導体メモリ装置

1.1. 半導体メモリ装置の構成

まず、本実施形態に係る半導体メモリ装置について、図面を参照しながら説明する。図1は、本実施形態に係る半導体メモリ装置100を模式的に示す断面図である。

【0022】

半導体メモリ装置100は、2端子メモリであり、不揮発性抵抗変化型メモリとして構成されることができる。半導体メモリ装置100は、図1に示すように、基板10と、炭化シリコン層20と、金属酸化物層30と、第1電極40と、第2電極50と、を含む。

【0023】

基板10は、例えば、n型不純物がドーピングされたn型Si基板である。基板10として、電子濃度の高いn型Si基板を用いることにより、メモリ動作を効果的に発現することができる。なお、基板10は、p型不純物がドーピングされたp型Si基板であってもよい。また、基板10には、n型のウェル領域やp型のウェル領域が形成されていてもよい。

【0024】

基板10の主面(炭化シリコン層20に接触する面)は、例えば、(100)面である。半導体メモリ装置100を、MOSトランジスタなどを有する半導体集積装置へ組み入れる場合、主面の面方位が(100)面である基板を用いることがあるので、基板10としても、主面の面方位が(100)面であることが好ましい。また、基板10の主面の面方位が(100)面であることにより、基板10上に形成される炭化シリコン層20の結晶性を向上させることができる。なお、基板10の主面の面方位は、(100)面に限定されず、例えば、(111)面であってもよい。主面の面方位が(111)面である基板10によっても、炭化シリコン層20の結晶性を向上させることができる。さらにこれらの(100)基板、(111)基板として、それぞれ(100)面、(111)面から多少斜めに切り出された面を使用しても、炭化シリコン層20の結晶性を向上させることができる。例えば(111)面から4度((111)4度オフ基板と呼ばれる)あるいは8度((111)8度オフ基板と呼ばれる)斜めになった面を用いることができる。

【0025】

基板10の厚みは、炭化シリコン層20の厚み、および金属酸化物層30の厚みよりも大きく、特に限定されないが、例えば、50μm以上1000μm以下である。

【0026】

炭化シリコン層20は、基板10上に形成されている。炭化シリコン層20としては、例えば、結晶構造として立方晶系の対称性を有する3C−SiC層を用いることができる。これにより、炭化シリコン層20の膜質を向上させることができる。なお、炭化シリコン層20として、六方対称の4H−SiC層、6H−SiC層でもよい。炭化シリコン層20は、不純物がドーピングされていても、されていなくてもよい。炭化シリコン層20の厚みは、特に限定されないが、例えば、5nm以上1000nm以下である。

【0027】

炭化シリコン層20は、金属酸化物層30との界面に、金属が拡散された金属拡散層22を有することができる。金属酸化物層30は、Al、Ga、In、Be、Ba、Srなどの典型金属元素、または、Ti、Ni、Cu、Crなどの遷移金属元素、または、これらの2種以上を含んでよい。金属酸化物30が2種以上の金属を含む場合は、その内の1種または2種以上の金属が拡散した金属拡散層22が形成されてよい。金属酸化物層30としては、典型金属元素または遷移金属元素またはその双方を含む金属の酸化物の層を用いることができ、例えば、Al2O3層、Ga2O3層、In2O3層、Fe3O4層、TiO2層、Cu2O層、ZnO層、NiO層、BaTiO3層、SrTiO3層などを用いることができる。

【0028】

より具体的には、金属酸化物層30として酸化アルミニウム層(Al2O3層)を用いた場合、金属拡散層22に拡散された金属は、アルミニウムであり、金属拡散層22はアルミニウム拡散層である。この場合、金属拡散層22は、例えば、炭素、シリコン、およびアルミニウムから構成されている。

【0029】

さらに金属拡散層22は、SiOx(ただし、0<x<2)を含むことができる。この場合、金属拡散層22は、例えば、炭素、シリコン、アルミニウム、および酸素から構成されている。

【0030】

金属拡散層22は、金属が拡散された位置において、電子を捕獲する捕獲準位を有することができる。さらに、金属拡散層22は、SiOx(ただし、0<x<2)を含むことによる欠陥(完全に酸化されていないことによる欠陥)によって、電子を捕獲する捕獲準位を有することができる。例えば、金属拡散層22は、xが2の場合であるSiO2を含んでもよいが、SiO2を含むことによって欠陥は生じない。

【0031】

金属拡散層22は、電子を捕獲する層(電子捕獲層)として機能することができ、第1電極40から注入された電子を、捕獲および放出することができる。すなわち、炭化シリコン層20は、金属酸化物層30との界面において、第1電極40から注入された電子を、捕獲および放出することができる。

【0032】

金属拡散層22の厚みは、炭化シリコン層20の厚み、および金属酸化物層30の厚みよりも小さく、特に限定されないが、例えば、1nm以上20nm以下である。金属拡散層22の厚みが1nmより小さいと、捕獲電子の数が少なくなり、半導体メモリ装置は、ON状態(低抵抗状態)となることが困難になる場合がある。金属拡散層22の厚みが20nmより大きいと、消去の際に十分に捕獲電子を放出させることができず捕獲電子が残って、OFF状態(高抵抗状態)となることが困難になる場合がある。

【0033】

なお、炭化シリコン層20は、例えばSiOx(ただし、0<x<2)層(図示せず)を有していてもよく、SiOx層が、酸化物層30との界面に、不純物拡散層22を有していてもよい。

【0034】

金属酸化物層30は、炭化シリコン層20上に(より具体的には金属拡散層22上に)形成されている。金属酸化物層30としては、例えば、酸化アルミニウム層(Al2O3層)を用いる。金属酸化物層30は、電子をトンネルすることができる電子トンネル層として機能することができる。なお、金属酸化物層30としては、電子をトンネルすることができれば、酸化アルミニウム層に限定されず、上述のように、典型金属元素または遷移金属元素またはその双方を含む金属の酸化物からなる層を用いることができ、例えば、Ga2O3層、In2O3層、Fe3O4層、TiO2層、Cu2O層、ZnO層、NiO層、BaTiO3層、SrTiO3層などを用いることができる。

【0035】

金属酸化物層30の厚みは、特に限定されないが、例えば、3nm以上40nm以下である。金属酸化物層30の厚みが3nmより小さいと、ON状態でも金属拡散層22に捕獲された電子が抜けやすくなる場合がある。金属酸化物層30の厚みが40nmより大きいと、ON状態でも電流が流れ難くなる場合がある。

【0036】

第1電極40は、金属酸化物層30と電気的に接続されている。図示の例では、第1電極40は、金属酸化物層30上に形成されている。第1電極40としては、仕事関数の大きな金属を挙げることができ、より具体的には、金、ニッケル、白金などを挙げることができる。

【0037】

第2電極50は、基板10と電気的に接続されている。図示の例では、第2電極50は、基板10の下に形成されている。第2電極50は、図1に示すように、基板10の下面全面に形成されていてもよい。第2電極50は、基板10とオーミックコンタクトが得られれば、どのような金属でもよく、例えば、アルミニウムが挙げられる。第1電極40および第2電極50によって、金属酸化物層30および炭化シリコン層20に電圧を印加することができる。

【0038】

なお、図示はしないが、第2電極50は、基板10の上面に形成されていてもよい。すなわち、基板10の上面の面積は、炭化シリコン層20の下面の面積よりも大きく、基板10の上面の、炭化シリコン層20が形成されていない領域に、第2電極50が形成されていてもよい。

【0039】

1.2. 半導体メモリ装置の動作原理

次に、本実施形態に係る半導体メモリ装置の予想される動作原理について、図面を参照しながら説明する。図2および図3は、本実施形態に係る半導体メモリ装置100の動作原理を説明するための図であって、模式化したエネルギーバンド図を示すものである。なお、図2および図3において、金属拡散層22のバンドギャップは、金属拡散層22が含むSiOx(ただし、0<x<2)の割合によって変化することができる。図2および図3では、金属拡散層22のバンドギャップは、炭化シリコン層20のバンドギャップとほぼ同じと考えられる場合について図示している。また、図2および図3において、点線EFは、フェルミレベルを示している。

【0040】

まず、図2(A)は、第1電極40および第2電極50間に電圧を印加していない状態である。この状態では、半導体メモリ装置100は、OFF状態である。金属拡散層22には、金属が炭化シリコン層に拡散することによってその拡散した不純物の金属の位置で、または、拡散した不純物の金属の位置と、金属拡散層22に含まれるSiOx(ただし、0<x<2)による欠陥と、の双方で、電子を捕獲することができる捕獲準位22aが存在する。図2および図3において、捕獲準位22aは、模式的に四角領域で図示している。

【0041】

次に、図2(B)に示すように、酸化アルミニウム層30の表面に形成された第1電極40側がマイナスとなるように、電極40,50間に負電圧をかけていくと、例えば、基板10は抵抗が低いため、印加した電圧は、金属酸化物層30、および金属拡散層22を有する炭化シリコン層20にかかる。図2(B)に示す状態では、金属酸化物層30および炭化シリコン層20にかかる電圧は不十分で、障壁が厚く、電流はほとんど流れない。半導体メモリ装置100としては、高抵抗状態であり、OFF状態である。

【0042】

次に、図2(C)に示すように、第1電極40側がマイナスとなるように、電極40,50間にかける負電圧を大きくしていくと、ある電圧(例えば図7に示すVth2)を超えたところで、第1電極40からの電子eが金属拡散層22の捕獲準位22aに捕獲される。これにより、炭化シリコン層20のバンドが急峻に曲げられて、障壁が薄くなり、電子eが金属酸化物層30をトンネルする確率が高くなって、電流が流れる。半導体メモリ装置100は、高抵抗状態から低抵抗状態となり、OFF状態からON状態となる。OFF状態からON状態に遷移することは、メモリ装置の動作として、情報“1”の書き込みに対応する。

【0043】

次に、図3(D)に示すように、第1電極40側がプラスとなるように、電極40,50間に正電圧を印加する。このとき、電子eは、捕獲準位22aに捕獲されたままなので、今度は炭化シリコン層20のバンドが下方に曲がりにくくなり、第1電極40側がプラスとなるように印加された電圧の内、金属酸化物層30に印加される電圧の割合が高く、電子eが金属酸化物層30をトンネルする確率は高くなり、電流が流れる。半導体メモリ装置100は、低抵抗状態であり、ON状態である。

【0044】

次に、図3(E)に示すように、第1電極40側がプラスとなるように、電極40,50間にかける正電圧を大きくしていくと、ある電圧(例えば図7に示すVth1)を超えたところで、捕獲準位22aに捕獲されていた電子eが、金属酸化物層30側(第1電極40側)に放出される。これにより、第1電極40側がプラスとなるように印加された電圧が炭化シリコン層20と金属酸化物層30の両方に同様の割合で電圧が印加され、金属酸化物層30に印加される電圧の割合が減って、そのため、電子eが金属酸化物層30をトンネルする確率が低くなり、流れる電流が減少する。半導体メモリ装置100は、低抵抗状態から高抵抗状態となり、ON状態からOFF状態となる。ON状態からOFF状態に遷移することは、メモリ装置の動作として、情報の消去または情報“0”の書き込みに対応する。

【0045】

以上のように、半導体メモリ装置100は、第1電極40にかける電圧を、マイナス側に十分大きくすれば(Vth2を超える電圧を印加すれば)OFF状態からON状態に、逆に、プラス側に十分大きくすれば(Vth1を超える電圧を印加すれば)ON状態からOFF状態に変えることができる。そして、半導体メモリ装置100では、0〜Vth2の間の電圧で電流が流れるが、流れないかを調べれば、メモリ装置の記憶置である“0(OFF状態)”か、“1(ON状態)”か、を読み取ることができる。

【0046】

本実施形態に係る半導体メモリ装置100は、例えば、以下の特徴を有する。

【0047】

半導体メモリ装置100によれば、後述する実施例に示すように、消去、書き込みを繰り返してもON/OFF比を高く維持することができる。これは、捕獲準位22aに捕獲した電子eを、印加電圧によって、金属酸化物層30側(第1電極40側)に容易に放出することができるためだと推測される(図3(E)参照)。特許文献1に記載の従来のメモリのように、捕獲した電子を、逆側(第2電極側)に放出する場合は、酸化物層の障壁より厚い炭化シリコン層などの障壁により、消去の際に十分に捕獲電子を放出させることができず、ON/OFF比が半導体メモリ装置100より小さくなる。

【0048】

2. 半導体メモリ装置の製造方法

次に、本実施形態に係る半導体メモリ装置の製造方法について、図面を参照しながら説明する。図4〜図6は、本実施形態に係る半導体メモリ装置100の製造工程を模式的に示す断面図である。

【0049】

図4に示すように、基板10上に炭化シリコン層20を形成する。炭化シリコン層20は、例えば、CVD(Chemical Vapor Deposition)法、スパッタ法により形成される。

【0050】

図5に示すように、炭化シリコン層20上に金属層32を形成する。金属層32は、例えば、スパッタ法、真空蒸着法により形成される。金属層32としてアルミニウム層を用いた場合、金属酸化物層30は酸化アルミニウム層であり、アルミニウム層32(金属層32)の厚みは、酸化アルミニウム層30(金属酸化物層30、図1参照)の厚みのおよそ1/1.3程度となるため、例えば、2.3nm以上31nm以下である。なお、金属層32の厚みと、後述のように金属層32を熱酸化した後の金属酸化物層30の厚みと、の比は、金属の種類によって異なる。

【0051】

図6に示すように、金属層32を酸素雰囲気中で熱処理して、金属酸化物層30を形成する。より具体的には、例えば、酸素100%の大気圧中において、550℃程度で50分程度熱処理することにより、金属酸化物層30を形成する。形成される金属酸化物層30の厚みは、金属層32がアルミニウム層の場合は、アルミニウム層32(金属層32)の厚みのおよそ1.3倍になる。本工程の熱処理によって、金属層32を構成する金属の一部は、炭化シリコン層20に拡散する。金属層32としてアルミニウム層を用いた場合、アルミニウム層32(金属層32)を構成するアルミニウムの一部が、炭化シリコン層20に拡散する。金属層32が、2種類以上の金属から構成されている場合は、熱処理温度に依存して、主に1種の元素の一部が、または2種以上の元素の一部が炭化シリコン層20に拡散する。これにより、炭化シリコン層20に、金属拡散層22を形成することができる。さらに、本工程の熱処理によって、金属層32を構成する金属の一部が炭化シリコン層20に拡散すると同時に、炭化シリコン層20の金属酸化物層30との界面が酸化される。これにより、SiOx(ただし、0<x<2)を含む金属拡散層22を形成することができる。

【0052】

図1に示すように、金属酸化物層30上に第1電極40を形成する。次に、基板10の下に第2電極50を形成する。第1電極40および第2電極50は、例えば、スパッタ法、真空蒸着法により形成される。なお、第1電極40を形成する工程と、第2電極50を形成する工程とは、その先後を問わない。

【0053】

以上の工程により、本実施形態に係る半導体メモリ装置100を製造することができる。

【0054】

半導体メモリ装置100の製造方法によれば、消去、書き込みを繰り返してもON/OFF比を高く維持することができる半導体メモリ装置100を得ることができる。

【0055】

3. 実施例

以下に実験例を示し、本発明をより具体的に説明する。なお、本発明は、以下の実験例によって何ら限定されるものではない。

【0056】

3.1. 半導体メモリ装置の作製

n型のSi基板上に、炭化シリコン層として厚み10nmの3C−SiC層を、CVD法により形成した。次に、3C−SiC層上に、金属層としてAl層を、スパッタ法により形成した。Al層の厚みを、5nmと10nmとの2水準に振った。次に、酸素100%の大気圧中において、550℃で50分熱処理することにより、金属酸化物層としてAl2O3層を形成した。該熱処理により、Al層の一部が、3C−SiC層に拡散した。さらに、該熱処理により、3C−SiC層のAl層との界面が酸化された。これにより、金属拡散層として、SiO0.5、SiO1.0、およびSiO1.5を含むAl拡散層が形成された。次に、Al2O3層上に、第1電極としてAu層を、スパッタ法により形成した。次に、Si基板の下に、第2電極としてAl層を、スパッタ法により形成した。

【0057】

3.2. I−V特性

上記のように作製した半導体メモリ装置のI−V特性を評価した。図7は、実施例に係る半導体メモリ装置のI−V特性を示すグラフである。

【0058】

図7に示すように、メモリ特性であるヒステリシスを得ることができ、実施例に係る半導体メモリ装置は、良好なメモリ特性を有していることが分かった。

【0059】

なお、上述のとおり、図7に示すVth2は、OFF状態からON状態に遷移する閾値電圧であり、Vth1は、ON状態からOFF状態に遷移する閾値電圧である。そして、0〜Vth2の間の電圧で電流が流れるが、流れないかを調べれば、メモリ装置の記憶置である“0(OFF状態)”か、“1(ON状態)”か、を読み取ることができる。

【0060】

3.3. エンデュランス特性

上記のように作製した半導体メモリ装置のエンデュランス特性(メモリ書き換え回数とON/OFF比との関係)を評価した。図8は、実施例に係る半導体メモリ装置のエンデュランス特性を示すグラフである。なお、ON/OFF比とは、ON状態に対するOFF状態の抵抗の比である。また、図8では、Al層の厚みが10nmの半導体メモリ装置について評価した。

【0061】

図8に示すように、実施例の半導体メモリ装置は、メモリ書き換え回数が10万回で、ON/OFF比が6.5程度であり、良好なエンデュランス特性を有していることがわかった。一方、特許文献1の2端子メモリでは、メモリ書き換え回数が1万回で、ON/OFF比が最大3.5程度である。すなわち、実施例の半導体メモリ装置は、消去、書き込みを繰り返してもON/OFF比を高く維持できることがわかった。

【0062】

4. 半導体集積装置

次に、本実施形態に係る半導体集積装置について、図面を参照しながら説明する。図9は、本実施形態に係る半導体集積装置1000を模式的に示す断面図である。

【0063】

半導体集積装置1000は、本発明に係る半導体メモリ装置と、トランジスタと、を含むことができる。図9に示す例では、半導体集積装置1000は、半導体メモリ装置100と、バイポーラトランジスタ200と、MOSトランジスタ300と、を有している。

【0064】

半導体集積装置1000では、基板10として、例えば、p型Si基板を用いることができる。図示の例では、基板10には、不純物をドーピングすることによって、n型ウェル領域11が形成されている。n型ウェル領域11には、さらに不純物を高濃度にドーピングしたp+型ウェル領域12が形成され、p+型ウェル領域12にはn+型ウェル領域13が形成されている。

【0065】

n型ウェル領域11、p+型ウェル領域12、およびn+型ウェル領域13によって、バイポーラトランジスタ200が構成されている。n型ウェル領域11は、コレクタとして機能することができる。p+型ウェル領域12は、ベースとして機能することができる。n+型ウェル領域13は、エミッタとして機能することができる。

【0066】

p+型ウェル領域12上には、炭化シリコン層20、金属酸化物層30、および第1電極40が、この順で形成されている。さらに、p+型ウェル領域12上には、第2電極50が形成されている。ウェル領域11,12が形成された基板10、炭化シリコン層20、金属酸化物層30、および電極40,50によって、半導体メモリ装置100が構成されている。図示の例では、1つの第2電極50を共通電極として、2つの第1電極40が形成されている。このように、第2電極50を共通電極として、複数の半導体メモリ装置100の集積化を図ることができる。

【0067】

なお、第2電極50は、バイポーラトランジスタ200のベース電極としても機能することができる。また、n+型ウェル領域13上には、図9に示すように、ベース電極70が形成されていてもよい。

【0068】

n型ウェル領域11には、さらに、p+型ウェル領域16,17が形成されている。p+型ウェル領域16は、ソース領域16となり、p+型ウェル領域17は、ドレイン領域17となることができる。さらに、n型ウェル領域11上にはゲート絶縁層60が形成され、ゲート絶縁層60上にはゲート電極72が形成されている。ソース領域16、ドレイン領域17、ゲート絶縁層60、およびゲート電極72によって、MOSトランジスタ300が形成されている。ソース領域16とドレイン領域17との間に位置するn型ウェル領域11は、チャネル領域15となることができる。図9に示すように、ソース領域16上にはソース電極74が形成され、ドレイン領域17上にはドレイン電極76が形成されていてもよい。

【0069】

バイポーラトランジスタ200とMOSトランジスタ300との間には、例えば、素子分離領域80が形成されている。素子分離領域80の材質としては、例えば、酸化シリコンが挙げられる。素子分離領域80によって、バイポーラトランジスタ200とMOSトランジスタ300とを、電気的に分離することができる。

【0070】

層間絶縁層90は、基板10の上方に形成されている。層間絶縁層90の材質としては、例えば、酸化シリコンが挙げられる。図示はしないが、層間絶縁層90の上方には、多層配線構造が形成されていてもよく、これによって、半導体メモリ装置100、バイポーラトランジスタ200、およびMOSトランジスタ300が結線されていてもよい。

【0071】

半導体集積装置1000によれば、消去、書き込みを繰り返してもON/OFF比を高く維持することができる半導体メモリ装置100を有することができる。そのため、半導体集積装置1000は、高い性能を有することができる。

【0072】

なお、本発明は、実施の形態で説明した構成と実質的に同一の構成(例えば、機能、方法及び結果が同一の構成、あるいは目的及び効果が同一の構成)を含む。また、本発明は、実施の形態で説明した構成の本質的でない部分を置き換えた構成を含む。また、本発明は、実施の形態で説明した構成と同一の作用効果を奏する構成又は同一の目的を達成することができる構成を含む。また、本発明は、実施の形態で説明した構成に公知技術を付加した構成を含む。

【符号の説明】

【0073】

10 基板、11 n型ウェル領域、12 p+型ウェル領域、

13 n+型ウェル領域、15 チャネル領域、16 ソース領域、

17 ドレイン領域、20 炭化シリコン層、22 金属拡散層、22a 捕獲準位、

30 金属酸化物層、32 金属層、40 第1電極、50 第2電極、

60 ゲート絶縁層、70 エミッタ電極、72 ゲート電極、74 ソース電極、

76 ドレイン電極、80 素子分離領域、90 層間絶縁層、

100 半導体メモリ素子、200 バイポーラトランジスタ、

300 MOSトランジスタ、1000 半導体集積装置

【特許請求の範囲】

【請求項1】

基板と、

前記基板の上に形成された炭化シリコン層と、

前記炭化シリコン層の上に形成された金属酸化物層と、

前記金属酸化物層と電気的に接続された第1電極と、

前記基板と電気的に接続された第2電極と、

を含む、半導体メモリ装置。

【請求項2】

請求項1において、

前記炭化シリコン層は、

前記金属酸化物層との界面に、金属が拡散された金属拡散層を有する、半導体メモリ装置。

【請求項3】

請求項2において、

前記金属酸化物層は、酸化アルミニウム層であり、

前記金属拡散層に拡散された前記金属は、アルミニウムである、半導体メモリ装置。

【請求項4】

請求項2または3において、

前記金属拡散層は、SiOx(ただし、0<x<2)を含む、半導体メモリ装置。

【請求項5】

請求項1ないし4のいずれか1項において、

前記炭化シリコン層は、前記金属酸化物層との界面において、前記第1電極から注入された電子を、捕獲および放出する層であり、

前記金属酸化物層は、前記電子をトンネルする層であり、

前記第1電極と前記第2電極との間に電圧が印加されることによって、情報の書き込みおよび消去を行う、半導体メモリ装置。

【請求項6】

基板の上に炭化シリコン層を形成する工程と、

前記炭化シリコン層の上に金属層を形成する工程と、

前記金属層を酸素雰囲気中で熱処理して、金属酸化物層を形成する工程と、

前記金属酸化物層と電気的に接続する第1電極を形成する工程と、

前記基板と電気的に接続する第2電極を形成する工程と、

を含む、半導体メモリ装置の製造方法。

【請求項7】

請求項6において、

前記金属酸化物層を形成する工程における前記熱処理によって、前記金属層を構成する金属の一部は、前記炭化シリコン層に拡散して、金属拡散層が形成される、半導体メモリ装置の製造方法。

【請求項8】

請求項7において、

前記金属層は、アルミニウム層であり、

前記金属酸化物層は、酸化アルミニウム層であり、

前記炭化シリコン層に拡散する前記金属は、アルミニウムである、半導体メモリ装置の製造方法。

【請求項9】

請求項7または8において、

前記金属酸化物層を形成する工程における前記熱処理によって、前記金属拡散層は、SiOx(ただし、0<x<2)を含む、半導体メモリ装置の製造方法。

【請求項10】

請求項6ないし9のいずれか1項において、

前記炭化シリコン層は、前記金属酸化物層との界面において、前記第1電極から注入された電子を、捕獲および放出する層であり、

前記金属酸化物層は、前記電子をトンネルする層であり、

前記第1電極と前記第2電極との間に電圧を印加して、情報の書き込みおよび消去を行う、半導体メモリ装置の製造方法。

【請求項1】

基板と、

前記基板の上に形成された炭化シリコン層と、

前記炭化シリコン層の上に形成された金属酸化物層と、

前記金属酸化物層と電気的に接続された第1電極と、

前記基板と電気的に接続された第2電極と、

を含む、半導体メモリ装置。

【請求項2】

請求項1において、

前記炭化シリコン層は、

前記金属酸化物層との界面に、金属が拡散された金属拡散層を有する、半導体メモリ装置。

【請求項3】

請求項2において、

前記金属酸化物層は、酸化アルミニウム層であり、

前記金属拡散層に拡散された前記金属は、アルミニウムである、半導体メモリ装置。

【請求項4】

請求項2または3において、

前記金属拡散層は、SiOx(ただし、0<x<2)を含む、半導体メモリ装置。

【請求項5】

請求項1ないし4のいずれか1項において、

前記炭化シリコン層は、前記金属酸化物層との界面において、前記第1電極から注入された電子を、捕獲および放出する層であり、

前記金属酸化物層は、前記電子をトンネルする層であり、

前記第1電極と前記第2電極との間に電圧が印加されることによって、情報の書き込みおよび消去を行う、半導体メモリ装置。

【請求項6】

基板の上に炭化シリコン層を形成する工程と、

前記炭化シリコン層の上に金属層を形成する工程と、

前記金属層を酸素雰囲気中で熱処理して、金属酸化物層を形成する工程と、

前記金属酸化物層と電気的に接続する第1電極を形成する工程と、

前記基板と電気的に接続する第2電極を形成する工程と、

を含む、半導体メモリ装置の製造方法。

【請求項7】

請求項6において、

前記金属酸化物層を形成する工程における前記熱処理によって、前記金属層を構成する金属の一部は、前記炭化シリコン層に拡散して、金属拡散層が形成される、半導体メモリ装置の製造方法。

【請求項8】

請求項7において、

前記金属層は、アルミニウム層であり、

前記金属酸化物層は、酸化アルミニウム層であり、

前記炭化シリコン層に拡散する前記金属は、アルミニウムである、半導体メモリ装置の製造方法。

【請求項9】

請求項7または8において、

前記金属酸化物層を形成する工程における前記熱処理によって、前記金属拡散層は、SiOx(ただし、0<x<2)を含む、半導体メモリ装置の製造方法。

【請求項10】

請求項6ないし9のいずれか1項において、

前記炭化シリコン層は、前記金属酸化物層との界面において、前記第1電極から注入された電子を、捕獲および放出する層であり、

前記金属酸化物層は、前記電子をトンネルする層であり、

前記第1電極と前記第2電極との間に電圧を印加して、情報の書き込みおよび消去を行う、半導体メモリ装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図7】

【図8】

【公開番号】特開2013−58715(P2013−58715A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−266625(P2011−266625)

【出願日】平成23年12月6日(2011.12.6)

【出願人】(504132881)国立大学法人東京農工大学 (595)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年12月6日(2011.12.6)

【出願人】(504132881)国立大学法人東京農工大学 (595)

【Fターム(参考)】

[ Back to top ]