半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体を用いたメモリ装置に関する。

【背景技術】

【0002】

最初に、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースとする。すなわち、電位の高低によって、それらを区別しない。したがって、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

【0003】

また、本明細書において、接続、とは、一時的であっても、実効的な直流電流が、供給可能な状態になる構造を有していることをいう。従って、接続している状態とは、直接、接続している状態のみを必ずしも指すわけではなく、直流電流が、供給可能であるように、配線、抵抗などの回路素子を介して間接的に接続している状態もその範疇に含む。なお、実際に回路に直流電流が供給されるように設計されているかどうかは問わない。

【0004】

例えば、2つのノード間にスイッチング素子が設けられている場合には、条件付ながら(すなわち、スイッチがオンであるときだけではあるが)、直流電流が供給可能となるので、接続する、という。一方、2つのノード間に、容量素子のみが設けられている場合には、容量素子を介しては、実効的な直流電流を供給することができないので、このノード間は接続されていない、という。

【0005】

同様に2つのノード間にダイオードのみが設けられている場合も、いずれかのノードの電位が高ければ直流電流を供給できるので、接続する,という。この際には、回路設計上、電流が流れないような電位が2つのノードに与えられている場合(この場合には、現実の回路において2つのノードにダイオードを介して電流が流れることがない)であっても、本明細書では、接続している、という。

【0006】

例えば、ノードAがトランジスタのソースに接続し、ノードBがドレインに接続する場合には、ノードAとノードBの間には、ゲートの電位によっては直流電流を流すことができるので、ノードAとノードBは接続している、という。

【0007】

一方、ノードAがトランジスタのソースに接続し、ノードCがゲートに接続する場合には、トランジスタのソース、ドレイン、ゲートの電位の如何にかかわらず、ノードAとノードCの間に実効的な直流電流を流すことができないので、ノードAとノードCは接続していない、という。

【0008】

上記において、実効的な直流電流とは、リーク電流等の意図しない電流を除いた電流という意味である。なお、実効的な直流電流の値は、その大きさ(絶対値)で定義されるものではなく、回路に応じて異なることがある。すなわち、ある回路では1pAという小電流であっても実効的な電流となりえるし、他の回路では、それより大きな1μAという電流であっても実効的な電流とみなされないこともある。

【0009】

なお、言うまでもないことであるが、入力と出力を有する1つの回路(例えば、インバータ)において、入力と出力が回路内で接続している必要はない。インバータを例に取れば、入力と出力はインバータ内部で接続していない。

【0010】

さらに、本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分が明確でなく、配線が延在している場合だけのこともある。例えば、絶縁ゲート型電界効果トランジスタ(以下、単にトランジスタ、という)の回路では、一本の配線が複数のトランジスタのゲートを兼ねている場合もある。その場合、回路図では、一本の配線からゲートに何本もの分岐が生じるように書かれることもある。本明細書では、そのような場合でも、「配線がゲートに接続する」という表現を用いることがある。

【0011】

なお、本明細書では、マトリクスにおいて特定の行や列、位置を扱う場合には、符号に座標を示す記号をつけて、例えば、「メモリセルMC_1_1」、「ビット線BL_2」というように表記する。また、一つの素子が複数の行や列の機能を有するときには、「センスアンプSA_1/2」というように表記することもある。

【0012】

しかし、特に、行や列、位置を特定しない場合や集合的に扱う場合、あるいはどの位置にあるか明らかである場合には、「メモリセルMC」、「ビット線BL」」、あるいは、単に「メモリセル」、「ビット線」というように表記することもある。

【0013】

1つのトランジスタと1つの容量素子を用いてメモリセルを形成するDRAMは、高集積化でき、原理的に無制限に書き込みでき、さらに、書き込み読み出しの速度も比較的高速でおこなえるため、多くの電子機器で使用されている。DRAMは、各メモリセルの容量素子に電荷を蓄積することにより、データを記憶し、この電荷を放出することによりデータを読み出す。

【0014】

従来は、トランジスタとしてシリコンを用いていたために、1秒間に数10回のリフレッシュが必要であったが、よりバンドギャップの大きな酸化物半導体を用いたトランジスタでは、実質的に永久にデータを保持できることが示された(特許文献1参照)。また、極端に薄いシリコン膜を用いることによっても、従来のトランジスタよりオフ電流を3桁以上も低減できることが示された(特許文献2参照)。

【0015】

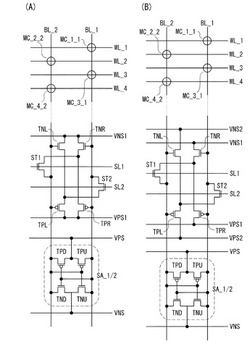

図2(A)および図2(B)に従来のDRAMの読み出しに関する回路と読み出し方法を示す。図2(A)に示すDRAMは、いわゆるフォールデッド方式のDRAMの回路であり、一対のビット線BL_1とビット線BL_2と、ワード線WL_1、ワード線WL_2、ワード線WL_3、ワード線WL_4等とそれらの交点にメモリセルMC_1_1、メモリセルMC_2_2、メモリセルMC_3_1、メモリセルMC_4_2等を有する。

【0016】

また、ビット線BL_1とビット線BL_2の一端にはセンスアンプSA_1/2が設けられている。通常、センスアンプはフリップフロップ型の回路を用いる。

【0017】

図2(B)にこれらの回路を駆動するタイミングチャートを示す。ここでは、”1”のデータはメモリセルMCの容量素子が+1Vに、”0”のデータはメモリセルMCの容量素子が0Vに充電されているものとする。

【0018】

メモリセルMC_1_1のデータを読み出すには以下のようにおこなう。まず、プリチャージ回路(図示せず)を用いて、ビット線BL_1とビット線BL_2とを+0.5Vにプリチャージする。その後、ビット線BL_1とビット線BL_2とをフローティング状態とする。また、フリップフロップ回路型のセンスアンプSA_1/2の、Pチャネル型トランジスタTPUおよびPチャネル型トランジスタTPDのソースに電位を供給するための配線VPSの電位、Nチャネル型トランジスタTNUおよびNチャネル型トランジスタTNDのソースに電位を供給するための配線VNSの電位は+0.5Vとする。

【0019】

その後、ワード線WL_1の電位を適切な値にして、メモリセルMC_1_1のセルトランジスタをオンとする(図2(B)の時刻T1)。なお、このように配線の電位を変化させることで、それに接続するトランジスタをオンとすることを、配線の電位をオンに設定する、という。この操作により、メモリセルMC_1_1の容量素子に蓄積されていた電荷がビット線BL_1に放出される。

【0020】

メモリセルMC_1_1の容量素子の容量とビット線BL_1の容量によって、ビット線BL_1の電位が決定される。ここでは、メモリセルの容量素子の電位が0Vであったため、プリチャージ電位より低下して、+0.4Vになったものとする。

【0021】

一方、ワード線WL_1の電位をオンに設定しても、ビット線BL_2に接続するメモリセルはないので、ビット線BL_2の電位は変動せず、+0.5Vのままである。すなわち、ビット線BL_1の電位の方が、ビット線BL_2の電位より、0.1V低い。

【0022】

その後、センスアンプSA_1/2の配線VPSの電位を+1Vに向けてある速度で上昇させ、また、配線VNSの電位を0Vに向けて同様な速度で下降させる(図2(B)の時刻T2)。この操作により、ある段階で、Pチャネル型トランジスタTPDとNチャネル型トランジスタTNUがオンとなる。

【0023】

その結果、相対的に電位の低いビット線BL_1の電位はさらに低下し、相対的に電位の高いビット線BL_2の電位はさらに高くなり、最終的には、ビット線BL_1の電位は0Vとなり、ビット線BL_2の電位は+1Vとなる。

【0024】

この過程(増幅過程)での配線VPSの電位と配線VNSの電位の変化する速度は、増幅初期においては、十分に小さいことが望ましい。上記のように、増幅初期電位差が0.1Vというように小さな場合には、配線VPSの電位と配線VNSの電位を急激に変動させると、増幅に失敗するためである。このため、増幅に時間を要する。

【0025】

一方で、増幅に時間がかかると、特に増幅初期段階では、外部のノイズにより読み出しに失敗する確率が高まる。

【0026】

また、このように0.1Vという微弱な電位差を増幅するため、センスアンプSA_1/2に用いるトランジスタのしきい値のばらつきは小さいことが求められる。例えば、Nチャネル型トランジスタTNUのしきい値が+0.35V、Pチャネル型トランジスタTPUのしきい値が−0.45V、Nチャネル型トランジスタTNDのしきい値が+0.45V、およびPチャネル型トランジスタTPDのしきい値が−0.35Vであるとすると、上記の増幅過程において、Pチャネル型トランジスタTPUおよびPチャネル型トランジスタTPDがともにオンとなり、データの読み出しに失敗することがある。

【0027】

一般に、センスアンプに用いるトランジスタのしきい値のばらつきは、ビット線間の増幅初期電位差の半分未満、好ましくは30%未満であることが要求される。上記の場合、トランジスタのしきい値のばらつきは50mV、ビット線間の増幅初期電位差は0.1Vであるため、増幅の際にエラーが発生しやすい。

【0028】

一般に、トランジスタのしきい値のばらつきは、ロット間ばらつき(基板間ばらつき)とチップ間ばらつき(基板内ばらつき)と隣接トランジスタばらつき、の3つに大きく分類される。

【0029】

ロット間ばらつきは、プロセス条件、膜厚や線幅のロット間の違いに依存するものであり、また、チップ間ばらつきは、ドーズ量、膜厚や線幅の基板面内のばらつきによるものである。いずれも、ばらつきは巨視的なものであり、これらの要因によるしきい値のばらつきは基板バイアス等により補正できる。

【0030】

これに対し、隣接トランジスタばらつきは、主として、ドーパント濃度の統計的ゆらぎ(非特許文献1参照)によるものであり、トランジスタが微細化するにつれ増大する。すなわち、DRAMの高集積化のためにトランジスタが微細化するとセンスアンプの動作が不安定となる。

【0031】

また、酸化物半導体のようにシリコンよりも移動度が1桁以上小さい半導体を用いる場合には、データのアクセスを高速でおこなうために容量素子の容量を通常のものよりも1桁以上小さくすることが必要となる。もし、1つのビット線に接続するメモリセルを従来と同等とするのであれば、読み出しの際のビット線の電位変動はより小さくなり、エラーが生じやすくなる。

【0032】

非特許文献2によれば、ビット線に接続するメモリセルが256個であれば、回路線幅40nmでは、ビット線の容量は35fFである。もし、容量素子の容量を3fFとし、1つのビット線に256個のメモリセルを接続するのであれば、ビット線の電位の変動は40mV程度であるため、そのような微細な電位変動をエラーなくかつ短時間で増幅する技術が求められる。

【先行技術文献】

【特許文献】

【0033】

【特許文献1】米国特許出願公開第2011/0156027号明細書

【特許文献2】米国特許第7772053号明細書

【非特許文献】

【0034】

【非特許文献1】K.Takeuchi et al., ”Channel Engineering for the Reduction of Random−Dopant−Placement−Induced Threshold Voltage Fluctuation”, pp. 841−844, TECHNICAL DIGEST OF INTERNATIONAL ELECTRON DEVICES MEETING, 1997.

【非特許文献2】Mueller et al.,”Challenges for the DRAM Cell Scaling to 40nm”, TECHNICAL DIGEST OF INTERNATIONAL ELECTRON DEVICES MEETING, pp.347−350, 2005.

【発明の概要】

【発明が解決しようとする課題】

【0035】

本発明の一態様はこのような問題点を解決することを課題とするものである。本発明の一態様はよりビット線の電位の変動が小さい場合でも、誤動作しにくい半導体メモリ装置を提供することを課題とする。また、本発明の一態様はトランジスタのしきい値のばらつきがより大きな場合でも、誤動作しにくい半導体メモリ装置を提供することを課題とする。また、本発明の一態様はより回路が微細化した場合でも誤動作しにくい半導体メモリ装置を提供することを課題とする。

【0036】

また、本発明の一態様は、容量素子の容量を従来のDRAMに用いられている値以下、具体的には10fF以下、好ましくは1fF以下としても十分に機能するメモリ装置を提供することを課題とする。

【0037】

また、本発明の一態様は、新規な構造のメモリ装置あるいはその駆動方法を提供することを課題とする。特に消費電力を低減できるメモリ装置あるいはメモリ装置の駆動方法を提供することを課題とする。

【課題を解決するための手段】

【0038】

本発明の一態様は、第1のビット線と第2のビット線と、これらの間にインバータとスイッチと、第1のビット線および第2のビット線のいずれかに接続するメモリセルとを有し、また、これらインバータとスイッチが直列に接続されている半導体メモリ装置である。

【0039】

また、本発明の一態様は、上記の半導体メモリ装置において、スイッチをオンとする過程と、その後に、第1のビット線と第2のビット線の電位差を増幅する過程と、を有する半導体メモリ装置の駆動方法である。

【0040】

また、本発明の一態様は、第1のビット線と第2のビット線と、これらの間に第1のインバータと第1のスイッチと第2のインバータと第2のスイッチと、第1のビット線および第2のビット線のいずれかに接続するメモリセルとを有し、第1のインバータと第1のスイッチおよび第2のインバータと第2のスイッチは、それぞれ接続されており、第1のビット線と第1のインバータ、第2のビット線と第1のスイッチ、第1のビット線と第2のスイッチ、第2のビット線と第2のインバータが、それぞれ接続されている半導体メモリ装置である。

【0041】

また、本発明の一態様は、上記の半導体メモリ装置において、第1のスイッチをオンとする過程と、その後に、第2のスイッチをオンとすることにより、第1のインバータ、第1のスイッチ、第2のインバータと第2のスイッチよりなるループを構成する半導体メモリ装置の駆動方法である。

【0042】

インバータ(あるいは第1のインバータ、第2のインバータ)としては、さまざまな種類のものを用いることができる。例えば、相補型インバータ、抵抗負荷型インバータ、クロックドインバータ等あるいはそれらの組み合わせを用いることができる。

【0043】

上記において、メモリセルのトランジスタはインバータのトランジスタとは異なる層に設けられていてもよいが、インバータのトランジスタは単結晶半導体を用いるとよい。インバータではトランジスタのしきい値のばらつきを十分に抑制することが必要であるので、そのチャネル面積をメモリセルのトランジスタの4倍以上、好ましくは16倍以上とするとよい。

【0044】

また、インバータの占有する部分のワード線方向の長さは、ビット線の幅の3倍以上、好ましくは5倍以上とするとよい。同様にインバータの占有する部分のビット線方向の長さは、ワード線の幅の3倍以上、好ましくは5倍以上とするとよい。

【0045】

このようにインバータは大きな面積を占有するが、インバータに用いるトランジスタのチャネル面積を十分に大きくすることにより、不純物濃度の統計的ゆらぎに起因するトランジスタのしきい値のばらつきを低減させることができる。また、メモリセルを薄膜状の半導体で形成する場合には、インバータ等の上に重ねてメモリセルを形成できるので集積度を高めることができる。

【0046】

また、上記において、スイッチ(あるいは第1のスイッチ、第2のスイッチ)は、1以上のトランジスタを用いて構成できる。最も簡単には1つのNチャネル型トランジスタあるいはPチャネル型トランジスタを用いて構成できる。また、導電型の異なる2つ以上のトランジスタを並列に接続した、トランスミッションゲートでもよい。

【発明の効果】

【0047】

上記の構成のいずれかを採用することにより、前記課題の少なくとも一を解決できる。本発明の一態様では、スイッチ(あるいは第1のスイッチ)をオンとし、インバータ(あるいは第1のインバータ)の電位をオンに設定することで、第1のビット線の電位に応じて、第2のビット線の電位は、第1のビット線の電位と逆位相の電位に変化する。すなわち、第1のビット線の電位が、インバータのしきい値よりも高ければ、第2のビット線の電位はインバータのしきい値よりも低くなり、第1のビット線の電位が、インバータのしきい値よりも低ければ、第2のビット線の電位はインバータのしきい値よりも高くなる。

【0048】

例えば、インバータを構成するPチャネル型トランジスタのしきい値が−0.35Vから−0.45V、Nチャネル型トランジスタのしきい値が+0.35Vから+0.45Vの範囲にあり、Pチャネル型トランジスタのソースの電位を+1V、Nチャネル型トランジスタのソースの電位を0Vとすると、インバータの入力の電位(すなわち、第1のビット線の電位)が+0.4Vであれば、インバータに信号を入力してから十分に時間が経過した状態では、インバータの出力の電位(すなわち、第2のビット線の電位)は、+0.75V以上とできる。

【0049】

読み出し過程のような短い期間では、インバータを構成するトランジスタの抵抗や第2のビット線の抵抗および容量によって、第2のビット線の電位は、より低い電位となるが、それでも、必要な期間に第2のビット線の電位を+0.6V以上とできる。

【0050】

このため、第1のビット線の第2のビット線の電位差は0.2V以上となるので、インバータと同じしきい値ばらつきを有するトランジスタよりなるセンスアンプを用いてもエラーが発生することは極力抑制される。

【0051】

また、増幅開始時点での第1のビット線と第2のビット線の電位差をより大きくできることにより、第1のビット線と第2のビット線に接続するセンスアンプのNチャネル型トランジスタのソースとPチャネル型トランジスタのソースの電位差を、急速に拡大させることもできる。そのため、読み出しに要する時間を短縮できる。

【0052】

さらに、増幅開始時点での第1のビット線と第2のビット線の電位差がより大きくなること、あるいは、増幅に要する期間を短縮することにより、増幅過程におけるノイズの影響を受けにくくなる。

【0053】

特にオープンビット方式のDRAMでは、読み出しに使うビット線と参照電位に用いるビット線が離れた位置にあるため、フォールデッド方式に比べてノイズの影響による読み出しエラーが大きいことが問題であるが、本発明の一態様では、ノイズの影響が相対的に小さくなることにより、オープンビット方式のDRAMで効果が顕著となる。

【0054】

ここで注意しておきたいことは、上記のようなしきい値のばらつきを有するトランジスタを用いて作製したフリップフロップ型センスアンプでは、0.1Vの電位差を増幅するとエラーが発生しやすくなるのに、同じばらつきのトランジスタを用いて作製したインバータでは、0.1Vの電位差を反転・増幅できるということである。本発明の一態様はこの特徴を有効に利用して効果を得ることができる。

【図面の簡単な説明】

【0055】

【図1】本発明の半導体メモリ装置の回路の例を示す図である。

【図2】従来の半導体メモリ装置の回路の例と駆動方法を示す図である。

【図3】本発明の半導体メモリ装置の回路の例を説明する図である。

【図4】本発明の半導体メモリ装置の駆動方法の例を説明する図である。

【図5】本発明の半導体メモリ装置の回路の例を説明する図である。

【図6】本発明の半導体メモリ装置のレイアウト例を示す図である。

【図7】本発明の半導体メモリ装置の回路の例を説明する図である。

【発明を実施するための形態】

【0056】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0057】

なお、電位として、以下に具体的な数値を挙げるが、それは、本発明の技術思想の理解を助けることが目的である。言うまでもなく、それらの値はトランジスタや容量素子のさまざまな特性によって、あるいは実施者の都合によって変更される。

【0058】

また、以下の実施の形態に示される半導体メモリ装置は、以下の方法以外の方法によっても、データを書き込み、あるいは読み出すことができる。

【0059】

(実施の形態1)

本実施の形態では、図1(A)、図1(B)、図4(A)を用いて本発明の一態様の半導体メモリ装置およびその動作の例について説明する。

【0060】

図1(A)に示す半導体メモリ装置は、ワード線WL、ワード線WLに直交するビット線BL、ワード線WLに平行な第1選択線SL1および第2選択線SL2と、複数のメモリセルMCを有する。また、第1選択トランジスタST1と第2選択トランジスタST2とPチャネル型トランジスタTPL、Pチャネル型トランジスタTPR、Nチャネル型トランジスタTNL、Nチャネル型トランジスタTNRとそれらのソースに電位を供給するための配線VPS1、配線VNS1を有する。

【0061】

Pチャネル型トランジスタTPRとNチャネル型トランジスタTNR、Pチャネル型トランジスタTPLとNチャネル型トランジスタTNLは、それぞれ第1のインバータ、第2のインバータを構成する。第1選択トランジスタST1のソースはビット線BL_2に接続し、ドレインはNチャネル型トランジスタTNRのドレインとPチャネル型トランジスタTPRのドレイン(すなわち第1のインバータの出力端子)に接続し、ゲートは第1選択線SL1に接続する。第2選択トランジスタST2のソースはビット線BL_1に接続し、ドレインはNチャネル型トランジスタTNLのドレインとPチャネル型トランジスタTPLのドレイン(すなわち第2のインバータの出力端子)に接続し、ゲートは第2選択線SL2に接続する。

【0062】

さらに、センスアンプSA_1/2と、それを構成するトランジスタのソースに電位を供給するための配線VPS、配線VNSを有する。センスアンプSA_1/2は従来のDRAMと同様に、ビット線BL_1とビット線BL_2の電位差を増幅するのに用いられる。

【0063】

このような半導体メモリ装置でデータを読み出す例について説明する。ここでも、メモリセルMC_1_1のデータを読み出すとする。本実施の形態のNチャネル型トランジスタのしきい値の平均値は+0.4Vで、しきい値のばらつきは50mV、Pチャネル型トランジスタのしきい値の平均値は−0.4Vでしきい値のばらつきは50mVとする。

【0064】

従来のDRAMの場合と同様に、プリチャージ回路(図示せず)を用いて、ビット線BL_1とビット線BL_2とを+0.5Vにプリチャージし、その後、ビット線BL_1とビット線BL_2とをフローティング状態とする。また、センスアンプSA_1/2の配線VPSの電位、配線VNSの電位は共に+0.5Vとする。一方で、配線VPS1の電位は+1V、配線VNS1の電位は0Vとする。

【0065】

その後、ワード線WL_1の電位をオンに設定して、メモリセルMC_1_1のセルトランジスタをオンとする(図4(A)の時刻T1)。この操作により、メモリセルMC_1_1の容量素子に蓄積されていた電荷がビット線BL_1に放出される。

【0066】

メモリセルMC_1_1の容量素子の容量とビット線BL_1の容量によって、ビット線BL_1の電位が決定される。ここでは、メモリセルMC_1_1の容量素子の電位が0Vであったため、プリチャージ電位より低下して、+0.4Vになったものとする。

【0067】

また、時刻T1に第1選択線SL1の電位をオンに設定して、第1選択トランジスタST1をオンとする。なお、第1選択線SL1の電位をオンに設定するタイミングは時刻T1の前あるいは後でもよい。ビット線BL_1の電位が+0.4Vであるので、トランジスタのしきい値ばらつきを考慮しても、Pチャネル型トランジスタTPRとNチャネル型トランジスタTNRで構成される第1のインバータは、プリチャージ電位(+0.5V)より高い電位を出力する。その電位は第1選択トランジスタST1を経て、ビット線BL_2に伝わり、ビット線BL_2の電位は、プリチャージ電位よりも高くなる。

【0068】

その後、配線VPSの電位を+1Vに向けて上昇させ、また、配線VNSの電位を0Vに向けて下降させ、センスアンプSA_1/2をアクティブとする(図4(A)の時刻T2)。このようにして、データを増幅することができる。従来のDRAMではこの操作に時間がかかっていたが、本実施の形態の半導体メモリ装置では、ビット線BL_1の電位とビット線BL_2の電位の差が十分に大きい状態で増幅が開始されるので、電位の変動する速度を大きくしても、増幅エラーとなることが少ない。そのため、増幅に要する時間が短縮できる。また、このように増幅に要する時間が短いので、この期間に外部のノイズの影響を受けることが少なく、読み出しに失敗する確率が低下する。

【0069】

図1(A)に示す半導体メモリ装置は、第1のインバータと第2のインバータの電源電圧を同時に制御するものであるが、図1(B)のように第1のインバータと第2のインバータの電源電圧を個別に制御する構造としてもよい。すなわち、第1のインバータに電源を供給する配線VPS1と配線VNS1と、第2のインバータに電源を供給する配線VPS2と配線VNS2とを分離してもよい。

【0070】

上記の例では、第2のインバータはデータの読み出しには使用されないが、配線VPS1と配線VNS1の間に電位差があると、Pチャネル型トランジスタTPLとNチャネル型トランジスタTNLの間に貫通電流が流れる。貫通電流は第2のインバータの電源電圧を0とする(例えば、配線VPS2と配線VNS2の電位を共に+0.5Vとして、電位差を0とする)ことでなくすことができる。このようにすると、消費電力を低減できる。

【0071】

また、上記の例では、第1のインバータおよび第2のインバータは最初から電源が入った状態であるが、消費電力を低減する観点からは、時刻T1あるいは時刻T1の前あるいは時刻T1の後に電源を入れ、時刻T2あるいは時刻T2の前あるいは時刻T2の後に電源を切ることも好ましい。特に、本実施の形態のインバータは、入力電位がプリチャージ電位付近であると、最も貫通電流が多く流れるため、第1のインバータおよび第2のインバータの電源をこまめにオンオフすることは消費電力を低減する上で有効である。

【0072】

より消費電力を低減するためには、第1のインバータおよび第2のインバータの電源電圧が個別に制御できるものであれば、第2のインバータの電源電圧を0とし、第1のインバータは時刻T1あるいは時刻T1の前あるいは時刻T1の後に電源を入れ、時刻T2あるいは時刻T2の前あるいは時刻T2の後に電源を切ることが好ましい。

【0073】

(実施の形態2)

本実施の形態では、図3(A)、図3(B)、図4(B)を用いて本発明の一態様の半導体メモリ装置およびその動作の例について説明する。

【0074】

図3(A)に示す半導体メモリ装置は、ワード線WL、ワード線WLに直交するビット線BL、ワード線WLに平行な第1選択線SL1および第2選択線SL2と、複数のメモリセルMCを有する。また、第1選択トランジスタST1と第2選択トランジスタST2とPチャネル型トランジスタTPL、Pチャネル型トランジスタTPR、Nチャネル型トランジスタTNL、Nチャネル型トランジスタTNRとそれらのソースに電位を供給するための配線VPS1、配線VNS1を有する。

【0075】

Pチャネル型トランジスタTPRとNチャネル型トランジスタTNR、Pチャネル型トランジスタTPLとNチャネル型トランジスタTNLは、それぞれ第1のインバータ、第2のインバータを構成する。第1選択トランジスタST1のソースはビット線BL_2に接続し、ドレインはNチャネル型トランジスタTNRのドレインとPチャネル型トランジスタTPRのドレイン(すなわち第1のインバータの出力端子)に接続し、ゲートは第1選択線SL1に接続する。第2選択トランジスタST2のソースはビット線BL_1に接続し、ドレインはNチャネル型トランジスタTNLのドレインとPチャネル型トランジスタTPLのドレイン(すなわち第2のインバータの出力端子)に接続し、ゲートは第2選択線SL2に接続する。

【0076】

本実施の形態の半導体メモリ装置はセンスアンプを用いず、上記の第1のインバータと第2のインバータの組み合わせでビット線BL_1とビット線BL_2の電位差を増幅するものである。そのため、図1(A)あるいは図1(B)の半導体メモリ装置より集積化できる。

【0077】

このような半導体メモリ装置でデータを読み出す例について説明する。ここでも、メモリセルMC_1_1のデータを読み出すとする。本実施の形態のNチャネル型トランジスタのしきい値の平均値は+0.4Vで、しきい値ばらつきは50mV、Pチャネル型トランジスタのしきい値の平均値は−0.4Vでしきい値ばらつきは50mVとする。

【0078】

実施の形態1と同様に、プリチャージ回路(図示せず)を用いて、ビット線BL_1とビット線BL_2とを+0.5Vにプリチャージし、その後、ビット線BL_1とビット線BL_2とをフローティング状態とする。また、配線VPS1、配線VNS1の電位は+0.5Vとする。

【0079】

その後、ワード線WL_1の電位をオンに設定して、メモリセルMC_1_1のセルトランジスタをオンとする(図4(B)の時刻T1)。この操作により、メモリセルMC_1_1の容量素子に蓄積されていた電荷がビット線BL_1に放出される。

【0080】

メモリセルMC_1_1の容量素子の容量とビット線BL_1の容量によって、ビット線BL_1の電位が決定される。ここでは、メモリセルMC_1_1の容量素子の電位が0Vであったため、プリチャージ電位より低下して、+0.4Vになったものとする。

【0081】

また、時刻T1に第1選択線SL1の電位をオンに設定して、第1選択トランジスタST1をオンとする。さらに、時刻T1に配線VPS1の電位を+1Vに向けて上昇させ、また、配線VNS1の電位を0Vに向けて下降させる。なお、第1選択線SL1の電位をオンに設定するタイミングは時刻T1の前あるいは後でもよい。また配線VPS1の電位を+1Vに向けて上昇させ、また、配線VNS1の電位を0Vに向けて下降させるタイミングは時刻T1の前あるいは後でもよい。

【0082】

ビット線BL_1の電位が+0.4Vであるので、Pチャネル型トランジスタTPRとNチャネル型トランジスタTNRで構成される第1のインバータは、プリチャージ電位より高い電位を出力する。その電位は第1選択トランジスタST1を経て、ビット線BL_2に伝わり、ビット線BL_2の電位は、プリチャージ電位よりも高くなる。

【0083】

その後、第2選択線SL2の電位をオンに設定して、第2選択トランジスタST2をオンとする(図4(B)の時刻T2)。この結果、第1のインバータと第2のインバータによりフリップフロップ回路が形成される。この際、第1のインバータの入力電位(ビット線BL_1の電位)と第2のインバータの入力電位(ビット線BL_2の電位)の差は十分に大きいので、ノイズの影響を受けることが少なく、第1のインバータと第2のインバータにより形成されるフリップフロップ回路はただちに安定な状態となる。このようにして、データを短時間で増幅することができる。

【0084】

なお、本実施の形態の半導体メモリ装置は、公知のDRAMで使用されるようなセンスアンプを有しないために、より効率的に書き込みをおこなうことができる。通常、DRAMはデータを読み出した後、データの書き換えが必要なメモリセルのあるビット線の電位は、書き換えるべきデータに応じた電位とするが、その際には、センスアンプ(フリップフロップ回路)の状態を反転させる必要があるため、時間と電力を必要とする。

【0085】

本実施の形態の半導体メモリ装置では、第1のインバータと第2のインバータで形成されたフリップフロップ回路の間に第1選択トランジスタST1や第2選択トランジスタST2を有するため、これらをオフとすることでフリップフロップ回路とそこに保持されていた状態を破壊することができる。

【0086】

例えば、上記の例では、少なくとも第2選択トランジスタST2をオフとすると、第2のインバータからビット線BL_1への回路が遮断される(図4(B)の時刻T3)ので、第2のインバータからの電位の供給は途絶える。データを書き換えるには、ビット線BL_1の電位を書き換える電位(この場合は+1V)にすればよいが、フリップフロップ回路の状態を反転させる必要がないので、ビット線BL_1を0Vから+1Vに充電する電荷を注入すれば十分であり、短時間で書き換えができる。

【0087】

なお、このとき、ビット線BL_2の電位をビット線BL_1の電位と逆の位相のものとする場合には、時刻T3において第1選択トランジスタST1もオフとするとよい。

【0088】

一方、この期間では、データを書き換えないビット線と、それらに接続する第2のインバータの出力端子の接続も遮断されるが、これらのビット線の電位は元のデータに応じた電位に保持されている。

【0089】

その後、メモリセルのトランジスタをオフとすることで、データを書き換えるメモリセルの容量素子には書き換えるべきデータに応じた電位が、データを書き換えないメモリセルの容量素子には元のデータに応じた電位が保持される。

【0090】

図3(A)に示す半導体メモリ装置は、第1のインバータと第2のインバータの電源電圧を同時に制御するものであるが、図3(B)のように第1のインバータと第2のインバータの電源電圧を個別に制御する構造としてもよい。すなわち、第1のインバータに電源を供給する配線VPS1と配線VNS1と、第2のインバータに電源を供給する配線VPS2と配線VNS2とを分離してもよい。

【0091】

そして、当初は、配線VPS2と配線VNS2の電位をともに+0.5Vとし、図4(B)の時刻T2あるいは時刻T2の前あるいは時刻T2の後に配線VPS2と配線VNS2の電位を、それぞれ+1V、0Vに変更してもよい。このようにすると、より消費電力を低減できる。

【0092】

(実施の形態3)

本実施の形態では、図5(A)および図5(B)を用いて本発明の一態様の半導体メモリ装置の例について説明する。図5(A)および図5(B)に示す半導体メモリ装置は実施の形態1あるいは実施の形態2と同様に動作させることができる。

【0093】

図5(A)に示す半導体メモリ装置は、ワード線WL、ワード線WLに直交するビット線BL、ワード線WLに平行な第1選択線SL1および第2選択線SL2と、複数のメモリセルMCを有する。ビット線BLは第1選択線SL1あるいは第2選択線SL2のあたりで分断され、いわゆるオープンビット構造となる。

【0094】

また、第1選択トランジスタST1と第2選択トランジスタST2とPチャネル型トランジスタTPL、Pチャネル型トランジスタTPR、Nチャネル型トランジスタTNL、Nチャネル型トランジスタTNRとそれらのソースに電位を供給するための配線VPS1、配線VNS1を有する。

【0095】

Pチャネル型トランジスタTPRとNチャネル型トランジスタTNR、Pチャネル型トランジスタTPLとNチャネル型トランジスタTNLは、それぞれ第1のインバータ、第2のインバータを構成する。第1選択トランジスタST1のソースはビット線BL_2Lに接続し、ドレインはNチャネル型トランジスタTNRのドレインとPチャネル型トランジスタTPRのドレイン(すなわち第1のインバータの出力端子)に接続し、ゲートは第1選択線SL1に接続する。第2選択トランジスタST2のソースはビット線BL_1Rに接続し、ドレインはNチャネル型トランジスタTNLのドレインとPチャネル型トランジスタTPLのドレイン(すなわち第2のインバータの出力端子)に接続し、ゲートは第2選択線SL2に接続する。

【0096】

さらに、センスアンプSA_1/2を有する。センスアンプSA_1/2は、ビット線BL_1Rとビット線BL_2Lの電位差を増幅するのに用いられる。

【0097】

また、図5(B)に示す半導体メモリ装置は、集積度を高めるために、図5(A)に示す半導体メモリ装置からセンスアンプを取り除き、第1のインバータと第2のインバータで電位の増幅をおこなうものである。

【0098】

なお、図5(A)および図5(B)に示す半導体メモリ装置は第1のインバータと第2のインバータの電源電圧が同時に制御されるものであるが、実施の形態1あるいは実施の形態2に示したように、第1のインバータと第2のインバータの電源電圧を個別に制御できるものとしてもよい。

【0099】

(実施の形態4)

本実施の形態では、本発明の一態様の半導体メモリ装置の例について図6(A)乃至図6(D)および図7を用いて説明する。なお、本実施の形態では、同じハッチングの部分は同じ種類のものを示す。

【0100】

図6(A)乃至図6(D)は、実施の形態2で説明した第1のインバータと第2のインバータの配置の例を示す。なお、詳細は公知の半導体集積回路作製技術を参照すればよい。図6(A)乃至図6(D)に示される回路配置では、第1のインバータと第2のインバータは、ビット線6本分の幅に形成される。

【0101】

図6(A)は、単結晶半導体基板上に形成されるN型ウェル、P型ウェルのうち素子分離絶縁物で覆われていない部分の位置を示す。ビット線方向(x方向)にN型ウェルとP型ウェルを交互に形成する。

【0102】

ここで、N型ウェルの中央部のy方向の長さはP型ウェルの中央部のy方向の長さよりも大きくする。これは、インバータに用いられるPチャネル型トランジスタ(N型ウェル上に形成される)のチャネル幅を、Nチャネル型トランジスタ(P型ウェル上に形成される)のチャネル幅よりも大きくするためである。

【0103】

また、P型ウェルのx方向の長さはN型ウェルのx方向の長さよりも大きくする。これは、インバータに用いられるNチャネル型トランジスタのチャネル長を、Pチャネル型トランジスタのチャネル長よりも大きくするためである。

【0104】

また、図6(B)乃至図6(D)には、その上に形成される第1配線、第1コンタクトプラグ(以上、図6(B))、第2配線、第2コンタクトプラグ(以上、図6(C))、第3配線(以上、図6(D))の配置例を示す。

【0105】

なお、メモリセルを薄膜状の半導体で形成する場合には、第2配線の上、あるいは第3配線の上に薄膜状の半導体を形成してもよく、その際には、インバータ等の上に重ねてメモリセルを形成できるので集積度を高めることができる。

【0106】

ここで、第1配線はトランジスタのゲートとなるのであるが、特に、第1のインバータ、第2のインバータに用いられるトランジスタではしきい値のばらつきが小さいことを要求されるので、それらのゲートとなる配線の幅はチャネル面積が大きくなるように、Feature Size(F)よりも大きくするとよい。

【0107】

また、Nチャネル型トランジスタとPチャネル型トランジスタを用いてインバータを構成する際には、それらのオン特性がほぼ対称となるように、移動度を考慮してチャネル長、チャネル幅を設定することが望まれる。好ましくは、インバータを構成するPチャネル型トランジスタのチャネル幅をチャネル長で除した値が、Nチャネル型トランジスタのチャネル幅をチャネル長で除した値の2.5倍以上4倍以下とするとよい。

【0108】

さらに、しきい値ばらつきやビット線との容量比も考慮すると、それらのチャネル面積はほぼ等しいことが好ましい。すなわち、Nチャネル型トランジスタのチャネル面積がPチャネル型トランジスタのチャネル面積の80%以上125%以下となるように設計するとよい。なお、この際、Nチャネル型トランジスタのチャネル面積は10F2以上、好ましくは20F2以上とするとよい。

【0109】

例えば、チャネルが長方形のトランジスタであれば、Nチャネル型トランジスタのチャネル長を5F、チャネル幅を3F、Pチャネル型トランジスタのチャネル長を3F、チャネル幅を5Fとすると、チャネル面積、オン電流ともほぼ等しくなる。また、これらのチャネル面積は通常の15倍であるので、しきい値ばらつきも抑制される。しきい値ばらつきはチャネル面積の平方根に反比例するので、この場合、約4分の1となる。

【0110】

同様に、Nチャネル型トランジスタのチャネル長を7F、チャネル幅を4F、Pチャネル型トランジスタのチャネル長を4F、チャネル幅を7Fとしてもよいし、Nチャネル型トランジスタのチャネル長を12F、チャネル幅を7F、Pチャネル型トランジスタのチャネル長を7F、チャネル幅を12Fとしてもよい。

【0111】

また、レイアウトの都合で、上記のような長方形のチャネルを形成することが困難な場合には、チャネルの形状を多角形その他の形状として、実質的に必要とするオン電流およびチャネル面積が得られるように設計してもよい。

【0112】

本実施の形態の半導体メモリ装置では、インバータを構成するPチャネル型トランジスタのチャネル長を3F、チャネル幅を5F、Nチャネル型トランジスタのチャネル長を5F、チャネル幅を3Fとする。その結果、チャネル長を1F、チャネル幅を1Fとするトランジスタに比べて、しきい値のばらつきが約4分の1に低下する。

【0113】

なお、第1配線のうち、y方向に延在するものは、第1選択線あるいは第2選択線となるものであり、第1選択トランジスタや第2選択トランジスタにはNチャネル型トランジスタを用い、チャネル長を1F、チャネル幅を3Fとする。

【0114】

したがって、第1選択トランジスタ(あるいは第2選択トランジスタ)と第1のインバータ(あるいは第2のインバータ)の直列回路では、主たる抵抗は第1のインバータ(あるいは第2のインバータ)であり、第1選択トランジスタ(あるいは第2選択トランジスタ)の抵抗は十分に小さいので、動作速度にはほとんど関係がない。

【0115】

また、第2配線のうち、y方向に延在するものは、インバータへ電源を供給するための配線である。さらに、第3配線はビット線であり、例えば、図6(D)に示されるように、第1選択線あるいは第2選択線に相当する第1配線が設けられている部分付近で、ビット線BL_1Lとビット線BL_1Rに分離する構成となっている。

【0116】

図7には、図6(A)乃至図6(D)に示したレイアウトを用いて形成される部分およびその周辺の回路図を示す。図に示すように、第1のインバータと第2のインバータが、ビット線6本分の幅に形成されているため、ビット線6本ごとに同じパターンが現れる。

【0117】

本実施の形態の半導体メモリ装置では、第1選択線SL1の電位をオンに設定すると、ビット線BL_nR(nは整数)の電位を反転した電位がビット線BL_nLに出力される。また、第2選択線SL2の電位をオンに設定すると、ビット線BL_nLの電位を反転した電位がビット線BL_nRに出力される。

【0118】

なお、本実施の形態の半導体メモリ装置では、図6(A)乃至図6(D)に示したレイアウトからわかるように、第1のインバータの電源電圧と第2のインバータの電源電圧とを個別に操作できる。

【符号の説明】

【0119】

BL ビット線

MC メモリセル

SA センスアンプ

SL1 第1選択線

SL2 第2選択線

ST1 第1選択トランジスタ

ST2 第2選択トランジスタ

TND Nチャネル型トランジスタ

TNL Nチャネル型トランジスタ

TNR Nチャネル型トランジスタ

TNU Nチャネル型トランジスタ

TPD Pチャネル型トランジスタ

TPL Pチャネル型トランジスタ

TPR Pチャネル型トランジスタ

TPU Pチャネル型トランジスタ

T1 時刻

T2 時刻

T3 時刻

VNS 配線

VNS1 配線

VNS2 配線

VPS 配線

VPS1 配線

VPS2 配線

WL ワード線

【技術分野】

【0001】

本発明は、半導体を用いたメモリ装置に関する。

【背景技術】

【0002】

最初に、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、一方をドレインと呼ぶとき他方をソースとする。すなわち、電位の高低によって、それらを区別しない。したがって、本明細書において、ソースとされている部分をドレインと読み替えることもできる。

【0003】

また、本明細書において、接続、とは、一時的であっても、実効的な直流電流が、供給可能な状態になる構造を有していることをいう。従って、接続している状態とは、直接、接続している状態のみを必ずしも指すわけではなく、直流電流が、供給可能であるように、配線、抵抗などの回路素子を介して間接的に接続している状態もその範疇に含む。なお、実際に回路に直流電流が供給されるように設計されているかどうかは問わない。

【0004】

例えば、2つのノード間にスイッチング素子が設けられている場合には、条件付ながら(すなわち、スイッチがオンであるときだけではあるが)、直流電流が供給可能となるので、接続する、という。一方、2つのノード間に、容量素子のみが設けられている場合には、容量素子を介しては、実効的な直流電流を供給することができないので、このノード間は接続されていない、という。

【0005】

同様に2つのノード間にダイオードのみが設けられている場合も、いずれかのノードの電位が高ければ直流電流を供給できるので、接続する,という。この際には、回路設計上、電流が流れないような電位が2つのノードに与えられている場合(この場合には、現実の回路において2つのノードにダイオードを介して電流が流れることがない)であっても、本明細書では、接続している、という。

【0006】

例えば、ノードAがトランジスタのソースに接続し、ノードBがドレインに接続する場合には、ノードAとノードBの間には、ゲートの電位によっては直流電流を流すことができるので、ノードAとノードBは接続している、という。

【0007】

一方、ノードAがトランジスタのソースに接続し、ノードCがゲートに接続する場合には、トランジスタのソース、ドレイン、ゲートの電位の如何にかかわらず、ノードAとノードCの間に実効的な直流電流を流すことができないので、ノードAとノードCは接続していない、という。

【0008】

上記において、実効的な直流電流とは、リーク電流等の意図しない電流を除いた電流という意味である。なお、実効的な直流電流の値は、その大きさ(絶対値)で定義されるものではなく、回路に応じて異なることがある。すなわち、ある回路では1pAという小電流であっても実効的な電流となりえるし、他の回路では、それより大きな1μAという電流であっても実効的な電流とみなされないこともある。

【0009】

なお、言うまでもないことであるが、入力と出力を有する1つの回路(例えば、インバータ)において、入力と出力が回路内で接続している必要はない。インバータを例に取れば、入力と出力はインバータ内部で接続していない。

【0010】

さらに、本明細書においては、「接続する」と表現される場合であっても、現実の回路においては、物理的な接続部分が明確でなく、配線が延在している場合だけのこともある。例えば、絶縁ゲート型電界効果トランジスタ(以下、単にトランジスタ、という)の回路では、一本の配線が複数のトランジスタのゲートを兼ねている場合もある。その場合、回路図では、一本の配線からゲートに何本もの分岐が生じるように書かれることもある。本明細書では、そのような場合でも、「配線がゲートに接続する」という表現を用いることがある。

【0011】

なお、本明細書では、マトリクスにおいて特定の行や列、位置を扱う場合には、符号に座標を示す記号をつけて、例えば、「メモリセルMC_1_1」、「ビット線BL_2」というように表記する。また、一つの素子が複数の行や列の機能を有するときには、「センスアンプSA_1/2」というように表記することもある。

【0012】

しかし、特に、行や列、位置を特定しない場合や集合的に扱う場合、あるいはどの位置にあるか明らかである場合には、「メモリセルMC」、「ビット線BL」」、あるいは、単に「メモリセル」、「ビット線」というように表記することもある。

【0013】

1つのトランジスタと1つの容量素子を用いてメモリセルを形成するDRAMは、高集積化でき、原理的に無制限に書き込みでき、さらに、書き込み読み出しの速度も比較的高速でおこなえるため、多くの電子機器で使用されている。DRAMは、各メモリセルの容量素子に電荷を蓄積することにより、データを記憶し、この電荷を放出することによりデータを読み出す。

【0014】

従来は、トランジスタとしてシリコンを用いていたために、1秒間に数10回のリフレッシュが必要であったが、よりバンドギャップの大きな酸化物半導体を用いたトランジスタでは、実質的に永久にデータを保持できることが示された(特許文献1参照)。また、極端に薄いシリコン膜を用いることによっても、従来のトランジスタよりオフ電流を3桁以上も低減できることが示された(特許文献2参照)。

【0015】

図2(A)および図2(B)に従来のDRAMの読み出しに関する回路と読み出し方法を示す。図2(A)に示すDRAMは、いわゆるフォールデッド方式のDRAMの回路であり、一対のビット線BL_1とビット線BL_2と、ワード線WL_1、ワード線WL_2、ワード線WL_3、ワード線WL_4等とそれらの交点にメモリセルMC_1_1、メモリセルMC_2_2、メモリセルMC_3_1、メモリセルMC_4_2等を有する。

【0016】

また、ビット線BL_1とビット線BL_2の一端にはセンスアンプSA_1/2が設けられている。通常、センスアンプはフリップフロップ型の回路を用いる。

【0017】

図2(B)にこれらの回路を駆動するタイミングチャートを示す。ここでは、”1”のデータはメモリセルMCの容量素子が+1Vに、”0”のデータはメモリセルMCの容量素子が0Vに充電されているものとする。

【0018】

メモリセルMC_1_1のデータを読み出すには以下のようにおこなう。まず、プリチャージ回路(図示せず)を用いて、ビット線BL_1とビット線BL_2とを+0.5Vにプリチャージする。その後、ビット線BL_1とビット線BL_2とをフローティング状態とする。また、フリップフロップ回路型のセンスアンプSA_1/2の、Pチャネル型トランジスタTPUおよびPチャネル型トランジスタTPDのソースに電位を供給するための配線VPSの電位、Nチャネル型トランジスタTNUおよびNチャネル型トランジスタTNDのソースに電位を供給するための配線VNSの電位は+0.5Vとする。

【0019】

その後、ワード線WL_1の電位を適切な値にして、メモリセルMC_1_1のセルトランジスタをオンとする(図2(B)の時刻T1)。なお、このように配線の電位を変化させることで、それに接続するトランジスタをオンとすることを、配線の電位をオンに設定する、という。この操作により、メモリセルMC_1_1の容量素子に蓄積されていた電荷がビット線BL_1に放出される。

【0020】

メモリセルMC_1_1の容量素子の容量とビット線BL_1の容量によって、ビット線BL_1の電位が決定される。ここでは、メモリセルの容量素子の電位が0Vであったため、プリチャージ電位より低下して、+0.4Vになったものとする。

【0021】

一方、ワード線WL_1の電位をオンに設定しても、ビット線BL_2に接続するメモリセルはないので、ビット線BL_2の電位は変動せず、+0.5Vのままである。すなわち、ビット線BL_1の電位の方が、ビット線BL_2の電位より、0.1V低い。

【0022】

その後、センスアンプSA_1/2の配線VPSの電位を+1Vに向けてある速度で上昇させ、また、配線VNSの電位を0Vに向けて同様な速度で下降させる(図2(B)の時刻T2)。この操作により、ある段階で、Pチャネル型トランジスタTPDとNチャネル型トランジスタTNUがオンとなる。

【0023】

その結果、相対的に電位の低いビット線BL_1の電位はさらに低下し、相対的に電位の高いビット線BL_2の電位はさらに高くなり、最終的には、ビット線BL_1の電位は0Vとなり、ビット線BL_2の電位は+1Vとなる。

【0024】

この過程(増幅過程)での配線VPSの電位と配線VNSの電位の変化する速度は、増幅初期においては、十分に小さいことが望ましい。上記のように、増幅初期電位差が0.1Vというように小さな場合には、配線VPSの電位と配線VNSの電位を急激に変動させると、増幅に失敗するためである。このため、増幅に時間を要する。

【0025】

一方で、増幅に時間がかかると、特に増幅初期段階では、外部のノイズにより読み出しに失敗する確率が高まる。

【0026】

また、このように0.1Vという微弱な電位差を増幅するため、センスアンプSA_1/2に用いるトランジスタのしきい値のばらつきは小さいことが求められる。例えば、Nチャネル型トランジスタTNUのしきい値が+0.35V、Pチャネル型トランジスタTPUのしきい値が−0.45V、Nチャネル型トランジスタTNDのしきい値が+0.45V、およびPチャネル型トランジスタTPDのしきい値が−0.35Vであるとすると、上記の増幅過程において、Pチャネル型トランジスタTPUおよびPチャネル型トランジスタTPDがともにオンとなり、データの読み出しに失敗することがある。

【0027】

一般に、センスアンプに用いるトランジスタのしきい値のばらつきは、ビット線間の増幅初期電位差の半分未満、好ましくは30%未満であることが要求される。上記の場合、トランジスタのしきい値のばらつきは50mV、ビット線間の増幅初期電位差は0.1Vであるため、増幅の際にエラーが発生しやすい。

【0028】

一般に、トランジスタのしきい値のばらつきは、ロット間ばらつき(基板間ばらつき)とチップ間ばらつき(基板内ばらつき)と隣接トランジスタばらつき、の3つに大きく分類される。

【0029】

ロット間ばらつきは、プロセス条件、膜厚や線幅のロット間の違いに依存するものであり、また、チップ間ばらつきは、ドーズ量、膜厚や線幅の基板面内のばらつきによるものである。いずれも、ばらつきは巨視的なものであり、これらの要因によるしきい値のばらつきは基板バイアス等により補正できる。

【0030】

これに対し、隣接トランジスタばらつきは、主として、ドーパント濃度の統計的ゆらぎ(非特許文献1参照)によるものであり、トランジスタが微細化するにつれ増大する。すなわち、DRAMの高集積化のためにトランジスタが微細化するとセンスアンプの動作が不安定となる。

【0031】

また、酸化物半導体のようにシリコンよりも移動度が1桁以上小さい半導体を用いる場合には、データのアクセスを高速でおこなうために容量素子の容量を通常のものよりも1桁以上小さくすることが必要となる。もし、1つのビット線に接続するメモリセルを従来と同等とするのであれば、読み出しの際のビット線の電位変動はより小さくなり、エラーが生じやすくなる。

【0032】

非特許文献2によれば、ビット線に接続するメモリセルが256個であれば、回路線幅40nmでは、ビット線の容量は35fFである。もし、容量素子の容量を3fFとし、1つのビット線に256個のメモリセルを接続するのであれば、ビット線の電位の変動は40mV程度であるため、そのような微細な電位変動をエラーなくかつ短時間で増幅する技術が求められる。

【先行技術文献】

【特許文献】

【0033】

【特許文献1】米国特許出願公開第2011/0156027号明細書

【特許文献2】米国特許第7772053号明細書

【非特許文献】

【0034】

【非特許文献1】K.Takeuchi et al., ”Channel Engineering for the Reduction of Random−Dopant−Placement−Induced Threshold Voltage Fluctuation”, pp. 841−844, TECHNICAL DIGEST OF INTERNATIONAL ELECTRON DEVICES MEETING, 1997.

【非特許文献2】Mueller et al.,”Challenges for the DRAM Cell Scaling to 40nm”, TECHNICAL DIGEST OF INTERNATIONAL ELECTRON DEVICES MEETING, pp.347−350, 2005.

【発明の概要】

【発明が解決しようとする課題】

【0035】

本発明の一態様はこのような問題点を解決することを課題とするものである。本発明の一態様はよりビット線の電位の変動が小さい場合でも、誤動作しにくい半導体メモリ装置を提供することを課題とする。また、本発明の一態様はトランジスタのしきい値のばらつきがより大きな場合でも、誤動作しにくい半導体メモリ装置を提供することを課題とする。また、本発明の一態様はより回路が微細化した場合でも誤動作しにくい半導体メモリ装置を提供することを課題とする。

【0036】

また、本発明の一態様は、容量素子の容量を従来のDRAMに用いられている値以下、具体的には10fF以下、好ましくは1fF以下としても十分に機能するメモリ装置を提供することを課題とする。

【0037】

また、本発明の一態様は、新規な構造のメモリ装置あるいはその駆動方法を提供することを課題とする。特に消費電力を低減できるメモリ装置あるいはメモリ装置の駆動方法を提供することを課題とする。

【課題を解決するための手段】

【0038】

本発明の一態様は、第1のビット線と第2のビット線と、これらの間にインバータとスイッチと、第1のビット線および第2のビット線のいずれかに接続するメモリセルとを有し、また、これらインバータとスイッチが直列に接続されている半導体メモリ装置である。

【0039】

また、本発明の一態様は、上記の半導体メモリ装置において、スイッチをオンとする過程と、その後に、第1のビット線と第2のビット線の電位差を増幅する過程と、を有する半導体メモリ装置の駆動方法である。

【0040】

また、本発明の一態様は、第1のビット線と第2のビット線と、これらの間に第1のインバータと第1のスイッチと第2のインバータと第2のスイッチと、第1のビット線および第2のビット線のいずれかに接続するメモリセルとを有し、第1のインバータと第1のスイッチおよび第2のインバータと第2のスイッチは、それぞれ接続されており、第1のビット線と第1のインバータ、第2のビット線と第1のスイッチ、第1のビット線と第2のスイッチ、第2のビット線と第2のインバータが、それぞれ接続されている半導体メモリ装置である。

【0041】

また、本発明の一態様は、上記の半導体メモリ装置において、第1のスイッチをオンとする過程と、その後に、第2のスイッチをオンとすることにより、第1のインバータ、第1のスイッチ、第2のインバータと第2のスイッチよりなるループを構成する半導体メモリ装置の駆動方法である。

【0042】

インバータ(あるいは第1のインバータ、第2のインバータ)としては、さまざまな種類のものを用いることができる。例えば、相補型インバータ、抵抗負荷型インバータ、クロックドインバータ等あるいはそれらの組み合わせを用いることができる。

【0043】

上記において、メモリセルのトランジスタはインバータのトランジスタとは異なる層に設けられていてもよいが、インバータのトランジスタは単結晶半導体を用いるとよい。インバータではトランジスタのしきい値のばらつきを十分に抑制することが必要であるので、そのチャネル面積をメモリセルのトランジスタの4倍以上、好ましくは16倍以上とするとよい。

【0044】

また、インバータの占有する部分のワード線方向の長さは、ビット線の幅の3倍以上、好ましくは5倍以上とするとよい。同様にインバータの占有する部分のビット線方向の長さは、ワード線の幅の3倍以上、好ましくは5倍以上とするとよい。

【0045】

このようにインバータは大きな面積を占有するが、インバータに用いるトランジスタのチャネル面積を十分に大きくすることにより、不純物濃度の統計的ゆらぎに起因するトランジスタのしきい値のばらつきを低減させることができる。また、メモリセルを薄膜状の半導体で形成する場合には、インバータ等の上に重ねてメモリセルを形成できるので集積度を高めることができる。

【0046】

また、上記において、スイッチ(あるいは第1のスイッチ、第2のスイッチ)は、1以上のトランジスタを用いて構成できる。最も簡単には1つのNチャネル型トランジスタあるいはPチャネル型トランジスタを用いて構成できる。また、導電型の異なる2つ以上のトランジスタを並列に接続した、トランスミッションゲートでもよい。

【発明の効果】

【0047】

上記の構成のいずれかを採用することにより、前記課題の少なくとも一を解決できる。本発明の一態様では、スイッチ(あるいは第1のスイッチ)をオンとし、インバータ(あるいは第1のインバータ)の電位をオンに設定することで、第1のビット線の電位に応じて、第2のビット線の電位は、第1のビット線の電位と逆位相の電位に変化する。すなわち、第1のビット線の電位が、インバータのしきい値よりも高ければ、第2のビット線の電位はインバータのしきい値よりも低くなり、第1のビット線の電位が、インバータのしきい値よりも低ければ、第2のビット線の電位はインバータのしきい値よりも高くなる。

【0048】

例えば、インバータを構成するPチャネル型トランジスタのしきい値が−0.35Vから−0.45V、Nチャネル型トランジスタのしきい値が+0.35Vから+0.45Vの範囲にあり、Pチャネル型トランジスタのソースの電位を+1V、Nチャネル型トランジスタのソースの電位を0Vとすると、インバータの入力の電位(すなわち、第1のビット線の電位)が+0.4Vであれば、インバータに信号を入力してから十分に時間が経過した状態では、インバータの出力の電位(すなわち、第2のビット線の電位)は、+0.75V以上とできる。

【0049】

読み出し過程のような短い期間では、インバータを構成するトランジスタの抵抗や第2のビット線の抵抗および容量によって、第2のビット線の電位は、より低い電位となるが、それでも、必要な期間に第2のビット線の電位を+0.6V以上とできる。

【0050】

このため、第1のビット線の第2のビット線の電位差は0.2V以上となるので、インバータと同じしきい値ばらつきを有するトランジスタよりなるセンスアンプを用いてもエラーが発生することは極力抑制される。

【0051】

また、増幅開始時点での第1のビット線と第2のビット線の電位差をより大きくできることにより、第1のビット線と第2のビット線に接続するセンスアンプのNチャネル型トランジスタのソースとPチャネル型トランジスタのソースの電位差を、急速に拡大させることもできる。そのため、読み出しに要する時間を短縮できる。

【0052】

さらに、増幅開始時点での第1のビット線と第2のビット線の電位差がより大きくなること、あるいは、増幅に要する期間を短縮することにより、増幅過程におけるノイズの影響を受けにくくなる。

【0053】

特にオープンビット方式のDRAMでは、読み出しに使うビット線と参照電位に用いるビット線が離れた位置にあるため、フォールデッド方式に比べてノイズの影響による読み出しエラーが大きいことが問題であるが、本発明の一態様では、ノイズの影響が相対的に小さくなることにより、オープンビット方式のDRAMで効果が顕著となる。

【0054】

ここで注意しておきたいことは、上記のようなしきい値のばらつきを有するトランジスタを用いて作製したフリップフロップ型センスアンプでは、0.1Vの電位差を増幅するとエラーが発生しやすくなるのに、同じばらつきのトランジスタを用いて作製したインバータでは、0.1Vの電位差を反転・増幅できるということである。本発明の一態様はこの特徴を有効に利用して効果を得ることができる。

【図面の簡単な説明】

【0055】

【図1】本発明の半導体メモリ装置の回路の例を示す図である。

【図2】従来の半導体メモリ装置の回路の例と駆動方法を示す図である。

【図3】本発明の半導体メモリ装置の回路の例を説明する図である。

【図4】本発明の半導体メモリ装置の駆動方法の例を説明する図である。

【図5】本発明の半導体メモリ装置の回路の例を説明する図である。

【図6】本発明の半導体メモリ装置のレイアウト例を示す図である。

【図7】本発明の半導体メモリ装置の回路の例を説明する図である。

【発明を実施するための形態】

【0056】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0057】

なお、電位として、以下に具体的な数値を挙げるが、それは、本発明の技術思想の理解を助けることが目的である。言うまでもなく、それらの値はトランジスタや容量素子のさまざまな特性によって、あるいは実施者の都合によって変更される。

【0058】

また、以下の実施の形態に示される半導体メモリ装置は、以下の方法以外の方法によっても、データを書き込み、あるいは読み出すことができる。

【0059】

(実施の形態1)

本実施の形態では、図1(A)、図1(B)、図4(A)を用いて本発明の一態様の半導体メモリ装置およびその動作の例について説明する。

【0060】

図1(A)に示す半導体メモリ装置は、ワード線WL、ワード線WLに直交するビット線BL、ワード線WLに平行な第1選択線SL1および第2選択線SL2と、複数のメモリセルMCを有する。また、第1選択トランジスタST1と第2選択トランジスタST2とPチャネル型トランジスタTPL、Pチャネル型トランジスタTPR、Nチャネル型トランジスタTNL、Nチャネル型トランジスタTNRとそれらのソースに電位を供給するための配線VPS1、配線VNS1を有する。

【0061】

Pチャネル型トランジスタTPRとNチャネル型トランジスタTNR、Pチャネル型トランジスタTPLとNチャネル型トランジスタTNLは、それぞれ第1のインバータ、第2のインバータを構成する。第1選択トランジスタST1のソースはビット線BL_2に接続し、ドレインはNチャネル型トランジスタTNRのドレインとPチャネル型トランジスタTPRのドレイン(すなわち第1のインバータの出力端子)に接続し、ゲートは第1選択線SL1に接続する。第2選択トランジスタST2のソースはビット線BL_1に接続し、ドレインはNチャネル型トランジスタTNLのドレインとPチャネル型トランジスタTPLのドレイン(すなわち第2のインバータの出力端子)に接続し、ゲートは第2選択線SL2に接続する。

【0062】

さらに、センスアンプSA_1/2と、それを構成するトランジスタのソースに電位を供給するための配線VPS、配線VNSを有する。センスアンプSA_1/2は従来のDRAMと同様に、ビット線BL_1とビット線BL_2の電位差を増幅するのに用いられる。

【0063】

このような半導体メモリ装置でデータを読み出す例について説明する。ここでも、メモリセルMC_1_1のデータを読み出すとする。本実施の形態のNチャネル型トランジスタのしきい値の平均値は+0.4Vで、しきい値のばらつきは50mV、Pチャネル型トランジスタのしきい値の平均値は−0.4Vでしきい値のばらつきは50mVとする。

【0064】

従来のDRAMの場合と同様に、プリチャージ回路(図示せず)を用いて、ビット線BL_1とビット線BL_2とを+0.5Vにプリチャージし、その後、ビット線BL_1とビット線BL_2とをフローティング状態とする。また、センスアンプSA_1/2の配線VPSの電位、配線VNSの電位は共に+0.5Vとする。一方で、配線VPS1の電位は+1V、配線VNS1の電位は0Vとする。

【0065】

その後、ワード線WL_1の電位をオンに設定して、メモリセルMC_1_1のセルトランジスタをオンとする(図4(A)の時刻T1)。この操作により、メモリセルMC_1_1の容量素子に蓄積されていた電荷がビット線BL_1に放出される。

【0066】

メモリセルMC_1_1の容量素子の容量とビット線BL_1の容量によって、ビット線BL_1の電位が決定される。ここでは、メモリセルMC_1_1の容量素子の電位が0Vであったため、プリチャージ電位より低下して、+0.4Vになったものとする。

【0067】

また、時刻T1に第1選択線SL1の電位をオンに設定して、第1選択トランジスタST1をオンとする。なお、第1選択線SL1の電位をオンに設定するタイミングは時刻T1の前あるいは後でもよい。ビット線BL_1の電位が+0.4Vであるので、トランジスタのしきい値ばらつきを考慮しても、Pチャネル型トランジスタTPRとNチャネル型トランジスタTNRで構成される第1のインバータは、プリチャージ電位(+0.5V)より高い電位を出力する。その電位は第1選択トランジスタST1を経て、ビット線BL_2に伝わり、ビット線BL_2の電位は、プリチャージ電位よりも高くなる。

【0068】

その後、配線VPSの電位を+1Vに向けて上昇させ、また、配線VNSの電位を0Vに向けて下降させ、センスアンプSA_1/2をアクティブとする(図4(A)の時刻T2)。このようにして、データを増幅することができる。従来のDRAMではこの操作に時間がかかっていたが、本実施の形態の半導体メモリ装置では、ビット線BL_1の電位とビット線BL_2の電位の差が十分に大きい状態で増幅が開始されるので、電位の変動する速度を大きくしても、増幅エラーとなることが少ない。そのため、増幅に要する時間が短縮できる。また、このように増幅に要する時間が短いので、この期間に外部のノイズの影響を受けることが少なく、読み出しに失敗する確率が低下する。

【0069】

図1(A)に示す半導体メモリ装置は、第1のインバータと第2のインバータの電源電圧を同時に制御するものであるが、図1(B)のように第1のインバータと第2のインバータの電源電圧を個別に制御する構造としてもよい。すなわち、第1のインバータに電源を供給する配線VPS1と配線VNS1と、第2のインバータに電源を供給する配線VPS2と配線VNS2とを分離してもよい。

【0070】

上記の例では、第2のインバータはデータの読み出しには使用されないが、配線VPS1と配線VNS1の間に電位差があると、Pチャネル型トランジスタTPLとNチャネル型トランジスタTNLの間に貫通電流が流れる。貫通電流は第2のインバータの電源電圧を0とする(例えば、配線VPS2と配線VNS2の電位を共に+0.5Vとして、電位差を0とする)ことでなくすことができる。このようにすると、消費電力を低減できる。

【0071】

また、上記の例では、第1のインバータおよび第2のインバータは最初から電源が入った状態であるが、消費電力を低減する観点からは、時刻T1あるいは時刻T1の前あるいは時刻T1の後に電源を入れ、時刻T2あるいは時刻T2の前あるいは時刻T2の後に電源を切ることも好ましい。特に、本実施の形態のインバータは、入力電位がプリチャージ電位付近であると、最も貫通電流が多く流れるため、第1のインバータおよび第2のインバータの電源をこまめにオンオフすることは消費電力を低減する上で有効である。

【0072】

より消費電力を低減するためには、第1のインバータおよび第2のインバータの電源電圧が個別に制御できるものであれば、第2のインバータの電源電圧を0とし、第1のインバータは時刻T1あるいは時刻T1の前あるいは時刻T1の後に電源を入れ、時刻T2あるいは時刻T2の前あるいは時刻T2の後に電源を切ることが好ましい。

【0073】

(実施の形態2)

本実施の形態では、図3(A)、図3(B)、図4(B)を用いて本発明の一態様の半導体メモリ装置およびその動作の例について説明する。

【0074】

図3(A)に示す半導体メモリ装置は、ワード線WL、ワード線WLに直交するビット線BL、ワード線WLに平行な第1選択線SL1および第2選択線SL2と、複数のメモリセルMCを有する。また、第1選択トランジスタST1と第2選択トランジスタST2とPチャネル型トランジスタTPL、Pチャネル型トランジスタTPR、Nチャネル型トランジスタTNL、Nチャネル型トランジスタTNRとそれらのソースに電位を供給するための配線VPS1、配線VNS1を有する。

【0075】

Pチャネル型トランジスタTPRとNチャネル型トランジスタTNR、Pチャネル型トランジスタTPLとNチャネル型トランジスタTNLは、それぞれ第1のインバータ、第2のインバータを構成する。第1選択トランジスタST1のソースはビット線BL_2に接続し、ドレインはNチャネル型トランジスタTNRのドレインとPチャネル型トランジスタTPRのドレイン(すなわち第1のインバータの出力端子)に接続し、ゲートは第1選択線SL1に接続する。第2選択トランジスタST2のソースはビット線BL_1に接続し、ドレインはNチャネル型トランジスタTNLのドレインとPチャネル型トランジスタTPLのドレイン(すなわち第2のインバータの出力端子)に接続し、ゲートは第2選択線SL2に接続する。

【0076】

本実施の形態の半導体メモリ装置はセンスアンプを用いず、上記の第1のインバータと第2のインバータの組み合わせでビット線BL_1とビット線BL_2の電位差を増幅するものである。そのため、図1(A)あるいは図1(B)の半導体メモリ装置より集積化できる。

【0077】

このような半導体メモリ装置でデータを読み出す例について説明する。ここでも、メモリセルMC_1_1のデータを読み出すとする。本実施の形態のNチャネル型トランジスタのしきい値の平均値は+0.4Vで、しきい値ばらつきは50mV、Pチャネル型トランジスタのしきい値の平均値は−0.4Vでしきい値ばらつきは50mVとする。

【0078】

実施の形態1と同様に、プリチャージ回路(図示せず)を用いて、ビット線BL_1とビット線BL_2とを+0.5Vにプリチャージし、その後、ビット線BL_1とビット線BL_2とをフローティング状態とする。また、配線VPS1、配線VNS1の電位は+0.5Vとする。

【0079】

その後、ワード線WL_1の電位をオンに設定して、メモリセルMC_1_1のセルトランジスタをオンとする(図4(B)の時刻T1)。この操作により、メモリセルMC_1_1の容量素子に蓄積されていた電荷がビット線BL_1に放出される。

【0080】

メモリセルMC_1_1の容量素子の容量とビット線BL_1の容量によって、ビット線BL_1の電位が決定される。ここでは、メモリセルMC_1_1の容量素子の電位が0Vであったため、プリチャージ電位より低下して、+0.4Vになったものとする。

【0081】

また、時刻T1に第1選択線SL1の電位をオンに設定して、第1選択トランジスタST1をオンとする。さらに、時刻T1に配線VPS1の電位を+1Vに向けて上昇させ、また、配線VNS1の電位を0Vに向けて下降させる。なお、第1選択線SL1の電位をオンに設定するタイミングは時刻T1の前あるいは後でもよい。また配線VPS1の電位を+1Vに向けて上昇させ、また、配線VNS1の電位を0Vに向けて下降させるタイミングは時刻T1の前あるいは後でもよい。

【0082】

ビット線BL_1の電位が+0.4Vであるので、Pチャネル型トランジスタTPRとNチャネル型トランジスタTNRで構成される第1のインバータは、プリチャージ電位より高い電位を出力する。その電位は第1選択トランジスタST1を経て、ビット線BL_2に伝わり、ビット線BL_2の電位は、プリチャージ電位よりも高くなる。

【0083】

その後、第2選択線SL2の電位をオンに設定して、第2選択トランジスタST2をオンとする(図4(B)の時刻T2)。この結果、第1のインバータと第2のインバータによりフリップフロップ回路が形成される。この際、第1のインバータの入力電位(ビット線BL_1の電位)と第2のインバータの入力電位(ビット線BL_2の電位)の差は十分に大きいので、ノイズの影響を受けることが少なく、第1のインバータと第2のインバータにより形成されるフリップフロップ回路はただちに安定な状態となる。このようにして、データを短時間で増幅することができる。

【0084】

なお、本実施の形態の半導体メモリ装置は、公知のDRAMで使用されるようなセンスアンプを有しないために、より効率的に書き込みをおこなうことができる。通常、DRAMはデータを読み出した後、データの書き換えが必要なメモリセルのあるビット線の電位は、書き換えるべきデータに応じた電位とするが、その際には、センスアンプ(フリップフロップ回路)の状態を反転させる必要があるため、時間と電力を必要とする。

【0085】

本実施の形態の半導体メモリ装置では、第1のインバータと第2のインバータで形成されたフリップフロップ回路の間に第1選択トランジスタST1や第2選択トランジスタST2を有するため、これらをオフとすることでフリップフロップ回路とそこに保持されていた状態を破壊することができる。

【0086】

例えば、上記の例では、少なくとも第2選択トランジスタST2をオフとすると、第2のインバータからビット線BL_1への回路が遮断される(図4(B)の時刻T3)ので、第2のインバータからの電位の供給は途絶える。データを書き換えるには、ビット線BL_1の電位を書き換える電位(この場合は+1V)にすればよいが、フリップフロップ回路の状態を反転させる必要がないので、ビット線BL_1を0Vから+1Vに充電する電荷を注入すれば十分であり、短時間で書き換えができる。

【0087】

なお、このとき、ビット線BL_2の電位をビット線BL_1の電位と逆の位相のものとする場合には、時刻T3において第1選択トランジスタST1もオフとするとよい。

【0088】

一方、この期間では、データを書き換えないビット線と、それらに接続する第2のインバータの出力端子の接続も遮断されるが、これらのビット線の電位は元のデータに応じた電位に保持されている。

【0089】

その後、メモリセルのトランジスタをオフとすることで、データを書き換えるメモリセルの容量素子には書き換えるべきデータに応じた電位が、データを書き換えないメモリセルの容量素子には元のデータに応じた電位が保持される。

【0090】

図3(A)に示す半導体メモリ装置は、第1のインバータと第2のインバータの電源電圧を同時に制御するものであるが、図3(B)のように第1のインバータと第2のインバータの電源電圧を個別に制御する構造としてもよい。すなわち、第1のインバータに電源を供給する配線VPS1と配線VNS1と、第2のインバータに電源を供給する配線VPS2と配線VNS2とを分離してもよい。

【0091】

そして、当初は、配線VPS2と配線VNS2の電位をともに+0.5Vとし、図4(B)の時刻T2あるいは時刻T2の前あるいは時刻T2の後に配線VPS2と配線VNS2の電位を、それぞれ+1V、0Vに変更してもよい。このようにすると、より消費電力を低減できる。

【0092】

(実施の形態3)

本実施の形態では、図5(A)および図5(B)を用いて本発明の一態様の半導体メモリ装置の例について説明する。図5(A)および図5(B)に示す半導体メモリ装置は実施の形態1あるいは実施の形態2と同様に動作させることができる。

【0093】

図5(A)に示す半導体メモリ装置は、ワード線WL、ワード線WLに直交するビット線BL、ワード線WLに平行な第1選択線SL1および第2選択線SL2と、複数のメモリセルMCを有する。ビット線BLは第1選択線SL1あるいは第2選択線SL2のあたりで分断され、いわゆるオープンビット構造となる。

【0094】

また、第1選択トランジスタST1と第2選択トランジスタST2とPチャネル型トランジスタTPL、Pチャネル型トランジスタTPR、Nチャネル型トランジスタTNL、Nチャネル型トランジスタTNRとそれらのソースに電位を供給するための配線VPS1、配線VNS1を有する。

【0095】

Pチャネル型トランジスタTPRとNチャネル型トランジスタTNR、Pチャネル型トランジスタTPLとNチャネル型トランジスタTNLは、それぞれ第1のインバータ、第2のインバータを構成する。第1選択トランジスタST1のソースはビット線BL_2Lに接続し、ドレインはNチャネル型トランジスタTNRのドレインとPチャネル型トランジスタTPRのドレイン(すなわち第1のインバータの出力端子)に接続し、ゲートは第1選択線SL1に接続する。第2選択トランジスタST2のソースはビット線BL_1Rに接続し、ドレインはNチャネル型トランジスタTNLのドレインとPチャネル型トランジスタTPLのドレイン(すなわち第2のインバータの出力端子)に接続し、ゲートは第2選択線SL2に接続する。

【0096】

さらに、センスアンプSA_1/2を有する。センスアンプSA_1/2は、ビット線BL_1Rとビット線BL_2Lの電位差を増幅するのに用いられる。

【0097】

また、図5(B)に示す半導体メモリ装置は、集積度を高めるために、図5(A)に示す半導体メモリ装置からセンスアンプを取り除き、第1のインバータと第2のインバータで電位の増幅をおこなうものである。

【0098】

なお、図5(A)および図5(B)に示す半導体メモリ装置は第1のインバータと第2のインバータの電源電圧が同時に制御されるものであるが、実施の形態1あるいは実施の形態2に示したように、第1のインバータと第2のインバータの電源電圧を個別に制御できるものとしてもよい。

【0099】

(実施の形態4)

本実施の形態では、本発明の一態様の半導体メモリ装置の例について図6(A)乃至図6(D)および図7を用いて説明する。なお、本実施の形態では、同じハッチングの部分は同じ種類のものを示す。

【0100】

図6(A)乃至図6(D)は、実施の形態2で説明した第1のインバータと第2のインバータの配置の例を示す。なお、詳細は公知の半導体集積回路作製技術を参照すればよい。図6(A)乃至図6(D)に示される回路配置では、第1のインバータと第2のインバータは、ビット線6本分の幅に形成される。

【0101】

図6(A)は、単結晶半導体基板上に形成されるN型ウェル、P型ウェルのうち素子分離絶縁物で覆われていない部分の位置を示す。ビット線方向(x方向)にN型ウェルとP型ウェルを交互に形成する。

【0102】

ここで、N型ウェルの中央部のy方向の長さはP型ウェルの中央部のy方向の長さよりも大きくする。これは、インバータに用いられるPチャネル型トランジスタ(N型ウェル上に形成される)のチャネル幅を、Nチャネル型トランジスタ(P型ウェル上に形成される)のチャネル幅よりも大きくするためである。

【0103】

また、P型ウェルのx方向の長さはN型ウェルのx方向の長さよりも大きくする。これは、インバータに用いられるNチャネル型トランジスタのチャネル長を、Pチャネル型トランジスタのチャネル長よりも大きくするためである。

【0104】

また、図6(B)乃至図6(D)には、その上に形成される第1配線、第1コンタクトプラグ(以上、図6(B))、第2配線、第2コンタクトプラグ(以上、図6(C))、第3配線(以上、図6(D))の配置例を示す。

【0105】

なお、メモリセルを薄膜状の半導体で形成する場合には、第2配線の上、あるいは第3配線の上に薄膜状の半導体を形成してもよく、その際には、インバータ等の上に重ねてメモリセルを形成できるので集積度を高めることができる。

【0106】

ここで、第1配線はトランジスタのゲートとなるのであるが、特に、第1のインバータ、第2のインバータに用いられるトランジスタではしきい値のばらつきが小さいことを要求されるので、それらのゲートとなる配線の幅はチャネル面積が大きくなるように、Feature Size(F)よりも大きくするとよい。

【0107】

また、Nチャネル型トランジスタとPチャネル型トランジスタを用いてインバータを構成する際には、それらのオン特性がほぼ対称となるように、移動度を考慮してチャネル長、チャネル幅を設定することが望まれる。好ましくは、インバータを構成するPチャネル型トランジスタのチャネル幅をチャネル長で除した値が、Nチャネル型トランジスタのチャネル幅をチャネル長で除した値の2.5倍以上4倍以下とするとよい。

【0108】

さらに、しきい値ばらつきやビット線との容量比も考慮すると、それらのチャネル面積はほぼ等しいことが好ましい。すなわち、Nチャネル型トランジスタのチャネル面積がPチャネル型トランジスタのチャネル面積の80%以上125%以下となるように設計するとよい。なお、この際、Nチャネル型トランジスタのチャネル面積は10F2以上、好ましくは20F2以上とするとよい。

【0109】

例えば、チャネルが長方形のトランジスタであれば、Nチャネル型トランジスタのチャネル長を5F、チャネル幅を3F、Pチャネル型トランジスタのチャネル長を3F、チャネル幅を5Fとすると、チャネル面積、オン電流ともほぼ等しくなる。また、これらのチャネル面積は通常の15倍であるので、しきい値ばらつきも抑制される。しきい値ばらつきはチャネル面積の平方根に反比例するので、この場合、約4分の1となる。

【0110】

同様に、Nチャネル型トランジスタのチャネル長を7F、チャネル幅を4F、Pチャネル型トランジスタのチャネル長を4F、チャネル幅を7Fとしてもよいし、Nチャネル型トランジスタのチャネル長を12F、チャネル幅を7F、Pチャネル型トランジスタのチャネル長を7F、チャネル幅を12Fとしてもよい。

【0111】

また、レイアウトの都合で、上記のような長方形のチャネルを形成することが困難な場合には、チャネルの形状を多角形その他の形状として、実質的に必要とするオン電流およびチャネル面積が得られるように設計してもよい。

【0112】

本実施の形態の半導体メモリ装置では、インバータを構成するPチャネル型トランジスタのチャネル長を3F、チャネル幅を5F、Nチャネル型トランジスタのチャネル長を5F、チャネル幅を3Fとする。その結果、チャネル長を1F、チャネル幅を1Fとするトランジスタに比べて、しきい値のばらつきが約4分の1に低下する。

【0113】

なお、第1配線のうち、y方向に延在するものは、第1選択線あるいは第2選択線となるものであり、第1選択トランジスタや第2選択トランジスタにはNチャネル型トランジスタを用い、チャネル長を1F、チャネル幅を3Fとする。

【0114】

したがって、第1選択トランジスタ(あるいは第2選択トランジスタ)と第1のインバータ(あるいは第2のインバータ)の直列回路では、主たる抵抗は第1のインバータ(あるいは第2のインバータ)であり、第1選択トランジスタ(あるいは第2選択トランジスタ)の抵抗は十分に小さいので、動作速度にはほとんど関係がない。

【0115】

また、第2配線のうち、y方向に延在するものは、インバータへ電源を供給するための配線である。さらに、第3配線はビット線であり、例えば、図6(D)に示されるように、第1選択線あるいは第2選択線に相当する第1配線が設けられている部分付近で、ビット線BL_1Lとビット線BL_1Rに分離する構成となっている。

【0116】

図7には、図6(A)乃至図6(D)に示したレイアウトを用いて形成される部分およびその周辺の回路図を示す。図に示すように、第1のインバータと第2のインバータが、ビット線6本分の幅に形成されているため、ビット線6本ごとに同じパターンが現れる。

【0117】

本実施の形態の半導体メモリ装置では、第1選択線SL1の電位をオンに設定すると、ビット線BL_nR(nは整数)の電位を反転した電位がビット線BL_nLに出力される。また、第2選択線SL2の電位をオンに設定すると、ビット線BL_nLの電位を反転した電位がビット線BL_nRに出力される。

【0118】

なお、本実施の形態の半導体メモリ装置では、図6(A)乃至図6(D)に示したレイアウトからわかるように、第1のインバータの電源電圧と第2のインバータの電源電圧とを個別に操作できる。

【符号の説明】

【0119】

BL ビット線

MC メモリセル

SA センスアンプ

SL1 第1選択線

SL2 第2選択線

ST1 第1選択トランジスタ

ST2 第2選択トランジスタ

TND Nチャネル型トランジスタ

TNL Nチャネル型トランジスタ

TNR Nチャネル型トランジスタ

TNU Nチャネル型トランジスタ

TPD Pチャネル型トランジスタ

TPL Pチャネル型トランジスタ

TPR Pチャネル型トランジスタ

TPU Pチャネル型トランジスタ

T1 時刻

T2 時刻

T3 時刻

VNS 配線

VNS1 配線

VNS2 配線

VPS 配線

VPS1 配線

VPS2 配線

WL ワード線

【特許請求の範囲】

【請求項1】

第1のビット線と、第2のビット線と、前記第1のビット線および前記第2のビット線のいずれかに接続するメモリセルと、前記第1のビット線と前記第2のビット線の間にインバータとスイッチを有し、前記インバータと前記スイッチが直列に接続されている半導体メモリ装置。

【請求項2】

前記メモリセルのトランジスタは、前記インバータのトランジスタとは異なる層に設けられていることを特徴とする請求項1記載の半導体メモリ装置。

【請求項3】

前記スイッチは、複数のトランジスタより構成されていることを特徴とする請求項1または請求項2のいずれか一項に記載の半導体メモリ装置。

【請求項4】

前記スイッチは、導電型の異なるトランジスタより構成されていることを特徴とする請求項1乃至請求項3のいずれか一項に記載の半導体メモリ装置。

【請求項5】

前記インバータを構成するNチャネル型トランジスタのチャネル面積が、Pチャネル型トランジスタのチャネル面積の80%以上125%以下であり、前記Pチャネル型トランジスタのチャネル幅をチャネル長で除した値が、前記Nチャネル型トランジスタのチャネル幅をチャネル長で除した値の2.5倍以上4倍以下であることを特徴とする請求項1乃至請求項4のいずれか一項に記載の半導体メモリ装置。

【請求項6】

前記インバータを構成するNチャネル型トランジスタのチャネル面積が、10F2以上(FはFeature Size)であることを特徴とする請求項1乃至請求項5のいずれか一項に記載の半導体メモリ装置。

【請求項7】

請求項1乃至請求項6のいずれか一項に記載の半導体メモリ装置において、前記スイッチをオンとする過程と、その後に、前記第1のビット線と前記第2のビット線の電位差を増幅する過程と、を有する半導体メモリ装置の駆動方法。

【請求項8】

第1のビット線と、第2のビット線と、前記第1のビット線および前記第2のビット線のいずれかに接続するメモリセルと、第1のインバータと、第1のスイッチと、第2のインバータと、第2のスイッチを有し、前記第1のインバータと前記第1のスイッチ、および前記第2のインバータと前記第2のスイッチは、それぞれ接続されており、前記第1のビット線と前記第1のインバータ、前記第2のビット線と前記第1のスイッチ、前記第1のビット線と前記第2のスイッチ、前記第2のビット線と前記第2のインバータが、それぞれ接続されている半導体メモリ装置。

【請求項9】

前記メモリセルのトランジスタは、前記第1のインバータのトランジスタとは異なる層に設けられていることを特徴とする請求項8記載の半導体メモリ装置。

【請求項10】

前記第1のスイッチは、複数のトランジスタより構成されていることを特徴とする請求項8または請求項9のいずれか一項に記載の半導体メモリ装置。

【請求項11】

前記第1のスイッチは、導電型の異なるトランジスタより構成されていることを特徴とする請求項8乃至請求項10のいずれか一項に記載の半導体メモリ装置。

【請求項12】

前記第1のインバータを構成するNチャネル型トランジスタのチャネル面積がPチャネル型トランジスタのチャネル面積の80%以上125%以下であり、前記Pチャネル型トランジスタのチャネル幅をチャネル長で除した値が、前記Nチャネル型トランジスタのチャネル幅をチャネル長で除した値の2.5倍以上4倍以下であることを特徴とする請求項8乃至請求項11のいずれか一項に記載の半導体メモリ装置。

【請求項13】

前記第1のインバータを構成するNチャネル型トランジスタのチャネル面積が、10F2以上(FはFeature Size)であることを特徴とする請求項8乃至請求項12のいずれか一項に記載の半導体メモリ装置。

【請求項14】

請求項8乃至請求項13のいずれか一項に記載の半導体メモリ装置において、前記第1のスイッチをオンとする過程と、その後に、前記第2のスイッチをオンとすることにより、前記第1のインバータ、前記第1のスイッチ、前記第2のインバータと前記第2のスイッチよりなるループを構成する過程、とを有する半導体メモリ装置の駆動方法。

【請求項1】

第1のビット線と、第2のビット線と、前記第1のビット線および前記第2のビット線のいずれかに接続するメモリセルと、前記第1のビット線と前記第2のビット線の間にインバータとスイッチを有し、前記インバータと前記スイッチが直列に接続されている半導体メモリ装置。

【請求項2】

前記メモリセルのトランジスタは、前記インバータのトランジスタとは異なる層に設けられていることを特徴とする請求項1記載の半導体メモリ装置。

【請求項3】

前記スイッチは、複数のトランジスタより構成されていることを特徴とする請求項1または請求項2のいずれか一項に記載の半導体メモリ装置。

【請求項4】

前記スイッチは、導電型の異なるトランジスタより構成されていることを特徴とする請求項1乃至請求項3のいずれか一項に記載の半導体メモリ装置。

【請求項5】

前記インバータを構成するNチャネル型トランジスタのチャネル面積が、Pチャネル型トランジスタのチャネル面積の80%以上125%以下であり、前記Pチャネル型トランジスタのチャネル幅をチャネル長で除した値が、前記Nチャネル型トランジスタのチャネル幅をチャネル長で除した値の2.5倍以上4倍以下であることを特徴とする請求項1乃至請求項4のいずれか一項に記載の半導体メモリ装置。

【請求項6】

前記インバータを構成するNチャネル型トランジスタのチャネル面積が、10F2以上(FはFeature Size)であることを特徴とする請求項1乃至請求項5のいずれか一項に記載の半導体メモリ装置。

【請求項7】

請求項1乃至請求項6のいずれか一項に記載の半導体メモリ装置において、前記スイッチをオンとする過程と、その後に、前記第1のビット線と前記第2のビット線の電位差を増幅する過程と、を有する半導体メモリ装置の駆動方法。

【請求項8】

第1のビット線と、第2のビット線と、前記第1のビット線および前記第2のビット線のいずれかに接続するメモリセルと、第1のインバータと、第1のスイッチと、第2のインバータと、第2のスイッチを有し、前記第1のインバータと前記第1のスイッチ、および前記第2のインバータと前記第2のスイッチは、それぞれ接続されており、前記第1のビット線と前記第1のインバータ、前記第2のビット線と前記第1のスイッチ、前記第1のビット線と前記第2のスイッチ、前記第2のビット線と前記第2のインバータが、それぞれ接続されている半導体メモリ装置。

【請求項9】

前記メモリセルのトランジスタは、前記第1のインバータのトランジスタとは異なる層に設けられていることを特徴とする請求項8記載の半導体メモリ装置。

【請求項10】

前記第1のスイッチは、複数のトランジスタより構成されていることを特徴とする請求項8または請求項9のいずれか一項に記載の半導体メモリ装置。

【請求項11】

前記第1のスイッチは、導電型の異なるトランジスタより構成されていることを特徴とする請求項8乃至請求項10のいずれか一項に記載の半導体メモリ装置。

【請求項12】

前記第1のインバータを構成するNチャネル型トランジスタのチャネル面積がPチャネル型トランジスタのチャネル面積の80%以上125%以下であり、前記Pチャネル型トランジスタのチャネル幅をチャネル長で除した値が、前記Nチャネル型トランジスタのチャネル幅をチャネル長で除した値の2.5倍以上4倍以下であることを特徴とする請求項8乃至請求項11のいずれか一項に記載の半導体メモリ装置。

【請求項13】

前記第1のインバータを構成するNチャネル型トランジスタのチャネル面積が、10F2以上(FはFeature Size)であることを特徴とする請求項8乃至請求項12のいずれか一項に記載の半導体メモリ装置。

【請求項14】

請求項8乃至請求項13のいずれか一項に記載の半導体メモリ装置において、前記第1のスイッチをオンとする過程と、その後に、前記第2のスイッチをオンとすることにより、前記第1のインバータ、前記第1のスイッチ、前記第2のインバータと前記第2のスイッチよりなるループを構成する過程、とを有する半導体メモリ装置の駆動方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−109818(P2013−109818A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2012−234262(P2012−234262)

【出願日】平成24年10月24日(2012.10.24)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成24年10月24日(2012.10.24)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]