半導体メモリ装置及びそのためのテスト回路

【課題】本発明は、テスト速度を向上させることができる半導体メモリ装置及びそのためのテスト回路に関するものである。

【解決手段】本発明に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含む。

【解決手段】本発明に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体集積回路に関し、特に半導体メモリ装置及びそのためのテスト回路に関する。

【背景技術】

【0002】

一般に、半導体メモリ装置のメモリセルにデータを書き込む場合、入出力パッドを介して入力されるデータは、ライトドライバによりセルに書き込まれる。また、メモリセルに書き込まれるデータを読み出す場合には、メモリセルのデータがセンスアンプに移動して増幅された後、入出力パッドを介して出力される。

【0003】

図1は、一般の半導体メモリ装置の構成図である。

【0004】

図1に示すように、半導体メモリ装置100は、メモリセルアレイ101、アドレス入力バッファ103、プリデコーダ105、カラムデコーダ107、ブロックデコーダ109、ローデコーダ111、データ入出力バッファ113、センスアンプ115、ライトドライバ117及びコントローラ120を含む。

【0005】

メモリセルアレイ101には、ワードライン及びビットライン間に複数のメモリセルが接続される。

【0006】

アドレス入力バッファ103では、外部アドレスが入力されて内部アドレスに変換出力され、プリデコーダ105は、内部アドレスを1次デコードした後、カラムデコーダ107、ブロックデコーダ109及びローデコーダ111に提供する。カラムデコーダ107はプリデコードした結果からメモリセルアレイ101の接近対象ワードラインを選択し、ブロックデコーダ109はプリデコードした結果からメモリセルアレイ101の接近対象ブロックを選択する。類似に、ローデコーダ111は、プリデコードした結果により、メモリセルアレイ101の接近したいビットラインを選択する。

【0007】

データ入出力バッファ113には、複数のデータ入出力パッド(DQパッド)が接続される。

【0008】

データの読み出し動作時には、コントローラ120で発生する制御信号により、メモリセルアレイ101の選択されたメモリセルから読み出されたデータがセンスアンプ115で増幅された後、データ入出力バッファ113を介してDQパッドに出力される。データの書き込み動作時には、コントローラ120で発生する制御信号により、DQパッドから入力されるデータがデータ入出力バッファ113を介してライトドライバ117に提供され、ライトドライバ117で選択されたメモリセルにデータが伝達される。

【0009】

一方、コントローラ120は、チップ選択信号(/CS)により駆動される第1の入力バッファ121と、ライトイネーブル信号(/WE)により駆動される第2の入力バッファ123と、出力イネーブル信号(/OE)により駆動される第3の入力バッファ125と、第2の入力バッファ123の出力信号に応じてライトパルス(WDEN)を生成するライトパルス生成部127と、第3の入力バッファ125の出力信号に応じてリードパルス(OEN)を生成するリードパルス生成部129とを含む。尚、ライトパルス生成部127は、データ入出力バッファイネーブル信号(BUFEN)も生成してデータ入出力バッファ113に提供し、リードパルス生成部129は、センスアンプイネーブル信号(SAEN)も生成してセンスアンプ115に提供する。

【0010】

このように、半導体メモリ装置は、ノーマル動作モード時、センスアンプによりデータの読み出しを行い、ライトドライバによりデータの書き込みを行う。

【0011】

ところで、新規のメモリセルの開発による半導体メモリ装置への適用時、開発されたメモリセルに対する検証が行われるべきであるが、センスアンプ及びライトドライバによる読み出し/書き込みデータの検証は信頼性が確保できない。したがって、センスアンプ及びライトドライバによるデータの読み出し/書き込み動作後、読み出し/書き込みの経路、メモリセルアレイ及びコントローラで発生する変数を検証した後、セルに対する評価を行うことができるので、テストに多くの時間が要求される。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2005−77339号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

本発明は、高速でメモリセルを検証できる半導体メモリ装置及びそのためのテスト回路を提供する。

【課題を解決するための手段】

【0014】

本発明の一実施例に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含むことができる。

【0015】

また、本発明の他の実施例に係る半導体メモリ装置は、ビットライン及びソースライン間に接続され、ワードラインに印加された電位により駆動される複数のメモリセルを含むメモリセルアレイ;及び、テストモード信号に応じてデータ入出力パッドに印加されたデータを前記メモリセルの前記ビットラインから前記ソースラインの方に直接伝達したり、前記データ入出力パッドに印加されたデータを前記メモリセルの前記ソースラインから前記ビットラインの方に直接伝達する両方向アクセス制御部を含むことができる。

【0016】

また、本発明の一実施例に係るテスト回路は、データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;及び、テストモード信号に応じて前記データ入出力パッドに印加されたデータを受信してメモリセルアレイに直接伝達する両方向アクセス制御部を含むことができる。

【発明の効果】

【0017】

本発明は、テストモード時、メモリセルに直接データを書き込むので、テストに要求される時間を大幅短縮できる。

【図面の簡単な説明】

【0018】

【図1】一般の半導体メモリ装置の構成図である。

【図2】本発明の一実施例に係る半導体メモリ装置の構成図である。

【図3】図2の両方向アクセス制御部の一例を示す図である。

【図4】図3の経路設定部の一例を示す図である。

【図5】本発明に適用されるテストモード信号生成回路の一例を示す図である。

【図6】図2のスイッチング部の一例を示す図である。

【発明を実施するための形態】

【0019】

以下、添付図面に基づき、本発明の好適な実施例を詳細に説明する。

【0020】

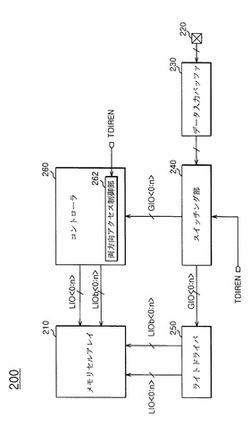

図2は、本発明の一実施例に係る半導体メモリ装置の構成図である。

【0021】

図2には、説明の便宜のために、半導体メモリ装置の主要構成だけを示したが、半導体メモリ装置の動作のために必要な構成部、例えばアドレス処理回路や制御信号発生回路などが含まれ得るのは、本発明が属する技術分野において自明であると言える。

【0022】

図2に示すように、本発明の一実施例に係る半導体メモリ装置200は、メモリセルアレイ210、データ入出力パッド(DQパッド)220、データ入力バッファ230、スイッチング部240、ライトドライバ250及びコントローラ260を含む。

【0023】

メモリセルアレイ210には、ワードライン及びビットライン間に接続される複数のメモリセルが含まれる。各単位メモリセルは、電流駆動方式によりデータの読み出し/書き込みが可能なメモリセルであり、より詳しくは極性(Polarity)のある抵抗性メモリセルであり得る。本発明の一実施例において、単位メモリセルは磁気メモリセルとして構成できる。

【0024】

スイッチング部240は、半導体メモリ装置200の動作モード(ノーマルモードやテストモード)により、データ入力バッファ230を介してメモリセルアレイ210に提供されるデータの経路を設定する。より詳しくは、スイッチング部240は、テストモード信号(TDIREN)により駆動され、ノーマルモードではグローバル入出力ライン(GIO<0:n>)を介してライトドライバ250にデータを伝達し、テストモードではグローバル入出力ライン(GIO<0:n>)を介してコントローラ260の両方向アクセス制御部262にデータを伝達する。

【0025】

両方向アクセス制御部262は、テストモード信号(TDIREN)に応じて、グローバル入出力ライン(GIO<0:n>)を介して伝達されたテストデータを、第1のローカル入出力ライン(LIO<0:n>)を介してメモリセルアレイ210に提供したり、第2のローカル入出力ライン(LIOb<0:n>)介してメモリセルアレイ210に提供する。

【0026】

前述したように、テストモード時、ライトドライバ250によりメモリセルアレイ210に書き込まれたテストデータは、その信頼性が確保できない。よって、本発明の一実施例では、テストモード時、ライトドライバ250を経由することなく直接メモリセルアレイ210にデータを書き込む。また、メモリセルアレイ210を構成する単位メモリセルが極性のある抵抗性メモリセルである場合、論理ハイレバベルのデータだけでなく、論理ローレベルのデータも直接書き込むことができるように、メモリセルのビットライン−ソースラインの方と、ソースライン−ビットラインの方とに電流を供給できるようにする。

【0027】

したがって、半導体メモリ装置200がノーマルモードにおいてデータの書き込み動作を行う場合、テストモード信号(TDIREN)により駆動されるスイッチング部240は、DQパッド220を介してデータ入力バッファ230に伝達されたデータを、グローバル入出力ライン(GIO<0:n>)を介してライトドライバ250に伝達する。また、ライトドライバ250は、伝達されたデータを駆動して、ローカル入出力ライン(LIO<0:n>)を介してメモリセルアレイ210にデータを書き込む。

【0028】

これに対し、半導体メモリ装置200がテストモードにおいてデータの書き込み動作を行う場合、スイッチング部240は、データ入力バッファ230に伝達されたデータを、グローバル入出力ライン(GIO<0:n>)を介してコントローラ260の両方向アクセス制御部262に伝達する。また、両方向アクセス制御部262は、第1のローカル入出力ライン(LIO<0:n>)又は第2のローカル入出力ライン(LIO<0:n>、LIOb<0:n>)を介してメモリセルアレイ210にテストデータを提供する。

【0029】

結果として、ライトドライバ250を経由することなくメモリセルアレイ210にテストデータを直接書き込むことができるため、テストデータの検証の信頼性を確保できる。また、テストデータを直接書き込むことにより、ライトパス、セルアレイ及びコントローラで発生する変数を検証し、これをテストデータの検証に反映する必要がないので、テストに要求される時間を大幅短縮できる。

【0030】

これにより、本発明の一実施例に係るスイッチング部240及び両方向アクセス制御部262は、半導体メモリ装置のためのテスト回路になり得る。

【0031】

図3は、図2の両方向アクセス制御部の一例を示す図である。

【0032】

図3に示すように、本実施例による両方向アクセス制御部262は、経路設定部301、第1のスイッチ303及び第2のスイッチ305を含む。

【0033】

経路設定部301は、一つの入力端がグローバル入出力ライン(GIO)を介してDQパッドと接続され、他の入力端が接地端子(VSS)に接続される。また、テストモード信号(TDIREN)に応じて、DQパッドに印加されたテストデータを、第1のローカル入出力ライン(LIO)又は第2の入出力ライン(LIOb)にスイッチングする。

【0034】

第1のスイッチ303は、経路設定部301とメモリセル212のビットライン(BL)との間に、第1のローカル入出力ライン(LIO)を介して接続される。

【0035】

第2のスイッチ305は、メモリセル212のソースライン(SL)と経路設定部301との間に、第2のローカル入出力ライン(LIOb)を介して接続される。

【0036】

第1のスイッチ303及び第2のスイッチ303、305は、ノーマルモード時にターンオフされ、テストモード時にターンオンされる。本発明の一実施例では、第1のスイッチ303及び第2のスイッチ303、305は、それぞれプリチャージ信号(PCGb)、テストモード信号(TDIREN)及びカラム選択信号(CYI)により駆動される複数のスイッチング素子を直列連結して構成できるが、これに限定されるものではない。ここで、未説明の符号214は、ワードライン駆動信号によりオン/オフされるワードライン選択スイッチを示す。

【0037】

テストモード時、メモリセル212に第1のレベルのデータを書き込みたい場合、経路設定部301は、例えばDQパッドのデータを、第1のローカル入出力ライン(LIO)を介してメモリセル212に伝達できる。また、第2のレベルのデータを書き込みたい場合、経路設定部301は、DQパッドのデータを、第2のローカル入出力ライン(LIOb)を介してメモリセル212に伝達できる。

【0038】

したがって、メモリセル212に対してライトドライバを経由することなく直接データを書き込むことができると同時に、メモリセル212のビットライン−ソースラインの方だけでなく、ソースライン−ビットラインの方にも書き込み電流を供給できる。これにより、テストを高速で行うことができ、多様な条件のテストデータを書き込むことができる。

【0039】

このための経路設定部301の動作を、図4及び図5を参照して説明する。

【0040】

図4は図3の経路設定部の一例を示す図であり、図5は本発明に適用されるテストモード信号生成回路の一例を示す図である。

【0041】

テストモード時、メモリセルに書き込みたいデータのレベルにより、DQパッドに印加されたデータの伝達経路を変更するために、経路設定部301は第1の経路選択部310及び第2の経路選択部320を含むように構成できる。

【0042】

第1の経路選択部310は、順方向テストモード信号(TDIRENFB、TDIRENFD)により駆動されて、DQパッドに印加されたデータを第1のローカル入出力ライン(LIO)に伝達又は遮断する第1の伝達素子(T11)と、第1のローカル入出力ライン(LIO)及び接地端子間に接続されて、逆方向テストモード信号(TDIRENRB、TDIRENRD)により駆動される第2の伝達素子(T13)とを含むことができる。

【0043】

第2の経路選択部320は、逆方向テストモード信号(TDIRENRB、TDIRENRD)により駆動されて、DQパッドに印加されたデータを第2のローカル入出力ライン(LIOb)に伝達又は遮断する第3の伝達素子(T15)と、第2のローカル入出力ライン(LIOb)及び接地端子間に接続されて、順方向テストモード信号(TDIRENFB、TDIRENFD)により駆動される第4の伝達素子(T17)とを含むことができる。

【0044】

一方、順方向テストモード信号(TDIRENFB、TDIRENFD)及び逆方向テストモード信号(TDIRENRB、TDIRENRD)は、テストモード信号(TDIREN)により生成でき、例えば図5のように生成できる。

【0045】

すなわち、テストモード信号(TDIREN)を遅延させて第1の順方向テストモード信号(TDIRENF)を生成し、テストモード信号(TDIREN)を反転させて第1の逆方向テストモード信号(TDIRENR)を生成する。

【0046】

そして、第1の順方向テストモード信号(TDIRENF)を反転させて第2の順方向テストモード信号(TDIRENFB)を生成し、これを再反転させて第3の順方向テストモード信号(TDIRENFD)を生成できる。

【0047】

類似に、第1の逆方向テストモード信号(TDIRENR)を反転させて第2の逆方向テストモード信号(TDIRENRB)を生成し、これを再反転させて第3の逆方向テストモード信号(TDIRENRD)を生成できる。

【0048】

テストモード信号により順方向及び逆方向テストモード信号を生成する例は、図5の回路に限定されず、多様な方法により変更できる。

【0049】

経路設定部301が図4及び図5のように構成されることで、テストモード信号(TDIREN)がハイレバルレベルに印加される場合、第1の伝達素子(T11)及び第4の伝達素子(T17)がターンオンされ、第2の伝達素子(T13)及び第3の伝達素子(T15)がターンオフされる。したがって、DQパッドに印加されたテストデータは、第1の伝達素子(T11)を介して第1のローカル入出力ライン(LIO)に伝達され、メモリセルのビットラインからソースラインの方にデータが書き込まれる。

【0050】

一方、テストモード信号(TDIREN)がローレベルに印加される場合、第2の伝達素子(T13)及び第3の伝達素子(T13、T15)がターンオンされ、DQパッドに印加されたデータが第2のローカル入出力ライン(LIOb)に伝達される。つまり、メモリセルのソースラインからビットラインの方にデータが書き込まれる。

【0051】

このように、本発明の一実施例では、テストモード信号にDQパッドからメモリセルに電流が流入する閉ループが形成される。そして、テストモード信号のレベルにより順方向又は逆方向電流パスが形成されて、メモリセルに両方向にテストデータを書き込むことができる。

【0052】

結果として、メモリセルに論理ハイレバルレベル及び論理ローレベルのテストデータを全部書き込むことができる。メモリセルが抵抗性メモリセルとして構成される場合、論理ハイレベル及び論理ローレベルのテストデータを書き込んだ後、メモリセルの抵抗値を実測でき、これに基づいてメモリセルアレイの特性分析を容易に行うことができる。

【0053】

また、ノーマルモード時にデータ入力バッファ及びライトドライバ間の電流パスを形成し、テストモード時にデータ入力バッファ及び両方向アクセス制御部間の電流パスを形成するためのスイッチング部(図2の240)は、例えば次の通り構成できる。

【0054】

図6は、図2のスイッチング部の一例を示す図である。

【0055】

図6に示すように、スイッチング部240は、テストモード信号(TDIREN)及びその反転信号を入力信号として、入力信号の位相が互いに異なる場合、論理ハイレバルレベルの出力信号を生成し、入力信号の位相が互いに同一の場合、論理ローレベルの出力信号を生成する第1の素子241と、第1の素子241の出力信号に応じてDQパッドに印加された電流を両方向アクセス制御部262に提供する第2の素子243と、第1の素子241の出力信号に応じてDQパッドに印加された電流をライトドライバ250に提供する第3の素子245とを含むように構成できる。

【0056】

本発明の一実施例において、第1の素子241は、排他的論理和演算を行う素子(XOR)からなる。また、第2の素子243及び第3の素子245は、互いに反対位相の信号によりターンオン/ターンオフされるように、各々NMOSトランジスタ及びPMOSトランジスタからなるが、これに限定されるものではない。

【0057】

なお、本発明の詳細な説明では具体的な実施例について説明したが、本発明の要旨から逸脱しない範囲内において適宜変更することができる。よって、本発明の範囲は、前述の実施例に限定されるものではなく、特許請求の範囲の記載及びこれと均等なものに基づいて定められるべきである。

【符号の説明】

【0058】

200 半導体メモリ装置

210 メモリセルアレイ

212 メモリセル

214 ワードライン選択スイッチ

220 データ入出力パッド

230 データ入力バッファ

240 スイッチング部

250 ライトドライバ

260 コントローラ

262 両方向アクセス制御部

301 経路設定部

303 第1のスイッチ

305 第2のスイッチ

310 第1の経路選択部

320 第2の経路選択部

【技術分野】

【0001】

本発明は、半導体集積回路に関し、特に半導体メモリ装置及びそのためのテスト回路に関する。

【背景技術】

【0002】

一般に、半導体メモリ装置のメモリセルにデータを書き込む場合、入出力パッドを介して入力されるデータは、ライトドライバによりセルに書き込まれる。また、メモリセルに書き込まれるデータを読み出す場合には、メモリセルのデータがセンスアンプに移動して増幅された後、入出力パッドを介して出力される。

【0003】

図1は、一般の半導体メモリ装置の構成図である。

【0004】

図1に示すように、半導体メモリ装置100は、メモリセルアレイ101、アドレス入力バッファ103、プリデコーダ105、カラムデコーダ107、ブロックデコーダ109、ローデコーダ111、データ入出力バッファ113、センスアンプ115、ライトドライバ117及びコントローラ120を含む。

【0005】

メモリセルアレイ101には、ワードライン及びビットライン間に複数のメモリセルが接続される。

【0006】

アドレス入力バッファ103では、外部アドレスが入力されて内部アドレスに変換出力され、プリデコーダ105は、内部アドレスを1次デコードした後、カラムデコーダ107、ブロックデコーダ109及びローデコーダ111に提供する。カラムデコーダ107はプリデコードした結果からメモリセルアレイ101の接近対象ワードラインを選択し、ブロックデコーダ109はプリデコードした結果からメモリセルアレイ101の接近対象ブロックを選択する。類似に、ローデコーダ111は、プリデコードした結果により、メモリセルアレイ101の接近したいビットラインを選択する。

【0007】

データ入出力バッファ113には、複数のデータ入出力パッド(DQパッド)が接続される。

【0008】

データの読み出し動作時には、コントローラ120で発生する制御信号により、メモリセルアレイ101の選択されたメモリセルから読み出されたデータがセンスアンプ115で増幅された後、データ入出力バッファ113を介してDQパッドに出力される。データの書き込み動作時には、コントローラ120で発生する制御信号により、DQパッドから入力されるデータがデータ入出力バッファ113を介してライトドライバ117に提供され、ライトドライバ117で選択されたメモリセルにデータが伝達される。

【0009】

一方、コントローラ120は、チップ選択信号(/CS)により駆動される第1の入力バッファ121と、ライトイネーブル信号(/WE)により駆動される第2の入力バッファ123と、出力イネーブル信号(/OE)により駆動される第3の入力バッファ125と、第2の入力バッファ123の出力信号に応じてライトパルス(WDEN)を生成するライトパルス生成部127と、第3の入力バッファ125の出力信号に応じてリードパルス(OEN)を生成するリードパルス生成部129とを含む。尚、ライトパルス生成部127は、データ入出力バッファイネーブル信号(BUFEN)も生成してデータ入出力バッファ113に提供し、リードパルス生成部129は、センスアンプイネーブル信号(SAEN)も生成してセンスアンプ115に提供する。

【0010】

このように、半導体メモリ装置は、ノーマル動作モード時、センスアンプによりデータの読み出しを行い、ライトドライバによりデータの書き込みを行う。

【0011】

ところで、新規のメモリセルの開発による半導体メモリ装置への適用時、開発されたメモリセルに対する検証が行われるべきであるが、センスアンプ及びライトドライバによる読み出し/書き込みデータの検証は信頼性が確保できない。したがって、センスアンプ及びライトドライバによるデータの読み出し/書き込み動作後、読み出し/書き込みの経路、メモリセルアレイ及びコントローラで発生する変数を検証した後、セルに対する評価を行うことができるので、テストに多くの時間が要求される。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2005−77339号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

本発明は、高速でメモリセルを検証できる半導体メモリ装置及びそのためのテスト回路を提供する。

【課題を解決するための手段】

【0014】

本発明の一実施例に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含むことができる。

【0015】

また、本発明の他の実施例に係る半導体メモリ装置は、ビットライン及びソースライン間に接続され、ワードラインに印加された電位により駆動される複数のメモリセルを含むメモリセルアレイ;及び、テストモード信号に応じてデータ入出力パッドに印加されたデータを前記メモリセルの前記ビットラインから前記ソースラインの方に直接伝達したり、前記データ入出力パッドに印加されたデータを前記メモリセルの前記ソースラインから前記ビットラインの方に直接伝達する両方向アクセス制御部を含むことができる。

【0016】

また、本発明の一実施例に係るテスト回路は、データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;及び、テストモード信号に応じて前記データ入出力パッドに印加されたデータを受信してメモリセルアレイに直接伝達する両方向アクセス制御部を含むことができる。

【発明の効果】

【0017】

本発明は、テストモード時、メモリセルに直接データを書き込むので、テストに要求される時間を大幅短縮できる。

【図面の簡単な説明】

【0018】

【図1】一般の半導体メモリ装置の構成図である。

【図2】本発明の一実施例に係る半導体メモリ装置の構成図である。

【図3】図2の両方向アクセス制御部の一例を示す図である。

【図4】図3の経路設定部の一例を示す図である。

【図5】本発明に適用されるテストモード信号生成回路の一例を示す図である。

【図6】図2のスイッチング部の一例を示す図である。

【発明を実施するための形態】

【0019】

以下、添付図面に基づき、本発明の好適な実施例を詳細に説明する。

【0020】

図2は、本発明の一実施例に係る半導体メモリ装置の構成図である。

【0021】

図2には、説明の便宜のために、半導体メモリ装置の主要構成だけを示したが、半導体メモリ装置の動作のために必要な構成部、例えばアドレス処理回路や制御信号発生回路などが含まれ得るのは、本発明が属する技術分野において自明であると言える。

【0022】

図2に示すように、本発明の一実施例に係る半導体メモリ装置200は、メモリセルアレイ210、データ入出力パッド(DQパッド)220、データ入力バッファ230、スイッチング部240、ライトドライバ250及びコントローラ260を含む。

【0023】

メモリセルアレイ210には、ワードライン及びビットライン間に接続される複数のメモリセルが含まれる。各単位メモリセルは、電流駆動方式によりデータの読み出し/書き込みが可能なメモリセルであり、より詳しくは極性(Polarity)のある抵抗性メモリセルであり得る。本発明の一実施例において、単位メモリセルは磁気メモリセルとして構成できる。

【0024】

スイッチング部240は、半導体メモリ装置200の動作モード(ノーマルモードやテストモード)により、データ入力バッファ230を介してメモリセルアレイ210に提供されるデータの経路を設定する。より詳しくは、スイッチング部240は、テストモード信号(TDIREN)により駆動され、ノーマルモードではグローバル入出力ライン(GIO<0:n>)を介してライトドライバ250にデータを伝達し、テストモードではグローバル入出力ライン(GIO<0:n>)を介してコントローラ260の両方向アクセス制御部262にデータを伝達する。

【0025】

両方向アクセス制御部262は、テストモード信号(TDIREN)に応じて、グローバル入出力ライン(GIO<0:n>)を介して伝達されたテストデータを、第1のローカル入出力ライン(LIO<0:n>)を介してメモリセルアレイ210に提供したり、第2のローカル入出力ライン(LIOb<0:n>)介してメモリセルアレイ210に提供する。

【0026】

前述したように、テストモード時、ライトドライバ250によりメモリセルアレイ210に書き込まれたテストデータは、その信頼性が確保できない。よって、本発明の一実施例では、テストモード時、ライトドライバ250を経由することなく直接メモリセルアレイ210にデータを書き込む。また、メモリセルアレイ210を構成する単位メモリセルが極性のある抵抗性メモリセルである場合、論理ハイレバベルのデータだけでなく、論理ローレベルのデータも直接書き込むことができるように、メモリセルのビットライン−ソースラインの方と、ソースライン−ビットラインの方とに電流を供給できるようにする。

【0027】

したがって、半導体メモリ装置200がノーマルモードにおいてデータの書き込み動作を行う場合、テストモード信号(TDIREN)により駆動されるスイッチング部240は、DQパッド220を介してデータ入力バッファ230に伝達されたデータを、グローバル入出力ライン(GIO<0:n>)を介してライトドライバ250に伝達する。また、ライトドライバ250は、伝達されたデータを駆動して、ローカル入出力ライン(LIO<0:n>)を介してメモリセルアレイ210にデータを書き込む。

【0028】

これに対し、半導体メモリ装置200がテストモードにおいてデータの書き込み動作を行う場合、スイッチング部240は、データ入力バッファ230に伝達されたデータを、グローバル入出力ライン(GIO<0:n>)を介してコントローラ260の両方向アクセス制御部262に伝達する。また、両方向アクセス制御部262は、第1のローカル入出力ライン(LIO<0:n>)又は第2のローカル入出力ライン(LIO<0:n>、LIOb<0:n>)を介してメモリセルアレイ210にテストデータを提供する。

【0029】

結果として、ライトドライバ250を経由することなくメモリセルアレイ210にテストデータを直接書き込むことができるため、テストデータの検証の信頼性を確保できる。また、テストデータを直接書き込むことにより、ライトパス、セルアレイ及びコントローラで発生する変数を検証し、これをテストデータの検証に反映する必要がないので、テストに要求される時間を大幅短縮できる。

【0030】

これにより、本発明の一実施例に係るスイッチング部240及び両方向アクセス制御部262は、半導体メモリ装置のためのテスト回路になり得る。

【0031】

図3は、図2の両方向アクセス制御部の一例を示す図である。

【0032】

図3に示すように、本実施例による両方向アクセス制御部262は、経路設定部301、第1のスイッチ303及び第2のスイッチ305を含む。

【0033】

経路設定部301は、一つの入力端がグローバル入出力ライン(GIO)を介してDQパッドと接続され、他の入力端が接地端子(VSS)に接続される。また、テストモード信号(TDIREN)に応じて、DQパッドに印加されたテストデータを、第1のローカル入出力ライン(LIO)又は第2の入出力ライン(LIOb)にスイッチングする。

【0034】

第1のスイッチ303は、経路設定部301とメモリセル212のビットライン(BL)との間に、第1のローカル入出力ライン(LIO)を介して接続される。

【0035】

第2のスイッチ305は、メモリセル212のソースライン(SL)と経路設定部301との間に、第2のローカル入出力ライン(LIOb)を介して接続される。

【0036】

第1のスイッチ303及び第2のスイッチ303、305は、ノーマルモード時にターンオフされ、テストモード時にターンオンされる。本発明の一実施例では、第1のスイッチ303及び第2のスイッチ303、305は、それぞれプリチャージ信号(PCGb)、テストモード信号(TDIREN)及びカラム選択信号(CYI)により駆動される複数のスイッチング素子を直列連結して構成できるが、これに限定されるものではない。ここで、未説明の符号214は、ワードライン駆動信号によりオン/オフされるワードライン選択スイッチを示す。

【0037】

テストモード時、メモリセル212に第1のレベルのデータを書き込みたい場合、経路設定部301は、例えばDQパッドのデータを、第1のローカル入出力ライン(LIO)を介してメモリセル212に伝達できる。また、第2のレベルのデータを書き込みたい場合、経路設定部301は、DQパッドのデータを、第2のローカル入出力ライン(LIOb)を介してメモリセル212に伝達できる。

【0038】

したがって、メモリセル212に対してライトドライバを経由することなく直接データを書き込むことができると同時に、メモリセル212のビットライン−ソースラインの方だけでなく、ソースライン−ビットラインの方にも書き込み電流を供給できる。これにより、テストを高速で行うことができ、多様な条件のテストデータを書き込むことができる。

【0039】

このための経路設定部301の動作を、図4及び図5を参照して説明する。

【0040】

図4は図3の経路設定部の一例を示す図であり、図5は本発明に適用されるテストモード信号生成回路の一例を示す図である。

【0041】

テストモード時、メモリセルに書き込みたいデータのレベルにより、DQパッドに印加されたデータの伝達経路を変更するために、経路設定部301は第1の経路選択部310及び第2の経路選択部320を含むように構成できる。

【0042】

第1の経路選択部310は、順方向テストモード信号(TDIRENFB、TDIRENFD)により駆動されて、DQパッドに印加されたデータを第1のローカル入出力ライン(LIO)に伝達又は遮断する第1の伝達素子(T11)と、第1のローカル入出力ライン(LIO)及び接地端子間に接続されて、逆方向テストモード信号(TDIRENRB、TDIRENRD)により駆動される第2の伝達素子(T13)とを含むことができる。

【0043】

第2の経路選択部320は、逆方向テストモード信号(TDIRENRB、TDIRENRD)により駆動されて、DQパッドに印加されたデータを第2のローカル入出力ライン(LIOb)に伝達又は遮断する第3の伝達素子(T15)と、第2のローカル入出力ライン(LIOb)及び接地端子間に接続されて、順方向テストモード信号(TDIRENFB、TDIRENFD)により駆動される第4の伝達素子(T17)とを含むことができる。

【0044】

一方、順方向テストモード信号(TDIRENFB、TDIRENFD)及び逆方向テストモード信号(TDIRENRB、TDIRENRD)は、テストモード信号(TDIREN)により生成でき、例えば図5のように生成できる。

【0045】

すなわち、テストモード信号(TDIREN)を遅延させて第1の順方向テストモード信号(TDIRENF)を生成し、テストモード信号(TDIREN)を反転させて第1の逆方向テストモード信号(TDIRENR)を生成する。

【0046】

そして、第1の順方向テストモード信号(TDIRENF)を反転させて第2の順方向テストモード信号(TDIRENFB)を生成し、これを再反転させて第3の順方向テストモード信号(TDIRENFD)を生成できる。

【0047】

類似に、第1の逆方向テストモード信号(TDIRENR)を反転させて第2の逆方向テストモード信号(TDIRENRB)を生成し、これを再反転させて第3の逆方向テストモード信号(TDIRENRD)を生成できる。

【0048】

テストモード信号により順方向及び逆方向テストモード信号を生成する例は、図5の回路に限定されず、多様な方法により変更できる。

【0049】

経路設定部301が図4及び図5のように構成されることで、テストモード信号(TDIREN)がハイレバルレベルに印加される場合、第1の伝達素子(T11)及び第4の伝達素子(T17)がターンオンされ、第2の伝達素子(T13)及び第3の伝達素子(T15)がターンオフされる。したがって、DQパッドに印加されたテストデータは、第1の伝達素子(T11)を介して第1のローカル入出力ライン(LIO)に伝達され、メモリセルのビットラインからソースラインの方にデータが書き込まれる。

【0050】

一方、テストモード信号(TDIREN)がローレベルに印加される場合、第2の伝達素子(T13)及び第3の伝達素子(T13、T15)がターンオンされ、DQパッドに印加されたデータが第2のローカル入出力ライン(LIOb)に伝達される。つまり、メモリセルのソースラインからビットラインの方にデータが書き込まれる。

【0051】

このように、本発明の一実施例では、テストモード信号にDQパッドからメモリセルに電流が流入する閉ループが形成される。そして、テストモード信号のレベルにより順方向又は逆方向電流パスが形成されて、メモリセルに両方向にテストデータを書き込むことができる。

【0052】

結果として、メモリセルに論理ハイレバルレベル及び論理ローレベルのテストデータを全部書き込むことができる。メモリセルが抵抗性メモリセルとして構成される場合、論理ハイレベル及び論理ローレベルのテストデータを書き込んだ後、メモリセルの抵抗値を実測でき、これに基づいてメモリセルアレイの特性分析を容易に行うことができる。

【0053】

また、ノーマルモード時にデータ入力バッファ及びライトドライバ間の電流パスを形成し、テストモード時にデータ入力バッファ及び両方向アクセス制御部間の電流パスを形成するためのスイッチング部(図2の240)は、例えば次の通り構成できる。

【0054】

図6は、図2のスイッチング部の一例を示す図である。

【0055】

図6に示すように、スイッチング部240は、テストモード信号(TDIREN)及びその反転信号を入力信号として、入力信号の位相が互いに異なる場合、論理ハイレバルレベルの出力信号を生成し、入力信号の位相が互いに同一の場合、論理ローレベルの出力信号を生成する第1の素子241と、第1の素子241の出力信号に応じてDQパッドに印加された電流を両方向アクセス制御部262に提供する第2の素子243と、第1の素子241の出力信号に応じてDQパッドに印加された電流をライトドライバ250に提供する第3の素子245とを含むように構成できる。

【0056】

本発明の一実施例において、第1の素子241は、排他的論理和演算を行う素子(XOR)からなる。また、第2の素子243及び第3の素子245は、互いに反対位相の信号によりターンオン/ターンオフされるように、各々NMOSトランジスタ及びPMOSトランジスタからなるが、これに限定されるものではない。

【0057】

なお、本発明の詳細な説明では具体的な実施例について説明したが、本発明の要旨から逸脱しない範囲内において適宜変更することができる。よって、本発明の範囲は、前述の実施例に限定されるものではなく、特許請求の範囲の記載及びこれと均等なものに基づいて定められるべきである。

【符号の説明】

【0058】

200 半導体メモリ装置

210 メモリセルアレイ

212 メモリセル

214 ワードライン選択スイッチ

220 データ入出力パッド

230 データ入力バッファ

240 スイッチング部

250 ライトドライバ

260 コントローラ

262 両方向アクセス制御部

301 経路設定部

303 第1のスイッチ

305 第2のスイッチ

310 第1の経路選択部

320 第2の経路選択部

【特許請求の範囲】

【請求項1】

複数のメモリセルを含むメモリセルアレイ;

データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;

ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、

テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含むことを特徴とする、半導体メモリ装置。

【請求項2】

前記コントローラは、前記テストモード信号に応じて前記データ入出力パッドから伝達されたデータを、第1のローカル入出力ラインを介して前記メモリセルアレイに提供する両方向アクセス制御部を含むことを特徴とする、請求項1に記載の半導体メモリ装置。

【請求項3】

前記両方向アクセス制御部は、前記テストモード信号に応じて前記データ入出力パッドから伝達されたデータを、第2のローカル入出力ラインを介して前記メモリセルアレイに提供することを特徴とする、請求項2に記載の半導体メモリ装置。

【請求項4】

前記スイッチング部は、前記データ入出力パッド及び前記ライトドライバ間、或いは、前記データ入出力パッド及び前記コントローラ間のグローバル入出力ライン上に接続されることを特徴とする、請求項3に記載の半導体メモリ装置。

【請求項5】

前記両方向アクセス制御部は、前記スイッチング部及び前記メモリセルアレイ間の前記第1のローカル入出力ライン及び第2のローカル入出力ライン上に接続されることを特徴とする、請求項3に記載の半導体メモリ装置。

【請求項6】

前記メモリセルは、電流駆動方式によりデータの読み出し/書き込みが行われることを特徴とする、請求項1乃至請求項5の何れか1項に記載の半導体メモリ装置。

【請求項7】

前記メモリセルは、抵抗性メモリセルであることを特徴とする、請求項1乃至請求項5の何れか1項に記載の半導体メモリ装置。

【請求項8】

ビットライン及びソースライン間に接続され、ワードラインに印加された電位により駆動される複数のメモリセルを含むメモリセルアレイ;及び、

テストモード信号に応じてデータ入出力パッドに印加されたデータを、前記メモリセルの前記ビットラインから前記ソースラインの方に直接伝達したり、前記データ入出力パッドに印加されたデータを、前記メモリセルの前記ソースラインから前記ビットラインの方に直接伝達する両方向アクセス制御部を含むことを特徴とする、半導体メモリ装置。

【請求項9】

ノーマルモード時、前記データ入出力パッドに印加されたデータを受信して駆動し、前記メモリセルアレイに書きこむライトドライバをさらに含むことを特徴とする、請求項8に記載の半導体メモリ装置。

【請求項10】

前記データ入出力パッドに接続され、前記テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を、前記両方向アクセス制御部又は前記ライトドライバの何れか一つに制御するスイッチング部をさらに含むことを特徴とする、請求項9に記載の半導体メモリ装置。

【請求項11】

前記メモリセルは、電流駆動方式によりデータの読み出し/書き込みが行われることを特徴とする、請求項8乃至請求項10の何れか1項に記載の半導体メモリ装置。

【請求項12】

前記メモリセルは、抵抗性メモリセルであることを特徴とする、請求項8乃至請求項10の何れか1項に記載の半導体メモリ装置。

【請求項13】

データ入出力パッドに印加されたデータの伝達経路を制御するスイッチグ部;及び、

テストモード信号に応じて前記データ入出力パッドに印加されたデータを受信してメモリセルアレイに直接伝達する両方向アクセス制御部を含むことを特徴とする、半導体メモリ装置のためのテスト回路。

【請求項14】

前記両方向アクセス制御部は、前記テストモード信号に応じて前記データ入出力パッドに印加されたデータを、第1のローカル入出力ライン又は第2のローカル入出力ラインにスイッチングする経路設定部を含むことを特徴とする、請求項13に記載の半導体メモリ装置のためのテスト回路。

【請求項15】

前記経路設定部は、前記データ入出力パッドに印加されたデータを前記第1のローカル入出力ラインに伝達し、前記メモリセルアレイに第1のレベルのデータを書き込むことを特徴とする、請求項14に記載の半導体メモリ装置のためのテスト回路。

【請求項16】

前記経路設定部は、前記データ入出力パッドに印加されたデータを前記第2のローカル入出力ラインに伝達し、前記メモリセルアレイに第2のレベルのデータを書き込むことを特徴とする、請求項14に記載の半導体メモリ装置のためのテスト回路。

【請求項17】

前記経路設定部は、前記テストモード信号から生成された順方向テストモード信号により駆動され、前記データ入出力パッドに印加されたデータを前記第1のローカル入出力ラインに伝達又は遮断する第1の伝達素子と、前記テストモード信号から生成された逆方向テストモード信号により駆動され、前記第1のローカル入出力ライン及び接地端子間に接続される第2の伝達素子とを備える第1の経路設定部を含むことを特徴とする、請求項14に記載の半導体メモリ装置のテスト回路。

【請求項18】

前記経路設定部は、前記テストモード信号から生成された逆方向テストモード信号により駆動され、前記データ入出力パッドに印加されたデータを前記第2のローカル入出力ラインに伝達又は遮断する第3の伝達素子と、前記テストモード信号から生成された順方向テストモード信号により駆動され、前記第2のローカル入出力ライン及び接地端子間に接続される第4の伝達素子とを備える第2の経路設定部を含むことを特徴とする、請求項14に記載の半導体メモリ装置のテスト回路。

【請求項1】

複数のメモリセルを含むメモリセルアレイ;

データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;

ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、

テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含むことを特徴とする、半導体メモリ装置。

【請求項2】

前記コントローラは、前記テストモード信号に応じて前記データ入出力パッドから伝達されたデータを、第1のローカル入出力ラインを介して前記メモリセルアレイに提供する両方向アクセス制御部を含むことを特徴とする、請求項1に記載の半導体メモリ装置。

【請求項3】

前記両方向アクセス制御部は、前記テストモード信号に応じて前記データ入出力パッドから伝達されたデータを、第2のローカル入出力ラインを介して前記メモリセルアレイに提供することを特徴とする、請求項2に記載の半導体メモリ装置。

【請求項4】

前記スイッチング部は、前記データ入出力パッド及び前記ライトドライバ間、或いは、前記データ入出力パッド及び前記コントローラ間のグローバル入出力ライン上に接続されることを特徴とする、請求項3に記載の半導体メモリ装置。

【請求項5】

前記両方向アクセス制御部は、前記スイッチング部及び前記メモリセルアレイ間の前記第1のローカル入出力ライン及び第2のローカル入出力ライン上に接続されることを特徴とする、請求項3に記載の半導体メモリ装置。

【請求項6】

前記メモリセルは、電流駆動方式によりデータの読み出し/書き込みが行われることを特徴とする、請求項1乃至請求項5の何れか1項に記載の半導体メモリ装置。

【請求項7】

前記メモリセルは、抵抗性メモリセルであることを特徴とする、請求項1乃至請求項5の何れか1項に記載の半導体メモリ装置。

【請求項8】

ビットライン及びソースライン間に接続され、ワードラインに印加された電位により駆動される複数のメモリセルを含むメモリセルアレイ;及び、

テストモード信号に応じてデータ入出力パッドに印加されたデータを、前記メモリセルの前記ビットラインから前記ソースラインの方に直接伝達したり、前記データ入出力パッドに印加されたデータを、前記メモリセルの前記ソースラインから前記ビットラインの方に直接伝達する両方向アクセス制御部を含むことを特徴とする、半導体メモリ装置。

【請求項9】

ノーマルモード時、前記データ入出力パッドに印加されたデータを受信して駆動し、前記メモリセルアレイに書きこむライトドライバをさらに含むことを特徴とする、請求項8に記載の半導体メモリ装置。

【請求項10】

前記データ入出力パッドに接続され、前記テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を、前記両方向アクセス制御部又は前記ライトドライバの何れか一つに制御するスイッチング部をさらに含むことを特徴とする、請求項9に記載の半導体メモリ装置。

【請求項11】

前記メモリセルは、電流駆動方式によりデータの読み出し/書き込みが行われることを特徴とする、請求項8乃至請求項10の何れか1項に記載の半導体メモリ装置。

【請求項12】

前記メモリセルは、抵抗性メモリセルであることを特徴とする、請求項8乃至請求項10の何れか1項に記載の半導体メモリ装置。

【請求項13】

データ入出力パッドに印加されたデータの伝達経路を制御するスイッチグ部;及び、

テストモード信号に応じて前記データ入出力パッドに印加されたデータを受信してメモリセルアレイに直接伝達する両方向アクセス制御部を含むことを特徴とする、半導体メモリ装置のためのテスト回路。

【請求項14】

前記両方向アクセス制御部は、前記テストモード信号に応じて前記データ入出力パッドに印加されたデータを、第1のローカル入出力ライン又は第2のローカル入出力ラインにスイッチングする経路設定部を含むことを特徴とする、請求項13に記載の半導体メモリ装置のためのテスト回路。

【請求項15】

前記経路設定部は、前記データ入出力パッドに印加されたデータを前記第1のローカル入出力ラインに伝達し、前記メモリセルアレイに第1のレベルのデータを書き込むことを特徴とする、請求項14に記載の半導体メモリ装置のためのテスト回路。

【請求項16】

前記経路設定部は、前記データ入出力パッドに印加されたデータを前記第2のローカル入出力ラインに伝達し、前記メモリセルアレイに第2のレベルのデータを書き込むことを特徴とする、請求項14に記載の半導体メモリ装置のためのテスト回路。

【請求項17】

前記経路設定部は、前記テストモード信号から生成された順方向テストモード信号により駆動され、前記データ入出力パッドに印加されたデータを前記第1のローカル入出力ラインに伝達又は遮断する第1の伝達素子と、前記テストモード信号から生成された逆方向テストモード信号により駆動され、前記第1のローカル入出力ライン及び接地端子間に接続される第2の伝達素子とを備える第1の経路設定部を含むことを特徴とする、請求項14に記載の半導体メモリ装置のテスト回路。

【請求項18】

前記経路設定部は、前記テストモード信号から生成された逆方向テストモード信号により駆動され、前記データ入出力パッドに印加されたデータを前記第2のローカル入出力ラインに伝達又は遮断する第3の伝達素子と、前記テストモード信号から生成された順方向テストモード信号により駆動され、前記第2のローカル入出力ライン及び接地端子間に接続される第4の伝達素子とを備える第2の経路設定部を含むことを特徴とする、請求項14に記載の半導体メモリ装置のテスト回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−97852(P2013−97852A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2012−24875(P2012−24875)

【出願日】平成24年2月8日(2012.2.8)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成24年2月8日(2012.2.8)

【出願人】(310024033)エスケーハイニックス株式会社 (122)

【氏名又は名称原語表記】SK hynix Inc.

【住所又は居所原語表記】2091, Gyeongchung−daero,Bubal−eub,Icheon−si,Gyeonggi−do,Korea

【Fターム(参考)】

[ Back to top ]