半導体モジュールおよびその製造方法、ならびに携帯機器

【課題】半導体モジュールの実装信頼性を向上させる。

【解決手段】半導体モジュールは、配線領域20aとこれに接続された電極領域20bを含み、Cuからなる配線層20と、電極領域20bと半導体素子300の素子電極302とを電気的に接続し、Snを含むはんだボール40と、を備える。電極領域20bは、はんだボール40と接する側の主表面が粗面であり、はんだボール40と接する表層部分にCuとSnの合金を含む合金層30を有し、主表面の表面粗さRmaxが合金層30の層厚よりも大きい。

【解決手段】半導体モジュールは、配線領域20aとこれに接続された電極領域20bを含み、Cuからなる配線層20と、電極領域20bと半導体素子300の素子電極302とを電気的に接続し、Snを含むはんだボール40と、を備える。電極領域20bは、はんだボール40と接する側の主表面が粗面であり、はんだボール40と接する表層部分にCuとSnの合金を含む合金層30を有し、主表面の表面粗さRmaxが合金層30の層厚よりも大きい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体モジュールおよびその製造方法、ならびに携帯機器に関する。

【背景技術】

【0002】

携帯電話、PDA、DVC、DSCといったポータブルエレクトロニクス機器の高機能化が加速するなか、こうした製品が市場で受け入れられるためには小型・軽量化が必須となっており、その実現のために高集積のシステムLSIが求められている。一方、これらのエレクトロニクス機器に対しては、より使い易く便利なものが求められており、機器に使用されるLSIに対し、高機能化、高性能化が要求されている。このため、LSIチップの高集積化にともないそのI/O数が増大する一方でパッケージ自体の小型化要求も強く、これらを両立させるために、半導体部品の高密度な基板実装に適合した半導体パッケージの開発が強く求められている。こうした要求に対応するため、CSP(Chip Size Package)と呼ばれるパッケージ技術が種々開発されている。

【0003】

こうしたパッケージの例として、BGA(Ball Grid Array)が知られている。BGAは、パッケージ用基板(素子搭載用基板)の上に半導体チップ(半導体素子)を実装し、それを樹脂モールディングした後、反対側の面に外部端子としてはんだボールをエリア状に形成したものである。

【0004】

このようなBGA型の半導体モジュールは、一般に、基板の表面に設けられた配線層、およびこの配線層を保護するソルダーレジスト層を含むパッケージ用基板と、ソルダーレジスト層の開口部において露出した配線層の電極領域に電気的に接続されたはんだバンプとを備えている。

【0005】

特許文献1には、このような半導体モジュールに用いられるパッケージ用基板において、粗化面を有するはんだパッド用導電回路(配線層)上に防錆層を設け、防錆層上にソルダーレジスト層を設けた構成が開示されている。このように、はんだパッド用導電回路上に防錆層を設けたことで、はんだパッド導電回路の変質が防止されるため、ソルダーレジスト層との密着性に優れた粗化面形状を保持することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−315854号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述のパッケージ用基板において、一般に、配線層は銅(Cu)からなる。また、半導体チップをパッケージ用基板に接続するためのはんだバンプは、スズ(Sn)を含む合金からなる。そのため、配線層の電極領域にはんだバンプを介して半導体チップが搭載されると、配線層におけるはんだバンプとの接続領域に、配線層のCuとはんだのSnとの合金からなる合金層が形成される。また、半導体モジュールを実装基板に接続するためのはんだバンプと配線層との間にも、同様の合金層が形成される。このCuとSnの合金は比較的脆いため、合金層にクラックが発生しやすいという問題があった。そして、この問題は、素子搭載用基板と半導体素子との接続信頼性や素子搭載用基板と実装基板との接続信頼性を向上させ、ひいては半導体モジュールの実装信頼性を向上させる上で大きな障害となっていた。

【0008】

本発明は上記事情に鑑みなされたものであって、その目的とするところは、半導体モジュールの実装信頼性を向上させる技術を提供することにある。

【課題を解決するための手段】

【0009】

本発明のある態様は、半導体モジュールである。当該半導体モジュールは、配線領域とこれに接続された電極領域を含み、Cuからなる配線層と、電極領域と被接続端子とを電気的に接続し、Snを含む接続部材と、を備え、電極領域は、接続部材と接する側の主表面が粗面であり、接続部材と接する表層部分にCuとSnの合金を含む合金層を有し、主表面の表面粗さRmaxが合金層の層厚よりも大きいことを特徴とする。

【0010】

この態様によれば、半導体モジュールの実装信頼性を向上させることができる。

【0011】

上記態様において、接続部材は、配線層の主表面に平行な方向で、合金層を挟んで電極領域における合金層の下方に位置する下層部と対向する部分を有してもよい。また、上記態様において、電極領域の粗面の凸部は、その頂面が配線領域の主表面と略面一な平面であってもよい。また、上記態様において、被接続端子は、半導体素子の素子電極であり、半導体素子が配線層にフリップチップ接続されてもよい。

【0012】

本発明の他の態様は携帯機器である。当該携帯機器は、上述したいずれかの態様の半導体モジュールを搭載したことを特徴とする。

【0013】

本発明のさらに他の態様は、半導体モジュールの製造方法である。当該半導体モジュールの製造方法は、一方の主表面にCuからなる金属層が設けられた基材を用意する工程と、金属層における、配線領域および電極領域を含む配線層の形成予定領域を被覆するマスクであって、電極領域の形成予定領域に対応する部分に複数の貫通孔が設けられたマスクを金属層の上に形成する工程と、マスクを用いて金属層を選択的に除去して配線層を形成するとともに、電極領域の主表面に粗化処理を施す工程と、電極領域にSnを含む接続部材を搭載するとともに溶融し、当該接続部材を介して電極領域と被接続端子とを電気的に接続する工程と、を含むことを特徴とする。

【0014】

上記態様において、接続部材を溶融した際に、電極領域の接続部材と接する表層部分に配線層のCuと接続部材のSnとの合金を含む合金層が形成され、粗化処理を施す工程において、電極領域の主表面の表面粗さRmaxが合金層の層厚よりも大きくなるように、電極領域の主表面を粗化してもよい。また、上記態様において、マスクに設けられた複数の貫通孔は、それぞれの間隔が合金層の層厚の2倍以上となるように設定されてもよい。

【発明の効果】

【0015】

本発明によれば、半導体モジュールの実装信頼性を向上させることができる。

【図面の簡単な説明】

【0016】

【図1】実施形態1に係る半導体モジュールの構成を示す概略断面図である。

【図2】図1に示したX領域の拡大断面図である。

【図3】図2における配線層とはんだボールの接続部分周囲の構造を示す拡大断面図である。

【図4】図4(A)〜(D)は、半導体モジュールの製造方法を示す工程断面図である。

【図5】図5(A)、(B)は、半導体モジュールの製造方法を示す工程断面図である。

【図6】レジストの部分概略平面図である。

【図7】実施形態2に係る携帯電話の構成を示す図である。

【図8】図7に示した携帯電話の部分断面図である。

【図9】変形例に係る半導体モジュールの構成を示す概略断面図である。

【発明を実施するための形態】

【0017】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0018】

(実施形態1)

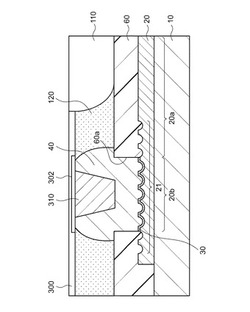

図1は、実施形態1に係る半導体モジュールの構成を示す概略断面図である。また、図2は、図1に示したX領域の拡大断面図である。図1に示すように、本実施形態に係る半導体モジュール1は、素子搭載用基板100に、半導体素子300がフリップチップ接続された構成を有する。

【0019】

素子搭載用基板100は、基材10と、配線層20と、下面側配線層50と、はんだボール40,42と、絶縁層60と、下面側絶縁層62と、を備える。また、素子搭載用基板100は、合金層30を備える(図2参照)。

【0020】

基材10は、コア基材として機能する。基材10は、例えば、BTレジン等のメラミン誘導体、液晶ポリマー、エポキシ樹脂、PPE樹脂、ポリイミド樹脂、フッ素樹脂、フェノール樹脂、ポリアミドビスマレイミド等の熱硬化性樹脂で形成することができる。また、素子搭載用基板100の放熱性向上の観点から、基材10は高熱伝導性を有することが望ましい。このため、基材10は、銀、ビスマス、銅、アルミニウム、マグネシウム、錫、亜鉛、およびこれらの合金や、シリカ、アルミナ、窒化ケイ素、窒化アルミニウムなどを高熱伝導性フィラーとして含有することが好ましい。基材10の厚さは、例えば約100μmである。

【0021】

配線層20は、所定パターンを有し、基材10の一方の主表面(本実施形態では、半導体素子300の搭載面側)に設けられている。配線層20は、銅(Cu)からなり、配線領域20aとこの配線領域20aに接続された電極領域20b(ランド領域ともいう)とを含む。配線領域20aは、回路配線の引き回しなどを行うためのものであり、電極領域20bは、配線層20と半導体素子300との接続に用いられる。電極領域20bは、はんだボール40との密着性を高めるために、はんだボール40と接する側の主表面が粗面である。本実施形態では、電極領域20bと配線領域20aの一部とを含むように、配線層20に粗面領域21が設けられている(図2参照)。配線層20の厚さは、例えば約10〜25μmである。

【0022】

また、電極領域20bは、はんだボール40と接する表層部分に合金層30(図2参照)を有する。合金層30は、配線層20に搭載したはんだボール40をリフローにより溶融させた際に形成される。リフロー処理を実施すると、マイグレーション現象によりはんだボール40のSnが配線層20に移動し、はんだボール40のSnと配線層20のCuとが反応して、CuとSnの合金であるCuSn合金を含む合金層30が形成される。したがって、合金層30は、はんだボール40のバルクよりもCu濃度が高く、かつ配線層20のバルクよりもSn濃度が高い部分と定義することができる。合金層30は、電極領域20bの、はんだボール40と接する側の表層に形成されるため、その表面は当然に粗面領域21の凹凸に対応した粗面となっている。

【0023】

下面側配線層50(配線層)は、所定パターンを有し、基材10の他方の主表面に設けられている。下面側配線層50は、銅(Cu)からなり、配線層20と同様に、配線領域50aとこの配線領域50aに接続された電極領域50bとを含む。下面側配線層50の厚さは、例えば約10〜25μmである。

【0024】

基材10の所定位置には、基材10を貫通するビア導体52が設けられている。ビア導体52は、例えば、銅めっきにより形成される。ビア導体52により、配線層20と下面側配線層50とが電気的に接続されている。

【0025】

絶縁層60は、配線層20の電極領域20bの周囲に設けられている。本実施形態では、絶縁層60は、配線層20を覆うように基材10の一方の主表面に設けられており、絶縁層60によって配線層20の酸化などが防止される。また、絶縁層60には電極領域20bが露出するように開口部60aが形成されている。絶縁層60は、例えばフォトソルダーレジストにより形成され、その厚さは、例えば約20〜50μmである。絶縁層60の開口部60aの径は、約0.1〜0.2mmである。

【0026】

下面側絶縁層62は、下面側配線層50を覆うように基材10の他方の主表面に設けられており、下面側絶縁層62によって下面側配線層50の酸化などが防止される。下面側絶縁層62には、下面側配線層50の電極領域50bが露出するように下面側開口部62aが形成されている。下面側絶縁層62は、例えばフォトソルダーレジストにより形成され、その厚さは、例えば約20〜50μmである。下面側開口部62aの径は、約0.15〜1.0mmである。

【0027】

はんだボール40は、絶縁層60の開口部60a内にて配線層20の電極領域20bに接続されている。はんだボール40は、スズ(Sn)を含むはんだからなり、例えば鉛(Pb)を含まない、いわゆる鉛フリーはんだからなる。はんだボール40を形成するはんだの例としては、Sn−3.0Ag−0.5Cu系はんだを挙げることができる。はんだボール40は、半導体素子300の素子電極302(図2参照)(被接続端子)と、配線層20の電極領域20bとを電気的に接続する接続部材としての役割を果たす。

【0028】

はんだボール42は、下面側絶縁層62の下面側開口部62a内にて下面側配線層50の電極領域50bに接続されている。はんだボール42は、はんだボール40と同様の材質を有する。はんだボール42は、マザーボードやプリント基板のような実装基板の接続端子(被接続端子)と、下面側配線層50の電極領域とを電気的に接続する接続部材としての役割を果たす。はんだボール42によって、半導体モジュール1が図示しない実装基板に電気的に接続される。

【0029】

このような構成を備えた素子搭載用基板100に半導体素子300が搭載されて、半導体モジュール1が形成される。本実施形態に係る半導体モジュール1では、半導体素子300が素子搭載用基板100にフリップチップ接続されている。具体的には、金(Au)などからなる導電性バンプ310が形成された半導体素子300の電極形成面がフェイスダウンされ、導電性バンプ310がはんだボール40を介して配線層20に電気的に接続されている。

【0030】

半導体素子300の電極形成面には、アルミニウム(Al)などからなる素子電極302が形成されており、素子電極302の表面に導電性バンプ310が設けられている。半導体素子300の具体例としては、集積回路(IC)、大規模集積回路(LSI)などの半導体チップが挙げられる。半導体素子300と絶縁層60との間には、エポキシ樹脂から成るアンダーフィル120が充填されている。

【0031】

封止樹脂110は、素子搭載用基板100の上面と半導体素子300とを封止している。封止樹脂110は、例えばエポキシ樹脂を用いて、トランスファーモールド法により形成される。

【0032】

続いて、図3を用いて配線層20とはんだボール40の接続構造について詳細に説明する。図3は、図2における配線層とはんだボールの接続部分周囲の構造を示す拡大断面図である。

【0033】

図3に示すように、配線層20の電極領域20bと配線領域20aの一部とには、粗面領域21が設けられている。粗面領域21は、電極領域20bの主表面の表面粗さRmaxが合金層30の層厚よりも大きくなるように設定されている。配線層20の表面粗さは、触針式表面形状測定器で計測するか、あるいは、断面SEM(走査電子顕微鏡)像などから計測することができる。本実施形態では、例えば、開口部60aの径が約0.2mmであった場合、電極領域20bの主表面の表面粗さRmaxは開口部60a内の約0.2mmφの範囲で測定され、その値は約5μmである。また、合金層30の層厚は約1〜3μmである。ここで、前記「合金層30の層厚」は、例えば、合金層30の平均厚さである。このように、電極領域20bの表面粗さRmaxが合金層30の層厚よりも大きくなるように粗面領域21が形成されているため、合金層30は、配線層20の主表面に直交する断面形状が蛇行した形状となる。

【0034】

上述のように、合金層30は、配線層20のCuとはんだボール40のSnとで形成されるCuSn合金を含む。このCuSn合金はCuやSnと比べて脆いため、配線層20やはんだボール40と比べて合金層30にはクラック(亀裂)が発生しやすい。そのため、電極領域20bに粗面領域21が設けられておらず、合金層30の断面形状が配線層20の主表面に平行に延びる直線形状であった場合には、合金層30に発生したクラックが配線層20に平行な方向に進行しやすく、そのため発生したクラックが大きくなってしまう可能性が高かった。これに対し、合金層30の断面形状が蛇行形状である場合には、CuSn合金よりも剛性の高いCuからなり、電極領域20bにおける合金層30の下方に位置する下層部22と、CuSn合金よりも剛性の高いSnを合金層30よりも高い割合で含むはんだボール40とが、あたかも合金層30に陥入したような形状となる。したがって、下層部22またははんだボール40によって、合金層30に発生したクラックの平行方向への進行を阻止することができる。これにより、合金層30に発生したクラックが大きくなることを回避することができ、その結果、素子搭載用基板100と半導体素子300との接続信頼性が向上して、半導体モジュール1の実装信頼性が向上する。

【0035】

ここで、はんだボール40は、配線層20の主表面に平行な方向で、合金層30を挟んで下層部22と対向する部分を有していてもよい。すなわち、はんだボール40のうち、電極領域20bの主表面の凹部32に進入した部分と、下層部22のはんだボール40側に突出した凸部24とが、配線層20の主表面に平行な方向(図3における左右方向)で合金層30を挟んで対向していてもよい。この場合には、合金層30に発生したクラックの大型化をより確実に阻止することができる。

【0036】

また、電極領域20bの粗面の凸部34は、その頂面が配線領域20aの絶縁層60側の主表面と略面一な平面であってもよい。この場合には、凸部34の両側面の合金層30同士が接触するのを回避できるため、凸部34における合金層30の厚さを他の領域の厚さと等しくすることができ、したがって合金層30の層厚を均一にすることができる。その結果、クラックの発生が合金層30の特定箇所に集中するのを防ぐことができる。この場合、凸部34の頂面は、配線層20の主表面と直交する断面で、その幅が合金層30の層厚の約2倍以上であることが好ましい。この場合には、より確実に合金層30の厚さを均一にすることができる。さらに、合金層30と下層部22との界面における凸部24の頂面が、配線層20の主表面と略平行な平面であってもよい。この場合にも、合金層30の凸部34において、凸部34の両側の合金層30同士が接触するのを回避できるため、凸部34における合金層30の厚さを均一にすることができる。

【0037】

(素子搭載用基板および半導体モジュールの製造方法)

実施形態1に係る半導体モジュール1の製造方法について図4および図5を参照して説明する。図4(A)〜(D)、図5(A)、(B)は、半導体モジュールの製造方法を示す工程断面図である。

【0038】

まず、図4(A)に示すように、一方の主表面に銅箔25が貼り付けられた基材10を用意する。銅箔25は、配線層20の厚さ以上の厚さを有する。なお、図1に示したように、基材10にはビア導体52が設けられているが、このビア導体52は従来公知の方法で形成することができるため、その説明は省略する。

【0039】

次に、図4(B)に示すように、フォトリソグラフィ法により、銅箔25の主表面に、配線領域20aおよび電極領域20bを含む配線層20(図2参照)の形成予定領域に対応したパターンに合わせてレジスト200(マスク)を選択的に形成する。具体的には、ラミネーター装置を用いて銅箔25に所定膜厚のレジスト膜を貼り付け、配線層20のパターンを有するフォトマスクを用いて露光した後、現像することによって、銅箔25の上にレジスト200が選択的に形成される。なお、レジストとの密着性向上のために、レジスト膜のラミネート前に、銅箔25の表面に研磨、洗浄等の前処理を必要に応じて施すことが望ましい。

【0040】

ここで、レジスト200には、複数の貫通孔200aが設けられている。この複数の貫通孔200aは、レジスト200の部分概略平面図である図6に示すように、電極領域20bあるいは絶縁層60の開口部60a(図2参照)に対応するA領域内と、その周囲に設けられている。

【0041】

次に、図4(C)に示すように、レジスト200をマスクとして塩化第二鉄溶液などの薬液を用いたウェットエッチング処理を行うことにより、銅箔25を選択的に除去して配線領域20aおよび電極領域20bを含む配線層20を形成する。このとき、貫通孔200a内にも薬液が進入するため、銅箔25のうち貫通孔200aによって露出した部分もエッチングされる。ここで、貫通孔200a内では、他の領域に比べて薬液の循環効率が低いため、他の領域に比べて薬液による銅箔25の侵食速度が遅くなる。そのため、銅箔25のうち貫通孔200aによって露出した部分は、配線層20のパターニング時に基材10側まで侵食されない。その結果、配線層20の電極領域20bの表面には、貫通孔200aに対応する凹部32とその間の凸部34(図3参照)とが形成された状態となる。凸部34の頂部は、配線層20の配線領域20aの主表面と略同じ高さとなる。このようにして、配線層20の電極領域20bの表面に粗化処理が施される。この方法によれば、配線層20の形成と電極領域20b表面の粗化とを一括して実施することができる。配線層20を形成した後、レジスト200を、剥離剤を用いて剥離する。

【0042】

次に、図4(D)に示すように、基材10の一方の主表面にフォトソルダーレジストを積層した後、周知のフォトリソグラフィ法を用いて、配線層20の電極領域20bが露出するような開口部60aを有する絶縁層60を形成する。本実施形態では、レジスト200の貫通孔200aが電極領域20bに対応する領域の周囲にまで設けられている。そのため、配線領域20aのうち電極領域20bに隣接する領域にも粗化処理が施されて、当該領域の表面に凹凸が形成されている。これにより、電極領域20bの周囲において、絶縁層60と配線層20との接触面積が増大して、両者の密着性が向上する。したがって、配線層20と絶縁層60とが剥離する可能性を低減することができる。

【0043】

次に、図5(A)に示すように、絶縁層60の開口部60aにおいて、例えばスクリーン印刷法により、配線層20の電極領域20bにはんだボール40を搭載する。具体的には、樹脂とはんだ材をペースト状にしたはんだペーストをスクリーンマスクにより所望の箇所に印刷してはんだボール40を形成する。そして、素子電極302に導電性バンプ310が設けられた半導体素子300を素子搭載用基板100上に搭載し、リフロー工程によりはんだボール40を溶融して、導電性バンプ310とはんだボール40とを接合することで、はんだボール40を介して電極領域20bと素子電極302とを電気的に接続する。配線層20の電極領域20bと半導体素子300の素子電極302とを電気的に接続するリフロー工程では、はんだボール40に含まれるSnが配線層20側に移動して、配線層20のCuとはんだボール40のSnとが反応し、電極領域20bにCuとSnとの合金を含む合金層30が形成される。

【0044】

本実施形態では、電極領域20bの主表面のRmaxが合金層30の厚さよりも大きくなるように電極領域20bの主表面が粗化される。これにより、配線層20の主表面に直交する断面に現れる合金層30の形状を蛇行形状とすることができる。また、レジスト200に設けられた複数の貫通孔200aは、粗化処理によって電極領域20bに形成される凸部34の頂面が平面となるように、それぞれの間隔を設定することができる。これにより、凸部34の両側面の合金層30同士が接触するのを回避できるため、合金層30の厚さを均一にすることができる。また、複数の貫通孔200aは、それぞれの間隔が合金層30の層厚の約2倍以上となるように設定されることが好ましい。この場合には、より確実に凸部34の両側面の合金層30同士が接触するのを回避することができる。

【0045】

図示は省略するが、上述の各工程と同様にして、下面側配線層50と、下面側絶縁層62と、はんだボール42とが形成される。以上の工程により、素子搭載用基板100が製造される。

【0046】

続いて、図5(B)に示すように、半導体素子300と絶縁層60との間にアンダーフィル120が充填され、半導体素子300が封止樹脂110によって封止される。以上の工程により、実施形態1に係る半導体モジュール1を製造することができる。

【0047】

以上説明したように、実施形態1に係る半導体モジュール1は、Cuからなる電極領域20bの主表面が粗面であり、電極領域20bのはんだボール40と接する表層部分にはCuSn合金を含む合金層30が設けられている。そして、電極領域20bの主表面の表面粗さRmaxが合金層30の層厚よりも大きい。そのため、合金層30は、配線層20の主表面に直交する断面形状が蛇行形状となる。これにより、合金層30に発生したクラックの配線層20に平行な方向への進行を防ぐことができるため、クラックが大きくなることを回避することができる。また、合金層30に生じるクラックの長さが同じであった場合、合金層30が平坦面形状である場合よりも凹凸を有する形状である場合の方が、配線層20の主表面に平行な方向のクラック長さが短くなる。そのため、素子搭載用基板100と半導体素子300との接続信頼性を向上させることができ、ひいては半導体モジュール1の実装信頼性を向上させることができる。

【0048】

また、電極領域20bの表面にNi/Au層などの金めっき層を設けることで素子搭載用基板100と半導体素子300との接続信頼性を向上させる場合と比べて、より安価な構成で両者の接続信頼性の向上を図ることができる。

【0049】

また、はんだボール40は、配線層20の主表面に平行な方向で、合金層30を挟んで下層部22と対向する部分を有してもよい。この場合には、合金層30に発生したクラックが水平方向に進行するのをより確実に阻止することができるため、合金層30に発生したクラックの大型化をより確実に阻止することができる。また、電極領域20bの粗面の凸部34は、その頂面が配線領域20aの主表面と略面一な平面であってもよい。この場合には、凸部34における合金層30の厚さを他の領域の厚さと等しくすることができるため、合金層30の層厚を均一にすることができる。そして、これにより、クラックの発生が合金層30の特定箇所に集中するのを防ぐことができるため、素子搭載用基板100と半導体素子300との接続信頼性をさらに向上させることができる。

【0050】

さらに、本実施形態では、電極領域20bの形成予定領域に対応する部分に貫通孔200aが設けられたレジスト200を用いて配線層20を形成している。そのため、レジスト200の形成と同時に電極領域20bの粗化処理を実施することができるため、製造工程数の増大を回避することができる。

【0051】

(実施形態2)

次に、上述の実施形態1に係る半導体モジュール1を備えた携帯機器について説明する。なお、携帯機器として携帯電話に搭載する例を示すが、たとえば、個人用携帯情報端末(PDA)、デジタルビデオカメラ(DVC)、及びデジタルスチルカメラ(DSC)といった電子機器であってもよい。

【0052】

図7は実施形態2に係る携帯電話の構成を示す図である。携帯電話1111は、第1の筐体1112と第2の筐体1114が可動部1120によって連結される構造になっている。第1の筐体1112と第2の筐体1114は可動部1120を軸として回動可能である。第1の筐体1112には文字や画像等の情報を表示する表示部1118やスピーカ部1124が設けられている。第2の筐体1114には操作用ボタンなどの操作部1122やマイク部1126が設けられている。実施形態1に係る半導体モジュール1はこうした携帯電話1111の内部に搭載されている。

【0053】

図8は図7に示した携帯電話の部分断面図(第1の筐体1112の断面図)である。上述の実施形態1に係る半導体モジュール1は、はんだボール42を介してプリント基板1128に搭載され、こうしたプリント基板1128を介して表示部1118などと電気的に接続されている。また、半導体モジュール1の裏面側(はんだボール42とは反対側の面)には金属基板などの放熱基板1116が設けられ、たとえば、半導体モジュール1から発生する熱を第1の筐体1112内部に篭もらせることなく、効率的に第1の筐体1112の外部に放熱することができるようになっている。

【0054】

本発明の実施形態1に係る半導体モジュール1によれば、素子搭載用基板100と半導体素子300との接続信頼性を高めることができ、したがって半導体モジュール1の実装信頼性を高めることができる。そのため、こうした半導体モジュール1を搭載した本実施形態に係る携帯機器について、動作信頼性の向上を図ることができる。また、実施形態1で示したCSPプロセスにより製造された半導体モジュール1は薄型化・小型化されるので、こうした半導体モジュール1を搭載した携帯機器の薄型化・小型化を図ることができる。

【0055】

本発明は、上述の実施形態に限定されるものではなく、当業者の知識に基づいて各種の設計変更等の変形を加えることも可能であり、そのような変形が加えられた実施の形態も本発明の範囲に含まれうるものである。

【0056】

例えば、実施形態1では、素子搭載用基板100上に設けた配線層20の電極領域20bとはんだボール40との接続構造を例としたが、本発明はこれに限られない。例えば、半導体モジュール1(電子部品)と実装基板の接続に用いられるはんだボール42と、下面側配線層50の電極領域50bとの接続構造に実施形態1の接続構造を適用することができる。すなわち、電極領域50bは、はんだボール42と接する側の主表面が粗面であり、はんだボール42と接する表層部分にCuとSnの合金を含む合金層を有し、主表面の表面粗さRmaxが合金層の層厚よりも大きくなるように設定されている。このような場合にも、実施形態1の効果を享受することができる。なお、例えば下面側開口部62aの径が1.0mmであった場合、電極領域20bの表面粗さRmaxは、下面側開口部62a内の約1.0mmφの範囲で測定される。

【0057】

また、半導体モジュール1は、図9に示すような構造であってもよい。図9は、変形例に係る半導体モジュールの構成を示す概略断面図である。図9に示す変形例に係る半導体モジュール1と、実施形態1に係る半導体モジュール1との主な相違点は、変形例に係る半導体モジュール1の素子搭載用基板100が基材と下面側配線層50とを有さず、配線層20(リードフレーム)の裏面側にはんだボール42が直接搭載されている点である。この場合には、配線層20とはんだボール42との接続構造に、実施形態1の接続構造が適用される。また、他の相違点として、変形例に係る半導体モジュール1では、半導体素子300がフィルム接着剤130を介して配線層20の主表面に固定されており、また、半導体素子300の素子電極と配線層20の電極領域20bとが金線320によりワイヤボンディング接続されている。配線層20の半導体素子300側には封止樹脂110が積層され、配線層20のはんだボール42が搭載された側には下面側絶縁層62が積層されている。

【0058】

さらに、はんだボール42と実装基板側の接続端子との接続構造、あるいは、半導体素子300の素子電極302とはんだボール40との接続構造に実施形態1の接続構造を適用してもよい。これらの場合にも、上述の効果を享受することができる。

【符号の説明】

【0059】

1 半導体モジュール、 10 基材、 20 配線層、 20a 配線領域、 20b 電極領域、 21 粗面領域、 30 合金層、 40,42 はんだボール、 50 下面側配線層、 50a 配線領域、 50b 電極領域、 100 素子搭載用基板、 300 半導体素子。

【技術分野】

【0001】

本発明は、半導体モジュールおよびその製造方法、ならびに携帯機器に関する。

【背景技術】

【0002】

携帯電話、PDA、DVC、DSCといったポータブルエレクトロニクス機器の高機能化が加速するなか、こうした製品が市場で受け入れられるためには小型・軽量化が必須となっており、その実現のために高集積のシステムLSIが求められている。一方、これらのエレクトロニクス機器に対しては、より使い易く便利なものが求められており、機器に使用されるLSIに対し、高機能化、高性能化が要求されている。このため、LSIチップの高集積化にともないそのI/O数が増大する一方でパッケージ自体の小型化要求も強く、これらを両立させるために、半導体部品の高密度な基板実装に適合した半導体パッケージの開発が強く求められている。こうした要求に対応するため、CSP(Chip Size Package)と呼ばれるパッケージ技術が種々開発されている。

【0003】

こうしたパッケージの例として、BGA(Ball Grid Array)が知られている。BGAは、パッケージ用基板(素子搭載用基板)の上に半導体チップ(半導体素子)を実装し、それを樹脂モールディングした後、反対側の面に外部端子としてはんだボールをエリア状に形成したものである。

【0004】

このようなBGA型の半導体モジュールは、一般に、基板の表面に設けられた配線層、およびこの配線層を保護するソルダーレジスト層を含むパッケージ用基板と、ソルダーレジスト層の開口部において露出した配線層の電極領域に電気的に接続されたはんだバンプとを備えている。

【0005】

特許文献1には、このような半導体モジュールに用いられるパッケージ用基板において、粗化面を有するはんだパッド用導電回路(配線層)上に防錆層を設け、防錆層上にソルダーレジスト層を設けた構成が開示されている。このように、はんだパッド用導電回路上に防錆層を設けたことで、はんだパッド導電回路の変質が防止されるため、ソルダーレジスト層との密着性に優れた粗化面形状を保持することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2000−315854号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述のパッケージ用基板において、一般に、配線層は銅(Cu)からなる。また、半導体チップをパッケージ用基板に接続するためのはんだバンプは、スズ(Sn)を含む合金からなる。そのため、配線層の電極領域にはんだバンプを介して半導体チップが搭載されると、配線層におけるはんだバンプとの接続領域に、配線層のCuとはんだのSnとの合金からなる合金層が形成される。また、半導体モジュールを実装基板に接続するためのはんだバンプと配線層との間にも、同様の合金層が形成される。このCuとSnの合金は比較的脆いため、合金層にクラックが発生しやすいという問題があった。そして、この問題は、素子搭載用基板と半導体素子との接続信頼性や素子搭載用基板と実装基板との接続信頼性を向上させ、ひいては半導体モジュールの実装信頼性を向上させる上で大きな障害となっていた。

【0008】

本発明は上記事情に鑑みなされたものであって、その目的とするところは、半導体モジュールの実装信頼性を向上させる技術を提供することにある。

【課題を解決するための手段】

【0009】

本発明のある態様は、半導体モジュールである。当該半導体モジュールは、配線領域とこれに接続された電極領域を含み、Cuからなる配線層と、電極領域と被接続端子とを電気的に接続し、Snを含む接続部材と、を備え、電極領域は、接続部材と接する側の主表面が粗面であり、接続部材と接する表層部分にCuとSnの合金を含む合金層を有し、主表面の表面粗さRmaxが合金層の層厚よりも大きいことを特徴とする。

【0010】

この態様によれば、半導体モジュールの実装信頼性を向上させることができる。

【0011】

上記態様において、接続部材は、配線層の主表面に平行な方向で、合金層を挟んで電極領域における合金層の下方に位置する下層部と対向する部分を有してもよい。また、上記態様において、電極領域の粗面の凸部は、その頂面が配線領域の主表面と略面一な平面であってもよい。また、上記態様において、被接続端子は、半導体素子の素子電極であり、半導体素子が配線層にフリップチップ接続されてもよい。

【0012】

本発明の他の態様は携帯機器である。当該携帯機器は、上述したいずれかの態様の半導体モジュールを搭載したことを特徴とする。

【0013】

本発明のさらに他の態様は、半導体モジュールの製造方法である。当該半導体モジュールの製造方法は、一方の主表面にCuからなる金属層が設けられた基材を用意する工程と、金属層における、配線領域および電極領域を含む配線層の形成予定領域を被覆するマスクであって、電極領域の形成予定領域に対応する部分に複数の貫通孔が設けられたマスクを金属層の上に形成する工程と、マスクを用いて金属層を選択的に除去して配線層を形成するとともに、電極領域の主表面に粗化処理を施す工程と、電極領域にSnを含む接続部材を搭載するとともに溶融し、当該接続部材を介して電極領域と被接続端子とを電気的に接続する工程と、を含むことを特徴とする。

【0014】

上記態様において、接続部材を溶融した際に、電極領域の接続部材と接する表層部分に配線層のCuと接続部材のSnとの合金を含む合金層が形成され、粗化処理を施す工程において、電極領域の主表面の表面粗さRmaxが合金層の層厚よりも大きくなるように、電極領域の主表面を粗化してもよい。また、上記態様において、マスクに設けられた複数の貫通孔は、それぞれの間隔が合金層の層厚の2倍以上となるように設定されてもよい。

【発明の効果】

【0015】

本発明によれば、半導体モジュールの実装信頼性を向上させることができる。

【図面の簡単な説明】

【0016】

【図1】実施形態1に係る半導体モジュールの構成を示す概略断面図である。

【図2】図1に示したX領域の拡大断面図である。

【図3】図2における配線層とはんだボールの接続部分周囲の構造を示す拡大断面図である。

【図4】図4(A)〜(D)は、半導体モジュールの製造方法を示す工程断面図である。

【図5】図5(A)、(B)は、半導体モジュールの製造方法を示す工程断面図である。

【図6】レジストの部分概略平面図である。

【図7】実施形態2に係る携帯電話の構成を示す図である。

【図8】図7に示した携帯電話の部分断面図である。

【図9】変形例に係る半導体モジュールの構成を示す概略断面図である。

【発明を実施するための形態】

【0017】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0018】

(実施形態1)

図1は、実施形態1に係る半導体モジュールの構成を示す概略断面図である。また、図2は、図1に示したX領域の拡大断面図である。図1に示すように、本実施形態に係る半導体モジュール1は、素子搭載用基板100に、半導体素子300がフリップチップ接続された構成を有する。

【0019】

素子搭載用基板100は、基材10と、配線層20と、下面側配線層50と、はんだボール40,42と、絶縁層60と、下面側絶縁層62と、を備える。また、素子搭載用基板100は、合金層30を備える(図2参照)。

【0020】

基材10は、コア基材として機能する。基材10は、例えば、BTレジン等のメラミン誘導体、液晶ポリマー、エポキシ樹脂、PPE樹脂、ポリイミド樹脂、フッ素樹脂、フェノール樹脂、ポリアミドビスマレイミド等の熱硬化性樹脂で形成することができる。また、素子搭載用基板100の放熱性向上の観点から、基材10は高熱伝導性を有することが望ましい。このため、基材10は、銀、ビスマス、銅、アルミニウム、マグネシウム、錫、亜鉛、およびこれらの合金や、シリカ、アルミナ、窒化ケイ素、窒化アルミニウムなどを高熱伝導性フィラーとして含有することが好ましい。基材10の厚さは、例えば約100μmである。

【0021】

配線層20は、所定パターンを有し、基材10の一方の主表面(本実施形態では、半導体素子300の搭載面側)に設けられている。配線層20は、銅(Cu)からなり、配線領域20aとこの配線領域20aに接続された電極領域20b(ランド領域ともいう)とを含む。配線領域20aは、回路配線の引き回しなどを行うためのものであり、電極領域20bは、配線層20と半導体素子300との接続に用いられる。電極領域20bは、はんだボール40との密着性を高めるために、はんだボール40と接する側の主表面が粗面である。本実施形態では、電極領域20bと配線領域20aの一部とを含むように、配線層20に粗面領域21が設けられている(図2参照)。配線層20の厚さは、例えば約10〜25μmである。

【0022】

また、電極領域20bは、はんだボール40と接する表層部分に合金層30(図2参照)を有する。合金層30は、配線層20に搭載したはんだボール40をリフローにより溶融させた際に形成される。リフロー処理を実施すると、マイグレーション現象によりはんだボール40のSnが配線層20に移動し、はんだボール40のSnと配線層20のCuとが反応して、CuとSnの合金であるCuSn合金を含む合金層30が形成される。したがって、合金層30は、はんだボール40のバルクよりもCu濃度が高く、かつ配線層20のバルクよりもSn濃度が高い部分と定義することができる。合金層30は、電極領域20bの、はんだボール40と接する側の表層に形成されるため、その表面は当然に粗面領域21の凹凸に対応した粗面となっている。

【0023】

下面側配線層50(配線層)は、所定パターンを有し、基材10の他方の主表面に設けられている。下面側配線層50は、銅(Cu)からなり、配線層20と同様に、配線領域50aとこの配線領域50aに接続された電極領域50bとを含む。下面側配線層50の厚さは、例えば約10〜25μmである。

【0024】

基材10の所定位置には、基材10を貫通するビア導体52が設けられている。ビア導体52は、例えば、銅めっきにより形成される。ビア導体52により、配線層20と下面側配線層50とが電気的に接続されている。

【0025】

絶縁層60は、配線層20の電極領域20bの周囲に設けられている。本実施形態では、絶縁層60は、配線層20を覆うように基材10の一方の主表面に設けられており、絶縁層60によって配線層20の酸化などが防止される。また、絶縁層60には電極領域20bが露出するように開口部60aが形成されている。絶縁層60は、例えばフォトソルダーレジストにより形成され、その厚さは、例えば約20〜50μmである。絶縁層60の開口部60aの径は、約0.1〜0.2mmである。

【0026】

下面側絶縁層62は、下面側配線層50を覆うように基材10の他方の主表面に設けられており、下面側絶縁層62によって下面側配線層50の酸化などが防止される。下面側絶縁層62には、下面側配線層50の電極領域50bが露出するように下面側開口部62aが形成されている。下面側絶縁層62は、例えばフォトソルダーレジストにより形成され、その厚さは、例えば約20〜50μmである。下面側開口部62aの径は、約0.15〜1.0mmである。

【0027】

はんだボール40は、絶縁層60の開口部60a内にて配線層20の電極領域20bに接続されている。はんだボール40は、スズ(Sn)を含むはんだからなり、例えば鉛(Pb)を含まない、いわゆる鉛フリーはんだからなる。はんだボール40を形成するはんだの例としては、Sn−3.0Ag−0.5Cu系はんだを挙げることができる。はんだボール40は、半導体素子300の素子電極302(図2参照)(被接続端子)と、配線層20の電極領域20bとを電気的に接続する接続部材としての役割を果たす。

【0028】

はんだボール42は、下面側絶縁層62の下面側開口部62a内にて下面側配線層50の電極領域50bに接続されている。はんだボール42は、はんだボール40と同様の材質を有する。はんだボール42は、マザーボードやプリント基板のような実装基板の接続端子(被接続端子)と、下面側配線層50の電極領域とを電気的に接続する接続部材としての役割を果たす。はんだボール42によって、半導体モジュール1が図示しない実装基板に電気的に接続される。

【0029】

このような構成を備えた素子搭載用基板100に半導体素子300が搭載されて、半導体モジュール1が形成される。本実施形態に係る半導体モジュール1では、半導体素子300が素子搭載用基板100にフリップチップ接続されている。具体的には、金(Au)などからなる導電性バンプ310が形成された半導体素子300の電極形成面がフェイスダウンされ、導電性バンプ310がはんだボール40を介して配線層20に電気的に接続されている。

【0030】

半導体素子300の電極形成面には、アルミニウム(Al)などからなる素子電極302が形成されており、素子電極302の表面に導電性バンプ310が設けられている。半導体素子300の具体例としては、集積回路(IC)、大規模集積回路(LSI)などの半導体チップが挙げられる。半導体素子300と絶縁層60との間には、エポキシ樹脂から成るアンダーフィル120が充填されている。

【0031】

封止樹脂110は、素子搭載用基板100の上面と半導体素子300とを封止している。封止樹脂110は、例えばエポキシ樹脂を用いて、トランスファーモールド法により形成される。

【0032】

続いて、図3を用いて配線層20とはんだボール40の接続構造について詳細に説明する。図3は、図2における配線層とはんだボールの接続部分周囲の構造を示す拡大断面図である。

【0033】

図3に示すように、配線層20の電極領域20bと配線領域20aの一部とには、粗面領域21が設けられている。粗面領域21は、電極領域20bの主表面の表面粗さRmaxが合金層30の層厚よりも大きくなるように設定されている。配線層20の表面粗さは、触針式表面形状測定器で計測するか、あるいは、断面SEM(走査電子顕微鏡)像などから計測することができる。本実施形態では、例えば、開口部60aの径が約0.2mmであった場合、電極領域20bの主表面の表面粗さRmaxは開口部60a内の約0.2mmφの範囲で測定され、その値は約5μmである。また、合金層30の層厚は約1〜3μmである。ここで、前記「合金層30の層厚」は、例えば、合金層30の平均厚さである。このように、電極領域20bの表面粗さRmaxが合金層30の層厚よりも大きくなるように粗面領域21が形成されているため、合金層30は、配線層20の主表面に直交する断面形状が蛇行した形状となる。

【0034】

上述のように、合金層30は、配線層20のCuとはんだボール40のSnとで形成されるCuSn合金を含む。このCuSn合金はCuやSnと比べて脆いため、配線層20やはんだボール40と比べて合金層30にはクラック(亀裂)が発生しやすい。そのため、電極領域20bに粗面領域21が設けられておらず、合金層30の断面形状が配線層20の主表面に平行に延びる直線形状であった場合には、合金層30に発生したクラックが配線層20に平行な方向に進行しやすく、そのため発生したクラックが大きくなってしまう可能性が高かった。これに対し、合金層30の断面形状が蛇行形状である場合には、CuSn合金よりも剛性の高いCuからなり、電極領域20bにおける合金層30の下方に位置する下層部22と、CuSn合金よりも剛性の高いSnを合金層30よりも高い割合で含むはんだボール40とが、あたかも合金層30に陥入したような形状となる。したがって、下層部22またははんだボール40によって、合金層30に発生したクラックの平行方向への進行を阻止することができる。これにより、合金層30に発生したクラックが大きくなることを回避することができ、その結果、素子搭載用基板100と半導体素子300との接続信頼性が向上して、半導体モジュール1の実装信頼性が向上する。

【0035】

ここで、はんだボール40は、配線層20の主表面に平行な方向で、合金層30を挟んで下層部22と対向する部分を有していてもよい。すなわち、はんだボール40のうち、電極領域20bの主表面の凹部32に進入した部分と、下層部22のはんだボール40側に突出した凸部24とが、配線層20の主表面に平行な方向(図3における左右方向)で合金層30を挟んで対向していてもよい。この場合には、合金層30に発生したクラックの大型化をより確実に阻止することができる。

【0036】

また、電極領域20bの粗面の凸部34は、その頂面が配線領域20aの絶縁層60側の主表面と略面一な平面であってもよい。この場合には、凸部34の両側面の合金層30同士が接触するのを回避できるため、凸部34における合金層30の厚さを他の領域の厚さと等しくすることができ、したがって合金層30の層厚を均一にすることができる。その結果、クラックの発生が合金層30の特定箇所に集中するのを防ぐことができる。この場合、凸部34の頂面は、配線層20の主表面と直交する断面で、その幅が合金層30の層厚の約2倍以上であることが好ましい。この場合には、より確実に合金層30の厚さを均一にすることができる。さらに、合金層30と下層部22との界面における凸部24の頂面が、配線層20の主表面と略平行な平面であってもよい。この場合にも、合金層30の凸部34において、凸部34の両側の合金層30同士が接触するのを回避できるため、凸部34における合金層30の厚さを均一にすることができる。

【0037】

(素子搭載用基板および半導体モジュールの製造方法)

実施形態1に係る半導体モジュール1の製造方法について図4および図5を参照して説明する。図4(A)〜(D)、図5(A)、(B)は、半導体モジュールの製造方法を示す工程断面図である。

【0038】

まず、図4(A)に示すように、一方の主表面に銅箔25が貼り付けられた基材10を用意する。銅箔25は、配線層20の厚さ以上の厚さを有する。なお、図1に示したように、基材10にはビア導体52が設けられているが、このビア導体52は従来公知の方法で形成することができるため、その説明は省略する。

【0039】

次に、図4(B)に示すように、フォトリソグラフィ法により、銅箔25の主表面に、配線領域20aおよび電極領域20bを含む配線層20(図2参照)の形成予定領域に対応したパターンに合わせてレジスト200(マスク)を選択的に形成する。具体的には、ラミネーター装置を用いて銅箔25に所定膜厚のレジスト膜を貼り付け、配線層20のパターンを有するフォトマスクを用いて露光した後、現像することによって、銅箔25の上にレジスト200が選択的に形成される。なお、レジストとの密着性向上のために、レジスト膜のラミネート前に、銅箔25の表面に研磨、洗浄等の前処理を必要に応じて施すことが望ましい。

【0040】

ここで、レジスト200には、複数の貫通孔200aが設けられている。この複数の貫通孔200aは、レジスト200の部分概略平面図である図6に示すように、電極領域20bあるいは絶縁層60の開口部60a(図2参照)に対応するA領域内と、その周囲に設けられている。

【0041】

次に、図4(C)に示すように、レジスト200をマスクとして塩化第二鉄溶液などの薬液を用いたウェットエッチング処理を行うことにより、銅箔25を選択的に除去して配線領域20aおよび電極領域20bを含む配線層20を形成する。このとき、貫通孔200a内にも薬液が進入するため、銅箔25のうち貫通孔200aによって露出した部分もエッチングされる。ここで、貫通孔200a内では、他の領域に比べて薬液の循環効率が低いため、他の領域に比べて薬液による銅箔25の侵食速度が遅くなる。そのため、銅箔25のうち貫通孔200aによって露出した部分は、配線層20のパターニング時に基材10側まで侵食されない。その結果、配線層20の電極領域20bの表面には、貫通孔200aに対応する凹部32とその間の凸部34(図3参照)とが形成された状態となる。凸部34の頂部は、配線層20の配線領域20aの主表面と略同じ高さとなる。このようにして、配線層20の電極領域20bの表面に粗化処理が施される。この方法によれば、配線層20の形成と電極領域20b表面の粗化とを一括して実施することができる。配線層20を形成した後、レジスト200を、剥離剤を用いて剥離する。

【0042】

次に、図4(D)に示すように、基材10の一方の主表面にフォトソルダーレジストを積層した後、周知のフォトリソグラフィ法を用いて、配線層20の電極領域20bが露出するような開口部60aを有する絶縁層60を形成する。本実施形態では、レジスト200の貫通孔200aが電極領域20bに対応する領域の周囲にまで設けられている。そのため、配線領域20aのうち電極領域20bに隣接する領域にも粗化処理が施されて、当該領域の表面に凹凸が形成されている。これにより、電極領域20bの周囲において、絶縁層60と配線層20との接触面積が増大して、両者の密着性が向上する。したがって、配線層20と絶縁層60とが剥離する可能性を低減することができる。

【0043】

次に、図5(A)に示すように、絶縁層60の開口部60aにおいて、例えばスクリーン印刷法により、配線層20の電極領域20bにはんだボール40を搭載する。具体的には、樹脂とはんだ材をペースト状にしたはんだペーストをスクリーンマスクにより所望の箇所に印刷してはんだボール40を形成する。そして、素子電極302に導電性バンプ310が設けられた半導体素子300を素子搭載用基板100上に搭載し、リフロー工程によりはんだボール40を溶融して、導電性バンプ310とはんだボール40とを接合することで、はんだボール40を介して電極領域20bと素子電極302とを電気的に接続する。配線層20の電極領域20bと半導体素子300の素子電極302とを電気的に接続するリフロー工程では、はんだボール40に含まれるSnが配線層20側に移動して、配線層20のCuとはんだボール40のSnとが反応し、電極領域20bにCuとSnとの合金を含む合金層30が形成される。

【0044】

本実施形態では、電極領域20bの主表面のRmaxが合金層30の厚さよりも大きくなるように電極領域20bの主表面が粗化される。これにより、配線層20の主表面に直交する断面に現れる合金層30の形状を蛇行形状とすることができる。また、レジスト200に設けられた複数の貫通孔200aは、粗化処理によって電極領域20bに形成される凸部34の頂面が平面となるように、それぞれの間隔を設定することができる。これにより、凸部34の両側面の合金層30同士が接触するのを回避できるため、合金層30の厚さを均一にすることができる。また、複数の貫通孔200aは、それぞれの間隔が合金層30の層厚の約2倍以上となるように設定されることが好ましい。この場合には、より確実に凸部34の両側面の合金層30同士が接触するのを回避することができる。

【0045】

図示は省略するが、上述の各工程と同様にして、下面側配線層50と、下面側絶縁層62と、はんだボール42とが形成される。以上の工程により、素子搭載用基板100が製造される。

【0046】

続いて、図5(B)に示すように、半導体素子300と絶縁層60との間にアンダーフィル120が充填され、半導体素子300が封止樹脂110によって封止される。以上の工程により、実施形態1に係る半導体モジュール1を製造することができる。

【0047】

以上説明したように、実施形態1に係る半導体モジュール1は、Cuからなる電極領域20bの主表面が粗面であり、電極領域20bのはんだボール40と接する表層部分にはCuSn合金を含む合金層30が設けられている。そして、電極領域20bの主表面の表面粗さRmaxが合金層30の層厚よりも大きい。そのため、合金層30は、配線層20の主表面に直交する断面形状が蛇行形状となる。これにより、合金層30に発生したクラックの配線層20に平行な方向への進行を防ぐことができるため、クラックが大きくなることを回避することができる。また、合金層30に生じるクラックの長さが同じであった場合、合金層30が平坦面形状である場合よりも凹凸を有する形状である場合の方が、配線層20の主表面に平行な方向のクラック長さが短くなる。そのため、素子搭載用基板100と半導体素子300との接続信頼性を向上させることができ、ひいては半導体モジュール1の実装信頼性を向上させることができる。

【0048】

また、電極領域20bの表面にNi/Au層などの金めっき層を設けることで素子搭載用基板100と半導体素子300との接続信頼性を向上させる場合と比べて、より安価な構成で両者の接続信頼性の向上を図ることができる。

【0049】

また、はんだボール40は、配線層20の主表面に平行な方向で、合金層30を挟んで下層部22と対向する部分を有してもよい。この場合には、合金層30に発生したクラックが水平方向に進行するのをより確実に阻止することができるため、合金層30に発生したクラックの大型化をより確実に阻止することができる。また、電極領域20bの粗面の凸部34は、その頂面が配線領域20aの主表面と略面一な平面であってもよい。この場合には、凸部34における合金層30の厚さを他の領域の厚さと等しくすることができるため、合金層30の層厚を均一にすることができる。そして、これにより、クラックの発生が合金層30の特定箇所に集中するのを防ぐことができるため、素子搭載用基板100と半導体素子300との接続信頼性をさらに向上させることができる。

【0050】

さらに、本実施形態では、電極領域20bの形成予定領域に対応する部分に貫通孔200aが設けられたレジスト200を用いて配線層20を形成している。そのため、レジスト200の形成と同時に電極領域20bの粗化処理を実施することができるため、製造工程数の増大を回避することができる。

【0051】

(実施形態2)

次に、上述の実施形態1に係る半導体モジュール1を備えた携帯機器について説明する。なお、携帯機器として携帯電話に搭載する例を示すが、たとえば、個人用携帯情報端末(PDA)、デジタルビデオカメラ(DVC)、及びデジタルスチルカメラ(DSC)といった電子機器であってもよい。

【0052】

図7は実施形態2に係る携帯電話の構成を示す図である。携帯電話1111は、第1の筐体1112と第2の筐体1114が可動部1120によって連結される構造になっている。第1の筐体1112と第2の筐体1114は可動部1120を軸として回動可能である。第1の筐体1112には文字や画像等の情報を表示する表示部1118やスピーカ部1124が設けられている。第2の筐体1114には操作用ボタンなどの操作部1122やマイク部1126が設けられている。実施形態1に係る半導体モジュール1はこうした携帯電話1111の内部に搭載されている。

【0053】

図8は図7に示した携帯電話の部分断面図(第1の筐体1112の断面図)である。上述の実施形態1に係る半導体モジュール1は、はんだボール42を介してプリント基板1128に搭載され、こうしたプリント基板1128を介して表示部1118などと電気的に接続されている。また、半導体モジュール1の裏面側(はんだボール42とは反対側の面)には金属基板などの放熱基板1116が設けられ、たとえば、半導体モジュール1から発生する熱を第1の筐体1112内部に篭もらせることなく、効率的に第1の筐体1112の外部に放熱することができるようになっている。

【0054】

本発明の実施形態1に係る半導体モジュール1によれば、素子搭載用基板100と半導体素子300との接続信頼性を高めることができ、したがって半導体モジュール1の実装信頼性を高めることができる。そのため、こうした半導体モジュール1を搭載した本実施形態に係る携帯機器について、動作信頼性の向上を図ることができる。また、実施形態1で示したCSPプロセスにより製造された半導体モジュール1は薄型化・小型化されるので、こうした半導体モジュール1を搭載した携帯機器の薄型化・小型化を図ることができる。

【0055】

本発明は、上述の実施形態に限定されるものではなく、当業者の知識に基づいて各種の設計変更等の変形を加えることも可能であり、そのような変形が加えられた実施の形態も本発明の範囲に含まれうるものである。

【0056】

例えば、実施形態1では、素子搭載用基板100上に設けた配線層20の電極領域20bとはんだボール40との接続構造を例としたが、本発明はこれに限られない。例えば、半導体モジュール1(電子部品)と実装基板の接続に用いられるはんだボール42と、下面側配線層50の電極領域50bとの接続構造に実施形態1の接続構造を適用することができる。すなわち、電極領域50bは、はんだボール42と接する側の主表面が粗面であり、はんだボール42と接する表層部分にCuとSnの合金を含む合金層を有し、主表面の表面粗さRmaxが合金層の層厚よりも大きくなるように設定されている。このような場合にも、実施形態1の効果を享受することができる。なお、例えば下面側開口部62aの径が1.0mmであった場合、電極領域20bの表面粗さRmaxは、下面側開口部62a内の約1.0mmφの範囲で測定される。

【0057】

また、半導体モジュール1は、図9に示すような構造であってもよい。図9は、変形例に係る半導体モジュールの構成を示す概略断面図である。図9に示す変形例に係る半導体モジュール1と、実施形態1に係る半導体モジュール1との主な相違点は、変形例に係る半導体モジュール1の素子搭載用基板100が基材と下面側配線層50とを有さず、配線層20(リードフレーム)の裏面側にはんだボール42が直接搭載されている点である。この場合には、配線層20とはんだボール42との接続構造に、実施形態1の接続構造が適用される。また、他の相違点として、変形例に係る半導体モジュール1では、半導体素子300がフィルム接着剤130を介して配線層20の主表面に固定されており、また、半導体素子300の素子電極と配線層20の電極領域20bとが金線320によりワイヤボンディング接続されている。配線層20の半導体素子300側には封止樹脂110が積層され、配線層20のはんだボール42が搭載された側には下面側絶縁層62が積層されている。

【0058】

さらに、はんだボール42と実装基板側の接続端子との接続構造、あるいは、半導体素子300の素子電極302とはんだボール40との接続構造に実施形態1の接続構造を適用してもよい。これらの場合にも、上述の効果を享受することができる。

【符号の説明】

【0059】

1 半導体モジュール、 10 基材、 20 配線層、 20a 配線領域、 20b 電極領域、 21 粗面領域、 30 合金層、 40,42 はんだボール、 50 下面側配線層、 50a 配線領域、 50b 電極領域、 100 素子搭載用基板、 300 半導体素子。

【特許請求の範囲】

【請求項1】

配線領域とこれに接続された電極領域を含み、Cuからなる配線層と、

前記電極領域と被接続端子とを電気的に接続し、Snを含む接続部材と、を備え、

前記電極領域は、前記接続部材と接する側の主表面が粗面であり、前記接続部材と接する表層部分にCuとSnの合金を含む合金層を有し、前記主表面の表面粗さRmaxが前記合金層の層厚よりも大きいことを特徴とする半導体モジュール。

【請求項2】

前記接続部材は、前記配線層の主表面に平行な方向で、前記合金層を挟んで前記電極領域における合金層の下方に位置する下層部と対向する部分を有することを特徴とする請求項1に記載の半導体モジュール。

【請求項3】

前記電極領域の粗面の凸部は、その頂面が前記配線領域の主表面と略面一な平面であることを特徴とする請求項1または2に記載の半導体モジュール。

【請求項4】

前記被接続端子は、半導体素子の素子電極であり、

前記半導体素子が前記配線層にフリップチップ接続されていることを特徴とする請求項1乃至3のいずれか1項に記載の半導体モジュール。

【請求項5】

請求項1乃至4のいずれか1項に記載の半導体モジュールを搭載したことを特徴とする携帯機器。

【請求項6】

一方の主表面にCuからなる金属層が設けられた基材を用意する工程と、

前記金属層における、配線領域および電極領域を含む配線層の形成予定領域を被覆するマスクであって、前記電極領域の形成予定領域に対応する部分に複数の貫通孔が設けられたマスクを前記金属層の上に形成する工程と、

前記マスクを用いて前記金属層を選択的に除去して前記配線層を形成するとともに、前記電極領域の主表面に粗化処理を施す工程と、

前記電極領域にSnを含む接続部材を搭載するとともに溶融し、当該接続部材を介して前記電極領域と被接続端子とを電気的に接続する工程と、

を含むことを特徴とする半導体モジュールの製造方法。

【請求項7】

前記接続部材を溶融した際に、前記電極領域の前記接続部材と接する表層部分に前記配線層のCuと前記接続部材のSnとの合金を含む合金層が形成され、

前記粗化処理を施す工程において、前記電極領域の主表面の表面粗さRmaxが前記合金層の層厚よりも大きくなるように、前記電極領域の主表面を粗化することを特徴とする請求項6に記載の半導体モジュールの製造方法。

【請求項8】

前記接続部材を溶融した際に、前記電極領域の前記接続部材と接する表層部分に前記配線層のCuと前記接続部材のSnとの合金を含む合金層が形成され、

前記マスクに設けられた複数の貫通孔は、それぞれの間隔が前記合金層の層厚の2倍以上となるように設定されていることを特徴とする請求項6または7に記載の半導体モジュールの製造方法。

【請求項1】

配線領域とこれに接続された電極領域を含み、Cuからなる配線層と、

前記電極領域と被接続端子とを電気的に接続し、Snを含む接続部材と、を備え、

前記電極領域は、前記接続部材と接する側の主表面が粗面であり、前記接続部材と接する表層部分にCuとSnの合金を含む合金層を有し、前記主表面の表面粗さRmaxが前記合金層の層厚よりも大きいことを特徴とする半導体モジュール。

【請求項2】

前記接続部材は、前記配線層の主表面に平行な方向で、前記合金層を挟んで前記電極領域における合金層の下方に位置する下層部と対向する部分を有することを特徴とする請求項1に記載の半導体モジュール。

【請求項3】

前記電極領域の粗面の凸部は、その頂面が前記配線領域の主表面と略面一な平面であることを特徴とする請求項1または2に記載の半導体モジュール。

【請求項4】

前記被接続端子は、半導体素子の素子電極であり、

前記半導体素子が前記配線層にフリップチップ接続されていることを特徴とする請求項1乃至3のいずれか1項に記載の半導体モジュール。

【請求項5】

請求項1乃至4のいずれか1項に記載の半導体モジュールを搭載したことを特徴とする携帯機器。

【請求項6】

一方の主表面にCuからなる金属層が設けられた基材を用意する工程と、

前記金属層における、配線領域および電極領域を含む配線層の形成予定領域を被覆するマスクであって、前記電極領域の形成予定領域に対応する部分に複数の貫通孔が設けられたマスクを前記金属層の上に形成する工程と、

前記マスクを用いて前記金属層を選択的に除去して前記配線層を形成するとともに、前記電極領域の主表面に粗化処理を施す工程と、

前記電極領域にSnを含む接続部材を搭載するとともに溶融し、当該接続部材を介して前記電極領域と被接続端子とを電気的に接続する工程と、

を含むことを特徴とする半導体モジュールの製造方法。

【請求項7】

前記接続部材を溶融した際に、前記電極領域の前記接続部材と接する表層部分に前記配線層のCuと前記接続部材のSnとの合金を含む合金層が形成され、

前記粗化処理を施す工程において、前記電極領域の主表面の表面粗さRmaxが前記合金層の層厚よりも大きくなるように、前記電極領域の主表面を粗化することを特徴とする請求項6に記載の半導体モジュールの製造方法。

【請求項8】

前記接続部材を溶融した際に、前記電極領域の前記接続部材と接する表層部分に前記配線層のCuと前記接続部材のSnとの合金を含む合金層が形成され、

前記マスクに設けられた複数の貫通孔は、それぞれの間隔が前記合金層の層厚の2倍以上となるように設定されていることを特徴とする請求項6または7に記載の半導体モジュールの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2011−54670(P2011−54670A)

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願番号】特願2009−200541(P2009−200541)

【出願日】平成21年8月31日(2009.8.31)

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願日】平成21年8月31日(2009.8.31)

【出願人】(000001889)三洋電機株式会社 (18,308)

【Fターム(参考)】

[ Back to top ]