半導体リレーモジュール

【課題】高周波特性を向上させるとともに、発光素子と制御素子を封止する透光性樹脂の形状を所望の形状に保持しやすい半導体リレーモジュールを提供する。

【解決手段】半導体リレーモジュールAは、ソース電極同士が接続されたMOSFET11,12からなり、高周波信号用の信号伝送線路110の途中に設けられた半導体スイッチ1と、入力信号に応じて光信号を発光する発光ダイオード31と、発光ダイオード31からの光信号を受光する受光素子を有し当該受光素子の出力に応じてMOSFET11,12のオン/オフを制御する制御IC32と、制御IC32が備える受光素子および発光ダイオード31を光学的に結合させた状態で樹脂封止する透光性樹脂8を備える。制御IC32は、信号伝送線路110を構成する導体パターン113から分岐させたランド132上に配置され、導体パターン113とランド132との間にはLPF4が挿入される。

【解決手段】半導体リレーモジュールAは、ソース電極同士が接続されたMOSFET11,12からなり、高周波信号用の信号伝送線路110の途中に設けられた半導体スイッチ1と、入力信号に応じて光信号を発光する発光ダイオード31と、発光ダイオード31からの光信号を受光する受光素子を有し当該受光素子の出力に応じてMOSFET11,12のオン/オフを制御する制御IC32と、制御IC32が備える受光素子および発光ダイオード31を光学的に結合させた状態で樹脂封止する透光性樹脂8を備える。制御IC32は、信号伝送線路110を構成する導体パターン113から分岐させたランド132上に配置され、導体パターン113とランド132との間にはLPF4が挿入される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体リレーモジュールに関するものである。

【背景技術】

【0002】

従来、図9に示す回路構成を有する半導体リレーモジュールが提供されていた(例えば特許文献1参照)。この半導体リレーモジュールAは、ゲート電極同士およびソース電極同士がそれぞれ接続されるとともにドレイン電極が接続端子T11,T12にそれぞれ接続された一対のMOSFET11,12と、入力信号に応じて光信号を発光する発光ダイオード(発光素子)31と、発光ダイオード31からの光信号を受光するとMOSFET11,12を導通させる制御IC32とを備えている。制御IC32は、フォトダイオードアレイ33と充放電回路34とを主要な構成として備え、フォトダイオードアレイ33および充放電回路34が1つのパッケージ内に収納されて構成される。フォトダイオードアレイ33は、複数個のフォトダイオードが直列接続されてなり、発光ダイオード31の光信号を受光して光起電力を発生する。フォトダイオードアレイ33が光起電力を発生しているときは、充放電回路34がMOSFET11,12のゲート−ソース電極間に効率よく電荷を充電するよう制御することで、MOSFET11,12のドレイン−ソース電極間を低インピーダンス状態とする。またフォトダイオードアレイ33が光起電力を発生していないときは、充放電回路34がMOSFET11,12のゲート−ソース電極間に充電された電荷の放電経路となることで、MOSFET11,12のドレイン−ソース電極間を高インピーダンス状態とする。すなわち、フォトダイオードアレイ33が光起電力を発生している時と光起電力を発生していない時とで、充放電回路34が、MOSFET11,12のドレイン−ソース電極間のインピーダンスを変化させ、接続端子T11,T12間の信号伝送を許可又は遮断している。

【0003】

この半導体リレーモジュールAは、上述した各回路部品を誘電体基板の表面に形成された回路パターン上に配置してある。図10は誘電体基板100への各回路部品の実装状態を示す要部拡大図であり、誘電体基板100の表面には、接続端子T11とMOSFET11のドレイン電極との間を接続する導体パターン111と、接続端子T12とMOSFET12のドレイン電極との間を接続する導体パターン112とが、所定の隙間を開けて、略同一直線上に並ぶように形成されている。また誘電体基板100の表面には、導体パターン111,112の近傍に制御IC32を実装するためのランド101が形成されるとともに、このランド101の近傍に発光ダイオード用の導体パターン121,122が形成されている。

【0004】

発光ダイオード31は上下両面にそれぞれ電極(アノード電極およびカソード電極)を有しており、一方の導体パターン121にダイボンディングされて、下面電極が導体パターン121に電気的に接続されると共に、導電性の良好な金などの金属細線からなるボンディングワイヤ200を介して上面電極が他方の導体パターン122に電気的に接続されている。

【0005】

制御IC32は、MOSFET11,12のゲート電極Gにそれぞれ接続される一対の出力電極32a,32bと、MOSFET11,12のソース電極Sに共通接続される電極32cとを上面に有している。この制御IC32はランド101上にダイボンディングされ、制御IC32の電極32cはボンディングワイヤ200を介してランド101に接続されている。ここで、制御IC32の備えるフォトダイオードアレイ33が発光ダイオード31からの光信号を受光できるように、制御IC32と発光ダイオード31が配置されている。また、発光ダイオード31および制御IC32は、図示しない透光性樹脂で封止されることによって光学的に結合されるとともに、透光性樹脂の表面が遮光性を有する部材で覆われることによって、外乱光の入射を防止している。

【0006】

MOSFET11,12は、いずれも裏面にドレイン電極を備えるとともに、表面にソース電極S及びゲート電極Gを備えている。そして、MOSFET11,12をそれぞれ導体パターン111,112にダイボンディングすることによって、各々のドレイン電極が導体パターン111,112に電気的に接続されている。またMOSFET11,12のゲート電極G,Gはそれぞれボンディングワイヤ200,200を介して制御IC32の電極32a,32bに電気的に接続されている。またMOSFET11,12のソース電極S,S間はボンディングワイヤ200を介して電気的に接続されると共に、一方のMOSFET12のソース電極Sがボンディングワイヤ200を介してランド101に電気的に接続されることによって、制御IC32の電極32cとMOSFET11,12のソース電極S,Sとの間がボンディングワイヤ200およびランド101を介して電気的に接続されている。

【0007】

この半導体リレーモジュールAでは、導体パターン111,112を高周波信号の信号伝送線路として用い、MOSFET11,12により信号の通過又は遮断を切り替えるようにした場合、MOSFET11,12の導通時にはドレイン−ソース電極間のインピーダンスが低下するために、制御IC32の電極32cと導体パターン111,112との間が電気的に導通した状態となり、その結果、導体パターン111,112と電極32cの間を接続するボンディングワイヤ200やランド101がスタブとなって、高周波信号線路のインピーダンス整合が乱れ、使用可能な周波数帯域が狭くなるという問題があった。

【0008】

このような制御ICと信号伝送線路との間の配線による高周波特性への悪影響を低減するため、本発明者らは図11に示すような構成の半導体リレーモジュールを提案している(特願2008−9831号参照)。この半導体リレーモジュールでは、導体パターン111,112の間に、制御IC32を実装するためのランド101が設けられ、このランド101上に、高周波信号の伝送方向に沿ってMOSFET11,12と一列に並ぶように制御IC32が配置されている。したがって、制御IC32とMOSFET11,12との間を接続するボンディングワイヤ200が信号の伝送方向に沿って配線されることになり、これらのボンディングワイヤ200によってスタブが形成されることはないから、スタブの影響による高周波特性の悪化を防止もしくは低減することができる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−5779号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

上述した後者の半導体リレーモジュールでは、MOSFET11,12の間に制御IC32が配置されるため、制御IC32とMOSFET11,12との間を接続するボンディングワイヤ200がスタブとなることはないが、制御IC32が実装されるランド101は導体パターン111,112に比べて幅広に形成されているので、このランド101や制御IC32がスタブとなって、高周波特性が悪化するという問題があった。

【0011】

また制御IC32は発光ダイオード31とともに透光性樹脂8で封止され、制御IC32が備えるフォトダイオードアレイ33と発光ダイオード31とが光学的に結合されるのであるが、透光性樹脂8は流動性を有しているので、この透光性樹脂8が制御IC32の近傍に配置されたMOSFET11,12まで流れ出てしまい、透光性樹脂8の形状を所望の形状に保持するのが困難であった。

【0012】

本発明は上記問題点に鑑みて為されたものであり、その目的とするところは、高周波特性を向上させるとともに、発光素子と制御素子を封止する透光性樹脂の形状を所望の形状に保持しやすい半導体リレーモジュールを提供することにある。

【課題を解決するための手段】

【0013】

請求項1の発明は、基板の表面に設けられた信号伝送線路の途中に設けられて、信号を通過又は遮断する半導体スイッチと、入力信号に応じて光信号を発光する発光素子と、発光素子からの光信号を受光する受光素子を有し当該受光素子の出力に応じて半導体スイッチのオン/オフを制御する制御素子と、制御素子が備える受光素子および発光素子を光学的に結合させた状態で樹脂封止する透光性樹脂とを備え、制御素子は、信号伝送線路から分岐させたランド上に配置され、信号伝送線路とランドとの間に低域通過フィルタが挿入されたことを特徴とする。

【0014】

請求項2の発明は、請求項1の発明において、半導体スイッチは、ソース電極同士が電気的に接続される一対のMOSFETからなり、信号伝送線路は、各MOSFETが配置されて各MOSFETのドレイン電極にそれぞれ電気的に接続される第1及び第2の導体パターンと、第1及び第2の導体パターンの間に配置されて各MOSFETのソース電極が共通接続される第3の導体パターンとを有し、制御素子は、第3の導体パターンから分岐されたランド上に配置されるとともに、出力電極が各MOSFETのゲート電極に金属細線を介して電気的に接続され、各MOSFETのゲート−ソース電極間に制御電圧を印加することで各MOSFETのドレイン−ソース電極間のインピーダンスを変化させており、ランドと第3の導体パターンとの間に低域通過フィルタが挿入されたことを特徴とする。

【0015】

請求項3の発明は、請求項1の発明において、半導体スイッチは、ドレイン電極同士が電気的に接続される一対のMOSFETからなり、信号伝送線路は、一対のMOSFETが信号の伝送方向に沿って配置され、各MOSFETのドレイン電極に電気的に接続される第1の導体パターンと、伝送方向において第1の導体パターンの両側にそれぞれ配置され、それぞれ対応するMOSFETのソース電極に電気的に接続される第2及び第3の導体パターンとを有し、制御素子は、第2及び第3の導体パターンから分岐されたランド上に配置されるとともに、出力電極が各MOSFETのゲート電極に金属細線を介して電気的に接続され、各MOSFETのゲート−ソース電極間に制御電圧を印加することで各MOSFETのドレイン−ソース電極間のインピーダンスを変化させており、第2及び第3の導体パターンとランドとの間にそれぞれ低域通過フィルタが挿入されたことを特徴とする。

【0016】

請求項4の発明は、請求項2又は3の発明において、基板の表面において各MOSFETの実装部位付近から制御素子の実装部位付近まで中継用の導体パターンが設けられ、各MOSFETのゲート電極および制御素子の出力電極がそれぞれ金属細線を介して中継用の導体パターンに接続されたことを特徴とする。

【0017】

請求項5の発明は、請求項4の発明において、中継用の導体パターンの途中に低域通過フィルタが挿入されたことを特徴とする。

【発明の効果】

【0018】

請求項1の発明によれば、制御素子が配置されるランドと信号伝送線路との間に低域通過フィルタが挿入されているので、信号伝送線路から分岐されたランドや当該ランドに配置された制御素子がスタブとなることはなく、スタブにより信号伝送線路のインピーダンス整合が乱れて、高周波特性が悪化するのを防止できるという効果がある。しかも、発光素子とともに透光性樹脂で封止される制御素子は、信号伝送線路から分岐させたランド上に配置されているので、発光素子および制御素子を封止する封止部の配置を自由に設計できる。したがって、信号伝送線路の途中に設けられた半導体スイッチや他の回路部品とは離れた位置に封止部を配置することができ、流動性を有する透光性樹脂が半導体スイッチや他の回路部品の実装部位に流れていきにくくなるから、透光性樹脂の形状を所望の形状に保つことが容易になるという効果がある。

【0019】

請求項2の発明によれば、信号伝送線路を構成する第3の導体パターンと、第3の導体パターンから分岐されて制御素子が配置されるランドとの間に低域通過フィルタが挿入されているので、信号伝送線路から分岐されたランドや当該ランドに配置された制御素子がスタブとなることはなく、スタブにより信号伝送線路のインピーダンス整合が乱れて、高周波特性が悪化するのを防止できるという効果がある。

【0020】

請求項3の発明によれば、信号伝送線路を構成する第2及び第3の導体パターンと、第2及び第3の導体パターンから分岐されて制御素子が配置されるランドとの間に低域通過フィルタが挿入されているので、信号伝送線路から分岐されたランドや当該ランドに配置された制御素子がスタブとなることはなく、スタブにより信号伝送線路のインピーダンス整合が乱れて、高周波特性が悪化するのを防止できるという効果がある。

【0021】

請求項4の発明によれば、各MOSFETのゲート電極と制御素子の出力電極との間を電気的に接続する導電路の一部が、基板の表面に形成された中継用の導体パターンで構成されているので、ゲート電極と出力電極との間を金属細線で直接接続する場合に比べて、金属細線の長さを短くでき、金属細線の形状を保ちやすくなるとともに、断線の可能性を低減できるという効果がある。

【0022】

請求項5の発明によれば、中継用の導体パターンの途中に低域通過フィルタを挿入することによって、中継用の導体パターンや、MOSFETのゲート電極や制御素子の出力電極と中継用の導体パターンとの間を接続する金属細線がスタブとなるのを防止でき、スタブにより信号伝送線路のインピーダンス整合が乱れて、高周波特性が悪化するのを防止できるという効果がある。

【図面の簡単な説明】

【0023】

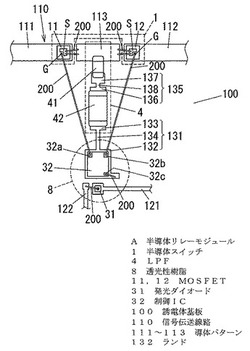

【図1】実施形態1を示し、パッケージ前のMOSFET付近の平面図である。

【図2】同上の概略構成を示す回路図である。

【図3】同上の詳細な回路図である。

【図4】実施形態2を示し、パッケージ前のMOSFET付近の平面図である。

【図5】実施形態3を示し、パッケージ前のMOSFET付近の平面図である。

【図6】同上の回路図である。

【図7】実施形態4を示し、パッケージ前のMOSFET付近の平面図である。

【図8】同上の回路図である。

【図9】従来の半導体リレーモジュールのブロック回路図である。

【図10】同上のパッケージ前のMOSFET付近の平面図である。

【図11】従来の別の半導体リレーモジュールを示し、パッケージ前のMOSFET付近の平面図である。

【発明を実施するための形態】

【0024】

以下に、本発明の技術思想を、高周波信号の伝送を許可又は遮断する半導体リレーモジュールに適用した実施形態について、図面を参照して説明する。

【0025】

(実施形態1)

本発明の実施形態1を図1〜図3に基づいて説明する。図2は本実施形態の半導体リレーモジュールAの概略的な回路図であり、この半導体リレーモジュールAは、高周波信号用の接続端子T1,T2と、低周波信号用の接続端子T3とを備える。

【0026】

高周波信号用の接続端子T1,T2間を接続する信号伝送線路110の途中には半導体スイッチ(以下、スイッチと略称す。)1が接続されている。このスイッチ1は制御回路3によってオン/オフが制御され、制御回路3の出力端とスイッチ1との間には、高周波帯域の信号に減衰を与える低域通過フィルタ(LPF)4が挿入されている。尚、LPF4は、カットオフ周波数の異なる2つのLPF41,42で構成されている。

【0027】

また、高周波信号用の接続端子T2とスイッチ1との間を接続する信号伝送線路110と、低周波信号用の接続端子T3との間には、高周波帯域の信号に減衰を与える低域通過フィルタ(以下、LPFと略称す。)6を介して半導体スイッチ(以下、スイッチと略称す。)2が接続されている。このスイッチ2は制御回路5によってオン/オフが制御される。

【0028】

次に、図3に示すより詳細な回路図を参照して半導体リレーモジュールAの各構成要素について説明を行う。

【0029】

高周波の信号伝送線路110に設けられたスイッチ1は、ソース電極同士が互いに接続されるとともに、ドレイン電極が接続端子T1,T2にそれぞれ接続された一対のMOSFET11,12からなる。

【0030】

スイッチ1のオン/オフを制御する制御回路3は、端子T4,T5を介して入力される入力信号に応じて光信号を発光する発光ダイオード(発光素子)31と、発光ダイオード31からの光信号を受光する受光素子を有し受光素子の出力に応じてMOSFET11,12をオン/オフする制御IC32(制御素子)とを備える。なお制御IC32は、図10で説明したものと同様の構成を有しており、発光ダイオード31の光信号を受光して光起電力を発生するフォトダイオードアレイ33(受光素子)と、フォトダイオードアレイ33が光起電力を発生しているときは、MOSFET11,12のゲート−ソース電極間に効率よく電荷を充電するよう制御するとともに、フォトダイオードアレイ33が光起電力を発生していないときはゲート−ソース電極間に充電された電荷の放電経路となることで、MOSFET11,12のドレイン−ソース間のインピーダンスを変化させる充放電回路34とで構成される。そして、制御IC32は、フォトダイオードアレイ33と充放電回路34とを含む回路を1つのパッケージ内に収納して構成されている。

【0031】

また、低周波信号用のスイッチ2は、上述したスイッチ1と同様、ソース電極同士が互いに接続された一対のMOSFET21,22からなり、一方のMOSFET21のドレイン電極Dは接続端子T3に接続され、他方のMOSFET22のドレイン電極DはLPF6を介して信号伝送線路110に接続されている。

【0032】

スイッチ2のオン/オフを制御する制御回路5は、端子T6,T7を介して入力される入力信号に応じて光信号を発光する発光ダイオード(発光素子)51と、発光ダイオード51からの光信号を受光する受光素子を有し受光素子の出力に応じてMOSFET21,22をオン/オフする制御IC52とを備えている。なお制御IC52は、上述の制御IC32と同様の構成を有しているので、その説明は省略する。

【0033】

この半導体リレーモジュールAは、図3の回路を構成する回路部品を、誘電体基板の表面に形成された回路パターン上に配置してある。図1は、MOSFET11,12およびその周辺部品を誘電体基板100に実装した状態を示すパッケージ前の平面図であり、図1を参照してMOSFET11,12近傍の実装状態を説明する。

【0034】

誘電体基板100の表面には、制御IC32が配置される実装用パターン131を分岐させた短冊状の第3の導体パターン(以下、導体パターンと略称す。)113が形成されるとともに、この導体パターン113を間にして左右方向の両側に帯状の第1及び第2の導体パターン(以下、導体パターンと略称す。)111,112が形成されている。これら導体パターン111,112,113は同一直線上に並ぶように配置されており、導体パターン111,112,113や、導体パターン111,112に実装されたMOSFET11,12のソース電極と導体パターン113の間を接続する後述のボンディングワイヤ200などから高周波信号の信号伝送線路110が構成されている。なお誘電体基板100には高周波信号の伝送方向(図1における左右方向)に沿って上記導体パターン111,112,113とともにマイクロストリップラインを構成するグランドライン(図示せず)が形成されている。

【0035】

実装用パターン131は、制御IC32が接続されるランド132と、LPF42の一端側が接続されるランド133と、ランド132,133間を接続する幅狭の導体パターン134とが連続一体に形成されて構成されている。この実装用パターン131と導体パターン113との間には、LPF42の他端側およびLPF41の一端側がそれぞれ接続される実装用パターン135が設けられている。実装用パターン135は、LPF42の他端側が接続されるランド136と、LPF41の一端側が接続されるランド137と、ランド136,137間を接続する幅狭のパターン138とが連続一体に形成されて構成されている。ここで、実装用パターン135,131は、高周波信号の伝送方向(図1における左右方向)と直交する方向(図1における上下方向)に向かって導体パターン113から延出するように設けられている。

【0036】

また誘電体基板100の表面には、制御IC32が配置されるランド132の近傍に、LED用の導体パターン121,122が形成されている。

【0037】

発光ダイオード31は上下両面にそれぞれ電極(アノード電極およびカソード電極)を有しており、上述した導体パターン121,122のうち、一方の導体パターン121にダイボンディングされて、下面電極が導体パターン121に電気的に接続されている。また発光ダイオード31の上面電極は、導電性の良好な金などの金属細線からなるボンディングワイヤ200を介して他方の導体パターン122に電気的に接続されている。

【0038】

制御IC32は、MOSFET11,12のゲート電極G,Gにそれぞれ接続される一対の電極32a,32bと、MOSFET11,12のソース電極S,Sに共通接続される電極32cを表面に備えている。この制御IC32は、ランド132上にダイボンディングされており、電極32cはボンディングワイヤ200を介してランド132に電気的に接続されている。

【0039】

LPF42は表面実装タイプのフィルタであり、両端に電極を有し、一端側の電極が実装用パターン131のランド133に接続され、他端側の電極が実装用パターン135のランド136に接続されるようにして両パターン131,135間に実装されている。またLPF41も表面実装タイプのフィルタからなり、両端に電極を有し、一端側の電極が実装用パターン135のランド137に接続され、他端側の電極が導体パターン113に接続されるように、両パターン135,113間に実装されている。

【0040】

またMOSFET11,12は、裏面にドレイン電極Dを備えるとともに、表面にソース電極Sおよびゲート電極Gを備えており、裏面のドレイン電極Dが導体パターン111,112にそれぞれ直接面接着されて、電気的に接続されている。MOSFET11,12のソース電極Sは、ボンディングワイヤ200を介して導体パターン113に電気的に接続されている。またMOSFET11,12のゲート電極G,Gは、それぞれ、ランド132上に実装された制御IC32の電極32a,32bにボンディングワイヤ200を介して電気的に接続されている。なお、制御IC32の共通電極32cは、ボンディングワイヤ200を介してランド132に接続されているので、LPF41,42および導体パターン113などを介して制御IC32の共通電極32cがMOSFET11,12のソース電極S,Sと電気的に接続されることになる。

【0041】

ここで、制御IC32の備えるフォトダイオードアレイ33が発光ダイオード31からの光信号を受光できるように、制御IC32と発光ダイオード31が配置されている。そして、発光ダイオード31と制御IC32とが透光性樹脂8で封止されることによって、発光ダイオード31とフォトダイオードアレイ33とが光学的に結合されており、さらに透光性樹脂8の表面が遮光性を有する部材で覆われることで、外乱光の入射が防止されるようになっている。

【0042】

上述のように本実施形態では、信号伝送線路110を構成する導体パターン113から、制御IC32が実装されるランド132を分岐させるとともに、導体パターン113とランド132との間にLPF4が挿入されているので、LPF4が高周波帯域の信号に減衰を与えることで、信号伝送線路110から分岐されたランド132(実装用パターン131)やこのランド132に配置された制御IC32がスタブとなって共振が発生するのを防止できる。したがって、スタブで共振が発生することにより、共振周波数付近でインサーションロスが増加して使用周波数帯域が狭くなるのを防止でき、スタブによって生じる高周波特性の悪化を防止することができる。

【0043】

ここにおいて、導体パターン113とランド132との間に挿入されるLPF4には、広帯域で減衰特性を持たせる必要があるが、本実施形態では、カットオフ周波数の異なる2つのLPF41,42を直列に接続してLPF4を構成することで、LPF4の広帯域化を図っている。なお、相対的に高い周波数の信号をカットするLPF42が、相対的に低い周波数の信号をカットするLPF41よりも導体パターン113に近い位置に配置された場合は、LPF42やそのフットパターン(実装用パターン135)がスタブとなってLPF41でカットできない周波数の共振が発生するため、高周波特性が悪化する可能性がある。したがって、本実施形態では、相対的に低い周波数の信号をカットするLPF41を、相対的に高い周波数の信号をカットするLPF42よりも導体パターン113に近い位置に配置しており、LPF41およびそのフットパターン(実装用パターン135)がスタブとなって共振が発生したとしても、その発振をLPF42でカットできるため、高周波特性を向上させることができる。また導体パターン113にはLPF41を接続するためのスタブが設けられておらず、LPF41は導体パターン113に直接実装されており、スタブとなるフットパターンを無くすことで、高周波特性の悪化を防止して、さらなる広帯域化を図ることができる。

【0044】

また、発光ダイオード31(発光素子)とともに透光性樹脂8で封止される制御IC32は、信号伝送線路110から分岐させたランド132上に配置されているので、発光ダイオード31および制御IC32を封止する封止部の配置を自由に設計できる。したがって、信号伝送線路110の途中に設けられたスイッチ1や他の回路部品とは離れた位置に封止部を配置することができ、流動性を有する透光性樹脂8がスイッチ1や他の回路部品の実装部位に流れていきにくくなるから、透光性樹脂8の形状を所望の形状に保つことが容易になる。

【0045】

次に、この半導体リレーモジュールAの動作について説明する。端子T6,T7間に信号が入力されていない状態では、発光ダイオード51が消灯しているので、制御IC52がスイッチ2(MOSFET21,22)をオフさせており、接続端子T3を介しての低周波信号の入出力が遮断される。

【0046】

そして、スイッチ2のオフ時に、端子T4,T5に信号が入力されていない状態では、発光ダイオード31が消灯しているので、制御IC32の充放電回路34がMOSFET11,12のゲート−ソース電極間に充電された電荷の放電経路になることで、MOSFET11,12のドレイン−ソース電極間を高インピーダンス状態とし、接続端子T1,T2間の信号伝送を遮断する。また、スイッチ2のオフ時に端子T4,T5間に信号が入力されると、発光ダイオード31が点灯し、発光ダイオード31の発光を受けて、制御IC32の充放電回路34がMOSFET11,12のゲート−ソース電極間に電荷を充電するよう制御することで、MOSFET11,12のドレイン−ソース電極間が低インピーダンス状態となるので、接続端子T1,T2間で高周波信号の伝送が許可される。而して、端子T4,T5間への信号入力の有無に応じて接続端子T1,T2間での高周波信号の伝送が許可又は遮断される。

【0047】

また、制御IC32がスイッチ1をオフさせた状態で、端子T6,T7間に信号が入力されると、発光ダイオード51の発光を受けて制御IC52が、MOSFET21,22のゲート−ソース電極間に電荷を充電するよう制御することによって、MOSFET21,22のドレイン−ソース電極間が低インピーダンス状態とされるので、接続端子T3に入力された低域の信号(低周波信号乃至直流信号)を接続端子T2に接続される機器(図示せず)に供給したり、接続端子T2に接続される機器から接続端子T2に入力された低域信号を接続端子T3から取り出すことができる。

【0048】

(実施形態2)

本発明の実施形態2について図4を参照して説明する。尚、MOSFET11,12のゲート電極G,Gと、制御IC32の電極32a,32bとの間を電気的に接続する構成以外は、実施形態1と同様であるので、共通する構成要素には同一の符号を付して、その説明は省略する。

【0049】

上述の実施形態1では、信号伝送線路110を構成する導体パターン111,112上にMOSFET11,12をそれぞれ配置して、信号伝送線路110を構成する導体パターン113から分岐させたランド132上に制御IC32を配置するとともに、MOSFET11のゲート電極Gと制御IC32の電極32aの間、MOSFET12のゲート電極Gと制御IC32の電極32bの間をそれぞれボンディングワイヤ200を介して直接接続しているため、ゲート電極G,Gと電極32a,32bの間を接続するボンディングワイヤ200の全長が長く、その形状が保ちにくくなっている。

【0050】

そこで、本実施形態では、図4に示すように誘電体基板100の表面においてMOSFET11,12の実装部位付近から制御IC32の実装部位付近まで、中継用の導体パターン141,142がそれぞれ形成されており、MOSFET11,12のゲート電極G,Gおよび制御IC32の電極32a,32bは、それぞれ、ボンディングワイヤ200を介して対応する導体パターン141,142に電気的に接続されている。すなわち、MOSFET11,12のゲート電極G,Gと、制御IC32の電極32a,32bとの間を電気的に接続する導電路の一部が、誘電体基板100の表面に形成された中継用の導体パターンで構成されているので、ゲート電極G,Gと出力電極32a,32bとの間をボンディングワイヤ200で直接接続する場合に比べて、ゲート電極G,Gと導体パターン141,142の間を接続するボンディングワイヤ200の長さや、電極32a,32bと導体パターン141,142の間を接続するボンディングワイヤ200の長さを短くでき、長さを短くすることでボンディングワイヤ200の形状を保ちやすくなるととともに、断線の可能性を低減することもできる。

【0051】

また本実施形態においても、表面実装タイプのLPF41は導体パターン113に直接実装されており、LPF41の接続されるフットパターンが導体パターン113に設けられていないので、スタブとなるフットパターンを無くすことで、高周波特性の悪化を防止することができる。

【0052】

ここで、導体パターン113においてLPF41が実装される部位は、接続される回路部品(LPF41)の影響によってインピーダンスが低下するため、本実施形態では導体パターン113の一側辺(LPF41が接続される側と反対側)を凹ませることによって、他の部位よりもパターン幅の狭い幅狭部113aが設けられている。したがって、導体パターン113においてLPF41が接続される部位(幅狭部113a)のパターン幅が、信号伝送線路110における他の部位のパターン幅よりも幅狭に形成されるので、LPF41が実装される部位のインピーダンスの低下を抑制して、高周波特性を改善することができる。

【0053】

(実施形態3)

本発明の実施形態3について図5及び図6を参照して説明する。実施形態2の半導体リレーモジュールでは、MOSFET11,12のゲート電極G,Gと制御IC32の出力電極32a,32bとの間をそれぞれ接続する導電路の一部を、誘電体基板100の表面に形成された導体パターン141,142で構成したものであるが、本実施形態では、図5及び図6に示すように、MOSFET11,12のゲート電極G,Gと制御IC32の出力電極32a,32bの間を中継するために設けた導体パターンの途中に低域通過フィルタ(LPF)7a,7bを挿入してある。尚、低域通過フィルタ7,7以外の構成は実施形態2と同様であるので、共通する構成要素には同一の符号を付して、その説明は省略する。

【0054】

低域通過フィルタ7a,7bは、それぞれ、2つのLPF71,72を直列に接続して構成されている。LPF71,72のカットオフ周波数は互いに異なっており、相対的に低い周波数の信号をカットするLPF71が、相対的に高い周波数の信号をカットするLPF72よりも導体パターン111,112に近い位置に配置されている。

【0055】

誘電体基板100の表面には、図5に示すように、MOSFET11,12の実装部位の近傍に、LPF71の一端側の電極が接続されるランド143がそれぞれ形成されるとともに、制御IC32の実装部位の近傍(左右両側)に、LPF72の一端側の電極が接続される実装用パターン145がそれぞれ形成されている。さらに、誘電体基板100の表面において、ランド143と実装用パターン145の間には、LPF71,72の他端側の電極が共通接続される実装用パターン144がそれぞれ形成されている。

【0056】

ここで、MOSFET11,12のゲート電極G,Gはボンディングワイヤ200を介してランド143,143に接続され、制御IC32の電極32a,32bはボンディングワイヤ200を介して実装用パターン145,145に接続されており、ランド143と実装用パターン144との間にはLPF71が、実装用パターン144と実装用パターン145との間にはLPF72がそれぞれ接続されている。

【0057】

而して、MOSFET11,12のゲート電極G,Gと、制御IC32の電極32a,32bとの間をそれぞれ接続する中継用の導体パターンの途中にLPF7(LPF71,72からなる)が挿入されることになり、中継用の導体パターンや、この導体パターンと制御IC32の出力電極32a,32bとの間を接続するボンディングワイヤ200がスタブとなるのを防止でき、スタブで共振が発生することによる高周波特性の悪化を防止することができる。

【0058】

(実施形態4)

本発明の実施形態4について図7及び図8を参照して説明する。上述の実施形態1〜3では、ソース電極同士が電気的に接続された一対のMOSFET11,12でスイッチ1が構成されているのに対して、本実施形態では、図8に示すようにドレイン電極同士が電気的に接続された一対のMOSFET11,12でスイッチ1が構成されている。そして、各MOSFET11,12のソース電極が接続される第2及び第3の導体パターン(以下、導体パターンと略称す。)111,112と、導体パターン111,112から分岐されて制御IC32,32がそれぞれ配置されるランド132,132との間にそれぞれLPF4a,4bが挿入されている。尚、MOSFET11,12と制御IC32,32とLPF4a,4b以外の構成は実施形態1〜3で説明した半導体リレーモジュールAと同様であるので、共通する構成要素には同一の符号を付して、その説明は省略する。

【0059】

図7は、誘電体基板100への各回路部品の実装状態を示す要部拡大図であり、誘電体基板100の表面には、MOSFET11,12の実装される帯状の第1の導体パターン(以下、導体パターンと略称す。)113が形成されるとともに、この導体パターン113を間にして両側に帯状の導体パターン111,112が形成されている。これら導体パターン111,112,113は同一直線上に並ぶように配置されており、導体パターン111,112,113や、導体パターン113に配置されたMOSFET11,12のソース電極と導体パターン111,112の間をそれぞれ接続するボンディングワイヤ200などから高周波信号の信号伝送線路110が構成されている。なお誘電体基板100には高周波信号の伝送方向に沿って上記導体パターン111,112,113とともにマイクロストリップラインを構成するグランドライン(図示せず)が形成されている。

【0060】

また誘電体基板100の表面には、制御IC32,32のそれぞれ実装される実装用パターン131,131が、導体パターン111,112から分岐させた形で形成されている。各実装用パターン131は、導体パターン113に対して信号伝送方向と直交する方向の片側に配置されて制御IC32が実装されるランド132と、ランド132において導体パターン113側の部位から信号伝送方向に沿って、互いに反対向きに延出し、LPF42の一方の電極が電気的に接続される接続パターン139とで形成されている。

【0061】

また誘電体基板100の表面には、制御IC32,32が実装されるランド132,132の近傍に、LED用導体パターン121,122が形成されている。

【0062】

MOSFET11,12は、いずれも裏面にドレイン電極を備えるとともに、表面にソース電極S及びゲート電極Gを備えている。そして、信号伝送線路110を構成する導体パターン113にMOSFET11,12をそれぞれダイボンディングすることによって、各々のドレイン電極が導体パターン113に電気的に接続されている。またMOSFET11,12のゲート電極G,Gはそれぞれボンディングワイヤ200を介して対応する制御IC32,32の電極32a又は32bに電気的に接続されている。またMOSFET11,12のソース電極S,Sは、それぞれボンディングワイヤ200を介して導体パターン111,112に電気的に接続されている。また導体パターン111(112)と、対応する実装用パターン135のランド137との間にはそれぞれLPF41が接続されており、さらに実装用パターン135のランド136と、対応するランド132から延出させた接続パターン139との間にはそれぞれLPF42が接続されている。

【0063】

このように本実施形態では、信号伝送線路110を構成する導体パターン111,112から、制御IC32,32が配置されるランド132,132を分岐させるとともに、導体パターン111,112とランド132,132との間にそれぞれLPF4a,4bが挿入されているので、LPF4a,4bが高周波帯域の信号に減衰を与えることで、信号伝送線路110から分岐されたランド132,132や各ランド132に配置された制御IC32がスタブとなって共振が発生するのを防止できる。したがって、スタブで共振が発生することにより、共振周波数付近でインサーションロスが増加して使用周波数帯域が狭くなるのを防止でき、スタブによって生じる高周波特性の悪化を防止することができる。

【0064】

ここにおいて、導体パターン111,112とランド132,132との間にそれぞれ挿入されるLPF4a,4bには、広帯域で減衰特性を持たせる必要があるが、本実施形態では、カットオフ周波数の異なる2つのLPF41,42を直列に接続してLPF4a,4bをそれぞれ構成することで、LPF4a,4bの広帯域化を図っている。なお、相対的に高い周波数の信号をカットするLPF42が、相対的に低い周波数の信号をカットするLPF41よりも導体パターン111,112に近い位置に配置された場合は、LPF42やそのフットパターン(実装用パターン135)がスタブとなってLPF41でカットできない周波数の共振が発生するため、高周波特性が悪化する可能性がある。したがって、本実施形態では、相対的に低い周波数の信号をカットするLPF41を、相対的に高い周波数の信号をカットするLPF42よりも導体パターン111,112に近い位置に配置しており、LPF41およびそのフットパターン(実装用パターン135)がスタブとなって共振が発生したとしても、その発振をLPF42でカットできるため、高周波特性を向上させることができる。また表面実装タイプのLPF41は導体パターン113に直接実装されており、LPF41が接続されるフットパターンを導体パターン113に設けた場合に比べて、スタブとなるフットパターンを無くすことで、高周波特性の悪化を防止でき、さらなる広帯域化を図ることができる。

【0065】

また、発光ダイオード31(発光素子)とともに透光性樹脂8で封止される制御IC32,32は、信号伝送線路110から分岐されたランド132,132上に配置されているので、発光ダイオード31および制御IC32,32を封止する封止部の配置を自由に設計できる。したがって、信号伝送線路100の途中に設けられたスイッチ1や他の回路部品とは離れた位置に封止部を配置することができ、流動性を有する透光性樹脂8がスイッチ1や他の回路部品の実装部位に流れていきにくくなるから、透光性樹脂8の形状を所望の形状に保つことが容易になる。

【0066】

尚、本実施形態においても実施形態2で説明したように、誘電体基板100の表面においてMOSFET11,12の実装部位付近から対応する制御IC32,32の実装部位付近まで、中継用の導体パターンを形成し、MOSFET11,12のゲート電極G,Gおよび制御IC32,32の電極32a,32bをそれぞれボンディングワイヤ200を介して中継用の導体パターンに接続してもよい。この場合、MOSFET11,12のゲート電極Gと制御IC32,32の電極32a,32bの間をボンディングワイヤ200で直接接続する場合に比べて、ボンディングワイヤ200の全長を短くできるので、ボンディングワイヤ200の形状を保ちやすくなり、また全長を短くすることで断線の可能性を少なくできるという利点もある。

【0067】

また実施形態3で説明したように、MOSFET11,12のゲート電極G,Gと制御IC32,32の電極32a,32bとの間を中継接続するために設けられた中継用の導体パターンの途中に低域通過フィルタを挿入することも好ましく、中継用の導体パターンや、制御IC32,32の電極32a,32bと中継用の導体パターンとの間を接続するボンディングワイヤ200がスタブとなるのを防止して、高周波特性の悪化を抑制することができる。

【0068】

また本実施形態においても、実施形態2で説明したように、導体パターン111,112においてLPF41が実装される部位のパターン幅を他の部位に比べて幅狭に形成しても良く、導体パターン111,112に接続されたLPF41の影響で配線路のインピーダンスが低下するのを抑制して、インピーダンス整合が乱れるのを防止することができる。

【0069】

次に、この半導体リレーモジュールAの動作について説明する。端子T6,T7間に信号が入力されていない状態では、発光ダイオード51が消灯しているので、制御IC52がスイッチ2(MOSFET21,22)をオフさせており、接続端子T3を介しての低周波信号の入出力が遮断される。

【0070】

そして、スイッチ2のオフ時に、端子T4,T5に信号が入力されていない状態では、発光ダイオード31が消灯しているので、制御IC32,32がMOSFET11,12のゲート−ソース電極間に充電された電荷の放電経路になることで、MOSFET11,12のドレイン−ソース電極間を高インピーダンス状態とし、接続端子T1,T2間の信号伝送を遮断する。また、スイッチ2のオフ時に端子T4,T5間に信号が入力されると、発光ダイオード31が点灯し、発光ダイオード31の発光を受けて、制御IC32,32の充放電回路がMOSFET11,12のゲート−ソース電極間に電荷を充電するよう制御することで、MOSFET11,12のドレイン−ソース電極間が低インピーダンス状態となるので、接続端子T1,T2間で高周波信号の伝送が許可される。而して、端子T4,T5間への信号入力の有無に応じて接続端子T1,T2間での高周波信号の伝送が許可又は遮断される。

【0071】

また、制御IC32,32がスイッチ1をオフさせた状態で、端子T6,T7間に信号が入力されると、発光ダイオード51の発光を受けて制御IC52が、MOSFET21,22のゲート−ソース電極間に電荷を充電するよう制御することによって、MOSFET21,22のドレイン−ソース電極間が低インピーダンス状態とされるので、接続端子T3に入力された低域の信号(低周波信号乃至直流信号)を接続端子T2に接続される機器(図示せず)に供給したり、接続端子T2に接続される機器から接続端子T2に入力された低域信号を接続端子T3から取り出すことができる。

【0072】

尚、図8の回路図では、端子T4,T5と端子T6,T7のY方向位置をずらして表記しているが、端子T4,T5と端子T6,T7のY方向位置が同じ位置となっていてもよい。

【符号の説明】

【0073】

A 半導体リレーモジュール

1 半導体スイッチ

4 LPF(低域通過フィルタ)

8 透光性樹脂

11,12 MOSFET

31 発光ダイオード(発光素子)

32 制御IC(制御素子)

33 フォトダイオードアレイ(受光素子)

34 充放電回路

100 誘電体基板

110 信号伝送線路

111〜113 導体パターン

132 ランド

【技術分野】

【0001】

本発明は、半導体リレーモジュールに関するものである。

【背景技術】

【0002】

従来、図9に示す回路構成を有する半導体リレーモジュールが提供されていた(例えば特許文献1参照)。この半導体リレーモジュールAは、ゲート電極同士およびソース電極同士がそれぞれ接続されるとともにドレイン電極が接続端子T11,T12にそれぞれ接続された一対のMOSFET11,12と、入力信号に応じて光信号を発光する発光ダイオード(発光素子)31と、発光ダイオード31からの光信号を受光するとMOSFET11,12を導通させる制御IC32とを備えている。制御IC32は、フォトダイオードアレイ33と充放電回路34とを主要な構成として備え、フォトダイオードアレイ33および充放電回路34が1つのパッケージ内に収納されて構成される。フォトダイオードアレイ33は、複数個のフォトダイオードが直列接続されてなり、発光ダイオード31の光信号を受光して光起電力を発生する。フォトダイオードアレイ33が光起電力を発生しているときは、充放電回路34がMOSFET11,12のゲート−ソース電極間に効率よく電荷を充電するよう制御することで、MOSFET11,12のドレイン−ソース電極間を低インピーダンス状態とする。またフォトダイオードアレイ33が光起電力を発生していないときは、充放電回路34がMOSFET11,12のゲート−ソース電極間に充電された電荷の放電経路となることで、MOSFET11,12のドレイン−ソース電極間を高インピーダンス状態とする。すなわち、フォトダイオードアレイ33が光起電力を発生している時と光起電力を発生していない時とで、充放電回路34が、MOSFET11,12のドレイン−ソース電極間のインピーダンスを変化させ、接続端子T11,T12間の信号伝送を許可又は遮断している。

【0003】

この半導体リレーモジュールAは、上述した各回路部品を誘電体基板の表面に形成された回路パターン上に配置してある。図10は誘電体基板100への各回路部品の実装状態を示す要部拡大図であり、誘電体基板100の表面には、接続端子T11とMOSFET11のドレイン電極との間を接続する導体パターン111と、接続端子T12とMOSFET12のドレイン電極との間を接続する導体パターン112とが、所定の隙間を開けて、略同一直線上に並ぶように形成されている。また誘電体基板100の表面には、導体パターン111,112の近傍に制御IC32を実装するためのランド101が形成されるとともに、このランド101の近傍に発光ダイオード用の導体パターン121,122が形成されている。

【0004】

発光ダイオード31は上下両面にそれぞれ電極(アノード電極およびカソード電極)を有しており、一方の導体パターン121にダイボンディングされて、下面電極が導体パターン121に電気的に接続されると共に、導電性の良好な金などの金属細線からなるボンディングワイヤ200を介して上面電極が他方の導体パターン122に電気的に接続されている。

【0005】

制御IC32は、MOSFET11,12のゲート電極Gにそれぞれ接続される一対の出力電極32a,32bと、MOSFET11,12のソース電極Sに共通接続される電極32cとを上面に有している。この制御IC32はランド101上にダイボンディングされ、制御IC32の電極32cはボンディングワイヤ200を介してランド101に接続されている。ここで、制御IC32の備えるフォトダイオードアレイ33が発光ダイオード31からの光信号を受光できるように、制御IC32と発光ダイオード31が配置されている。また、発光ダイオード31および制御IC32は、図示しない透光性樹脂で封止されることによって光学的に結合されるとともに、透光性樹脂の表面が遮光性を有する部材で覆われることによって、外乱光の入射を防止している。

【0006】

MOSFET11,12は、いずれも裏面にドレイン電極を備えるとともに、表面にソース電極S及びゲート電極Gを備えている。そして、MOSFET11,12をそれぞれ導体パターン111,112にダイボンディングすることによって、各々のドレイン電極が導体パターン111,112に電気的に接続されている。またMOSFET11,12のゲート電極G,Gはそれぞれボンディングワイヤ200,200を介して制御IC32の電極32a,32bに電気的に接続されている。またMOSFET11,12のソース電極S,S間はボンディングワイヤ200を介して電気的に接続されると共に、一方のMOSFET12のソース電極Sがボンディングワイヤ200を介してランド101に電気的に接続されることによって、制御IC32の電極32cとMOSFET11,12のソース電極S,Sとの間がボンディングワイヤ200およびランド101を介して電気的に接続されている。

【0007】

この半導体リレーモジュールAでは、導体パターン111,112を高周波信号の信号伝送線路として用い、MOSFET11,12により信号の通過又は遮断を切り替えるようにした場合、MOSFET11,12の導通時にはドレイン−ソース電極間のインピーダンスが低下するために、制御IC32の電極32cと導体パターン111,112との間が電気的に導通した状態となり、その結果、導体パターン111,112と電極32cの間を接続するボンディングワイヤ200やランド101がスタブとなって、高周波信号線路のインピーダンス整合が乱れ、使用可能な周波数帯域が狭くなるという問題があった。

【0008】

このような制御ICと信号伝送線路との間の配線による高周波特性への悪影響を低減するため、本発明者らは図11に示すような構成の半導体リレーモジュールを提案している(特願2008−9831号参照)。この半導体リレーモジュールでは、導体パターン111,112の間に、制御IC32を実装するためのランド101が設けられ、このランド101上に、高周波信号の伝送方向に沿ってMOSFET11,12と一列に並ぶように制御IC32が配置されている。したがって、制御IC32とMOSFET11,12との間を接続するボンディングワイヤ200が信号の伝送方向に沿って配線されることになり、これらのボンディングワイヤ200によってスタブが形成されることはないから、スタブの影響による高周波特性の悪化を防止もしくは低減することができる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−5779号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

上述した後者の半導体リレーモジュールでは、MOSFET11,12の間に制御IC32が配置されるため、制御IC32とMOSFET11,12との間を接続するボンディングワイヤ200がスタブとなることはないが、制御IC32が実装されるランド101は導体パターン111,112に比べて幅広に形成されているので、このランド101や制御IC32がスタブとなって、高周波特性が悪化するという問題があった。

【0011】

また制御IC32は発光ダイオード31とともに透光性樹脂8で封止され、制御IC32が備えるフォトダイオードアレイ33と発光ダイオード31とが光学的に結合されるのであるが、透光性樹脂8は流動性を有しているので、この透光性樹脂8が制御IC32の近傍に配置されたMOSFET11,12まで流れ出てしまい、透光性樹脂8の形状を所望の形状に保持するのが困難であった。

【0012】

本発明は上記問題点に鑑みて為されたものであり、その目的とするところは、高周波特性を向上させるとともに、発光素子と制御素子を封止する透光性樹脂の形状を所望の形状に保持しやすい半導体リレーモジュールを提供することにある。

【課題を解決するための手段】

【0013】

請求項1の発明は、基板の表面に設けられた信号伝送線路の途中に設けられて、信号を通過又は遮断する半導体スイッチと、入力信号に応じて光信号を発光する発光素子と、発光素子からの光信号を受光する受光素子を有し当該受光素子の出力に応じて半導体スイッチのオン/オフを制御する制御素子と、制御素子が備える受光素子および発光素子を光学的に結合させた状態で樹脂封止する透光性樹脂とを備え、制御素子は、信号伝送線路から分岐させたランド上に配置され、信号伝送線路とランドとの間に低域通過フィルタが挿入されたことを特徴とする。

【0014】

請求項2の発明は、請求項1の発明において、半導体スイッチは、ソース電極同士が電気的に接続される一対のMOSFETからなり、信号伝送線路は、各MOSFETが配置されて各MOSFETのドレイン電極にそれぞれ電気的に接続される第1及び第2の導体パターンと、第1及び第2の導体パターンの間に配置されて各MOSFETのソース電極が共通接続される第3の導体パターンとを有し、制御素子は、第3の導体パターンから分岐されたランド上に配置されるとともに、出力電極が各MOSFETのゲート電極に金属細線を介して電気的に接続され、各MOSFETのゲート−ソース電極間に制御電圧を印加することで各MOSFETのドレイン−ソース電極間のインピーダンスを変化させており、ランドと第3の導体パターンとの間に低域通過フィルタが挿入されたことを特徴とする。

【0015】

請求項3の発明は、請求項1の発明において、半導体スイッチは、ドレイン電極同士が電気的に接続される一対のMOSFETからなり、信号伝送線路は、一対のMOSFETが信号の伝送方向に沿って配置され、各MOSFETのドレイン電極に電気的に接続される第1の導体パターンと、伝送方向において第1の導体パターンの両側にそれぞれ配置され、それぞれ対応するMOSFETのソース電極に電気的に接続される第2及び第3の導体パターンとを有し、制御素子は、第2及び第3の導体パターンから分岐されたランド上に配置されるとともに、出力電極が各MOSFETのゲート電極に金属細線を介して電気的に接続され、各MOSFETのゲート−ソース電極間に制御電圧を印加することで各MOSFETのドレイン−ソース電極間のインピーダンスを変化させており、第2及び第3の導体パターンとランドとの間にそれぞれ低域通過フィルタが挿入されたことを特徴とする。

【0016】

請求項4の発明は、請求項2又は3の発明において、基板の表面において各MOSFETの実装部位付近から制御素子の実装部位付近まで中継用の導体パターンが設けられ、各MOSFETのゲート電極および制御素子の出力電極がそれぞれ金属細線を介して中継用の導体パターンに接続されたことを特徴とする。

【0017】

請求項5の発明は、請求項4の発明において、中継用の導体パターンの途中に低域通過フィルタが挿入されたことを特徴とする。

【発明の効果】

【0018】

請求項1の発明によれば、制御素子が配置されるランドと信号伝送線路との間に低域通過フィルタが挿入されているので、信号伝送線路から分岐されたランドや当該ランドに配置された制御素子がスタブとなることはなく、スタブにより信号伝送線路のインピーダンス整合が乱れて、高周波特性が悪化するのを防止できるという効果がある。しかも、発光素子とともに透光性樹脂で封止される制御素子は、信号伝送線路から分岐させたランド上に配置されているので、発光素子および制御素子を封止する封止部の配置を自由に設計できる。したがって、信号伝送線路の途中に設けられた半導体スイッチや他の回路部品とは離れた位置に封止部を配置することができ、流動性を有する透光性樹脂が半導体スイッチや他の回路部品の実装部位に流れていきにくくなるから、透光性樹脂の形状を所望の形状に保つことが容易になるという効果がある。

【0019】

請求項2の発明によれば、信号伝送線路を構成する第3の導体パターンと、第3の導体パターンから分岐されて制御素子が配置されるランドとの間に低域通過フィルタが挿入されているので、信号伝送線路から分岐されたランドや当該ランドに配置された制御素子がスタブとなることはなく、スタブにより信号伝送線路のインピーダンス整合が乱れて、高周波特性が悪化するのを防止できるという効果がある。

【0020】

請求項3の発明によれば、信号伝送線路を構成する第2及び第3の導体パターンと、第2及び第3の導体パターンから分岐されて制御素子が配置されるランドとの間に低域通過フィルタが挿入されているので、信号伝送線路から分岐されたランドや当該ランドに配置された制御素子がスタブとなることはなく、スタブにより信号伝送線路のインピーダンス整合が乱れて、高周波特性が悪化するのを防止できるという効果がある。

【0021】

請求項4の発明によれば、各MOSFETのゲート電極と制御素子の出力電極との間を電気的に接続する導電路の一部が、基板の表面に形成された中継用の導体パターンで構成されているので、ゲート電極と出力電極との間を金属細線で直接接続する場合に比べて、金属細線の長さを短くでき、金属細線の形状を保ちやすくなるとともに、断線の可能性を低減できるという効果がある。

【0022】

請求項5の発明によれば、中継用の導体パターンの途中に低域通過フィルタを挿入することによって、中継用の導体パターンや、MOSFETのゲート電極や制御素子の出力電極と中継用の導体パターンとの間を接続する金属細線がスタブとなるのを防止でき、スタブにより信号伝送線路のインピーダンス整合が乱れて、高周波特性が悪化するのを防止できるという効果がある。

【図面の簡単な説明】

【0023】

【図1】実施形態1を示し、パッケージ前のMOSFET付近の平面図である。

【図2】同上の概略構成を示す回路図である。

【図3】同上の詳細な回路図である。

【図4】実施形態2を示し、パッケージ前のMOSFET付近の平面図である。

【図5】実施形態3を示し、パッケージ前のMOSFET付近の平面図である。

【図6】同上の回路図である。

【図7】実施形態4を示し、パッケージ前のMOSFET付近の平面図である。

【図8】同上の回路図である。

【図9】従来の半導体リレーモジュールのブロック回路図である。

【図10】同上のパッケージ前のMOSFET付近の平面図である。

【図11】従来の別の半導体リレーモジュールを示し、パッケージ前のMOSFET付近の平面図である。

【発明を実施するための形態】

【0024】

以下に、本発明の技術思想を、高周波信号の伝送を許可又は遮断する半導体リレーモジュールに適用した実施形態について、図面を参照して説明する。

【0025】

(実施形態1)

本発明の実施形態1を図1〜図3に基づいて説明する。図2は本実施形態の半導体リレーモジュールAの概略的な回路図であり、この半導体リレーモジュールAは、高周波信号用の接続端子T1,T2と、低周波信号用の接続端子T3とを備える。

【0026】

高周波信号用の接続端子T1,T2間を接続する信号伝送線路110の途中には半導体スイッチ(以下、スイッチと略称す。)1が接続されている。このスイッチ1は制御回路3によってオン/オフが制御され、制御回路3の出力端とスイッチ1との間には、高周波帯域の信号に減衰を与える低域通過フィルタ(LPF)4が挿入されている。尚、LPF4は、カットオフ周波数の異なる2つのLPF41,42で構成されている。

【0027】

また、高周波信号用の接続端子T2とスイッチ1との間を接続する信号伝送線路110と、低周波信号用の接続端子T3との間には、高周波帯域の信号に減衰を与える低域通過フィルタ(以下、LPFと略称す。)6を介して半導体スイッチ(以下、スイッチと略称す。)2が接続されている。このスイッチ2は制御回路5によってオン/オフが制御される。

【0028】

次に、図3に示すより詳細な回路図を参照して半導体リレーモジュールAの各構成要素について説明を行う。

【0029】

高周波の信号伝送線路110に設けられたスイッチ1は、ソース電極同士が互いに接続されるとともに、ドレイン電極が接続端子T1,T2にそれぞれ接続された一対のMOSFET11,12からなる。

【0030】

スイッチ1のオン/オフを制御する制御回路3は、端子T4,T5を介して入力される入力信号に応じて光信号を発光する発光ダイオード(発光素子)31と、発光ダイオード31からの光信号を受光する受光素子を有し受光素子の出力に応じてMOSFET11,12をオン/オフする制御IC32(制御素子)とを備える。なお制御IC32は、図10で説明したものと同様の構成を有しており、発光ダイオード31の光信号を受光して光起電力を発生するフォトダイオードアレイ33(受光素子)と、フォトダイオードアレイ33が光起電力を発生しているときは、MOSFET11,12のゲート−ソース電極間に効率よく電荷を充電するよう制御するとともに、フォトダイオードアレイ33が光起電力を発生していないときはゲート−ソース電極間に充電された電荷の放電経路となることで、MOSFET11,12のドレイン−ソース間のインピーダンスを変化させる充放電回路34とで構成される。そして、制御IC32は、フォトダイオードアレイ33と充放電回路34とを含む回路を1つのパッケージ内に収納して構成されている。

【0031】

また、低周波信号用のスイッチ2は、上述したスイッチ1と同様、ソース電極同士が互いに接続された一対のMOSFET21,22からなり、一方のMOSFET21のドレイン電極Dは接続端子T3に接続され、他方のMOSFET22のドレイン電極DはLPF6を介して信号伝送線路110に接続されている。

【0032】

スイッチ2のオン/オフを制御する制御回路5は、端子T6,T7を介して入力される入力信号に応じて光信号を発光する発光ダイオード(発光素子)51と、発光ダイオード51からの光信号を受光する受光素子を有し受光素子の出力に応じてMOSFET21,22をオン/オフする制御IC52とを備えている。なお制御IC52は、上述の制御IC32と同様の構成を有しているので、その説明は省略する。

【0033】

この半導体リレーモジュールAは、図3の回路を構成する回路部品を、誘電体基板の表面に形成された回路パターン上に配置してある。図1は、MOSFET11,12およびその周辺部品を誘電体基板100に実装した状態を示すパッケージ前の平面図であり、図1を参照してMOSFET11,12近傍の実装状態を説明する。

【0034】

誘電体基板100の表面には、制御IC32が配置される実装用パターン131を分岐させた短冊状の第3の導体パターン(以下、導体パターンと略称す。)113が形成されるとともに、この導体パターン113を間にして左右方向の両側に帯状の第1及び第2の導体パターン(以下、導体パターンと略称す。)111,112が形成されている。これら導体パターン111,112,113は同一直線上に並ぶように配置されており、導体パターン111,112,113や、導体パターン111,112に実装されたMOSFET11,12のソース電極と導体パターン113の間を接続する後述のボンディングワイヤ200などから高周波信号の信号伝送線路110が構成されている。なお誘電体基板100には高周波信号の伝送方向(図1における左右方向)に沿って上記導体パターン111,112,113とともにマイクロストリップラインを構成するグランドライン(図示せず)が形成されている。

【0035】

実装用パターン131は、制御IC32が接続されるランド132と、LPF42の一端側が接続されるランド133と、ランド132,133間を接続する幅狭の導体パターン134とが連続一体に形成されて構成されている。この実装用パターン131と導体パターン113との間には、LPF42の他端側およびLPF41の一端側がそれぞれ接続される実装用パターン135が設けられている。実装用パターン135は、LPF42の他端側が接続されるランド136と、LPF41の一端側が接続されるランド137と、ランド136,137間を接続する幅狭のパターン138とが連続一体に形成されて構成されている。ここで、実装用パターン135,131は、高周波信号の伝送方向(図1における左右方向)と直交する方向(図1における上下方向)に向かって導体パターン113から延出するように設けられている。

【0036】

また誘電体基板100の表面には、制御IC32が配置されるランド132の近傍に、LED用の導体パターン121,122が形成されている。

【0037】

発光ダイオード31は上下両面にそれぞれ電極(アノード電極およびカソード電極)を有しており、上述した導体パターン121,122のうち、一方の導体パターン121にダイボンディングされて、下面電極が導体パターン121に電気的に接続されている。また発光ダイオード31の上面電極は、導電性の良好な金などの金属細線からなるボンディングワイヤ200を介して他方の導体パターン122に電気的に接続されている。

【0038】

制御IC32は、MOSFET11,12のゲート電極G,Gにそれぞれ接続される一対の電極32a,32bと、MOSFET11,12のソース電極S,Sに共通接続される電極32cを表面に備えている。この制御IC32は、ランド132上にダイボンディングされており、電極32cはボンディングワイヤ200を介してランド132に電気的に接続されている。

【0039】

LPF42は表面実装タイプのフィルタであり、両端に電極を有し、一端側の電極が実装用パターン131のランド133に接続され、他端側の電極が実装用パターン135のランド136に接続されるようにして両パターン131,135間に実装されている。またLPF41も表面実装タイプのフィルタからなり、両端に電極を有し、一端側の電極が実装用パターン135のランド137に接続され、他端側の電極が導体パターン113に接続されるように、両パターン135,113間に実装されている。

【0040】

またMOSFET11,12は、裏面にドレイン電極Dを備えるとともに、表面にソース電極Sおよびゲート電極Gを備えており、裏面のドレイン電極Dが導体パターン111,112にそれぞれ直接面接着されて、電気的に接続されている。MOSFET11,12のソース電極Sは、ボンディングワイヤ200を介して導体パターン113に電気的に接続されている。またMOSFET11,12のゲート電極G,Gは、それぞれ、ランド132上に実装された制御IC32の電極32a,32bにボンディングワイヤ200を介して電気的に接続されている。なお、制御IC32の共通電極32cは、ボンディングワイヤ200を介してランド132に接続されているので、LPF41,42および導体パターン113などを介して制御IC32の共通電極32cがMOSFET11,12のソース電極S,Sと電気的に接続されることになる。

【0041】

ここで、制御IC32の備えるフォトダイオードアレイ33が発光ダイオード31からの光信号を受光できるように、制御IC32と発光ダイオード31が配置されている。そして、発光ダイオード31と制御IC32とが透光性樹脂8で封止されることによって、発光ダイオード31とフォトダイオードアレイ33とが光学的に結合されており、さらに透光性樹脂8の表面が遮光性を有する部材で覆われることで、外乱光の入射が防止されるようになっている。

【0042】

上述のように本実施形態では、信号伝送線路110を構成する導体パターン113から、制御IC32が実装されるランド132を分岐させるとともに、導体パターン113とランド132との間にLPF4が挿入されているので、LPF4が高周波帯域の信号に減衰を与えることで、信号伝送線路110から分岐されたランド132(実装用パターン131)やこのランド132に配置された制御IC32がスタブとなって共振が発生するのを防止できる。したがって、スタブで共振が発生することにより、共振周波数付近でインサーションロスが増加して使用周波数帯域が狭くなるのを防止でき、スタブによって生じる高周波特性の悪化を防止することができる。

【0043】

ここにおいて、導体パターン113とランド132との間に挿入されるLPF4には、広帯域で減衰特性を持たせる必要があるが、本実施形態では、カットオフ周波数の異なる2つのLPF41,42を直列に接続してLPF4を構成することで、LPF4の広帯域化を図っている。なお、相対的に高い周波数の信号をカットするLPF42が、相対的に低い周波数の信号をカットするLPF41よりも導体パターン113に近い位置に配置された場合は、LPF42やそのフットパターン(実装用パターン135)がスタブとなってLPF41でカットできない周波数の共振が発生するため、高周波特性が悪化する可能性がある。したがって、本実施形態では、相対的に低い周波数の信号をカットするLPF41を、相対的に高い周波数の信号をカットするLPF42よりも導体パターン113に近い位置に配置しており、LPF41およびそのフットパターン(実装用パターン135)がスタブとなって共振が発生したとしても、その発振をLPF42でカットできるため、高周波特性を向上させることができる。また導体パターン113にはLPF41を接続するためのスタブが設けられておらず、LPF41は導体パターン113に直接実装されており、スタブとなるフットパターンを無くすことで、高周波特性の悪化を防止して、さらなる広帯域化を図ることができる。

【0044】

また、発光ダイオード31(発光素子)とともに透光性樹脂8で封止される制御IC32は、信号伝送線路110から分岐させたランド132上に配置されているので、発光ダイオード31および制御IC32を封止する封止部の配置を自由に設計できる。したがって、信号伝送線路110の途中に設けられたスイッチ1や他の回路部品とは離れた位置に封止部を配置することができ、流動性を有する透光性樹脂8がスイッチ1や他の回路部品の実装部位に流れていきにくくなるから、透光性樹脂8の形状を所望の形状に保つことが容易になる。

【0045】

次に、この半導体リレーモジュールAの動作について説明する。端子T6,T7間に信号が入力されていない状態では、発光ダイオード51が消灯しているので、制御IC52がスイッチ2(MOSFET21,22)をオフさせており、接続端子T3を介しての低周波信号の入出力が遮断される。

【0046】

そして、スイッチ2のオフ時に、端子T4,T5に信号が入力されていない状態では、発光ダイオード31が消灯しているので、制御IC32の充放電回路34がMOSFET11,12のゲート−ソース電極間に充電された電荷の放電経路になることで、MOSFET11,12のドレイン−ソース電極間を高インピーダンス状態とし、接続端子T1,T2間の信号伝送を遮断する。また、スイッチ2のオフ時に端子T4,T5間に信号が入力されると、発光ダイオード31が点灯し、発光ダイオード31の発光を受けて、制御IC32の充放電回路34がMOSFET11,12のゲート−ソース電極間に電荷を充電するよう制御することで、MOSFET11,12のドレイン−ソース電極間が低インピーダンス状態となるので、接続端子T1,T2間で高周波信号の伝送が許可される。而して、端子T4,T5間への信号入力の有無に応じて接続端子T1,T2間での高周波信号の伝送が許可又は遮断される。

【0047】

また、制御IC32がスイッチ1をオフさせた状態で、端子T6,T7間に信号が入力されると、発光ダイオード51の発光を受けて制御IC52が、MOSFET21,22のゲート−ソース電極間に電荷を充電するよう制御することによって、MOSFET21,22のドレイン−ソース電極間が低インピーダンス状態とされるので、接続端子T3に入力された低域の信号(低周波信号乃至直流信号)を接続端子T2に接続される機器(図示せず)に供給したり、接続端子T2に接続される機器から接続端子T2に入力された低域信号を接続端子T3から取り出すことができる。

【0048】

(実施形態2)

本発明の実施形態2について図4を参照して説明する。尚、MOSFET11,12のゲート電極G,Gと、制御IC32の電極32a,32bとの間を電気的に接続する構成以外は、実施形態1と同様であるので、共通する構成要素には同一の符号を付して、その説明は省略する。

【0049】

上述の実施形態1では、信号伝送線路110を構成する導体パターン111,112上にMOSFET11,12をそれぞれ配置して、信号伝送線路110を構成する導体パターン113から分岐させたランド132上に制御IC32を配置するとともに、MOSFET11のゲート電極Gと制御IC32の電極32aの間、MOSFET12のゲート電極Gと制御IC32の電極32bの間をそれぞれボンディングワイヤ200を介して直接接続しているため、ゲート電極G,Gと電極32a,32bの間を接続するボンディングワイヤ200の全長が長く、その形状が保ちにくくなっている。

【0050】

そこで、本実施形態では、図4に示すように誘電体基板100の表面においてMOSFET11,12の実装部位付近から制御IC32の実装部位付近まで、中継用の導体パターン141,142がそれぞれ形成されており、MOSFET11,12のゲート電極G,Gおよび制御IC32の電極32a,32bは、それぞれ、ボンディングワイヤ200を介して対応する導体パターン141,142に電気的に接続されている。すなわち、MOSFET11,12のゲート電極G,Gと、制御IC32の電極32a,32bとの間を電気的に接続する導電路の一部が、誘電体基板100の表面に形成された中継用の導体パターンで構成されているので、ゲート電極G,Gと出力電極32a,32bとの間をボンディングワイヤ200で直接接続する場合に比べて、ゲート電極G,Gと導体パターン141,142の間を接続するボンディングワイヤ200の長さや、電極32a,32bと導体パターン141,142の間を接続するボンディングワイヤ200の長さを短くでき、長さを短くすることでボンディングワイヤ200の形状を保ちやすくなるととともに、断線の可能性を低減することもできる。

【0051】

また本実施形態においても、表面実装タイプのLPF41は導体パターン113に直接実装されており、LPF41の接続されるフットパターンが導体パターン113に設けられていないので、スタブとなるフットパターンを無くすことで、高周波特性の悪化を防止することができる。

【0052】

ここで、導体パターン113においてLPF41が実装される部位は、接続される回路部品(LPF41)の影響によってインピーダンスが低下するため、本実施形態では導体パターン113の一側辺(LPF41が接続される側と反対側)を凹ませることによって、他の部位よりもパターン幅の狭い幅狭部113aが設けられている。したがって、導体パターン113においてLPF41が接続される部位(幅狭部113a)のパターン幅が、信号伝送線路110における他の部位のパターン幅よりも幅狭に形成されるので、LPF41が実装される部位のインピーダンスの低下を抑制して、高周波特性を改善することができる。

【0053】

(実施形態3)

本発明の実施形態3について図5及び図6を参照して説明する。実施形態2の半導体リレーモジュールでは、MOSFET11,12のゲート電極G,Gと制御IC32の出力電極32a,32bとの間をそれぞれ接続する導電路の一部を、誘電体基板100の表面に形成された導体パターン141,142で構成したものであるが、本実施形態では、図5及び図6に示すように、MOSFET11,12のゲート電極G,Gと制御IC32の出力電極32a,32bの間を中継するために設けた導体パターンの途中に低域通過フィルタ(LPF)7a,7bを挿入してある。尚、低域通過フィルタ7,7以外の構成は実施形態2と同様であるので、共通する構成要素には同一の符号を付して、その説明は省略する。

【0054】

低域通過フィルタ7a,7bは、それぞれ、2つのLPF71,72を直列に接続して構成されている。LPF71,72のカットオフ周波数は互いに異なっており、相対的に低い周波数の信号をカットするLPF71が、相対的に高い周波数の信号をカットするLPF72よりも導体パターン111,112に近い位置に配置されている。

【0055】

誘電体基板100の表面には、図5に示すように、MOSFET11,12の実装部位の近傍に、LPF71の一端側の電極が接続されるランド143がそれぞれ形成されるとともに、制御IC32の実装部位の近傍(左右両側)に、LPF72の一端側の電極が接続される実装用パターン145がそれぞれ形成されている。さらに、誘電体基板100の表面において、ランド143と実装用パターン145の間には、LPF71,72の他端側の電極が共通接続される実装用パターン144がそれぞれ形成されている。

【0056】

ここで、MOSFET11,12のゲート電極G,Gはボンディングワイヤ200を介してランド143,143に接続され、制御IC32の電極32a,32bはボンディングワイヤ200を介して実装用パターン145,145に接続されており、ランド143と実装用パターン144との間にはLPF71が、実装用パターン144と実装用パターン145との間にはLPF72がそれぞれ接続されている。

【0057】

而して、MOSFET11,12のゲート電極G,Gと、制御IC32の電極32a,32bとの間をそれぞれ接続する中継用の導体パターンの途中にLPF7(LPF71,72からなる)が挿入されることになり、中継用の導体パターンや、この導体パターンと制御IC32の出力電極32a,32bとの間を接続するボンディングワイヤ200がスタブとなるのを防止でき、スタブで共振が発生することによる高周波特性の悪化を防止することができる。

【0058】

(実施形態4)

本発明の実施形態4について図7及び図8を参照して説明する。上述の実施形態1〜3では、ソース電極同士が電気的に接続された一対のMOSFET11,12でスイッチ1が構成されているのに対して、本実施形態では、図8に示すようにドレイン電極同士が電気的に接続された一対のMOSFET11,12でスイッチ1が構成されている。そして、各MOSFET11,12のソース電極が接続される第2及び第3の導体パターン(以下、導体パターンと略称す。)111,112と、導体パターン111,112から分岐されて制御IC32,32がそれぞれ配置されるランド132,132との間にそれぞれLPF4a,4bが挿入されている。尚、MOSFET11,12と制御IC32,32とLPF4a,4b以外の構成は実施形態1〜3で説明した半導体リレーモジュールAと同様であるので、共通する構成要素には同一の符号を付して、その説明は省略する。

【0059】

図7は、誘電体基板100への各回路部品の実装状態を示す要部拡大図であり、誘電体基板100の表面には、MOSFET11,12の実装される帯状の第1の導体パターン(以下、導体パターンと略称す。)113が形成されるとともに、この導体パターン113を間にして両側に帯状の導体パターン111,112が形成されている。これら導体パターン111,112,113は同一直線上に並ぶように配置されており、導体パターン111,112,113や、導体パターン113に配置されたMOSFET11,12のソース電極と導体パターン111,112の間をそれぞれ接続するボンディングワイヤ200などから高周波信号の信号伝送線路110が構成されている。なお誘電体基板100には高周波信号の伝送方向に沿って上記導体パターン111,112,113とともにマイクロストリップラインを構成するグランドライン(図示せず)が形成されている。

【0060】

また誘電体基板100の表面には、制御IC32,32のそれぞれ実装される実装用パターン131,131が、導体パターン111,112から分岐させた形で形成されている。各実装用パターン131は、導体パターン113に対して信号伝送方向と直交する方向の片側に配置されて制御IC32が実装されるランド132と、ランド132において導体パターン113側の部位から信号伝送方向に沿って、互いに反対向きに延出し、LPF42の一方の電極が電気的に接続される接続パターン139とで形成されている。

【0061】

また誘電体基板100の表面には、制御IC32,32が実装されるランド132,132の近傍に、LED用導体パターン121,122が形成されている。

【0062】

MOSFET11,12は、いずれも裏面にドレイン電極を備えるとともに、表面にソース電極S及びゲート電極Gを備えている。そして、信号伝送線路110を構成する導体パターン113にMOSFET11,12をそれぞれダイボンディングすることによって、各々のドレイン電極が導体パターン113に電気的に接続されている。またMOSFET11,12のゲート電極G,Gはそれぞれボンディングワイヤ200を介して対応する制御IC32,32の電極32a又は32bに電気的に接続されている。またMOSFET11,12のソース電極S,Sは、それぞれボンディングワイヤ200を介して導体パターン111,112に電気的に接続されている。また導体パターン111(112)と、対応する実装用パターン135のランド137との間にはそれぞれLPF41が接続されており、さらに実装用パターン135のランド136と、対応するランド132から延出させた接続パターン139との間にはそれぞれLPF42が接続されている。

【0063】

このように本実施形態では、信号伝送線路110を構成する導体パターン111,112から、制御IC32,32が配置されるランド132,132を分岐させるとともに、導体パターン111,112とランド132,132との間にそれぞれLPF4a,4bが挿入されているので、LPF4a,4bが高周波帯域の信号に減衰を与えることで、信号伝送線路110から分岐されたランド132,132や各ランド132に配置された制御IC32がスタブとなって共振が発生するのを防止できる。したがって、スタブで共振が発生することにより、共振周波数付近でインサーションロスが増加して使用周波数帯域が狭くなるのを防止でき、スタブによって生じる高周波特性の悪化を防止することができる。

【0064】

ここにおいて、導体パターン111,112とランド132,132との間にそれぞれ挿入されるLPF4a,4bには、広帯域で減衰特性を持たせる必要があるが、本実施形態では、カットオフ周波数の異なる2つのLPF41,42を直列に接続してLPF4a,4bをそれぞれ構成することで、LPF4a,4bの広帯域化を図っている。なお、相対的に高い周波数の信号をカットするLPF42が、相対的に低い周波数の信号をカットするLPF41よりも導体パターン111,112に近い位置に配置された場合は、LPF42やそのフットパターン(実装用パターン135)がスタブとなってLPF41でカットできない周波数の共振が発生するため、高周波特性が悪化する可能性がある。したがって、本実施形態では、相対的に低い周波数の信号をカットするLPF41を、相対的に高い周波数の信号をカットするLPF42よりも導体パターン111,112に近い位置に配置しており、LPF41およびそのフットパターン(実装用パターン135)がスタブとなって共振が発生したとしても、その発振をLPF42でカットできるため、高周波特性を向上させることができる。また表面実装タイプのLPF41は導体パターン113に直接実装されており、LPF41が接続されるフットパターンを導体パターン113に設けた場合に比べて、スタブとなるフットパターンを無くすことで、高周波特性の悪化を防止でき、さらなる広帯域化を図ることができる。

【0065】

また、発光ダイオード31(発光素子)とともに透光性樹脂8で封止される制御IC32,32は、信号伝送線路110から分岐されたランド132,132上に配置されているので、発光ダイオード31および制御IC32,32を封止する封止部の配置を自由に設計できる。したがって、信号伝送線路100の途中に設けられたスイッチ1や他の回路部品とは離れた位置に封止部を配置することができ、流動性を有する透光性樹脂8がスイッチ1や他の回路部品の実装部位に流れていきにくくなるから、透光性樹脂8の形状を所望の形状に保つことが容易になる。

【0066】

尚、本実施形態においても実施形態2で説明したように、誘電体基板100の表面においてMOSFET11,12の実装部位付近から対応する制御IC32,32の実装部位付近まで、中継用の導体パターンを形成し、MOSFET11,12のゲート電極G,Gおよび制御IC32,32の電極32a,32bをそれぞれボンディングワイヤ200を介して中継用の導体パターンに接続してもよい。この場合、MOSFET11,12のゲート電極Gと制御IC32,32の電極32a,32bの間をボンディングワイヤ200で直接接続する場合に比べて、ボンディングワイヤ200の全長を短くできるので、ボンディングワイヤ200の形状を保ちやすくなり、また全長を短くすることで断線の可能性を少なくできるという利点もある。

【0067】

また実施形態3で説明したように、MOSFET11,12のゲート電極G,Gと制御IC32,32の電極32a,32bとの間を中継接続するために設けられた中継用の導体パターンの途中に低域通過フィルタを挿入することも好ましく、中継用の導体パターンや、制御IC32,32の電極32a,32bと中継用の導体パターンとの間を接続するボンディングワイヤ200がスタブとなるのを防止して、高周波特性の悪化を抑制することができる。

【0068】

また本実施形態においても、実施形態2で説明したように、導体パターン111,112においてLPF41が実装される部位のパターン幅を他の部位に比べて幅狭に形成しても良く、導体パターン111,112に接続されたLPF41の影響で配線路のインピーダンスが低下するのを抑制して、インピーダンス整合が乱れるのを防止することができる。

【0069】

次に、この半導体リレーモジュールAの動作について説明する。端子T6,T7間に信号が入力されていない状態では、発光ダイオード51が消灯しているので、制御IC52がスイッチ2(MOSFET21,22)をオフさせており、接続端子T3を介しての低周波信号の入出力が遮断される。

【0070】

そして、スイッチ2のオフ時に、端子T4,T5に信号が入力されていない状態では、発光ダイオード31が消灯しているので、制御IC32,32がMOSFET11,12のゲート−ソース電極間に充電された電荷の放電経路になることで、MOSFET11,12のドレイン−ソース電極間を高インピーダンス状態とし、接続端子T1,T2間の信号伝送を遮断する。また、スイッチ2のオフ時に端子T4,T5間に信号が入力されると、発光ダイオード31が点灯し、発光ダイオード31の発光を受けて、制御IC32,32の充放電回路がMOSFET11,12のゲート−ソース電極間に電荷を充電するよう制御することで、MOSFET11,12のドレイン−ソース電極間が低インピーダンス状態となるので、接続端子T1,T2間で高周波信号の伝送が許可される。而して、端子T4,T5間への信号入力の有無に応じて接続端子T1,T2間での高周波信号の伝送が許可又は遮断される。

【0071】

また、制御IC32,32がスイッチ1をオフさせた状態で、端子T6,T7間に信号が入力されると、発光ダイオード51の発光を受けて制御IC52が、MOSFET21,22のゲート−ソース電極間に電荷を充電するよう制御することによって、MOSFET21,22のドレイン−ソース電極間が低インピーダンス状態とされるので、接続端子T3に入力された低域の信号(低周波信号乃至直流信号)を接続端子T2に接続される機器(図示せず)に供給したり、接続端子T2に接続される機器から接続端子T2に入力された低域信号を接続端子T3から取り出すことができる。

【0072】

尚、図8の回路図では、端子T4,T5と端子T6,T7のY方向位置をずらして表記しているが、端子T4,T5と端子T6,T7のY方向位置が同じ位置となっていてもよい。

【符号の説明】

【0073】

A 半導体リレーモジュール

1 半導体スイッチ

4 LPF(低域通過フィルタ)

8 透光性樹脂

11,12 MOSFET

31 発光ダイオード(発光素子)

32 制御IC(制御素子)

33 フォトダイオードアレイ(受光素子)

34 充放電回路

100 誘電体基板

110 信号伝送線路

111〜113 導体パターン

132 ランド

【特許請求の範囲】

【請求項1】

基板の表面に設けられた信号伝送線路の途中に設けられて、信号を通過又は遮断する半導体スイッチと、

入力信号に応じて光信号を発光する発光素子と、

前記発光素子からの光信号を受光する受光素子を有し当該受光素子の出力に応じて前記半導体スイッチのオン/オフを制御する制御素子と、

前記制御素子が備える前記受光素子および前記発光素子を光学的に結合させた状態で樹脂封止する透光性樹脂とを備え、

前記制御素子は、前記信号伝送線路から分岐させたランド上に配置され、

前記信号伝送線路と前記ランドとの間に低域通過フィルタが挿入されたことを特徴とする半導体リレーモジュール。

【請求項2】

前記半導体スイッチは、ソース電極同士が電気的に接続される一対のMOSFETからなり、

前記信号伝送線路は、各MOSFETが配置されて各MOSFETのドレイン電極にそれぞれ電気的に接続される第1及び第2の導体パターンと、第1及び第2の導体パターンの間に配置されて各MOSFETのソース電極が共通接続される第3の導体パターンとを有し、

前記制御素子は、前記第3の導体パターンから分岐された前記ランド上に配置されるとともに、出力電極が各MOSFETのゲート電極に金属細線を介して電気的に接続され、各MOSFETのゲート−ソース電極間に制御電圧を印加することで各MOSFETのドレイン−ソース電極間のインピーダンスを変化させており、

前記ランドと前記第3の導体パターンとの間に前記低域通過フィルタが挿入されたことを特徴とする請求項1記載の半導体リレーモジュール。

【請求項3】

前記半導体スイッチは、ドレイン電極同士が電気的に接続される一対のMOSFETからなり、

前記信号伝送線路は、前記一対のMOSFETが信号の伝送方向に沿って配置され、各MOSFETのドレイン電極に電気的に接続される第1の導体パターンと、前記伝送方向において第1の導体パターンの両側にそれぞれ配置され、それぞれ対応するMOSFETのソース電極に電気的に接続される第2及び第3の導体パターンとを有し、

前記制御素子は、前記第2及び第3の導体パターンから分岐された前記ランド上に配置されるとともに、出力電極が各MOSFETのゲート電極に金属細線を介して電気的に接続され、各MOSFETのゲート−ソース電極間に制御電圧を印加することで各MOSFETのドレイン−ソース電極間のインピーダンスを変化させており、

第2及び第3の導体パターンと前記ランドとの間にそれぞれ前記低域通過フィルタが挿入されたことを特徴とする請求項1記載の半導体リレーモジュール。

【請求項4】

前記基板の表面において前記各MOSFETの実装部位付近から前記制御素子の実装部位付近まで中継用の導体パターンが設けられ、各MOSFETのゲート電極および前記制御素子の出力電極がそれぞれ金属細線を介して中継用の導体パターンに接続されたことを特徴とする請求項2又は3の何れか1項に記載の半導体リレーモジュール。

【請求項5】

前記中継用の導体パターンの途中に低域通過フィルタが挿入されたことを特徴とする請求項4記載の半導体リレーモジュール。

【請求項1】

基板の表面に設けられた信号伝送線路の途中に設けられて、信号を通過又は遮断する半導体スイッチと、

入力信号に応じて光信号を発光する発光素子と、

前記発光素子からの光信号を受光する受光素子を有し当該受光素子の出力に応じて前記半導体スイッチのオン/オフを制御する制御素子と、

前記制御素子が備える前記受光素子および前記発光素子を光学的に結合させた状態で樹脂封止する透光性樹脂とを備え、

前記制御素子は、前記信号伝送線路から分岐させたランド上に配置され、

前記信号伝送線路と前記ランドとの間に低域通過フィルタが挿入されたことを特徴とする半導体リレーモジュール。

【請求項2】

前記半導体スイッチは、ソース電極同士が電気的に接続される一対のMOSFETからなり、

前記信号伝送線路は、各MOSFETが配置されて各MOSFETのドレイン電極にそれぞれ電気的に接続される第1及び第2の導体パターンと、第1及び第2の導体パターンの間に配置されて各MOSFETのソース電極が共通接続される第3の導体パターンとを有し、

前記制御素子は、前記第3の導体パターンから分岐された前記ランド上に配置されるとともに、出力電極が各MOSFETのゲート電極に金属細線を介して電気的に接続され、各MOSFETのゲート−ソース電極間に制御電圧を印加することで各MOSFETのドレイン−ソース電極間のインピーダンスを変化させており、

前記ランドと前記第3の導体パターンとの間に前記低域通過フィルタが挿入されたことを特徴とする請求項1記載の半導体リレーモジュール。

【請求項3】

前記半導体スイッチは、ドレイン電極同士が電気的に接続される一対のMOSFETからなり、

前記信号伝送線路は、前記一対のMOSFETが信号の伝送方向に沿って配置され、各MOSFETのドレイン電極に電気的に接続される第1の導体パターンと、前記伝送方向において第1の導体パターンの両側にそれぞれ配置され、それぞれ対応するMOSFETのソース電極に電気的に接続される第2及び第3の導体パターンとを有し、

前記制御素子は、前記第2及び第3の導体パターンから分岐された前記ランド上に配置されるとともに、出力電極が各MOSFETのゲート電極に金属細線を介して電気的に接続され、各MOSFETのゲート−ソース電極間に制御電圧を印加することで各MOSFETのドレイン−ソース電極間のインピーダンスを変化させており、

第2及び第3の導体パターンと前記ランドとの間にそれぞれ前記低域通過フィルタが挿入されたことを特徴とする請求項1記載の半導体リレーモジュール。

【請求項4】

前記基板の表面において前記各MOSFETの実装部位付近から前記制御素子の実装部位付近まで中継用の導体パターンが設けられ、各MOSFETのゲート電極および前記制御素子の出力電極がそれぞれ金属細線を介して中継用の導体パターンに接続されたことを特徴とする請求項2又は3の何れか1項に記載の半導体リレーモジュール。

【請求項5】

前記中継用の導体パターンの途中に低域通過フィルタが挿入されたことを特徴とする請求項4記載の半導体リレーモジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2011−4381(P2011−4381A)

【公開日】平成23年1月6日(2011.1.6)

【国際特許分類】

【出願番号】特願2009−196067(P2009−196067)

【出願日】平成21年8月26日(2009.8.26)

【出願人】(000005832)パナソニック電工株式会社 (17,916)

【Fターム(参考)】

【公開日】平成23年1月6日(2011.1.6)

【国際特許分類】

【出願日】平成21年8月26日(2009.8.26)

【出願人】(000005832)パナソニック電工株式会社 (17,916)

【Fターム(参考)】

[ Back to top ]