半導体リレー

【課題】出力用MOSFETにおけるゲート酸化膜の絶縁劣化を防止する。

【解決手段】出力用MOSFET16a、16bの各ゲート・ソース間に、2つの抵抗R1、R2と、抵抗R2に並列に接続されたダイオードD1から構成されるクランプ回路を接続する。フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、抵抗R2における電圧降下がダイオードD1の順方向電圧に略等しくなり、出力用MOSFET16a、16bのゲートには、フォトダイオードアレイ13の出力電圧がそのまま印加される。一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R2における電圧降下がダイオードの順方向電圧で固定されるので、20Vの電圧が印加される。

【解決手段】出力用MOSFET16a、16bの各ゲート・ソース間に、2つの抵抗R1、R2と、抵抗R2に並列に接続されたダイオードD1から構成されるクランプ回路を接続する。フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、抵抗R2における電圧降下がダイオードD1の順方向電圧に略等しくなり、出力用MOSFET16a、16bのゲートには、フォトダイオードアレイ13の出力電圧がそのまま印加される。一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R2における電圧降下がダイオードの順方向電圧で固定されるので、20Vの電圧が印加される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力信号を光電変換して得られる起電力に基づいて、負荷電流を開閉する半導体リレーに関する。

【背景技術】

【0002】

入力信号に基づいて発光する発光素子と、発光素子からの光信号を受光して起電力を発生する受光素子を備え、この起電力によって出力用MOSFETをオン、オフする半導体リレーが知られている(例えば、特許文献1参照)。

【0003】

図7は、従来の半導体リレーの構成を示す図である。図7における半導体リレー7は、入力端子71a、71bからの入力信号に応答して光信号を生成するLED等の発光素子72と、光信号を受光して起電力を発生するフォトダイオードアレイ73と、発生した起電力を充放電する充放電回路74と、充放電回路74からの電圧に対応して導通・遮断する2つの出力用MOSFET76a、76bから構成されている。

【0004】

出力用MOSFET76a、76bに炭化珪素(SiC)を材料としたSiC−MOSFETが用いられる場合、このSiC−MOSFETはドレイン・ソース間を導通させるためのしきい値電圧が3V以上と高くなる。

【0005】

一方、フォトダイオードアレイ73の起電力には、略−120mV/℃の温度勾配がある。例えば、半導体リレー7の動作温度範囲を−40〜85℃、出力用MOSFET76a、76bのゲート最大定格電圧を20Vとすると、ゲート印加電圧が動作温度範囲内で最大定格電圧以下となるには、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定する必要がある。すると、次の式(1)に示すように、室温(20℃)におけるゲート印加電圧が下がってしまう。

【0006】

20V−{120mV・(25+40)}=12.2V・・・(1)

【0007】

しかしながら、ゲート印加電圧が12.2Vでは、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することができない場合がある。

【0008】

これらの問題点を回避するには、発光素子72の発光光量を増加させるか、又は、フォトダイオードアレイ73のセル数を増やすことによって起電力を上げることが望ましいが、SiC−MOSFETのゲート酸化膜は500Åと薄いので、ゲート酸化膜の絶縁劣化あるいは破壊を防止する必要がある。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平8-204533号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は、前記実情に鑑みてなされたもので、フォトダイオードアレイの起電力が大きくなっても、出力用MOSFETのゲート酸化膜の絶縁劣化を防止することのできる半導体リレーを提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明は、入力信号に応答して光信号を生成する発光素子と、前記光信号を受光して電圧を発生するフォトダイオードアレイと、前記フォトダイオードアレイによって発生した電圧を充放電する充放電回路と、前記充放電回路にゲート及びソースが接続された出力用MOSFETを備える半導体リレーにおいて、前記充放電回路と前記出力用MOSFETの間に、前記フォトダイオードアレイによって発生した電圧を制限するクランプ回路を接続し、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の一方あるいは双方に、並列に接続された電圧クランプ手段とを具備したことを特徴とするものである。

【0012】

この構成により、フォトダイオードアレイの起電力が大きくなっても、出力用MOSFETのゲート印加電圧を、導通に必要十分なレベルに維持することができるので、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0013】

また、本発明は、上記の半導体リレーにおいて、前記クランプ手段は、前記2つの抵抗の一方に、並列に接続されたダイオードと、から構成されることを特徴とする。すなわち、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の一方に、並列に接続されたダイオードと、から構成されることを特徴とするものを含む。

【0014】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、ダイオードが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0015】

また、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の接続点にゲートが接続され、前記出力用MOSFETの前記ゲートに抵抗を介してドレインが接続され、前記出力用MOSFETの前記ソースにソースが接続されたNチャネルFETと、から構成されることを特徴とするものを含む。

【0016】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、NチャネルFETが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0017】

また、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の接続点にゲートが接続され、前記出力用MOSFETの前記ゲートにソースが接続され、前記出力用MOSFETの前記ソースに抵抗を介してドレインが接続されたPチャネルFETと、から構成されることを特徴とするものを含む。

【0018】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、PチャネルFETが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0019】

また、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の接続点にベースが接続され、前記出力用MOSFETの前記ゲートに抵抗を介してコレクタが接続され、前記出力用MOSFETの前記ソースにエミッタが接続されたNPNバイポーラトランジスタと、から構成されることを特徴とするものを含む。

【0020】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、NPNバイポーラトランジスタが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0021】

また、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の接続点にベースが接続され、前記出力用MOSFETの前記ゲートにエミッタが接続され、前記出力用MOSFETの前記ソースに抵抗を介してコレクタが接続されたPNPバイポーラトランジスタと、から構成されることを特徴とするものを含む。

【0022】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、PNPバイポーラトランジスタが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0023】

更に、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に接続されたツェナーダイオードから構成されることを特徴とするものを含む。

【0024】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、ツェナーダイオードのツェナー電圧によって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を、導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【発明の効果】

【0025】

本発明によれば、フォトダイオードアレイの起電力が大きくなっても、出力用MOSFETのゲート酸化膜の絶縁劣化を防止することのできる半導体リレーを提供できる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施の形態1に係る半導体リレーの概略構成を示す図

【図2】本発明の実施の形態2に係る半導体リレーの概略構成を示す図

【図3】本発明の実施の形態3に係る半導体リレーの概略構成を示す図

【図4】本発明の実施の形態3に係る半導体リレーにおいて、変形例の概略構成を示す図

【図5】本発明の実施の形態4に係る半導体リレーの概略構成を示す図

【図6】本発明の実施の形態4に係る半導体リレーにおいて、変形例の概略構成を示す図

【図7】従来の半導体リレーの概略構成を示す図

【発明を実施するための形態】

【0027】

以下、本発明の実施の形態に係る半導体リレーについて、図面を用いて説明する。

【0028】

(実施の形態1)

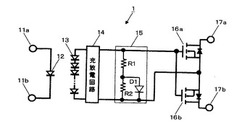

図1は、本発明の実施の形態1に係る半導体リレーの概略構成を示す図である。同図に示すように、本実施の形態の半導体リレー1は、第1の入力端子11aと第2の入力端子11bを有するLED等の発光素子12と、発光素子12と絶縁されたフォトダイオードセルを直列に接続してなり、発光素子12の発光に応じて起電力を発生し電圧を出力するフォトダイオードアレイ13と、フォトダイオードアレイ13の出力電圧を充放電する充放電回路14と、フォトダイオードアレイ13の出力電圧を所定電圧に制限するクランプ回路15と、所定電圧の出力電圧をゲートに印加することによってドレインとソースの間がオン、オフされる炭化珪素(SiC)を材料とする2つの出力用MOSFET16a、16bを有する構成である。

【0029】

2つの出力用MOSFET16a、16bは、それぞれのゲートがクランプ回路15を介してフォトダイオードアレイ13のアノード端子に接続され、それぞれのソースが互いに逆直列に接続された上でクランプ回路15を介してフォトダイオードアレイ13のカソード端子に接続される。また、出力用MOSFET16aのドレインは第1の出力端子17aに接続され、出力用MOSFET16bのドレインが第2の出力端子17bに接続されている。

【0030】

クランプ回路15は、2つの出力用MOSFET16a、16bのゲートとソース間に直列に接続された抵抗R1、R2と、抵抗R2に並列に接続されたダイオードD1から構成される。なお、抵抗R1、R2の抵抗値は、例えば、R1が19.3MΩ、R2が0.7MΩである。

【0031】

次に、このように構成された本発明の実施の形態1に係る半導体リレーの動作について説明する。

【0032】

発光素子12は、第1及び第2の入力端子11a、11bから入力信号が入力されることによって発光し、光信号を生成する。フォトダイオードアレイ13は、発光素子12の光信号を受光してその両端で起電力を発生し、電圧を出力する。

【0033】

充放電回路14は、フォトダイオードアレイ13の出力電圧を充放電し、クランプ回路15を介して出力用MOSFET16a、16bのゲートに印加する。そして、出力用MOSFET16a、16bのゲートに印加されるフォトダイオードアレイ13の出力電圧がしきい値電圧Vthよりも大きくなると、出力用MOSFET16a、16bのドレイン・ソース間がオンになり、第1及び第2の出力端子17a、16bの間が導通して、リレーが閉じられる。

【0034】

一方、第1及び第2の入力端子11a、11bにおいて入力信号がオフになると、充放電回路14からの出力電圧がなくなり、出力用MOSFET16a、16bのドレイン・ソース間がオフとなって、第1及び第2の出力端子17a、16bの間が遮断し、リレーが開放される。

【0035】

次に、クランプ回路15の動作について説明する。

【0036】

クランプ回路15は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、抵抗R2における電圧降下がダイオードD1の順方向電圧Vf(約0.7V)に略等しくなるので、出力用MOSFET16a、16bのゲートには、フォトダイオードアレイ13の出力電圧がそのまま印加される。

【0037】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R2における電圧降下がダイオードD1の順方向電圧Vfで固定される。そのため、例えば発光素子12の発光量が増えることによってフォトダイオードアレイ13の起電力が増し、出力電圧が上昇しようとしても、電流が増加するだけで出力電圧が高くなることはない。

【0038】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化がゲート印加電圧の20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0039】

なお、実際には、ダイオードD1の順方向電圧Vfにも−1〜2mV/℃の温度勾配があるが、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は、次の式(2)で計算されるように小さい値である。

【0040】

−1〜2×(19.3+0.7)/0.7≒−30mV/℃・・・(2)

【0041】

この値は、クランプ回路15がない場合の―120mV/℃に比較して大幅に改善されており、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0042】

以上説明したように、このような本発明の実施の形態1に係る半導体リレーによれば、入力信号に応答して光信号を生成する発光素子と、光信号を受光して起電力を発生するフォトダイオードアレイと、フォトダイオードアレイで発生した起電力の電圧を充放電する充放電回路と、ゲート及びソースが充放電回路を介してフォトダイオードアレイに接続された2つの出力用MOSFETを備える半導体リレーにおいて、2つの出力用MOSFETの各ゲート・ソース間に、直列に接続された2つの抵抗と、抵抗の一方に並列に接続されたダイオードから構成されるクランプ回路を接続する。

【0043】

これにより、フォトダイオードアレイの出力電圧が設計値の例えば20V以上になった場合でも、抵抗の一方における電圧降下がダイオードの順方向電圧Vfで固定されるので、2つの出力用MOSFETには20V以上のゲート電圧が印加されることがなく、ゲート酸化膜の絶縁劣化を防止することができる。

【0044】

(実施の形態2)

図2は、本発明の実施の形態2に係る半導体リレーの概略構成を示す図である。同図に示すように、本実施の形態の半導体リレー2は、図1に示した実施の形態1に係る半導体リレー1において、クランプ回路15に替えてクランプ回路25を有する構成である。なお、図1と同じ構成要素については、同一符号を付して説明を簡略にし、若しくは省略する。

【0045】

クランプ回路25は、ツェナー電圧が例えば20VであるツェナーダイオードZD1から構成される。

【0046】

次に、このように構成された本発明の実施の形態2に係る半導体リレーの動作について説明する。なお、リレー動作は実施の形態1と同じであるので説明を省略し、クランプ回路25の動作のみを説明する。

【0047】

クランプ回路25は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、ツェナーダイオードZD1にツェナー電流が流れることはないので、フォトダイオードアレイ13の出力電圧がそのまま出力用MOSFET16a、16bのゲートに印加される。

【0048】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、ツェナーダイオードZD1にツェナー電流が流れ、ツェナー電圧で制限された20Vの電圧が出力用MOSFET16a、16bのゲートに印加される。

【0049】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化がゲート印加電圧の20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0050】

なお、実際には、ツェナーダイオードZD1のツェナー電圧にも温度勾配があるが、この値は略−30mV/℃であって、クランプ回路25がない場合の、―120mV/℃に比較して大幅に改善されており、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0051】

以上説明したように、このような本発明の実施の形態2に係る半導体リレーによれば、入力信号に応答して光信号を生成する発光素子と、光信号を受光して起電力を発生するフォトダイオードアレイと、フォトダイオードアレイで発生した起電力の電圧を充放電する充放電回路と、ゲート及びソースが充放電回路を介してフォトダイオードアレイに接続された2つの出力用MOSFETを備える半導体リレーにおいて、2つの出力用MOSFETのゲート及びソース間に、ツェナー電圧が例えば20Vであるツェナーダイオードから構成されるクランプ回路を接続する。

【0052】

これにより、フォトダイオードアレイの出力電圧が設計値の例えば20Vを超えた場合でも、ツェナーダイオードのツェナー電圧20Vで制限されるので、2つの出力用MOSFETに20V以上のゲート電圧が印加されることがなく、ゲート酸化膜の絶縁劣化を防止できる。

【0053】

(実施の形態3)

図3は、本発明の実施の形態3に係る半導体リレーの概略構成を示す図である。同図に示すように、本実施の形態の半導体リレー3は、図1に示した実施の形態1に係る半導体リレー1において、クランプ回路15に替えてクランプ回路35を有する構成である。なお、図1と同じ構成要素については同一符号を付して説明を簡略にし、若しくは省略する。

【0054】

クランプ回路35は、2つの出力用MOSFET16a、16bのゲート・ソース間に直列に接続された抵抗R3、R4と、抵抗R3、R4の接続点にゲートが接続され、出力用MOSFET16a、16bの各ゲートに抵抗R5を介してドレインが接続され、出力用MOSFET16a、16bの各ソースにソースが接続されたNチャネルFET(Q1)から構成される。なお、抵抗R3〜R5の各抵抗値は、例えば、R3が19MΩ、R4が1MΩ、R5が抵抗R3、R4の各抵抗値の和20MΩより十分小さい値である。

【0055】

次に、このように構成された本発明の実施の形態3に係る半導体リレーの動作について説明する。なお、リレー動作は実施の形態1と同じであるので説明を省略し、クランプ回路35の動作のみを説明する。

【0056】

クランプ回路35は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、NチャネルFET(Q1)のゲートに印加される抵抗R3、R4によって分圧された電圧は、NチャネルFET(Q1)をオンするための略1Vのしきい値を超えることはない。そのため、NチャネルFET(Q1)はオフのままであり、出力用MOSFET16a、16bのゲートには、20V以下のフォトダイオードアレイ13の出力電圧がそのまま印加される。

【0057】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R3、R4によって分圧された電圧は、しきい値の略1Vを超え、NチャネルFET(Q1)がオンしてドレイン・ソース間が導通する。そのため、例えば発光素子12の発光量が増えることによって、フォトダイオードアレイ13の出力電圧が上昇しようとしても、電流が増加するだけで出力電圧が高くなることはない。

【0058】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化が20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0059】

なお、実際には、NチャネルFET(Q1)のしきい値電圧にも温度勾配があるが、この値は略−2mV/℃であって、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は−20mV/℃程度と小さく、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0060】

図4は、本発明の実施の形態3に係る半導体リレーにおいて、変形例の概略構成を示す図である。同図に示すように、変形例の半導体リレー4は、図3に示した本実施の形態に係る半導体リレー3におけるクランプ回路35に替えて、クランプ回路45を有する構成である。

【0061】

クランプ回路45は、2つの出力用MOSFET16a、16bのゲートとソース間に直列に接続された抵抗R6、R7と、抵抗R6、R7の接続点にゲートが接続され、出力用MOSFET16a、16bの各ゲートにソースが接続され、出力用MOSFET16a、16bの各ソースに抵抗R8を介してドレインが接続されたPチャネルFET(Q2)から構成される。なお、抵抗R6〜R8の各抵抗値は、例えば、R6が19MΩ、R7が1MΩ、R8が抵抗R6、R7の各抵抗値の和20MΩより十分小さい値である。

【0062】

このように構成された本発明の実施の形態3に係る半導体リレーの変形例において、クランプ回路45の動作を説明する。

【0063】

クランプ回路45は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、PチャネルFET(Q2)のゲートに印加される抵抗R6、R7によって分圧された電圧は、PチャネルFET(Q2)をオンするための略−1Vのしきい値を超えることはない。そのためPチャネルFET(Q2)はオフのままであり、出力用MOSFET16a、16bのゲート・ソース間には、20V以下のフォトダイオードアレイ13の出力電圧がそのまま印加される。

【0064】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R6、R7によって分圧された電圧は、しきい値の略−1Vを超え、PチャネルFET(Q2)がオンしてドレイン・ソース間が導通する。そのため、例えば発光素子12の発光量が増えることによって、フォトダイオードアレイ13の出力電圧が上昇しようとしても、電流が増加するだけで出力電圧は増えることはない。

【0065】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化が20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0066】

なお、実際には、PチャネルFET(Q2)のしきい値電圧にも温度勾配があるが、この値は略−2mV/℃であって、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は−20mV/℃程度と小さく、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0067】

以上説明したように、このような本発明の実施の形態3に係る半導体リレーによれば、入力信号に応答して光信号を生成する発光素子と、光信号を受光して起電力を発生するフォトダイオードアレイと、フォトダイオードアレイで発生した起電力の電圧を充放電する充放電回路と、ゲート及びソースが充放電回路を介してフォトダイオードアレイに接続された2つの出力用MOSFETを備える半導体リレーにおいて、2つの出力用MOSFETのゲート及びソース間に、直列に接続された2つの抵抗と、両抵抗の接続点にゲートが接続され、2つの出力用MOSFETの各ゲートに抵抗を介してドレインが接続され、出力用MOSFETの各ソースにソースが接続されたNチャネルFETから構成されるクランプ回路を接続する。

【0068】

また、クランプ回路は、2つの出力用MOSFETのゲートとソース間に、直列に接続された2つの抵抗と、両抵抗の接続点にゲートが接続され、2つの出力用MOSFETの各ゲートにソースが接続され、各ソースに抵抗を介してドレインが接続されたPチャネルFETから構成されるものであってもよい。

【0069】

これにより、フォトダイオードアレイの出力電圧が設計値の例えば20Vを超えた場合でも、2つの抵抗によって分圧された電圧は、NチャネルFET及びPチャネルFETの各しきい値であるそれぞれ略1V及び略−1Vを超えてドレイン・ソース間が導通するので、2つの出力用MOSFETに20V以上のゲート電圧が印加されることがなく、ゲート酸化膜の絶縁劣化を防止できる。

【0070】

(実施の形態4)

図5は、本発明の実施の形態5に係る半導体リレーの概略構成を示す図である。同図に示すように、本実施の形態の半導体リレー4は、図1に示した実施の形態1に係る半導体リレー1において、クランプ回路15に替えてクランプ回路55を有する構成である。なお、図1と同じ構成要素については、同一符号を付して説明を簡略にし、若しくは省略する。

【0071】

クランプ回路55は、2つの出力用MOSFET16a、16bのゲートとソース間に直列に接続された抵抗R9、R10と、抵抗R9、R10の接続点にベースが接続され、出力用MOSFET16a、16bの各ゲートに抵抗R11を介してコレクタが接続され、出力用MOSFET16a、16bの各ソースにエミッタが接続されたNPNバイポーラトランジスタQ3から構成される。なお、抵抗R9〜R11の各抵抗値は、例えば、R9が30MΩ、R10が1MΩ、R11が抵抗R9、R10の各抵抗値の和31MΩより十分小さい値である。

【0072】

次に、このように構成された本発明の実施の形態4に係る半導体リレーの動作について説明する。なお、リレー動作は実施の形態1と同じであるので説明を省略し、クランプ回路55の動作のみを説明する。

【0073】

クランプ回路55は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、NPNバイポーラトランジスタQ3のベースに印加される抵抗R9、R10によって分圧された電圧は、NPNバイポーラトランジスタQ3をオンするためのベース・エミッタ電圧Vbeの略0.7Vを超えることはない。そのため、NPNバイポーラトランジスタQ3はオフのままであり、出力用MOSFET16a、16bのゲート・ソース間には、20V以下のフォトダイオードアレイ13の出力電圧がそのまま印加される。

【0074】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R9、R10によって分圧された電圧は、Vbeの略0.7Vを超え、NPNバイポーラトランジスタQ3がオンしてコレクタ・エミッタ間が導通する。そのため、例えば発光素子12の発光量が増えることによって、フォトダイオードアレイ13の出力電圧が上昇しようとしても、電流が増加するだけで出力電圧が高くなることはない。

【0075】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化が20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0076】

なお、実際には、NPNバイポーラトランジスタQ3のベース・エミッタ電圧Vbeにも温度勾配があるが、この値は略−2mV/℃であって、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は−20mV/℃程度と小さく、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0077】

図6は、本発明の実施の形態4に係る半導体リレーにおいて、変形例の概略構成を示す図である。同図に示すように、本変形例の半導体リレー6は、図5に示した本実施の形態に係る半導体リレー5におけるクランプ回路55に替えてクランプ回路65を有する構成である。

【0078】

クランプ回路65は、2つの出力用MOSFET16a、16bのゲートとソース間に直列に接続された抵抗R12、R13と、抵抗R12、R13の接続点にベースが接続され、出力用MOSFET16a、16bの各ゲートにエミッタが接続され、出力用MOSFET16a、16bの各ソースに抵抗R14を介してコレクタが接続されたPNPバイポーラトランジスタQ4から構成される。

【0079】

このように構成された本発明の実施の形態4に係る半導体リレーの変形例において、クランプ回路65の動作を説明する。

【0080】

クランプ回路65は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、PNPバイポーラトランジスタQ4のベースに印加される抵抗R12、R13によって分圧された電圧は、PNPバイポーラトランジスタQ4をオンするためのベース・エミッタ電圧Vbeの略−0.7Vを超えることはない。そのため、PNPバイポーラトランジスタQ4はオフのままであり、出力用MOSFET16a、16bのゲート・ソース間には、20V以下のフォトダイオードアレイ13の出力電圧がそのまま印加される。

【0081】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R6、R7によって分圧された電圧は、Vbeの略−0.7Vを超え、PNPバイポーラトランジスタQ4がオンしてコレクタ・エミッタ間が導通する。そのため、例えば発光素子12の発光量が増えることによって、フォトダイオードアレイ13の出力電圧が上昇しようとしても、電流が増加するだけで出力電圧が高くなることはない。

【0082】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化が20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0083】

なお、実際には、PNPバイポーラトランジスタQ4のベース・エミッタ電圧Vbeにも温度勾配があるが、この値は略−2mV/℃であって、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は−20mV/℃程度と小さく、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0084】

以上説明したように、このような本発明の実施の形態4に係る半導体リレーによれば、入力信号に応答して光信号を生成する発光素子と、光信号を受光して起電力を発生するフォトダイオードアレイと、フォトダイオードアレイで発生した起電力の電圧を充放電する充放電回路と、ゲート及びソースが充放電回路を介してフォトダイオードアレイに接続された2つの出力用MOSFETを備える半導体リレーにおいて、2つの出力用MOSFETのゲート及びソース間に、直列に接続された2つの抵抗と、両抵抗の接続点にベースが接続され、出力用MOSFETの各ゲートに抵抗を介してコレクタが接続され、出力用MOSFETの各ソースにエミッタが接続されたNPNバイポーラトランジスタから構成されるクランプ回路を接続する。

【0085】

また、クランプ回路は、2つの出力用MOSFETのゲートとソース間に直列に接続された2つの抵抗と、両抵抗の接続点にベースが接続され、2つの出力用MOSFETの各ゲートにエミッタが接続され、各ソースに抵抗を介してコレクタが接続されたPNPバイポーラトランジスタから構成されるものであってもよい。

【0086】

これにより、フォトダイオードアレイの出力電圧が設計値の例えば20Vを超えた場合でも、2つの抵抗によって分圧された電圧は、NPNバイポーラトランジスタ及びPNPバイポーラトランジスタのベース・エミッタ電圧Vbeの略0.7V及び略−0.7Vを超えてコレクタ・エミッタ間が導通するので、2つの出力用MOSFETに20V以上のゲート電圧が印加されることがなく、ゲート酸化膜の絶縁劣化を防止できる。

【符号の説明】

【0087】

1〜6 半導体リレー

12 発光素子

13 フォトダイオードアレイ

14 充放電回路

15、25、35、45、55、65 クランプ回路

16a、16b 出力用MOSFET

D1 ダイオード

R1〜R14 抵抗

Q1 NチャネルFET

Q2 PチャネルFET

Q3 NPNバイポーラトランジスタ

Q4 PNPバイポーラトランジスタ

ZD1 ツェナーダイオード

【技術分野】

【0001】

本発明は、入力信号を光電変換して得られる起電力に基づいて、負荷電流を開閉する半導体リレーに関する。

【背景技術】

【0002】

入力信号に基づいて発光する発光素子と、発光素子からの光信号を受光して起電力を発生する受光素子を備え、この起電力によって出力用MOSFETをオン、オフする半導体リレーが知られている(例えば、特許文献1参照)。

【0003】

図7は、従来の半導体リレーの構成を示す図である。図7における半導体リレー7は、入力端子71a、71bからの入力信号に応答して光信号を生成するLED等の発光素子72と、光信号を受光して起電力を発生するフォトダイオードアレイ73と、発生した起電力を充放電する充放電回路74と、充放電回路74からの電圧に対応して導通・遮断する2つの出力用MOSFET76a、76bから構成されている。

【0004】

出力用MOSFET76a、76bに炭化珪素(SiC)を材料としたSiC−MOSFETが用いられる場合、このSiC−MOSFETはドレイン・ソース間を導通させるためのしきい値電圧が3V以上と高くなる。

【0005】

一方、フォトダイオードアレイ73の起電力には、略−120mV/℃の温度勾配がある。例えば、半導体リレー7の動作温度範囲を−40〜85℃、出力用MOSFET76a、76bのゲート最大定格電圧を20Vとすると、ゲート印加電圧が動作温度範囲内で最大定格電圧以下となるには、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定する必要がある。すると、次の式(1)に示すように、室温(20℃)におけるゲート印加電圧が下がってしまう。

【0006】

20V−{120mV・(25+40)}=12.2V・・・(1)

【0007】

しかしながら、ゲート印加電圧が12.2Vでは、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することができない場合がある。

【0008】

これらの問題点を回避するには、発光素子72の発光光量を増加させるか、又は、フォトダイオードアレイ73のセル数を増やすことによって起電力を上げることが望ましいが、SiC−MOSFETのゲート酸化膜は500Åと薄いので、ゲート酸化膜の絶縁劣化あるいは破壊を防止する必要がある。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平8-204533号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明は、前記実情に鑑みてなされたもので、フォトダイオードアレイの起電力が大きくなっても、出力用MOSFETのゲート酸化膜の絶縁劣化を防止することのできる半導体リレーを提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明は、入力信号に応答して光信号を生成する発光素子と、前記光信号を受光して電圧を発生するフォトダイオードアレイと、前記フォトダイオードアレイによって発生した電圧を充放電する充放電回路と、前記充放電回路にゲート及びソースが接続された出力用MOSFETを備える半導体リレーにおいて、前記充放電回路と前記出力用MOSFETの間に、前記フォトダイオードアレイによって発生した電圧を制限するクランプ回路を接続し、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の一方あるいは双方に、並列に接続された電圧クランプ手段とを具備したことを特徴とするものである。

【0012】

この構成により、フォトダイオードアレイの起電力が大きくなっても、出力用MOSFETのゲート印加電圧を、導通に必要十分なレベルに維持することができるので、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0013】

また、本発明は、上記の半導体リレーにおいて、前記クランプ手段は、前記2つの抵抗の一方に、並列に接続されたダイオードと、から構成されることを特徴とする。すなわち、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の一方に、並列に接続されたダイオードと、から構成されることを特徴とするものを含む。

【0014】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、ダイオードが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0015】

また、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の接続点にゲートが接続され、前記出力用MOSFETの前記ゲートに抵抗を介してドレインが接続され、前記出力用MOSFETの前記ソースにソースが接続されたNチャネルFETと、から構成されることを特徴とするものを含む。

【0016】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、NチャネルFETが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0017】

また、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の接続点にゲートが接続され、前記出力用MOSFETの前記ゲートにソースが接続され、前記出力用MOSFETの前記ソースに抵抗を介してドレインが接続されたPチャネルFETと、から構成されることを特徴とするものを含む。

【0018】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、PチャネルFETが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0019】

また、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の接続点にベースが接続され、前記出力用MOSFETの前記ゲートに抵抗を介してコレクタが接続され、前記出力用MOSFETの前記ソースにエミッタが接続されたNPNバイポーラトランジスタと、から構成されることを特徴とするものを含む。

【0020】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、NPNバイポーラトランジスタが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0021】

また、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、前記2つの抵抗の接続点にベースが接続され、前記出力用MOSFETの前記ゲートにエミッタが接続され、前記出力用MOSFETの前記ソースに抵抗を介してコレクタが接続されたPNPバイポーラトランジスタと、から構成されることを特徴とするものを含む。

【0022】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、PNPバイポーラトランジスタが導通することによって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【0023】

更に、本発明は、上記の半導体リレーにおいて、前記クランプ回路は、前記出力用MOSFETの前記ゲート及び前記ソース間に接続されたツェナーダイオードから構成されることを特徴とするものを含む。

【0024】

この構成により、フォトダイオードアレイの起電力が大きくなった場合に、ツェナーダイオードのツェナー電圧によって出力電圧がクランプされ、出力用MOSFETのゲート印加電圧を、導通に必要十分なレベルに維持することができ、ゲート酸化膜の絶縁劣化を防止することが可能となる。

【発明の効果】

【0025】

本発明によれば、フォトダイオードアレイの起電力が大きくなっても、出力用MOSFETのゲート酸化膜の絶縁劣化を防止することのできる半導体リレーを提供できる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施の形態1に係る半導体リレーの概略構成を示す図

【図2】本発明の実施の形態2に係る半導体リレーの概略構成を示す図

【図3】本発明の実施の形態3に係る半導体リレーの概略構成を示す図

【図4】本発明の実施の形態3に係る半導体リレーにおいて、変形例の概略構成を示す図

【図5】本発明の実施の形態4に係る半導体リレーの概略構成を示す図

【図6】本発明の実施の形態4に係る半導体リレーにおいて、変形例の概略構成を示す図

【図7】従来の半導体リレーの概略構成を示す図

【発明を実施するための形態】

【0027】

以下、本発明の実施の形態に係る半導体リレーについて、図面を用いて説明する。

【0028】

(実施の形態1)

図1は、本発明の実施の形態1に係る半導体リレーの概略構成を示す図である。同図に示すように、本実施の形態の半導体リレー1は、第1の入力端子11aと第2の入力端子11bを有するLED等の発光素子12と、発光素子12と絶縁されたフォトダイオードセルを直列に接続してなり、発光素子12の発光に応じて起電力を発生し電圧を出力するフォトダイオードアレイ13と、フォトダイオードアレイ13の出力電圧を充放電する充放電回路14と、フォトダイオードアレイ13の出力電圧を所定電圧に制限するクランプ回路15と、所定電圧の出力電圧をゲートに印加することによってドレインとソースの間がオン、オフされる炭化珪素(SiC)を材料とする2つの出力用MOSFET16a、16bを有する構成である。

【0029】

2つの出力用MOSFET16a、16bは、それぞれのゲートがクランプ回路15を介してフォトダイオードアレイ13のアノード端子に接続され、それぞれのソースが互いに逆直列に接続された上でクランプ回路15を介してフォトダイオードアレイ13のカソード端子に接続される。また、出力用MOSFET16aのドレインは第1の出力端子17aに接続され、出力用MOSFET16bのドレインが第2の出力端子17bに接続されている。

【0030】

クランプ回路15は、2つの出力用MOSFET16a、16bのゲートとソース間に直列に接続された抵抗R1、R2と、抵抗R2に並列に接続されたダイオードD1から構成される。なお、抵抗R1、R2の抵抗値は、例えば、R1が19.3MΩ、R2が0.7MΩである。

【0031】

次に、このように構成された本発明の実施の形態1に係る半導体リレーの動作について説明する。

【0032】

発光素子12は、第1及び第2の入力端子11a、11bから入力信号が入力されることによって発光し、光信号を生成する。フォトダイオードアレイ13は、発光素子12の光信号を受光してその両端で起電力を発生し、電圧を出力する。

【0033】

充放電回路14は、フォトダイオードアレイ13の出力電圧を充放電し、クランプ回路15を介して出力用MOSFET16a、16bのゲートに印加する。そして、出力用MOSFET16a、16bのゲートに印加されるフォトダイオードアレイ13の出力電圧がしきい値電圧Vthよりも大きくなると、出力用MOSFET16a、16bのドレイン・ソース間がオンになり、第1及び第2の出力端子17a、16bの間が導通して、リレーが閉じられる。

【0034】

一方、第1及び第2の入力端子11a、11bにおいて入力信号がオフになると、充放電回路14からの出力電圧がなくなり、出力用MOSFET16a、16bのドレイン・ソース間がオフとなって、第1及び第2の出力端子17a、16bの間が遮断し、リレーが開放される。

【0035】

次に、クランプ回路15の動作について説明する。

【0036】

クランプ回路15は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、抵抗R2における電圧降下がダイオードD1の順方向電圧Vf(約0.7V)に略等しくなるので、出力用MOSFET16a、16bのゲートには、フォトダイオードアレイ13の出力電圧がそのまま印加される。

【0037】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R2における電圧降下がダイオードD1の順方向電圧Vfで固定される。そのため、例えば発光素子12の発光量が増えることによってフォトダイオードアレイ13の起電力が増し、出力電圧が上昇しようとしても、電流が増加するだけで出力電圧が高くなることはない。

【0038】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化がゲート印加電圧の20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0039】

なお、実際には、ダイオードD1の順方向電圧Vfにも−1〜2mV/℃の温度勾配があるが、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は、次の式(2)で計算されるように小さい値である。

【0040】

−1〜2×(19.3+0.7)/0.7≒−30mV/℃・・・(2)

【0041】

この値は、クランプ回路15がない場合の―120mV/℃に比較して大幅に改善されており、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0042】

以上説明したように、このような本発明の実施の形態1に係る半導体リレーによれば、入力信号に応答して光信号を生成する発光素子と、光信号を受光して起電力を発生するフォトダイオードアレイと、フォトダイオードアレイで発生した起電力の電圧を充放電する充放電回路と、ゲート及びソースが充放電回路を介してフォトダイオードアレイに接続された2つの出力用MOSFETを備える半導体リレーにおいて、2つの出力用MOSFETの各ゲート・ソース間に、直列に接続された2つの抵抗と、抵抗の一方に並列に接続されたダイオードから構成されるクランプ回路を接続する。

【0043】

これにより、フォトダイオードアレイの出力電圧が設計値の例えば20V以上になった場合でも、抵抗の一方における電圧降下がダイオードの順方向電圧Vfで固定されるので、2つの出力用MOSFETには20V以上のゲート電圧が印加されることがなく、ゲート酸化膜の絶縁劣化を防止することができる。

【0044】

(実施の形態2)

図2は、本発明の実施の形態2に係る半導体リレーの概略構成を示す図である。同図に示すように、本実施の形態の半導体リレー2は、図1に示した実施の形態1に係る半導体リレー1において、クランプ回路15に替えてクランプ回路25を有する構成である。なお、図1と同じ構成要素については、同一符号を付して説明を簡略にし、若しくは省略する。

【0045】

クランプ回路25は、ツェナー電圧が例えば20VであるツェナーダイオードZD1から構成される。

【0046】

次に、このように構成された本発明の実施の形態2に係る半導体リレーの動作について説明する。なお、リレー動作は実施の形態1と同じであるので説明を省略し、クランプ回路25の動作のみを説明する。

【0047】

クランプ回路25は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、ツェナーダイオードZD1にツェナー電流が流れることはないので、フォトダイオードアレイ13の出力電圧がそのまま出力用MOSFET16a、16bのゲートに印加される。

【0048】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、ツェナーダイオードZD1にツェナー電流が流れ、ツェナー電圧で制限された20Vの電圧が出力用MOSFET16a、16bのゲートに印加される。

【0049】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化がゲート印加電圧の20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0050】

なお、実際には、ツェナーダイオードZD1のツェナー電圧にも温度勾配があるが、この値は略−30mV/℃であって、クランプ回路25がない場合の、―120mV/℃に比較して大幅に改善されており、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0051】

以上説明したように、このような本発明の実施の形態2に係る半導体リレーによれば、入力信号に応答して光信号を生成する発光素子と、光信号を受光して起電力を発生するフォトダイオードアレイと、フォトダイオードアレイで発生した起電力の電圧を充放電する充放電回路と、ゲート及びソースが充放電回路を介してフォトダイオードアレイに接続された2つの出力用MOSFETを備える半導体リレーにおいて、2つの出力用MOSFETのゲート及びソース間に、ツェナー電圧が例えば20Vであるツェナーダイオードから構成されるクランプ回路を接続する。

【0052】

これにより、フォトダイオードアレイの出力電圧が設計値の例えば20Vを超えた場合でも、ツェナーダイオードのツェナー電圧20Vで制限されるので、2つの出力用MOSFETに20V以上のゲート電圧が印加されることがなく、ゲート酸化膜の絶縁劣化を防止できる。

【0053】

(実施の形態3)

図3は、本発明の実施の形態3に係る半導体リレーの概略構成を示す図である。同図に示すように、本実施の形態の半導体リレー3は、図1に示した実施の形態1に係る半導体リレー1において、クランプ回路15に替えてクランプ回路35を有する構成である。なお、図1と同じ構成要素については同一符号を付して説明を簡略にし、若しくは省略する。

【0054】

クランプ回路35は、2つの出力用MOSFET16a、16bのゲート・ソース間に直列に接続された抵抗R3、R4と、抵抗R3、R4の接続点にゲートが接続され、出力用MOSFET16a、16bの各ゲートに抵抗R5を介してドレインが接続され、出力用MOSFET16a、16bの各ソースにソースが接続されたNチャネルFET(Q1)から構成される。なお、抵抗R3〜R5の各抵抗値は、例えば、R3が19MΩ、R4が1MΩ、R5が抵抗R3、R4の各抵抗値の和20MΩより十分小さい値である。

【0055】

次に、このように構成された本発明の実施の形態3に係る半導体リレーの動作について説明する。なお、リレー動作は実施の形態1と同じであるので説明を省略し、クランプ回路35の動作のみを説明する。

【0056】

クランプ回路35は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、NチャネルFET(Q1)のゲートに印加される抵抗R3、R4によって分圧された電圧は、NチャネルFET(Q1)をオンするための略1Vのしきい値を超えることはない。そのため、NチャネルFET(Q1)はオフのままであり、出力用MOSFET16a、16bのゲートには、20V以下のフォトダイオードアレイ13の出力電圧がそのまま印加される。

【0057】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R3、R4によって分圧された電圧は、しきい値の略1Vを超え、NチャネルFET(Q1)がオンしてドレイン・ソース間が導通する。そのため、例えば発光素子12の発光量が増えることによって、フォトダイオードアレイ13の出力電圧が上昇しようとしても、電流が増加するだけで出力電圧が高くなることはない。

【0058】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化が20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0059】

なお、実際には、NチャネルFET(Q1)のしきい値電圧にも温度勾配があるが、この値は略−2mV/℃であって、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は−20mV/℃程度と小さく、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0060】

図4は、本発明の実施の形態3に係る半導体リレーにおいて、変形例の概略構成を示す図である。同図に示すように、変形例の半導体リレー4は、図3に示した本実施の形態に係る半導体リレー3におけるクランプ回路35に替えて、クランプ回路45を有する構成である。

【0061】

クランプ回路45は、2つの出力用MOSFET16a、16bのゲートとソース間に直列に接続された抵抗R6、R7と、抵抗R6、R7の接続点にゲートが接続され、出力用MOSFET16a、16bの各ゲートにソースが接続され、出力用MOSFET16a、16bの各ソースに抵抗R8を介してドレインが接続されたPチャネルFET(Q2)から構成される。なお、抵抗R6〜R8の各抵抗値は、例えば、R6が19MΩ、R7が1MΩ、R8が抵抗R6、R7の各抵抗値の和20MΩより十分小さい値である。

【0062】

このように構成された本発明の実施の形態3に係る半導体リレーの変形例において、クランプ回路45の動作を説明する。

【0063】

クランプ回路45は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、PチャネルFET(Q2)のゲートに印加される抵抗R6、R7によって分圧された電圧は、PチャネルFET(Q2)をオンするための略−1Vのしきい値を超えることはない。そのためPチャネルFET(Q2)はオフのままであり、出力用MOSFET16a、16bのゲート・ソース間には、20V以下のフォトダイオードアレイ13の出力電圧がそのまま印加される。

【0064】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R6、R7によって分圧された電圧は、しきい値の略−1Vを超え、PチャネルFET(Q2)がオンしてドレイン・ソース間が導通する。そのため、例えば発光素子12の発光量が増えることによって、フォトダイオードアレイ13の出力電圧が上昇しようとしても、電流が増加するだけで出力電圧は増えることはない。

【0065】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化が20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0066】

なお、実際には、PチャネルFET(Q2)のしきい値電圧にも温度勾配があるが、この値は略−2mV/℃であって、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は−20mV/℃程度と小さく、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0067】

以上説明したように、このような本発明の実施の形態3に係る半導体リレーによれば、入力信号に応答して光信号を生成する発光素子と、光信号を受光して起電力を発生するフォトダイオードアレイと、フォトダイオードアレイで発生した起電力の電圧を充放電する充放電回路と、ゲート及びソースが充放電回路を介してフォトダイオードアレイに接続された2つの出力用MOSFETを備える半導体リレーにおいて、2つの出力用MOSFETのゲート及びソース間に、直列に接続された2つの抵抗と、両抵抗の接続点にゲートが接続され、2つの出力用MOSFETの各ゲートに抵抗を介してドレインが接続され、出力用MOSFETの各ソースにソースが接続されたNチャネルFETから構成されるクランプ回路を接続する。

【0068】

また、クランプ回路は、2つの出力用MOSFETのゲートとソース間に、直列に接続された2つの抵抗と、両抵抗の接続点にゲートが接続され、2つの出力用MOSFETの各ゲートにソースが接続され、各ソースに抵抗を介してドレインが接続されたPチャネルFETから構成されるものであってもよい。

【0069】

これにより、フォトダイオードアレイの出力電圧が設計値の例えば20Vを超えた場合でも、2つの抵抗によって分圧された電圧は、NチャネルFET及びPチャネルFETの各しきい値であるそれぞれ略1V及び略−1Vを超えてドレイン・ソース間が導通するので、2つの出力用MOSFETに20V以上のゲート電圧が印加されることがなく、ゲート酸化膜の絶縁劣化を防止できる。

【0070】

(実施の形態4)

図5は、本発明の実施の形態5に係る半導体リレーの概略構成を示す図である。同図に示すように、本実施の形態の半導体リレー4は、図1に示した実施の形態1に係る半導体リレー1において、クランプ回路15に替えてクランプ回路55を有する構成である。なお、図1と同じ構成要素については、同一符号を付して説明を簡略にし、若しくは省略する。

【0071】

クランプ回路55は、2つの出力用MOSFET16a、16bのゲートとソース間に直列に接続された抵抗R9、R10と、抵抗R9、R10の接続点にベースが接続され、出力用MOSFET16a、16bの各ゲートに抵抗R11を介してコレクタが接続され、出力用MOSFET16a、16bの各ソースにエミッタが接続されたNPNバイポーラトランジスタQ3から構成される。なお、抵抗R9〜R11の各抵抗値は、例えば、R9が30MΩ、R10が1MΩ、R11が抵抗R9、R10の各抵抗値の和31MΩより十分小さい値である。

【0072】

次に、このように構成された本発明の実施の形態4に係る半導体リレーの動作について説明する。なお、リレー動作は実施の形態1と同じであるので説明を省略し、クランプ回路55の動作のみを説明する。

【0073】

クランプ回路55は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、NPNバイポーラトランジスタQ3のベースに印加される抵抗R9、R10によって分圧された電圧は、NPNバイポーラトランジスタQ3をオンするためのベース・エミッタ電圧Vbeの略0.7Vを超えることはない。そのため、NPNバイポーラトランジスタQ3はオフのままであり、出力用MOSFET16a、16bのゲート・ソース間には、20V以下のフォトダイオードアレイ13の出力電圧がそのまま印加される。

【0074】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R9、R10によって分圧された電圧は、Vbeの略0.7Vを超え、NPNバイポーラトランジスタQ3がオンしてコレクタ・エミッタ間が導通する。そのため、例えば発光素子12の発光量が増えることによって、フォトダイオードアレイ13の出力電圧が上昇しようとしても、電流が増加するだけで出力電圧が高くなることはない。

【0075】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化が20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0076】

なお、実際には、NPNバイポーラトランジスタQ3のベース・エミッタ電圧Vbeにも温度勾配があるが、この値は略−2mV/℃であって、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は−20mV/℃程度と小さく、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0077】

図6は、本発明の実施の形態4に係る半導体リレーにおいて、変形例の概略構成を示す図である。同図に示すように、本変形例の半導体リレー6は、図5に示した本実施の形態に係る半導体リレー5におけるクランプ回路55に替えてクランプ回路65を有する構成である。

【0078】

クランプ回路65は、2つの出力用MOSFET16a、16bのゲートとソース間に直列に接続された抵抗R12、R13と、抵抗R12、R13の接続点にベースが接続され、出力用MOSFET16a、16bの各ゲートにエミッタが接続され、出力用MOSFET16a、16bの各ソースに抵抗R14を介してコレクタが接続されたPNPバイポーラトランジスタQ4から構成される。

【0079】

このように構成された本発明の実施の形態4に係る半導体リレーの変形例において、クランプ回路65の動作を説明する。

【0080】

クランプ回路65は、フォトダイオードアレイ13の出力電圧が設計値の例えば20V以下であれば、PNPバイポーラトランジスタQ4のベースに印加される抵抗R12、R13によって分圧された電圧は、PNPバイポーラトランジスタQ4をオンするためのベース・エミッタ電圧Vbeの略−0.7Vを超えることはない。そのため、PNPバイポーラトランジスタQ4はオフのままであり、出力用MOSFET16a、16bのゲート・ソース間には、20V以下のフォトダイオードアレイ13の出力電圧がそのまま印加される。

【0081】

一方、フォトダイオードアレイ13の出力電圧が20V以上になると、抵抗R6、R7によって分圧された電圧は、Vbeの略−0.7Vを超え、PNPバイポーラトランジスタQ4がオンしてコレクタ・エミッタ間が導通する。そのため、例えば発光素子12の発光量が増えることによって、フォトダイオードアレイ13の出力電圧が上昇しようとしても、電流が増加するだけで出力電圧が高くなることはない。

【0082】

その結果、出力用MOSFET16a、16bのゲート酸化膜の絶縁劣化が20V以下では生じないとすれば、絶縁劣化を効果的に防止できる。

【0083】

なお、実際には、PNPバイポーラトランジスタQ4のベース・エミッタ電圧Vbeにも温度勾配があるが、この値は略−2mV/℃であって、出力用MOSFET16a、16bのゲートへ印加する電圧に及ぼす影響は−20mV/℃程度と小さく、例えば、動作温度範囲の下限−40℃においてゲート印加電圧を20Vに設定したとしても、室温(20℃)におけるゲート印加電圧の低下を小さくでき、しきい値電圧の高い出力用MOSFET76a、76bを十分に導通することが可能となる。

【0084】

以上説明したように、このような本発明の実施の形態4に係る半導体リレーによれば、入力信号に応答して光信号を生成する発光素子と、光信号を受光して起電力を発生するフォトダイオードアレイと、フォトダイオードアレイで発生した起電力の電圧を充放電する充放電回路と、ゲート及びソースが充放電回路を介してフォトダイオードアレイに接続された2つの出力用MOSFETを備える半導体リレーにおいて、2つの出力用MOSFETのゲート及びソース間に、直列に接続された2つの抵抗と、両抵抗の接続点にベースが接続され、出力用MOSFETの各ゲートに抵抗を介してコレクタが接続され、出力用MOSFETの各ソースにエミッタが接続されたNPNバイポーラトランジスタから構成されるクランプ回路を接続する。

【0085】

また、クランプ回路は、2つの出力用MOSFETのゲートとソース間に直列に接続された2つの抵抗と、両抵抗の接続点にベースが接続され、2つの出力用MOSFETの各ゲートにエミッタが接続され、各ソースに抵抗を介してコレクタが接続されたPNPバイポーラトランジスタから構成されるものであってもよい。

【0086】

これにより、フォトダイオードアレイの出力電圧が設計値の例えば20Vを超えた場合でも、2つの抵抗によって分圧された電圧は、NPNバイポーラトランジスタ及びPNPバイポーラトランジスタのベース・エミッタ電圧Vbeの略0.7V及び略−0.7Vを超えてコレクタ・エミッタ間が導通するので、2つの出力用MOSFETに20V以上のゲート電圧が印加されることがなく、ゲート酸化膜の絶縁劣化を防止できる。

【符号の説明】

【0087】

1〜6 半導体リレー

12 発光素子

13 フォトダイオードアレイ

14 充放電回路

15、25、35、45、55、65 クランプ回路

16a、16b 出力用MOSFET

D1 ダイオード

R1〜R14 抵抗

Q1 NチャネルFET

Q2 PチャネルFET

Q3 NPNバイポーラトランジスタ

Q4 PNPバイポーラトランジスタ

ZD1 ツェナーダイオード

【特許請求の範囲】

【請求項1】

入力信号に応答して光信号を生成する発光素子と、前記光信号を受光して電圧を発生するフォトダイオードアレイと、前記フォトダイオードアレイによって発生した電圧を充放電する充放電回路と、前記充放電回路にゲート及びソースが接続された出力用MOSFETとを具備した半導体リレーにおいて、

前記充放電回路と前記出力用MOSFETの間に、前記フォトダイオードアレイによって発生した電圧を制限するクランプ回路を具備し、

前記クランプ回路は、

前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、

前記2つの抵抗の一方あるいは双方に、並列に接続され、電圧を制御するクランプ手段を具備した半導体リレー。

【請求項2】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の一方に、並列に接続されたダイオードである半導体リレー。

【請求項3】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の接続点にゲートが接続され、前記出力用MOSFETの前記ゲートに抵抗を介してドレインが接続され、前記出力用MOSFETの前記ソースにソースが接続されたNチャネルFETと、

から構成されることを特徴とする半導体リレー。

【請求項4】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の接続点にゲートが接続され、前記出力用MOSFETの前記ゲートにソースが接続され、前記出力用MOSFETの前記ソースに抵抗を介してドレインが接続されたPチャネルFETから構成される半導体リレー。

【請求項5】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の接続点にベースが接続され、前記出力用MOSFETの前記ゲートに抵抗を介してコレクタが接続され、前記出力用MOSFETの前記ソースにエミッタが接続されたNPNバイポーラトランジスタから構成される半導体リレー。

【請求項6】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の接続点にベースが接続され、前記出力用MOSFETの前記ゲートにエミッタが接続され、前記出力用MOSFETの前記ソースに抵抗を介してコレクタが接続されたPNPバイポーラトランジスタから構成される半導体リレー。

【請求項7】

入力信号に応答して光信号を生成する発光素子と、前記光信号を受光して電圧を発生するフォトダイオードアレイと、前記フォトダイオードアレイによって発生した電圧を充放電する充放電回路と、前記充放電回路にゲート及びソースが接続された出力用MOSFETとを具備した半導体リレーにおいて、

前記充放電回路と前記出力用MOSFETの間に、前記フォトダイオードアレイによって発生した電圧を制限するクランプ回路を具備し、

前記クランプ回路は、

前記出力用MOSFETの前記ゲート及び前記ソース間に接続されたツェナーダイオードから構成されることを特徴とする半導体リレー。

【請求項1】

入力信号に応答して光信号を生成する発光素子と、前記光信号を受光して電圧を発生するフォトダイオードアレイと、前記フォトダイオードアレイによって発生した電圧を充放電する充放電回路と、前記充放電回路にゲート及びソースが接続された出力用MOSFETとを具備した半導体リレーにおいて、

前記充放電回路と前記出力用MOSFETの間に、前記フォトダイオードアレイによって発生した電圧を制限するクランプ回路を具備し、

前記クランプ回路は、

前記出力用MOSFETの前記ゲート及び前記ソース間に、直列に接続された2つの抵抗と、

前記2つの抵抗の一方あるいは双方に、並列に接続され、電圧を制御するクランプ手段を具備した半導体リレー。

【請求項2】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の一方に、並列に接続されたダイオードである半導体リレー。

【請求項3】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の接続点にゲートが接続され、前記出力用MOSFETの前記ゲートに抵抗を介してドレインが接続され、前記出力用MOSFETの前記ソースにソースが接続されたNチャネルFETと、

から構成されることを特徴とする半導体リレー。

【請求項4】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の接続点にゲートが接続され、前記出力用MOSFETの前記ゲートにソースが接続され、前記出力用MOSFETの前記ソースに抵抗を介してドレインが接続されたPチャネルFETから構成される半導体リレー。

【請求項5】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の接続点にベースが接続され、前記出力用MOSFETの前記ゲートに抵抗を介してコレクタが接続され、前記出力用MOSFETの前記ソースにエミッタが接続されたNPNバイポーラトランジスタから構成される半導体リレー。

【請求項6】

請求項1に記載の半導体リレーであって、

前記クランプ手段は、

前記2つの抵抗の接続点にベースが接続され、前記出力用MOSFETの前記ゲートにエミッタが接続され、前記出力用MOSFETの前記ソースに抵抗を介してコレクタが接続されたPNPバイポーラトランジスタから構成される半導体リレー。

【請求項7】

入力信号に応答して光信号を生成する発光素子と、前記光信号を受光して電圧を発生するフォトダイオードアレイと、前記フォトダイオードアレイによって発生した電圧を充放電する充放電回路と、前記充放電回路にゲート及びソースが接続された出力用MOSFETとを具備した半導体リレーにおいて、

前記充放電回路と前記出力用MOSFETの間に、前記フォトダイオードアレイによって発生した電圧を制限するクランプ回路を具備し、

前記クランプ回路は、

前記出力用MOSFETの前記ゲート及び前記ソース間に接続されたツェナーダイオードから構成されることを特徴とする半導体リレー。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−171574(P2010−171574A)

【公開日】平成22年8月5日(2010.8.5)

【国際特許分類】

【出願番号】特願2009−10643(P2009−10643)

【出願日】平成21年1月21日(2009.1.21)

【出願人】(000005832)パナソニック電工株式会社 (17,916)

【Fターム(参考)】

【公開日】平成22年8月5日(2010.8.5)

【国際特許分類】

【出願日】平成21年1月21日(2009.1.21)

【出願人】(000005832)パナソニック電工株式会社 (17,916)

【Fターム(参考)】

[ Back to top ]