半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体回路、半導体装置、及び電池監視システム、特に短絡保護機能を有する半導体回路、半導体装置、及び電池監視システムに関するものである。

【背景技術】

【0002】

一般に、ハイブリッド自動車や電気自動車のモータ駆動等に用いられる大容量で高出力なバッテリーとして、複数の電池セルが直列に接続されたバッテリー(具体的一例としては、リチウムイオンバッテリー等が挙げられる)が用いられている。当該バッテリーの電池や太陽電池等の電池電圧を監視・制御するための電池監視システムが知られている。

【0003】

このような電池監視システムとして、電池の充電/放電を制御するスイッチング素子を備えた電池監視システムが知られている(例えば特許文献1〜特許文献4参照。)

【0004】

このような従来の電池監視システムでは、複数の電池セルを含む電池と、当該電池に含まれる電池セルの電圧を監視・制御する電池監視IC(Integrated Circuit、電池監視素子)と、を備えて構成されている。

【0005】

一般に、電池監視システムにおいて、電池監視IC外部に設けられたFET(Field Effect Transistor、以下、外部FETという)をスイッチング素子として使用し、電池の充電や放電を制御する方式が多く適用されている。このような電池監視システムでは、外部FETのゲートを駆動する駆動回路を電池監視ICに内蔵しているものが多い。図5に、外部FETとして、PMOSトランジスタを用いた電池監視システムの具体例を示す。また、図6に、外部FETとして、NMOSトランジスタを用いた電池監視システムの具体例を示す。

【0006】

電池監視ICを多セル接続された電池に使用する場合、その電源電圧VDDは、数十V以上で使用され、また、電池セルの電圧により大きく変動するため、外部FETの駆動回路は、外部FETのゲート−ソース間耐圧を越えないよう、図5、6に示すようにFET駆動電圧(ゲート電圧)を所定の電圧でクランプする機能を付加して構成される。

【0007】

図5に示した、外部FET0がPMOSトランジスタである場合のON/OFFの制御動作について詳細に説明する。

【0008】

図5に示した電池監視システム100のFET駆動回路120(電池監視IC114)では、外部FET0のON/OFFを制御するFET ON信号を受け付けると、外部FET0を駆動するPMOSトランジスタMP0とNMOSトランジスタMN0とが同時にONしないよう制御するデッドタイム回路122を介して、PMOSトランジスタMP0のON/OFFの制御信号pgと、NMOSトランジスタMN0のON/OFFを制御する制御信号ngとを生成する。外部FET0をOFFする場合は、制御信号pgを「L」レベル、制御信号ngを「L」レベルとし、PMOSトランジスタMP0をON、NMOSトランジスタをOFFにすることで、FETゲート電圧出力端子FET_PADに電源電圧VDDを出力し、外部FET0をOFFする。一方、外部FET0をONする場合は、制御信号pgを「H」レベル、制御信号ngを「H」レベルとし、PMOSトランジスタMP0をOFF、NMOSトランジスタをONにすることで、FETゲート電圧出力端子FET_PADに電圧VCLAMP−を出力し、外部FET0をONにする。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平9−261861号公報

【特許文献2】特開平8−190936号公報

【特許文献3】特開平8−196042号公報

【特許文献4】特開2000−102176号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

図5に示したFET駆動回路120の場合、外部FET0をON、つまりNMOSトランジスタMN0がONとなっている状態で、何からの外的要因により、FETゲート電圧出力端子FET_PADが電源電圧VDD、或いはGNDに短絡して短絡電流が発生する場合でも、クランプ電圧源124の電流能力により、その短絡電流の大きさが制限されるため、電池監視IC114の破壊には至らない。

【0011】

しかしながら、外部FET0をOFF、つまりPMOSトランジスタMP0がONとなっている状態で、FETゲート電圧出力端子FET_PADが、GNDに短絡すると、PMOSトランジスタMP0を介して電源電圧VDDからGNDへ大きな短絡電流が流れ、電池監視IC114の破壊を引き起こしてしまう場合がある、という問題が生じる。

【0012】

また、同様に図6に示した電池監視システム150のFET駆動回路160(電池監視IC154)の場合、外部FET1をON、つまりPMOSトランジスタMP0がONとなっている状態で、何からの外的要因により、FETゲート電圧出力端子FET_PADが電源電圧VDDに短絡して短絡電流が発生する場合でも、クランプ電圧源164の電流能力により、その短絡電流の大きさが制限されるため、電池監視IC154の破壊には至らない。

【0013】

しかしながら、外部FET1をOFF、つまりPMOSトランジスタMP0がOFFとなっている状態で、FETゲート電圧出力端子FET_PADが、電源電圧VDDに短絡すると、NMOSトランジスタMN0を介して電源電圧VDDからGNDへ大きな短絡電流が流れ、電池監視ICの破壊を引き起こしてしまう場合がある、という問題が生じる。

【0014】

本発明は、上述した問題を解決するために提案されたものであり、過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供することを目的とする。

【課題を解決するための手段】

【0015】

請求項1に記載の半導体回路は、第1スイッチ手段をオフするための電圧を供給するオフ電源と、前記第1スイッチ手段と、を電気的に接続する第1伝送路と、前記第1伝送路上に設けられた第2スイッチ手段と、前記オフ電源と前記第2スイッチ手段との間の前記第1伝送路と、前記第1スイッチ手段と、を電気的に接続し、かつ前記第1伝送路よりも抵抗値が高い第2伝送路と、前記第2伝送路上に設けられた第3スイッチ手段と、前記第1伝送路に接続され、前記第2スイッチ手段と前記第1スイッチ手段との間の前記第1伝送路に流れる電流に応じた電圧を検知し、かつ、検知した前記電圧と閾値とに応じて前記第2スイッチ手段をオフにすると共に、前記第3スイッチ手段をオンにする電圧検知手段と、前記電圧検知手段と前記第1伝送路との間に設けられ、前記オフ電源の電圧値の変動に応じて前記電圧値が変動しないように前記電圧値を調整する調整手段と、を備える。

【0016】

請求項6に記載の半導体装置は、第1スイッチ手段と、前記第1スイッチ手段をオフするための電圧を供給するオフ電源と前記第1スイッチ手段とを電気的に接続するための請求項1から請求項5のいずれか1項に記載の半導体回路と、を備える。

【0017】

請求項7に記載の電池監視システムは、電池と、前記電池の高電位側に接続され、かつ前記電池の充電、放電を制御する第1スイッチ手段と、前記第1スイッチ手段をオフするための電圧を供給するオフ電源と前記第1スイッチ手段とを電気的に接続するための請求項1から請求項5のいずれか1項に記載の半導体回路と、を備える。

【発明の効果】

【0018】

本発明によれば、過大電流による素子の破壊を防止することができる、という効果を奏する。

【図面の簡単な説明】

【0019】

【図1】第1の実施の形態に係る電池監視システムの概略構成の一例を示す概略構成図である。

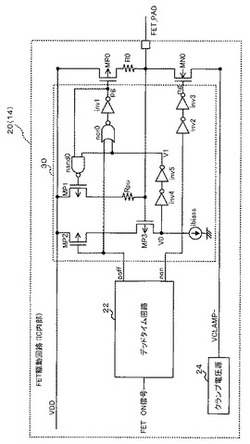

【図2】第1の実施の形態に係る短絡保護回路を備えたFET駆動回路の概略構成の一例を示す回路図である。

【図3】第2の実施の形態に係る池監視システムの概略構成の一例を示す概略構成図である。

【図4】第2の実施の形態に係る短絡保護回路を備えたFET駆動回路の概略構成の一例を示す回路図である。

【図5】従来の電池監視システムの概略構成の一例を示す概略構成図である。

【図6】従来の電池監視システムの概略構成の一例を示す概略構成図である。

【発明を実施するための形態】

【0020】

[第1の実施の形態]

【0021】

まず、以下、図面を参照して本発明の基本構成となる、第1の実施の形態の電池監視システムについて詳細に説明する。

【0022】

本実施の形態の電池監視システムの概略構成の一例の概略構成図を図1に示す。また、本実施の形態のFET駆動回路の概略構成の一例の回路図を図2に示す。

【0023】

図1に示した本実施の形態の電池監視システム10は、電池12と、電池12の充電・放電を制御する外部FET0と、外部FET0を駆動するためのFET駆動回路20を含む電池監視IC14と、を備えて構成されている。

【0024】

本実施の形態では、外部FET0は、PMOSトランジスタであり、ソース端子が電池12の高電位側に接続されており、ドレイン端子が端子PACK(+)に接続されており、かつゲート端子が抵抗素子Rgを介して、電池監視IC14のFET駆動回路20のFETゲート電圧出力端子FET_PADに接続されている。

【0025】

また、電池12は、複数の電池セルを含んで成り、低電位側が端子PACK(−)(本実施の形態ではGND)に接続されている。

【0026】

FET駆動回路20は、電池監視IC14内部に設けられており、外部FET0のON/OFFを制御する機能を有している。本実施の形態のFET駆動回路20は、デッドタイム回路22、クランプ電圧源24、短絡保護回路30、外部FET0駆動用のPMOSトランジスタMP0、NMOSトランジスタMN0、及び短絡電流検出用抵抗素子R0を備えて構成されている。

【0027】

本実施の形態のFET駆動回路20は、PMOSトランジスタMP0及びNMOSトランジスタMN0のON/OFFにより、FETゲート電圧出力端子FET_PADの電圧を電源電圧VDDとした場合(PMOSトランジスタMP0=ON、NMOSトランジスタMN0=OFF)に、外部FET0がOFF、FETゲート電圧出力端子FET_PADの電圧をクランプ電圧源24から出力されたクランプ電圧VCLAMP−とした場合(PMOSトランジスタMP0=OFF、NMOSトランジスタMN0=ON)に、外部FET0がONするように外部FET0を制御(駆動)する機能を有している。このように外部FET0を制御することにより、電池12を使用可/不可を切り替える。

【0028】

デッドタイム回路22は、外部FET0を駆動するPMOSトランジスタMP0とNMOSトランジスタMN0とが同時にONしないよう(両者のON期間が重ならないよう)に制御する機能を有するものである。

【0029】

クランプ電圧源24は、外部FET0をONさせるための電圧VCLAMP−を生成して出力する機能を有するものである。

【0030】

短絡電流検出用抵抗素子R0は、FETゲート電圧出力端子FET_PADが短絡したか否かを検出するための機能を有するものであり、PMOSトランジスタMP0のドレイン端子とFETゲート電圧出力端子FET_PADとの間に設けられている。本実施の形態の電池監視システム10では、短絡電流検出用抵抗素子R0を別途、電池監視IC14内部の回路(図示省略)でモニタし、短絡電流検出用抵抗素子R0を流れる電流(短絡電流)の大きさにより、短絡状態を検出している。また本実施の形態では、短絡電流検出用抵抗素子R0のモニタにより短絡状態であることを検出した場合は、短絡要因を除去するために所定の措置を、所定の回路や人的手段により行うものとしている。

【0031】

なお、短絡電流検出用抵抗素子R0を設ける場所は、本実施の形態の位置に限るものではないが、PMOSトランジスタMP0がONの場合のFETゲート電圧出力端子FET_PADの短絡を検出し、本実施の形態では、短絡状態の場合は、PMOSトランジスタMP0がオフ状態になり、電流が流れなくなることから、本実施の形態のように、PMOSトランジスタMP0のドレイン端子とFETゲート電圧出力端子FET_PADとの間に設けることが好ましい。

【0032】

図2に示すように、短絡保護回路30は、FETゲート電圧出力端子FET_PADがGND電位に短絡した場合に、電池監視IC14を破壊から保護するための機能を有するものである。

【0033】

短絡保護回路30は、PMOSトランジスタMP1、MP2、MP3、電流源ibiass、抵抗素子Rpu、インバータ回路inv1、inv2、inv3、inv4、inv5、NOR回路nor0、及びnand回路nand0を備えて構成されている。

【0034】

PMOSトランジスタMP1のソース端子、MP2のソース端子は、共に、電源電圧VDDに接続される。PMOSトランジスタMP1のゲート端子はNAND回路nand0の出力端子と接続され、ドレイン端子は、抵抗素子Rpuを介してFETゲート電圧出力端子FET_PADに接続される。

【0035】

PMOSトランジスタMP2のゲート端子は、出力信号poffが入力されるようにデッドタイム回路22に接続され、ドレイン端子は、PMOSトランジスタMP3のソース端子に接続される。

【0036】

PMOSトランジスタMP3のゲート端子は、FETゲート電圧出力端子FET_PADに接続され、ドレイン端子(ノードV0)は、電流源ibiassを介してGNDに接続される。PMOSトランジスタMP3のドレイン端子は、インバータ回路inv4、inv5を介してNAND回路nand0及びNOR回路nor0の入力端子へ接続される。

【0037】

デッドタイム回路22は、インバータ回路inv2に出力信号nonが入力されるように接続されると共に、インバータ回路inv2、inv3を介してNMOSトランジスタMN0のゲート端子に接続される。

【0038】

デッドタイム回路22の出力信号poffは、NOR回路nor0の入力端子に接続され、NOR回路nor0、インバータ回路inv1を介して、PMOSトランジスタMP0のゲート端子、及びNAND回路nand0の入力端子に接続される。

【0039】

本実施の形態のFET駆動回路20では、外部FET0のON/OFFを制御するFET ON信号を受け付けると、デッドタイム回路22は、出力信号poff及び出力信号nonを生成して出力する。外部FET0をONする場合は、出力信号poffを「H」レベル、出力信号nonを「H」レベルとする。「H」レベルの出力信号poffにより、PMOSトランジスタMP2はOFFになる。また、NOR回路nor0では、出力信号poffが「H」レベルであるため、ノードV1のレベル(電圧値)にかかわらず、「L」レベルの信号をインバータ回路inv1に出力する。従って、制御信号pgは「H」レベルになり、PMOSトランジスタMP0はOFFになる。一方、「H」レベルの出力信号nonにより、制御信号ngは「H」レベルになり、NMOSトランジスタMN0はONになる。これにより、FETゲート電圧出力端子FET_PADにクランプ電圧VCLAMP−が出力され、外部FET0のゲート端子に、クランプ電圧VCLAMP−が印加され、外部FET0がONする。

【0040】

一方、外部FET0をOFFする場合は、出力信号poffを「L」レベル、出力信号nonを「L」レベルとする。外部FET0がOFFの場合は、PMOSトランジスタMP0がON、NMOSトランジスタMN0がOFFとなり、FETゲート電圧出力端子FET_PADの電圧は電源電圧VDDとなり、外部FET0のゲート端子に、電源圧VDDが印加される。この状態では、制御信号pgは、「L」レベルであるため、NAND回路nand0の出力は、ノードV1のレベル(電圧値)にかかわらず、「H」レベルとなり、PMOSトランジスタMP1は、OFFしている。一方、PMOSトランジスタMP2では、「L」レベルの出力信号poffがゲート端子に印加されるため、ONしているが、PMOSトランジスタMP3では、FETゲート電圧出力端子FET_PADが電源電圧VDDであるため、ゲート端子に電源電圧VDDが印加され、OFFになっている。従って、ノードV0、V1は「L」レベルとなり、NOR回路nor0の入力端子には、「L」レベルの出力信号poffと、「L」レベルのノードV1の電圧とが入力されるため、出力が「H」レベルになり、制御信号pgが「L」レベルになり、PMOSトランジスタMP0のON状態が保持される。

【0041】

また、「L」レベルの出力信号nonにより、制御信号ngは「L」レベルになり、NMOSトランジスタMN0のOFF状態が保持される。

【0042】

この状態において、FETゲート電圧出力端子FET_PADの電圧が、何らかの要因によりGNDに短絡した場合等、PMOSトランジスタMP3の閾値電圧、PMOSトランジスタMP0、MP2のON抵抗、短絡電流検出用抵抗素子R0により決まる短絡検出電圧以下となると、PMOSトランジスタMP3がONする。具体的には、PMOSトランジスタMP3の閾値電圧をVTH_MP3、PMOSトランジスタMP0のON抵抗をRON_MP0、PMOSトランジスタMP2のON抵抗をRON_MP2、短絡電流をIshort、短絡電流検出用抵抗素子R0の抵抗値をR0、電流源ibiassの電流値をIbiassとすると、以下の(1)式を満たすと、PMOSトランジスタMP3がONする。

【0043】

VTH_MP3<(R0+RON_MP0)Ishort−RON_MP2×Ibiass ・・・(1)

【0044】

PMOSトランジスタMP3がONすることにより、ノードV0、V1が「H」レベルになり、NOR回路nor0の出力が「L」レベルになり、制御信号pgは「H」レベルとなるため、PMOSトランジスタMP0がOFFとなる。

【0045】

一方、ノードV1及び制御信号pgが「H」レベルとなるため、NAND回路nand0の出力が「L」レベルになり、PMOSトランジスタMP1がONされる。

【0046】

PMOSトランジスタMP1がONされることにより、FETゲート電圧出力端子FET_PADは、抵抗素子Rpuを介して、電源電圧VDDにプルアップされた状態となり、短絡電流Ishortは、PMOSトランジスタMP1のON抵抗を無視すると、次の(2)式により制限される(抵抗素子Rpuの抵抗値をRpuとする)。

【0047】

Ishort=(電源電圧VDD−FET_PAD電圧値)/Rpu ・・・(2)

【0048】

従って、FETゲート電圧出力端子FET_PADがGNDに短絡した場合の最大短絡電流Ishort_maxは、Ishort_max=VDD/Rpuに制限される。

【0049】

この後、FETゲート電圧出力端子FET_PADをGNDに短絡した要因が上述のようにして除去され、FETゲート電圧出力端子FET_PADが開放されると、FETゲート電圧出力端子FET_PADはプルアップ状態であるため、電圧値が上昇する。電圧値が短絡検出電圧以上となると、PMOSトランジスタMP3はOFFする。これにより、ノードV0、V1は「L」レベルとなり、NOR回路nor0の出力が「H」レベルになり、制御信号pgは「L」レベルとなるため、PMOSトランジスタMP0がONする。一方、ノードV1及び制御信号pgが「L」レベルとなるため、NAND回路nand0の出力が「H」レベルになり、PMOSトランジスタMP1がOFFされる。PMOSトランジスタMP1がOFFすることにより、FETゲート電圧出力端子FET_PADのプルアップ状態が解除され、短絡検出前の状態(通常状態)に復帰する。

【0050】

本実施の形態の短絡保護回路30において、PMOSトランジスタMP2は、短絡検出電圧を電源電圧VDDにより調整する機能を有している。電源電圧VDDが低くなるにつれ、PMOSトランジスタMP0のON抵抗が大きくなり無視できなくなると、短絡検出電圧も大きくなるため、短絡状態でない場合であっても、PMOSトランジスタMP0をONする際に外部FET0のゲート駆動電流が流れることで、瞬間的に短絡検出電圧以下となり、短絡保護回路30による短絡保護機能(上述の動作)が動作してしまう可能性がある。

【0051】

もし、PMOSトランジスタMP2を設けない場合、外部FET0をOFFする際に、外部FET0のゲート端子の電荷を放電するため(OFFするため)の電流が瞬間的に流れる。電源電圧VDDが低い状態で、外部FET0をOFFすると、PMOSトランジスタMP0のON抵抗は、電源電圧VDDが高い場合に比べて大きくなるため、このゲート端子の電荷を放電するための電流により、短絡状態ではないにもかかわらず、短絡を検出してしまう可能性が生じる。PMOSトランジスタMP2を設けない場合は、上述の式(1)において、RON_MP2×Ibiass=0となり、R0+RON_MP0は電源電圧VDDが低い場合では大きくなるため、より小さい電流で短絡検出をすることになる。

【0052】

短絡保護が誤って動作してしまう場合、このゲート端子の電荷を放電する電流を短絡電流と判断してしまうため、短絡保護機能により電荷を放電する電流が制限されてしまい、外部FET0をONからOFFにする場合の動作速度が遅くなるという、問題が生じてしまう。

【0053】

本実施の形態のFET駆動回路20の短絡保護回路30では、PMOSトランジスタMP2を設けることにより、PMOSトランジスタMP2のON抵抗も電源電圧VDDが低くなるにつれ大きくなるため、短絡検出電圧が低くなり、上述のように短絡検出電圧が大きくなることを抑制することができる。従って、FETゲート電圧出力端子FET_PADの電圧値が短絡検出電圧を下回るのを防止することができる。すなわち、PMOSトランジスタMP2のトランジスタサイズ(ON抵抗値)を適切に選定することにより、上述の問題を回避することができる。

【0054】

以上説明したように、本実施の形態の電池監視システム10では、電池12の充電・放電を制御する外部FET0と、短絡保護回路30を有するFET駆動回路20を内蔵する電池監視IC14と、を備える。外部FET0がOFF状態の場合において、FETゲート電圧出力端子FET_PADの電圧が、何らかの要因により短絡し、短絡検出電圧以下となり、VTH_MP3<(R0+RON_MP0)Ishort−RON_MP2×Ibiassを満たすと、PMOSトランジスタMP3がONする。すなわち、短絡電流Ishortが生じることにより、PMOSトランジスタMP3がONする。また、PMOSトランジスタMP0がOFFとなり、さらにPMOSトランジスタMP1がONされる。PMOSトランジスタMP1がONされることにより、FETゲート電圧出力端子FET_PADは、抵抗素子Rpuを介して、プルアップされた状態となり、GNDに短絡した場合の最大短絡電流Ishort_maxは、Ishort_max=VDD/Rpuに制限される。

【0055】

すなわち、短絡状態の場合は、短絡保護回路30のPMOSトランジスタMP3により、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

【0056】

また、本実施の形態では、短絡発生後にその要因が除去された場合、FETゲート電圧出力端子FET_PADがプルアップ状態であるため、電圧値が短絡検出電圧以上となると、PMOSトランジスタMP3がOFFし、PMOSトランジスタMP0がONする。また、PMOSトランジスタMP1がOFFする。これにより、FETゲート電圧出力端子FET_PADのプルアップ状態が解除され、短絡検出前の状態(通常状態)に復帰する。従って、電池監視IC14をそのまま継続して使用することができる。

【0057】

[第2の実施の形態]

【0058】

以下、図面を参照して本発明の第2の実施の形態の電池監視システムについて詳細に説明する。第1の実施の形態では外部FET0としてPMOSトランジスタを用いた場合について説明したが、本実施の形態の電池監視システムでは、は外部FETとしてNMOSトランジスタ(外部FET1、図3参照)を用いた場合について説明する。

【0059】

本実施の形態の電池監視システムの概略構成の一例の概略構成図を図3に示す。また、本実施の形態のFET駆動回路の概略構成の一例の回路図を図4に示す。なお、本実施の形態において、第1の実施の形態と略同様の構成、及び動作については、その旨を記載し、詳細な説明を省略する。

【0060】

図3に示した本実施の形態の電池監視システム50は、電池12と、電池12の充電・放電を制御する外部FET1と、外部FET1を駆動するためのFET駆動回路60を含む電池監視IC54と、を備えて構成されている。

【0061】

本実施の形態では、外部FET1は、NMOSトランジスタであり、ソース端子が電池12の低電位側に接続されており、ドレイン端子が端子PACK(−)(本実施の形態ではGND電位)に接続されており、かつゲート端子が抵抗素子Rgを介して、電池監視IC54のFET駆動回路60のFETゲート電圧出力端子FET_PADに接続されている。

【0062】

また、電池12は、複数の電池セルを含んで成り、低電位側が端子PACK(+)に接続されている。

【0063】

FET駆動回路60は、電池監視IC54内部に形成されており、外部FET1のON/OFFを制御する機能を有している。本実施の形態のFET駆動回路60は、デッドタイム回路62、クランプ電圧源64、短絡保護回路70、外部FET1駆動用のPMOSトランジスタMP0、NMOSトランジスタMN0、及び短絡電流検出用抵抗素子R1を備えて構成されている。

【0064】

本実施の形態のFET駆動回路60は、PMOSトランジスタMP0及びNMOSトランジスタMN0のON/OFFにより、FETゲート電圧出力端子FET_PADの電圧をGNDとした場合(PMOSトランジスタMP0=OFF、NMOSトランジスタMN0=ON)に、外部FET1がOFF、FETゲート電圧出力端子FET_PADの電圧をクランプ電圧源64から出力されたクランプ電圧VCLAMP+とした場合(PMOSトランジスタMP0=ON、NMOSトランジスタMN0=OFF)に、外部FET1がONするように外部FET1を制御(駆動)する機能を有している。このように外部FET1を制御することにより、電池12を使用可/不可を切り替える。

【0065】

デッドタイム回路62は、外部FET1を駆動するPMOSトランジスタMP0とNMOSトランジスタMN0とが同時にONしないよう(両者のON期間が重ならないよう)に制御する機能を有するものである。

【0066】

クランプ電圧源64は、外部FET1をONさせるための電圧VCLAMP+を生成して出力する機能を有するものである。

【0067】

短絡電流検出用抵抗素子R1は、FETゲート電圧出力端子FET_PADが短絡したか否かを検出するための機能(第1の実施の形態の短絡電流検出用抵抗素子R0と略同様の機能)を有するものであり、NMOSトランジスタMN0のドレイン端子とFETゲート電圧出力端子FET_PADとの間に設けられている。

【0068】

なお、短絡電流検出用抵抗素子R0を設ける場所は、第1の実施の形態と同様に本実施の形態の位置に限るものではないが、NMOSトランジスタMN0がONの場合のFETゲート電圧出力端子FET_PADの短絡を検出し、本実施の形態では、短絡状態の場合は、NMOSトランジスタMM0がオフ状態になり、電流が流れなくなることから、本実施の形態のように、NMOSトランジスタMN0のドレイン端子とFETゲート電圧出力端子FET_PADとの間に設けることが好ましい。

【0069】

短絡保護回路70は、FETゲート電圧出力端子FET_PADが短絡した場合に、電池監視IC54を破壊から保護するための機能を有するものである。

【0070】

短絡保護回路60は、NMOSトランジスタMN1、MN2、MN3、電流源ibiass、抵抗素子Rpd、インバータ回路inv0、inv1、inv3、inv6、inv7、NOR回路nor1、及びnand回路nand1を備えて構成されている。

【0071】

NMOSトランジスタMN1のソース端子、MN2のソース端子は、共に、GND端子に接続される。NMOSトランジスタMN1のゲート端子はNOR回路nor1の出力端子と接続され、ドレイン端子は、抵抗素子Rpdを介してFETゲート電圧出力端子FET_PADに接続される。

【0072】

NMOSトランジスタMN2のゲート端子は、出力信号poffが入力されるようにデッドタイム回路62に接続され、ドレイン端子は、NMOSトランジスタMN3のソース端子に接続される。

【0073】

NMOSトランジスタMN3のゲート端子は、FETゲート電圧出力端子FET_PADに接続され、ドレイン端子(ノードV2)は、電流源ibiassを介してクランプ電圧源64出力のクランプ電圧VCLAMP+に接続される。NMOSトランジスタMN3のドレイン端子は、インバータ回路inv6、inv7を介してNAND回路nand1及びNOR回路nor1の入力端子へ接続される。

【0074】

デッドタイム回路62は、インバータ回路inv0に出力信号poffが入力されるように接続されると共に、インバータ回路inv0、inv1を介してPMOSトランジスタMP0のゲート端子に接続される。

【0075】

デッドタイム回路62の出力信号nonは、NAND回路nand1の入力端子に接続され、NAND回路nand1、インバータ回路inv3を介して、NMOSトランジスタMN0のゲート端子、及びNOR回路nor1の入力端子に接続される。

【0076】

本実施の形態のFET駆動回路60では、外部FET0のON/OFFを制御するFET ON信号を受け付けると、デッドタイム回路62は、出力信号poff及び出力信号nonを生成して出力する。外部FET1をONする場合は、出力信号poffを「L」レベル、出力信号nonを「L」レベルとする。「L」レベルの出力信号nonにより、NMOSトランジスタMN2はOFFになる。また、NAND回路nand1では、出力信号nonが「L」レベルであるため、ノードV3のレベル(電圧値)にかかわらず、「H」レベルの信号をインバータ回路inv3に出力する。従って、制御信号ngは「L」レベルになり、NMOSトランジスタMN0はOFFになる。一方、「L」レベルの出力信号poffにより、制御信号pgは「L」レベルになり、PMOSトランジスタMP0はONになる。これにより、FETゲート電圧出力端子FET_PADにクランプ電圧VCLAMP+が出力され、外部FET1のゲート端子に、クランプ電圧VCLAMP+が印加され、外部FET1がONする。

【0077】

一方、外部FET01OFFする場合は、出力信号poffを「H」レベル、出力信号nonを「H」レベルとする。外部FET1がOFFの場合は、NMOSトランジスタMN0がON、PMOSトランジスタMP0がOFFとなり、FETゲート電圧出力端子FET_PADの電圧はGNDとなり、外部FET1のゲート端子に、GNDが印加される。この状態では、制御信号ngは、「H」レベルであるため、NOR回路nor1の出力は、ノードV3のレベル(電圧値)にかかわらず、「L」レベルとなり、NMOSトランジスタMN1は、OFFしている。一方、NMOSトランジスタMN2では、「H」レベルの出力信号nonがゲート端子に印加されるため、ONしているが、NMOSトランジスタMN3では、FETゲート電圧出力端子FET_PADがGNDであるため、ゲート端子にGNDが印加され、OFFになっている。従って、ノードV2、V3は「H」レベルとなり、NAND回路nand1の入力端子には、「H」レベルの出力信号nonと、「H」レベルのノードV3の電圧とが入力されるため、出力が「L」レベルになり、制御信号ngが「H」レベルになり、NMOSトランジスタMN0のON状態が保持される。

【0078】

また、「H」レベルの出力信号poffより、制御信号pgは「H」レベルになり、PMOSトランジスタMP0のOFF状態が保持される。

【0079】

この状態において、FETゲート電圧出力端子FET_PADの電圧が、何らかの要因により電源電圧VDDに短絡した場合等、NMOSトランジスタMN3の閾値電圧、NMOSトランジスタMN0、MN2のON抵抗、短絡電流検出用抵抗素子R1により決まる短絡検出電圧以上となると、NMOSトランジスタMN3がONする。具体的には、NMOSトランジスタMN3の閾値電圧をVTH_MN3、NMOSトランジスタMN0のON抵抗をRON_MN0、NMOSトランジスタMN2のON抵抗をRON_MN2、短絡電流をIshort、短絡電流検出用抵抗素子R1の抵抗値をR1、電流源ibiassの電流値をIbiassとすると、以下の(3)式を満たすと、NMOSトランジスタMN3がONする。

【0080】

VTH_MN3>RON_MN2×Ibiass−(R1+RON_MN0)Ishort ・・・(3)

【0081】

NMOSトランジスタMN3がONすることにより、ノードV2、V3が「L」レベルになり、NAND回路nand1の出力が「H」レベルになり、制御信号ngは「L」レベルとなるため、NMOSトランジスタMN0がOFFとなる。

【0082】

一方、ノードV3及び制御信号ngが「L」レベルとなるため、NOR回路nor1の出力が「H」レベルになり、NMOSトランジスタMN1がONされる。

【0083】

NMOSトランジスタMN1がONされることにより、FETゲート電圧出力端子FET_PADは、抵抗素子Rpdを介して、GNDにプルダウンされた状態となり、短絡電流Ishortは、NMOSトランジスタMN1のON抵抗を無視すると、次の(4)式により制限される(抵抗素子Rpdの抵抗値をRpdとする)。

【0084】

Ishort=(FET_PAD電圧値)/Rpd ・・・(4)

【0085】

従って、FETゲート電圧出力端子FET_PADが電源電圧VDDに短絡した場合の最大短絡電流Ishort_maxは、Ishort_max=VDD/Rpdに制限される。

【0086】

この後、FETゲート電圧出力端子FET_PADを電源電圧VDDに短絡した要因が上述のようにして除去され、FETゲート電圧出力端子FET_PADが開放されると、FETゲート電圧出力端子FET_PADはプルダウン状態であるため、電圧値が下降する。電圧値が短絡検出電圧以下となると、NMOSトランジスタMN3はOFFする。これにより、ノードV2、V3は「H」レベルとなり、NAND回路nand1の出力が「L」レベルになり、制御信号ngは「H」レベルとなるため、NMOSトランジスタMN0がONする。一方、ノードV3及び制御信号ngが「H」レベルとなるため、NOR回路nor1の出力が「L」レベルになり、NMOSトランジスタMN1がOFFされる。NMOSトランジスタMN1がOFFすることにより、FETゲート電圧出力端子FET_PADのプルダウン状態が解除され、短絡検出前の状態(通常状態)に復帰する。

【0087】

本実施の形態の短絡保護回路70において、NMOSトランジスタMN2は、短絡検出電圧を電源電圧VDDにより調整する機能を有している。電源電圧VDDが低くなるにつれ、NMOSトランジスタMN0のON抵抗が大きくなり無視できなくなると、短絡検出電圧も大きくなるため、短絡状態でない場合であっても、NMOSトランジスタMN0をONする際に外部FET1のゲート駆動電流が流れることで、瞬間的に短絡検出電圧以上となり、短絡保護回路70による短絡保護機能(上述の動作)が動作してしまう可能性がある。

【0088】

もし、NMOSトランジスタMN2を設けない場合、外部FET1をOFFする際に、外部FET1のゲート端子の電荷を放電するため(OFFするため)の電流が瞬間的に流れる。電源電圧VDDが低い状態で、外部FET1をOFFすると、NMOSトランジスタMN0のON抵抗は、電源電圧VDDが高い場合に比べて大きくなるため、このゲート端子の電荷を放電するための電流により、短絡状態ではないにもかかわらず、短絡を検出してしまう可能性が生じる。NMOSトランジスタMN2を設けない場合は、上述の式(3)において、RON_MN2×Ibiass=0となり、R1+RON_MN0は電源で圧VDDが低い場合では大きくなるため、より小さい電流で短絡検出をすることになる。

【0089】

従って、第1の実施の形態と同様に、短絡保護が誤って動作してしまう場合、このゲート端子の電荷を放電する電流を短絡電流と判断してしまうため、短絡保護機能により電荷を放電する電流が制限されてしまい、外部FET1をONからOFFにする場合の動作速度が遅くなるという、問題が生じてしまう。

【0090】

本実施の形態のFET駆動回路60の短絡保護回路70では、NMOSトランジスタMN2を設けることにより、NMOSトランジスタMN2のON抵抗も電源電圧VDDが低くなるにつれ大きくなるため、短絡検出電圧が高くなり、従って、FETゲート電圧出力端子FET_PADの電圧値が短絡検出電圧を上回るのを防止することができる。すなわち、NMOSトランジスタMN2のトランジスタサイズ(ON抵抗値)を適切に選定することにより、上述の問題を回避することができる。

【0091】

以上説明したように、本実施の形態の電池監視システム50では、電池12の充電・放電を制御するNMOSトランジスタである外部FET1と、短絡保護回路70を有するFET駆動回路60を内蔵する電池監視IC54と、を備える。外部FET1がOFF状態の場合において、FETゲート電圧出力端子FET_PADの電圧が、何らかの要因により短絡し、短絡検出電圧以上となり、VTH_MN3>RON_MN2×Ibiass−(R1+RON_MN0)Ishortを満たすと、NMOSトランジスタMN3がONする。すなわち、短絡電流Ishortが生じることにより、NMOSトランジスタMN3がONする。また、NMOSトランジスタMN0がOFFとなり、さらにNMOSトランジスタMN1がONされる。NMOSトランジスタMN1がONされることにより、FETゲート電圧出力端子FET_PADは、抵抗素子Rpdを介して、プルダウンされた状態となり、電源電圧VDDに短絡した場合の最大短絡電流Ishort_maxは、Ishort_max=VDD/Rpdに制限される。

【0092】

すなわち、短絡状態の場合は、短絡保護回路70のNMOSトランジスタMN3により、GND端子とFETゲート電圧出力端子FET_PAD(外部FET1)との間で電流が流れる経路をNMOSトランジスタMN0及び短絡電流検出用抵抗素子R1を経由する経路から、NMOSトランジスタMN1及び抵抗素子Rpdを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC54が破壊されるのを防止することができる。

【0093】

また、本実施の形態では、短絡発生後にその要因が除去された場合、FETゲート電圧出力端子FET_PADがプルダウン状態であるため、電圧値が短絡検出電圧以下となると、NMOSトランジスタMN3がOFFし、NMOSトランジスタMN0がONする。また、NMOSトランジスタMN1がOFFする。これにより、FETゲート電圧出力端子FET_PADのプルダウン状態が解除され、短絡検出前の状態(通常状態)に復帰する。従って、電池監視IC54をそのまま継続して使用することができる。

【0094】

なお、上述の第1の実施の形態及び第2の実施の形態では、多セル接続された電池12の電池監視IC(電池監視IC14、54)に内蔵されるFET駆動回路(FET駆動回路20、60)を想定し、外部FET(外部FET0、1)をONする際の出力電圧としてクランプ電圧源(クランプ電圧源24、64)から出力されたクランプ電圧(VCLAMP−、VCLAMP+)を用いる構成について説明したがこれに限らず、例えば、クランプ電圧源を仕様せず電源電圧VDD−GNDを駆動電源とするFET駆動回路を用いるように構成してもよい。なお、この場合において、FETゲート電圧出力端子に電源電圧VDD短絡、GND短絡の両方の保護を設ける必要がある場合には、第1の実施の形態及び第2の実施の形態を併用して適用するようにすればよい。

【0095】

また、上述の第1の実施の形態及び第2の実施の形態では、FETゲート電圧出力端子FET_PADが短絡したか否かを検出する場合について詳細に説明したがFETゲート電圧出力端子FET_PADに限らず、第1の実施の形態では、MOSトランジスタMP0と外部FET0とを接続する配線、また、第2の実施の形態では、MOSトランジスタMN0と外部FET1とを接続する配線が短絡したか否かについても、それぞれ第1の実施の形態及び第2の実施の形態と同様に検出することができる。

【0096】

また、上述の第1の実施の形態及び第2の実施の形態では、外部FET(外部FET0、1)に対する短絡保護回路(短絡保護回路30、70)を有するFET駆動回路(FET駆動回路20、60)について詳細に説明したが外部FET駆動用の回路に限らない。例えば、FET以外の部品駆動用回路に同様な駆動回路を用いる場合には、当該駆動回路に上述の保護回路を適用して、短絡から保護するように構成してもよい。

【0097】

また、上述の第1の実施の形態及び第2の実施の形態では、FETゲート電圧出力端子FET_PADが短絡した場合の短絡保護回路(短絡保護回路30、70)を有するFET駆動回路(FET駆動回路20、60)について詳細に説明したがこれに限らない。例えば、過電流保護機能(過電流保護回路)つき負荷駆動回路として用いるものであってもよい。当該過電流保護回路の場合、例えば、第1の実施の形態のように構成される場合は、検出電圧をPMOSトランジスタMP0、MP2、MP3、短絡電流検出用抵抗素子R0により特定の検出電圧に設定できる(上述の(1)式参照)ため、万一、想定よりも過大な電流を駆動するような負荷が負荷駆動回路(当該負荷駆動回路を内蔵するIC)に接続された場合に上述と同様な動作により過大電流を制限することによりICを保護することができる。

【0098】

また、上述の第1の実施の形態及び第2の実施の形態では、電池12を制御するスイッチング素子として、PMOSトランジスタ(外部FET0)、NMOSトランジスタ(外部FET1)を外部に設けるように構成しているが、これに限らず、電池監視IC(電池監視IC14、54)に内蔵するようにしてもよい。なお、本実施の形態のように電池保護ICの場合では、電池12の充電電流/負荷電流を制御するには大電流を流してON/OFFすることとなるため、この大電流を制御するスイッチング素子(FET)を電池監視ICに内蔵しようとすると電池監視ICのサイズが非常に大きくなるため、実装的な観点からあまり好ましくない。また、また発熱の観点からも他回路と同一のパッケージに収めるのは好ましくない。従って、上述の第1の実施の形態及び第2の実施の形態のように、外部FETとすることが好ましい。なお、このように外部に設けることにより内蔵する場合に比べて、FETゲート電圧出力端子FET_PADと外部FETとの間の伝送路(FETゲート電圧出力端子FET_PAD)が短絡しやすくなるため、上述の第1の実施の形態及び第2の実施の形態のように短絡保護回路(短絡保護回路30、70)を設けることにより、短絡から保護する効果がより高くなる。

【0099】

また、上述の第1の実施の形態及び第2の実施の形態では、短絡検出電圧を調整する機能を有する手段として、PMOSトランジスタMP2、NMOSトランジスタMN2を設けるように構成しているが、短絡検出電圧を調整する機能を有する手段の構成はこれに限らない。本実施の形態では、抵抗値により短絡検出電圧を調整するため、その他の抵抗素子であってもよい。なお、例えば、第1の実施の形態の場合、短絡検出電圧が短絡電流検出用抵抗素子R0の抵抗値とPMOSトランジスタMP0のON抵抗で決まり、PMOSトランジスタMP0のON抵抗は、温度と電源電圧VDDによりその値が変化するため、PMOSトランジスタMP0と温度、電源電圧VDDに対するON抵抗の変化が同様であるPMOSトランジスタを使用したほうが、温度、電源電圧VDDの変化による短絡検出電圧値の影響を抑制することができる。一方、抵抗素子を用いた場合、当該抵抗素子の抵抗値自体は電源電圧VDDの変化の影響を受けず、またPMOSトランジスタMP0と異なる温度特性を持っているため、温度条件や電源電圧VDDの変化に対し、短絡検出電圧値が影響を受けやすくなるため、上述の第1の実施の形態及び第2の実施の形態のようにMOSトランジスタ(PMOSトランジスタMP2、NMOSトランジスタMN2)とすることが好ましい。

【符号の説明】

【0100】

10、50 電池監視システム

12 電池

14、54 電池監視IC

24、64 クランプ電圧源

30、70 短絡保護回路

VDD 電源電圧

FET0、FET1 外部FET

【技術分野】

【0001】

本発明は、半導体回路、半導体装置、及び電池監視システム、特に短絡保護機能を有する半導体回路、半導体装置、及び電池監視システムに関するものである。

【背景技術】

【0002】

一般に、ハイブリッド自動車や電気自動車のモータ駆動等に用いられる大容量で高出力なバッテリーとして、複数の電池セルが直列に接続されたバッテリー(具体的一例としては、リチウムイオンバッテリー等が挙げられる)が用いられている。当該バッテリーの電池や太陽電池等の電池電圧を監視・制御するための電池監視システムが知られている。

【0003】

このような電池監視システムとして、電池の充電/放電を制御するスイッチング素子を備えた電池監視システムが知られている(例えば特許文献1〜特許文献4参照。)

【0004】

このような従来の電池監視システムでは、複数の電池セルを含む電池と、当該電池に含まれる電池セルの電圧を監視・制御する電池監視IC(Integrated Circuit、電池監視素子)と、を備えて構成されている。

【0005】

一般に、電池監視システムにおいて、電池監視IC外部に設けられたFET(Field Effect Transistor、以下、外部FETという)をスイッチング素子として使用し、電池の充電や放電を制御する方式が多く適用されている。このような電池監視システムでは、外部FETのゲートを駆動する駆動回路を電池監視ICに内蔵しているものが多い。図5に、外部FETとして、PMOSトランジスタを用いた電池監視システムの具体例を示す。また、図6に、外部FETとして、NMOSトランジスタを用いた電池監視システムの具体例を示す。

【0006】

電池監視ICを多セル接続された電池に使用する場合、その電源電圧VDDは、数十V以上で使用され、また、電池セルの電圧により大きく変動するため、外部FETの駆動回路は、外部FETのゲート−ソース間耐圧を越えないよう、図5、6に示すようにFET駆動電圧(ゲート電圧)を所定の電圧でクランプする機能を付加して構成される。

【0007】

図5に示した、外部FET0がPMOSトランジスタである場合のON/OFFの制御動作について詳細に説明する。

【0008】

図5に示した電池監視システム100のFET駆動回路120(電池監視IC114)では、外部FET0のON/OFFを制御するFET ON信号を受け付けると、外部FET0を駆動するPMOSトランジスタMP0とNMOSトランジスタMN0とが同時にONしないよう制御するデッドタイム回路122を介して、PMOSトランジスタMP0のON/OFFの制御信号pgと、NMOSトランジスタMN0のON/OFFを制御する制御信号ngとを生成する。外部FET0をOFFする場合は、制御信号pgを「L」レベル、制御信号ngを「L」レベルとし、PMOSトランジスタMP0をON、NMOSトランジスタをOFFにすることで、FETゲート電圧出力端子FET_PADに電源電圧VDDを出力し、外部FET0をOFFする。一方、外部FET0をONする場合は、制御信号pgを「H」レベル、制御信号ngを「H」レベルとし、PMOSトランジスタMP0をOFF、NMOSトランジスタをONにすることで、FETゲート電圧出力端子FET_PADに電圧VCLAMP−を出力し、外部FET0をONにする。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開平9−261861号公報

【特許文献2】特開平8−190936号公報

【特許文献3】特開平8−196042号公報

【特許文献4】特開2000−102176号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

図5に示したFET駆動回路120の場合、外部FET0をON、つまりNMOSトランジスタMN0がONとなっている状態で、何からの外的要因により、FETゲート電圧出力端子FET_PADが電源電圧VDD、或いはGNDに短絡して短絡電流が発生する場合でも、クランプ電圧源124の電流能力により、その短絡電流の大きさが制限されるため、電池監視IC114の破壊には至らない。

【0011】

しかしながら、外部FET0をOFF、つまりPMOSトランジスタMP0がONとなっている状態で、FETゲート電圧出力端子FET_PADが、GNDに短絡すると、PMOSトランジスタMP0を介して電源電圧VDDからGNDへ大きな短絡電流が流れ、電池監視IC114の破壊を引き起こしてしまう場合がある、という問題が生じる。

【0012】

また、同様に図6に示した電池監視システム150のFET駆動回路160(電池監視IC154)の場合、外部FET1をON、つまりPMOSトランジスタMP0がONとなっている状態で、何からの外的要因により、FETゲート電圧出力端子FET_PADが電源電圧VDDに短絡して短絡電流が発生する場合でも、クランプ電圧源164の電流能力により、その短絡電流の大きさが制限されるため、電池監視IC154の破壊には至らない。

【0013】

しかしながら、外部FET1をOFF、つまりPMOSトランジスタMP0がOFFとなっている状態で、FETゲート電圧出力端子FET_PADが、電源電圧VDDに短絡すると、NMOSトランジスタMN0を介して電源電圧VDDからGNDへ大きな短絡電流が流れ、電池監視ICの破壊を引き起こしてしまう場合がある、という問題が生じる。

【0014】

本発明は、上述した問題を解決するために提案されたものであり、過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供することを目的とする。

【課題を解決するための手段】

【0015】

請求項1に記載の半導体回路は、第1スイッチ手段をオフするための電圧を供給するオフ電源と、前記第1スイッチ手段と、を電気的に接続する第1伝送路と、前記第1伝送路上に設けられた第2スイッチ手段と、前記オフ電源と前記第2スイッチ手段との間の前記第1伝送路と、前記第1スイッチ手段と、を電気的に接続し、かつ前記第1伝送路よりも抵抗値が高い第2伝送路と、前記第2伝送路上に設けられた第3スイッチ手段と、前記第1伝送路に接続され、前記第2スイッチ手段と前記第1スイッチ手段との間の前記第1伝送路に流れる電流に応じた電圧を検知し、かつ、検知した前記電圧と閾値とに応じて前記第2スイッチ手段をオフにすると共に、前記第3スイッチ手段をオンにする電圧検知手段と、前記電圧検知手段と前記第1伝送路との間に設けられ、前記オフ電源の電圧値の変動に応じて前記電圧値が変動しないように前記電圧値を調整する調整手段と、を備える。

【0016】

請求項6に記載の半導体装置は、第1スイッチ手段と、前記第1スイッチ手段をオフするための電圧を供給するオフ電源と前記第1スイッチ手段とを電気的に接続するための請求項1から請求項5のいずれか1項に記載の半導体回路と、を備える。

【0017】

請求項7に記載の電池監視システムは、電池と、前記電池の高電位側に接続され、かつ前記電池の充電、放電を制御する第1スイッチ手段と、前記第1スイッチ手段をオフするための電圧を供給するオフ電源と前記第1スイッチ手段とを電気的に接続するための請求項1から請求項5のいずれか1項に記載の半導体回路と、を備える。

【発明の効果】

【0018】

本発明によれば、過大電流による素子の破壊を防止することができる、という効果を奏する。

【図面の簡単な説明】

【0019】

【図1】第1の実施の形態に係る電池監視システムの概略構成の一例を示す概略構成図である。

【図2】第1の実施の形態に係る短絡保護回路を備えたFET駆動回路の概略構成の一例を示す回路図である。

【図3】第2の実施の形態に係る池監視システムの概略構成の一例を示す概略構成図である。

【図4】第2の実施の形態に係る短絡保護回路を備えたFET駆動回路の概略構成の一例を示す回路図である。

【図5】従来の電池監視システムの概略構成の一例を示す概略構成図である。

【図6】従来の電池監視システムの概略構成の一例を示す概略構成図である。

【発明を実施するための形態】

【0020】

[第1の実施の形態]

【0021】

まず、以下、図面を参照して本発明の基本構成となる、第1の実施の形態の電池監視システムについて詳細に説明する。

【0022】

本実施の形態の電池監視システムの概略構成の一例の概略構成図を図1に示す。また、本実施の形態のFET駆動回路の概略構成の一例の回路図を図2に示す。

【0023】

図1に示した本実施の形態の電池監視システム10は、電池12と、電池12の充電・放電を制御する外部FET0と、外部FET0を駆動するためのFET駆動回路20を含む電池監視IC14と、を備えて構成されている。

【0024】

本実施の形態では、外部FET0は、PMOSトランジスタであり、ソース端子が電池12の高電位側に接続されており、ドレイン端子が端子PACK(+)に接続されており、かつゲート端子が抵抗素子Rgを介して、電池監視IC14のFET駆動回路20のFETゲート電圧出力端子FET_PADに接続されている。

【0025】

また、電池12は、複数の電池セルを含んで成り、低電位側が端子PACK(−)(本実施の形態ではGND)に接続されている。

【0026】

FET駆動回路20は、電池監視IC14内部に設けられており、外部FET0のON/OFFを制御する機能を有している。本実施の形態のFET駆動回路20は、デッドタイム回路22、クランプ電圧源24、短絡保護回路30、外部FET0駆動用のPMOSトランジスタMP0、NMOSトランジスタMN0、及び短絡電流検出用抵抗素子R0を備えて構成されている。

【0027】

本実施の形態のFET駆動回路20は、PMOSトランジスタMP0及びNMOSトランジスタMN0のON/OFFにより、FETゲート電圧出力端子FET_PADの電圧を電源電圧VDDとした場合(PMOSトランジスタMP0=ON、NMOSトランジスタMN0=OFF)に、外部FET0がOFF、FETゲート電圧出力端子FET_PADの電圧をクランプ電圧源24から出力されたクランプ電圧VCLAMP−とした場合(PMOSトランジスタMP0=OFF、NMOSトランジスタMN0=ON)に、外部FET0がONするように外部FET0を制御(駆動)する機能を有している。このように外部FET0を制御することにより、電池12を使用可/不可を切り替える。

【0028】

デッドタイム回路22は、外部FET0を駆動するPMOSトランジスタMP0とNMOSトランジスタMN0とが同時にONしないよう(両者のON期間が重ならないよう)に制御する機能を有するものである。

【0029】

クランプ電圧源24は、外部FET0をONさせるための電圧VCLAMP−を生成して出力する機能を有するものである。

【0030】

短絡電流検出用抵抗素子R0は、FETゲート電圧出力端子FET_PADが短絡したか否かを検出するための機能を有するものであり、PMOSトランジスタMP0のドレイン端子とFETゲート電圧出力端子FET_PADとの間に設けられている。本実施の形態の電池監視システム10では、短絡電流検出用抵抗素子R0を別途、電池監視IC14内部の回路(図示省略)でモニタし、短絡電流検出用抵抗素子R0を流れる電流(短絡電流)の大きさにより、短絡状態を検出している。また本実施の形態では、短絡電流検出用抵抗素子R0のモニタにより短絡状態であることを検出した場合は、短絡要因を除去するために所定の措置を、所定の回路や人的手段により行うものとしている。

【0031】

なお、短絡電流検出用抵抗素子R0を設ける場所は、本実施の形態の位置に限るものではないが、PMOSトランジスタMP0がONの場合のFETゲート電圧出力端子FET_PADの短絡を検出し、本実施の形態では、短絡状態の場合は、PMOSトランジスタMP0がオフ状態になり、電流が流れなくなることから、本実施の形態のように、PMOSトランジスタMP0のドレイン端子とFETゲート電圧出力端子FET_PADとの間に設けることが好ましい。

【0032】

図2に示すように、短絡保護回路30は、FETゲート電圧出力端子FET_PADがGND電位に短絡した場合に、電池監視IC14を破壊から保護するための機能を有するものである。

【0033】

短絡保護回路30は、PMOSトランジスタMP1、MP2、MP3、電流源ibiass、抵抗素子Rpu、インバータ回路inv1、inv2、inv3、inv4、inv5、NOR回路nor0、及びnand回路nand0を備えて構成されている。

【0034】

PMOSトランジスタMP1のソース端子、MP2のソース端子は、共に、電源電圧VDDに接続される。PMOSトランジスタMP1のゲート端子はNAND回路nand0の出力端子と接続され、ドレイン端子は、抵抗素子Rpuを介してFETゲート電圧出力端子FET_PADに接続される。

【0035】

PMOSトランジスタMP2のゲート端子は、出力信号poffが入力されるようにデッドタイム回路22に接続され、ドレイン端子は、PMOSトランジスタMP3のソース端子に接続される。

【0036】

PMOSトランジスタMP3のゲート端子は、FETゲート電圧出力端子FET_PADに接続され、ドレイン端子(ノードV0)は、電流源ibiassを介してGNDに接続される。PMOSトランジスタMP3のドレイン端子は、インバータ回路inv4、inv5を介してNAND回路nand0及びNOR回路nor0の入力端子へ接続される。

【0037】

デッドタイム回路22は、インバータ回路inv2に出力信号nonが入力されるように接続されると共に、インバータ回路inv2、inv3を介してNMOSトランジスタMN0のゲート端子に接続される。

【0038】

デッドタイム回路22の出力信号poffは、NOR回路nor0の入力端子に接続され、NOR回路nor0、インバータ回路inv1を介して、PMOSトランジスタMP0のゲート端子、及びNAND回路nand0の入力端子に接続される。

【0039】

本実施の形態のFET駆動回路20では、外部FET0のON/OFFを制御するFET ON信号を受け付けると、デッドタイム回路22は、出力信号poff及び出力信号nonを生成して出力する。外部FET0をONする場合は、出力信号poffを「H」レベル、出力信号nonを「H」レベルとする。「H」レベルの出力信号poffにより、PMOSトランジスタMP2はOFFになる。また、NOR回路nor0では、出力信号poffが「H」レベルであるため、ノードV1のレベル(電圧値)にかかわらず、「L」レベルの信号をインバータ回路inv1に出力する。従って、制御信号pgは「H」レベルになり、PMOSトランジスタMP0はOFFになる。一方、「H」レベルの出力信号nonにより、制御信号ngは「H」レベルになり、NMOSトランジスタMN0はONになる。これにより、FETゲート電圧出力端子FET_PADにクランプ電圧VCLAMP−が出力され、外部FET0のゲート端子に、クランプ電圧VCLAMP−が印加され、外部FET0がONする。

【0040】

一方、外部FET0をOFFする場合は、出力信号poffを「L」レベル、出力信号nonを「L」レベルとする。外部FET0がOFFの場合は、PMOSトランジスタMP0がON、NMOSトランジスタMN0がOFFとなり、FETゲート電圧出力端子FET_PADの電圧は電源電圧VDDとなり、外部FET0のゲート端子に、電源圧VDDが印加される。この状態では、制御信号pgは、「L」レベルであるため、NAND回路nand0の出力は、ノードV1のレベル(電圧値)にかかわらず、「H」レベルとなり、PMOSトランジスタMP1は、OFFしている。一方、PMOSトランジスタMP2では、「L」レベルの出力信号poffがゲート端子に印加されるため、ONしているが、PMOSトランジスタMP3では、FETゲート電圧出力端子FET_PADが電源電圧VDDであるため、ゲート端子に電源電圧VDDが印加され、OFFになっている。従って、ノードV0、V1は「L」レベルとなり、NOR回路nor0の入力端子には、「L」レベルの出力信号poffと、「L」レベルのノードV1の電圧とが入力されるため、出力が「H」レベルになり、制御信号pgが「L」レベルになり、PMOSトランジスタMP0のON状態が保持される。

【0041】

また、「L」レベルの出力信号nonにより、制御信号ngは「L」レベルになり、NMOSトランジスタMN0のOFF状態が保持される。

【0042】

この状態において、FETゲート電圧出力端子FET_PADの電圧が、何らかの要因によりGNDに短絡した場合等、PMOSトランジスタMP3の閾値電圧、PMOSトランジスタMP0、MP2のON抵抗、短絡電流検出用抵抗素子R0により決まる短絡検出電圧以下となると、PMOSトランジスタMP3がONする。具体的には、PMOSトランジスタMP3の閾値電圧をVTH_MP3、PMOSトランジスタMP0のON抵抗をRON_MP0、PMOSトランジスタMP2のON抵抗をRON_MP2、短絡電流をIshort、短絡電流検出用抵抗素子R0の抵抗値をR0、電流源ibiassの電流値をIbiassとすると、以下の(1)式を満たすと、PMOSトランジスタMP3がONする。

【0043】

VTH_MP3<(R0+RON_MP0)Ishort−RON_MP2×Ibiass ・・・(1)

【0044】

PMOSトランジスタMP3がONすることにより、ノードV0、V1が「H」レベルになり、NOR回路nor0の出力が「L」レベルになり、制御信号pgは「H」レベルとなるため、PMOSトランジスタMP0がOFFとなる。

【0045】

一方、ノードV1及び制御信号pgが「H」レベルとなるため、NAND回路nand0の出力が「L」レベルになり、PMOSトランジスタMP1がONされる。

【0046】

PMOSトランジスタMP1がONされることにより、FETゲート電圧出力端子FET_PADは、抵抗素子Rpuを介して、電源電圧VDDにプルアップされた状態となり、短絡電流Ishortは、PMOSトランジスタMP1のON抵抗を無視すると、次の(2)式により制限される(抵抗素子Rpuの抵抗値をRpuとする)。

【0047】

Ishort=(電源電圧VDD−FET_PAD電圧値)/Rpu ・・・(2)

【0048】

従って、FETゲート電圧出力端子FET_PADがGNDに短絡した場合の最大短絡電流Ishort_maxは、Ishort_max=VDD/Rpuに制限される。

【0049】

この後、FETゲート電圧出力端子FET_PADをGNDに短絡した要因が上述のようにして除去され、FETゲート電圧出力端子FET_PADが開放されると、FETゲート電圧出力端子FET_PADはプルアップ状態であるため、電圧値が上昇する。電圧値が短絡検出電圧以上となると、PMOSトランジスタMP3はOFFする。これにより、ノードV0、V1は「L」レベルとなり、NOR回路nor0の出力が「H」レベルになり、制御信号pgは「L」レベルとなるため、PMOSトランジスタMP0がONする。一方、ノードV1及び制御信号pgが「L」レベルとなるため、NAND回路nand0の出力が「H」レベルになり、PMOSトランジスタMP1がOFFされる。PMOSトランジスタMP1がOFFすることにより、FETゲート電圧出力端子FET_PADのプルアップ状態が解除され、短絡検出前の状態(通常状態)に復帰する。

【0050】

本実施の形態の短絡保護回路30において、PMOSトランジスタMP2は、短絡検出電圧を電源電圧VDDにより調整する機能を有している。電源電圧VDDが低くなるにつれ、PMOSトランジスタMP0のON抵抗が大きくなり無視できなくなると、短絡検出電圧も大きくなるため、短絡状態でない場合であっても、PMOSトランジスタMP0をONする際に外部FET0のゲート駆動電流が流れることで、瞬間的に短絡検出電圧以下となり、短絡保護回路30による短絡保護機能(上述の動作)が動作してしまう可能性がある。

【0051】

もし、PMOSトランジスタMP2を設けない場合、外部FET0をOFFする際に、外部FET0のゲート端子の電荷を放電するため(OFFするため)の電流が瞬間的に流れる。電源電圧VDDが低い状態で、外部FET0をOFFすると、PMOSトランジスタMP0のON抵抗は、電源電圧VDDが高い場合に比べて大きくなるため、このゲート端子の電荷を放電するための電流により、短絡状態ではないにもかかわらず、短絡を検出してしまう可能性が生じる。PMOSトランジスタMP2を設けない場合は、上述の式(1)において、RON_MP2×Ibiass=0となり、R0+RON_MP0は電源電圧VDDが低い場合では大きくなるため、より小さい電流で短絡検出をすることになる。

【0052】

短絡保護が誤って動作してしまう場合、このゲート端子の電荷を放電する電流を短絡電流と判断してしまうため、短絡保護機能により電荷を放電する電流が制限されてしまい、外部FET0をONからOFFにする場合の動作速度が遅くなるという、問題が生じてしまう。

【0053】

本実施の形態のFET駆動回路20の短絡保護回路30では、PMOSトランジスタMP2を設けることにより、PMOSトランジスタMP2のON抵抗も電源電圧VDDが低くなるにつれ大きくなるため、短絡検出電圧が低くなり、上述のように短絡検出電圧が大きくなることを抑制することができる。従って、FETゲート電圧出力端子FET_PADの電圧値が短絡検出電圧を下回るのを防止することができる。すなわち、PMOSトランジスタMP2のトランジスタサイズ(ON抵抗値)を適切に選定することにより、上述の問題を回避することができる。

【0054】

以上説明したように、本実施の形態の電池監視システム10では、電池12の充電・放電を制御する外部FET0と、短絡保護回路30を有するFET駆動回路20を内蔵する電池監視IC14と、を備える。外部FET0がOFF状態の場合において、FETゲート電圧出力端子FET_PADの電圧が、何らかの要因により短絡し、短絡検出電圧以下となり、VTH_MP3<(R0+RON_MP0)Ishort−RON_MP2×Ibiassを満たすと、PMOSトランジスタMP3がONする。すなわち、短絡電流Ishortが生じることにより、PMOSトランジスタMP3がONする。また、PMOSトランジスタMP0がOFFとなり、さらにPMOSトランジスタMP1がONされる。PMOSトランジスタMP1がONされることにより、FETゲート電圧出力端子FET_PADは、抵抗素子Rpuを介して、プルアップされた状態となり、GNDに短絡した場合の最大短絡電流Ishort_maxは、Ishort_max=VDD/Rpuに制限される。

【0055】

すなわち、短絡状態の場合は、短絡保護回路30のPMOSトランジスタMP3により、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

【0056】

また、本実施の形態では、短絡発生後にその要因が除去された場合、FETゲート電圧出力端子FET_PADがプルアップ状態であるため、電圧値が短絡検出電圧以上となると、PMOSトランジスタMP3がOFFし、PMOSトランジスタMP0がONする。また、PMOSトランジスタMP1がOFFする。これにより、FETゲート電圧出力端子FET_PADのプルアップ状態が解除され、短絡検出前の状態(通常状態)に復帰する。従って、電池監視IC14をそのまま継続して使用することができる。

【0057】

[第2の実施の形態]

【0058】

以下、図面を参照して本発明の第2の実施の形態の電池監視システムについて詳細に説明する。第1の実施の形態では外部FET0としてPMOSトランジスタを用いた場合について説明したが、本実施の形態の電池監視システムでは、は外部FETとしてNMOSトランジスタ(外部FET1、図3参照)を用いた場合について説明する。

【0059】

本実施の形態の電池監視システムの概略構成の一例の概略構成図を図3に示す。また、本実施の形態のFET駆動回路の概略構成の一例の回路図を図4に示す。なお、本実施の形態において、第1の実施の形態と略同様の構成、及び動作については、その旨を記載し、詳細な説明を省略する。

【0060】

図3に示した本実施の形態の電池監視システム50は、電池12と、電池12の充電・放電を制御する外部FET1と、外部FET1を駆動するためのFET駆動回路60を含む電池監視IC54と、を備えて構成されている。

【0061】

本実施の形態では、外部FET1は、NMOSトランジスタであり、ソース端子が電池12の低電位側に接続されており、ドレイン端子が端子PACK(−)(本実施の形態ではGND電位)に接続されており、かつゲート端子が抵抗素子Rgを介して、電池監視IC54のFET駆動回路60のFETゲート電圧出力端子FET_PADに接続されている。

【0062】

また、電池12は、複数の電池セルを含んで成り、低電位側が端子PACK(+)に接続されている。

【0063】

FET駆動回路60は、電池監視IC54内部に形成されており、外部FET1のON/OFFを制御する機能を有している。本実施の形態のFET駆動回路60は、デッドタイム回路62、クランプ電圧源64、短絡保護回路70、外部FET1駆動用のPMOSトランジスタMP0、NMOSトランジスタMN0、及び短絡電流検出用抵抗素子R1を備えて構成されている。

【0064】

本実施の形態のFET駆動回路60は、PMOSトランジスタMP0及びNMOSトランジスタMN0のON/OFFにより、FETゲート電圧出力端子FET_PADの電圧をGNDとした場合(PMOSトランジスタMP0=OFF、NMOSトランジスタMN0=ON)に、外部FET1がOFF、FETゲート電圧出力端子FET_PADの電圧をクランプ電圧源64から出力されたクランプ電圧VCLAMP+とした場合(PMOSトランジスタMP0=ON、NMOSトランジスタMN0=OFF)に、外部FET1がONするように外部FET1を制御(駆動)する機能を有している。このように外部FET1を制御することにより、電池12を使用可/不可を切り替える。

【0065】

デッドタイム回路62は、外部FET1を駆動するPMOSトランジスタMP0とNMOSトランジスタMN0とが同時にONしないよう(両者のON期間が重ならないよう)に制御する機能を有するものである。

【0066】

クランプ電圧源64は、外部FET1をONさせるための電圧VCLAMP+を生成して出力する機能を有するものである。

【0067】

短絡電流検出用抵抗素子R1は、FETゲート電圧出力端子FET_PADが短絡したか否かを検出するための機能(第1の実施の形態の短絡電流検出用抵抗素子R0と略同様の機能)を有するものであり、NMOSトランジスタMN0のドレイン端子とFETゲート電圧出力端子FET_PADとの間に設けられている。

【0068】

なお、短絡電流検出用抵抗素子R0を設ける場所は、第1の実施の形態と同様に本実施の形態の位置に限るものではないが、NMOSトランジスタMN0がONの場合のFETゲート電圧出力端子FET_PADの短絡を検出し、本実施の形態では、短絡状態の場合は、NMOSトランジスタMM0がオフ状態になり、電流が流れなくなることから、本実施の形態のように、NMOSトランジスタMN0のドレイン端子とFETゲート電圧出力端子FET_PADとの間に設けることが好ましい。

【0069】

短絡保護回路70は、FETゲート電圧出力端子FET_PADが短絡した場合に、電池監視IC54を破壊から保護するための機能を有するものである。

【0070】

短絡保護回路60は、NMOSトランジスタMN1、MN2、MN3、電流源ibiass、抵抗素子Rpd、インバータ回路inv0、inv1、inv3、inv6、inv7、NOR回路nor1、及びnand回路nand1を備えて構成されている。

【0071】

NMOSトランジスタMN1のソース端子、MN2のソース端子は、共に、GND端子に接続される。NMOSトランジスタMN1のゲート端子はNOR回路nor1の出力端子と接続され、ドレイン端子は、抵抗素子Rpdを介してFETゲート電圧出力端子FET_PADに接続される。

【0072】

NMOSトランジスタMN2のゲート端子は、出力信号poffが入力されるようにデッドタイム回路62に接続され、ドレイン端子は、NMOSトランジスタMN3のソース端子に接続される。

【0073】

NMOSトランジスタMN3のゲート端子は、FETゲート電圧出力端子FET_PADに接続され、ドレイン端子(ノードV2)は、電流源ibiassを介してクランプ電圧源64出力のクランプ電圧VCLAMP+に接続される。NMOSトランジスタMN3のドレイン端子は、インバータ回路inv6、inv7を介してNAND回路nand1及びNOR回路nor1の入力端子へ接続される。

【0074】

デッドタイム回路62は、インバータ回路inv0に出力信号poffが入力されるように接続されると共に、インバータ回路inv0、inv1を介してPMOSトランジスタMP0のゲート端子に接続される。

【0075】

デッドタイム回路62の出力信号nonは、NAND回路nand1の入力端子に接続され、NAND回路nand1、インバータ回路inv3を介して、NMOSトランジスタMN0のゲート端子、及びNOR回路nor1の入力端子に接続される。

【0076】

本実施の形態のFET駆動回路60では、外部FET0のON/OFFを制御するFET ON信号を受け付けると、デッドタイム回路62は、出力信号poff及び出力信号nonを生成して出力する。外部FET1をONする場合は、出力信号poffを「L」レベル、出力信号nonを「L」レベルとする。「L」レベルの出力信号nonにより、NMOSトランジスタMN2はOFFになる。また、NAND回路nand1では、出力信号nonが「L」レベルであるため、ノードV3のレベル(電圧値)にかかわらず、「H」レベルの信号をインバータ回路inv3に出力する。従って、制御信号ngは「L」レベルになり、NMOSトランジスタMN0はOFFになる。一方、「L」レベルの出力信号poffにより、制御信号pgは「L」レベルになり、PMOSトランジスタMP0はONになる。これにより、FETゲート電圧出力端子FET_PADにクランプ電圧VCLAMP+が出力され、外部FET1のゲート端子に、クランプ電圧VCLAMP+が印加され、外部FET1がONする。

【0077】

一方、外部FET01OFFする場合は、出力信号poffを「H」レベル、出力信号nonを「H」レベルとする。外部FET1がOFFの場合は、NMOSトランジスタMN0がON、PMOSトランジスタMP0がOFFとなり、FETゲート電圧出力端子FET_PADの電圧はGNDとなり、外部FET1のゲート端子に、GNDが印加される。この状態では、制御信号ngは、「H」レベルであるため、NOR回路nor1の出力は、ノードV3のレベル(電圧値)にかかわらず、「L」レベルとなり、NMOSトランジスタMN1は、OFFしている。一方、NMOSトランジスタMN2では、「H」レベルの出力信号nonがゲート端子に印加されるため、ONしているが、NMOSトランジスタMN3では、FETゲート電圧出力端子FET_PADがGNDであるため、ゲート端子にGNDが印加され、OFFになっている。従って、ノードV2、V3は「H」レベルとなり、NAND回路nand1の入力端子には、「H」レベルの出力信号nonと、「H」レベルのノードV3の電圧とが入力されるため、出力が「L」レベルになり、制御信号ngが「H」レベルになり、NMOSトランジスタMN0のON状態が保持される。

【0078】

また、「H」レベルの出力信号poffより、制御信号pgは「H」レベルになり、PMOSトランジスタMP0のOFF状態が保持される。

【0079】

この状態において、FETゲート電圧出力端子FET_PADの電圧が、何らかの要因により電源電圧VDDに短絡した場合等、NMOSトランジスタMN3の閾値電圧、NMOSトランジスタMN0、MN2のON抵抗、短絡電流検出用抵抗素子R1により決まる短絡検出電圧以上となると、NMOSトランジスタMN3がONする。具体的には、NMOSトランジスタMN3の閾値電圧をVTH_MN3、NMOSトランジスタMN0のON抵抗をRON_MN0、NMOSトランジスタMN2のON抵抗をRON_MN2、短絡電流をIshort、短絡電流検出用抵抗素子R1の抵抗値をR1、電流源ibiassの電流値をIbiassとすると、以下の(3)式を満たすと、NMOSトランジスタMN3がONする。

【0080】

VTH_MN3>RON_MN2×Ibiass−(R1+RON_MN0)Ishort ・・・(3)

【0081】

NMOSトランジスタMN3がONすることにより、ノードV2、V3が「L」レベルになり、NAND回路nand1の出力が「H」レベルになり、制御信号ngは「L」レベルとなるため、NMOSトランジスタMN0がOFFとなる。

【0082】

一方、ノードV3及び制御信号ngが「L」レベルとなるため、NOR回路nor1の出力が「H」レベルになり、NMOSトランジスタMN1がONされる。

【0083】

NMOSトランジスタMN1がONされることにより、FETゲート電圧出力端子FET_PADは、抵抗素子Rpdを介して、GNDにプルダウンされた状態となり、短絡電流Ishortは、NMOSトランジスタMN1のON抵抗を無視すると、次の(4)式により制限される(抵抗素子Rpdの抵抗値をRpdとする)。

【0084】

Ishort=(FET_PAD電圧値)/Rpd ・・・(4)

【0085】

従って、FETゲート電圧出力端子FET_PADが電源電圧VDDに短絡した場合の最大短絡電流Ishort_maxは、Ishort_max=VDD/Rpdに制限される。

【0086】

この後、FETゲート電圧出力端子FET_PADを電源電圧VDDに短絡した要因が上述のようにして除去され、FETゲート電圧出力端子FET_PADが開放されると、FETゲート電圧出力端子FET_PADはプルダウン状態であるため、電圧値が下降する。電圧値が短絡検出電圧以下となると、NMOSトランジスタMN3はOFFする。これにより、ノードV2、V3は「H」レベルとなり、NAND回路nand1の出力が「L」レベルになり、制御信号ngは「H」レベルとなるため、NMOSトランジスタMN0がONする。一方、ノードV3及び制御信号ngが「H」レベルとなるため、NOR回路nor1の出力が「L」レベルになり、NMOSトランジスタMN1がOFFされる。NMOSトランジスタMN1がOFFすることにより、FETゲート電圧出力端子FET_PADのプルダウン状態が解除され、短絡検出前の状態(通常状態)に復帰する。

【0087】

本実施の形態の短絡保護回路70において、NMOSトランジスタMN2は、短絡検出電圧を電源電圧VDDにより調整する機能を有している。電源電圧VDDが低くなるにつれ、NMOSトランジスタMN0のON抵抗が大きくなり無視できなくなると、短絡検出電圧も大きくなるため、短絡状態でない場合であっても、NMOSトランジスタMN0をONする際に外部FET1のゲート駆動電流が流れることで、瞬間的に短絡検出電圧以上となり、短絡保護回路70による短絡保護機能(上述の動作)が動作してしまう可能性がある。

【0088】

もし、NMOSトランジスタMN2を設けない場合、外部FET1をOFFする際に、外部FET1のゲート端子の電荷を放電するため(OFFするため)の電流が瞬間的に流れる。電源電圧VDDが低い状態で、外部FET1をOFFすると、NMOSトランジスタMN0のON抵抗は、電源電圧VDDが高い場合に比べて大きくなるため、このゲート端子の電荷を放電するための電流により、短絡状態ではないにもかかわらず、短絡を検出してしまう可能性が生じる。NMOSトランジスタMN2を設けない場合は、上述の式(3)において、RON_MN2×Ibiass=0となり、R1+RON_MN0は電源で圧VDDが低い場合では大きくなるため、より小さい電流で短絡検出をすることになる。

【0089】

従って、第1の実施の形態と同様に、短絡保護が誤って動作してしまう場合、このゲート端子の電荷を放電する電流を短絡電流と判断してしまうため、短絡保護機能により電荷を放電する電流が制限されてしまい、外部FET1をONからOFFにする場合の動作速度が遅くなるという、問題が生じてしまう。

【0090】

本実施の形態のFET駆動回路60の短絡保護回路70では、NMOSトランジスタMN2を設けることにより、NMOSトランジスタMN2のON抵抗も電源電圧VDDが低くなるにつれ大きくなるため、短絡検出電圧が高くなり、従って、FETゲート電圧出力端子FET_PADの電圧値が短絡検出電圧を上回るのを防止することができる。すなわち、NMOSトランジスタMN2のトランジスタサイズ(ON抵抗値)を適切に選定することにより、上述の問題を回避することができる。

【0091】

以上説明したように、本実施の形態の電池監視システム50では、電池12の充電・放電を制御するNMOSトランジスタである外部FET1と、短絡保護回路70を有するFET駆動回路60を内蔵する電池監視IC54と、を備える。外部FET1がOFF状態の場合において、FETゲート電圧出力端子FET_PADの電圧が、何らかの要因により短絡し、短絡検出電圧以上となり、VTH_MN3>RON_MN2×Ibiass−(R1+RON_MN0)Ishortを満たすと、NMOSトランジスタMN3がONする。すなわち、短絡電流Ishortが生じることにより、NMOSトランジスタMN3がONする。また、NMOSトランジスタMN0がOFFとなり、さらにNMOSトランジスタMN1がONされる。NMOSトランジスタMN1がONされることにより、FETゲート電圧出力端子FET_PADは、抵抗素子Rpdを介して、プルダウンされた状態となり、電源電圧VDDに短絡した場合の最大短絡電流Ishort_maxは、Ishort_max=VDD/Rpdに制限される。

【0092】

すなわち、短絡状態の場合は、短絡保護回路70のNMOSトランジスタMN3により、GND端子とFETゲート電圧出力端子FET_PAD(外部FET1)との間で電流が流れる経路をNMOSトランジスタMN0及び短絡電流検出用抵抗素子R1を経由する経路から、NMOSトランジスタMN1及び抵抗素子Rpdを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC54が破壊されるのを防止することができる。

【0093】

また、本実施の形態では、短絡発生後にその要因が除去された場合、FETゲート電圧出力端子FET_PADがプルダウン状態であるため、電圧値が短絡検出電圧以下となると、NMOSトランジスタMN3がOFFし、NMOSトランジスタMN0がONする。また、NMOSトランジスタMN1がOFFする。これにより、FETゲート電圧出力端子FET_PADのプルダウン状態が解除され、短絡検出前の状態(通常状態)に復帰する。従って、電池監視IC54をそのまま継続して使用することができる。

【0094】

なお、上述の第1の実施の形態及び第2の実施の形態では、多セル接続された電池12の電池監視IC(電池監視IC14、54)に内蔵されるFET駆動回路(FET駆動回路20、60)を想定し、外部FET(外部FET0、1)をONする際の出力電圧としてクランプ電圧源(クランプ電圧源24、64)から出力されたクランプ電圧(VCLAMP−、VCLAMP+)を用いる構成について説明したがこれに限らず、例えば、クランプ電圧源を仕様せず電源電圧VDD−GNDを駆動電源とするFET駆動回路を用いるように構成してもよい。なお、この場合において、FETゲート電圧出力端子に電源電圧VDD短絡、GND短絡の両方の保護を設ける必要がある場合には、第1の実施の形態及び第2の実施の形態を併用して適用するようにすればよい。

【0095】

また、上述の第1の実施の形態及び第2の実施の形態では、FETゲート電圧出力端子FET_PADが短絡したか否かを検出する場合について詳細に説明したがFETゲート電圧出力端子FET_PADに限らず、第1の実施の形態では、MOSトランジスタMP0と外部FET0とを接続する配線、また、第2の実施の形態では、MOSトランジスタMN0と外部FET1とを接続する配線が短絡したか否かについても、それぞれ第1の実施の形態及び第2の実施の形態と同様に検出することができる。

【0096】

また、上述の第1の実施の形態及び第2の実施の形態では、外部FET(外部FET0、1)に対する短絡保護回路(短絡保護回路30、70)を有するFET駆動回路(FET駆動回路20、60)について詳細に説明したが外部FET駆動用の回路に限らない。例えば、FET以外の部品駆動用回路に同様な駆動回路を用いる場合には、当該駆動回路に上述の保護回路を適用して、短絡から保護するように構成してもよい。

【0097】

また、上述の第1の実施の形態及び第2の実施の形態では、FETゲート電圧出力端子FET_PADが短絡した場合の短絡保護回路(短絡保護回路30、70)を有するFET駆動回路(FET駆動回路20、60)について詳細に説明したがこれに限らない。例えば、過電流保護機能(過電流保護回路)つき負荷駆動回路として用いるものであってもよい。当該過電流保護回路の場合、例えば、第1の実施の形態のように構成される場合は、検出電圧をPMOSトランジスタMP0、MP2、MP3、短絡電流検出用抵抗素子R0により特定の検出電圧に設定できる(上述の(1)式参照)ため、万一、想定よりも過大な電流を駆動するような負荷が負荷駆動回路(当該負荷駆動回路を内蔵するIC)に接続された場合に上述と同様な動作により過大電流を制限することによりICを保護することができる。

【0098】

また、上述の第1の実施の形態及び第2の実施の形態では、電池12を制御するスイッチング素子として、PMOSトランジスタ(外部FET0)、NMOSトランジスタ(外部FET1)を外部に設けるように構成しているが、これに限らず、電池監視IC(電池監視IC14、54)に内蔵するようにしてもよい。なお、本実施の形態のように電池保護ICの場合では、電池12の充電電流/負荷電流を制御するには大電流を流してON/OFFすることとなるため、この大電流を制御するスイッチング素子(FET)を電池監視ICに内蔵しようとすると電池監視ICのサイズが非常に大きくなるため、実装的な観点からあまり好ましくない。また、また発熱の観点からも他回路と同一のパッケージに収めるのは好ましくない。従って、上述の第1の実施の形態及び第2の実施の形態のように、外部FETとすることが好ましい。なお、このように外部に設けることにより内蔵する場合に比べて、FETゲート電圧出力端子FET_PADと外部FETとの間の伝送路(FETゲート電圧出力端子FET_PAD)が短絡しやすくなるため、上述の第1の実施の形態及び第2の実施の形態のように短絡保護回路(短絡保護回路30、70)を設けることにより、短絡から保護する効果がより高くなる。

【0099】

また、上述の第1の実施の形態及び第2の実施の形態では、短絡検出電圧を調整する機能を有する手段として、PMOSトランジスタMP2、NMOSトランジスタMN2を設けるように構成しているが、短絡検出電圧を調整する機能を有する手段の構成はこれに限らない。本実施の形態では、抵抗値により短絡検出電圧を調整するため、その他の抵抗素子であってもよい。なお、例えば、第1の実施の形態の場合、短絡検出電圧が短絡電流検出用抵抗素子R0の抵抗値とPMOSトランジスタMP0のON抵抗で決まり、PMOSトランジスタMP0のON抵抗は、温度と電源電圧VDDによりその値が変化するため、PMOSトランジスタMP0と温度、電源電圧VDDに対するON抵抗の変化が同様であるPMOSトランジスタを使用したほうが、温度、電源電圧VDDの変化による短絡検出電圧値の影響を抑制することができる。一方、抵抗素子を用いた場合、当該抵抗素子の抵抗値自体は電源電圧VDDの変化の影響を受けず、またPMOSトランジスタMP0と異なる温度特性を持っているため、温度条件や電源電圧VDDの変化に対し、短絡検出電圧値が影響を受けやすくなるため、上述の第1の実施の形態及び第2の実施の形態のようにMOSトランジスタ(PMOSトランジスタMP2、NMOSトランジスタMN2)とすることが好ましい。

【符号の説明】

【0100】

10、50 電池監視システム

12 電池

14、54 電池監視IC

24、64 クランプ電圧源

30、70 短絡保護回路

VDD 電源電圧

FET0、FET1 外部FET

【特許請求の範囲】

【請求項1】

第1スイッチ手段をオフするための電圧を供給するオフ電源と、前記第1スイッチ手段と、を電気的に接続する第1伝送路と、

前記第1伝送路上に設けられた第2スイッチ手段と、

前記オフ電源と前記第2スイッチ手段との間の前記第1伝送路と、前記第1スイッチ手段と、を電気的に接続し、かつ前記第1伝送路よりも抵抗値が高い第2伝送路と、

前記第2伝送路上に設けられた第3スイッチ手段と、

前記第1伝送路に接続され、前記第2スイッチ手段と前記第1スイッチ手段との間の前記第1伝送路に流れる電流に応じた電圧を検知し、かつ、検知した前記電圧と閾値とに応じて前記第2スイッチ手段をオフにすると共に、前記第3スイッチ手段をオンにする電圧検知手段と、

前記電圧検知手段と前記第1伝送路との間に設けられ、前記オフ電源の電圧値の変動に応じて前記電圧値が変動しないように前記電圧値を調整する調整手段と、

を備えた半導体回路。

【請求項2】

前記第1スイッチ手段と、前記第2スイッチ手段との間の前記第1伝送路上に設けられ、前記第1伝送路に流れる電流の電流値を検知する電流検知手段を備えた、請求項1に記載の半導体回路。

【請求項3】

前記第2スイッチ手段及び前記調整手段は、MOSトランジスタである、請求項1または請求項2に記載の半導体回路。

【請求項4】

前記第2伝送路は、前記オフ電源と前記第2スイッチ手段との間の前記第1伝送路と、前記第2スイッチ手段と前記第1スイッチ手段との間の前記第1伝送路と、を電気的に接続する、請求項1から請求項3のいずれか1項に記載の半導体回路。

【請求項5】

前記第1スイッチ手段をオンするための電圧を供給するオン電源と、前記第1スイッチ手段と、を電気的に接続する第3伝送路と、

前記第3伝送路上に設けられた第4スイッチ手段と、

を備えた、請求項1から請求項4のいずれか1項に記載の半導体回路。

【請求項6】

第1スイッチ手段と、

前記第1スイッチ手段をオフするための電圧を供給するオフ電源と前記第1スイッチ手段とを電気的に接続するための請求項1から請求項5のいずれか1項に記載の半導体回路と、

を備えた半導体装置。

【請求項7】

電池と、

前記電池の高電位側に接続され、かつ前記電池の充電、放電を制御する第1スイッチ手段と、

前記第1スイッチ手段をオフするための電圧を供給するオフ電源と前記第1スイッチ手段とを電気的に接続するための請求項1から請求項5のいずれか1項に記載の半導体回路と、

を備えた電池監視システム。

【請求項1】

第1スイッチ手段をオフするための電圧を供給するオフ電源と、前記第1スイッチ手段と、を電気的に接続する第1伝送路と、

前記第1伝送路上に設けられた第2スイッチ手段と、

前記オフ電源と前記第2スイッチ手段との間の前記第1伝送路と、前記第1スイッチ手段と、を電気的に接続し、かつ前記第1伝送路よりも抵抗値が高い第2伝送路と、

前記第2伝送路上に設けられた第3スイッチ手段と、

前記第1伝送路に接続され、前記第2スイッチ手段と前記第1スイッチ手段との間の前記第1伝送路に流れる電流に応じた電圧を検知し、かつ、検知した前記電圧と閾値とに応じて前記第2スイッチ手段をオフにすると共に、前記第3スイッチ手段をオンにする電圧検知手段と、

前記電圧検知手段と前記第1伝送路との間に設けられ、前記オフ電源の電圧値の変動に応じて前記電圧値が変動しないように前記電圧値を調整する調整手段と、

を備えた半導体回路。

【請求項2】

前記第1スイッチ手段と、前記第2スイッチ手段との間の前記第1伝送路上に設けられ、前記第1伝送路に流れる電流の電流値を検知する電流検知手段を備えた、請求項1に記載の半導体回路。

【請求項3】

前記第2スイッチ手段及び前記調整手段は、MOSトランジスタである、請求項1または請求項2に記載の半導体回路。

【請求項4】

前記第2伝送路は、前記オフ電源と前記第2スイッチ手段との間の前記第1伝送路と、前記第2スイッチ手段と前記第1スイッチ手段との間の前記第1伝送路と、を電気的に接続する、請求項1から請求項3のいずれか1項に記載の半導体回路。

【請求項5】

前記第1スイッチ手段をオンするための電圧を供給するオン電源と、前記第1スイッチ手段と、を電気的に接続する第3伝送路と、

前記第3伝送路上に設けられた第4スイッチ手段と、

を備えた、請求項1から請求項4のいずれか1項に記載の半導体回路。

【請求項6】

第1スイッチ手段と、

前記第1スイッチ手段をオフするための電圧を供給するオフ電源と前記第1スイッチ手段とを電気的に接続するための請求項1から請求項5のいずれか1項に記載の半導体回路と、

を備えた半導体装置。

【請求項7】

電池と、

前記電池の高電位側に接続され、かつ前記電池の充電、放電を制御する第1スイッチ手段と、

前記第1スイッチ手段をオフするための電圧を供給するオフ電源と前記第1スイッチ手段とを電気的に接続するための請求項1から請求項5のいずれか1項に記載の半導体回路と、

を備えた電池監視システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2012−161184(P2012−161184A)

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願番号】特願2011−19759(P2011−19759)

【出願日】平成23年2月1日(2011.2.1)

【出願人】(308033711)ラピスセミコンダクタ株式会社 (898)

【Fターム(参考)】

【公開日】平成24年8月23日(2012.8.23)

【国際特許分類】

【出願日】平成23年2月1日(2011.2.1)

【出願人】(308033711)ラピスセミコンダクタ株式会社 (898)

【Fターム(参考)】

[ Back to top ]