半導体回路の電流測定装置

【課題】高密度化されている半導体の電流測定対象の配線を切断・変更する必要がなく、回路パラメータに影響を与えずに電流を測定できる電流測定装置を提供する。

【解決手段】測定電流から生じる磁束を検出する磁束検出装置と、磁束検出装置の出力電圧を電流波形に変換する積分装置と、電流波形を視覚化する電流波形観測装置とを有し、磁束検出装置10は、ベース基板の両面に導電パターンにより形成した一対の表裏対称な形状をした第1コイルC1と、測定配線を配置する位置に対して第1コイルC1と線対称に第2コイルC2を配置し、第1コイルC1および第2コイルC2のそれぞれの表の巻き終わりの導電パターンと裏の巻き始めの導電パターンの端部間、および第1コイルC1の巻き終わりの導電パターンの端部と第2コイルC2の巻き始めの導電パターンの端部間とを、それぞれベース基板を貫通するスルーホールにより接続した構造とした電流測定装置。

【解決手段】測定電流から生じる磁束を検出する磁束検出装置と、磁束検出装置の出力電圧を電流波形に変換する積分装置と、電流波形を視覚化する電流波形観測装置とを有し、磁束検出装置10は、ベース基板の両面に導電パターンにより形成した一対の表裏対称な形状をした第1コイルC1と、測定配線を配置する位置に対して第1コイルC1と線対称に第2コイルC2を配置し、第1コイルC1および第2コイルC2のそれぞれの表の巻き終わりの導電パターンと裏の巻き始めの導電パターンの端部間、および第1コイルC1の巻き終わりの導電パターンの端部と第2コイルC2の巻き始めの導電パターンの端部間とを、それぞれベース基板を貫通するスルーホールにより接続した構造とした電流測定装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、小型化・高密度化される半導体回路の電流測定に関するものであり、特に測定回路のパラメータへ影響を与えずに電流を測定できることを特徴とする電流測定装置に関する。

【背景技術】

【0002】

従来の電流測定装置としては、CT(Current Transformer)、センス抵抗、ホール素子、ロゴスキーコイルがある(非特許文献1)。これらの電流測定装置の模式図を図1に示す。

【0003】

図1(a)に示すCTは、成層鉄心にコイルを巻いたものである。プローブの中心に測定電流が流れる配線を挿入して使用するものである(その他の文献として、例えば、特許文献1)。このため、配線長が長くなり、回路の寄生インダクタンスが増加する。また、CTはコアに磁性材料を使用しており、大電流での磁気飽和防止のため、形状が大きくなる。加えて、外部磁界の影響を受けやすい。

【0004】

図1(b)に示すセンス抵抗は、測定電流が流れている箇所に抵抗を挿入し、抵抗両端の電圧から電流を測定する方法である。この方法では直流・交流電流ともに測定可能である。しかし、回路に抵抗を挿入するため、特に大電流の測定を行う場合、損失が発生し、効率が悪化する。また、ノイズの影響を受けやすく、高周波での測定においては、寄生インダクタンスの小さい抵抗を使用する必要がある。

【0005】

図1(c)に示すホール素子は、磁界中に挿入することにより、バイアス電流に対して直交する方向に磁界の強さに比例した電圧が発生するというホール効果を利用したもので、直流・交流電流ともに測定可能である(その他の文献として、例えば、特許文献2)。しかし、周波数帯域が狭く高周波での測定には適していない。また、温度特性も悪い。

【0006】

図1(d)に示すロゴスキーコイルは、円形の巻型に線材を巻いたものである(その他の文献として、例えば、特許文献3)。ロゴスキーコイルは測定電流を取り囲むように配置して使用する。コイルに誘起される電圧は測定電流の時間微分に比例し、この電圧を積分することで電流が測定できる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平06−213937号公報

【特許文献2】特開平05−273257号公報

【特許文献3】実登第2506548号公報

【非特許文献】

【0008】

【非特許文献1】W. F. Ray and C. R. Hewson, “High Performance Rogowski Current Transducers”, Conference Record of the 2000 IEEE, pp.3083-3090 vol.5, 2000, Fig.2

【発明の概要】

【発明が解決しようとする課題】

【0009】

半導体回路は、性能の向上に伴い小型化され回路素子が基板上に高密度に実装されている。そのため、回路の電流を測定する際、電流プローブの挿入が困難であり、従来の電流プローブでは回路配線の切断・変更なしに電流測定を行うことは不可能である。したがって、電流を測定する際に配線長が長くなり寄生インダクタンスが増加するため本来の正しい電流測定を行うことができない。

【0010】

本発明は上記事情を考慮してなされたもので、高密度化されている半導体の電流測定対象の配線を切断・変更する必要がなく、回路パラメータに影響を与えずに電流を測定できる電流測定装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

前記課題を解決するために、本発明の第1の構成は、測定電流から生じる磁束を検出する磁束検出装置と、前記磁束検出装置の出力電圧を電流波形に変換する積分装置と、前記積分装置によって変換された電流波形を視覚化する電流波形観測装置とを有し、前記磁束検出装置は、回路基板の両面に導電パターンにより形成した一対の表裏対称な形状をした第1コイルと、かつ測定配線を配置する位置に対して前記第1コイルと線対称に第2コイルを配置し、前記第1コイルおよび前記第2コイルのそれぞれの表の巻き終わりの導電パターンと裏の巻き始めの導電パターンの端部間、および前記第1コイルの巻き終わりの導電パターンの端部と前記第2コイルの巻き始めの導電パターンの端部間とを、それぞれ前記回路基板を貫通するスルーホールにより接続した構造とした電流測定装置である。

【0012】

本発明の第1の構成では、磁束検出装置において対称な形状をしたコイルを有しており、測定配線の位置に対して上下対称にコイルを配置した構造とすることにより、測定配線に対して上下対称に配置されたコイルが測定配線の周囲の磁束を検出するため、電流測定の際に回路の配線を切断・変更することなく測定対象に近付けることにより電流を測定できる。

【0013】

本発明の第2の構成は、第1の構成において、前記第1コイルの巻き終わりの導電パターンの端部と前記第2コイルの巻き始めの導電パターンの端部間とを前記回路基板の裏表間で接続しているスルーホールを、前記第1コイルおよび前記第2コイルの形成領域より外側の位置に配置した構造を有するものである。

この構造により、コイル間の近接距離の調節幅の自由度を確保し、また、コイルを接続している配線により形成されるループによるインダクタンスの影響を最小限に抑えることができる。

【0014】

本発明の第3の構成は、前記電流波形観測装置において、測定した電流波形にドループが発生していた場合に測定波形のディジタルデータを用いて、測定波形データからオフセット電圧の値を減算することによるオフセット除去処理、オフセット除去処理後の測定波形データの時間積分及び積分回路のフィードバックCR時定数による除算を行う積分処理、オフセット除去処理後の測定データに積分処理後の測定データを加える加算処理、加算処理後の測定波形データを電流波形の大きさと一致させるために定数倍する定数倍処理を経てドループ補償を行う手段を設けたものである。電流波形のディジタルデータを用いてドループ補償を行う手段を有していることにより、本発明の電流測定装置の課題であるドループの問題を解決することができる。

【発明の効果】

【0015】

本発明によれば、高密度化されている半導体の電流測定対象の配線を切断・変更する必要がなく、回路パラメータに影響を与えずに電流を測定できる電流測定装置が得られる。

【図面の簡単な説明】

【0016】

【図1】従来の電流測定装置の種類と模式図である。

【図2】本発明の電流測定装置の構成を示す概略図である。

【図3】本発明の実施の形態に係る磁束検出装置の構成を示す分解斜視図である。

【図4】本発明の実施の形態に係る磁束検出装置のベース基板を示す表面図および裏面図である。

【図5】本発明の実施の形態に係る磁束検出コイルC1の表面図および裏面図である。

【図6】本発明の実施の形態に係る磁束検出コイルC1およびC2の表面図および裏面図である。

【図7】本発明の実施の形態に係る磁束検出コイルのスルーホールの位置を示す表面図である。

【図8】本発明の実施の形態において電流を測定する際の磁束検出コイルと測定電流の位置関係を示す説明図である。

【図9】本発明の実施の形態に係る磁束検出装置のカバーレイの表面図および裏面図である。

【図10】本発明の実施の形態に係る不完全積分回路の構成を示す回路図である。

【図11】本発明の磁束検出装置を用いてパワー回路に流れる電流を測定する実験の説明図である。

【図12】図11の実験結果を示すグラフである。

【図13】図12の測定波形の立下り部分の時間軸を拡大したグラフである。

【図14】本発明の実施の形態に係る磁束検出装置を測定ワイヤーから水平方向および垂直方向に移動させた場合の模式図である。

【図15】本発明の実施の形態に係る磁束検出装置を測定ワイヤーから水平方向(y軸方向)に移動させた場合の出力の変化を示すグラフである。

【図16】本発明の実施の形態に係る磁束検出装置を測定ワイヤーから垂直方向(z軸方向)に移動させた場合の出力の変化を示すグラフである。

【図17】本発明の実施の形態に係る磁束検出装置を用いて半導体チップのボンディングワイヤに流れる電流を測定している状態の斜視図である。

【図18】本発明の実施の形態に係る8チャンネルの磁束検出装置を用いて複数の半導体チップのボンディングワイヤに流れる電流を測定している状態の斜視図である。

【図19】パルスジェネレータからパルス幅10μsのパルスを入力してIGBTを動かしたときに積分回路から得られた出力波形図(1〜8ch)である。

【図20】本発明の実施の形態に係るディジタルドループ補償の方法を示すブロックク図である。

【図21】積分回路の出力電圧のディジタルデータを用いてドループ補正を行なった後の電流波形図(1〜8ch)である。

【図22】従来のCTプローブと本発明の電流プローブ1〜8chの電流波形の和を示す図である。

【図23】8chの磁束検出装置によりIGBTモジュール内のボンディングワイヤに流れる電流を測定するための実験回路図である。

【図24】図23の実験回路におけるゲートの電圧波形とCTの電流波形図である。

【図25】デジタイザーの波形図である。

【図26】LabVIEWでドループ補正した波形図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施形態について図面を参照しつつ詳細に説明する。図2に本発明による電流測定装置の概略を示す。図2に示すように、この電流測定装置は、磁束検出装置10、積分装置20、電流波形観測装置30により構成されている。

【0018】

磁束検出装置10の構成を図3に示す。磁束検出装置10は、プリント基板作製技術を用いて作製される。磁束検出装置10は、配線が施されているベース基板1と、絶縁のためのカバーレイ2,3から構成されている。本発明の実施形態の一例として、導電パターン幅70μm以下、導電パターン間隔90μm以下、導電パターン厚35μm以上、基板厚75μm以下(ベース基板1の厚み25μm以下、カバーレイ2,3の厚み各25μm以下)の3層フレキシブル基板で作製する場合について説明する。フレキシブル基板を用いることにより、基板を曲げることや不要な部分を切断して使用することができるため柔軟性に富んだ使い方ができる。基板の厚さを薄くすると、測定スペースが狭い場合にも有効である。また、プリント基板作製技術を用いることにより量産性の向上とコスト低減が期待できる。導電パターンについては幅70μm以下、間隔90μm以下としたことにより、後述する基本コイルの小型化に貢献している。また、導電パターンの厚さを35μm以上にすることで断線を防いでいる。

【0019】

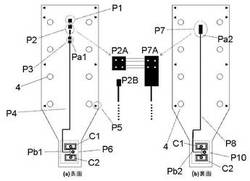

ベース基板1について説明する。ベース基板1の詳細を図4に示す。図4(a)は表面、図4(b)は裏面を示すが、裏面は表面から見た鏡像を示している。ベース基板1には、同軸ケーブル固定用パターンP1、同軸ケーブル接続用パターンP2、積分回路のCR時定数調整抵抗用パターンP3、磁束検出コイルパターンP6,P10、16個の基板位置合わせ用パターンP5、8個の基板固定用ネジ穴4が施されている。

【0020】

同軸ケーブル接続用パターンP2は、同軸ケーブルの信号線用パターンP2Bとグランド線用パターンP2Aがある。グランド線用パターンP2Aは、スルーホールにより裏面のパターンP7Aと接続されている。CR時定数調整抵抗用パターンP3は、積分回路のCR時定数調整用抵抗(図示せず)を搭載するためにある。配線P4とP8(Pa1〜Pb1の間の配線、Pa2〜Pb2の間の配線)はコイルのパターン幅より太い150μm以上のパターンで配線する。これによりフレキシブル基板を曲げた場合に導電パターンが断線することを防ぐことができる。同軸ケーブル固定用パターンP1は、同軸ケーブル接続用パターンP2に負荷が集中して同軸ケーブルが外れることや導電パターンが剥がれるのを防ぐために、接着剤などで同軸ケーブルを基板に固定するためのものである。基板位置合わせ用パターンP5は、複数の磁束検出装置を使用する際、互いの基板の位置を合わせるための目印である。基板固定用ネジ穴4は電流測定の際に磁束検出装置10を固定するために設けてある。

【0021】

磁束検出コイルC1,C2について説明する。磁束検出コイルC1,C2は、基板表裏の対称な形状をした2個のコイルにより構成されている。図5(a),(b)に示すように、磁束検出コイルC1の表面と裏面のコイルは、コイルの中心にあるスルーホールP11A、P11Bにより電気的に接続されている。スルーホールP11A、P11Bの大きさは、ランド径が550μm以下、ビア径が300μm以下である。スルーホールP11A、P11Bの大きさを小型化することによりコイルと鎖交する磁束数が増えるため、コイルの出力電圧増加の点で有効である。また、表面と裏面のコイルは中心線に対して左右対称である。コイルの形状を対称にすることにより表面と裏面のコイルの出力を等しくできる。また、設計をする際の能率の点でも有効である。

【0022】

磁束検出コイルC1,C2は、図6に示すように上下2個のコイルパターンP13A,P13BとP14A,P14Bからなっており、表裏合わせて計4個のコイルパターンで構成されている。コイルパターンP13AとP14A、P13BとP14Bはそれぞれ中心線L1a−L1bに対し線対称である。各コイルパターンを対称な形状とし図6のように接続することにより、並行磁束が磁束検出コイルC1,C2と鎖交した場合、上下のコイルC1,C2の出力電圧は大きさが等しく互いに打ち消すように発生するため、外部磁界の影響を受けにくい構造となっている。また、図6のように上下のコイルパターンを接続しているスルーホールP12A−P12Bをセンター(中心線L2a−L2b)からずらして配置し、A、B部分のパターンの近接距離を最小にすることにより、A、B部分のパターンによって形成されるループによるインダクタンスの影響を最小限にしている。

【0023】

また、図7のようにスルーホールP12A−P12Bの位置をコイルの外側に配置した場合、上下の磁束検出コイルC1,C2の近接距離をより短くすることができるため、上下の磁束検出コイルC1,C2の近接距離を調整できる幅が広がる。上下の磁束検出コイルC1,C2の近接距離は磁束検出コイルの出力特性に関係しているため、上下の磁束検出コイルC1,C2の近接距離の調整幅が広がることにより磁束検出コイルC1,C2の出力特性を調整できる幅が広がる利点がある。

【0024】

電流を測定する際の磁束検出コイルC1,C2と測定電流の位置関係を図8に示す。図8に示すように磁束検出装置10は、磁束検出コイルC1,C2を測定対象配線Wに近接させ、なおかつ測定電流が流れる配線Wが上下の磁束検出コイルC1,C2の間に来るように配置して使用する。磁束が図8(b)のように磁束検出コイルC1,C2と鎖交した場合に上下の磁束検出コイルC1,C2の出力電圧は加算されるように接続されている。コイルを小型化するとコイルの出力電圧は小さくなるため、この構造は出力電圧を増加させる点でも有効である。

【0025】

カバーレイ2の詳細を図9に示す。カバーレイ2,3は、基板強度増加と磁束検出コイルパターンP6,P10や配線パターンの絶縁のためのものである。カバーレイ2,3はベース基板1の両面に施されており、表面のカバーレイ2には抵抗および同軸ケーブルをはんだ付けすることができるように窓5が開けられている。

【0026】

以上では磁束検出装置10を、2層フレキシブル基板を3枚積層して作製する場合について述べたが、2層フレキシブル基板以外にも2層以上の多層プリント基板やSiウェハ(半導体プロセス技術を利用)を用いて作製することも考えられる。多層プリント基板を用いることによりコイルの個数を増加させることができるため磁束検出コイルの出力電圧増加の点で有効である。また、Siウェハを用いることにより微細加工が可能になるため超小型のコイルを作製することができ、より小型の磁束検出装置を作製することが可能になる。

【0027】

積分装置20は、磁束検出コイルC1,C2の出力電圧を電流波形に変換するために必要である。一般的にはオペアンプを用いた不完全積分回路を用いる。図10にオペアンプOP1を用いた不完全積分回路の回路図を示す。入力Vinには磁束検出装置10からの出力信号が同軸ケーブルを通して入力される。出力Voutからは積分回路の出力信号が出力され、同軸ケーブルを通って電流波形観測装置30に入力される。入力部の抵抗R1と出力部の抵抗R2を50Ωに設定することで同軸ケーブルとインピーダンスマッチングをとり、信号の反射を防いでいる。フィードバック部分の抵抗Rfは積分回路の出力が飽和するのを防ぐために入れている。積分回路の出力信号の大きさは1/R1Cfに比例するため、Cfの値はなるべく小さくした方が出力信号の大きさの点では有利である。また、フィードバック部分の抵抗RfとコンデンサCfの積CfRfの値を大きくした方がフィードバック部分のRC回路の時定数が大きくなるためドループが起こりにくくなる点で有利である。CfとRfの値は使用する磁束検出装置10の磁束検出コイルC1、C2の大きさに応じて最適な値を決定する。ディジタルドループ補償システム31でドループ補償を行う際にCfRfの値を使用するため、フィードバック部分の抵抗RfとコンデンサCfには精度の高いものを使用し、フィードバック部分の配線の寄生キャパシタンスは小さくした方がドループ補償の点で有効である。特に複数個の磁束検出装置10を用いて多チャンネルで電流を測定する場合には、フィードバックのCR時定数の精度が揃っていることが精度のよい測定をする点で重要である。また、積分回路21から出力される波形を実際の測定電流波形と対応させるために図4のCR時定数調整用抵抗用パターンP3に搭載されるCR時定数調整用抵抗(図示せず)を用いて調整する。

【0028】

電流波形観測装置30は、積分装置20により得られた電流波形を視覚化するためのものであり、一般的にはオシロスコープやデジタイザを用いる。

【0029】

本発明の電流測定装置により、図11のパワー回路40に流れる電流を測定する実験を行った。パワー回路40は、ゲートドライブ回路41、パワー半導体42、抵抗43、コンデンサ44、直流電源45よりなっており、パワー半導体42を流れる電流を測定するために、配線Wに磁束検出装置10とCTプローブ51を取り付けた。磁束検出コイルC1,C2のコイル1個の大きさは1.5mm角、巻数は3ターンである。パルスジェネレータから1MHzのパルスを入力しパワー回路40に電流を流した。CTプローブ51と本発明の電流測定装置の磁束検出装置10により回路を流れる電流を測定し、両者の測定結果の比較を行った。その結果を図11に、測定波形の立ち下り部分の拡大図を図13に示す。図12および図13より、本発明の磁束検出装置は従来のCTと同等の性能を持っていることがわかる。

【0030】

次に、本実施の形態の磁束検出装置10と電流測定対象の配線Wとの最適位置を調べるために、図14のように測定配線Wから水平方向(y軸方向)または垂直方向(z軸方向)に移動させた場合の出力電圧特性を測定した。

【0031】

図15に示すように、磁束検出装置10の磁束検出コイルC1とC2の中間位置に配線Wを近接させた状態の出力を1とすると、水平位置が離れるにつれて、出力が急激に低下していることが分かる。

【0032】

また、図16に示すように、磁束検出装置10の磁束検出コイルC1とC2の中間位置に配線Wを近接させた状態の出力を1とすると、垂直位置が離れても1mm程度までは出力は同程度であり、それから徐々に低下して、1.6mmを過ぎたところで出力が一旦0になり、それから出力が負になり、2.4mm位まで絶対値が上昇するが、それを越えると出力の絶対値が低下し、−0.15程度となっていることが分かる。これは、磁束検出コイルC1とC2に対して配線Wが対象位置から外れたことにより、磁束検出C1とC2が別々に配線Wによる磁束を検出していることによる。

【0033】

図17は、本発明の実施の形態に係る磁束検出装置10を用いて半導体チップ61のボンディングワイヤ62に流れる電流を測定している状態の斜視図である。磁束検出装置10はフレキシブル基板で作製され、薄いので、複数のボンディングワイヤ62が密集して配置されている箇所にも、挿入して電流を測定することができる。

【0034】

また、図18は、本発明の実施の形態に係る8チャンネルの磁束検出装置10(1〜8ch)を用いて複数の半導体チップ61のボンディングワイヤ62に流れる電流を測定している状態の斜視図である。上述した磁束検出装置10を8枚、所定の間隔を開けて積層することにより、8本のボンディングワイヤ62に流れる電流を同時に測定することができ、いずれかのチャンネルの電流が不均等に流れていないかどうかをチェックすることができる。

【0035】

ところで、本発明の電流測定装置では、積分装置20に積分回路21を用いた場合に測定波形にドループが発生することが問題である。ドループとは、コイルの出力信号が小さい場合に、特に低周波領域では積分回路の出力波形が減衰してしまい、積分動作が不完全の状態で出力される現象をいう。図19は、パルスジェネレータからパルス幅10μsのパルスを入力して半導体チップ(IGBT)を動かしたときに積分回路21から得られた出力波形図(1〜8ch)であり、ドループが発生していることが分かる。ドループが発生すると、測定されるべき本来の電流波形が得られないという問題が生じる。

【0036】

このドループを解消する手法を図20に示す。図20において、磁束検出コイルの出力電圧は同軸ケーブルを介して積分回路21に入力され積分される。積分回路21の出力波形には、特に低周波の場合、ドループが発生するため測定波形を補償する必要がある。ディジタルドループ補償システム31では、積分回路21からの出力をA/D変換器に入力することによりアナログの測定データをディジタルのデータに変換してドループ波形の補償を行う(S1)。アナログの測定データをディジタルのデータに変換することにより、ドループ補償のデータ処理を行うことが容易になる。次にオフセット電圧の値を検出し測定データからオフセット電圧の値を減算することにより測定データからオフセット電圧を取り去る(S2)。測定データからオフセット電圧を除去することにより、ドループ補償を行なった際に波形が傾くのを補正している。次にオフセット電圧を取り除いたデータを時間積分して1/CR倍する(S3)。ここで、C、Rは積分回路のフィードバックのキャパシタンスと抵抗値である。C=C0+ΔC,R=R0+ΔR(C0とR0はそれぞれキャパシタンスと抵抗値の数値,ΔCとΔRはそれぞれキャパシタンスと抵抗値の誤差を補正するための補正値)としてS3のデータ処理プログラムを組むことにより、磁束検出装置10を複数個用いて電流を測定する場合に、各チャンネルごとに積分回路21のフィードバックのCR定数のばらつきの影響を無くし、全てのチャンネルで精度の揃った測定を行うことができる。さらに、S2とS3で求めたデータを加え(S4)、定数倍する(S5)。これにより、ドループ補償した波形が得られる。S5の定数倍する過程では、ドループ補償波形と測定電流の大きさが1対1に対応するように調整する。ドループが補償されたことは、ディスプレイ32で確認することができる。

【0037】

上記のドループ補償方法を実施する例としては、ディジタル・オシロスコープから得た測定波形のデータをコンピュータに取り入れてEXCEL(登録商標)上でS2〜S5の処理を行う方法やデジタイザーから得た測定波形のデータをLabVIEW(ビジュアルプログラミング言語)上で組んだプログラム(S2〜S5の処理を行うプログラム)によりドループ補償して波形を表示する方法などがある。

【0038】

ドループの補償を、ディジタルデータを用いて行うことにより、アナログの場合に比べてデータの処理が容易になり、波形のひずみやノイズの影響を受けにくくなる利点がある。また、この方法では、コンピュータ内で組んだプログラムによりデータの処理を行うことができるためコストの面でも有効である。デジタイザーにより得た測定波形のデータをLabVIEW上で処理して補償した例を図21に示す。

【0039】

図22は、従来のCTプローブと本発明の電流プローブ1〜8chの電流波形の和を示す図である。この図から、CTプローブと本発明の電流プローブとの電流波形が一致していることが分かる。

【0040】

図24は、図23の実験回路において、半導体チップ(IGBTモジュール)61のゲートにパルス幅50μsのパルスを入力し、コレクタ−エミッタ間に20Vの直流電圧を印加して電流を流し、IGBTモジュールに流れる電流を測定した実験のゲート電圧波形とCTプローブ51の電流波形を示した図である。この図から、IGBTモジュールが動いている間にパワー回路40に流れる電流の様子が分かる。

【0041】

図25は、図23の実験回路において、パワー回路40に電流が流れている際に積分回路21の各チャンネル(1〜8ch)の出力電圧波形を示したものである。この図から、パワー回路40に電流が流れIGBTモジュール内の各ボンディングワイヤ62に電流が流れるのを磁束検出装置(1〜8ch)10が検出し積分回路により電流波形に変換された様子が分かる。ただし、この場合では、積分回路21の波形にはドループが発生しており、本来の電流波形は示されていない。(ここで、図25中のslotとは、デジタイザー33の信号入力部分であり、一つのslotに複数の信号を入力することができる。図23の実験回路では一つのslotに2ch分の信号入力し、4slotを使用して実験を行った。)

【0042】

図26は、LabVIEWでドループ補正した電流波形の図である。この図から、IGBTモジュール内の各ボンディングワイヤに流れている電流の様子が分かる。

【産業上の利用可能性】

【0043】

本発明は、高密度化されている半導体の電流測定対象の配線を切断・変更する必要がなく、回路パラメータに影響を与えずに電流を測定できる電流測定装置として、小型化・高密度化が進んでいるIGBTその他のパワー半導体回路の電流測定に好適に利用することができる。

【符号の説明】

【0044】

1 ベース基板

2,3 カバーレイ

4 基板固定用ネジ穴

10 磁束検出装置

20 積分装置

21 積分回路

30 電流波形観測装置

31 ディジタルドループ補償システム

32 ディスプレイ

33 デジタイザー

40 パワー回路

41 ゲートドライブ回路

42 パワー半導体

43 抵抗

44 コンデンサ

45 直流電源

51 CTプローブ

61 半導体チップ

62 ボンディングワイヤ

P11A,P11B,P12A,P12B スルーホール

C1,C2 磁束検出コイル

W 配線

【技術分野】

【0001】

本発明は、小型化・高密度化される半導体回路の電流測定に関するものであり、特に測定回路のパラメータへ影響を与えずに電流を測定できることを特徴とする電流測定装置に関する。

【背景技術】

【0002】

従来の電流測定装置としては、CT(Current Transformer)、センス抵抗、ホール素子、ロゴスキーコイルがある(非特許文献1)。これらの電流測定装置の模式図を図1に示す。

【0003】

図1(a)に示すCTは、成層鉄心にコイルを巻いたものである。プローブの中心に測定電流が流れる配線を挿入して使用するものである(その他の文献として、例えば、特許文献1)。このため、配線長が長くなり、回路の寄生インダクタンスが増加する。また、CTはコアに磁性材料を使用しており、大電流での磁気飽和防止のため、形状が大きくなる。加えて、外部磁界の影響を受けやすい。

【0004】

図1(b)に示すセンス抵抗は、測定電流が流れている箇所に抵抗を挿入し、抵抗両端の電圧から電流を測定する方法である。この方法では直流・交流電流ともに測定可能である。しかし、回路に抵抗を挿入するため、特に大電流の測定を行う場合、損失が発生し、効率が悪化する。また、ノイズの影響を受けやすく、高周波での測定においては、寄生インダクタンスの小さい抵抗を使用する必要がある。

【0005】

図1(c)に示すホール素子は、磁界中に挿入することにより、バイアス電流に対して直交する方向に磁界の強さに比例した電圧が発生するというホール効果を利用したもので、直流・交流電流ともに測定可能である(その他の文献として、例えば、特許文献2)。しかし、周波数帯域が狭く高周波での測定には適していない。また、温度特性も悪い。

【0006】

図1(d)に示すロゴスキーコイルは、円形の巻型に線材を巻いたものである(その他の文献として、例えば、特許文献3)。ロゴスキーコイルは測定電流を取り囲むように配置して使用する。コイルに誘起される電圧は測定電流の時間微分に比例し、この電圧を積分することで電流が測定できる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平06−213937号公報

【特許文献2】特開平05−273257号公報

【特許文献3】実登第2506548号公報

【非特許文献】

【0008】

【非特許文献1】W. F. Ray and C. R. Hewson, “High Performance Rogowski Current Transducers”, Conference Record of the 2000 IEEE, pp.3083-3090 vol.5, 2000, Fig.2

【発明の概要】

【発明が解決しようとする課題】

【0009】

半導体回路は、性能の向上に伴い小型化され回路素子が基板上に高密度に実装されている。そのため、回路の電流を測定する際、電流プローブの挿入が困難であり、従来の電流プローブでは回路配線の切断・変更なしに電流測定を行うことは不可能である。したがって、電流を測定する際に配線長が長くなり寄生インダクタンスが増加するため本来の正しい電流測定を行うことができない。

【0010】

本発明は上記事情を考慮してなされたもので、高密度化されている半導体の電流測定対象の配線を切断・変更する必要がなく、回路パラメータに影響を与えずに電流を測定できる電流測定装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

前記課題を解決するために、本発明の第1の構成は、測定電流から生じる磁束を検出する磁束検出装置と、前記磁束検出装置の出力電圧を電流波形に変換する積分装置と、前記積分装置によって変換された電流波形を視覚化する電流波形観測装置とを有し、前記磁束検出装置は、回路基板の両面に導電パターンにより形成した一対の表裏対称な形状をした第1コイルと、かつ測定配線を配置する位置に対して前記第1コイルと線対称に第2コイルを配置し、前記第1コイルおよび前記第2コイルのそれぞれの表の巻き終わりの導電パターンと裏の巻き始めの導電パターンの端部間、および前記第1コイルの巻き終わりの導電パターンの端部と前記第2コイルの巻き始めの導電パターンの端部間とを、それぞれ前記回路基板を貫通するスルーホールにより接続した構造とした電流測定装置である。

【0012】

本発明の第1の構成では、磁束検出装置において対称な形状をしたコイルを有しており、測定配線の位置に対して上下対称にコイルを配置した構造とすることにより、測定配線に対して上下対称に配置されたコイルが測定配線の周囲の磁束を検出するため、電流測定の際に回路の配線を切断・変更することなく測定対象に近付けることにより電流を測定できる。

【0013】

本発明の第2の構成は、第1の構成において、前記第1コイルの巻き終わりの導電パターンの端部と前記第2コイルの巻き始めの導電パターンの端部間とを前記回路基板の裏表間で接続しているスルーホールを、前記第1コイルおよび前記第2コイルの形成領域より外側の位置に配置した構造を有するものである。

この構造により、コイル間の近接距離の調節幅の自由度を確保し、また、コイルを接続している配線により形成されるループによるインダクタンスの影響を最小限に抑えることができる。

【0014】

本発明の第3の構成は、前記電流波形観測装置において、測定した電流波形にドループが発生していた場合に測定波形のディジタルデータを用いて、測定波形データからオフセット電圧の値を減算することによるオフセット除去処理、オフセット除去処理後の測定波形データの時間積分及び積分回路のフィードバックCR時定数による除算を行う積分処理、オフセット除去処理後の測定データに積分処理後の測定データを加える加算処理、加算処理後の測定波形データを電流波形の大きさと一致させるために定数倍する定数倍処理を経てドループ補償を行う手段を設けたものである。電流波形のディジタルデータを用いてドループ補償を行う手段を有していることにより、本発明の電流測定装置の課題であるドループの問題を解決することができる。

【発明の効果】

【0015】

本発明によれば、高密度化されている半導体の電流測定対象の配線を切断・変更する必要がなく、回路パラメータに影響を与えずに電流を測定できる電流測定装置が得られる。

【図面の簡単な説明】

【0016】

【図1】従来の電流測定装置の種類と模式図である。

【図2】本発明の電流測定装置の構成を示す概略図である。

【図3】本発明の実施の形態に係る磁束検出装置の構成を示す分解斜視図である。

【図4】本発明の実施の形態に係る磁束検出装置のベース基板を示す表面図および裏面図である。

【図5】本発明の実施の形態に係る磁束検出コイルC1の表面図および裏面図である。

【図6】本発明の実施の形態に係る磁束検出コイルC1およびC2の表面図および裏面図である。

【図7】本発明の実施の形態に係る磁束検出コイルのスルーホールの位置を示す表面図である。

【図8】本発明の実施の形態において電流を測定する際の磁束検出コイルと測定電流の位置関係を示す説明図である。

【図9】本発明の実施の形態に係る磁束検出装置のカバーレイの表面図および裏面図である。

【図10】本発明の実施の形態に係る不完全積分回路の構成を示す回路図である。

【図11】本発明の磁束検出装置を用いてパワー回路に流れる電流を測定する実験の説明図である。

【図12】図11の実験結果を示すグラフである。

【図13】図12の測定波形の立下り部分の時間軸を拡大したグラフである。

【図14】本発明の実施の形態に係る磁束検出装置を測定ワイヤーから水平方向および垂直方向に移動させた場合の模式図である。

【図15】本発明の実施の形態に係る磁束検出装置を測定ワイヤーから水平方向(y軸方向)に移動させた場合の出力の変化を示すグラフである。

【図16】本発明の実施の形態に係る磁束検出装置を測定ワイヤーから垂直方向(z軸方向)に移動させた場合の出力の変化を示すグラフである。

【図17】本発明の実施の形態に係る磁束検出装置を用いて半導体チップのボンディングワイヤに流れる電流を測定している状態の斜視図である。

【図18】本発明の実施の形態に係る8チャンネルの磁束検出装置を用いて複数の半導体チップのボンディングワイヤに流れる電流を測定している状態の斜視図である。

【図19】パルスジェネレータからパルス幅10μsのパルスを入力してIGBTを動かしたときに積分回路から得られた出力波形図(1〜8ch)である。

【図20】本発明の実施の形態に係るディジタルドループ補償の方法を示すブロックク図である。

【図21】積分回路の出力電圧のディジタルデータを用いてドループ補正を行なった後の電流波形図(1〜8ch)である。

【図22】従来のCTプローブと本発明の電流プローブ1〜8chの電流波形の和を示す図である。

【図23】8chの磁束検出装置によりIGBTモジュール内のボンディングワイヤに流れる電流を測定するための実験回路図である。

【図24】図23の実験回路におけるゲートの電圧波形とCTの電流波形図である。

【図25】デジタイザーの波形図である。

【図26】LabVIEWでドループ補正した波形図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施形態について図面を参照しつつ詳細に説明する。図2に本発明による電流測定装置の概略を示す。図2に示すように、この電流測定装置は、磁束検出装置10、積分装置20、電流波形観測装置30により構成されている。

【0018】

磁束検出装置10の構成を図3に示す。磁束検出装置10は、プリント基板作製技術を用いて作製される。磁束検出装置10は、配線が施されているベース基板1と、絶縁のためのカバーレイ2,3から構成されている。本発明の実施形態の一例として、導電パターン幅70μm以下、導電パターン間隔90μm以下、導電パターン厚35μm以上、基板厚75μm以下(ベース基板1の厚み25μm以下、カバーレイ2,3の厚み各25μm以下)の3層フレキシブル基板で作製する場合について説明する。フレキシブル基板を用いることにより、基板を曲げることや不要な部分を切断して使用することができるため柔軟性に富んだ使い方ができる。基板の厚さを薄くすると、測定スペースが狭い場合にも有効である。また、プリント基板作製技術を用いることにより量産性の向上とコスト低減が期待できる。導電パターンについては幅70μm以下、間隔90μm以下としたことにより、後述する基本コイルの小型化に貢献している。また、導電パターンの厚さを35μm以上にすることで断線を防いでいる。

【0019】

ベース基板1について説明する。ベース基板1の詳細を図4に示す。図4(a)は表面、図4(b)は裏面を示すが、裏面は表面から見た鏡像を示している。ベース基板1には、同軸ケーブル固定用パターンP1、同軸ケーブル接続用パターンP2、積分回路のCR時定数調整抵抗用パターンP3、磁束検出コイルパターンP6,P10、16個の基板位置合わせ用パターンP5、8個の基板固定用ネジ穴4が施されている。

【0020】

同軸ケーブル接続用パターンP2は、同軸ケーブルの信号線用パターンP2Bとグランド線用パターンP2Aがある。グランド線用パターンP2Aは、スルーホールにより裏面のパターンP7Aと接続されている。CR時定数調整抵抗用パターンP3は、積分回路のCR時定数調整用抵抗(図示せず)を搭載するためにある。配線P4とP8(Pa1〜Pb1の間の配線、Pa2〜Pb2の間の配線)はコイルのパターン幅より太い150μm以上のパターンで配線する。これによりフレキシブル基板を曲げた場合に導電パターンが断線することを防ぐことができる。同軸ケーブル固定用パターンP1は、同軸ケーブル接続用パターンP2に負荷が集中して同軸ケーブルが外れることや導電パターンが剥がれるのを防ぐために、接着剤などで同軸ケーブルを基板に固定するためのものである。基板位置合わせ用パターンP5は、複数の磁束検出装置を使用する際、互いの基板の位置を合わせるための目印である。基板固定用ネジ穴4は電流測定の際に磁束検出装置10を固定するために設けてある。

【0021】

磁束検出コイルC1,C2について説明する。磁束検出コイルC1,C2は、基板表裏の対称な形状をした2個のコイルにより構成されている。図5(a),(b)に示すように、磁束検出コイルC1の表面と裏面のコイルは、コイルの中心にあるスルーホールP11A、P11Bにより電気的に接続されている。スルーホールP11A、P11Bの大きさは、ランド径が550μm以下、ビア径が300μm以下である。スルーホールP11A、P11Bの大きさを小型化することによりコイルと鎖交する磁束数が増えるため、コイルの出力電圧増加の点で有効である。また、表面と裏面のコイルは中心線に対して左右対称である。コイルの形状を対称にすることにより表面と裏面のコイルの出力を等しくできる。また、設計をする際の能率の点でも有効である。

【0022】

磁束検出コイルC1,C2は、図6に示すように上下2個のコイルパターンP13A,P13BとP14A,P14Bからなっており、表裏合わせて計4個のコイルパターンで構成されている。コイルパターンP13AとP14A、P13BとP14Bはそれぞれ中心線L1a−L1bに対し線対称である。各コイルパターンを対称な形状とし図6のように接続することにより、並行磁束が磁束検出コイルC1,C2と鎖交した場合、上下のコイルC1,C2の出力電圧は大きさが等しく互いに打ち消すように発生するため、外部磁界の影響を受けにくい構造となっている。また、図6のように上下のコイルパターンを接続しているスルーホールP12A−P12Bをセンター(中心線L2a−L2b)からずらして配置し、A、B部分のパターンの近接距離を最小にすることにより、A、B部分のパターンによって形成されるループによるインダクタンスの影響を最小限にしている。

【0023】

また、図7のようにスルーホールP12A−P12Bの位置をコイルの外側に配置した場合、上下の磁束検出コイルC1,C2の近接距離をより短くすることができるため、上下の磁束検出コイルC1,C2の近接距離を調整できる幅が広がる。上下の磁束検出コイルC1,C2の近接距離は磁束検出コイルの出力特性に関係しているため、上下の磁束検出コイルC1,C2の近接距離の調整幅が広がることにより磁束検出コイルC1,C2の出力特性を調整できる幅が広がる利点がある。

【0024】

電流を測定する際の磁束検出コイルC1,C2と測定電流の位置関係を図8に示す。図8に示すように磁束検出装置10は、磁束検出コイルC1,C2を測定対象配線Wに近接させ、なおかつ測定電流が流れる配線Wが上下の磁束検出コイルC1,C2の間に来るように配置して使用する。磁束が図8(b)のように磁束検出コイルC1,C2と鎖交した場合に上下の磁束検出コイルC1,C2の出力電圧は加算されるように接続されている。コイルを小型化するとコイルの出力電圧は小さくなるため、この構造は出力電圧を増加させる点でも有効である。

【0025】

カバーレイ2の詳細を図9に示す。カバーレイ2,3は、基板強度増加と磁束検出コイルパターンP6,P10や配線パターンの絶縁のためのものである。カバーレイ2,3はベース基板1の両面に施されており、表面のカバーレイ2には抵抗および同軸ケーブルをはんだ付けすることができるように窓5が開けられている。

【0026】

以上では磁束検出装置10を、2層フレキシブル基板を3枚積層して作製する場合について述べたが、2層フレキシブル基板以外にも2層以上の多層プリント基板やSiウェハ(半導体プロセス技術を利用)を用いて作製することも考えられる。多層プリント基板を用いることによりコイルの個数を増加させることができるため磁束検出コイルの出力電圧増加の点で有効である。また、Siウェハを用いることにより微細加工が可能になるため超小型のコイルを作製することができ、より小型の磁束検出装置を作製することが可能になる。

【0027】

積分装置20は、磁束検出コイルC1,C2の出力電圧を電流波形に変換するために必要である。一般的にはオペアンプを用いた不完全積分回路を用いる。図10にオペアンプOP1を用いた不完全積分回路の回路図を示す。入力Vinには磁束検出装置10からの出力信号が同軸ケーブルを通して入力される。出力Voutからは積分回路の出力信号が出力され、同軸ケーブルを通って電流波形観測装置30に入力される。入力部の抵抗R1と出力部の抵抗R2を50Ωに設定することで同軸ケーブルとインピーダンスマッチングをとり、信号の反射を防いでいる。フィードバック部分の抵抗Rfは積分回路の出力が飽和するのを防ぐために入れている。積分回路の出力信号の大きさは1/R1Cfに比例するため、Cfの値はなるべく小さくした方が出力信号の大きさの点では有利である。また、フィードバック部分の抵抗RfとコンデンサCfの積CfRfの値を大きくした方がフィードバック部分のRC回路の時定数が大きくなるためドループが起こりにくくなる点で有利である。CfとRfの値は使用する磁束検出装置10の磁束検出コイルC1、C2の大きさに応じて最適な値を決定する。ディジタルドループ補償システム31でドループ補償を行う際にCfRfの値を使用するため、フィードバック部分の抵抗RfとコンデンサCfには精度の高いものを使用し、フィードバック部分の配線の寄生キャパシタンスは小さくした方がドループ補償の点で有効である。特に複数個の磁束検出装置10を用いて多チャンネルで電流を測定する場合には、フィードバックのCR時定数の精度が揃っていることが精度のよい測定をする点で重要である。また、積分回路21から出力される波形を実際の測定電流波形と対応させるために図4のCR時定数調整用抵抗用パターンP3に搭載されるCR時定数調整用抵抗(図示せず)を用いて調整する。

【0028】

電流波形観測装置30は、積分装置20により得られた電流波形を視覚化するためのものであり、一般的にはオシロスコープやデジタイザを用いる。

【0029】

本発明の電流測定装置により、図11のパワー回路40に流れる電流を測定する実験を行った。パワー回路40は、ゲートドライブ回路41、パワー半導体42、抵抗43、コンデンサ44、直流電源45よりなっており、パワー半導体42を流れる電流を測定するために、配線Wに磁束検出装置10とCTプローブ51を取り付けた。磁束検出コイルC1,C2のコイル1個の大きさは1.5mm角、巻数は3ターンである。パルスジェネレータから1MHzのパルスを入力しパワー回路40に電流を流した。CTプローブ51と本発明の電流測定装置の磁束検出装置10により回路を流れる電流を測定し、両者の測定結果の比較を行った。その結果を図11に、測定波形の立ち下り部分の拡大図を図13に示す。図12および図13より、本発明の磁束検出装置は従来のCTと同等の性能を持っていることがわかる。

【0030】

次に、本実施の形態の磁束検出装置10と電流測定対象の配線Wとの最適位置を調べるために、図14のように測定配線Wから水平方向(y軸方向)または垂直方向(z軸方向)に移動させた場合の出力電圧特性を測定した。

【0031】

図15に示すように、磁束検出装置10の磁束検出コイルC1とC2の中間位置に配線Wを近接させた状態の出力を1とすると、水平位置が離れるにつれて、出力が急激に低下していることが分かる。

【0032】

また、図16に示すように、磁束検出装置10の磁束検出コイルC1とC2の中間位置に配線Wを近接させた状態の出力を1とすると、垂直位置が離れても1mm程度までは出力は同程度であり、それから徐々に低下して、1.6mmを過ぎたところで出力が一旦0になり、それから出力が負になり、2.4mm位まで絶対値が上昇するが、それを越えると出力の絶対値が低下し、−0.15程度となっていることが分かる。これは、磁束検出コイルC1とC2に対して配線Wが対象位置から外れたことにより、磁束検出C1とC2が別々に配線Wによる磁束を検出していることによる。

【0033】

図17は、本発明の実施の形態に係る磁束検出装置10を用いて半導体チップ61のボンディングワイヤ62に流れる電流を測定している状態の斜視図である。磁束検出装置10はフレキシブル基板で作製され、薄いので、複数のボンディングワイヤ62が密集して配置されている箇所にも、挿入して電流を測定することができる。

【0034】

また、図18は、本発明の実施の形態に係る8チャンネルの磁束検出装置10(1〜8ch)を用いて複数の半導体チップ61のボンディングワイヤ62に流れる電流を測定している状態の斜視図である。上述した磁束検出装置10を8枚、所定の間隔を開けて積層することにより、8本のボンディングワイヤ62に流れる電流を同時に測定することができ、いずれかのチャンネルの電流が不均等に流れていないかどうかをチェックすることができる。

【0035】

ところで、本発明の電流測定装置では、積分装置20に積分回路21を用いた場合に測定波形にドループが発生することが問題である。ドループとは、コイルの出力信号が小さい場合に、特に低周波領域では積分回路の出力波形が減衰してしまい、積分動作が不完全の状態で出力される現象をいう。図19は、パルスジェネレータからパルス幅10μsのパルスを入力して半導体チップ(IGBT)を動かしたときに積分回路21から得られた出力波形図(1〜8ch)であり、ドループが発生していることが分かる。ドループが発生すると、測定されるべき本来の電流波形が得られないという問題が生じる。

【0036】

このドループを解消する手法を図20に示す。図20において、磁束検出コイルの出力電圧は同軸ケーブルを介して積分回路21に入力され積分される。積分回路21の出力波形には、特に低周波の場合、ドループが発生するため測定波形を補償する必要がある。ディジタルドループ補償システム31では、積分回路21からの出力をA/D変換器に入力することによりアナログの測定データをディジタルのデータに変換してドループ波形の補償を行う(S1)。アナログの測定データをディジタルのデータに変換することにより、ドループ補償のデータ処理を行うことが容易になる。次にオフセット電圧の値を検出し測定データからオフセット電圧の値を減算することにより測定データからオフセット電圧を取り去る(S2)。測定データからオフセット電圧を除去することにより、ドループ補償を行なった際に波形が傾くのを補正している。次にオフセット電圧を取り除いたデータを時間積分して1/CR倍する(S3)。ここで、C、Rは積分回路のフィードバックのキャパシタンスと抵抗値である。C=C0+ΔC,R=R0+ΔR(C0とR0はそれぞれキャパシタンスと抵抗値の数値,ΔCとΔRはそれぞれキャパシタンスと抵抗値の誤差を補正するための補正値)としてS3のデータ処理プログラムを組むことにより、磁束検出装置10を複数個用いて電流を測定する場合に、各チャンネルごとに積分回路21のフィードバックのCR定数のばらつきの影響を無くし、全てのチャンネルで精度の揃った測定を行うことができる。さらに、S2とS3で求めたデータを加え(S4)、定数倍する(S5)。これにより、ドループ補償した波形が得られる。S5の定数倍する過程では、ドループ補償波形と測定電流の大きさが1対1に対応するように調整する。ドループが補償されたことは、ディスプレイ32で確認することができる。

【0037】

上記のドループ補償方法を実施する例としては、ディジタル・オシロスコープから得た測定波形のデータをコンピュータに取り入れてEXCEL(登録商標)上でS2〜S5の処理を行う方法やデジタイザーから得た測定波形のデータをLabVIEW(ビジュアルプログラミング言語)上で組んだプログラム(S2〜S5の処理を行うプログラム)によりドループ補償して波形を表示する方法などがある。

【0038】

ドループの補償を、ディジタルデータを用いて行うことにより、アナログの場合に比べてデータの処理が容易になり、波形のひずみやノイズの影響を受けにくくなる利点がある。また、この方法では、コンピュータ内で組んだプログラムによりデータの処理を行うことができるためコストの面でも有効である。デジタイザーにより得た測定波形のデータをLabVIEW上で処理して補償した例を図21に示す。

【0039】

図22は、従来のCTプローブと本発明の電流プローブ1〜8chの電流波形の和を示す図である。この図から、CTプローブと本発明の電流プローブとの電流波形が一致していることが分かる。

【0040】

図24は、図23の実験回路において、半導体チップ(IGBTモジュール)61のゲートにパルス幅50μsのパルスを入力し、コレクタ−エミッタ間に20Vの直流電圧を印加して電流を流し、IGBTモジュールに流れる電流を測定した実験のゲート電圧波形とCTプローブ51の電流波形を示した図である。この図から、IGBTモジュールが動いている間にパワー回路40に流れる電流の様子が分かる。

【0041】

図25は、図23の実験回路において、パワー回路40に電流が流れている際に積分回路21の各チャンネル(1〜8ch)の出力電圧波形を示したものである。この図から、パワー回路40に電流が流れIGBTモジュール内の各ボンディングワイヤ62に電流が流れるのを磁束検出装置(1〜8ch)10が検出し積分回路により電流波形に変換された様子が分かる。ただし、この場合では、積分回路21の波形にはドループが発生しており、本来の電流波形は示されていない。(ここで、図25中のslotとは、デジタイザー33の信号入力部分であり、一つのslotに複数の信号を入力することができる。図23の実験回路では一つのslotに2ch分の信号入力し、4slotを使用して実験を行った。)

【0042】

図26は、LabVIEWでドループ補正した電流波形の図である。この図から、IGBTモジュール内の各ボンディングワイヤに流れている電流の様子が分かる。

【産業上の利用可能性】

【0043】

本発明は、高密度化されている半導体の電流測定対象の配線を切断・変更する必要がなく、回路パラメータに影響を与えずに電流を測定できる電流測定装置として、小型化・高密度化が進んでいるIGBTその他のパワー半導体回路の電流測定に好適に利用することができる。

【符号の説明】

【0044】

1 ベース基板

2,3 カバーレイ

4 基板固定用ネジ穴

10 磁束検出装置

20 積分装置

21 積分回路

30 電流波形観測装置

31 ディジタルドループ補償システム

32 ディスプレイ

33 デジタイザー

40 パワー回路

41 ゲートドライブ回路

42 パワー半導体

43 抵抗

44 コンデンサ

45 直流電源

51 CTプローブ

61 半導体チップ

62 ボンディングワイヤ

P11A,P11B,P12A,P12B スルーホール

C1,C2 磁束検出コイル

W 配線

【特許請求の範囲】

【請求項1】

測定電流から生じる磁束を検出する磁束検出装置と、

前記磁束検出装置の出力電圧を電流波形に変換する積分装置と、

前記積分装置によって変換された電流波形を視覚化する電流波形観測装置とを有し、

前記磁束検出装置は、回路基板の両面に導電パターンにより形成した一対の表裏対称な形状をした第1コイルと、かつ測定配線を配置する位置に対して前記第1コイルと線対称に第2コイルを配置し、前記第1コイルおよび前記第2コイルのそれぞれの表の巻き終わりの導電パターンと裏の巻き始めの導電パターンの端部間、および前記第1コイルの巻き終わりの導電パターンの端部と前記第2コイルの巻き始めの導電パターンの端部間とを、それぞれ前記回路基板を貫通するスルーホールにより接続した構造とした電流測定装置。

【請求項2】

前記第1コイルの巻き終わりの導電パターンの端部と前記第2コイルの巻き始めの導電パターンの端部間とを前記回路基板の裏表間で接続しているスルーホールを、前記第1コイルおよび前記第2コイルの形成領域より外側の位置に配置した構造を有する請求項1記載の電流測定装置。

【請求項3】

前記電流波形観測装置において、測定した電流波形にドループが発生していた場合に測定波形のディジタルデータを用いて、測定波形データからオフセット電圧の値を減算することによるオフセット除去処理、オフセット除去処理後の測定波形データの時間積分及び積分回路のフィードバックCR時定数による除算を行う積分処理、オフセット除去処理後の測定データに積分処理後の測定データを加える加算処理、加算処理後の測定波形データを電流波形の大きさと一致させるために定数倍する定数倍処理を経てドループ補償を行う手段を設けた請求項1または2に記載の電流測定装置。

【請求項1】

測定電流から生じる磁束を検出する磁束検出装置と、

前記磁束検出装置の出力電圧を電流波形に変換する積分装置と、

前記積分装置によって変換された電流波形を視覚化する電流波形観測装置とを有し、

前記磁束検出装置は、回路基板の両面に導電パターンにより形成した一対の表裏対称な形状をした第1コイルと、かつ測定配線を配置する位置に対して前記第1コイルと線対称に第2コイルを配置し、前記第1コイルおよび前記第2コイルのそれぞれの表の巻き終わりの導電パターンと裏の巻き始めの導電パターンの端部間、および前記第1コイルの巻き終わりの導電パターンの端部と前記第2コイルの巻き始めの導電パターンの端部間とを、それぞれ前記回路基板を貫通するスルーホールにより接続した構造とした電流測定装置。

【請求項2】

前記第1コイルの巻き終わりの導電パターンの端部と前記第2コイルの巻き始めの導電パターンの端部間とを前記回路基板の裏表間で接続しているスルーホールを、前記第1コイルおよび前記第2コイルの形成領域より外側の位置に配置した構造を有する請求項1記載の電流測定装置。

【請求項3】

前記電流波形観測装置において、測定した電流波形にドループが発生していた場合に測定波形のディジタルデータを用いて、測定波形データからオフセット電圧の値を減算することによるオフセット除去処理、オフセット除去処理後の測定波形データの時間積分及び積分回路のフィードバックCR時定数による除算を行う積分処理、オフセット除去処理後の測定データに積分処理後の測定データを加える加算処理、加算処理後の測定波形データを電流波形の大きさと一致させるために定数倍する定数倍処理を経てドループ補償を行う手段を設けた請求項1または2に記載の電流測定装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【公開番号】特開2013−76569(P2013−76569A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−215005(P2011−215005)

【出願日】平成23年9月29日(2011.9.29)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 2011年7月23日、http://www.sciencedirect.com/science/article/pii/S0026271411002149にてWeb公開した「Tiny−scale“stealth”current sensor to probe power semiconductor device failure」

【出願人】(504174135)国立大学法人九州工業大学 (489)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月29日(2011.9.29)

【新規性喪失の例外の表示】特許法第30条第1項適用申請有り 2011年7月23日、http://www.sciencedirect.com/science/article/pii/S0026271411002149にてWeb公開した「Tiny−scale“stealth”current sensor to probe power semiconductor device failure」

【出願人】(504174135)国立大学法人九州工業大学 (489)

【Fターム(参考)】

[ Back to top ]